(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5704848号

(P5704848)

(45) 発行日 平成27年4月22日(2015.4.22)

(24) 登録日 平成27年3月6日(2015.3.6)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/146 | (2006.01) |

| HO 4 N 5/369  | (2011.01) |

| HO 4 N 5/357  | (2011.01) |

| HO 4 N 5/374  | (2011.01) |

| HO 1 L        | 27/14     |

| HO 4 N        | 5/335     |

| HO 4 N        | 5/335     |

| HO 4 N        | 5/335     |

請求項の数 10 (全 12 頁)

(21) 出願番号 特願2010-150252 (P2010-150252)

(22) 出願日 平成22年6月30日 (2010.6.30)

(65) 公開番号 特開2012-15315 (P2012-15315A)

(43) 公開日 平成24年1月19日 (2012.1.19)

審査請求日 平成25年6月27日 (2013.6.27)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置およびカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置であって、

前記画素アレイ領域に配置された光電変換素子と、

前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、

前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、

前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、CMPによって平坦化された層間絶縁膜と、

前記層間絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の上面および前記光電変換素子との間に配置され、前記光電変換素子へ向かう光の反射を低減する第1絶縁膜と、

前記層間絶縁膜と前記周辺MOSトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、

前記第1絶縁膜および前記第2絶縁膜は、積層膜であり、

前記第1絶縁膜は、前記増幅MOSトランジスタの前記ゲート電極の前記上面および前記光電変換素子のほか、前記増幅MOSトランジスタの前記ゲート電極の側面を覆うように広がっていて、前記第1絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の前記側面との間にサイドウォールがない、

10

20

ことを特徴とする固体撮像装置。

【請求項 2】

前記周辺MOSトランジスタの前記ゲート電極の側面に配置されたサイドウォールを更に備え、

前記周辺MOSトランジスタは、LDD構造を有し、

前記第1絶縁膜および前記層間絶縁膜の少なくとも1つは、シリコン酸化物を含む積層膜であり、

前記サイドウォールは、シリコン酸化物を含む積層膜である、

ことを特徴とする請求項1に記載の固体撮像装置。

【請求項 3】

前記周辺回路領域に配置された導電体パターンの上面の上に配置された第3絶縁膜を更に備え、

前記導電体パターンは、前記周辺MOSトランジスタの前記ゲート電極の材料と同一の材料で構成され、前記第3絶縁膜は、前記第2絶縁膜の材料と同一の材料で構成されている、

ことを特徴とする請求項1に記載の固体撮像装置。

【請求項 4】

画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置であって、

前記画素アレイ領域に配置された光電変換素子と、

前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、

前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、

前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、CMPによって平坦化された層間絶縁膜と、

前記層間絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の上面との間に配置された第1絶縁膜と、

前記層間絶縁膜と前記周辺MOSトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、

前記第1絶縁膜は、前記光電変換素子と、前記増幅MOSトランジスタの前記ゲート電極の側面とを覆うように広がっていて、前記第1絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の前記側面との間にサイドウォールがなく、前記層間絶縁膜は、コンタクトホールを有し、前記第2絶縁膜は、開口を有し、前記周辺MOSトランジスタの前記ゲート電極に接続されたコンタクトプラグが前記開口を通して前記コンタクトホールに配置され、前記開口の面積は、前記コンタクトホールの面積より大きい、

ことを特徴とする固体撮像装置。

【請求項 5】

画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置であって、

前記画素アレイ領域に配置された光電変換素子と、

前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、

前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、

前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、CMPによって平坦化された層間絶縁膜と、

前記層間絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の上面との間に配置された第1絶縁膜と、

前記層間絶縁膜と前記周辺MOSトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、

前記第1絶縁膜は、前記光電変換素子と、前記増幅MOSトランジスタの前記ゲート電

10

20

30

40

50

極の側面とを覆うように広がっていて、前記第1絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の前記側面との間にサイドウォールがなく、

前記第1絶縁膜および前記第2絶縁膜は、シリコン窒化物およびシリコン酸窒化物の少なくとも一方で構成される、

ことを特徴とする固体撮像装置。

【請求項6】

画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置であって、

前記画素アレイ領域に配置された光電変換素子と、

前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、10

前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、

前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、CMPによって平坦化された層間絶縁膜と、

前記層間絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の上面との間に配置された第1絶縁膜と、

前記層間絶縁膜と前記周辺MOSトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、

前記第1絶縁膜は、前記光電変換素子と、前記増幅MOSトランジスタの前記ゲート電極の側面とを覆うように広がっていて、前記第1絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の前記側面との間にサイドウォールがなく、20

前記第1絶縁膜は、シリコン酸化膜およびシリコン窒化膜を含み、前記シリコン窒化膜は、前記シリコン酸化膜と前記光電変換素子との間に配置され、前記第2絶縁膜は、シリコン酸化膜およびシリコン窒化膜を含み、前記第2絶縁膜の前記シリコン窒化膜は、前記第2絶縁膜の前記シリコン酸化膜と前記周辺MOSトランジスタの前記ゲート電極の前記上面との間に配置されている、

ことを特徴とする固体撮像装置。

【請求項7】

前記第1絶縁膜および前記第2絶縁膜が同一の材料で構成され、該材料は、前記層間絶縁膜の材料とは異なる、30

ことを特徴とする請求項1乃至6のいずれか1項に記載の固体撮像装置。

【請求項8】

画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置であって、

前記画素アレイ領域に配置された光電変換素子と、

前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、

前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、

前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、CMPによって平坦化された層間絶縁膜と、40

前記層間絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の上面との間に配置された第1絶縁膜と、

前記層間絶縁膜と前記周辺MOSトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、

前記第1絶縁膜は、前記光電変換素子と、前記増幅MOSトランジスタの前記ゲート電極の側面とを覆うように広がっていて、前記第1絶縁膜と前記増幅MOSトランジスタの前記ゲート電極の前記側面との間にサイドウォールがなく、

前記層間絶縁膜は、前記周辺MOSトランジスタの前記ゲート電極の前記上面に接触し、50

前記周辺MOSトランジスタの前記ゲート電極の前記上面の上に配置された前記第2絶

縁膜の面積は、前記周辺MOSトランジスタの前記ゲート電極の前記上面の面積より小さい。

ことを特徴とする固体撮像装置。

#### 【請求項9】

前記第1絶縁膜は、複数の画素にわたって前記光電変換素子を覆っている、

ことを特徴とする請求項1乃至8のいずれか1項に記載の固体撮像装置。

#### 【請求項10】

請求項1乃至9のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とするカメラ。 10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、固体撮像装置およびそれを備えるカメラに関する。

##### 【背景技術】

##### 【0002】

固体撮像装置における層間絶縁膜の表面を平坦化するためにCMP (Chemical Mechanical Polishing)と呼ばれる平坦化技術が使用される。特許文献1には、チップ全体にわたる層間絶縁膜の表面の高低差であるグローバル段差を低減する技術が開示されている。具体的には、特許文献1には、画素領域におけるフォトダイードを被覆する絶縁膜と、周辺回路領域およびスクライブレーン領域におけるゲート電極ダミーを被覆する絶縁膜とを同時に形成し、これらの絶縁膜の上に層間絶縁膜を形成することが開示されている。ここで、周辺回路領域に配置されるゲート電極ダミーは、MOSトランジスタのゲート電極および配線が密集していないスペースに形成される。また、フォトダイードを被覆する絶縁膜と同時に周辺回路領域に形成される絶縁膜は、周辺回路領域に配置されたMOSトランジスタのゲート電極の上には形成されない。 20

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

##### 【特許文献1】特開2008-098373号公報 30

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

特許文献1に記載された固体撮像装置では、フォトダイードを被覆する絶縁膜と同時に周辺回路領域に形成される絶縁膜は、周辺回路領域においてMOSトランジスタのゲート電極の上や、ポリシリコン配線が密集していないスペースには形成されない。そのため、該保護膜による半導体基板の被覆率が画素領域と周辺回路領域とで異なり、許容できないグローバル段差が残りうる。その結果、例えば、画素領域の中心部と画素領域の周縁部とで感度が異なり、シェーディングが生じうる。

##### 【0005】

本発明は、上記の課題認識を契機としてなされたものであり、固体撮像装置における層間絶縁膜の表面を平坦化するために有利な技術を提供することを目的とする。

##### 【課題を解決するための手段】

##### 【0006】

本発明の1つの側面は、画素アレイ領域と、前記画素アレイ領域の外に配置された周辺回路領域とを有する固体撮像装置に係り、前記固体撮像装置は、前記画素アレイ領域に配置された光電変換素子と、前記画素アレイ領域に配置され、ゲート電極を有し、前記光電変換素子が発生した電荷に応じた信号を出力する増幅MOSトランジスタと、前記周辺回路領域に配置され、ゲート電極を有する周辺MOSトランジスタと、前記光電変換素子、前記増幅MOSトランジスタおよび前記周辺MOSトランジスタを覆うように配置され、 50

C M P によって平坦化された層間絶縁膜と、前記層間絶縁膜と前記増幅M O Sトランジスタの前記ゲート電極の上面および前記光電変換素子との間に配置され、反射を防止する第1絶縁膜と、前記層間絶縁膜と前記周辺M O Sトランジスタの前記ゲート電極の上面との間に配置された第2絶縁膜とを備え、前記第1絶縁膜および前記第2絶縁膜は、積層膜であり、前記第1絶縁膜は、前記増幅M O Sトランジスタの前記ゲート電極の前記上面および前記光電変換素子のほか、前記増幅M O Sトランジスタの前記ゲート電極の側面を覆うように広がっていて、前記第1絶縁膜と前記増幅M O Sトランジスタの前記ゲート電極の前記側面との間にサイドウォールがない。

## 【発明の効果】

## 【0007】

10

本発明によれば、固体撮像装置における層間絶縁膜の表面を平坦化するために有利な技術が提供される。

## 【図面の簡単な説明】

## 【0008】

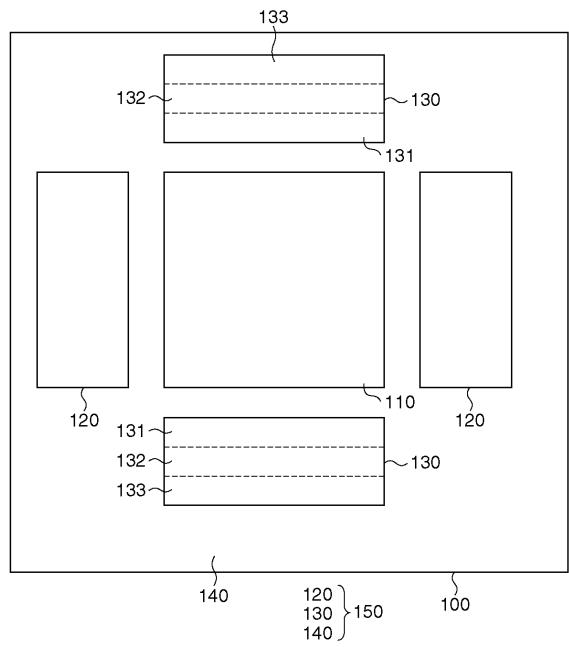

【図1】本発明の1つの実施形態における固体撮像装置の構成を例示する図である。

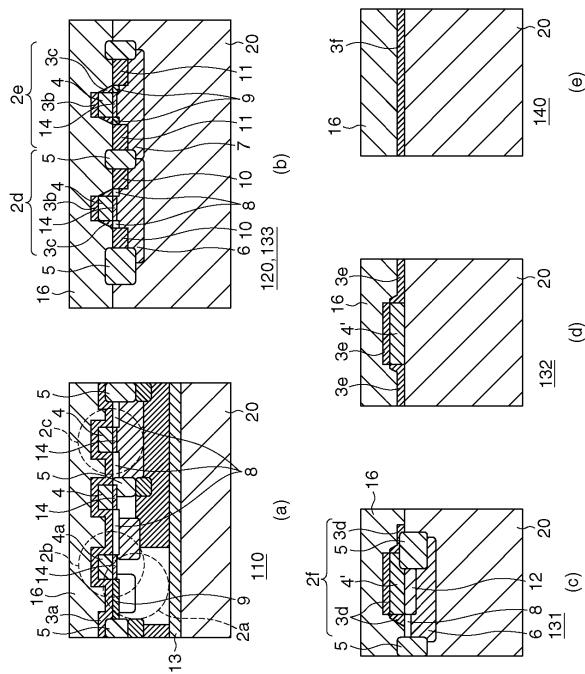

【図2】本発明の第1実施形態における固体撮像装置の断面構造を例示する図である。

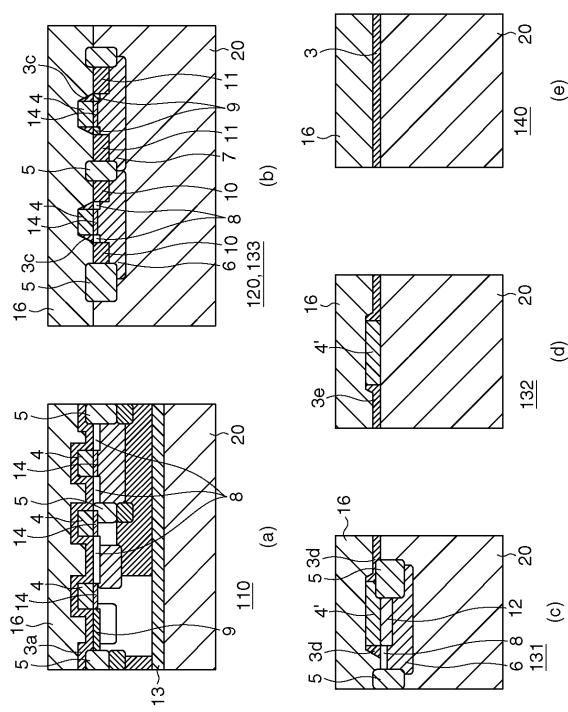

【図3】比較例を示す断面図である。

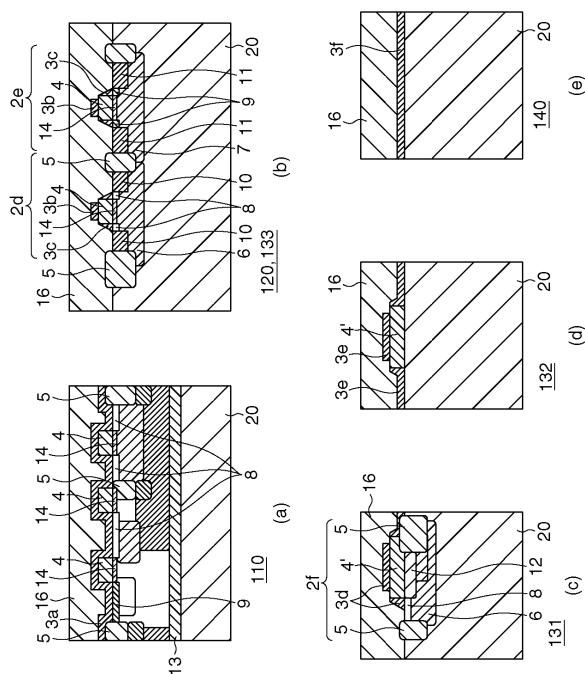

【図4】本発明の第2実施形態における固体撮像装置の断面構造を例示する図である。

【図5】素子分離部の上に配置された導電体パターンおよびその周辺の構造を例示する断面図である。

20

【図6】本発明の第3実施形態における固体撮像装置の断面構造を例示する図である。

【図7】本発明の第3実施形態における固体撮像装置のコントラクトプラグおよびその周辺を例示する平面図である。

## 【発明を実施するための形態】

## 【0009】

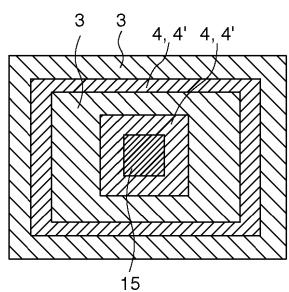

図1を参照しながら本発明の1つの実施形態における固体撮像装置100の構成を説明する。固体撮像装置100は、複数の画素が二次元状に配列された画素アレイ領域110と、画素アレイ領域110の外側に配置された周辺回路領域150とを含みうる。画素アレイ領域110は、行方向に延びる複数の制御線（例えば、転送信号線、リセット信号線）と、列方向に延びる複数の列信号線とを含む。画素アレイ領域110に配列された各画素は、入射光を電荷に変換する光電変換素子と、該光電変換素子で発生した電荷を電荷電圧変換部（フローティングディフュージョン）に転送するチャネルを形成する転送ゲート電極（転送M O Sトランジスタ）とを含みうる。転送ゲート電極は、転送信号線を介して行選択回路120によって駆動される。電荷電圧変換部は、各画素に設けられてもよいし、複数の画素によって共有されてもよい。各画素、または、電荷電圧変換部を共有する複数の画素で構成される各グループは、電荷電圧変換部の電圧に応じた信号を列信号線に出力する増幅M O Sトランジスタ、電荷電圧変換部の電圧をリセットするリセットM O Sトランジスタを含みうる。リセットM O Sトランジスタは、リセット信号線を介して行選択回路120によって駆動される。

30

## 【0010】

40

周辺回路領域150は、例えば、行選択回路120と、読み出し回路130と、低密度領域140とを含みうる。読み出し回路130は、行選択回路120は、複数の制御線（例えば、転送信号線、リセット信号線、行選択線）を駆動しながら画素アレイ領域110における行を選択する。読み出し回路130は、例えば、読み出し回路131と、スイッチ回路132と、列選択回路133とを含みうる。低密度領域140は、例えば、入出力回路を含みうる。読み出し回路131は、複数の容量素子を含み、複数の列信号線を介して画素アレイ領域110の画素から出力される信号を増幅して該複数の容量素子にそれぞれ格納する。列選択回路133は、列を選択する。スイッチ回路132は、読み出し回路131に配置された複数の容量素子のうち列選択回路133によって選択された列に対応する容量素子に格納された信号を水平信号線（不図示）を介して出力アンプに出力するた

50

めのスイッチ群を含む。

#### 【0011】

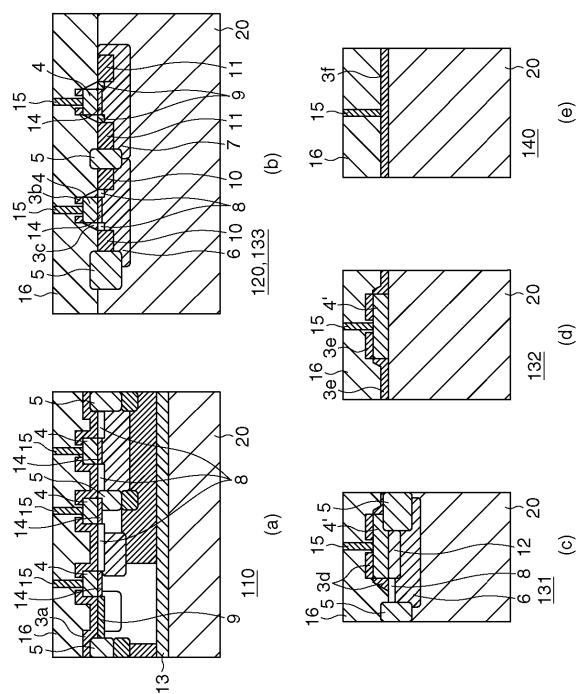

図2を参照しながら本発明の第1実施形態における固体撮像装置を説明する。図2は、図1に示す固体撮像装置100における各領域の構成の一部を例示的に示す断面図である。固体撮像装置100は、シリコン基板(半導体基板)20に形成されている。図2(a)は、画素アレイ領域110の画素の構成を例示する断面図である。図2(b)は、行選択回路120および列選択回路133の一部の構成を例示する断面図である。図2(c)は、読み出し回路131の一部の構成を例示する断面図である。図2(d)は、スイッチ回路132の一部の構成を例示する断面図である。図2(e)は、低密度領域140の一部の構成を例示する断面図である。

10

#### 【0012】

各画素は、埋込みフォトダイオードからなる光電変換素子2aと、転送MOSトランジスタ2bと、増幅MOSトランジスタ2cと、リセットMOSトランジスタ(不図示)とを含みうる。各画素は、半導体領域(例えば、N型半導体基板)20の上に形成されたP型領域13の上に形成されうる。転送MOSトランジスタ2bのゲート電極である転送ゲート電極4aは、その下に電荷の転送のためのチャネルを形成する。リセットMOSトランジスタは、増幅MOSトランジスタ2cと同様の構成を有しうる。転送MOSトランジスタ2b、増幅MOSトランジスタ2cおよびリセットMOSトランジスタを画素内MOSトランジスタと呼ぶ。画素内MOSトランジスタは、ゲート電極4、4a、その下に配置されたゲート絶縁膜14および拡散領域(例えば、N+領域)8を含む。転送ゲート電極4aおよびゲート電極4は、同一の導電性材料(例えば、ポリシリコン)により同一の工程において形成される。転送MOSトランジスタ2bの光電変換素子2aとゲート電極4aを挟んで対向して配置された拡散領域8の下部には、P型の領域が配置されうる。

20

#### 【0013】

行選択回路120および列選択回路133は、図2(b)に例示されるNMOSトランジスタ2dおよびPMOSトランジスタ2eが密集した領域を含みうる。読み出し回路131は、図2(c)に例示される容量素子2fが密集した領域を含みうる。スイッチ回路132は、図2(d)に例示される配線パターンが密集した領域を含みうる。低密度領域140は、図2(e)に例示されるように、低密度にしか配置されていない領域である。低密度領域140は、は、回路素子やパターンが存在しない領域を含みうる。周辺回路領域150のNMOSトランジスタ2dは、Pウェル6に形成され、ゲート電極4、ゲート電極4の下に配置されたゲート絶縁膜14、および、拡散領域8、10を含む。周辺回路領域150のPMOSトランジスタ2eは、Nウェル7に形成され、ゲート電極4、ゲート電極4の下に配置されたゲート絶縁膜14、および、拡散領域9、11を含む。

30

#### 【0014】

光電変換素子2aの上面、転送ゲート電極4aの上面の少なくとも一部および側面、ゲート電極4の上面の少なくとも一部および側面を覆うように第1絶縁膜3aが配置されている。典型的には、画素アレイ領域110は、コンタクトプラグ等が配置される領域を除き、その全体が第1絶縁膜3aで覆われうる。第1絶縁膜3aは、光電変換素子2aを保護する保護膜として機能する。第1絶縁膜3aは、例えば、(a)シリコン酸化膜、(b)シリコン窒化酸化膜、(c)シリコン窒化膜、および、(d)これらの全部又は一部の積層膜、のいずれかでありうる。シリコン基板と第1絶縁膜との界面における反射の防止効果を考慮すると、シリコン基板側にシリコン窒化膜、その上にシリコン酸化膜又はシリコン窒化酸化膜を積層する2層構成であることが好ましい。

40

#### 【0015】

MOSトランジスタ、光電変換素子、容量素子などの素子は、素子分離部5によって相互に分離される。素子分離部5は、例えば、STI(Shallow Trench Isolation)構造を有しうる。素子分離部5によって囲まれた領域は、素子が形成される活性領域である。拡散領域8は、N+領域、拡散領域10はN++領域である。拡散領域9はP+領域、拡散領域11はP++領域である。

50

## 【0016】

読み出し回路131に配置される容量素子2fは、Pウェル6に下部電極としてのN領域12を形成し、N領域12の上に上部電極としての導電体パターン4'を配置した構造を有する。そしてN領域12と電気的に接続した拡散領域8を有する。この容量素子2fにおける拡散領域8は下部電極の端子として機能する。ここで、導電体パターン4'は、転送ゲート電極4aおよびゲート電極4と同一の導電性材料（例えば、ポリシリコン）により同一の工程において形成されうる。スイッチ回路132は、導電体パターン4'を配線パターンとして有する。なお、読み出し回路131及びスイッチ回路132における導電体パターン4'の下部には、ゲート絶縁膜14が配置されてうる。

## 【0017】

周辺回路領域150は、周辺回路領域150に配置されたMOSトランジスタ2d、2eのゲート電極4のそれぞれの上面の上に配置された第2絶縁膜3bを有する。第2絶縁膜3bは、第1絶縁膜3aと同一の材料で構成されうる。MOSトランジスタ2d、2eのゲート電極4の側面には、サイドウォール3cが形成されている。サイドウォール3cは、第1絶縁膜3aおよび第2絶縁膜3bと同一の材料で構成されてもよいし、異なる材料で構成されてもよい。

## 【0018】

周辺回路領域150は、周辺回路領域150に配置された容量素子2fの上部電極としての導電体パターン4'の上面の上に配置された第3絶縁膜3dを有しうる。第3絶縁膜3dは、更に、容量素子2fの上部電極としての導電体パターン4'の周囲領域を覆ってもよい。第3絶縁膜3dは、第1絶縁膜3aおよび第2絶縁膜3bと同一の材料で構成されうる。

## 【0019】

周辺回路領域150は、スイッチ回路132に配置された配線パターンとしての導電体パターン4'の上面の上に配置された第4絶縁膜3eを有しうる。第4絶縁膜3eは、更に、スイッチ回路132に配置された配線パターンとしての導電体パターン4の周囲における半導体基板20を覆ってもよい。第4絶縁膜3eは、第1絶縁膜3aおよび第2絶縁膜3bと同一の材料で構成されうる。周辺回路領域150はまた、低密度領域140における半導体基板20を覆うように第5絶縁膜3fを有しうる。第5絶縁膜3fは、第1絶縁膜3aおよび第2絶縁膜3bと同一の材料で構成されうる。ここで、絶縁膜3a、3b、3d、3e、3fおよびサイドウォール3cは、典型的には、同一の材料で構成される。絶縁膜3a、3b、3d、3e、3fおよびサイドウォール3cを覆うように絶縁膜3a、3b、3d、3e、3fおよびサイドウォール3cに接して層間絶縁膜16が形成される。層間絶縁膜16の表面は、CMPによって平坦化される。なお、絶縁膜3d、3e、3fは任意的な構成要素である。何故なら、読み出し回路131およびスイッチ回路132にもMOSトランジスタが含まれ、そのMOSトランジスタのゲート電極の上にも第2絶縁膜3bが形成され、これが平坦化に寄与するからである。

## 【0020】

以上のような構成によれば、絶縁膜3a、3b、3d、3e、3fを含む絶縁層（以下、これらを纏めて絶縁膜3と記載することもある。）による半導体基板の被覆率差（密度差）が小さくなり、画素アレイ領域110と周辺回路領域150との間ににおける段差が低減される。これによって、層間絶縁膜16の表面の平坦性が向上し、例えば、画素アレイ領域110の中心部と周縁部との感度差が小さくなり、シェーディングが改善される。

## 【0021】

図2(b)に例示するように、周辺回路領域150におけるMOSトランジスタ2d、2eのゲート電極4の側面には、サイドウォール3cが形成されうる。ゲート電極4およびサイドウォール3cを介してPウェル6およびNウェル7（または、半導体基板20）にイオンを注入することによってMOSトランジスタ2d、2eをLDD構造にことができる。NMOSトランジスタ2dは、ゲート電極4と、ゲート絶縁膜14とを有するほか、ソース又はドレイン領域として、N++拡散領域10と、N++拡散領域10より

10

20

30

40

50

も低濃度のP+拡散領域8とを有する。PMOSトランジスタ2eは、ゲート電極4と、ゲート絶縁膜14とを有するほか、ソース又はドレイン領域として、P++拡散領域11と、P++拡散領域11よりも低濃度のP+拡散領域9とを有する。

#### 【0022】

1つの実施形式において、画素アレイ領域110における絶縁膜3aによる被覆率(密度)は、最大でほぼ100%にすることができる。行選択回路120および列選択回路133における絶縁膜3bによる被覆率(密度)は、行選択回路120および列選択回路133の全体面積の20~30%でありうる。読み出し回路131における絶縁膜3dによる被覆率は、読み出し回路131の全体面積の50%~60%でありうる。スイッチ回路132における絶縁膜3eによる被覆率は、スイッチ回路132の全体面積のほぼ100%とすることが可能である。10

#### 【0023】

図3は、比較例を示す断面図である。図3に示す比較例では、周辺回路領域150(120、131、132、133、140)におけるゲート電極4および導電体パターン4'の上には絶縁膜3b、3d、3eに相当する絶縁膜が配置されていない。一方、画素アレイ領域110には、絶縁膜3aが配置されている。よって、層間絶縁膜16の堆積後にその表面に大きな段差が形成され、層間絶縁膜16の表面をCMPによって平坦化した後にも相応の段差が残る。

#### 【0024】

周辺回路領域150に配置されたゲート電極4および導電体パターン4'の上に絶縁膜3を配置することにより、層間絶縁膜16の下における画素アレイ領域110と周辺回路領域150における高さを等しくすることができる。これも、グローバル段差の低減に寄与する。20

#### 【0025】

図4を参照しながら本発明の第2実施形態における固体撮像装置を説明する。なお、第2実施形態として言及しない事項は、第1実施形態に従う。第2実施形態では、周辺回路領域150に配置されたMOSトランジスタ2d、2eのゲート電極4の上に配置された第2絶縁膜3bの幅(面積)がゲート電極4の幅(面積)よりも小さい。この構成は、光電変換素子および拡散領域8、7、9の形成時に第2絶縁膜3bがマスクとなってMOSトランジスタ2d、2eのゲート電極4の近傍にイオンが注入されにくいう問題を解決するために有用である。特に、半導体基板20の表面に垂直な方向から傾けてイオン注入する際に有用である。これは、容量素子においても同様であり、容量素子2fの上部電極としての導電体パターン4'の上面に配置される第3絶縁膜3dの幅(面積)を導電体パターン4'の幅(面積)よりも小さくすることが望ましい。30

#### 【0026】

MOSトランジスタ2d、2eのゲート電極4の上の第2絶縁膜3bの幅および容量素子2fの導電体パターン4'の上の第3絶縁膜3dの幅(面積)は、上記のイオン注入における問題を解決できる範囲で最大にすることが望ましい。これは、画素アレイ領域110と周辺回路領域150との間ににおける絶縁膜3による被覆率の差を小さくするためである。40

#### 【0027】

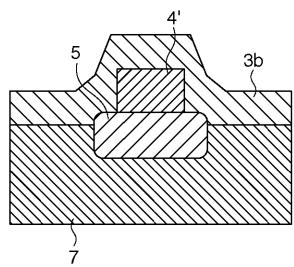

図5は、Nウェル7に配置された素子分離部5の上に配置された導電体パターン4'およびその周辺の構造を例示する断面図である。素子分離部5の上に配置された導電体パターン4'は、その上面および側面、更にはその周辺部分が第2絶縁膜3bによって覆われている。これは、素子分離部5の上に配置された導電体パターン4'は、ソースおよびドレインを形成するためのイオン注入におけるマスクとして機能させる必要がないからである。ただし、素子分離部5の上に配置された導電体パターン4'の上に配置する第2絶縁膜3bについても、その幅(面積)を導電体パターン4'の幅(面積)よりも小さくしてもよい。

#### 【0028】

10

20

30

40

50

第2実施形態によれば、第1実施形態の効果に加えて、イオン注入時における絶縁膜3によるシャドウイングを低減することができるという付加的な効果を提供することができる。

#### 【0029】

図6および図7を参照しながら本発明の第3実施形態における固体撮像装置を説明する。図6に示す固体撮像装置100における各領域の構成の一部を例示的に示す断面図である。図7は、図6におけるコンタクトプラグおよびその周辺を示す平面図である。なお、第2実施形態として言及しない事項は、第1又は第2実施形態に従う。第3実施形態では、第1又は第2実施形態で説明した工程の後におけるコンタクトホールおよびコンタクトプラグの形成工程を説明する。

10

#### 【0030】

ここでは、絶縁膜3(3a、3b、3c、3d、3e、3f)は、反射防止に有効なシリコン窒化膜とシリコン酸化膜との積層膜であり、ゲート電極4および導電体パターン4'は、ポリシリコンであるものとする。また、層間絶縁膜16は、シリコン酸化膜であるものとする。ポリシリコンで構成されたゲート電極4および導電体パターン4'にコンタクトプラグ15を電気的に接続させるためには工夫が必要である。なぜなら、層間絶縁膜16を構成するシリコン酸化膜にコンタクトホールを形成するために、シリコン酸化膜をエッチングすることができるエッチングガスが使用される。このガスは、一般的にはシリコン窒化膜をエッチングしないため、ポリシリコンで構成されたゲート電極4および導電体パターン4'のコンタクト領域の上に絶縁膜3を構成するシリコン窒化膜が残ってしまう。このシリコン窒化膜が残ると、コンタクトプラグ15とゲート電極4および導電体パターン4'が電気的に接続されないことになる。

20

#### 【0031】

よって、第3実施形態では、第1絶縁膜3aは、転送ゲート電極4aの上に開口部を有し、該開口部を通してコンタクトプラグ15が転送ゲート電極4aに接続され、該開口部の面積がコンタクトプラグ15の底面積よりも大きい。同様に、第1絶縁膜3aは、ゲート電極4の上に開口部を有し、該開口部を通してコンタクトプラグ15がゲート電極4に接続され、該開口部の面積がコンタクトプラグ15の底面積よりも大きい。同様に、第2絶縁膜3bは、周回路領域150におけるゲート電極4の上に開口部を有し、該開口部を通してコンタクトプラグ15がゲート電極4に接続され、該開口部の面積がコンタクトプラグ15の底面積よりも大きい。同様に、第3絶縁膜3cは、周回路領域150における導電体パターン4'の上に開口部を有し、該開口部を通してコンタクトプラグ15が導電体パターン4'に接続され、該開口部の面積がコンタクトプラグ15の底面積よりも大きい。

30

#### 【0032】

ここで、絶縁膜3(3a、3b、3c、3d、3e、3f)の開口部は、絶縁膜3を形成するための絶縁体を半導体基板20の全面に堆積した後に、該絶縁体の不要部分を除去する際に同時に形成することができる。

#### 【0033】

以下、上記の各実施形態に係る固体撮像装置の応用例として、該固体撮像装置が組み込まれたカメラについて例示的に説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置(例えば、パーソナルコンピュータ、携帯端末)も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、該固体撮像装置から出力される信号を処理する処理部とを含む。該処理部は、例えば、A/D変換器、および、該A/D変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

40

【 図 1 】

【 図 2 】

【図3】

【 四 4 】

【図5】

【 义 6 】

【図7】

---

フロントページの続き

(72)発明者 秋山 健史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 成瀬 裕章

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 松野 靖司

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 山口 大志

(56)参考文献 特開2008-060357(JP,A)

特開2005-347655(JP,A)

特開2006-319158(JP,A)

特開2008-041726(JP,A)

特開2005-101442(JP,A)

特開2006-216615(JP,A)

特表2007-513495(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| H 01 L | 27 / 146 |

| H 04 N | 5 / 357  |

| H 04 N | 5 / 369  |

| H 04 N | 5 / 374  |