(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4460781号

(P4460781)

(45) 発行日 平成22年5月12日(2010.5.12)

(24) 登録日 平成22年2月19日(2010.2.19)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>G06F 13/00</b> | <b>(2006.01)</b> | G06F 13/00 | 301A |

| <b>G06F 5/00</b>  | <b>(2006.01)</b> | G06F 5/00  | S    |

| <b>G06F 13/12</b> | <b>(2006.01)</b> | G06F 13/12 | 330E |

| <b>H04L 29/08</b> | <b>(2006.01)</b> | H04L 13/00 | 307C |

請求項の数 14 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-585740 (P2000-585740)  |

| (86) (22) 出願日 | 平成11年12月2日 (1999.12.2)        |

| (65) 公表番号     | 特表2002-531888 (P2002-531888A) |

| (43) 公表日      | 平成14年9月24日 (2002.9.24)        |

| (86) 國際出願番号   | PCT/US1999/028805             |

| (87) 國際公開番号   | W02000/033166                 |

| (87) 國際公開日    | 平成12年6月8日 (2000.6.8)          |

| 審査請求日         | 平成13年9月12日 (2001.9.12)        |

| 審判番号          | 不服2005-17426 (P2005-17426/J1) |

| 審判請求日         | 平成17年9月12日 (2005.9.12)        |

| (31) 優先権主張番号  | 09/204,669                    |

| (32) 優先日      | 平成10年12月2日 (1998.12.2)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504107339<br>エミュレックス デザイン アンド マニ<br>ュファクチュアリング コーポレーション<br>アメリカ合衆国 92626 カリフォル<br>ニア州 コスタ メサ スーザンストリー<br>ト 3333 |

| (74) 代理人  | 100088971<br>弁理士 大庭 咲夫                                                                                          |

| (72) 発明者  | ヘンソン カール エム<br>アメリカ合衆国 カリフォルニア州 92<br>688 ランチョ サンタ マルガリータ<br>サン リカルド 2                                          |

最終頁に続く

(54) 【発明の名称】 8B／10Bデータ転送速度の自動検出

## (57) 【特許請求の範囲】

## 【請求項 1】

ネットワーク装置をネットワークに接続するポートであって、

(a) あるデータ転送速度を有するビットストリームをネットワークから受け取るデータ入力と、

(b) 前記データ入力に接続されると共に一つのクロック速度より多い速度で動作可能なデシリアライザであって、クロック速度が最高速度に設定され、前記データ入力を介して受け取ったビットストリームのキャラクタの境界に同期し、前記ビットストリームを非直列化し、該ビットストリーム内で第一のパターンを見つけ、該第一のパターンに対応するデータキャラクタを含む一つ以上のデータキャラクタを生成するデシリアライザと、

(c) 前記デシリアライザに接続されるネットワーク装置であって、前記デシリアライザから前記データキャラクタを受け取り、該データキャラクタ内で第二のパターンを認識することによって前記ビットストリームのデータ転送速度を決定し、前記デシリアライザにクロック制御信号を送り、該クロック制御信号に従って前記デシリアライザのクロック速度を前記認識された第二のパターンに基づいて決定されたビットストリームのデータ転送速度に合わせるように設定するネットワーク装置と、を有するポート。

## 【請求項 2】

前記ネットワークがファイバ・チャネル・ネットワークである請求項1に記載のポート。

## 【請求項 3】

10

前記ネットワークが 8 B / 10 B 符号化スキームを用いる請求項 1 に記載のポート。

**【請求項 4】**

前記デシリアルライザが毎秒 1 . 0 6 2 5 ギガビットの倍数であるデータ転送速度と互換性のあるクロック速度で動作可能である請求項 1 に記載のポート。

**【請求項 5】**

前記ネットワーク装置が、

( a ) 前記デシリアルライザから前記データキャラクタを受け取り、どのクロック速度が前記ビットストリームのデータ転送速度と対応するかを決定し、前記ビットストリームのデータ転送速度を示す制御信号を生成するパターン認識ロジックと、

( b ) 前記パターン認識ロジックと前記デシリアルライザとに接続されたデシリアルライザ制御回路であって、前記パターン認識ロジックから前記制御信号を受け取り、前記デシリアルライザにクロック制御信号を送り、該クロック制御信号に従って前記デシリアルライザのクロック速度を前記認識された第二のパターンに基づいて決定されたビットストリームのデータ転送速度に合わせるように設定するデシリアルライザ制御回路と、を有する請求項 1 に記載のポート。 10

**【請求項 6】**

前記パターン認識ロジックが前記デシリアルライザから受け取った前記データキャラクタ内で K 28 . 5 キャラクタを認識することによって前記ビットストリームのデータ転送速度を決定する請求項 5 に記載のポート。

**【請求項 7】**

ファイバ・チャネルのプロトコル装置をファイバ・チャネル・ネットワークに接続するノードポートであって、

( a ) あるデータ転送速度を有するビットストリームをファイバ・チャネル・ネットワークから受け取るデータ入力と、

( b ) 前記データ入力に接続されると共に一つのクロック速度より多い速度で動作可能なデシリアルライザであって、クロック速度が最高速度に設定され、前記データ入力を介して受け取ったビットストリームのキャラクタの境界に同期し、前記ビットストリームを非直列化し、該ビットストリーム内でコンマパターンを見つけ、該コンマパターンに対応する K 28 . 5 + キャラクタを含む一つ以上の 10 ビットデータキャラクタを生成するデシリアルライザと、 30

( c ) 前記デシリアルライザに接続されるファイバ・チャネルのプロトコル装置であって、前記デシリアルライザから前記 10 ビットデータキャラクタを受け取り、該 10 ビットデータキャラクタの前記コンマパターンの直ぐ後に続く第二のパターンを認識することによって前記ビットストリームのデータ転送速度を決定し、前記デシリアルライザにクロック制御信号を送り、該クロック制御信号に従って前記デシリアルライザのクロック速度を前記認識された第二のパターンに基づいて決定されたビットストリームのデータ転送速度に合わせるように設定するファイバ・チャネルのプロトコル装置と、を有するポート。

**【請求項 8】**

前記ファイバ・チャネルのプロトコル装置が、

( a ) 前記デシリアルライザから前記 10 ビットデータキャラクタを受け取り、どのクロック速度が前記ビットストリームのデータ転送速度と対応するかを決定し、前記ビットストリームのデータ転送速度を示す制御信号を生成するパターン認識ロジックと、 40

( b ) 前記パターン認識ロジックと前記デシリアルライザとに接続されたデシリアルライザ制御回路であって、前記パターン認識ロジックから前記制御信号を受け取り、前記デシリアルライザにクロック制御信号を送り、該クロック制御信号に従って前記デシリアルライザのクロック速度を前記認識された第二のパターンに基づいて決定されたビットストリームのデータ転送速度に合わせるように設定するデシリアルライザ制御回路と、を有する請求項 7 に記載のポート。

**【請求項 9】**

デシリアルライザのクロック速度を設定する方法であって、

10

20

30

40

50

- ( a ) デシリアルライザのクロック速度を最高速度に設定し、

- ( b ) 前記デシリアルライザにてデータのビットストリームを受け取り、前記ビットストリームのキャラクタの境界に同期し、

- ( c ) 前記ビットストリームを非直列化し、

- ( d ) 前記ビットストリーム内で第一のパターンを見つけ、

- ( e ) 前記第一のパターンに対応する第一のデータキャラクタを含む一つ以上のデータキャラクタを生成し、

- ( f ) 前記データキャラクタ内で第二のパターンを認識することによって前記ビットストリームのデータ転送速度を決定し、

- ( g ) 前記デシリアルライザのクロック速度を前記認識された第二のパターンに基づいて決定された前記ビットストリームのデータ転送速度に合わせるように設定する方法。 10

**【請求項 10】**

前記第一のパターンがコンマパターンである請求項 9 に記載の方法。

**【請求項 11】**

前記第一のデータキャラクタが K 28.5 キャラクタである請求項 9 に記載の方法。

**【請求項 12】**

前記ビットストリームがファイバ・チャネル・ネットワーク内にある請求項 9 に記載の方法。

**【請求項 13】**

前記ビットストリームが 8B / 10B 符号化スキームを用いるネットワーク内にある請求項 9 に記載の方法。 20

**【請求項 14】**

デシリアルライザのクロック速度を設定するシステムであって、

- ( a ) デシリアルライザのクロック速度を最高速度に設定する手段と、

- ( b ) ビットストリームのキャラクタの境界に同期する前記デシリアルライザにてデータのビットストリームを受け取る手段と、

- ( c ) 前記ビットストリームを非直列化する手段と、

- ( d ) 前記ビットストリーム内で第一のパターンを見つける手段と、

- ( e ) 前記第一のパターンに対応する第一のデータキャラクタを含む一つ以上のデータキャラクタを生成する手段と、

- ( f ) 前記データキャラクタ内で第二のパターンを認識することによって前記ビットストリームのデータ転送速度を決定する手段と、

- ( g ) 前記デシリアルライザのクロック速度を前記認識された第二のパターンに基づいて決定された前記ビットストリームのデータ転送速度に合わせるように設定する手段と、を有するシステム。 30

**【発明の詳細な説明】****【0001】****【技術分野】**

この発明は、電子ネットワーク通信システムに関し、より詳細には入力ビットストリームの速度の決定に関する。 40

**【0002】****【背景】**

電子データシステムは、ネットワーク通信システムを用いて相互接続することが多い。広域ネットワークやチャネルは、コンピュータ・ネットワークのアーキテクチャ用に開発された二つの方法である。従来のネットワーク（例えば LAN や WAN ）は、多くの柔軟性と比較的長距離の能力を提供する。 ESCON (Enterprise System Connection) や SCSI (Small Computer System Interface) といったチャネルは、高い性能と信頼性のために開発されている。チャネルは、一般にコンピュータ間またはコンピュータと周辺装置の間の専用の短距離接続を用いる。 50

## 【0003】

チャネルとネットワークの両方の特徴は、「ファイバ・チャネル」として知られている新しいネットワーク標準内に組み込まれている。ファイバ・チャネルのシステムでは、ネットワークの柔軟性と接続性、そしてチャネルの速度と信頼性を兼ね備えている。ファイバ・チャネル製品は現在、1062 M b p s という非常に高いデータ転送速度で実行できる。こういった速度は、非圧縮、フルモーション、高品質映像といったかなり厳しい用途(quite demanding application)でも十分処理できる。X3.230-1994といったANSI仕様が、ファイバ・チャネル・ネットワークを定義している。この仕様は、ファイバ・チャネルの機能を五つのレイヤに割り当てている。このファイバ・チャネルの五つの機能レイヤは、FC-0(物理媒体レイヤ)、FC-1(符号化・復号化レイヤ)、FC-2(実転送機構、フレーム・プロトコルとノード間のフロー制御を含む)、FC-3(共通サービスレイヤ)、及びFC-4(上位層プロトコル)である。

## 【0004】

ファイバ・チャネル・ネットワークを配置するには一般に、簡単なポイントツーポイント接続、アービトレーント型ループ、スイッチ型構成の三つの方法がある。最も簡単な接続形態は、ポイントツーポイント構成であり、これは任意の二つのファイバ・チャネルのシステムを単に直接接続する。アービトレーント型ループは、アービトレーションを介した帯域幅への共有アクセスを提供するファイバ・チャネルのリング接続である。スイッチ型ファイバ・チャネル・ネットワーク(「ファブリック」と呼ぶ)は、クロスポイントスイッチングの形態をとる。

## 【0005】

ファイバ・チャネル・ネットワーク内の装置間の接続はリンクと呼ばれる。データは、装置間のリンクを介してシリアル・ビットストリームで送られる。このシリアル・ビットストリームは、8ビット/10ビット(「8B/10B」)符号化スキームを用いて符号化される。このビットストリームは、連続的な10ビットキャラクタを含んでいる。この装置は一般に、入力された10ビットキャラクタを8ビットキャラクタに非直列化、復号化し、出力データを直列化、符号化して10ビットキャラクタに戻す。従って、各ファイバ・チャネルのプロトコル装置は、その装置のリンクからのデータ及びリンクへのデータを直列化、非直列化する「serdes」装置を有する。例えば、装置がリンク上にデータを出力するとき、その装置のserdesが、その装置からのデータをシリアル・ビットストリームに直列化する。リンクからデータを受け取るときは、その装置のserdesが、リンク上のシリアル・ビットストリームを10ビットキャラクタに非直列化する。次に、これらのキャラクタは四つのキャラクタのワードに集められる。

## 【0006】

ファイバ・チャネルのノードポートが、動作中のファイバ・チャネルのリンクに適切に接続されているとき、そのノードポートは、あるストリームのデータのワードと、ファイバ・チャネルの順序セットのワード(ordered set words)(例えばプリミティブ信号、プリミティブシーケンス、およびフレーム・デリミタ)を受け取る。各順序セットのワードは、四つの10ビットキャラクタを含む。最初の10ビットキャラクタは、「K28.5」キャラクタとして知られる特別なキャラクタであると定義されている。全てのプリミティブ信号とプリミティブシーケンスに対して、このK28.5の10ビットキャラクタが「K28.5+」キャラクタとなる。このK28.5+キャラクタは、0x0FA、つまり001111010と符号化される。このキャラクタの最初の7ビットは、「コンマパターン」、つまり0011111と呼ばれるパターンに対応する。市販のserdes装置内のデシリアルライザは、非直列化プロセスを、このコンマパターンを用いて、ビットストリーム内の10ビットのキャラクタの境界に同期させる。

## 【0007】

発明者は、ノードポート内に、入力ビットストリームのデータ転送速度を決定する装置と方法を提供し、さらにデシリアルライザのクロック速度を設定して、そのデータ転送速度に合わせる機能を提供することが望ましいことを確認した。

10

20

30

40

50

**【0008】****【概要】**

この発明は、パターン認識を用いて、シリアル・ビットストリームのデータ転送速度を決定し、そのデータ転送速度にデシリアライザのクロック速度を合わせる技術を実現する方法と装置を提供する。一実施形態では、ネットワーク装置をネットワークに接続するポートは、あるデータ転送速度を有するビットストリームをネットワークから受け取るデータ入力と、そのデータ入力に接続し、そのデータ入力を介して受け取ったビットストリームを非直列化し、データキャラクタを生成するデシリアライザと、そのデシリアライザに接続し、そのデシリアライザからデータキャラクタを受け取り、そのデシリアライザによって生成されたデータキャラクタ内でパターンを認識することにより、そのビットストリームのデータ転送速度を決定するネットワーク装置とを有する。

10

**【0009】**

別の実施形態では、ノードポートはさらに、デシリアライザ用のデータ転送速度を選択し、ビットストリームのデータ転送速度に合わせる。このノードポートは、あるデータ転送速度を有するビットストリームをネットワークから受け取るデータ入力と、そのデータ入力に接続し、そのデータ入力を介して受け取ったビットストリームを非直列化し、データキャラクタを生成し、一つのクロック速度より多い速度で動作可能なデシリアライザと、そのデシリアライザに接続し、そのデシリアライザから受取ったデータキャラクタ内でパターンを認識することで、そのビットストリームのデータ転送速度を決定し、制御信号をデシリアライザに送って、そのデシリアライザのクロック速度を、そのビットストリームのデータ転送速度に合わせるように設定するネットワーク装置とを有する。

20

**【0010】**

ファイバ・チャネルの実現において、ファイバ・チャネルのプロトコル装置をファイバ・チャネル・ネットワークに接続するファイバ・チャネルのノードポートは、ファイバ・チャネル・ネットワークにてあるデータ転送速度を有するビットストリームをそのネットワークから受け取るデータ入力と、そのデータ入力に接続し、そのデータ入力を介して受け取ったビットストリームを非直列化し、10ビットデータキャラクタを生成し、一つのクロック速度より多い速度で動作可能なデシリアライザと、そのデシリアライザに接続し、そのデシリアライザからデータキャラクタを受け取り、クロック制御信号をデシリアライザに送って、そのデシリアライザのクロック速度を、そのビットストリームのデータ転送速度に合わせるように設定するファイバ・チャネル・プロトコル装置とを有する。

30

**【0011】**

別の実施形態では、あるデータのビットストリームをデシリアライザで受け取る。このビットストリームは、データキャラクタへと非直列化される。最終的に、そのデータキャラクタのパターンを認識して、そのビットストリームのデータ転送速度を決定する。

**【0012】**

別の実施形態では、デシリアライザのクロック速度は、最高速度に設定する。あるデータのビットストリームは、デシリアライザで受け取る。このビットストリームをデータキャラクタに非直列化する。そのデータキャラクタ内のパターンを認識して、そのビットストリームのデータ転送速度を決定する。次に、デシリアライザのクロック速度を、認識したパターンに基づいて（基いた）ビットストリームのデータ転送速度に合わせるように（合わせるために）、設定する。

40

**【0013】**

この発明の技術は、いくつかの利点を提供する。ファイバ・チャネルのノードポートが、受け取ったシリアル・ビットストリームのデータ転送速度を確実に識別できるようにすることによって、試行錯誤による決定が避けられる。このノードポートはさらに、受け取ったビットストリームのパターンを確認することによって、機能していない接続と、正確に構成されていないリンクの接続を区別できる（つまり、一般に機能していない接続は、認識可能なパターンを生成しない）。非直列化したデータストリーム内で所定のパターンを認識することによって、ノードポートは、受け取ったシリアル・ビットストリームのデータ転送速度を決定する。

50

タ転送速度を即座に決定し、リンクデータのトランスマッタのデータ転送速度の制御プロトコルに明確な指示を行う。ノードポートはデシリアルライザのクロック速度を設定して、決定されたシリアルビットストリームのデータ転送速度に合わせるので、1データ転送速度より多い速度で動作可能なファイバ・チャネル装置を配置可能で、このような装置は、現設置ベースの、一般に1.0625ギガビット/秒(Gbps)のリンク速度で動作する、ファイバ・チャネル・ネットワークと下位互換性がある。

#### 【0014】

##### 【詳細な説明】

この発明は、パターン認識を用いて、シリアル・ビットストリームのデータ転送速度を決定し、そのデータ転送速度にデシリアルライザのクロック速度を合わせる技術を実現する方法と装置を提供する。この発明は、好ましい実施形態の説明として、ファイバ・チャネル・ネットワークに関して下記に説明されている。しかし、この発明は、ファイバ・チャネル・ネットワークと同様の特徴を備えたネットワークにも適用可能である。例えば、この発明は、ギガビット・イーサネット(登録商標)やNGIOといった、8B/10B符号化スキームを用いる他のネットワークにも適用できる。

10

#### 【0015】

好ましい実施形態において、ネットワークに接続したポート内のデシリアルライザは、シリアル・ビットストリームを受け取る。このデシリアルライザは、所定のパターンを用いて、ビットストリーム内のキャラクタの境界に同期する。次に、このデシリアルライザが、シリアル・ビットストリームから一連の複数ビット幅のキャラクタを生成する。このデシリアルライザは、これらのキャラクタをネットワーク装置内のパターン認識ロジックに送る。このパターン認識ロジックは、デシリアルライザにより受け取られたキャラクタを調べて、ネットワーク装置の利用可能なデータ転送速度に対応する所定のパターンを見つける。これらのパターンを用いて、ネットワーク装置が、シリアル・ビットストリームのデータ転送速度を決定する。さらに、一実施形態において、このネットワークはシリアル・ビットストリームの決定されたデータ転送速度を用いて、デシリアルライザのクロック速度を調節し、そのビットストリームのデータ転送速度に合わせる。

20

#### 【0016】

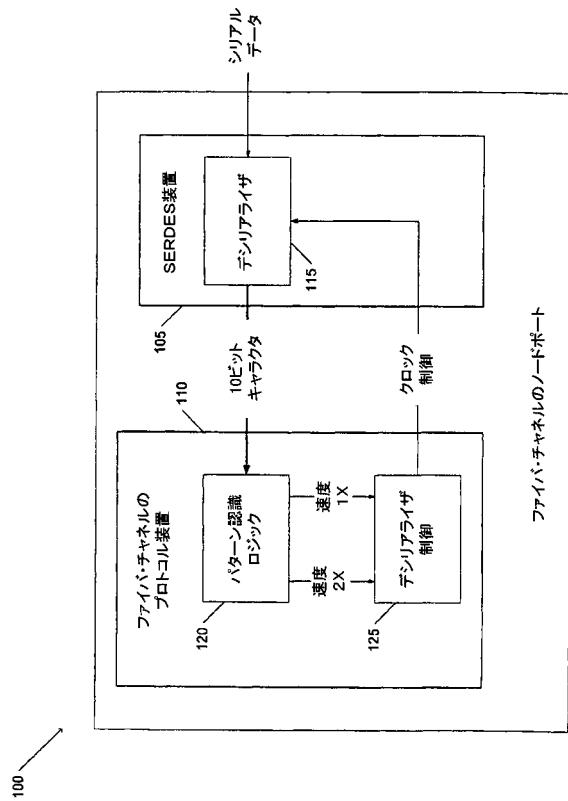

図1は、この発明によるファイバ・チャネルのノードポート100のファイバ・チャネル実施形態を示している。このファイバ・チャネルのノードポート100は、シリアルライザ/デシリアルライザ(「serdes」)装置105と、ファイバ・チャネルのプロトコル装置110(つまり、ファイバ・チャネルのプロトコルに従って動作するネットワーク装置)への接続部を有する。serdes装置105は、デシリアルライザ115を有する。デシリアルライザ115は、接続されたネットワークからのシリアル・ビットストリームのデータを受け取る。デシリアルライザ115は、そのシリアル・ビットストリーム内のキャラクタの境界に同期し、下記に説明するように複数ビットのキャラクタを生成する。ファイバ・チャネル実施形態では、デシリアルライザは10ビットキャラクタを生成する。デシリアルライザ115は、そのキャラクタをファイバ・チャネルのプロトコル装置110内のパターン認識ロジック120に送る。パターン認識ロジック120は、下記に説明するように、デシリアルライザ115から受け取ったキャラクタ内の所定のパターンを認識することによって、そのシリアル・ビットストリームのデータ転送速度を決定する。パターン認識ロジック120は、デシリアルライザ制御回路125にそのシリアル・ビットストリームのデータ転送速度を決定したことを示す制御信号を送る。図1は、ノードポート100が、二つの速度「2x」と「1x」(例えば、各々約2Gbpsと1Gbps)で動作可能である実施形態を示している。別の実施形態では、より多くの速度、且つ2倍という比率とは異なった速度の比率に適応するようにノードポートを設計できる。パターン認識ロジック120が、デシリアルライザ115から受け取ったキャラクタ内に第一パターンを認識すると、パターン認識ロジック120は第一速度制御信号(つまり2x)をデシリアルライザ制御回路125に送る。パターン認識ロジック120が、デシリアルライザ115から受け取ったキャラクタ内に第二パターンを認識すると、そのパターン認識ロジックは第二速度制御信号(

30

40

50

つまり 1 × ) をデシリアルライザ制御回路 125 に送る。

【 0017 】

デシリアルライザ制御回路 125 は、クロック制御信号をデシリアルライザ 115 に送り返し、デシリアルライザ 115 のクロック速度を調節する。クロック制御信号は、デシリアルライザ 115 のクロック速度を設定し、そのシリアル・ビットストリームの決定したデータ転送速度に合わせる。

【 0018 】

別の実施形態では、ファイバ・チャネルのプロトコル装置 110 は、デシリアルライザ制御回路 125 を含まない。このような実施形態では、ファイバ・チャネルのプロトコル装置 110 は、パターン認識ロジック 120 からシリアル・ビットストリームのデータ転送速度を示す出力信号を受け取り、ファイバ・チャネルのプロトコル装置 110 は、その用途に応じ、その信号を適切に用いる。10

【 0019 】

ビットストリームのデータ転送速度の決定は、デシリアルライザが出力した複数ビットキャラクタ内のパターン認識に基づいている。デシリアルライザが、シリアル・ビットストリームのデータ転送速度と一致するクロック速度で動作しているとき、そのデシリアルライザの出力は、受け取ったシリアル・ビットストリームに一致する。しかし、デシリアルライザが、シリアル・ビットストリームのデータ転送速度より速いクロック速度で動作しているとき、そのデシリアルライザは供給されたビットストリーム内の各ビットに対して、複数のクロックパルスを生成するので、追加のビットを導入し、そのため同じビットを複数回読み込む。従って、データ転送速度が、デシリアルライザのクロック速度より遅い場合、認識されたビットストリームのビットのパターンは、クロック速度対データ転送速度の割り合いで比例して拡大する。例えば、クロック速度がデータ転送速度の三倍であれば、そのビットストリーム内の各ビットは、デシリアルライザが認識したビットストリーム内に三回現れる。20

【 0020 】

ファイバ・チャネル実施形態の一例において、デシリアルライザは(数 1)のビットストリームを受け取ると仮定する。

【 0021 】

【数 1】

30

000011111010101010001010101010101010100011111010

【 0022 】

デシリアルライザが、ビットストリームのデータ転送速度と同じクロック速度で動作しているとき、そのデシリアルライザのクロックパルスは、ビットストリームのデータ転送速度と一致し、デシリアルライザは、そのビットストリーム内の各ビットに対して 1 ビットを受け取る。デシリアルライザはコンマのパターンを見つけ、(数 2)の 10 ビットキャラクタを出力する。

【 0023 】

【数 2】

40

0011111010 (0x0FA)

1010100010 (0x2A2)

1010101010 (0x2AA)

1010101010 (0x2AA)

0011111010 (0x0FA)

【 0024 】

50

デシリアルライザが、シリアル・ビットストリームのデータ転送速度の二倍のクロック速度で動作しているとき、そのデシリアルライザは、ビットストリーム内の各ビットに対して、二つのクロックパルスを生成し、デシリアルライザは、そのビットストリーム内で各ビットを二回認識する。従って、デシリアルライザは、上記のビットストリームを（数3）のビットストリームとして認識する。

【 0 0 2 5 】

【数3】

0110011001100110011000000111111111001100

10

【 0 0 2 6 】

その結果、デシリアルライザはコンマパターンを見つけ、(数4)の10ビットキャラクタを出力する。

【 0 0 2 7 】

【数4】

0011111111 (0x0FF)

1100110011 (0x333)

0011001100 (0x0CC)

0000110011 (0x033)

0011001100 (0x0CC)

1100110011 (0x333)

0011001100 (0x0CC)

1100110000 (0x330)

0011111111 (0x0FF)

1100110011 (0x333)

【 0 0 2 8 】

30

従って、得られるキャラクタは非常に異なる。しかし、この違いは、クロック速度とデータ転送速度の関係に基づいて予測できる。特に、第二の場合にデシリアライザが出力した最初の 18 ピットは、第一の場合の最初のキャラクタの下位 9 ピットの各ビットを二倍にしたものと同じである。同様のパターンは、異なる比率の速度に対して保持される。

( 0 0 2 9 )

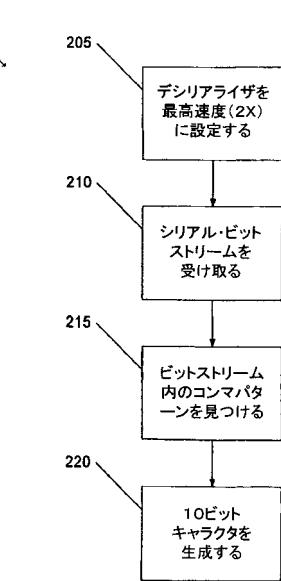

図2は、シリアル・ビットストリームのキャラクタの境界に、デシリアルライザを同期させるプロセス200を示している。ファイバ・チャネルのプロトコル装置は、デシリアルライザのクロック速度を最高速度（例えば2×）に設定する（ステップ205）。デシリアルライザは、接続されたネットワークからのシリアル・ビットストリームとして、あるストリームのビットを受け取る（ステップ210）。デシリアルライザは、その入力ビットストリームを調べて、所定のパターンを見つける（ステップ215）。このパターンは、そのネットワークのネットワーク・プロトコルに従って、特別なキャラクタを示すように事前に定義されている。ファイバ・チャネル実施形態では、このパターンはコンマパターンである。このコンマパターンは一意的であり、順序セットのワードの始まりでK28.5キャラクタを示すためにのみ用いられる。デシリアルライザがビットストリーム内に所定のパターンを見つけると、そのデシリアルライザが、開始点として所定のパターンを用いる複数ビットのキャラクタを出力する（ステップ220）。ファイバ・チャネルの実施形態では、コンマパターンは7ビットのパターンである。そのビットストリーム内の次の3ビットで、コンマパターンを含むキャラクタが完成する。従って、デシリアルライザは、コンマパターンと次の3ビットが適切な10ビットキャラクタを構成すると結論付けることができる。

40

。このデシリアルライザは、これらの 10 ビットキャラクタを一つのキャラクタとしてファイバ・チャネルのプロトコル装置に送る。そのデシリアルライザは、シリアル・ビットストリームからの 10 ビットからなる次のグループを、次のキャラクタとしてファイバ・チャネルのプロトコル装置に送り、そのビットストリーム内の 10 ビットキャラクタの境界に同期される。

#### 【0030】

約 1 Gbps (1x) と 2 Gbps (2x) といった複数の速度で動作可能なノードポートでは、そのノードポートは、デシリアルライザを最大のクロック速度（つまり 2x）に設定し、K28.5 + キャラクタのどの速度がパターン認識ロジックで検出されるかを確認するのを待つことで、受け取ったシリアル・ビットストリームのデータ転送速度を即座に決定できる。2x 速度の K28.5 + キャラクタが検出されるならば、デシリアルライザが正確に設定されていて、ビットストリームのデータ転送速度に合致しているので、ファイバ・チャネルのプロトコル装置は、デシリアルライザの設定を変更しない。もし、1x 速度の K28.5 + キャラクタが検出されるならば、ファイバ・チャネルのプロトコル装置は、デシリアルライザがより遅い 1x のクロック速度で動作するように設定し、その後そのリンク上で通信を確立しようとする。利用可能な速度で K28.5 + キャラクタが検出されない場合、パターン認識ロジックは、そのリンクが有効に機能していないと判断する。

#### 【0031】

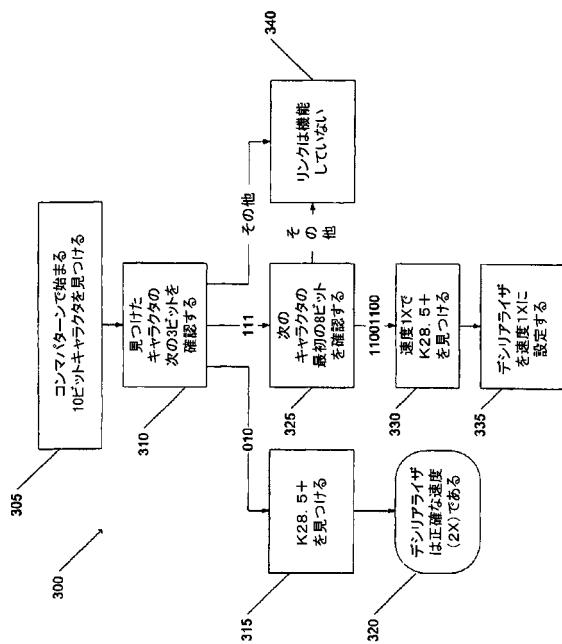

図 3 は、デシリアルライザのクロック速度を、シリアル・ビットストリームのデータ転送速度に合わせるように設定するプロセス 300 を示している。図 3 は、ファイバ・チャネルの実施形態についてこのプロセスを説明している。しかし、キャラクタ内のビット数、またはシリアル・ビットストリームのデータ転送速度を認識するために用いられるパターンの内容といった後述の詳細は、別のネットワークのプロトコルや用途に適応するために変更できる。デシリアルライザが、シリアル・ビットストリームのビットとキャラクタの境界の両方で同期した後、パターン認識ロジックは、上位 7 ビットが 7 ビットのコンマパターンである 10 ビットキャラクタを探す（ステップ 305）。次に、パターン認識ロジックは、そのキャラクタの下位 3 ビットを確認する（ステップ 310）。これらの 3 ビットが 010 であれば、このキャラクタは K28.5 + キャラクタである（ステップ 315）。受け取ったシリアル・ビットストリームのデータ転送速度は、デシリアルライザのクロック速度と同じであり、ファイバ・チャネルのプロトコル装置は、デシリアルライザのクロック速度を調整しなくてもよい（ステップ 320）。デシリアルライザが、K28.5 + キャラクタ用の 10 ビットコードに対応する 10 ビットキャラクタを生成したので、パターン認識ロジックは、デシリアルライザとシリアル・ビットストリームが同じ速度であると認識する。

#### 【0032】

パターン認識ロジックが見つけ、コンマパターンを含むキャラクタの下位 3 ビットが 111 であれば、そのパターン認識ロジックは、デシリアルライザが、シリアル・ビットストリームのデータ転送速度より速い速度で動作していると認識する。次に、パターン認識ロジックは、次の 10 ビットキャラクタの上位 8 ビットを確認する（ステップ 325）。これらの上位 8 ビットが 11001100 であれば、パターン認識ロジックは、そのシリアル・ビットストリーム内の K28.5 + キャラクタが、シリアル・ビットストリームのデータ転送速度の二倍のクロック速度で、デシリアルライザによって直列化されていると認識する（ステップ 330）。パターン認識ロジックは、デシリアルライザ制御回路に速度制御信号を送り、次にデシリアルライザにクロック制御信号を送って、デシリアルライザのクロック速度を 2 分の 1 だけ（例えば、2x から 1x に）低減する（ステップ 335）。デシリアルライザは、K28.5 + キャラクタの 10 ビットを表す 18 ビット（最初のワードの 10 ビットと次のワードの 8 ビット）のシーケンスを送っているので、このパターン認識ロジックは、デシリアルライザが、そのシリアル・ビットストリームのデータ転送速度の二倍で動作していると認識する。K28.5 の最初の 0 は、デシリアルライザによるコンマパターンの認識では失われる所以、デシリアルライザは、20 ビットではなく 18 ビットを送る。

10

20

30

40

50

この喪失は、デシリアルライザがシリアル・ビットストリームのデータ転送速度の二倍で実際に動作していることを、デシリアルライザが認識しないことから生じる。

【0033】

パターン認識ロジックが見つけ、コンマパターンを含むキャラクタの下位3ビットが、010でも111でもなければ、パターン認識ロジックは、そのリンクが有効なシリアル・ビットストリームを送っていないと認識する（ステップ340）。パターン認識ロジックはさらに、ステップ325に続くキャラクタの上位8ビットが、11001100でなければ、リンクが機能していないと認識する（ステップ340）。

【0034】

別の実施形態では、図3について上記に説明した同じ概念を、別の複数のデータ転送速度とクロック速度を備えた用途に対しても適用できる。例えば、パターン認識ロジックは、シリアル・ビットストリームが、デシリアルライザの最大のクロック速度、デシリアルライザの最大のクロック速度の2分の1、またはデシリアルライザの最大のクロック速度の4分の1に対応するデータ転送速度で動作していることを認識できる。このような別のデータ転送速度に適応するために、パターン認識ロジックは、対応するビットパターンと意志決定機構を有し、このような別のデータ転送速度を十分に認識できる。さらに別の実施形態では、上記のパターン認識ロジックは、serdes装置のデシリアルライザに含まれている。

10

【0035】

好ましい実施形態は、いくつかの別の実施形態と共に説明してきた。しかし、次の請求項の範囲内にある変形態様は、この発明の範囲内にある。例えば、この技術はプログラム可能なハードウェアまたはソフトウェア内に実現できる。従って、この発明は、上記に説明した実施形態ではなく、次の請求項の範囲によってのみ制限される。

20

【図面の簡単な説明】

【図1】 この発明によるファイバ・チャネルのノードポートを示す図である。

【図2】 デシリアルライザの動作のフローチャートである。

【図3】 デシリアルライザの速度を入力ビットストリームのデータ転送速度に合わせるフローチャートである。

【図1】

【図2】

【図3】

---

フロントページの続き

合議体

審判長 江嶋 清仁

審判官 近藤 聰

審判官 圓道 浩史

(56)参考文献 特開昭62-234446(JP,A)

特開平6-37804(JP,A)

特開平10-243020(JP,A)

特開平8-249263(JP,A)

特開平10-293633(JP,A)

特開平5-207529(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 13/00

H04L 12/00

G06F 13/00