(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4198251号

(P4198251)

(45) 発行日 平成20年12月17日(2008.12.17)

(24) 登録日 平成20年10月10日(2008.10.10)

(51) Int.Cl.

F 1

|             |           |            |       |      |

|-------------|-----------|------------|-------|------|

| HO1L 27/04  | (2006.01) | HO1L 29/78 | 29/78 | 657D |

| HO1L 29/78  | (2006.01) | HO1L       | 29/48 | M    |

| HO1L 29/47  | (2006.01) | HO1L       | 29/78 | 653A |

| HO1L 29/872 | (2006.01) | HO1L       | 29/78 | 655C |

| HO1L 29/739 | (2006.01) | HO1L       | 29/78 | 658K |

請求項の数 4 (全 39 頁) 最終頁に続く

(21) 出願番号

特願平11-1713

(22) 出願日

平成11年1月7日(1999.1.7)

(65) 公開番号

特開2000-200906(P2000-200906A)

(43) 公開日

平成12年7月18日(2000.7.18)

審査請求日

平成16年7月16日(2004.7.16)

前置審査

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 楠 茂

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 小野田 誠

最終頁に続く

(54) 【発明の名称】電力用半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1の半導体層と、

前記第1の半導体層の第1の正面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、

前記第1の半導体層の第2の正面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、

少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、少なくとも前記第4の半導体領域に接するように形成された第2の主電極と、を備え、

前記第1の半導体層の厚み方向の中央部よりも、前記第2ユニットの集合体よりの所定位置から、前記第2ユニットの集合体までの前記第1の半導体層のキャリアライフタイムは、前記第1ユニットの集合体側の前記第1の半導体層よりも短く設定される、電力用半導体装置。

## 【請求項 2】

第1導電型の第1の半導体層と、

前記第1の半導体層の第1の正面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、

前記第1の半導体層の第2の正面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、

少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、

少なくとも前記第4の半導体領域に接するように形成された第2の主電極と、を備え、

前記第1の半導体層の厚み方向の中央部よりも、前記第2ユニットの集合体よりの位置に、少なくとも、前記第1および第2のユニットの集合体の形成領域の広さに対応する広さで形成された、ライフタイム設定領域をさらに備え、

前記ライフタイム設定領域のキャリアライフタイムは、前記第1の半導体層よりも短く設定され、

前記第1の半導体層は、前記第1ユニットの集合体側と、前記第2ユニットの集合体側とで、結晶面方位および結晶軸方位のうち少なくとも一方が異なっており、

前記ライフタイム設定領域は、前記第1ユニットの集合体側の前記第1の半導体層と、前記第2ユニットの集合体側の前記第1の半導体層の境界領域である、電力用半導体装置。

**【請求項3】**第1導電型の第1の半導体層と、

前記第1の半導体層の第1の正面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、

前記第1の半導体層の第2の正面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、

少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、

少なくとも前記第4の半導体領域に接するように形成された第2の主電極と、を備え、

前記第1の半導体層の厚み方向の中央部よりも、前記第2ユニットの集合体よりの位置に、少なくとも、前記第1および第2のユニットの集合体の形成領域の広さに対応する広さで形成された、金属層あるいは不純物濃度が前記第1の半導体層よりも高濃度の第1導電型の第2の半導体層をさらに備える、電力用半導体装置。

**【請求項4】**

(a)第1導電型の第1の半導体基板を準備し、前記第1の半導体基板の第1の正面の表面内に選択的に第2導電型の第1の半導体領域を形成し、前記第1の半導体領域の表面内に選択的に第1導電型の第2の半導体領域を形成し、少なくとも、前記第2の半導体領域と前記第1の半導体基板の間の前記第1の半導体領域の表面に接するように第1のゲート絶縁膜を形成し、前記第1のゲート絶縁膜上に第1のゲート電極を形成して第1ユニットの集合体を形成する工程と、

(b)第1導電型の第2の半導体基板を準備し、前記第2の半導体基板の第1の正面の表面内に選択的に第2導電型の第3の半導体領域を形成し、前記第3の半導体領域の表面内

10

20

30

40

50

に選択的に第1導電型の第4の半導体領域を形成し、少なくとも、前記第4の半導体領域と前記第2の半導体基板の間の前記第3の半導体領域の表面に接するように第2のゲート絶縁膜を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成して第2ユニットの集合体を形成する工程と、

(c) 前記第1および第2の半導体基板のそれぞれの第2の主面どうしを貼り合わせ法により接合する工程と、を備え、

前記工程(b)の後、前記工程(c)に先だって、前記第1および第2の半導体基板の一方に、粒子線の照射、あるいは基板濃度の変更により、キャリアライフトайムを短くする工程をさらに備える、電力用半導体装置の製造方法。

【発明の詳細な説明】

10

【0001】

【発明の属する技術分野】

本発明は電力用半導体装置およびその製造方法に関し、特にインバータに用いられる電力用半導体装置およびその製造方法に関する。

【0002】

【従来の技術】

近年、省エネルギーの観点から、例えば、エアコンディショニングに見るよう電動機のインバータ駆動化が進んできており、インバータ用の電力用半導体装置の生産量が増加している。

【0003】

20

このような、電力用半導体装置に対しては低損失であるだけでなく、省スペース化の観点から小型化、低コスト化の要望も強まっている。

【0004】

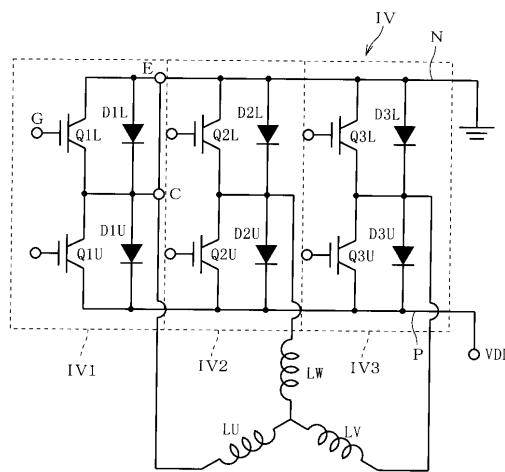

以下、従来の電力用半導体装置について、図38～図43を用いて説明する。まず、図38に3相インバータINVの回路図を示す。

【0005】

図38に示すように3相インバータINVは3つのインバータINV1～INV3で構成されている。インバータINV1は、電源電圧VDDが与えられる電源線Pと、接地電位に接続される電源線N間に直列に接続されたIGBT (insulated gate bipolar transistor: 以後、単にトランジスタと呼称する場合もあり) Q1LおよびQ1Uと、トランジスタQ1LおよびQ1Uにそれぞれに逆並列接続されたフリーホイールダイオードD1LおよびD1Uとを備えている。そして、トランジスタQ1LおよびQ1Uの接続ノードは負荷LUの一端に接続されている。

30

【0006】

インバータINV2も同様の構成であり、電源線P-N間に直列に接続されたトランジスタQ2LおよびQ2Uと、トランジスタQ2LおよびQ2Uにそれぞれに逆並列接続されたフリーホイールダイオードD2LおよびD2Uとを備え、トランジスタQ2LおよびQ2Uの接続ノードは負荷LWの一端に接続されている。

【0007】

インバータINV3は、電源線P-N間に直列に接続されたトランジスタQ3LおよびQ3Uと、トランジスタQ3LおよびQ3Uにそれぞれに逆並列接続されたフリーホイールダイオードD3LおよびD3Uとを備え、トランジスタQ3LおよびQ3Uの接続ノードは負荷LVの一端に接続されている。そして、負荷LU, LV, LWは互いに共通して接続される他端を有している。

40

【0008】

また、図中においてはインバータINV1のうちトランジスタQ1LとダイオードD1Lとで構成される部分において、トランジスタQ1Lのエミッタ、コレクタ、ゲート端子をそれぞれ、E、C、Gとして示す。なお、ダイオードD1Lのアノード端子およびカソード端子はエミッタ端子Eおよびコレクタ端子Cに接続される。

【0009】

50

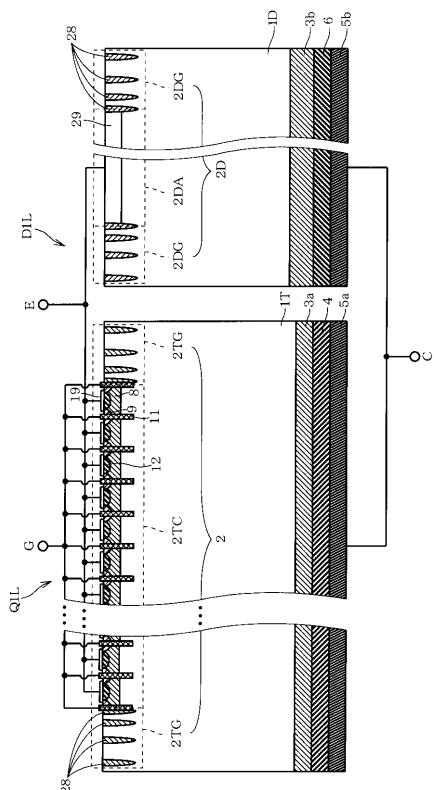

次に、図39を用いてトランジスタQ1LとダイオードD1Lの断面構造の一例について説明する。なお、以下の説明においては、トランジスタQ1Lをnチャネル型とし、ダイオードD1Lをn型半導体基板上に形成されたp型アノードを有するダイオードとして説明する。

【0010】

図39に示すように、トランジスタQ1Lはn型のシリコン基板1Tの上主面表面内において、p型ベース領域8が形成され、当該p型ベース領域8を深さ方向に貫通するよう複数のトレンチ型のゲート電極11が並列に形成されている。ゲート電極11の間のp型ベース領域8の表面内には、p型不純物を比較的高濃度に含んだp型半導体領域12が選択的に形成されている。p型半導体領域12はp型ベース領域8とエミッタ電極19との電気的接続が良好に行われることを目的として設けられている。

10

【0011】

そして、p型半導体領域12を両側から挟むように、n型不純物を比較的高濃度に含んだn型エミッタ領域9が形成されている。なおn型エミッタ領域9はゲート電極11の表面に形成されたゲート絶縁膜(図示省略)に接触する構成となっている。ここで、シリコン基板1TはIGBTのn型ベース層となる。

【0012】

そして、n型エミッタ領域9の表面の一部にはエミッタ電極19が形成され、エミッタ電極19はエミッタ端子Eに電気的に接続され、ゲート電極11はゲート端子Gに電気的に接続され、複数のIGBT構造の並列接続によってトランジスタQ1Lが構成されている。これら、p型ベース領域8、n型エミッタ領域9、ゲート電極11が形成される領域をセル領域2TCと呼称する。

20

【0013】

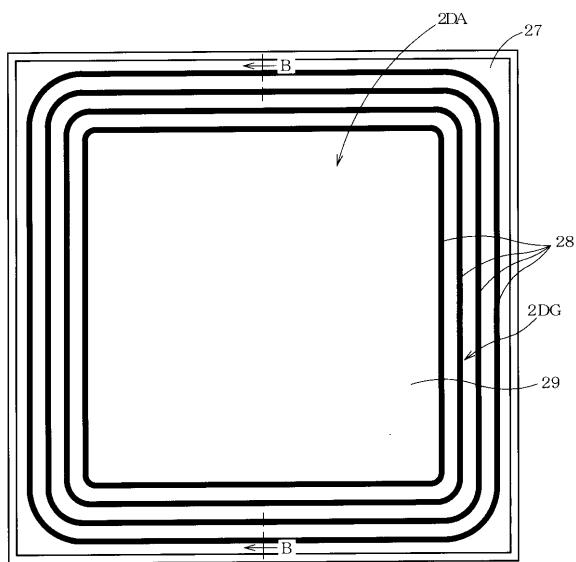

また、セル領域2TCを取り囲むように浮遊電位の複数のp型半導体領域28が同心状に形成され、電界緩和リング領域2TGを形成している。なお、セル領域2TCおよび電界緩和リング領域2TGの構造を総称して、エミッタ側構造2とする。

【0014】

そして、シリコン基板1Tの下主面上には、n型バッファ層3a、p型コレクタ層4、金属のコレクタ電極5aが順に積層されている。

30

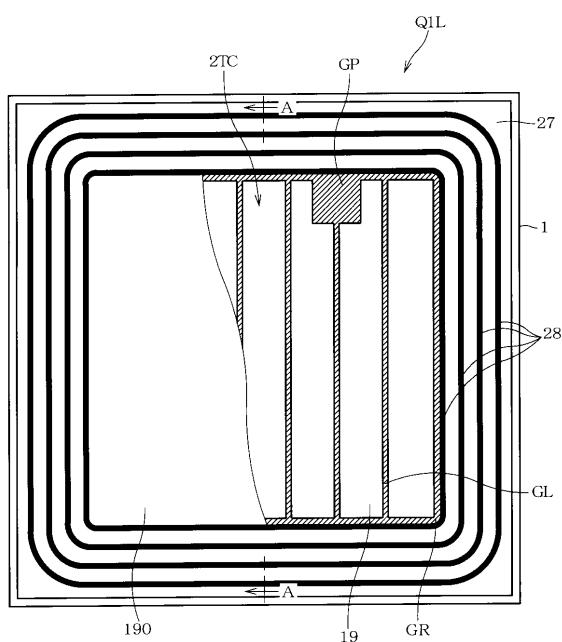

【0015】

ここで、トランジスタQ1Lをエミッタ電極側から見た平面構成を図40に示す。図40に示すようにトランジスタQ1Lは矩形形状の基板上に形成され、矩形のセル領域2TCを矩形の電界緩和リング領域2TGが取り囲む形状となっている。そして、電界緩和リング領域2TGを取り囲むように浮遊電位のn型半導体領域27が形成されている。

【0016】

セル領域2TCには複数のゲートラインGLが並列に形成され、ゲートラインGLの端部はセル領域2TCの外縁を規定するゲートリング領域GRに接続され、全ゲートラインGLが共通の電位となる構成となっている。また、ゲートラインGLと外部との電気的接続を行うゲートパッドGPが部分的に設けられている。

40

【0017】

なお、ゲートラインGL間はエミッタ電極19で覆われ、その上には各エミッタ電極19を電気的に接続する上部エミッタ電極190で覆われているが、図40においては便宜的に上部エミッタ電極190の一部を省略している。

【0018】

なお、図39に示したトランジスタQ1Lの断面構成は、図40におけるA-A線での断面を示しており、図39に示すゲート電極11は、ゲートラインGLの長手方向に沿って垂直に配設された複数のゲート電極11のごく一部だけである。

【0019】

また、ダイオードD1Lは、図39に示すように、n型のシリコン基板1Dの上主面表面内において、p型のアノード層29が形成され、アノード層29の表面には図示しないア

50

ノード電極が形成され、アノード電極はエミッタ端子 E に電気的に接続されている。これらアノード層 29、アノード電極が形成される領域をアノード領域 2DA と呼称する。

【0020】

そして、アノード領域 2DA を取り囲むように浮遊電位の複数の p 型半導体領域 28 が同心状に形成され、電界緩和リング領域 2DG を形成している。なお、アノード領域 2DA および電界緩和リング領域 2DG の構造を総称して、アノード側構造 2D とする。

【0021】

そして、シリコン基板 1D の下主面上には、n 型バッファ層 3b、n 型不純物を比較的高濃度に含んだ n 型半導体層 6、金属のカソード電極 5b が順に積層されている。また、カソード電極 5b はコレクタ端子 C に電気的に接続されている。

10

【0022】

ここで、n 型半導体層 6 はカソード電極 5b と n 型バッファ層 3b とのオーミックコンタクトを達成するための層であり、シリコン基板 1D は pin ダイオードの i (intrinsic) 層に対応する層である。

【0023】

次に、ダイオード D1L をアノード電極側から見た平面構成を図 41 に示す。図 41 に示すようにダイオード D1L は矩形形状の基板上に形成され、矩形のアノード領域 2DA を矩形の電界緩和リング領域 2DG が取り囲む形状となっている。そして、電界緩和リング領域 2DG を取り囲むように浮遊電位の n 型半導体領域 27 が形成されている。

20

【0024】

図 39 に示したダイオード D1L の断面構成は、図 41 における B-B 線での断面を示しており、図 39 に示すアノード層 29 はアノード層 29 のごく一部だけである。

【0025】

以上説明したように、3 相インバータ IV を実現するための一例としては、別個に形成された IGBT とフリーホイールダイオードの 2 種類の素子を並列に配置する構成を採用していた。従って、3 相インバータのモジュール面積が大きくなるという問題があった。

【0026】

そこで、フリーホイールダイオードを IGBT に内蔵した構成が開発された。以下、図 42 および図 43 を用いてフリーホイールダイオードを内蔵した IGBT の構成について説明する。

30

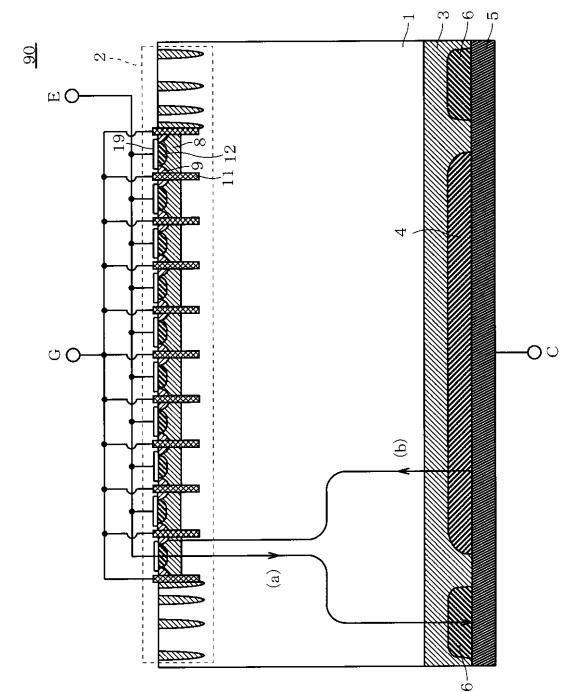

【0027】

図 42 にフリーホイールダイオードを内蔵した IGBT90 の断面構成を示す。IGBT90 の基本構成は、図 39 を用いて説明したトランジスタ Q1L と同様であり、同一の構成には同一の符号を付し、重複する説明は省略する。なお、図 42 におけるエミッタ側構造 2 は、図 39 におけるエミッタ側構造 2T に対応しており、両者は実質的に同じものである。また、図 39 におけるシリコン基板 1T は n 型ベース層 1 と呼称する。

【0028】

IGBT90 は n 型バッファ層 3 の主面内に、p 型コレクタ層 4 が p 型ベース領域 8 の形成領域（すなわち図 39 におけるセル領域 2TC）にほぼ対応して選択的に形成され、p 型コレクタ層 4 と間隔を開けて p 型コレクタ層 4 を囲むように n 型カソード領域 6 が選択的に形成された構成となっている。そして、n 型バッファ層 3、p 型コレクタ層 4、n 型カソード領域 6 に接触するように金属のコレクタ電極 5 が形成された構成となっている。

40

【0029】

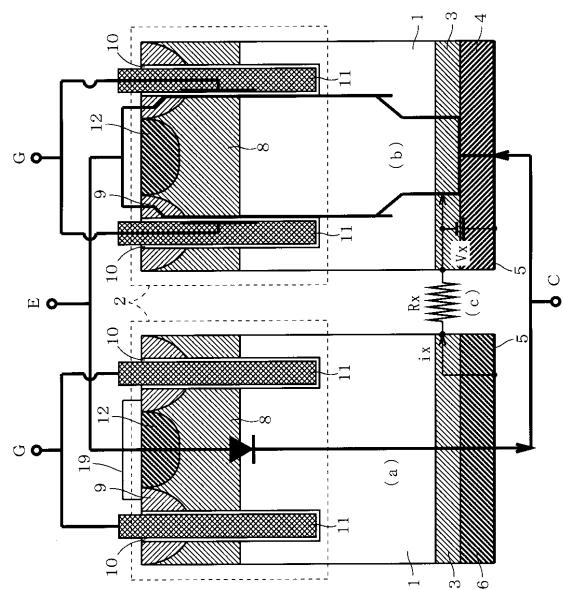

次に、図 42 に示す 2 つの電流経路 a および b について図 43 を用いて詳細に説明する。

【0030】

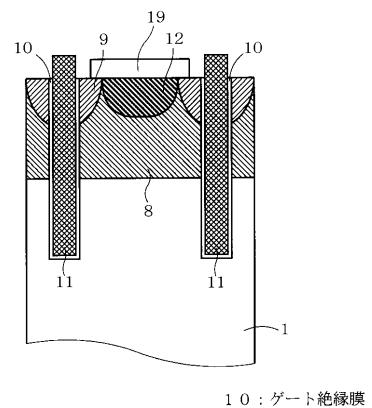

図 43 は複数の IGBT 構造のうち 2 つのゲート電極 11 を含む部分を抜き出した図である。なお、図 43 においては、図 39、図 42 において省略したゲート絶縁膜 10 を明示している。ゲート絶縁膜 10 はゲート電極 11 を囲むように形成され、ゲート電極 11 に所定の電位を与えることで、ゲート絶縁膜 10 の近傍の p 型ベース領域 8 の一部の導電型が反転し、n 型エミッタ領域 9 と n 型ベース層 1 との間にチャネルが形成されることにな

50

る。

【0031】

図43に示すように、電流経路aはエミッタ電極19、p型半導体領域12、p型ベース領域8、n型ベース層1、n型バッファ層3、n型カソード領域6、コレクタ電極5で構成され、電流経路bはコレクタ電極5、p型コレクタ層4、n型バッファ層3、n型ベース層1、p型ベース領域8、n型エミッタ領域9、エミッタ電極19で構成されている。

【0032】

従って、図43に示すように、電流経路bに沿っては2つのIGBTが並列に存在するが、電流経路aに沿ってはIGBTに寄生してフリーホイールダイオード構造が存在している。なお、図43においては便宜的に電流経路aを形成する構成および電流経路bを形成する構成を別個に示したが、両者の構成は大部分が共通である。

10

【0033】

次に、IGBT90の動作について説明する。コレクタ端子Cに負の電圧が印加された場合、p型コレクタ層4とn型バッファ層3とで構成されるpn接合のため、電流経路bに沿っては電流が流れずに、電流経路aに沿った電流が流れ、ダイオード動作を行う。

【0034】

しかし、電流経路a、bは互いにコレクタ電極5、n型バッファ層3、n型ベース層1、エミッタ側構造2を共通とするため、コレクタ端子Cに正電圧が印加された場合、コレクタ電極5からn型カソード領域6を通ってn型バッファ層3に到る電流経路cが形成され、n型バッファ層3の電位が上昇し、n型バッファ層3とp型コレクタ層4との間の電圧Vxが電導度変調を起こすに十分な電圧となるのが困難となる。その結果、構造上はIGBTであってもIGBTとして動作せず、MOS電界効果トランジスタ(MOSトランジスタ)として動作してしまう。

20

【0035】

これを回避するためには、フリーホイールダイオードを構成するn型カソード領域6および、n型バッファ層3の一部の面積を小さくする一方で、p型コレクタ層4の面積を大きくして、抵抗Rxに流れる電流ixを小さくしなければならない。

【0036】

しかし、n型カソード領域6(およびn型バッファ層3の一部)の面積を小さくすると、電流経路aの構成、すなわちフリーホイールダイオードが動作している場合の、フリーホイールダイオードの順方向電圧Vfが高くなったり、フリーホイールダイオードのオン電流およびリカバリ電流が、n型カソード領域6(およびn型バッファ層3の一部)に集中して電流密度が高くなり、素子が破壊することもある。

30

【0037】

【発明が解決しようとする課題】

従来のインバータは、別個に形成されたIGBTとフリーホイールダイオードの2種類の素子を並列に配置した構成、あるいはフリーホイールダイオードをIGBTに内蔵した構成を採用していたが、前者の場合はインバータのモジュール面積が大きくなるという問題があり、後者の場合は、IGBTをオンさせるためには、n型バッファ層3の電位上昇を抑制するために、n型カソード領域6の面積をできるだけ小さくする必要があり、フリーホイールダイオードの動作時に電流集中による素子破壊が発生する可能性が高いという問題があった。

40

【0038】

本発明は上記のような問題点を解消するためになされたもので、IGBTおよびフリーホイールダイオードで構成される電力用半導体装置の小型化を実現するとともに、IGBTに内蔵されるフリーホイールダイオードの動作時に電流集中による素子破壊を防止した構成を提供することを目的とする。

【0048】

【課題を解決するための手段】

本発明に係る請求項1記載の電力用半導体装置は、第1導電型の第1の半導体層と、前

50

記第1の半導体層の第1の主面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、前記第1の半導体層の第2の主面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、少なくとも前記第4の半導体領域に接するように形成された第2の主電極とを備え、前記第1の半導体層の厚み方向の中央部よりも、前記第2ユニットの集合体よりの所定位置から、前記第2ユニットの集合体までの前記第1の半導体層のキャリアライフタイムは、前記第1ユニットの集合体側の前記第1の半導体層よりも短く設定されている。10

#### 【0049】

本発明に係る請求項2記載の電力用半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の第1の主面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、前記第1の半導体層の第2の主面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、少なくとも前記第4の半導体領域に接するように形成された第2の主電極と、を備え、前記第1の半導体層の厚み方向の中央部よりも、前記第2ユニットの集合体よりの位置に、少なくとも、前記第1および第2のユニットの集合体の形成領域の広さに対応する広さで形成された、ライフタイム設定領域をさらに備え、前記ライフタイム設定領域のキャリアライフタイムは、前記第1の半導体層よりも短く設定され、前記第1の半導体層は、前記第1ユニットの集合体側と、前記第2ユニットの集合体側とで、結晶面方位および結晶軸方位のうち少なくとも一方が異なっており、前記ライフタイム設定領域は、前記第1ユニットの集合体側の前記第1の半導体層と、前記第2ユニットの集合体側の前記第1の半導体層の境界領域である。20

#### 【0052】

本発明に係る請求項3記載の電力用半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の第1の主面の表面内に選択的に形成された第2導電型の第1の半導体領域、前記第1の半導体領域の表面内に選択的に形成された第1導電型の第2の半導体領域、少なくとも、前記第2の半導体領域と前記第1の半導体層の間の前記第1の半導体領域の表面に接するように形成された第1のゲート絶縁膜、前記第1のゲート絶縁膜上に形成された第1のゲート電極で構成される第1ユニットの集合体と、前記第1の半導体層の第2の主面の表面内に選択的に形成された第2導電型の第3の半導体領域、前記第3の半導体領域の表面内に選択的に形成された第1導電型の第4の半導体領域、少なくとも、前記第4の半導体領域と前記第1の半導体層の間の前記第3の半導体領域の表面に接するように形成された第2のゲート絶縁膜、前記第2のゲート絶縁膜上に形成された第2のゲート電極で構成される第2ユニットの集合体と、少なくとも前記第2の半導体領域に接するように形成された第1の主電極と、少なくとも前記第4の半導体領域に接するように形成された第2の主電極と、を備え、前記第1の半導体層の厚み方向の中央部よりも、前記第30

40

50

2ユニットの集合体よりの位置に、少なくとも、前記第1および第2のユニットの集合体の形成領域の広さに対応する広さで形成された、金属層あるいは不純物濃度が前記第1の半導体層よりも高濃度の第1導電型の第2の半導体層をさらに備えている。

【0056】

本発明に係る請求項4記載の電力用半導体装置の製造方法は、第1導電型の第1の半導体基板を準備し、前記第1の半導体基板の第1の主面の表面内に選択的に第2導電型の第1の半導体領域を形成し、前記第1の半導体領域の表面内に選択的に第1導電型の第2の半導体領域を形成し、少なくとも、前記第2の半導体領域と前記第1の半導体基板の間の前記第1の半導体領域の表面に接するように第1のゲート絶縁膜を形成し、前記第1のゲート絶縁膜上に第1のゲート電極を形成して第1ユニットの集合体を形成する工程(a)と、第1導電型の第2の半導体基板を準備し、前記第2の半導体基板の第1の主面の表面内に選択的に第2導電型の第3の半導体領域を形成し、前記第3の半導体領域の表面内に選択的に第1導電型の第4の半導体領域を形成し、少なくとも、前記第4の半導体領域と前記第2の半導体基板の間の前記第3の半導体領域の表面に接するように第2のゲート絶縁膜を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成して第2ユニットの集合体を形成する工程(b)と、前記第1および第2の半導体基板のそれぞれの第2の主面どうしを貼り合わせ法により接合する工程(c)とを備え、前記工程(b)の後、前記工程(c)に先だって、前記第1および第2の半導体基板の一方に、粒子線の照射、あるいは基板濃度の変更により、キャリアライフトайムを短くする工程をさらに備えている。

【0058】

【発明の実施の形態】

< A . 実施の形態 1 >

< A - 1 . 装置構成 >

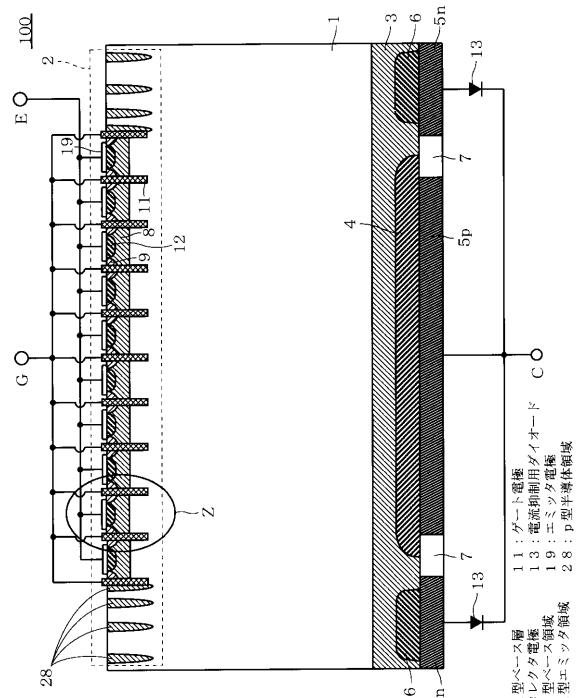

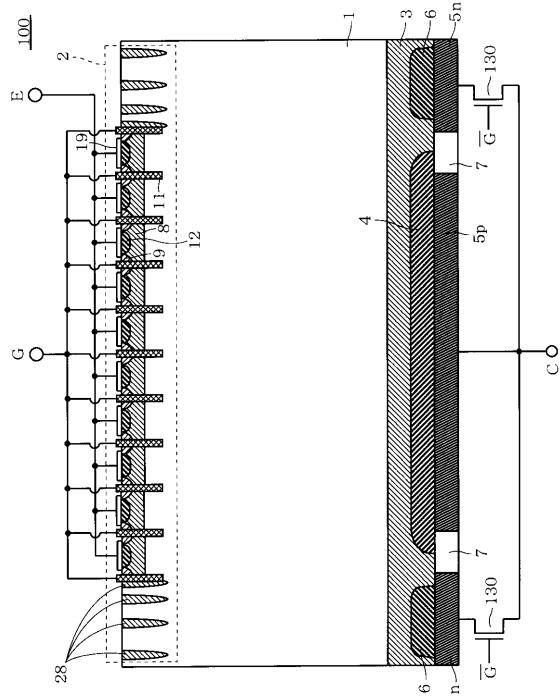

本発明に係る電力用半導体装置の実施の形態1を図1～図4を用いて説明する。図1はフリーホイールダイオードを内蔵したIGBT100の全体構成を示す断面図であり、図2は図1における領域Z部分の詳細構成を示す図である。

【0059】

IGBT100はnチャネル型であり、図1および図2に示すように、n型のシリコン基板1(n型ベース層1と呼称する場合あり)の上主面表面内において、不純物濃度 $1 \times 10^{16} \sim 1 \times 10^{19} / \text{cm}^3$ 程度のp型ベース領域8が形成され、当該p型ベース領域8を深さ方向に貫通するように複数のトレンチ型のゲート電極11が並列に形成されている。なお、ゲート電極11の周囲にはゲート絶縁膜が形成されている。ゲート電極11の間のp型ベース領域8の表面内には、p型不純物を比較的高濃度( $1 \times 10^{19} \sim 1 \times 10^{21} / \text{cm}^3$ 程度)に含んだp型半導体領域12が選択的に形成されている。p型半導体領域12はp型ベース領域8と後述するエミッタ電極19との電気的接続が良好に行われるこことを目的として設けられている。

【0060】

そして、p型半導体領域12を両側から挟むように、n型不純物を比較的高濃度( $1 \times 10^{18} \sim 1 \times 10^{21} / \text{cm}^3$ 程度)に含んだn型エミッタ領域9が形成されている。なおn型エミッタ領域9はゲート電極11の表面に形成されたゲート絶縁膜10に接触する構成となっている。ここで、シリコン基板1はIGBTのn型ベース層となる。

【0061】

そして、n型エミッタ領域9の表面にはエミッタ電極19が形成され、エミッタ電極19はエミッタ端子Eに電気的に接続され、ゲート電極11はゲート端子Gに電気的に接続され、複数のIGBT構造の並列接続によってIGBT100が構成されている。

【0062】

また、p型ベース領域8を取り囲むようにp型不純物を $1 \times 10^{17} \sim 1 \times 10^{20} / \text{cm}^3$ 程度含んだ浮遊電位の複数のp型半導体領域28が同心状に形成されている。

【0063】

これら、p型ベース領域8、n型エミッタ領域9、ゲート電極11、p型半導体領域28

10

20

30

40

50

で構成される構造の集まりを総称して、エミッタ側構造2(ユニットの集合体)とする。

【0064】

そして、シリコン基板1の下主面上には不純物濃度 $1 \times 10^{17} \sim 1 \times 10^{19} / \text{cm}^3$ 程度のn型バッファ層3が形成され、n型バッファ層3の主面内には不純物濃度 $1 \times 10^{17} \sim 1 \times 10^{21} / \text{cm}^3$ 程度のp型コレクタ層4がp型ベース領域8の形成領域にほぼ対応して選択的に形成され、p型コレクタ層4と間隔を開けてp型コレクタ層4を囲むように不純物濃度 $1 \times 10^{17} \sim 1 \times 10^{21} / \text{cm}^3$ 程度のn型カソード領域6が選択的に形成された構成となっている。なお、p型コレクタ層4およびn型カソード領域6はシリコン基板1とは距離を隔てて形成されている。

【0065】

また、p型コレクタ層4に接触するように金属のコレクタ電極5pが形成され、n型カソード領域6およびn型バッファ層3の一部に接触するように金属のカソード電極5n(すなわち、IGBTに内蔵されたフリーホイールダイオードのカソード電極)が形成され、コレクタ電極5pとカソード電極5nの間には絶縁層7が形成されている。

【0066】

そして、カソード電極5nとコレクタ端子Cとの間には、アノードがカソード電極5nに接続され、カソードがコレクタ端子Cに接続されたダイオード13が電流抑制用素子として配設されている。

【0067】

< A - 2 . 動作 >

次にIGBT100の動作について説明する。

まず、コレクタ端子Cに負電圧(エミッタ端子に比べて負を意味する)が印加された場合、電流はエミッタ端子Eからエミッタ電極19、p型半導体領域12、p型ベース領域8、n型ベース層1、n型バッファ層3、n型カソード6、カソード電極5n、外部接続されたダイオード13を経てコレクタ端子Cに達する。

【0068】

すなわち、コレクタ端子Cに負電圧が印加された場合、p型半導体領域12、p型ベース領域8、n型ベース層1、n型バッファ層3、n型カソード領域6で構成される内蔵ダイオード(フリーホイールダイオード)と、カソード電極5nを介して外部から直列に接続されたダイオード13とは、エミッタ端子Eをアノード端子、コレクタ端子Cをカソード端子としていずれも順バイアスされて動作することになる。

【0069】

また、コレクタ端子Cに印加される負電圧が大きくなり、p型コレクタ層4とn型バッファ層3のpn接合の耐圧、いわゆる逆耐圧を超えた場合や、上記pn接合にリーク電流がある場合にはn型バッファ層3、p型コレクタ層4、コレクタ電極5pを経て、コレクタ端子Cに達する経路にも電流は流れれる。

【0070】

一方、コレクタ端子Cに正電圧(エミッタ端子に比べて正を意味する)が印加され、ゲート端子Gの電圧がオフ電位の場合、p型ベース領域8とn型ベース層1との間のpn接合で電圧が保持され、空乏層によって電流は遮断される。

【0071】

そして、コレクタ端子Cに正電圧が印加された状態で、ゲート端子Gの電圧がオン電圧となった場合、コレクタ端子C、コレクタ電極5p、p型コレクタ層4、n型バッファ層3、n型ベース層1、p型ベース領域8中のチャネル、n型エミッタ領域9、エミッタ電極19を経て、エミッタ端子Eに達する電流が流れれる。

【0072】

ここで、コレクタ端子Cに正電圧が印加された場合に、カソード電極5nからn型カソード領域6を通ってn型バッファ層3に到る電流経路(すなわち図43に示した電流i<sub>x</sub>)は、外部接続されたダイオード13によって遮断されるため、コレクタ端子Cに印加された電圧が従来の電力用半導体装置に比べて低くても、n型バッファ層3とp型コレクタ層

10

20

30

40

50

4との間の電圧（すなわち図43に示した電圧 $V_x$ ）は電導度変調を十分に起こすことができる電圧となる。

【0073】

従って、コレクタ端子Cに正電圧が印加された場合に、MOS電界効果トランジスタ（MOSトランジスタ）として動作することを防止し、オン電圧の低いIGBTを動作させることができる。

【0074】

外部接続されたダイオード13は、コレクタ端子Cに正の電圧が印加された場合に、カソード電極5nを介して電流が流れるのを抑制するものであり、動作上は高電圧がかからない。すなわち、コレクタ端子Cに正の電圧が印加されれば、IGBT100のp型コレクタ層4には順方向の電圧が印加されることになるため、n型バッファ層3は印加された電圧とほぼ同じ電圧となる。従って、ダイオード13は印加された電圧とn型バッファ層3の電圧との差に相当する耐圧があれば良いことになる。

【0075】

その結果、順方向電圧を低くでき、電流密度も高くすることができる所以、ダイオード13のチップ面積を小さくできる。

【0076】

なお、図1においては、ダイオード13は2つ配設されているように記載されているが、平面的にはn型カソード領域6はp型コレクタ層4の周囲に形成されているのでダイオード13は1つで良い。

10

20

【0077】

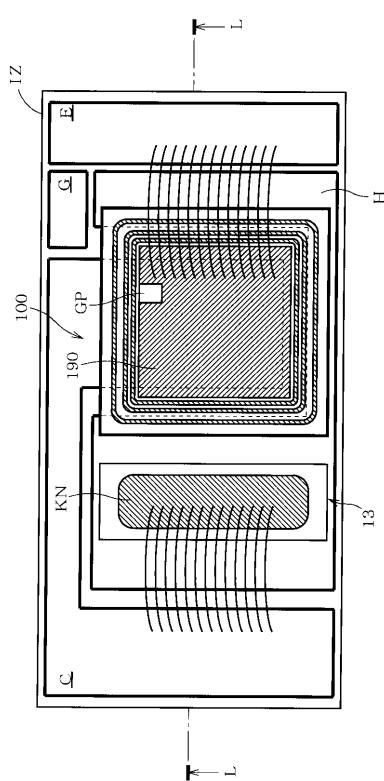

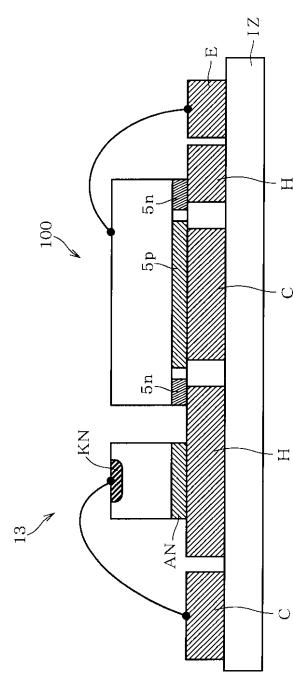

図3および図4にダイオード13が外部接続されたIGBT100の外観構成を示す。

【0078】

図3はダイオード13が外部接続されたIGBT100をエミッタ側の外部から見た図であり、図4は図3のL-L線での断面図である。なお、図4においては主要な構成の断面のみを示している。

【0079】

図3および図4に示すように絶縁基板IZ上に金属材料で、コレクタ端子C、エミッタ端子E、ゲート端子G、ダイオード接続端子Hがパターニングされている。IGBT100はコレクタ電極5pがコレクタ端子C上に、カソード電極5nがダイオード接続端子H上に接触するように載置されている。

30

【0080】

ダイオード13は、アノード層ANがダイオード接続端子H上に接触するように載置されている。そして、ダイオード13のカソード層KNは、ワイヤボンディングによりコレクタ端子Cに電気的に接続されている。

【0081】

なお、IGBT100のゲートパッドGPはゲート端子Gに、上部エミッタ電極190はエミッタ端子Eにワイヤボンディングにより電気的に接続されている。

【0082】

< A - 3 . 特徴的効果 >

40

以上説明したように、本発明に係る実施の形態1のIGBT100は、低耐圧、小面積の電流抑制用のダイオード13をカソード電極5nとコレクタ端子Cとの間に外部接続したので、フリーホイールダイオードを内蔵した構成であっても、コレクタ端子に正電圧が印加された場合に、カソード電極5nからn型カソード領域6を通ってn型バッファ層3に電流が流れることが防止され、n型バッファ層3の電位が上昇することを防止して、IGBTとして動作することが可能となる。電流抑制用のダイオード13を接続することで、n型カソード領域6の面積を小さくする必要がなくなるので、フリーホイールダイオードの動作時に電流集中による素子破壊が発生することを防止できる。

【0083】

なお、IGBT100およびダイオード13をインバータに採用してモデュール化した場

50

合には、ダイオード 13 が小型化できるのでモジュール面積を小さくできるという効果がある。

【0084】

また、フリーホイールダイオードを内蔵した IGBT をインバータに採用する場合、n 型ベース層 1 には IGBT がオンするときには、ダイオードがオフしたときのキャリアが残っており、キャリア発生に費やす時間が短くなり、IGBT をオンするのに必要な時間が短くなって、動作速度を早くすることができ、スイッチング損失を小さくすることができる。これは、ダイオードのオンに関しても同様である。

【0085】

< A - 4 . 変形例 >

10

以上説明したように、本発明に係る実施の形態 1 においては、IGBT 100 にダイオード 13 が外部接続された例を示したが、ダイオード 13 の代わりに図 5 に示すように、IGBT 100 のゲートとは相補的な信号が与えられる MOS ドランジスタ 130 を外部接続するようにしても良い。

【0086】

図 5 においてはカソード電極 5n とコレクタ端子 C との間に、n 型 MOS ドランジスタ 130 が電流抑制用トランジスタとして配設された例が示されている。n 型 MOS ドランジスタ 130 のゲートには IGBT 100 のゲート端子 G の反転信号バー G が与えられる構成となっている。n 型 MOS ドランジスタ 130 は、ゲート端子 G にゲートをオン状態とする (p 型ベース領域 8 中にチャネルを形成する) 電圧が与えられている場合には導通しないので、カソード電極 5n から n 型カソード領域 6 を通って n 型バッファ層 3 に到る電流経路が形成されないので、IGBT 100 のオン動作が妨げられることがない。

20

【0087】

< B . 実施の形態 2 >

< B - 1 . 装置構成 >

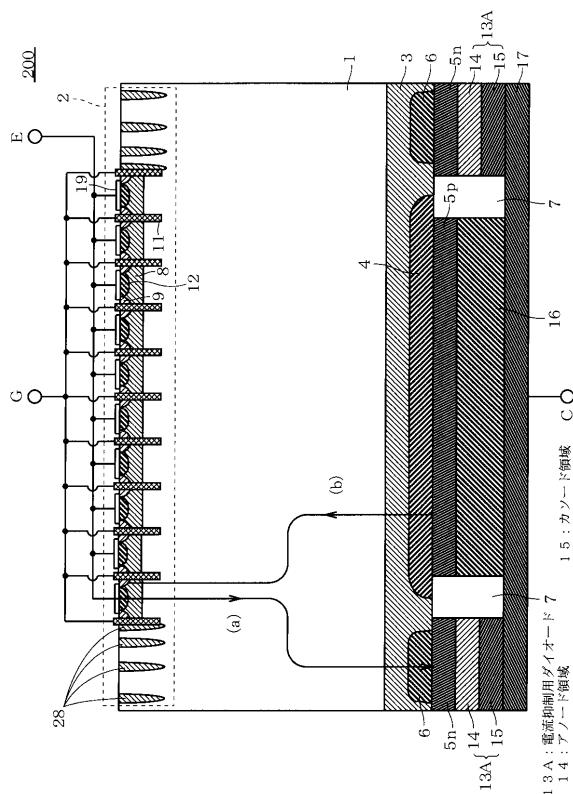

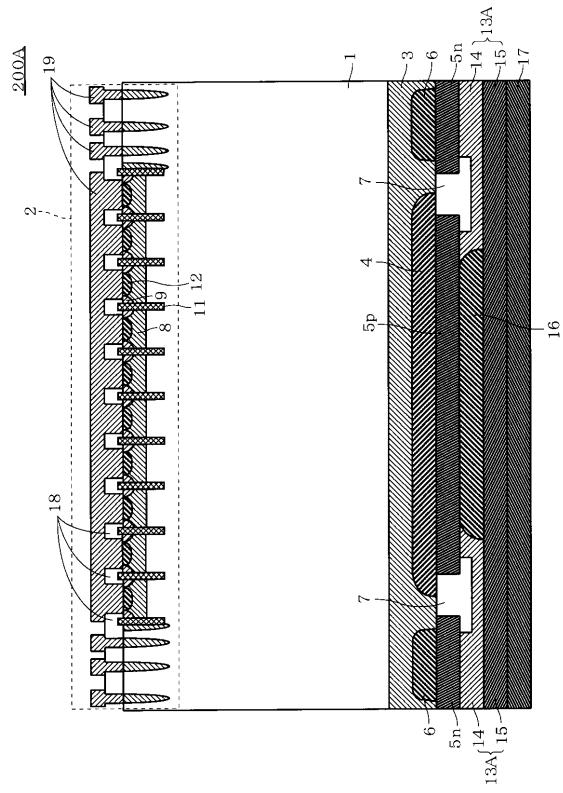

本発明に係る電力用半導体装置の実施の形態 2 を図 6 ~ 図 9 を用いて説明する。図 6 はフリーホイールダイオードを内蔵した IGBT 200 の構成を示す断面図である。なお、図 6 において、図 1 を用いて説明した IGBT 100 と同一の構成については同一の符号を付し、重複する説明は省略する。

30

【0088】

IGBT 200 においては、シリコン基板 1 の下主面上に n 型バッファ層 3 が形成され、n 型バッファ層 3 の主面内には p 型コレクタ層 4 が p 型ベース領域 8 の形成領域にほぼ対応して選択的に形成され、p 型コレクタ層 4 と間隔を開けて p 型コレクタ層 4 を挟むように n 型カソード領域 6 が選択的に形成された構成となっている。なお、p 型コレクタ層 4 および n 型カソード領域 6 はシリコン基板 1 とは距離を隔てて形成されている。そして、p 型コレクタ層 4 に接触するように金属のコレクタ電極 5p が形成され、n 型カソード領域 6 および n 型バッファ層 3 の一部に接触するように金属のカソード電極 5n が形成されている。

【0089】

さらに、カソード電極 5n (すなわち、IGBT に内蔵されたフリーホイールダイオードのカソード電極) には、p 型不純物を  $1 \times 10^{15} \sim 1 \times 10^{18} / \text{cm}^3$  程度含むアノード領域 14 がオーミック接続され、当該アノード領域 14 には n 型不純物を  $1 \times 10^{18} \sim 1 \times 10^{21} / \text{cm}^3$  程度含むカソード領域 15 がオーミック接続され、カソード電極 5n に直列に接続された電流抑制用ダイオード 13A を構成している。

40

【0090】

そして、コレクタ電極 5p には金属材料で形成された低抵抗導電体層 16 がオーミック接続され、コレクタ電極 5p および低抵抗導電体層 16 の積層体と、カソード電極 5n 、アノード領域 14 およびカソード領域 15 で構成される積層体の間には絶縁層 7 が形成されている。

【0091】

50

また、低抵抗導電体層 1 6 および電流抑制用ダイオードのカソード領域 1 5 にオーミック接続するとともに絶縁層 7 を覆うように最外部コレクタ電極 1 7 が形成されている。なお、最外部コレクタ電極 1 7 はコレクタ端子 C に接続されている。

【 0 0 9 2 】

< B - 2 . 動作 >

I G B T 2 0 0 の動作は、図 1 に示す I G B T 1 0 0 と基本的には同じである。I G B T 1 0 0 と異なる点は、I G B T 1 0 0 においては電流抑制用のダイオード 1 3 が外部接続されているのに対し、I G B T 2 0 0 ではフリー・ホール・ダイオードに加えて、アノード領域 1 4 およびカソード領域 1 5 で構成される電流抑制用のダイオード 1 3 A を内蔵しているので、コレクタ端子 C が負電位の場合、I G B T 1 0 0 では外部接続されたダイオード 1 3 を通って流れていた電流が、I G B T 2 0 0 では、内蔵されたダイオード 1 3 A を通って流れる点である。

10

【 0 0 9 3 】

ダイオード 1 3 A の存在により、コレクタ端子 C に正電圧が印加された場合に、カソード電極 5 n から n 型カソード領域 6 を通って n 型バッファ層 3 に電流が流れることが防止され、n 型バッファ層 3 の電位が上昇することを防止して、I G B T として動作させることが可能となる。

【 0 0 9 4 】

< B - 3 . 製造方法 >

次に、図 6 に示す I G B T 2 0 0 と実質的に同じ構成の I G B T 2 0 0 A の製造方法を、

20

製造工程を順に示す図 7 ~ 図 9 を用いて説明する。

【 0 0 9 5 】

まず、不純物濃度  $1 \times 10^{13} \sim 1 \times 10^{15} / \text{cm}^3$  程度の n 型シリコン基板 1 を準備し、図 7 に示すように n 型シリコン基板 1 の上主面に、p 型ベース領域 8 、n 型エミッタ領域 9 、ゲート電極 1 1 、p 型半導体領域 2 8 で構成されるエミッタ側構造 2 を形成し、n 型シリコン基板 1 の上主面から突出した各ゲート電極 1 1 の上部に個々に層間絶縁膜 1 8 を形成する。層間絶縁膜 1 8 は、ゲート電極 1 1 と、後に形成されるエミッタ電極とを電気的に分離するためのものである。なお、エミッタ側構造 2 の製造方法は従来の I G B T またはパワー MOS トランジスタと同じであり説明は省略する。

【 0 0 9 6 】

30

一方、n 型シリコン基板 1 の下主面に n 型バッファ層 3 を形成し、n 型バッファ層 3 の主面内に、p 型コレクタ層 4 を p 型ベース領域 8 の形成領域にほぼ対応させて選択的に形成し、p 型コレクタ層 4 と間隔を開けて p 型コレクタ層 4 を挟むように n 型カソード領域 6 を選択的に形成する。なお、n 型バッファ層 3 、p 型コレクタ層 4 、n 型カソード領域 6 はイオン注入などの通常の半導体製造プロセスで形成する。

【 0 0 9 7 】

その後、n 型バッファ層 3 、p 型コレクタ層 4 、n 型カソード領域 6 を覆うように、例えばアルミニウム、モリブデンなどの高融点金属で構成される導電体層をスパッタリング法などで形成し、当該導電体層を写真製版とエッティングにより p 型コレクタ層 4 に接触するコレクタ電極 5 p 、n 型カソード領域 6 および n 型バッファ層 3 の一部に接触するカソード電極 5 n にパターニングする。

40

【 0 0 9 8 】

そして、コレクタ電極 5 p およびカソード電極 5 n を覆うように、例えばシリコン酸化膜などの絶縁膜を形成し、当該絶縁膜を写真製版とエッティングによりコレクタ電極 5 p とカソード電極 5 n との間に埋め込まれた絶縁層 7 を形成する。

【 0 0 9 9 】

次に図 8 に示すように、コレクタ電極 5 p およびカソード電極 5 n 、絶縁層 7 を覆うように低濃度の p 型半導体層を形成し、写真製版とエッティングにより、カソード電極 5 n 、絶縁層 7 およびコレクタ電極 5 p の一部に接触するアノード領域 1 4 にパターニングする。

そして、アノード領域 1 4 に覆われない部分に高濃度に n 型不純物を含んだ n 型半導体層

50

を形成し、低抵抗導電体層 16 とする。

【0100】

なお、p 型半導体層を形成した後、低抵抗導電体層 16 となる部分にイオン注入により n 型不純物を高濃度に注入することで、アノード領域 14 および低抵抗導電体層 16 を形成するようにしても良い。

【0101】

その後、アノード領域 14 および低抵抗導電体層 16 に接触するように n 型不純物を高濃度に含んだ n 型半導体層を形成し、カソード領域 15 とすることで、電流抑制用のダイオードと並列に、コレクタ端子 C に接続される導電体層が同時に形成される。

【0102】

最後に、図 9 に示すように、カソード領域 15 上に、例えば、金を含む多層膜で構成される最外部コレクタ電極 17 を形成し、n 型エミッタ領域 9 の表面に接触するように、例えばアルミニウムの合金で構成されるエミッタ電極 19 を形成することで、IGBT200A を得ることができる。

【0103】

なお、IGBT200 と IGBT200A との大きな相違点は、IGBT200A ではカソード領域 15 が低抵抗導電体層 16 にも接触し、絶縁層 7 が最外部コレクタ電極 17 にまで達していない点と、低抵抗導電体層 16 が IGBT200 では金属材料で形成されているのに対し、IGBT200A では高濃度 n 型半導体層で形成されている点である。しかし、コレクタ電極 5p およびカソード電極 5n は、高濃度 n 型半導体層 ( すなわち低抵抗導電体層 16 ) とアノード領域 14 の p-n 接合で分離することができるので、IGBT200 および 200A の構成は実質的に同等である。

【0104】

< B - 4 . 特徴的効果 >

以上説明したように、本発明に係る実施の形態 2 の IGBT200 および 200A は、フリーホイールダイオードに加え、電流抑制用のダイオードも IGBT 内に内蔵されているため、モジュール内に外部接続の電流抑制用のダイオードを別個に配置する必要がなくなるので、IGBT200 および 200A をインバータ用途としてモジュール化した場合には、モジュール面積をさらに小さくできる。

【0105】

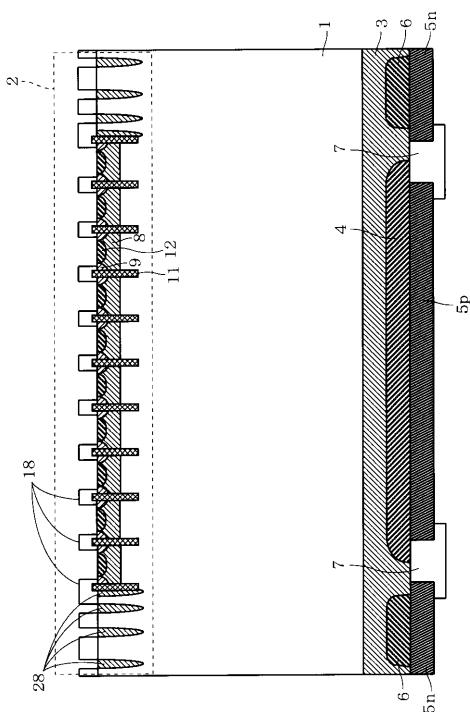

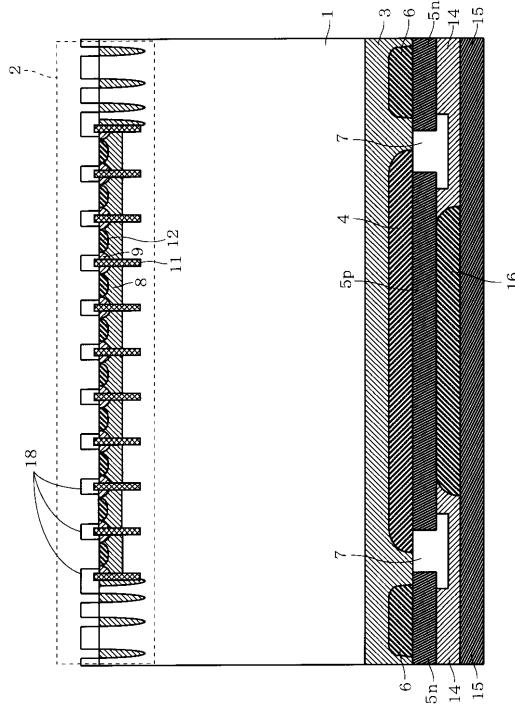

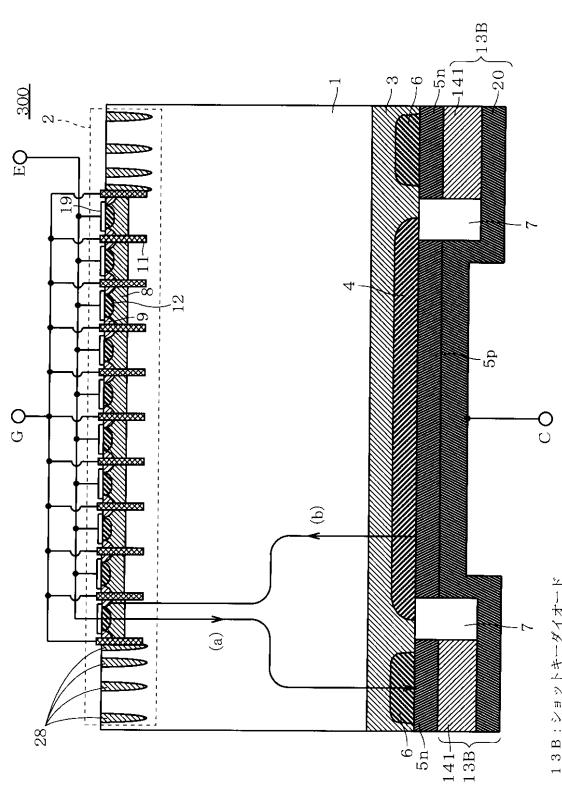

< C . 実施の形態 3 >

< C - 1 . 装置構成 >

本発明に係る電力用半導体装置の実施の形態 3 を図 10 ~ 図 12 を用いて説明する。図 10 はフリーホイールダイオードを内蔵した IGBT300 の構成を示す断面図である。なお、図 10 において、図 1 を用いて説明した IGBT100 と同一の構成については同一の符号を付し、重複する説明は省略する。

【0106】

IGBT300 においては、シリコン基板 1 の下主面上に n 型バッファ層 3 が形成され、n 型バッファ層 3 の主面内には p 型コレクタ層 4 が p 型ベース領域 8 の形成領域にほぼ対応して選択的に形成され、p 型コレクタ層 4 と間隔を開けて p 型コレクタ層 4 を挟むように n 型カソード領域 6 が選択的に形成された構成となっている。そして、p 型コレクタ層 4 にオーミック接続するように例えばアルミニウムの合金で構成されるコレクタ電極 5p が形成されている。

【0107】

また、n 型カソード領域 6 および n 型バッファ層 3 の一部にオーミック接続するように例えばアルミニウムの合金で構成されるカソード電極 5n ( すなわち、IGBT に内蔵されたフリーホイールダイオードのカソード電極 ) が形成され、カソード電極 5n には、p 型不純物を高濃度 (  $1 \times 10^{17} / \text{cm}^3$  程度 ) に含んだ p 型アノード領域 141 が接触するように形成されている。そして、コレクタ電極 5p および p 型アノード領域 141 に接触するように金属の最外部電極 20 が形成されている。

10

20

30

40

50

## 【0108】

最外部電極20は、p型アノード領域141とショットキー接続するように例えばニッケル(Ni)、チタン(Ti)、パラジウム(Pd)などの金属材料で形成されている。

## 【0109】

そして、コレクタ電極5pおよびカソード電極5nの間には絶縁層7が形成されている。なお、最外部電極20はコレクタ端子Cに接続されている。

## 【0110】

<C-2.動作>

IGBT300の動作は、図6に示すIGBT200と基本的には同じである。IGBT200と異なる点は、IGBT200においては電流抑制用のダイオード13Aが、p型アノード領域14およびn型カソード領域15の接合によるpn接合ダイオードであったものが、IGBT300においては、p型アノード領域141と最外部電極20とのショットキー接続によるショットキーダイオード13Bとなっている点である。

10

## 【0111】

なお、電流抑制用ダイオードをショットキーダイオードとしてすることで、そこでの電圧降下はカソード面積が同じであるならばpn接合ダイオードに比べて大きくなるため、ショットキーダイオード13Bのカソード面積は、例えば図6に示すダイオード13Aに比べ大きく設定されている。

## 【0112】

<C-3.特徴的効果>

20

以上説明したように、本発明に係る実施の形態3のIGBT300は、電流抑制用ダイオードをショットキーダイオードとしてすることで、半導体層一層分が不要になり、製造方法を簡略化して、製造コストを低減することができる。

## 【0113】

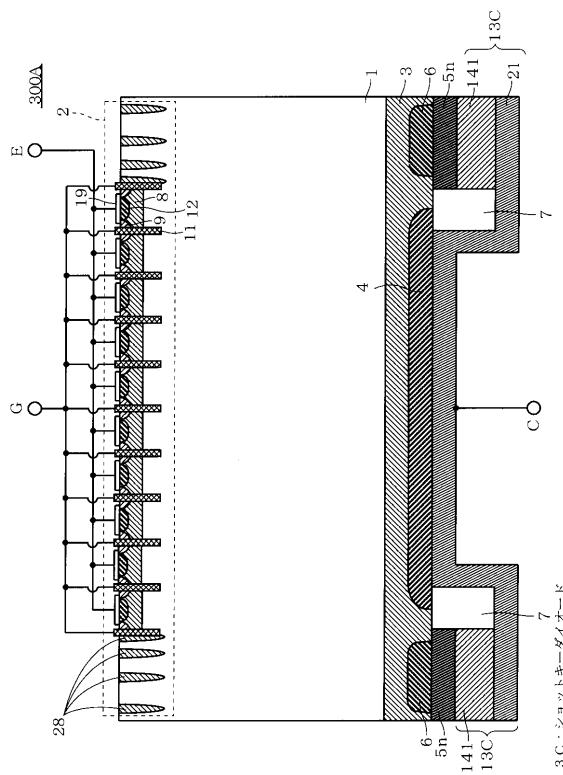

<C-4.変形例1>

電流抑制用ダイオードとしてショットキーダイオードを用いる構成としては、図10に示すIGBT300以外に、図11に示すIGBT300Aの構成を用いても良い。

## 【0114】

図11に示すIGBT300Aにおいては、p型コレクタ層4にはオーミック接続し、p型アノード領域141とはショットキー接続するように、例えばニッケル(Ni)、チタン(Ti)、パラジウム(Pd)などの金属材料で最外部電極21が形成され、p型アノード領域141と最外部電極21とのショットキー接続によるショットキーダイオード13Cが形成されている。また、カソード電極5nと最外部電極21との間には絶縁層7が形成されている。なお、図10に示すIGBT300と同一の構成については同一の符号を付している。

30

## 【0115】

このような構成とすることで、IGBT300のようにコレクタ電極5pを形成する必要がなく、構成がさらに単純になり、製造方法をさらに簡略化して、製造コストをさらに低減することができる。

## 【0116】

40

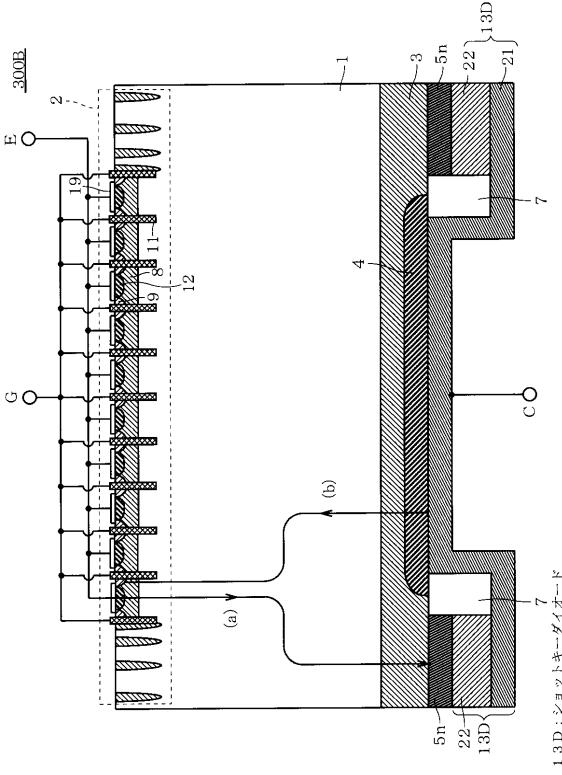

<C-5.変形例2>

電流抑制用ダイオードとしてショットキーダイオードを用いる構成としては、図10に示すIGBT300以外に、図12に示すIGBT300Bの構成を用いても良い。

## 【0117】

図12に示すIGBT300Bにおいては、シリコン基板1の下主面上にn型バッファ層3が形成され、n型バッファ層3の主面内にはp型コレクタ層4がp型ベース領域8の形成領域にほぼ対応して選択的に形成されている。

## 【0118】

そして、p型コレクタ層4の周囲のn型バッファ層3の主面にオーミック接続するように例えばアルミニウムの合金で構成されるカソード電極5n接続され、カソード電極5nに

50

は p 型コレクタ層 4 とは異なる半導体材料、例えばゲルマニウム (Ge)、PbS、InAs、InSb、PbTeなどの電子親和力がシリコンよりも大きな半導体で、p 型不純物を高濃度 ( $1 \times 10^{17} / \text{cm}^3$  程度) に含んで構成される p 型アノード領域 22 が接触するように形成されている。そして、p 型コレクタ層 4 および p 型アノード領域 22 に接触するように金属の最外部電極 21 が形成されている。そして、カソード電極 5n と最外部電極 21 との間には絶縁層 7 が形成されている。

#### 【0119】

最外部電極 21 は、p 型コレクタ層 4 にはオーミック接続し、p 型アノード領域 22 とはショットキー接続するように、例えばニッケル (Ni)、チタン (Ti)、パラジウム (Pd) などの金属材料で形成され、p 型アノード領域 22 と最外部電極 21 とのショットキー接続によるショットキーダイオード 13D が形成されている。なお、図 10 に示す IGBT300 と同一の構成については同一の符号を付している。

10

#### 【0120】

p 型アノード領域 22 を p 型コレクタ層 4 とは異なる半導体材料、すなわち電子親和力がシリコンよりも大きな半導体で構成することで、最外部電極 21 と p 型アノード領域 22 とのショットキー接続がより確実に行われることになる。

#### 【0121】

< D . 実施の形態 4 >

< D - 1 . 装置構成 >

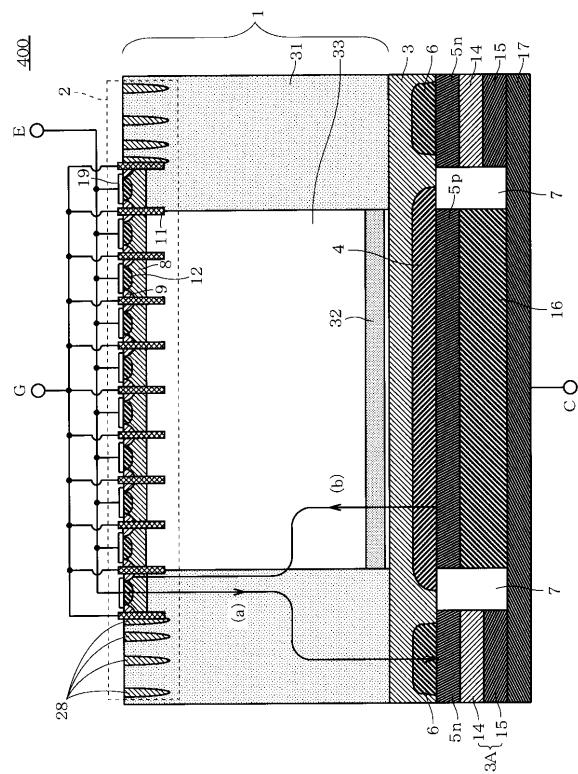

本発明に係る電力用半導体装置の実施の形態 4 を図 13 を用いて説明する。図 13 はフリー・ホイールダイオードを内蔵した IGBT400 の構成を示す断面図である。なお、図 13 において、図 2 を用いて説明した IGBT200 と同一の構成については同一の符号を付し、重複する説明は省略する。

20

#### 【0122】

IGBT400においては、シリコン基板 1 の p 型半導体領域 28 を含む周辺領域 31 (第 1 のライフタイム設定領域) と、シリコン基板 1 の下正面の n 型バッファ層 3 近傍で、p 型コレクタ層 4 の形成領域にほぼ対応した領域 32 (第 2 のライフタイム設定領域) と、シリコン基板 1 の中央部 33 とで、キャリア・ライフタイムがそれぞれ異なるように構成されている。

#### 【0123】

30

シリコン基板 1 の周辺領域 31 、すなわちフリー・ホイールダイオードの電流経路が集中する部分は、キャリア・ライフタイムが  $1 \mu\text{sec}$  程度の領域となっており、領域 32 ではキャリア・ライフタイムが  $0.1 \mu\text{sec}$  程度の領域となっている。また、中央部 33 ではキャリア・ライフタイムが  $10 \sim 100 \mu\text{sec}$  程度の領域となっている。

#### 【0124】

キャリア・ライフタイムの制御は、プロトン、ヘリウム、電子線等の粒子線をシリコン基板 1 に注入し、注入粒子の飛程位置付近で局所的に結晶欠陥を発生させ、当該結晶欠陥を少数キャリアの再結合中心として利用することで達成される。その際に、粒子線をステンレス、シリコン等の材料で構成されるマスクを通過させることで、加速エネルギーを加減して飛程位置を調整したり、注入量を調整して結晶欠陥の発生量を調整する。

40

#### 【0125】

例えば、周辺領域 31 の形成においては、シリコン基板 1 の中央部には、ステンレス、シリコン等の材料で構成されるマスクを配置し、質量が軽い電子線を  $1 \times 10^{14} / \text{cm}^2 \sim 1 \times 10^{15} / \text{cm}^2$  の照射量で注入する。

#### 【0126】

また、領域 32 の形成においては、シリコン基板 1 の周辺部には、ステンレス、シリコン等の材料で構成されるマスクを配置し、質量が比較的重いプロトン、ヘリウムを注入する。例えば、プロトンを使用する場合には、 $1 \times 10^{11} / \text{cm}^2 \sim 1 \times 10^{12} / \text{cm}^2$  の照射量で注入する。

#### 【0127】

50

なお、中央部 3 3 はシリコン基板 1 が本来有しているキャリアライフトайムとなっている。

【 0 1 2 8 】

< D - 2 . 動作 >

I G B T 4 0 0 の動作は、図 6 に示す I G B T 2 0 0 と基本的には同じである。I G B T 2 0 0 と異なる点は、フリーホイールダイオードの電流経路が集中する周辺領域 3 1 と、n 型バッファ層 3 近傍の領域 3 2 においてキャリアライフトайムの改変が行われている点である。

【 0 1 2 9 】

一般的に、I G B T ではコレクタ側のキャリアライフトайムを短くして、n 型ベース層中のキャリア密度を少なくし、1 パルス当たりのスイッチング損失を抑制する手法がとられている。この場合、I G B T のオン電圧は高くなり、定常損失は大きくなる。ここで、全消費電力において、スイッチング損失は動作周波数にほぼ比例し、定常損失は動作周波数に対してほぼ一定であるため、動作周波数に基づいて、消費電力が最小になるようにコレクタ側のキャリアライフトайムを設定する。 10

【 0 1 3 0 】

一方、I G B T のターンオン時、p i n ダイオード、すなわちフリーホイールダイオードのリカバリによる損失、p i n ダイオードでの定常損失は p i n ダイオードの i 層内のキャリア分布、すなわち、キャリアライフトайム分布によって決まり、ある動作周波数での最適キャリアライフトайム分布は I G B T の消費電力を最小にする分布とは異なるのが一般的である。 20

【 0 1 3 1 】

しかるに、I G B T 4 0 0 においてはフリーホイールダイオードの電流経路が集中する周辺領域 3 1 と、I G B T の電流経路が形成される n 型バッファ層 3 近傍の領域 3 2 においてキャリアライフトайム分布をそれぞれ改変している。そして、両領域におけるキャリアライフトайム分布は、フリーホイールダイオードと I G B T のそれぞれの消費電力を最小にする最適のキャリアライフトайム分布に設定されている。 20

【 0 1 3 2 】

従って、I G B T およびフリーホイールダイオードの動作時の消費電力が低減されることになる。 30

【 0 1 3 3 】

< D - 3 . 特徴的効果 >

以上説明したように、本発明に係る実施の形態 4 の I G B T 4 0 0 は、I G B T と内蔵されたフリーホイールダイオードとで、独立にほぼ最適にキャリアライフトайム分布が設定でき、I G B T 動作時の消費電力とダイオード動作時の消費電力を総合した全消費電力が最適化されている。

【 0 1 3 4 】

なお、I G B T 4 0 0 では図 6 を用いて説明した I G B T 2 0 0 と同様に、フリーホイールダイオードに加え、電流抑制用のダイオードも I G B T 内に内蔵されているため、モジュール内に外部接続の電流抑制用のダイオードを別個に配置する必要がなくなるので、I G B T 4 0 0 をインバータ用途としてモジュール化した場合には、モジュール面積をさらに小さくできることは言うまでもない。 40

【 0 1 3 5 】

なお、フリーホイールダイオードの電流経路が集中する周辺領域と、I G B T の電流経路が形成される領域においてキャリアライフトайムの改変を行うことは、図 1 に示した I G B T 1 0 0 および図 1 0 ~ 図 1 2 に示した I G B T 3 0 0 ~ 3 0 0 B に適用しても良いことは言うまでもない。

【 0 1 3 6 】

< E . 実施の形態 5 >

< E - 1 . 装置構成 >

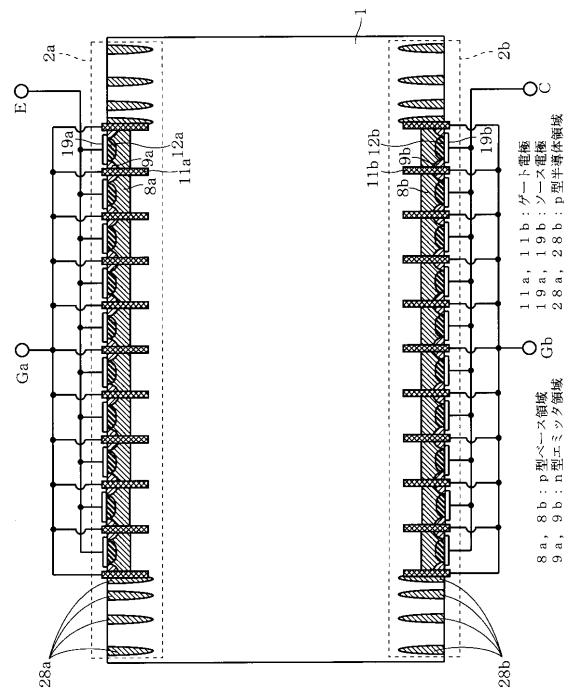

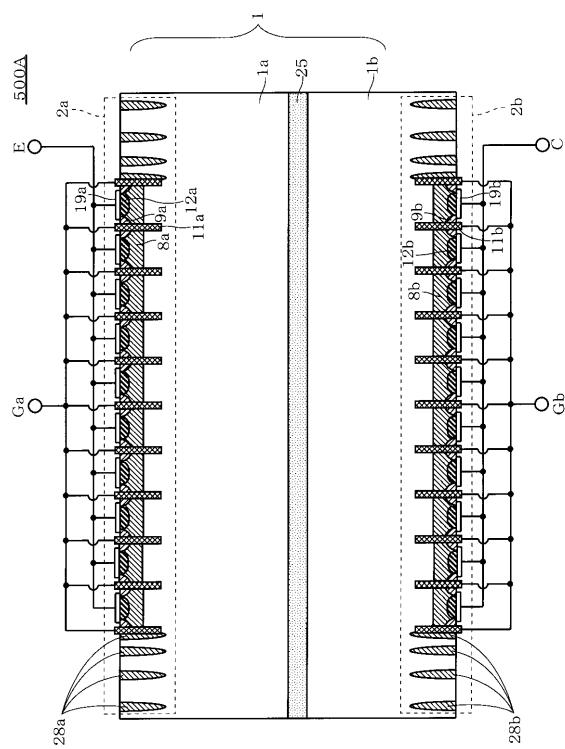

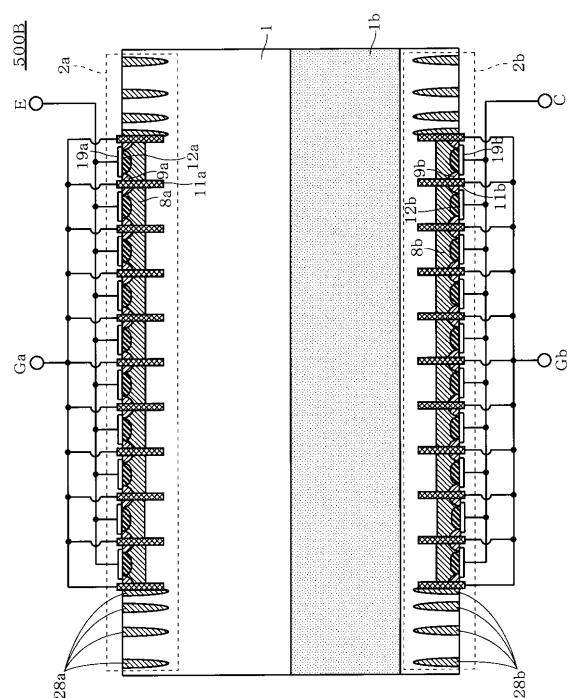

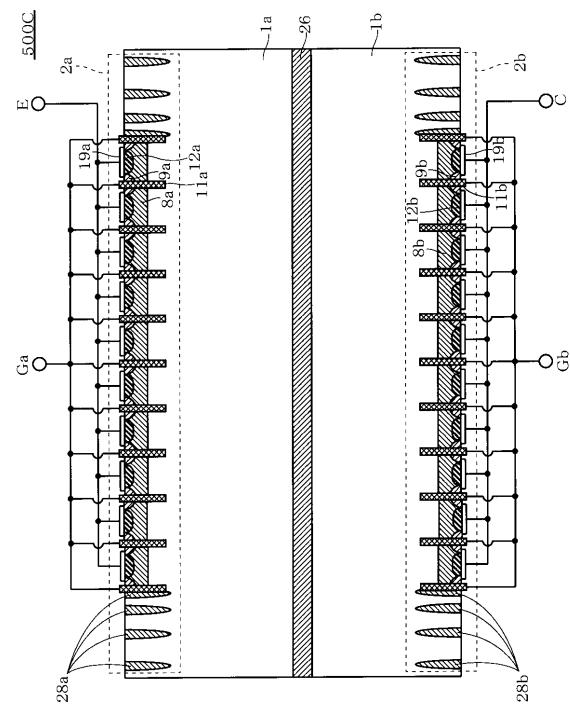

本発明に係る電力用半導体装置の実施の形態5を図14～図25を用いて説明する。図14は、フリーホイールダイオードを内蔵するとともに、電流抑制用素子としてMOSトランジスタを内蔵したIGBT500の構成を示す断面図である。

【0137】

図14に示すようにIGBT500は、シリコン基板1の上下主面に図1に示すIGBT100におけるエミッタ側構造2と同様のソース側構造2aおよび2bが形成された構成となっている。

【0138】

すなわち、n型のシリコン基板1の上主面表面内において、p型ベース領域8aが形成され、当該p型ベース領域8aを深さ方向に貫通するように複数のトレンチ型のゲート電極11aが並列に形成されている。ゲート電極11aの間のp型ベース領域8aの表面内には、p型不純物を比較的高濃度に含んだp型半導体領域12aが選択的に形成されている。p型半導体領域12aはp型ベース領域8aとソース電極19aとの電気的接続が良好に行われることを目的として設けられている。

【0139】

そして、p型半導体領域12aを両側から挟むように、n型不純物を比較的高濃度に含んだn型ソース領域9aが形成されている。なおn型ソース領域9aはゲート電極11aの表面に形成されたゲート絶縁膜(図示は省略)に接触する構成となっている。ここで、シリコン基板1はMOSトランジスタのドレイン層となる。

【0140】

そして、n型ソース領域9aの表面にはソース電極19aが形成され、ソース電極19aはエミッタ端子Eに電気的に接続され、ゲート電極11aはゲート端子Gaに電気的に接続されている。また、p型ベース領域8aを取り囲むように浮遊電位の複数のp型半導体領域28a(第1の電界緩和手段)が同心状に形成されている。

【0141】

これら、p型ベース領域8a、n型ソース領域9a、ゲート電極11a、p型半導体領域28aで構成される構造はMOSトランジスタからドレイン層を省いた構造と同様で、それらが複数集まっているので、ソース側構造2a(第1ユニットの集合体)と総称する。

【0142】

なお、ソース側構造2b(第2ユニットの集合体)も同様であり、p型ベース領域8aがp型ベース領域8b、n型ソース領域9aがn型ソース領域9b、ゲート電極11aがゲート電極11b、p型半導体領域28aがp型半導体領域28b(第2の電界緩和手段)となっている。なお、ソース電極19bがコレクタ端子Cに電気的に接続され、ゲート電極11bはゲート端子Gbに電気的に接続されている。

【0143】

< E - 2 . 動作 >

次にIGBT500の動作について説明する。

まず、ゲート端子GaおよびGbに共にゲートをオンさせる電圧が与えられた場合、コレクタ端子Cの電圧の正負にかかわらず、IGBT500は直列接続されたMOSトランジスタとして動作する。

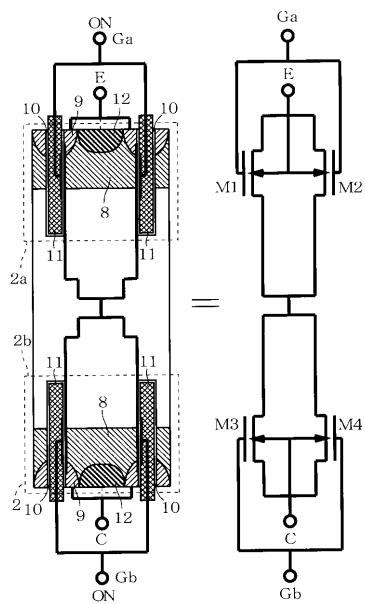

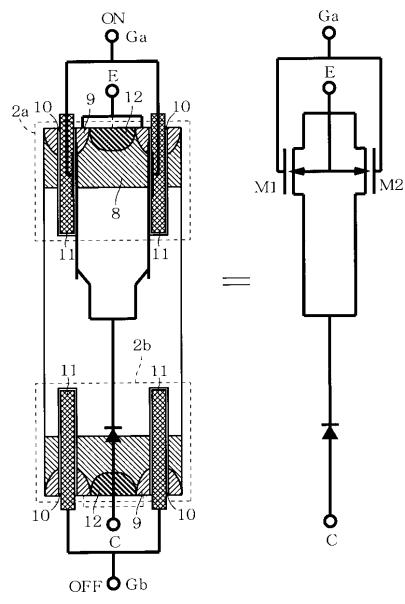

【0144】

図15にその状態を等価回路で示す。図15は、ソース側構造2aおよび2bにおいて、それぞれ2つのゲート電極11を含むようにIGBT500の一部を抜き出した図である。図15には、ソース側構造2aおよび2bでそれぞれ、並列接続されたMOSトランジスタM1、M2の組およびMOSトランジスタM3、M4の組が形成され、2つの組が直列に接続された状態が示されている。従って、コレクタ端子Cに与えられる電圧の正負によって電流の方向を逆転できる。

【0145】

同様に、ゲート端子GaおよびGbに共にゲートをオフさせる電圧が与えられた場合、コレクタ端子Cの電圧の正負にかかわらず、IGBT500はIGBTのオフ状態と同じ状

10

20

30

40

50

態になる。

【0146】

一方、ゲート端子G aがオン、ゲート端子G bがオフの場合、コレクタ端子Cに正電圧（エミッタ端子Eに負電圧）が印加されれば、IGBT500はIGBTのオン状態として動作し、コレクタ端子Cに負電圧（エミッタ端子Eに正電圧）が印加された場合は、ダイオードを構成するソース側構造2bに逆方向電圧が印加されたことになり、IGBT500には電流は流れない。

【0147】

逆に、ゲート端子G aがオフ、ゲート端子G bがオンの場合、コレクタ端子Cに正電圧（エミッタ端子Eに負電圧）が印加されれば、ダイオードを構成するソース側構造2aに逆方向電圧が印加されたことになり、IGBT500には電流は流れない。そして、コレクタ端子Cに負電圧（エミッタ端子Eに正電圧）が印加された場合は、IGBT500はIGBTのオン状態として動作するがゲート端子G aがオンの場合とは逆方向に電流が流れ、ソース側構造2aがフリーホイールダイオードとして動作する。

【0148】

このように、IGBT500はゲート端子G aおよびG bに相補的に信号を与えることで、実施の形態1～4で説明したと同様に、逆接続されたフリーホイールダイオードが内蔵されたIGBTとして動作する。

【0149】

なお、ゲート端子G aおよびG bに相補的に信号を与えることで、IGBTとフリーホイールダイオードとは完全に独立して動作することになるので、フリーホイールダイオードの存在によりIGBTとして動作せず、MOSトランジスタとして動作するという問題は生じない。

【0150】

図16にIGBTのオン状態を等価回路で示す。図16は、ソース側構造2aおよび2bにおいて、それぞれ2つのゲート電極11を含むようにIGBT500の一部を抜き出した図である。図16には、ソース側構造2aにおいて並列接続されたMOSトランジスタ1、M2の組が形成され、ソース側構造2bにおいてMOSトランジスタM1、M2の組に直列に順方向に接続されたダイオードD10が形成された状態が示されている。

【0151】

< E - 3 . 製造方法 >

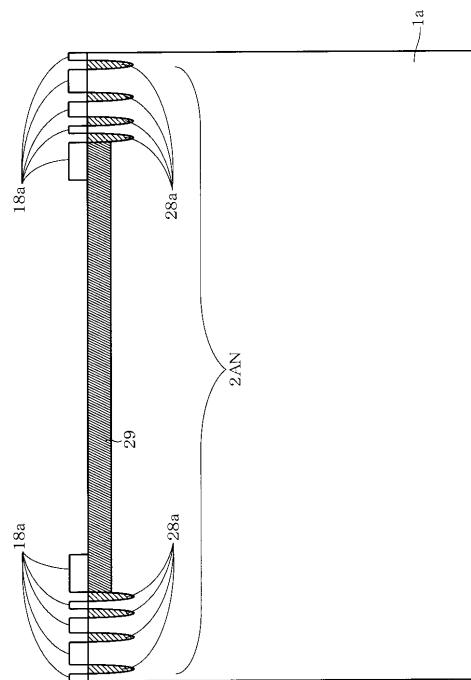

以下、IGBT500の製造方法を、製造工程を順に示す図17～図22を用いて説明する。

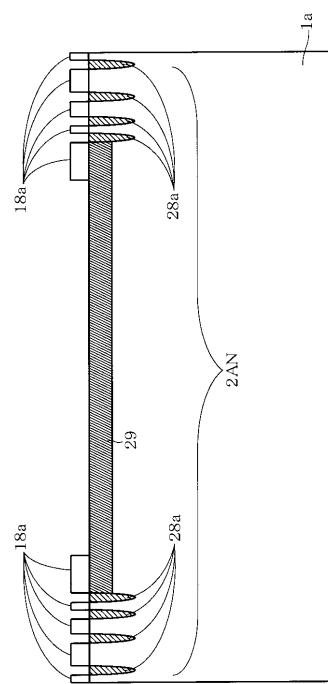

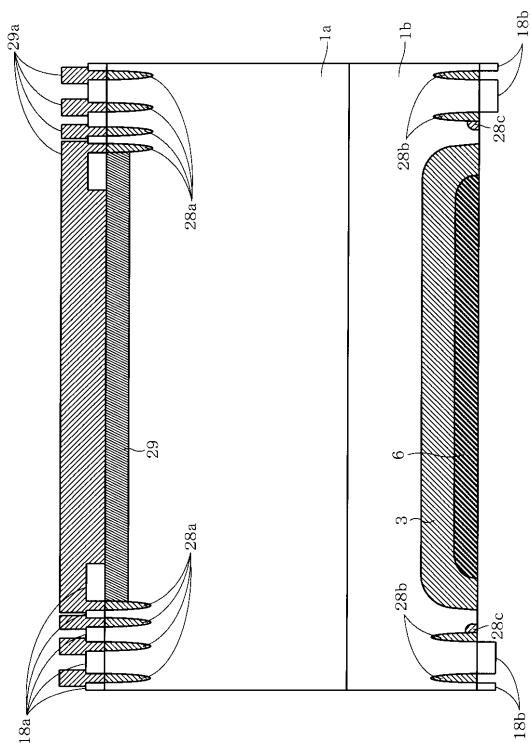

【0152】

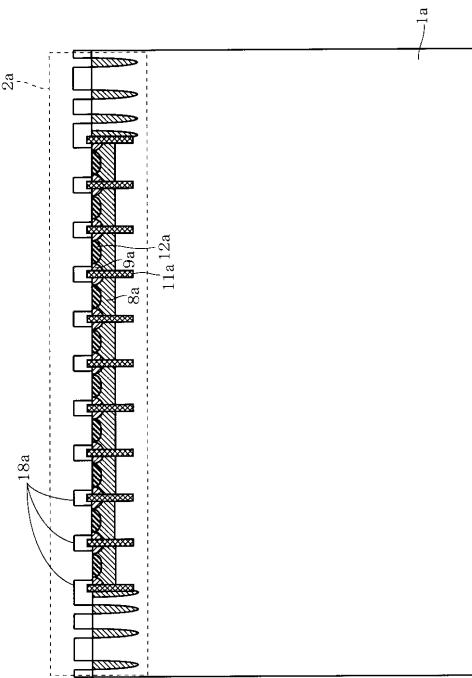

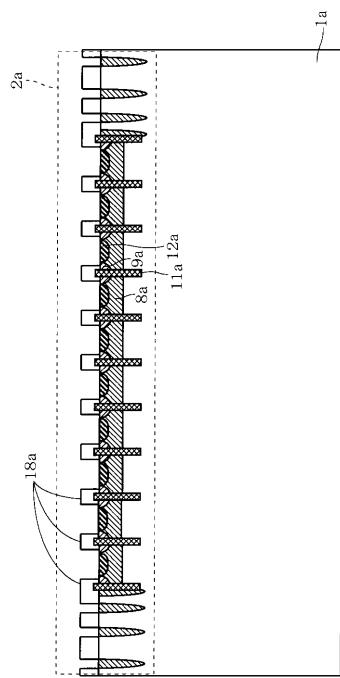

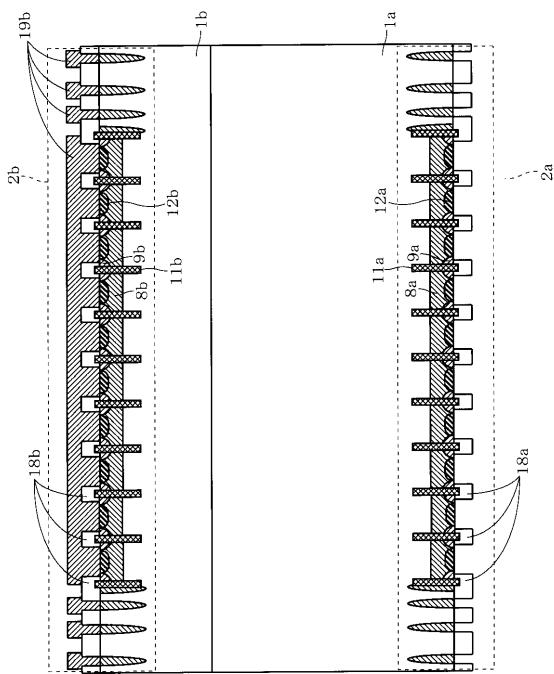

まず、図17および図18に示すように、不純物濃度 $1 \times 10^{13} \sim 1 \times 10^{15} / \text{cm}^3$ 程度のn型シリコン基板1aおよび1bを準備し、それぞれの一方の主面に、ソース側構造2aおよび2bを形成し、n型シリコン基板1aおよび1bの上主面から突出したゲート電極11aおよび11bの上部に個々に層間絶縁膜18aおよび18bを形成する。なお、ソース側構造2aおよび2bの製造方法は従来のIGBTまたはパワーMOSトランジスタと同じであり説明は省略する。

【0153】

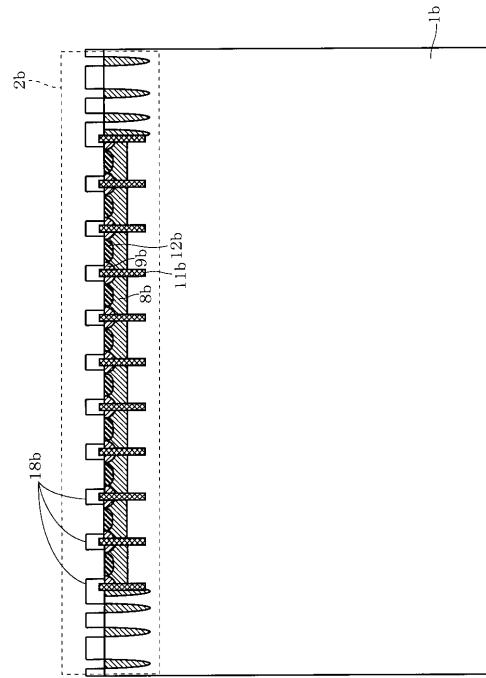

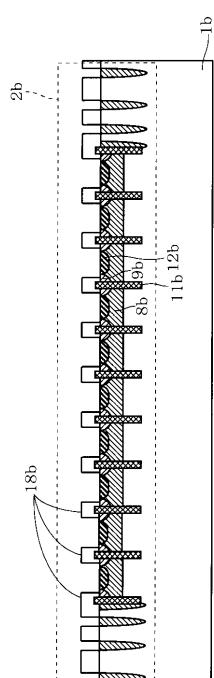

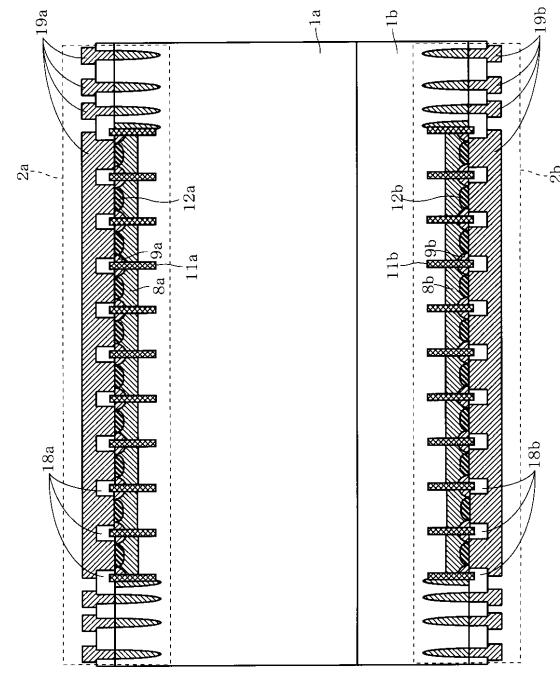

次に、図19および図20に示すように、シリコン基板1aおよび1bのドレイン側を所定の厚さに研磨する。

【0154】

次に、図21に示すように、研磨後のシリコン基板1aおよび1bをウェハ貼り合わせ法によって接合し、n型ソース領域9bの表面に接触するように、例えばアルミニウムの合金で構成されるソース電極19bを形成する。

【0155】

最後に、図22に示すように、n型ソース領域9aの表面に接触するように、例えばアルミニウムの合金で構成されるソース電極19aを形成することでIGBT500が完成す

10

20

30

40

50

る。

【0156】

なお、以上の説明では、ウェハ貼り合わせ法を用いた例を示したが、1枚のシリコン基板の上下主面に、通常の半導体装置の製造方法を用いてソース側構造2aおよび2bを作成するようにしても良いことは言うまでもない。

【0157】

< E - 4 . 特徴的効果 >

以上説明したように、ゲート端子G aおよびG bに相補的に信号を与えることで、本発明に係る実施の形態5のIGBT500は、基本的に実施の形態2と同様な効果を有する。

【0158】

加えて、ソース側構造2aおよび2bから双方向に電流を流すことができるため、トライアックの代替素子としても用いることができる。

【0159】

すなわち、コレクタ端子Cに正電圧が印加されている場合、ゲート端子G aをオン、ゲート端子G bをオフすることで、電流がソース側構造2bから2aの方向に流れ、ゲート端子G aをオフ、ゲート端子G bをオンすることで、電流が流れなくなる。

【0160】

そして、コレクタ端子Cに負電圧が印加されている場合、ゲート端子G aをオフ、ゲート端子G bをオンすることで、電流がソース側構造2aから2bの方向に流れ、ゲート端子G aをオン、ゲート端子G bをオフすることで、電流が流れなくなる。

【0161】

また、IGBT500は、双方向に電源電圧以上のコレクタ - エミッタ耐圧を有するため、異常電圧が印加されても破壊することが少なくなるという効果も有している。

【0162】

また、エミッタ領域内にモニタ用のエミッタ領域を設け、そこから得られるモニタ電流に基づいて、2つのゲート端子のオン・オフを切り換えて、ダイオード動作をさせたり、MOSトランジスタ動作をさせたりすることができる。

【0163】

一例を挙げると、ゲート端子G aおよびG bにそれぞれオン、オフの信号が印加されており、IGBTがオンからオフにスイッチする場合、オフする1μsec前にゲート端子G bにオン信号を印加し、半導体基板1内部のホール電流を減衰させた後、両ゲート端子をオフすることによって、スイッチング損失を低減することができる。

【0164】

この場合、ゲート端子G bがオンしている1μsec間の定常損失は増加するが、MOSトランジスタの駆動力を定格電流に比べて高く設定しておけば、全体の損失は低減できる。

【0165】

また、IGBT500は、ゲート信号、コレクタ - エミッタ間電圧の与え方によって、ダイオード、IGBT、あるいはMOSトランジスタとして双極性で動作させることができるので、例えば、インバータ回路をコンバータ回路に変更することもできる。

【0166】

< E - 5 . 変形例 1 >

以上説明したIGBT500については、図23に示すIGBT500Aのような構成としても良い。

【0167】

すなわち、IGBT500Aはシリコン基板1の厚み方向の中央部よりもソース側構造2bよりも位置に、少なくともp型ベース領域8aおよび8bの形成領域に対応するよう正面と平行にライフトライムの短い短ライフトライム領域25を有している。なお、短ライフトライム領域25を境として、便宜的に、ソース側構造2a側のシリコン基板1を基板1a、ソース側構造2b側のシリコン基板1を基板1bとする。

10

20

30

40

50

## 【0168】

このように、短ライフタイム領域25を有したIGBT500Aは図17～図22を用いて説明したIGBT500の製造工程において、図21および図22に示す工程の後、シリコン基板1aおよび1bの貼り合わせを行う前に、一方または双方のドレイン側の浅い領域に粒子線を照射し、結晶欠陥を形成してライフタイムを短くしておくことで、シリコン基板1aおよび1bの貼り合わせ後に、図23の短ライフタイム領域25が得られることになる。

## 【0169】

また、ウェハ貼り合わせ法で2枚の結晶性基板を接合した場合、例えば(100)面と(111)面、あるいは(100)面と(110)面のように各々の基板の結晶軸方位が異なっていたり、結晶軸方位が同じでも基板の面内回転により面方位が異なっている場合には、接合界面にライフタイムの短いアモルファス層が形成される。これを利用することできシリコン基板1aおよび1bの貼り合わせ後に、図23の短ライフタイム領域25を得るようにも良い。

10

## 【0170】

なお、面内回転により面方位が異なる場合とは、端的に言えば2枚のシリコン基板のオリエンテーションフラット面が互いにずれるように重ね合わせたときに生じる現象である。

## 【0171】

IGBT500Aのような構成を採用することで、IGBTとして動作する場合に、短ライフタイム領域25がホールのインジェクションを抑制しスイッチングによるエネルギー損失を低減することができる。

20

## 【0172】

すなわち、IGBTがオン状態にある場合に高電圧に耐えられるようにMOSトランジスタのチャネルとコレクタ層との間には抵抗値の高いn型半導体層が存在している。この層の抵抗値を下げるため、コレクタからホールがインジェクションされるが、IGBTがオン状態からオフ状態にスイッチングしたとき、ホールが残った状態になっているのでオフするのに時間がかかり、エネルギー損失が生じる。従って、IGBTをスイッチングが頻繁に行われる使い方をする場合には、コレクタからのホールのインジェクションを抑制して、オン状態からオフ状態の遷移速度を高めることでエネルギー損失を低減することができる。

30

## 【0173】

< E - 6 . 変形例 2 >

また、IGBT500は図24に示すIGBT500Bのような構成としても良い。すなわち、IGBT500Bは、シリコン基板1のライフタイムが、ソース側構造2a側とソース側構造2b側とで異なっている。

## 【0174】

図24においては、ソース側構造2a側のシリコン基板を基板1a、ソース側構造2b側のシリコン基板1を基板1bとし、基板1bライフタイムは基板1aよりも短く設定されている。

40

## 【0175】

このように、2つのソース側構造のうち一方よりのドレイン層のライフタイムが短くなったIGBT500Bは、図17～図22を用いて説明したIGBT500の製造工程において、図21および図22に示す工程の後、シリコン基板1aおよび1bの貼り合わせを行う前に、一方の基板への粒子線の照射、あるいは基板濃度の変更により得ることができる。

## 【0176】

そして、IGBT500Bのような構成を採用することで、IGBTとして動作する場合に、シリコン基板1bがホールのインジェクションを抑制しスイッチングによるエネルギー損失を低減することができる。

## 【0177】

50

なお、以上説明した変形例1および2の構成においては、ソース側構造2b側、すなわちコレクタ端子側に短ライフトайム領域25、ライフトайムが短かい基板1bを設けている。これは、ホールのインジェクションを抑制するにはコレクタ端子に近い方にインジェクション抑制手段を設けることが有効であり、その領域も狭い方が有効なので基板1bの厚さは基板1aよりも薄くなっている。

【0178】

<E-7. 変形例3>

また、IGBT500は図25に示すIGBT500Cのような構成としても良い。すなわち、IGBT500Cは、シリコン基板1の内部に、少なくともp型ベース領域8aおよび8bの形成領域に対応するように主面と平行に金属層あるいはn型不純物を高濃度( $1 \times 10^{16} \sim 1 \times 10^{20} / \text{cm}^3$ 程度)に含んだn型半導体層26を有している。なお、金属層26を境として、便宜的に、ソース側構造2a側のシリコン基板1を基板1a、ソース側構造2b側のシリコン基板1を基板1bとする。なお、金属層は単一金属層でも合金層でも良い。

10

【0179】

このように、金属層(あるいは高濃度n型半導体層)26を有したIGBT500Cは図17～図22を用いて説明したIGBT500の製造工程において、図21および図22に示す工程の後、シリコン基板1aおよび1bの貼り合わせを行う前に、一方または双方のドレイン側にアルミニウムなどの金属層をスパッタ法などで堆積したり、一方または双方のドレイン側の浅い領域にリンや砒素などのn型不純物をイオン注入することで得られる。

20

【0180】

IGBT500Cのような構成を採用することで、金属層(あるいは高濃度n型半導体層)26での抵抗が低減され、オン電圧を低くすることができる。

【0181】

<F. 実施の形態6>

<F-1. 装置構成>

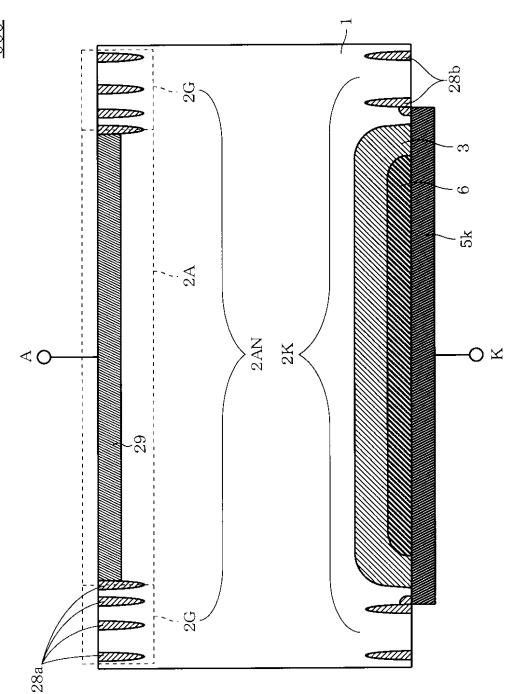

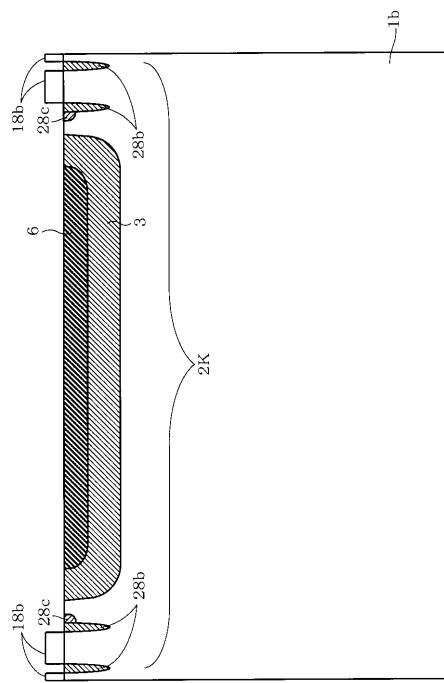

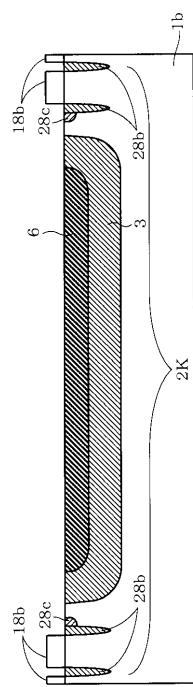

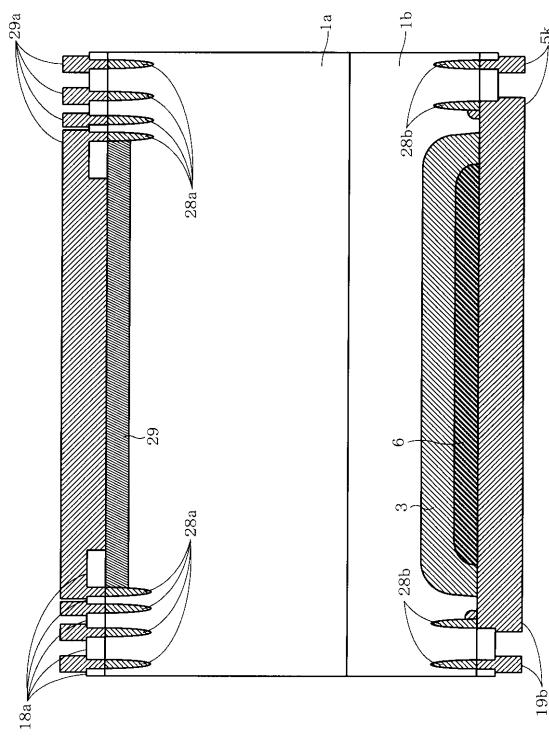

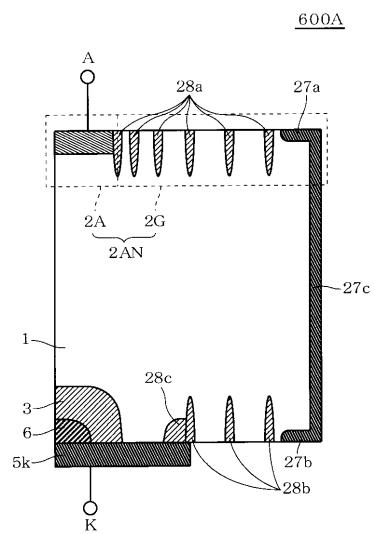

本発明に係る電力用半導体装置の実施の形態6を図26～図37を用いて説明する。図26は独立したIGBTおよびフリーホイールダイオードで構成される電力用半導体装置のうち、フリーホイールダイオード600の構成を示す断面図である。

30

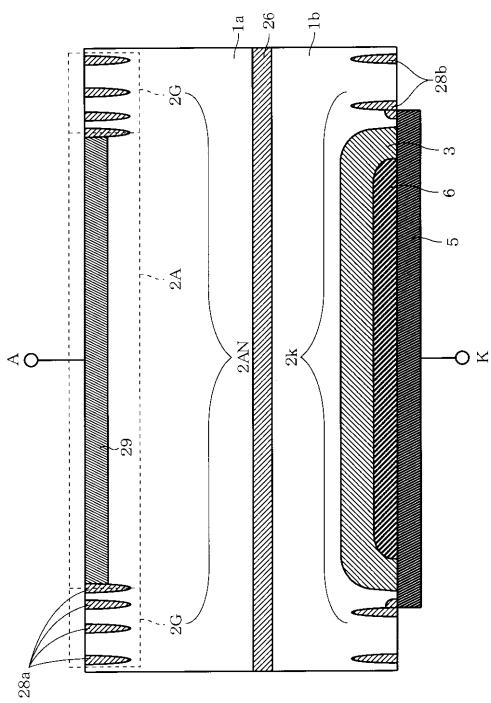

【0182】

図26に示すようにフリーホイールダイオード600は、n型のシリコン基板1の上主面表面内において、p型不純物を $1 \times 10^{13} \sim 1 \times 10^{18} / \text{cm}^3$ 程度含んだアノード層29が形成され、アノード層29の表面には図示しないアノード電極が形成され、アノード電極はアノード端子Aに電気的に接続されている。これらアノード層29が形成される領域をアノード領域2Aと呼称する。

【0183】

そして、アノード領域2Aを取り囲むように浮遊電位の複数のp型半導体領域28aが同心状に形成され、電界緩和リング領域2Gを形成している。なお、アノード領域2Aおよび電界緩和リング領域2Gの構造を総称して、アノード側構造2ANとする。

40

【0184】

また、シリコン基板1の下主面表面内には、n型バッファ層3が選択的に形成され、n型バッファ層3の表面内にはn型不純物を比較的高濃度に含んだn型半導体層で構成されたn型カソード領域6が選択的に形成されている。そして、n型バッファ層3、n型カソード領域6、シリコン基板1の表面に接触するように金属のカソード電極5kが形成されている。また、カソード電極5kはカソード端子Kに電気的に接続されている。そして、n型バッファ層3を取り囲むように浮遊電位の複数のp型半導体領域28bが同心状に形成されている。なお、n型バッファ層3、n型カソード領域6、p型半導体領域28bを総称してカソード側構造2Kとする。なお、p型半導体領域28aおよび28bは、最も内側のものはそれぞれアノード電位およびカソード電位となっており、それ以外は浮遊電

50

位となっている。

【0185】

ここで、n型カソード領域6はカソード電極5kとn型バッファ層3とのオーミックコンタクトを達成するための層であり、シリコン基板1はp in nダイオードのi層に対応する層である。

【0186】

図27にフリー・ホイール・ダイオード600の周辺領域の詳細を示す。図27において、p型半導体領域28aは内側から外側に向けて順に配設間隔が徐々に広くなるように形成されている。なお、p型半導体領域28bも内側から外側に向けて順に配設間隔が徐々に広くなるように形成されているが、その間隔の変化の度合いはp型半導体領域28aよりも緩やかである。このような構成とすることで、カソード電極5kに正電圧を印加した場合、最も電界緩和を効率的に行うことができる。

【0187】

また、電界緩和リング領域2Gの端縁部にはn型不純物を $1 \times 10^{18} \sim 1 \times 10^{20} / \text{cm}^3$ 程度含んだ浮遊電位のn型半導体領域27が浅く形成され、最もn型バッファ層3よりもp型半導体領域28bには、カソード電極5kとの接続を確実に行うため、形成深さが浅いp型半導体領域28cが接続されている。

【0188】

< F - 2 . 動作 >

浮遊電位のp型半導体領域28aおよび28bは、周辺部での電界を緩和するために設けられたもので、p n接合近傍で空乏層を広げることによって一定の電界を保つようにしている。

【0189】

カソード電極5kに正電圧が印加された場合、図39に示したダイオードD1Lなどでは、その周辺部、すなわち電界緩和リング領域2DGにも上記電圧と同程度の電圧がかかっていた。しかし、n型バッファ層3を取り囲むように浮遊電位の複数のp型半導体領域28bを形成することで、当該p型半導体領域28bとn型のシリコン基板1とのp n接合近傍で空乏層が広がり、電圧降下が発生するので、電界緩和リング領域2Gにかかる電圧が低下し、電界緩和リング領域2Gに設けるべきp型半導体領域28aの個数および配設間隔を削減することができる。

【0190】

また、図27においては電界緩和リング領域2Gの端縁部に浮遊電位のn型半導体領域27が浅く形成された例を示したが、n型半導体領域はシリコン基板1の下主面のp型半導体領域28bが形成される領域に形成しても良い。n型半導体領域は空乏層が基板端面に及ぶのを防止することができる。

【0191】

< F - 3 . 製造方法 >

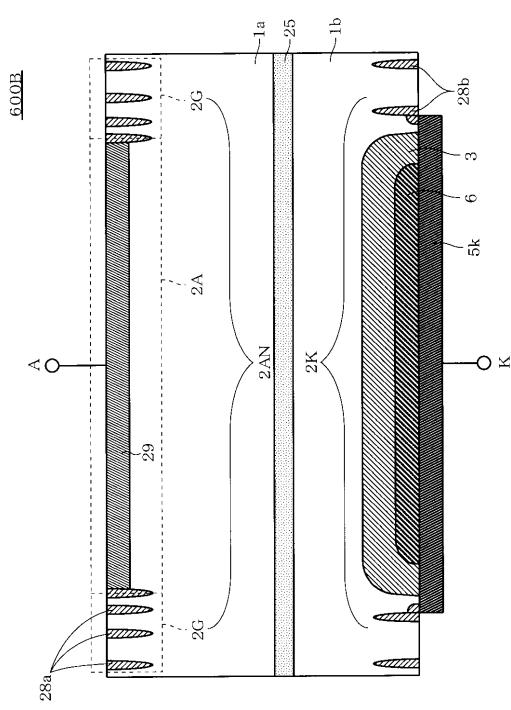

以下、フリー・ホイール・ダイオード600の製造方法を、製造工程を順に示す図28～図33を用いて説明する。

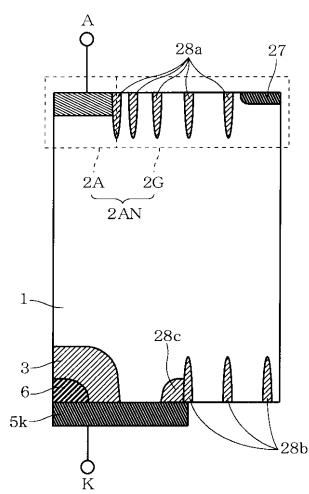

【0192】

まず、図28および図29に示すように、不純物濃度 $1 \times 10^{13} \sim 1 \times 10^{15} / \text{cm}^3$ 程度のn型シリコン基板1aおよび1bを準備し、それぞれの一方の主面に、アノード側構造2ANおよびカソード側構造2Kを形成する。このとき、p型半導体領域28aの形成個数および配設間隔は従来のフリー・ホイール・ダイオードよりも少なく形成する。その後、後に形成されるアノード電極およびカソード電極とp型半導体領域28aおよび28bとを電気的に分離するための層間絶縁膜18aおよび18bを選択的に形成する。なお、p型半導体領域28bの形成に際してp型半導体領域28cを形成し、p型半導体領域28aの形成後にn型半導体領域(図示せず)を形成する。

【0193】

なお、アノード側構造2ANの製造方法は従来のフリー・ホイール・ダイオードの製造方法

10

20

30

40

50

と同様であり、カソード側構造 2 K は、一般的なイオン注入法により、シリコン基板 1 表面内に n 型バッファ層 3 を選択的に形成し、n 型バッファ層 3 の表面内に n 型カソード領域 6 を選択的に形成し、n 型バッファ層 3 を囲むように p 型半導体領域 2 8 b を形成することを得られる。

【 0 1 9 4 】

次に、図 3 0 および図 3 1 に示すように、シリコン基板 1 a および 1 b を所定の厚さに研磨する。このとき、シリコン基板 1 b の厚さがシリコン基板 1 a よりも薄くなるまで研磨する。

【 0 1 9 5 】

次に、図 3 2 に示すように、研磨後のシリコン基板 1 a および 1 b をウェハ貼り合わせ法 10 によって接合し、アノード層 2 9 の表面に接触するように、例えばアルミニウムの合金で構成されるアノード電極 2 9 a を形成する。

【 0 1 9 6 】

最後に、図 3 3 に示すように、n 型バッファ層 3 、n 型カソード領域 6 、シリコン基板 1 の表面に接触するように、例えばアルミニウムの合金で構成されるカソード電極 5 k を形成することでフリー・ホイール・ダイオード 6 0 0 が完成する。

【 0 1 9 7 】

なお、以上の説明では、ウェハ貼り合わせ法を用いた例を示したが、1 枚のシリコン基板の上下主面に、通常の半導体装置の製造方法を用いてアノード側構造 2 A N およびカソード側構造 2 K を交互に作成するようにしても良いことは言うまでもない。 20

【 0 1 9 8 】

< F - 4 . 特徴的効果 >

以上説明した、本発明に係る実施の形態 6 のフリー・ホイール・ダイオード 6 0 0 は、n 型バッファ層 3 を取り囲むように浮遊電位の複数の p 型半導体領域 2 8 b が設けられており、電界緩和リング領域 2 G にかかる電圧が低下し、電界緩和リング領域 2 G に設けるべき p 型半導体領域 2 8 a の個数および配設間隔を削減することができる、周辺領域の面積を低減して素子面積を小さくでき、独立した I G B T およびフリー・ホイール・ダイオードで構成される電力用半導体装置の小型化、低コスト化が達成できる。

【 0 1 9 9 】

なお、実施の形態 6 においては浮遊電位の複数の p 型半導体領域で構成される電界緩和リングについて説明したが、本発明は p 型半導体領域の代わりに、基板主面上に形成された酸化膜と、その上に形成された電極とで構成されるフィールドプレートを設ける場合でも同様の効果を有する。なお、フィールドプレートはその電極に電圧を印加することで、印加した電圧と反対極性の電荷を基板中に誘起し空乏層の電界を緩和する機能を有している。 30

【 0 2 0 0 】

< F - 5 . 変形例 1 >

以上説明したフリー・ホイール・ダイオード 6 0 0 については、図 3 4 に示すフリー・ホイール・ダイオード 6 0 0 A のような構成としても良い。

【 0 2 0 1 】

図 3 4 はフリー・ホイール・ダイオード 6 0 0 A の周辺領域の詳細を示す図である。図 3 4 において、電界緩和リング領域 2 G の端縁部には浮遊電位の n 型半導体領域 2 7 a が浅く形成され、シリコン基板 1 の下主面の p 型半導体領域 2 8 b が形成される領域の端縁部にも浮遊電位の n 型半導体領域 2 7 b が浅く形成されている。 40

【 0 2 0 2 】

そして、シリコン基板 1 の側面にも浮遊電位の n 型半導体領域 2 7 c が形成されている。

【 0 2 0 3 】

なお、n 型半導体領域 2 7 a および 2 7 b は、図 2 8 ~ 図 3 3 を用いて説明したフリー・ホイール・ダイオード 6 0 0 の製造工程において、図 3 0 および図 3 1 に示す工程の後、シリコン基板 1 a および 1 b の貼り合わせを行う前に、それぞれの基板主面の端縁部に選択的 50

に n 型不純物をイオン注入することによって形成すれば良い。

【 0 2 0 4 】

また、n 型半導体領域 2 7 c は、シリコン基板 1 a および 1 b の貼り合わせを行った後、斜め方向から n 型不純物をイオン注入する方法や、貼り合わせ後の基板を n 型不純物雰囲気にさらす方法で形成する。

【 0 2 0 5 】

このように、n 型半導体領域を基板の側面にも形成することで、空乏層が基板側面に及ぶのを防止することができる。

【 0 2 0 6 】

< F - 6 . 変形例 2 >

10

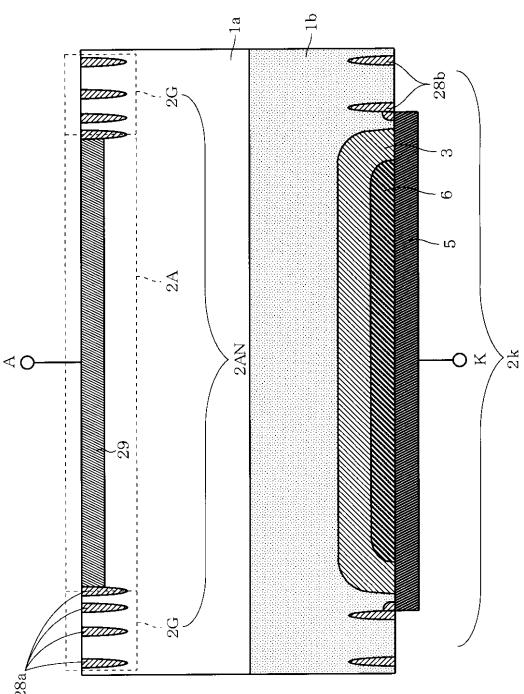

また、フリー・ホイールダイオード 6 0 0 は、図 3 5 に示すフリー・ホイールダイオード 6 0 0 B のような構成としても良い。

【 0 2 0 7 】

すなわち、フリー・ホイールダイオード 6 0 0 B はシリコン基板 1 の厚み方向の中央部よりもカソード側構造 2 K よりの位置にライフタイムの短い短ライフタイム領域 2 5 を有している。なお、短ライフタイム領域 2 5 を境として、便宜的に、アノード側構造 2 A N 側のシリコン基板 1 を基板 1 a 、カソード側構造 2 K 側のシリコン基板 1 を基板 1 b とする。

【 0 2 0 8 】

このように、短ライフタイム領域 2 5 を有したフリー・ホイールダイオード 6 0 0 B は、図 2 8 ~ 図 3 3 を用いて説明したフリー・ホイールダイオード 6 0 0 の製造工程において、図 3 0 および図 3 1 に示す工程の後、シリコン基板 1 a および 1 b の貼り合わせを行う前に、一方または双方の基板の浅い領域に粒子線を照射し、結晶欠陥を形成してライフタイムを短くしておくことで、シリコン基板 1 a および 1 b の貼り合わせ後に、図 3 5 の短ライフタイム領域 2 5 が得られることになる。

20

【 0 2 0 9 】

また、ウェハ貼り合わせ法で 2 枚の結晶性基板を接合した場合、例えば (1 0 0) 面と (1 1 1) 面、あるいは (1 0 0) 面と (1 1 0) 面のように各々の基板の結晶軸方位が異なっていたり、結晶軸方位が同じでも基板の面内回転により面方位が異なっている場合には、接合界面にライフタイムの短いアモルファス層が形成される。これを利用することでシリコン基板 1 a および 1 b の貼り合わせ後に、図 3 5 の短ライフタイム領域 2 5 を得るようにも良い。

30

【 0 2 1 0 】

フリー・ホイールダイオード 6 0 0 B のような構成を採用することで、短ライフタイム領域 2 5 がホールのインジェクションを抑制しスイッチングによるエネルギー損失を低減することができる。

【 0 2 1 1 】

< F - 7 . 変形例 3 >

また、フリー・ホイールダイオード 6 0 0 は図 3 6 に示すフリー・ホイールダイオード 6 0 0 C のような構成としても良い。すなわち、フリー・ホイールダイオード 6 0 0 C は、シリコン基板 1 のライフタイムが、アノード側構造 2 A N 側とカソード側構造 2 K 側とで異なっている。

40

【 0 2 1 2 】

図 3 6 においては、アノード側構造 2 A N 側のシリコン基板を基板 1 a 、カソード側構造 2 K 側のシリコン基板 1 を基板 1 b とし、基板 1 b のライフタイムは基板 1 a よりも短く設定されている。

【 0 2 1 3 】

このような構造のフリー・ホイールダイオード 6 0 0 C は、図 2 8 ~ 図 3 3 を用いて説明したフリー・ホイールダイオード 6 0 0 の製造工程において、図 3 0 および図 3 1 に示す工程の後、シリコン基板 1 a および 1 b の貼り合わせを行う前に、基板 1 b への粒子線の照射、あるいは基板濃度の変更により得ることができる。

50

## 【0214】

そして、フリーホイールダイオード600Cのような構成を採用することで、シリコン基板1bがホールのインジェクションを抑制しスイッチングによるエネルギー損失を低減することができる。

## 【0215】

<F-8.変形例4>

また、フリーホイールダイオード600は図37に示すフリーホイールダイオード600Dのような構成としても良い。すなわち、フリーホイールダイオード600Dは、シリコン基板1の厚み方向の中央部よりもカソード側構造2Kよりの位置に金属層（あるいは高濃度n型半導体層）26を有している。なお、金属層26を境として、便宜的に、アノード側構造2AN側のシリコン基板を基板1a、カソード側構造2K側のシリコン基板1を基板1bとする。なお、金属層は単一金属層でも合金層でも良い。

10

## 【0216】

このように、金属層（あるいは高濃度n型半導体層）26を有したフリーホイールダイオード600Dは、図28～図33を用いて説明したフリーホイールダイオード600の製造工程において、図30および図31に示す工程の後、シリコン基板1aおよび1bの貼り合わせを行う前に、一方または双方の基板の浅い領域にアルミニウムなどの金属層をスパッタ法などで堆積したり、一方または双方の基板の浅い領域にリンや砒素などのn型不純物をイオン注入することで得られる。

## 【0217】

20

フリーホイールダイオード600Dのような構成を採用することで、金属層（あるいは高濃度n型半導体層）26での抵抗が低減され、オン電圧を低くすることができる。

## 【0218】

<G.本発明の他の適用例>

以上説明した実施の形態1～5においては、本発明をトレンチ型IGBTに適用した例を示したが、平面型IGBTに適用しても同様の効果があること言うまでもない。

## 【0219】

また、以上説明した実施の形態1～6においては、本発明をnチャネル型IGBT、nチャネル型MOSトランジスタ、p<sup>+</sup>/n<sup>-</sup>型ダイオードに適用した例を示したが、nチャネル型IGBT、nチャネル型MOSトランジスタ、p<sup>-</sup>/n<sup>+</sup>型ダイオードに適用しても同様の効果があること言うまでもない。

30

## 【0220】

また、以上説明した実施の形態1～4および6における、n型カソード領域6およびn型バッファ層3は電極とのコンタクト抵抗が十分低くできるならばなくても良い。

## 【0221】

また、以上説明した実施の形態1～5における、p型半導体領域12は電極とのコンタクト抵抗が十分低くできるならばなくても良い。

## 【0231】

## 【発明の効果】

本発明に係る請求項1記載の電力用半導体装置によれば、第1および第2のゲート電極に相補的に信号を与えることで、IGBTとフリーホイールダイオードを内蔵した構成を得ることができ、また、IGBTとフリーホイールダイオードとは完全に独立して動作することになるので、フリーホイールダイオードの存在によりIGBTとして動作せず、MOSトランジスタとして動作するという問題は生じない。また、IGBTとして動作する場合に、第2ユニットの集合体側のキャリアライフトайムが短く設定された第1の半導体層の存在により、IGBT動作時にコレクタからのホールのインジェクションを抑制してスイッチングによるエネルギー損失を低減することができる。

40

## 【0232】

本発明に係る請求項2記載の電力用半導体装置によれば、キャリアのライフトайムが第1の半導体層よりも短く設定されたライフトайム設定領域の存在により、IGBT動作時

50

にコレクタからのホールのインジェクションを抑制してスイッチングによるエネルギー損失を低減することができる。また、ライフタイム設定領域を得るために簡便な構成を得ることができる。

【0235】

本発明に係る請求項3記載の電力用半導体装置によれば、IGBTとして動作する場合に、金属層あるいは第3の半導体層の存在によりオン電圧を低くすることができる。

【0239】

本発明に係る請求項4記載の電力用半導体装置の製造方法によれば、請求項2記載の電力用半導体装置を簡便に確実に得ることができる。

【図面の簡単な説明】

10

【図1】 本発明に係る電力用半導体装置の実施の形態1の構成を説明する図である。

【図2】 本発明に係る電力用半導体装置の実施の形態1の詳細な構成を説明する図である。

【図3】 本発明に係る電力用半導体装置の実施の形態1の外観構成を示す図である。

【図4】 本発明に係る電力用半導体装置の実施の形態1の外観構成を示す図である。

【図5】 本発明に係る電力用半導体装置の実施の形態1変形例の構成を説明する図である。

【図6】 本発明に係る電力用半導体装置の実施の形態2の構成を説明する図である。

【図7】 本発明に係る電力用半導体装置の実施の形態2の製造方法を説明する図である。

20

【図8】 本発明に係る電力用半導体装置の実施の形態2の製造方法を説明する図である。

【図9】 本発明に係る電力用半導体装置の実施の形態2の製造方法を説明する図である。

【図10】 本発明に係る電力用半導体装置の実施の形態3の構成を説明する図である。

【図11】 本発明に係る電力用半導体装置の実施の形態3の変形例の構成を説明する図である。

【図12】 本発明に係る電力用半導体装置の実施の形態3の変形例の構成を説明する図である。

【図13】 本発明に係る電力用半導体装置の実施の形態4の構成を説明する図である。

30

【図14】 本発明に係る電力用半導体装置の実施の形態5の構成を説明する図である。

【図15】 本発明に係る電力用半導体装置の実施の形態5の動作を説明する図である。

【図16】 本発明に係る電力用半導体装置の実施の形態5の動作を説明する図である。

【図17】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

【図18】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

【図19】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

【図20】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

40

【図21】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

【図22】 本発明に係る電力用半導体装置の実施の形態5の製造方法を説明する図である。

【図23】 本発明に係る電力用半導体装置の実施の形態5の変形例の構成を説明する図である。

【図24】 本発明に係る電力用半導体装置の実施の形態5の変形例の構成を説明する図である。

【図25】 本発明に係る電力用半導体装置の実施の形態5の変形例の構成を説明する図

50

である。

- 【図 2 6】 本発明に係る電力用半導体装置の実施の形態 6 の構成を説明する図である。

- 【図 2 7】 本発明に係る電力用半導体装置の実施の形態 6 の詳細な構成を説明する図である。

- 【図 2 8】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。

- 【図 2 9】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。

- 【図 3 0】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。 10

- 【図 3 1】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。

- 【図 3 2】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。

- 【図 3 3】 本発明に係る電力用半導体装置の実施の形態 6 の製造方法を説明する図である。

- 【図 3 4】 本発明に係る電力用半導体装置の実施の形態 6 の変形例の構成を説明する図である。

- 【図 3 5】 本発明に係る電力用半導体装置の実施の形態 6 の変形例の構成を説明する図である。 20

- 【図 3 6】 本発明に係る電力用半導体装置の実施の形態 6 の変形例の構成を説明する図である。

- 【図 3 7】 本発明に係る電力用半導体装置の実施の形態 6 の変形例の構成を説明する図である。

- 【図 3 8】 3 相インバータの構成を説明する図である。

- 【図 3 9】 従来の電力用半導体装置の構成を説明する図である。

- 【図 4 0】 電力用半導体装置の平面構成を説明する図である。

- 【図 4 1】 電力用半導体装置の平面構成を説明する図である。

- 【図 4 2】 従来の電力用半導体装置の動作を説明する図である。

- 【図 4 3】 従来の電力用半導体装置の動作を詳細に説明する図である。 30

【符号の説明】

1 n 型ベース層、 8 , 8 a , 8 b p 型ベース領域、 9 , 9 a , 9 b n 型エミッタ領域、 10 , 10 a , 10 b ゲート絶縁膜、 11 , 11 a , 11 b ゲート電極、 19 エミッタ電極、 19 a , 19 b ソース電極、 5 p コレクタ電極、 13 , 13 A 電流抑制用ダイオード、 13 B ~ 13 D ショットキーダイオード、 14 アノード領域、 15 カソード領域、 28 , 28 a , 28 b p 型半導体領域。

【図1】

【図2】

10: ゲート絶縁膜

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

13 A : 電流制御用ダイオード

14 : アノード領域

15 : カソード領域

16 : ジョード

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

### 【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/336 (2006.01) H 01 L 29/78 6 5 8 H

H 01 L 29/861 (2006.01) H 01 L 29/91 D

(56)参考文献 特開昭59-132666(JP,A)

特開平11-340246(JP,A)

特表2002-507058(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/04

H01L 21/336

H01L 29/47

H01L 29/739

H01L 29/78

H01L 29/861

H01L 29/872