(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5202877号

(P5202877)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/338 | (2006.01) | HO1L 29/80 | F    |

| HO1L 29/812 | (2006.01) | HO1L 21/28 | L    |

| HO1L 21/28  | (2006.01) | HO1L 21/28 | 301B |

| HO1L 21/329 | (2006.01) | HO1L 29/48 | P    |

| HO1L 29/47  | (2006.01) | HO1L 29/48 | D    |

請求項の数 3 (全 7 頁) 最終頁に続く

(21) 出願番号

特願2007-152496 (P2007-152496)

(22) 出願日

平成19年6月8日(2007.6.8)

(65) 公開番号

特開2008-306027 (P2008-306027A)

(43) 公開日

平成20年12月18日(2008.12.18)

審査請求日

平成22年4月26日(2010.4.26)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100087480

弁理士 片山 修平

(74) 復代理人 100137615

弁理士 横山 照夫

(74) 復代理人 100134511

弁理士 八田 俊之

(72) 発明者 西 真弘

山梨県中巨摩郡昭和町大字紙漉阿原100

○番地 ユーディナデバイス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

化合物半導体層の上に窒化シリコン膜である第1絶縁膜を形成する工程と、前記第1絶縁膜を550以上的温度で熱処理する工程と、前記第1絶縁膜上に窒化シリコン膜である第2絶縁膜を形成する工程と、前記第2絶縁膜及び前記第1絶縁膜を同一マスクを用い選択的にエッチングすることで、前記化合物半導体層が露出するとともに、前記第1絶縁膜における開口幅が前記第2絶縁膜における開口幅よりも小さい開口部を形成する工程と、前記開口部の内壁に接するゲート電極を形成する工程と、

を有し、

前記熱処理は、ソース電極及びドレイン電極をオーム化するための熱処理であることを特徴とする半導体装置の製造方法。

## 【請求項 2】

前記化合物半導体層はGaN系半導体層であることを特徴とする請求項1記載の半導体装置の製造方法。

## 【請求項 3】

前記エッチングは、ドライエッチングであることを特徴とする請求項1記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は半導体装置の製造方法に関し、特に、化合物半導体層上に電極を形成する工程を有する半導体装置の製造方法に関する。

## 【背景技術】

## 【0002】

化合物半導体層を用いた半導体装置、例えばHEMT(High Electron Mobility Transistor)等のFET(Field Effect Transistor)は、携帯電話基地局用増幅器などの高周波数かつ高出力で動作する高周波高出力増幅用素子として注目されている。

## 【0003】

10

特許文献1には、化合物半導体層としてGaN系半導体層上に窒化シリコン膜を形成し、該窒化シリコン膜の所定領域を除去し、GaN系半導体層上にゲート電極を形成するFETの製造方法が開示されている。

【特許文献1】特開2005-286135号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

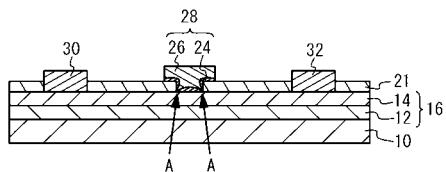

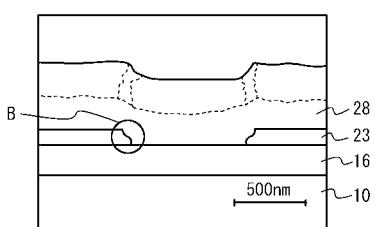

ここで、図1を参照して、特許文献1に示されるようなFETの製造方法について検討してみる。図1は、化合物半導体層を用いたFETの断面図である。サファイア基板10上に、GaN電子走行層12及びAlGaN電子供給層14からなる化合物半導体層16が形成されている。化合物半導体層16上に絶縁膜21が形成されている。絶縁膜21には開口が形成され。それぞれの開口を覆うように、ゲート電極28、ソース電極30及びドレイン電極32が化合物半導体層16上に形成されている。ゲート電極28はNi(ニッケル)等のショットキ層24とAu(金)等の導電層26とから構成される。

20

## 【0005】

図1に記載のFETにおいては、開口端Aの形状が急峻であるため、開口端Aにショットキ層24が成膜されにくく、ショットキ層24の被覆性が悪くなってしまう。このため、導電層26がショットキ層24の被覆性の悪い部分から化合物半導体層16に拡散する可能性がある。なお、絶縁膜21の開口をウエットエッチング等の等方性エッチングを用いて行うことにより、開口端でのショットキ層24の被覆性を向上させることが考えられる。しかし、ゲート電極28は短ゲート長とすること、ゲート長の制御性を向上させることが求められる。絶縁膜21を等方性エッチングしたのでは、短いゲート長あるいは制御性のよいゲート電極の形成が困難となる。

30

## 【0006】

本発明は、上記課題に鑑みなされたものであり、簡単な製造方法により、絶縁膜の開口に形成する電極の被覆性を向上させることを目的とする。

## 【課題を解決するための手段】

## 【0007】

本発明は、化合物半導体層の上に窒化シリコン膜である第1絶縁膜を形成する工程と、前記第1絶縁膜を550以上的温度で熱処理する工程と、前記第1絶縁膜上に窒化シリコン膜である第2絶縁膜を形成する工程と、前記第2絶縁膜及び前記第1絶縁膜を同一マスクを用い選択的にエッチングすることで、前記化合物半導体層が露出するとともに、前記第1絶縁膜における開口幅が前記第2絶縁膜における開口幅よりも小さい開口部を形成する工程と、前記開口部の内壁に接するゲート電極を形成する工程と、を有し、前記熱処理は、ソース電極及びドレイン電極をオーミック化するための熱処理であることを特徴とする半導体装置の製造方法である。本発明によれば、第1絶縁膜及び第2絶縁膜の開口端に段差が形成される。これにより、絶縁膜の開口端における電極の被覆性を向上させることができる。

40

## 【0009】

上記構成において、前記熱処理は、ソース電極及びドレイン電極をオーミック化するた

50

めの熱処理である構成とすることができる。この構成によれば、製造工程を簡略化することができる。

#### 【0010】

上記構成において、前記化合物半導体層はGaN系半導体層である構成とすることができる。

#### 【0011】

上記構成において、前記エッチングは、ドライエッチングである構成とすることができる。

#### 【発明の効果】

#### 【0012】

本発明によれば、第1絶縁膜及び第2絶縁膜の開口端に段差が形成される。これにより、絶縁膜の開口端における電極の被覆性を向上させることができる。

10

#### 【発明を実施するための最良の形態】

#### 【0013】

本発明は、絶縁膜を熱処理するとドライエッチングのレートが低下することを利用している。以下、図面を参照に、本発明の実施例について説明する。

#### 【実施例1】

#### 【0014】

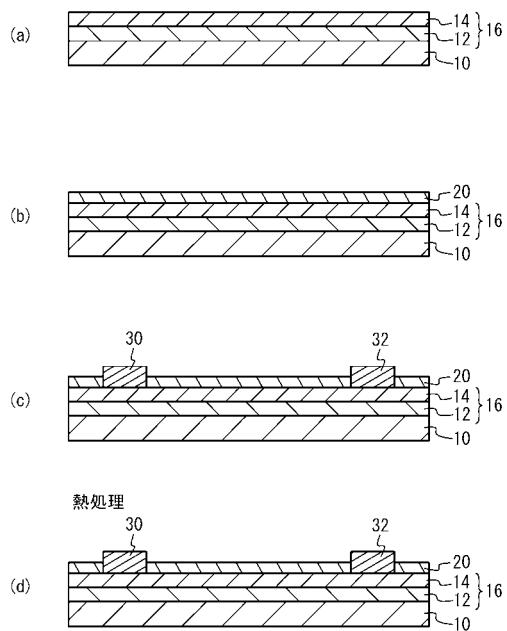

図2(a)から図4を用い、実施例1に係るFETの製造方法を説明する。図2(a)のように、サファイア基板10上にGaN電子走行層12及びAlGaN電子供給層14をMOCVD(Metal Organic Chemical Vapor Deposition)法を用い成長する。これにより、GaN電子走行層12及びAlGaN電子供給層14からなる化合物半導体層16が形成される。

20

#### 【0015】

図2(b)のように、化合物半導体層16上にプラズマCVD法を用い、窒化シリコン膜からなる第1絶縁膜20を形成する。ここで、プラズマCVD法による成膜条件は、温度が300℃、圧力が0.9 torr、モノシランガス流量が4sccm、窒素ガス流量が200sccm、アンモニアガス流量が0.5sccm、ヘリウムガス流量が900scm、RF(高周波)パワーが50Wとすることができる。第1絶縁膜20の膜厚は約30nmである。図2(c)のように、第1絶縁膜20のオーミック電極を形成すべき領域を除去し、化合物半導体層16上に形成された第1絶縁膜20の開口にオーミック電極としてソース電極30及びドレイン電極32を蒸着法及びリフトオフ法を用い形成する。ソース電極30及びドレイン電極32は下から膜厚が5nmから15nmのTa(タンタル)、膜厚が200から400nmのAl(アルミニウム)からなる。図2(d)のように、550℃で熱処理を行う。これにより、ソース電極30及びドレイン電極32が化合物半導体層16と合金化され、ソース電極30及びドレイン電極32と化合物半導体層16との間がオーミック接触される。

30

#### 【0016】

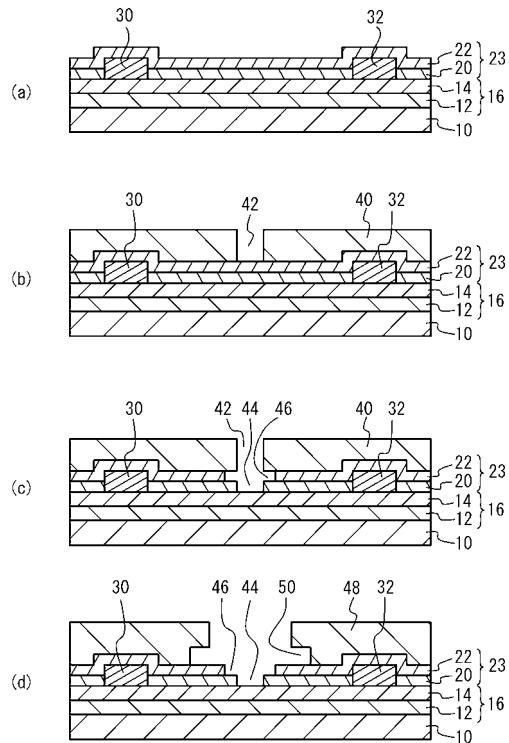

図3(a)のように、第1絶縁膜20、ソース電極30及びドレイン電極32上にプラズマCVD法を用い、窒化シリコン膜からなる第2絶縁膜22を形成する。第2絶縁膜22の膜厚は約30nmである。これにより、第1絶縁膜20と第2絶縁膜22とから絶縁膜23が形成される。図3(b)のように、第2絶縁膜22上にフォトレジスト40を塗布し、露光現像を行うことにより、フォトレジスト40のゲート電極を形成すべき領域に開口部42を形成する。

40

#### 【0017】

図3(c)のように、第2絶縁膜22及び第1絶縁膜20を同一マスク(フォトレジスト40)を用い選択的にエッチングし化合物半導体層16が露出する開口部44を形成する。エッチングは、例えばSF<sub>6</sub>及びCHF<sub>3</sub>を用いたドライエッチングで行う。このとき、第1絶縁膜20は熱処理によりエッチングレートが低下する。一方、第2絶縁膜22は熱処理を経ていないため、エッチングレートは低下していない。そこで、第1絶縁膜2

50

0を異方性エッティングし開口部44を形成した際、第2絶縁膜22はオーバエッティング状態となり、第2絶縁膜22にサイドエッティング領域46が形成される。

#### 【0018】

図3(d)のように、フォトレジスト40を除去する。第2絶縁膜22上に感光性の異なる2層のフォトレジスト層を塗布し、露光現像する。これにより、フォトレジスト48にオーバーハング形状の開口部50を形成する。

#### 【0019】

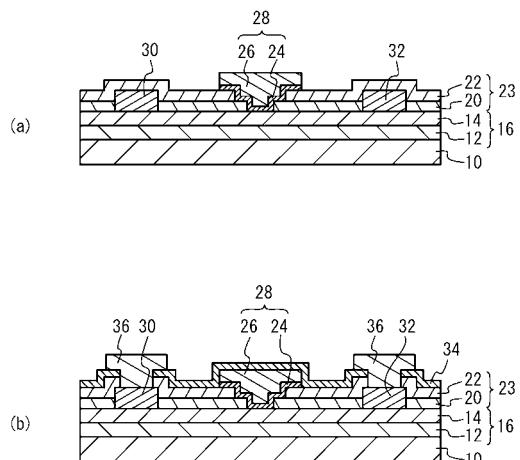

図4(a)のように、絶縁膜23の開口部44、46の内壁及び化合物半導体層16に接するようにゲート電極28を蒸着法及びリフトオフ法を用い形成する。ゲート電極28は下から、膜厚が60nmのNi(ニッケル)からなるショットキ層24と、膜厚が300nmのAu(金)からなる導電層26と、から構成される。図4(b)のように、ソース電極30、ドレイン電極32、ゲート電極28及び第2絶縁膜22上に保護膜34として窒化シリコン膜を形成する。ソース電極30及びドレイン電極32にそれぞれ接続されるAuからなる配線36を形成する。以上により、実施例1に係るFETが完成する。

#### 【0020】

実施例1によれば、熱処理工程を経た第1絶縁膜20と熱処理工程を経ていない第2絶縁膜22をエッティングすることにより、図3(c)のように、開口部に段差を設けることができる。図5は、実施例1の図2(a)から図3(c)と同じ工程を行い、フォトレジスト40を除去後、ゲート電極28と同じ金属を形成した後の断面SEM画像を模式化した図である。図5のBのように、絶縁膜23の開口端Bは、上部の開口が下部の開口より大きくなるような段差を有している。これにより、絶縁膜23の開口端Bにおけるゲート電極28中のショットキ層24の被覆性が向上する。よって、導電層26が化合物半導体層16に拡散することを抑制することができる。

#### 【0021】

実施例1においては、電極としてゲート電極28を例に説明したが、その他の電極でもよい。半導体装置としてFETを例に説明したが他の半導体装置でもよい。しかしながら、化合物半導体層16に接する電極はゲート電極28であることが好ましい。ゲート電極28は短ゲート長化及びゲート長制御性の向上が求められている。よって、本発明を適用することが有効である。特に、図3(c)のエッティングとしてドライエッティングを用いることにより、第1絶縁膜20が異方性エッティングされるため、ゲート電極の短ゲート長化及びゲート長制御性の向上を図ることができる。

#### 【0022】

図2(d)のように、熱処理工程は、ソース電極30及びドレイン電極32をオーミック化するための熱処理であることが好ましい。これにより、製造工程を簡略化することができる。なお、実施例1のようにGaN系半導体層16とオーミック電極とのオーミック化のための熱処理は、比較的高温(例えば550以上)で実施されている。これは、第1絶縁膜20と第2絶縁膜22とのエッティングレート差を実用的に得ることのできる温度であり、絶縁膜23に開口部の段差を設けることによりショットキ層24の被覆性を向上させるという目的によく合致する。

#### 【0023】

化合物半導体層16としてGaN系半導体層を例に説明したが、化合物半導体層はGaAs等の化合物半導体層であってもよい。しかしながら、GaN系半導体層の場合、図2(d)のオーミック電極の合金化のための熱処理を比較的高温で行う。化合物半導体層16はGaN系半導体層であることが好ましい。なお、GaN系半導体としては、例えば、窒化ガリウム(GaN)並びにGaNと窒化アルミニウム(AlN)または窒化インジウム(InN)との混晶であるAlGaNまたはInGaN等の半導体を用いることができる。

#### 【0024】

熱処理温度として550、第1絶縁膜20及び第2絶縁膜22として窒化シリコン膜、エッティングのエッチャントとしてSF<sub>6</sub>及びCHF<sub>3</sub>を例に説明した。熱処理により工

10

20

30

40

50

ツチングレートが遅くなる熱処理温度、材料、エッチャントを適宜選択することができる。

【0025】

以上、発明の好ましい実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

【0026】

【図1】図1は従来例に係るFETの製造方法を示す断面図である。

【図2】図2(a)から図2(d)は実施例1に係るFETの製造方法を示す断面図(その1)である。 10

【図3】図3(a)から図3(d)は実施例1に係るFETの製造方法を示す断面図(その2)である。

【図4】図4(a)及び図4(b)は実施例1に係るFETの製造方法を示す断面図(その3)である。

【図5】図5は断面SEM画像の模式図である。

【符号の説明】

【0027】

|     |            |    |

|-----|------------|----|

| 1 0 | サファイア基板    |    |

| 1 2 | GaN電子走行層   | 20 |

| 1 4 | AlGaN電子供給層 |    |

| 1 6 | 化合物半導体層    |    |

| 2 0 | 第1絶縁膜      |    |

| 2 2 | 第2絶縁膜      |    |

| 2 8 | ゲート電極      |    |

| 3 0 | ソース電極      |    |

| 3 2 | ドレイン電極     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/872 (2006.01)

(72)発明者 生松 均

山梨県中巨摩郡昭和町大字紙漉阿原1000番地 ユーディナデバイス株式会社内

(72)発明者 駒谷 務

山梨県中巨摩郡昭和町大字紙漉阿原1000番地 ユーディナデバイス株式会社内

審査官 李 哲次

(56)参考文献 特開平08-191147 (JP, A)

特開2004-063492 (JP, A)

特開平11-162995 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/338

H 01 L 21/28

H 01 L 21/329

H 01 L 29/47

H 01 L 29/812

H 01 L 29/872