(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7114694号**

**(P7114694)**

(45)発行日 令和4年8月8日(2022.8.8)

(24)登録日 令和4年7月29日(2022.7.29)

(51)国際特許分類

|         |                |     |         |       |       |

|---------|----------------|-----|---------|-------|-------|

| G 0 6 N | 3/08 (2006.01) | F I | G 0 6 N | 3/08  | 1 8 0 |

| G 0 6 N | 3/063(2006.01) |     | G 0 6 N | 3/063 |       |

請求項の数 12 (全28頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2020-511472(P2020-511472) |

| (86)(22)出願日       | 平成30年9月7日(2018.9.7)         |

| (65)公表番号          | 特表2020-533668(P2020-533668) |

| A)                |                             |

| (43)公表日           | 令和2年11月19日(2020.11.19)      |

| (86)国際出願番号        | PCT/IB2018/000994           |

| (87)国際公開番号        | WO2019/048922               |

| (87)国際公開日         | 平成31年3月14日(2019.3.14)       |

| 審査請求日             | 令和3年9月7日(2021.9.7)          |

| (31)優先権主張番号       | 62/556,312                  |

| (32)優先日           | 平成29年9月8日(2017.9.8)         |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

| (31)優先権主張番号       | 16/124,104                  |

| (32)優先日           | 平成30年9月6日(2018.9.6)         |

| 最終頁に続く            |                             |

|          |                                                                                         |

|----------|-----------------------------------------------------------------------------------------|

| (73)特許権者 | 517202814<br>セス, ロヒット<br>カナダ国, オンタリオ州 エルフジー 0<br>エヌ 7 , テラ コタ , サイドロード 2 7<br>1 6 2 8 2 |

| (74)代理人  | 100079108<br>弁理士 稲葉 良幸                                                                  |

| (74)代理人  | 100109346<br>弁理士 大貫 敏史                                                                  |

| (74)代理人  | 100117189<br>弁理士 江口 昭彦                                                                  |

| (74)代理人  | 100134120<br>弁理士 内藤 和彦                                                                  |

| (72)発明者  | セス, ロヒット<br>カナダ国, オンタリオ州 エルフジー 0<br>最終頁に続く                                              |

(54)【発明の名称】 人工知能向けのパラレルニューラルプロセッサ

**(57)【特許請求の範囲】****【請求項 1】**

入力信号(402)を処理するように構成された第1の下位分類器であって、加重入力モジュール(440, 442, 444)であって、前記加重入力モジュール(440, 442, 444)は、コントロールグループ信号(502)を受信し、前記入力信号に重みを適用して、前記コントロールグループ信号(502)に基づいて、加重入力信号を生成するように構成されている、加重入力モジュール(440, 442, 444)と、前記加重入力モジュール(440, 442, 444)に結合された比較モジュールであって、前記比較モジュールは、比較モジュールの入力ラインにおける前記加重入力信号を受信し、比較モジュールの出力ラインにおける第1の出力信号を生成するように構成されており、前記比較モジュールは、前記加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを判定し、前記加重入力信号が前記下のウィンドウ範囲値と前記上のウィンドウ範囲値との間の値を有すると判定することに応答して、前記比較モジュールの出力ラインにおいて第1の値を有するように前記第1の出力信号を設定し、前記加重入力信号が前記下のウィンドウ範囲値と前記上のウィンドウ範囲値との間でない値を有すると判定することに応答して、前記比較モジュールの出力ラインにおいて前記第1の値と異なる第2の値を有するように前記第1の出力信号を設定するように更に構成されている、比較モジュールと、

を含み、

前記コントロールグループ信号(502)は、前記第1の下位分類器を含む複数の下位分

類器の比較モジュールの前記入力信号に対する応答性を制御する、第1の下位分類器。

**【請求項 2】**

前記比較モジュールが、前記加重入力信号を受信し前記第1の出力信号を設定するように構成された少なくとも1つの演算増幅器を含む、請求項1に記載の第1の下位分類器。

**【請求項 3】**

前記加重入力信号を生成するために前記入力信号に適用される前記重み(404)は、第2の下位分類器からの第2の出力信号に基づく、請求項1又は2に記載の第1の下位分類器。

**【請求項 4】**

前記第1の下位分類器からの前記第1の出力信号は、第2の下位分類器に伝送される、請求項1乃至3のうち何れか一項に記載の第1の下位分類器。

10

**【請求項 5】**

前記加重入力モジュール(440, 442, 444)は、前記コントロールグループ信号(502)を受信し、前記コントロールグループ信号(502)に基づいて前記加重入力信号を調節するように、又は比較モジュールの刺激感度に影響を及ぼすように構成された可変抵抗器又は可変電流若しくは電圧調整器を含む、請求項1乃至4のうち何れか一項に記載の第1の下位分類器。

**【請求項 6】**

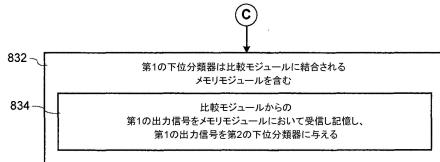

前記比較モジュールからの前記第1の出力信号を受信及び記憶し、前記第1の出力信号を第2の下位分類器に出力するように構成されたメモリモジュール(410, 412, 420)を更に含む、請求項1乃至5のうち何れか一項に記載の第1の下位分類器。

20

**【請求項 7】**

前記コントロールグループ信号は、前記比較モジュールに継続的に及び/又は断続的に動作中に適用される、請求項1乃至6のうち何れか一項に記載の第1の下位分類器。

**【請求項 8】**

第1の下位分類器を使用して入力信号を処理するための方法であって、前記第1の下位分類器は、加重入力モジュール(440, 442, 444)及び前記加重入力モジュール(440, 442, 444)に結合された比較モジュールを含み、前記方法は、前記加重入力モジュール(440, 442, 444)においてコントロールグループ信号(502)を受信すること、

30

前記加重入力モジュール(440, 442, 444)において前記入力信号に重みを適用して、前記コントロールグループ信号(502)に基づいて、加重入力信号を生成すること、

比較モジュールの入力ラインにおける前記加重入力信号を前記比較モジュールにおいて受信すること、及び

比較モジュールの出力ラインにおける第1の出力信号を前記比較モジュールにおいて生成することであって、前記加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを前記比較モジュールにおいて判定することと、前記加重入力信号が前記下のウィンドウ範囲値と前記上のウィンドウ範囲値との間の値を有すると判定することに応答して、前記比較モジュールの出力ラインにおいて第1の値を有するよう前に記第1の出力信号を前記比較モジュールにおいて設定することと、前記加重入力信号が前記下のウィンドウ範囲値と前記上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、前記比較モジュールの出力ラインにおいて前記第1の値と異なる第2の値を有するよう前に記第1の出力信号を前記比較モジュールにおいて設定することとを含む、こと、

40

を含み、

前記コントロールグループ信号(502)は、前記第1の下位分類器を含む複数の下位分類器の比較モジュールの前記入力信号に対する応答性を制御する、方法。

**【請求項 9】**

前記比較モジュールは、少なくとも1つの演算増幅器モジュールを含み、

50

前記方法は、前記少なくとも 1 つの演算増幅器モジュールにおいて前記加重入力信号を受信し、前記少なくとも 1 つの演算増幅器モジュールにおいて前記第 1 の出力信号を設定することを更に含む、請求項 8 に記載の方法。

**【請求項 10】**

第 2 の下位分類器からの第 2 の出力信号を前記加重入力モジュール (440, 442, 444) において受信すること、及び / 又は

前記第 1 の下位分類器から第 2 の下位分類器に前記第 1 の出力信号を伝送すること、

を更に含む、請求項 8 又は 9 に記載の方法。

**【請求項 11】**

前記加重入力モジュール (440, 442, 444) は、可変抵抗モジュールを含み、

前記方法は、前記可変抵抗モジュールにおいて前記コントロールグループ信号 (502)

を受信し、前記コントロールグループ信号 (502) に基づいて前記加重入力信号を調節

することを含み、及び / 又は

前記第 1 の下位分類器は、前記比較モジュールに結合されるメモリモジュールを含み、

前記方法は、前記メモリモジュールにおいて前記比較モジュールからの前記第 1 の出力信

号を受信及び記憶し、前記第 1 の出力信号を第 2 の下位分類器に出力することを含む、請

求項 8 乃至 10 のうち何れか一項に記載の方法。

**【請求項 12】**

前記コントロールグループ信号は、前記比較モジュールに継続的に及び / 又は断続的に動

作中に適用される、請求項 8 乃至 11 のうち何れか一項に記載の方法。

10

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**技術分野**

[0002] 開示する実装形態は一般に人工知能に関し、より詳細には人工知能向けのパラ

レルニューラルプロセッサを実装するための方法、システム、及び装置に関する。

**【背景技術】**

**【0002】**

**背景**

[0003] 人工知能 (AI) 応用は、ソフトウェア駆動型システム向けに及びソフトウェ

ア駆動型システムとして従来から設計してきた。かかるシステムでは、(AIの「脳」

内の「ニューロン」として働く) 処理要素がハードウェアメモリ内の固定状態を占有する

ようにプログラムされる。それらのニューロンは、人工ニューラルネットワークを形成す

るよう结合変数の代表値によって相互接続される。それらのニューロンの状態は、重み

、バイアス、及び入力データを処理してバイナリ出力値 (即ち 0 か 1) を生成する活性化

関数を使用して反復的に評価される。その結果生じるニューロンの状態はニューロンの出

力状態としてメモリ内に記憶され、その後、人工ニューラルネットワーク内の接続された

ニューロンのための入力として使用される。高いレベルにおいて、幾つかのニューロンの

入力及び出力の状態が反復的に評価される。一部のシステムはニューロンの幾つかのブロ

ックを同時に評価するためにマルチスレッディング及びマルチコアプロセッサを使用する

が、システムは全体として性質上「シリアル」のままである。大規模なニューラルネット

ワークは、小規模なネットワークよりも複雑且つ多岐にわたる問題を解決する能力がある

。しかし、大規模なニューラルネットワークは、より多くのコア数及び / 又はより多くの

スレッド数を有するマイクロプロセッサを必要とする。従って AI 応用は、そうした従来

のプロセッサの速度によって制限される。

30

40

**【0003】**

[0004] 従来のハードウェアの制限を補償するために、AI システムは様々なショート

カット及び境界条件を用いて巧みに設計されており、特定の問題集合に合わせて調整され

ている。境界条件は予め定められるので、それらのシステムは極めて特定的な応用に限定

される。例えば、人間の顔を認識するように訓練される AI システムは麒麟の顔を認識す

50

るには効果的ではない可能性がある。

**【0004】**

[0005] 従来のシステムは大きいオーバヘッドを生じさせ、コスト効率の良いやり方で複雑な問題集合に迅速に応答できず、人工意識を実現できるようになるには程遠い。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

**概要**

[0006] 従って、パラレルAI処理向けに特別に設計された人工ニューラルネットワークを実装するためのより効率的且つ直感的な方法を有するシステム及び/又は装置が求められている。一部の実装形態では、開示するシステム、装置、及び方法が、(a)より複雑な問題集合を処理するのに必要なニューラル処理時間を大幅に短縮し、(b)自己学習に必要な神経可塑性を実装し、(c)直感の要素を吹き込むのに必要なexplicitメモリに加えてimplicitメモリの概念及び応用を導入するパラレルニューラル処理に関して、従来のシステム、装置、及び方法を補完し又は置換する。これらの特性を用いて、開示する発明の一部の実装形態は人間の意識又は認識をエミュレートできるようになる。

10

**【課題を解決するための手段】**

**【0006】**

[0007] (A1) 一態様では、一部の実装形態が入力信号を処理するように構成された第1の下位分類器を含む。第1の下位分類器は、入力信号に重みを適用して加重入力信号を生成するように構成された加重入力モジュールを含む。第1の下位分類器は、加重入力モジュールに結合された比較モジュールも含む。比較モジュールは、比較モジュールの出力ラインにおける加重入力信号を受信し、比較モジュールの出力ラインにおける第1の出力信号を生成するように構成されている。比較モジュールは、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを判定するように更に構成されている。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、比較モジュールは、比較モジュールの出力ラインにおいて第1の値を有するように第1の出力信号を設定するように構成されている。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、比較モジュールは、比較モジュールの出力ラインにおいて第1の値と異なる第2の値を有するように第1の出力信号を設定するように構成されている。

20

**【0007】**

[0008] (A2) A1の第1の下位分類器の一部の実装形態では、比較モジュールが、加重入力信号を受信し第1の出力信号を設定するように構成された少なくとも1つの演算增幅器を含む。

30

**【0008】**

[0009] (A3) A1の第1の下位分類器の一部の実装形態では、加重入力信号を生成するために入力信号に適用される重みが第2の下位分類器からの第2の出力信号に基づく。

**【0009】**

[0010] (A4) A1の第1の下位分類器の一部の実装形態では、第1の下位分類器からの第1の出力信号が第2の下位分類器に伝送される。

40

**【0010】**

[0011] (A5) A4の第1の下位分類器の一部の実装形態では、加重入力モジュールがコントロールグループ信号を受信し、コントロールグループ信号に基づいて加重入力信号を生成するために入力信号に重みを適用するように構成されている。

**【0011】**

[0012] (A6) A5の第1の下位分類器の一部の実装形態では、加重入力モジュールがコントロールグループ信号を受信し、コントロールグループ信号に基づいて加重入力信号を調節するように構成された可変抵抗器を含む。

**【0012】**

50

[0013] (A7) A1の第1の下位分類器の一部の実装形態では、第1の下位分類器が、比較モジュールからの第1の出力信号を受信し記憶し、第1の出力信号を第2の下位分類器に与えるように構成されたメモリモジュールを更に含む。

#### 【0013】

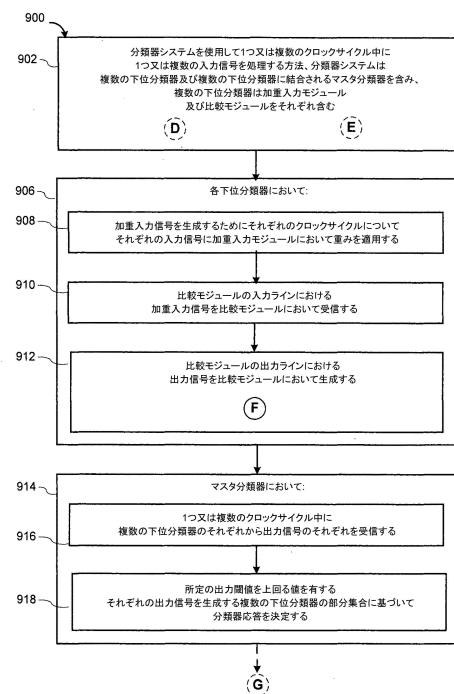

[0014] (A8) 別の態様では、一部の実装形態が、1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理するように構成された分類器システムを含む。分類器システムは複数の下位分類器を含む。複数の下位分類器のそれぞれは、加重入力信号を生成するためにそれぞれのクロックサイクルについてそれぞれの入力信号に重みを適用するように構成された加重入力モジュールを含む。複数の下位分類器のそれぞれは、加重入力モジュールに結合された比較モジュールも含む。比較モジュールは、比較モジュールの入力ラインにおける加重入力信号を受信し、比較モジュールの出力ラインにおける出力信号を生成するように構成されている。比較モジュールは、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを判定するように更に構成されている。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、比較モジュールは、比較モジュールの出力ラインにおいて所定の出力閾値を上回る値を有するように第1の出力信号を設定するように更に構成されている。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、比較モジュールは、比較モジュールの出力ラインにおいて所定の出力閾値を下回る値を有するように第1の出力信号を設定するように更に構成されている。分類器システムは、複数の下位分類器に結合されたマスタ分類器も含む。マスタ分類器は、1つ又は複数のクロックサイクル中に複数の下位分類器のそれぞれから個々の出力信号のそれぞれを受信し、所定の出力閾値を上回る値を有するそれぞれの出力信号を生成する複数の下位分類器の部分集合に基づいて分類器応答を決定するように構成されている。

#### 【0014】

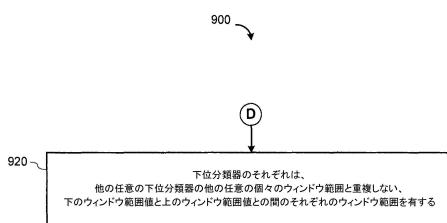

[0015] (A9) (A8) の分類器システムの一部の実装形態では、下位分類器のそれぞれが、他の任意の下位分類器の他の任意の個々のウィンドウ範囲と重複しない、下のウィンドウ範囲値と上のウィンドウ範囲値との間のそれぞれのウィンドウ範囲を有する。

#### 【0015】

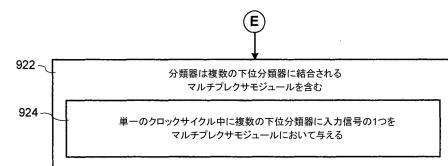

[0016] (A10) (A8) の分類器システムの一部の実装形態では、分類器システムが複数の下位分類器に結合されたマルチプレクサを更に含み、マルチプレクサは单一のクロックサイクル中に複数の下位分類器に入力信号の1つを与えるように構成されている。

#### 【0016】

[0017] (A11) 別の態様では、一部の実装形態が、第1の下位分類器を使用して入力信号を処理するための方法を含む。第1の下位分類器は、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む。この方法は、加重入力モジュールにおいて入力信号に重みを適用して加重入力信号を生成することを含む。この方法は、比較モジュールの入力ラインにおける加重入力信号を比較モジュールにおいて受信することを更に含む。この方法は、比較モジュールの出力ラインにおける第1の出力信号を電気的プロセスによって比較モジュールにおいて生成することを更に含む。電気的プロセスは、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを比較モジュールにおいて判定することを含む一連のステップとしてナショナライズ (nationalize) することができる。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、一連のステップは、比較モジュールの出力ラインにおいて第1の値を有するように第1の出力信号を比較モジュールにおいて設定することを更に含む。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、一連のステップは、比較モジュールの出力ラインにおいて第1の値と異なる第2の値を有するように第1の出力信号を比較モジュールにおいて設定することを更に含む。

#### 【0017】

10

20

30

40

50

[0018] (A12)(A11)の方法の一部の実装形態では、比較モジュールが少なくとも1つの演算増幅器モジュールを含み、この方法が、少なくとも1つの演算増幅器モジュールにおいて加重入力信号を受信し、少なくとも1つの演算増幅器モジュールにおいて第1の出力信号を設定することを更に含む。

#### 【0018】

[0019] (A13)(A11)の方法の一部の実装形態では、この方法が、第2の下位分類器からの第2の出力信号を加重入力モジュールにおいて受信することを更に含む。

#### 【0019】

[0020] (A14)(A11)の方法の一部の実装形態では、この方法が、第1の下位分類器から第2の下位分類器に第1の出力信号を伝送することを更に含む。

#### 【0020】

[0021] (A15)(A14)の方法の一部の実装形態では、この方法が、加重入力モジュールにおいてコントロールグループ信号を受信すること、及び加重入力モジュールにおいて、コントロールグループ信号に基づいて加重入力信号を生成するために入力信号に重みを適用することを更に含む。

#### 【0021】

[0022] (A16)(A15)の方法の一部の実装形態では、加重入力モジュールが電流フロー又は電圧コントローラ(可変抵抗器モジュール、抵抗ラダー、抵抗回路網、又は電流フローを制御するための回路)を含み、この方法が、可変抵抗器モジュールにおいてコントロールグループ信号を受信し、コントロールグループ信号に基づいて加重入力信号を調節することを更に含む。

#### 【0022】

[0023] (A17)(A13)の方法の一部の実装形態では、第1の下位分類器が比較モジュールに結合されたメモリモジュールを含み、この方法が、メモリモジュールにおいて比較モジュールからの第1の出力信号を受信し記憶し、第1の出力信号を第2の下位分類器に与えることを更に含む。

#### 【0023】

[0024] (A18)更に別の態様では、一部の実装形態は、分類器システムを使用して1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理するための方法を含む。分類器システムは、複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。この方法は、各下位分類器において、加重入力信号を生成するためにそれぞれのクロックサイクルについてそれぞれの入力信号に加重入力モジュールにおいて重みを適用すること、比較モジュールの入力ラインにおける加重入力信号を比較モジュールにおいて受信すること、及び比較モジュールの出力ラインにおける出力信号を電気的プロセスによって比較モジュールにおいて生成することを含む。このプロセスは、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを比較モジュールにおいて判定することを含む一連のステップとしてナショナライズすることができる。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、一連のステップは、比較モジュールの出力ラインにおいて所定の出力閾値を上回る値を有するように出力信号を比較モジュールにおいて設定することを更に含む。加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、一連のステップは、比較モジュールの出力ラインにおいて所定の出力閾値を下回る値を有するように出力信号を比較モジュールにおいて設定することを更に含む。この方法はマスタ分類器において、1つ又は複数のクロックサイクル中に複数の下位分類器のそれから出力信号のそれそれを受信すること、及び所定の出力閾値を上回る値を有するそれぞれの出力信号を生成する複数の下位分類器の部分集合に基づいて分類器応答を決定することを更に含む。

#### 【0024】

[0025] (A19)(A18)の方法の一部の実装形態では、下位分類器のそれぞれが

10

20

30

40

50

、他の任意の下位分類器の他の任意の個々のウィンドウ範囲と重複しない、下のウィンドウ範囲値と上のウィンドウ範囲値との間のそれぞれのウィンドウ範囲を有する。

**【0025】**

[0026] (A20) (A18) の方法の一部の実装形態では、分類器システムが複数の下位分類器に結合されたマルチプレクサモジュールを含み、この方法は、マルチプレクサモジュールにおいて単一のクロックサイクル中に複数の下位分類器に入力信号の1つを与えることを更に含む。

**【0026】**

**図面の簡単な説明**

[0027] 記載する様々な実装形態をより良く理解するために下記の図面に関連して以下の実装形態の説明を参照すべきであり、下記の図面では図面の全体を通して同様の参照番号が対応する部分を指す。 10

**【図面の簡単な説明】**

**【0027】**

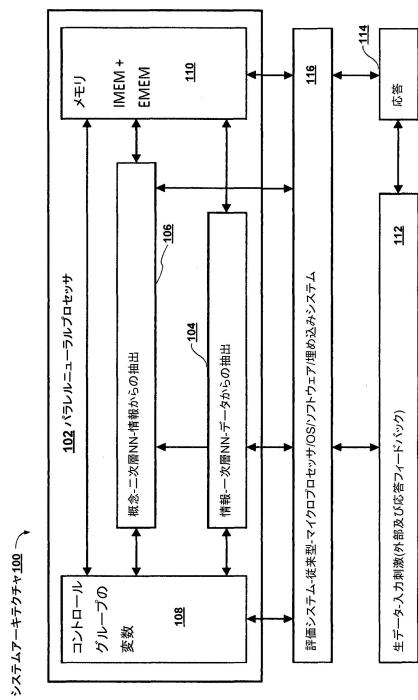

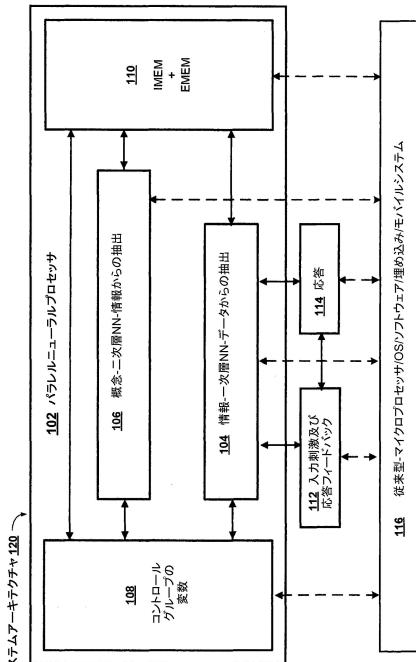

【図1A】[0028]一部の実装形態による、パラレルニューラル処理(PNP)AIプロセッサを有するシステムアーキテクチャの一例を示すブロック図である。

【図1B】[0028]一部の実装形態による、パラレルニューラル処理(PNP)AIプロセッサを有するシステムアーキテクチャの一例を示すブロック図である。

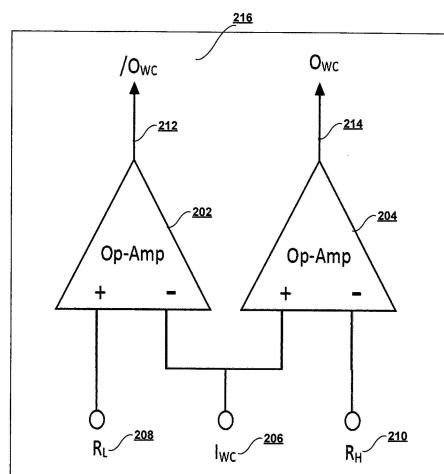

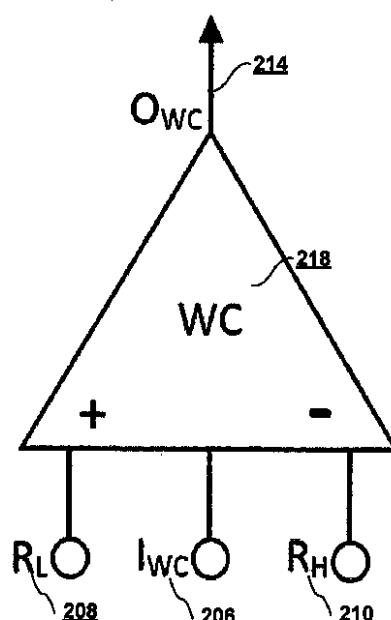

【図2A】[0029]一部の実装形態による、PNP AIプロセッサのコンポーネントであるアナログウィンドウコンパレータを示す。 20

【図2B】[0029]一部の実装形態による、非反転ウィンドウコンパレータを示す。

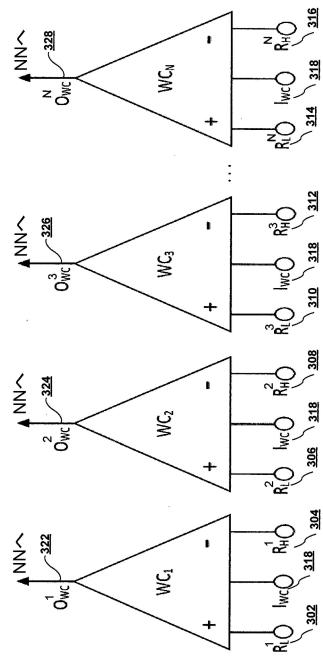

【図3】[0030]一部の実装形態による、ニューラルネットワーク内の一連のウィンドウコンパレータ回路を示す。

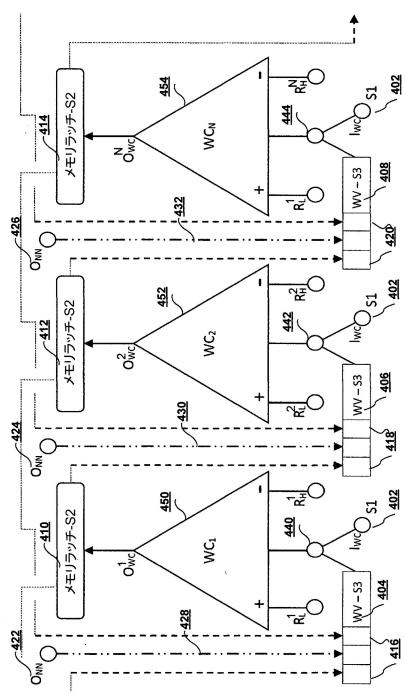

【図4】[0031]一部の実装形態による、データフロー制御段階を有する相互接続されたニューラルネットワーク内の一連のウィンドウコンパレータを示す。

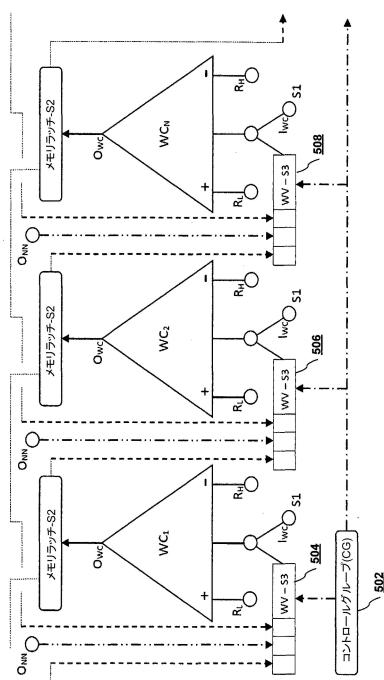

【図5】[0032]一部の実装形態による、ニューラルネットワークの神経可塑性及び拳動を制御するためのコントロールグループ(CG:control group)が追加された図4の一連のウィンドウコンパレータを示す。

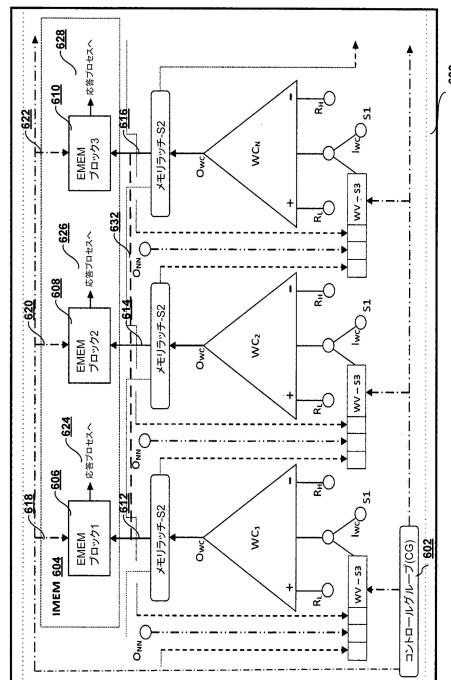

【図6】[0033]一部の実装形態による、CG及びニューラルネットワークによってアドレス指定可能なimplicitメモリブロックが追加された図5の一連のウィンドウコンパレータを示す。 30

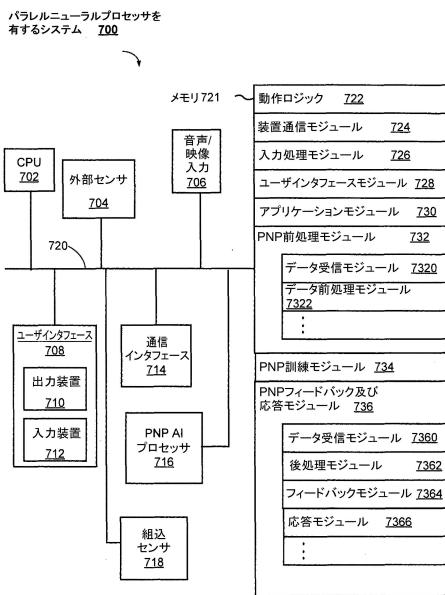

【図7】[0034]一部の実装形態による、図1A又は図1Bのパラレルニューラルプロセッサを有する代表的なシステム700を示すブロック図である。

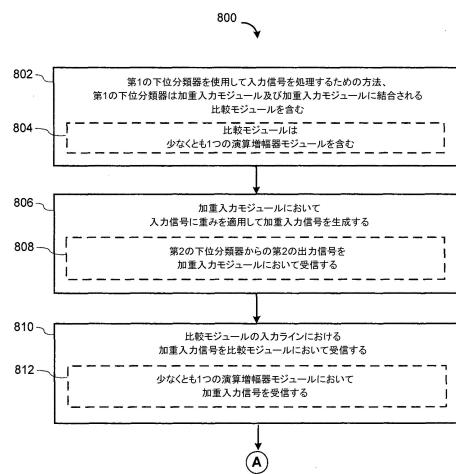

【図8A】[0035]一部の実装形態による、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む下位分類器を使用して入力信号を処理する方法の流れ図の表現を示す。

【図8B】[0035]一部の実装形態による、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む下位分類器を使用して入力信号を処理する方法の流れ図の表現を示す。

【図8C】[0035]一部の実装形態による、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む下位分類器を使用して入力信号を処理する方法の流れ図の表現を示す。 40

【図8D】[0035]一部の実装形態による、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む下位分類器を使用して入力信号を処理する方法の流れ図の表現を示す。

【図9A】[0036]一部の実装形態による、分類器を使用して1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理する方法の流れ図の表現を示し、分類器は複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。

【図9B】[0036]一部の実装形態による、分類器を使用して1つ又は複数のクロックサイ 50

クル中に1つ又は複数の入力信号を処理する方法の流れ図の表現を示し、分類器は複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。

【図9C】[0036]一部の実装形態による、分類器を使用して1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理する方法の流れ図の表現を示し、分類器は複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。

【図9D】[0036]一部の実装形態による、分類器を使用して1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理する方法の流れ図の表現を示し、分類器は複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。 10

【図9E】[0036]一部の実装形態による、分類器を使用して1つ又は複数のクロックサイクル中に1つ又は複数の入力信号を処理する方法の流れ図の表現を示し、分類器は複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。

#### 【発明を実施するための形態】

##### 【0028】

###### 実装形態の説明

[0037] 次に、添付図面にその例を示す実装形態を詳細に参照する。以下の詳細な説明では、説明する様々な実装形態の完全な理解を与えるために数多くの具体的な詳細を記載する。但し、記載する様々な実装形態はそれらの具体的な詳細なしに実践できることが当業者には明らかである。他の例では、実装形態の側面を無駄に不明瞭にしないために、よく知られている方法、手続き、コンポーネント、回路、及びネットワークについて詳しく説明していない。 20

##### 【0029】

[0038] 様々な要素を説明するために第1の、第2の等の用語を本明細書で場合によつては使用するが、これらの要素はこれらの用語によって限定されるべきではないことも理解されよう。これらの用語は、或る要素を別の要素と区別するために使用するに過ぎない。記載する様々な実装形態の範囲から逸脱することなしに、例えば第1の電子装置を第2の電子装置と呼ぶことができ、同様に第2の電子装置を第1の電子装置と呼ぶことができる。第1の電子装置及び第2の電子装置はどちらも電子装置だが、それらは必ずしも同じ電子装置ではない。 30

##### 【0030】

[0039] 本明細書で記載する様々な実装形態の説明の中で使用する用語は、特定の実装形態を説明するためのものに過ぎず、限定的であることは意図しない。記載する様々な実装形態の説明及び添付の特許請求の範囲の中で使用するとき、単数形「a」、「an」、及び「the」は、文脈に別段の指示がない限り複数形も含むことを意図する。本明細書で使用するとき「及び／又は」という用語は、列挙する関連アイテムの1つ又は複数の任意の及びあり得る全ての組合せを指し、包含することも理解されよう。「含む/includes」、「含んでいる/including」、「備える/comprises」、及び／又は「備えている/comprising」という用語は、本明細書で使用するとき、述べられた特徴、完全体、ステップ、操作、要素、及び／又はコンポーネントの存在を明示するが、1つ又は複数の他の特徴、完全体、ステップ、操作、要素、コンポーネント、及び／又はそれらのグループの存在若しくは追加を排除しないことが更に理解されよう。 40

##### 【0031】

[0040] 本明細書で使用するとき、「場合(if)」という用語は、文脈に応じて「とき(when)」、又は「すると(upon)」、又は「判定することに応答して(in response to determining)」、又は「検出することに応答して(in response to detecting)」、又は「～という判定に従って(in accordance with a determination that)」を意味すると任意選択的に解釈される。同様に、「～と判定される場合(if it is determined)」、又は「[述

べられた条件又は事象]が検出される場合(if [a stated condition or event] is detected)」という表現は、文脈に応じて「判定すると(upon determining)」、又は「判定することに応答して(in response to determining)」、又は「[述べられた条件又は事象]を検出すると(upon detecting [the stated condition or event])」、又は「[述べられた条件又は事象]を検出することに応答して(in response to detecting [the stated condition or event])」、又は「[述べられた条件又は事象]が検出されたと判定することに従って(in accordance with a determination that [a stated condition or event] is detected)」を意味すると任意選択的に解釈される。

### 【0032】

[0041] 図1A及び図1Bは、一部の実装形態による、パラレルニューラル処理(PNP)AIプロセッサを有するシステムアーキテクチャの一例を示すブロック図である。図1Aは、一部の実装形態による、PNP AIプロセッサ102を評価システム116と統合するシステムアーキテクチャ100の一例を示すブロック図であり、評価システム116は生データを処理し、AIタスク(例えば画像認識、自然言語処理)をPNP AIプロセッサ102に伝送し、PNP AIプロセッサ102の出力を評価する。評価システム116はAIタスクをPNP AIプロセッサ102に伝送し、システムが有意味の応答114と共に外部刺激112に素早く反応することを可能にする。この構成では、PNP AIプロセッサ102がコプロセッサとして働き、評価システム116から受信される重大なタスクを実行する。一部の実装形態では、評価システム116が従来のマイクロプロセッサ、ソフトウェア、埋め込み又はモバイルアプリケーションを含む。図1Bは、PNP AIプロセッサ102が入力刺激112に応答して独立に(図1Aの評価システム116の支援なしに)動作し、入力刺激112を処理し、応答114を生成する、システムアーキテクチャ120の一例を示すブロック図である。この構成では、破線が示すようにPNP AIプロセッサ102が既存のマイクロプロセッサ、ソフトウェア、埋め込み又はモバイルアプリケーションを含む従来のシステムと共に動作することもできる。

### 【0033】

[0042] 図1Aに示すようにPNP AIプロセッサ102がコプロセッサとして働く場合、一部の実装形態によれば、評価システム116(本明細書ではプロセッササブシステムと呼ぶこともある)が外部入力装置からの生データ入力(本明細書では刺激と呼ぶこともある)を前処理し、その生データ入力をPNP AIプロセッサ102に送信する役割を担う。例えばプロセッササブシステムは、入力データをPNP AIプロセッサへの代表的な電圧レベル入力へと変換する。様々な実装形態において、かかる刺激はユーザ(例えばキーボード又はマウス)によって入力されるデータ、外部装置(例えばカメラ)から入力される画像又は映像入力、音声入力、センサ及び/又はモータからの感覚データを含む。この一覧は例示的であり網羅的であることは意図しない。例示として、システムアーキテクチャ100によって制御される可動ロボットアームが外部の物理的制約(例えば壁に妨げられること)によって動きが取れなくなる場合、ロボットアーム内の1つ又は複数のセンサが(図6に関して以下で詳細に説明する)コントロールグループ(CG)モジュール108に影響を及ぼすシステムへのフィードバックを生成することができる。

### 【0034】

[0043] 一部の実装形態によれば、図1Aに示す評価システム116はPNP AIプロセッサと組み合わせて対話型インテリジェンスシステムを実装する。一部の実装形態では、評価システムが刺激に応答してPNP AIプロセッサ102(本明細書では分類器又は分類器システムと呼ぶこともある)から受信されるアクションの選択肢を一部の実装形態に従って1組の記憶済みの経験に基づいて評価する。一部の実装形態では、評価システム116が1組の記憶済みの経験に基づいてアクションの選択肢の成功確率を分類し、ランキングが最も高いアクション(即ち成功確率が最も高いアクション)を返す。その後、一部の実装形態では、評価システム116が最も高いランディングの(刺激性、implicit、反射)アクションに対応するアクション応答を生成する(例えばロボットアームを動かすモータを始動する)。一部の実装形態では、評価システム116がメモリ110のEM

10

20

30

40

50

E M 内に記憶されている経験データをメモリ 110 の I M E M 内に記憶されているデータと比較し、2つのデータ間に一致がある場合はアクションを生成する（評価、 explicit、認知）。かかる一部の実装形態では、 explicit 応答と implicit 応答とが一致しない場合、評価システムが（図 5 に関して以下で説明する） C G モジュール 108 内の 1 つ又は複数の因子又は変数を調節する（神経可塑性）。以下でより詳細に説明するように、 C G モジュール 108 の因子又は変数は、処理クロックサイクル中に利用されるニューロンの数並びにニューロンの学習率に影響を及ぼす。更に一部の実装形態では、刺激が成功裏のアクションを引き起こす場合、その後の処理ステップ内で更に使用するために成功裏のアクションを示す情報が（例えばメモリブロック 110 及び / 又は C G モジュール 108 へのフィードバック信号によって） P N P A I プロセッサにフィードバックされる。一部の実装形態では、刺激に対応して行われるアクションが更なる刺激を引き起こす。

10

#### 【 0035 】

[0044] 次に P N P A I プロセッサ 102 に注目する。図 1A 及び図 1B に示すように、一部の実装形態では P N P A I プロセッサ 102 が、ニューラルネットワークの 1 つ又は複数の層（例えばデータ入力又は刺激から情報を抽出するニューラルネットワークの情報層又は一次層 104 、及び / 又は一次層 104 の情報出力から概念を抽出するニューラルネットワークの概念層又は二次層 106 ）、コントロールグループ（ C G ）モジュール 108 、及び 1 つ又は複数のメモリブロック 110 （例えば implicit メモリブロック I M E M 、 explicit メモリブロック E M E M ）で構成されている。一部の実装形態では、 C G モジュール 108 及び / 又はメモリブロック 110 が任意選択的なコンポーネントである。

20

#### 【 0036 】

[0045] 各層 104 、 106 は、複数の相互接続されたニューロン（本明細書では下位分類器とも呼ぶ）を含み得る。一部の実装形態では、構成可能なトポロジに基づいてニューロンが接続される。（図 2 ~ 図 6 に関して以下で詳細に説明する）ニューロンは、ニューラルネットワークの処理要素又はエンジンである。人工ニューラルネットワーク内でソフトウェアのニューロンが動作するやり方と同様に、パラレルニューラルプロセッサ 102 内のハードウェアのニューロンもデータを処理し分類する。しかしそフトウェアのニューロンと異なり、ハードウェアのニューロンは時として一度に何百万、何十億、更には何兆もの組で並列に動作する。一部の実装形態では、層内のニューロンのネットワークが段階単位で組織化され、段階内のニューロンの各組は所与のクロックサイクル中に並列に動作する。例えばニューロンの第 1 段階が入力に作用し、その後ニューロンの 1 つ又は複数の段階（隠れ層と呼ぶこともある）がニューロンの第 1 段階の出力を連続して処理し、最後にニューロンの出力段階にフィードする。一部の実装形態によれば、各段階は同じ入力に対して作用する段階内の全てのニューロンを完了するのに 1 クロックサイクルかかる。従って、これらの実装形態は完全にソフトウェアによって実装されるシステムと比較してより速い処理速度を実現する。一部の実装形態によれば、入力段階ではニューラルプロセッサにとって外部の又は内部のハードウェア（例えばマルチプレクサ）がニューラルネットワークの全体にわたって生データを供給し又は分散する。一部の実装形態では、評価システム 116 が生データ（例えば生データ 112 ）を前処理し、処理済みの入力（例えば所定の電圧レベル）を P N P A I プリプロセッサに与える。一部の実装形態によれば、特定のデータセットに基づいてニューロンのネットワークが訓練されると、ニューロンの様々なグループが様々なデータセットについて活性化する。例えば、テニスボールの画像を表す入力データを受信することに応答して（第 1 の勝利ニューロンを有する） 1 組のニューロンが活性化する一方、花の画像を表す入力データを受信することに応答して（第 2 の勝利ニューロンを有する）別の 1 組のニューロンが活性化する。

30

#### 【 0037 】

[0046] コントロールグループ（ C G ）モジュール 108 については、一部の実装形態に従って以下の図 5 及び図 6 に関して詳細に説明する。メモリブロック 110 については以下の図 6 に関して説明する。一部の実装形態に従い、 P N P A I プロセッサ 102 の

40

50

モジュール間の様々な内部接続、及び P N P A I プロセッサ 1 0 2 からの外部接続を図 1 A の中の黒い実線によって示している。

#### 【 0 0 3 8 】

[0047] 一部の実装形態では、入力刺激 1 1 2 は、評価システム 1 1 6 が生入力データを前処理する必要なしに、パラレルニューラルプロセッサ 1 0 2 内の 1 つ又は複数のニューラルネットワークに直接接続される。一部の実装形態では、P N P A I プロセッサ 1 0 2 の出力が、介在する評価システム 1 1 6 なしに応答モジュール 1 1 4 に直接接続される。一部の実装形態では、刺激受信モジュール 1 1 2 及び / 又は応答モジュール 1 1 4 が P N P A I プロセッサ内に統合され、即ち P N P A I プロセッサ 1 0 2 は外部のソフトウェア / ハードウェアなしに刺激（例えば何らかの種類の干渉）を受信し、及び / 又は応答（例えばロボットアームを動かすこと）を生成することができる。10

#### 【 0 0 3 9 】

[0048] ここで及び以下に記載する回路は、何百万、何十億、更には何兆ものニューロンを使用するニューラルネットワークのパラレルハードウェア実装を可能にする。そのように著しくパラレルなハードウェア実装は複雑な問題集合に対処する A I 実装を可能にする。

#### 【 0 0 4 0 】

[0049] 一部の実装形態では、段階内で互いにフィードする多次元のニューロン層を作り出すために、ニューラルネットワークの様々なセクションが階層式に組織化される。例えば階層状のニューラルネットワークは、神経回路網が人間の目の中で組織化される方法と似ている。別の例としてニューラルネットワークが 2 つの層によって組織化され、ニューロンデータの第 1 の層（例えばニューロンの層 1 0 4 、図 1 A 及び図 1 B ）は入力から情報を抽出し、ニューロンデータの第 2 の層（例えばニューロンの層 1 0 6 、図 1 A 及び図 1 B ）は第 1 の層の出力に基づく概念を認識する。かかる一部の実装形態では、低レベルの情報（例えばパターンを含む生データ）から高レベルの概念を抽出し保持する能力により、ニューラルネットワークは新たな刺激（即ち訓練中に過去に認められなかったデータ）に対する応答を処理し生成する。例えば「聴覚は耳であるのに対して視覚は目である（感覚）」を接続されたより高い層内で抽出し、新たな無関連の且つまだ経験されていない味覚等の刺激中に適用できること等、上記の回路を使用するニューラルネットワークは関連する高レベルの概念を認識することができる。20

#### 【 0 0 4 1 】

[0050] 図 2 A は、一部の実装形態による、図 1 A ~ 図 1 B の P N P A I プロセッサ 1 0 2 の下位分類器のコンポーネントであるアナログウィンドウコンパレータ ( W C ) 2 1 6 を示す。一部の実装形態では、マイクロプロセッサ、ランダムアクセスメモリ、オペレーティングシステム / 埋め込みシステム、及びソフトウェアを使用することによって人工ニューロンをエミュレートする従来のニューラルネットワークと異なり、本明細書で開示するシステムがハードウェアの実装である。一部の実装形態によれば、図 2 A に示すような W C 回路（本明細書ではコンパレータと呼ぶこともある） 2 1 6 がニューロンの基礎を形成する。一部の実装形態では、多岐にわたる基本電子コンポーネント（例えば接合トランジスタ、F E T ）を使用して W C 回路が構築される。一部の実装形態では、集積回路（例えば演算増幅器）を使用して W C 回路が構築される。図 2 A に示すように、一部の実装形態によれば W C 回路は、その入力 ( I W C 2 0 6 ) に印加される電圧が低基準電圧 ( R L 2 0 8 ) と高基準電圧 ( R H 2 1 0 ) との間に含まれる場合は高ビット ( 1 ) を出力し ( O W C 2 1 4 ) 、入力 ( I W C 2 0 6 ) が高基準電圧及び低基準電圧の基準電圧の範囲外である場合は低ビット ( 0 ) を出力する ( / O W C 2 1 2 ) 。一部の実装形態では、単一の W C 回路が個々の「ハードウェアニューロン」を形成し、ハードウェアニューロンは入力電圧が或る範囲内に含まれる場合に「発火」（又は活性化）し、ソフトウェアアプリケーションによって実現される仮想ニューロンの応答と同様の全か無かの応答をもたらす。40

#### 【 0 0 4 2 】

10

20

30

40

50

[0051] 図2Bは、一部の実装形態による非反転WC218を示す。一部の実装形態では、WC218が図2AのWC回路216とほぼ同じ機能を実行する。一部の実装形態では、WC218が2つの接続された演算増幅器（図2AのOp-Amp202及びOp-Amp204）を使用して形成される。

#### 【0043】

[0052] 一部の実装形態では、WC回路が入力条件に対して反転的又は非反転的であるように構成されている。簡単にするために、図2A～図2BではWCの非反転出力（OWC214）だけを示す。本明細書で論じる例は限定ではなく例示として解釈すべきである。

#### 【0044】

[0053] 図3は、一部の実装形態による、ニューラルネットワーク（例えば図1A～図1Bの一次層104又は二次層106）内の一連のWC回路（WC1, WC2, WC3, ..., WC<sub>N</sub>）を示す。一部の実装形態では、ソフトウェアニューロンがソフトウェアに基づく従来のニューラルネットワークを形成するやり方と同様に、一連のWCが相互接続されてニューラルネットワークを形成する。一部の実装形態によれば、ニューラルネットワークトポロジに基づいてWCが相互接続される。ニューラルネットワークトポロジは、ネットワークを形成するためにニューロンが接続される方法を表す。ニューラルネットワークトポロジは、ニューロンの接続によるニューロン間の関係と見なすこともできる。WCは同じ入力刺激IW<sub>C</sub>(318)にそれぞれ作用して対応する出力を生成することができる。

#### 【0045】

[0054] 一部の実装形態では、各WCがウインドウ電圧範囲（WVR：Window Voltage Range）を有し、WCは入力がWVRの範囲内にある場合は第1の値を生成し、入力がWVRの範囲外にある場合は第2の値を生成する。一部の実装形態では、WVRが低基準電圧と高基準電圧との差である。一部の実装形態では、各WCが固有のWVRを有する。例えば図3では、対応するWVRが全て固有であるようにコンパレータWC1の基準電圧（RL1302及びRH1304）、コンパレータWC2の基準電圧（RL2306及びRH2308）、コンパレータWC3の基準電圧（RL3310及びRH3312）、及びコンパレータWC<sub>N</sub>の基準電圧（RL<sub>N</sub>314及びRH<sub>N</sub>316）がそれぞれ設定される。一部の実装形態ではWVRが重複しない。一部の実装形態では、複数のWCが所与の刺激に応答するようにWVRが重複する。例えば複数のWCの出力（例えばOWC1322、OWC2324、OWC3326、及びOWC<sub>N</sub>328）が所与の入力刺激IW<sub>C</sub>(318)に関して高値(1)に等しくあり得る。各WCの基準電圧入力RL及びRHはRH > RLとなるように電圧でロードされ、それにより各WCのWVRを作り出す。一部の実装形態によれば、各WCが始動時に応答するWVRで初期設定される。一部の実装形態では、各WCがランダムWVRで初期設定される。他の一部の実装形態では、WVRが全ニューラルネットワークにわたって一様勾配を形成するように各WCがWVRで初期設定される。

#### 【0046】

[0055] 図4は、一部の実装形態による、データフロー制御段階を有する相互接続されたニューラルネットワーク（例えば図1A～図1Bの一次層104又は二次層106）内の一連のWCを示す。第1段階（S1）は、データ入力段階又はシステムに刺激（例えば入力IW<sub>C</sub>402）が入力される場所である。一部の実装形態では、入力データ電圧IW<sub>C</sub>に加えて電圧を導入することによってWCへの入力重みを制御するために重み電圧（WV：Weight Voltage）回路を使用する。様々な実装形態において、異なるWCの重み電圧（例えばWV404、WV406、及びWV408）を同じ電圧値又は異なる電圧値に設定することができる。一部の実装形態では、入力刺激を重み電圧と組み合わせるために、及び最終的な加重入力をそれぞれのWCに供給するために回路（本明細書では加重入力モジュールと呼ぶこともある）を使用する。例えば図4では、回路440がWC404からの重み電圧を入力刺激IW<sub>C</sub>402と組み合わせてコンパレータWC1450に加重入力を供給し、回路442がWC406からの重み電圧を入力刺激IW<sub>C</sub>402と組み合わ

10

20

30

40

50

せてコンパレータ W C 2 4 5 2 に加重入力を供給し、回路 4 4 4 が W C 4 0 8 からの重み電圧を入力刺激 I W C 4 0 2 と組み合わせてコンパレータ W C N 4 5 4 に加重入力を供給する。一部の実装形態では、下位分類器がコンパレータモジュールに結合された加重入力モジュールを含む。例えば図 4 では、コンパレータ W C 1 4 5 0 が加重入力モジュール 4 4 0 に結合されており、コンパレータ W C 2 4 5 2 が加重入力モジュール 4 4 2 に結合されており、コンパレータ W C N 4 5 4 が加重入力モジュール 4 4 4 に結合されている。

#### 【 0 0 4 7 】

[0056] 一部の実装形態によれば、一部のトポロジでは、ラッチ又は一時的なメモリセル（本明細書ではメモリモジュールと呼ぶこともある、例えばラッチ 4 1 0 、 4 1 2 、及び 4 1 4 ）の第 2 段階（ S 2 ）回路が W C の出力（ O W C ）を記憶する。様々なシーケンスを使用してデータを記憶するための様々なラッチング技法がある。例えば単純化されたシーケンスでは、ラッチが指定の期間にわたって一度に 1 つの刺激に対する応答を記憶する。より複雑なシーケンスでは、入力データがデータチャンクに分割され、ラッチが一度に 1 つのデータチャンクに対応する応答データを記憶する。10

#### 【 0 0 4 8 】

[0057] 一部の実装形態によれば、一部の実装形態では、ニューラルネットワークのトポロジ又は相互接続方法に基づいてそれぞれの W C の出力（ O W C ）データが他の W C に入力される。一部の実装形態では、図 4 に示すように、段階 3 （ S 3 ）内の W C の入力段階の W V を調節するために、第 2 段階（ S 2 ）メモリラッチの後に配置されるニューラルネットワーク内の別の 1 組の回路（例えば回路 4 1 6 、 4 1 8 、及び 4 2 0 ）が近傍のニューロン（ W C ）内に電圧をフィードバックする。一部の実装形態では、トポロジバス O N N （例えばトポロジバス 4 2 2 、 4 2 4 、又は 4 2 6 ）によって示すように、ニューラルネットワーク内の 1 つ又は複数のニューロンからの追加の接続（例えば接続 4 2 8 、 4 3 0 、及び 4 3 2 ）が W V 回路に適用される。一部の実装形態では、ラッチの第 2 段階（ S 2 ）回路なしに、現在のフィードバックがニューロンのネットワークを飽和させないように、及びニューロンがニューロンの出力に基づいてのみオンになるように、ニューロンを活性化するためのクロックサイクル又はパルス幅を設定することができる。20

#### 【 0 0 4 9 】

[0058] 図 4 ではトポロジバス（例えばバス 4 2 2 、 4 2 4 、及び 4 2 6 ）を同じ名前 O N N によって識別するが、様々な実装形態においてトポロジバスは異なるように構成され、例えばニューラルネットワークの様々な部分又は領域が局所トポロジに基づいて異なるように組織化され又は相互接続され得る。人間の脳が高度に特化した領域に分けられる方法と同様に、一部の実装形態では、人工頭脳を形成するためにそれ自体が相互接続される特定の機能（言語、視覚、聴覚等）について個々のトポロジを特化した状態で、（何百万更には何十億もの W C を有する）単一のシリコンウエハをニューラルネットワークの領域へと更に細分することができる。30

#### 【 0 0 5 0 】

[0059] 回路及びハードウェア接続の種類により、全ての W C を並列計算式に同時に処理し、完全にソフトウェアに基づくネットワークと比較して広範な応用も提供しながら著しい性能向上をもたらすことができる。例えば半導体ウエハ上に百万の W C がエッチされた状態で、百万以上の W C の全ての組を単一のクロックサイクル内で評価することができる。クロック周波数が 2 G H z だと仮定し、例えば百万以上のニューロン（ W C ）のニューラルネットワークの二十億以上の反復を 1 秒で評価することができる。40

#### 【 0 0 5 1 】

[0060] ニューラルネットワークを構築するために図 2 ~ 図 4 に関して上記で説明した W C のネットワークがどのように使用されるのかを更に示すために、一部の実装形態による、一種の教師なし学習ネットワークである自己組織化マップ（ S O M ）の構築例を検討されたい。 S O M 内の自己組織化プロセスは初期設定、競争、協力、及び適応で構成されている。最初に全てのニューロンの重みベクトルを小さい乱数値で初期設定する。 W C ハードウェアニューロンの場合、重み電圧（ W V ）を乱数値に初期設定する。ニューロンは50

、入力パターン（例えば画像内の全てのピクセル）ごとに判別関数のその個々の値を計算する。従来の仮想ニューロン内で概して使用される判別関数は、入力ベクトルとニューロンごとの相互接続重みベクトルとの間の平方ユークリッド距離である。WCに基づくハードウェアニューロンでは、判別関数は入力電圧と重み電圧との間の平方ユークリッド距離であり得る。判別関数の最小値を有する特定のニューロンをデータミナントニューロン（determinant neuron）と見なす。WCに基づくハードウェアニューラルネットワークでは、電圧閾値の初期構成及び関連する重みにもよるが、1つ又は複数のWCニューロンが入力パターンに応じたデータミナントニューロンであり得る。簡単にするために、例えば単一のデータミナントニューロンを検討されたい。データミナントニューロンは、（例えば近傍内の重みを調節するために）協力する活性化済みのニューロンの近傍の空間位置をトポロジに基づいて決定する。1つのニューロンが活性化すると、その最も近い近傍が、より遠くに位置する近傍よりも強く影響を受けた応答を有する傾向がある。WCに基づくハードウェアニューラルネットワークでは、データミナントニューロンからの電圧出力がその近傍に接続されるので、出力が近傍の重み電圧に影響を及ぼす。影響を受けるニューロンは、関連する接続の重みを調節することにより、入力パターンに関して判別関数のその個々の値を更新する。WCに基づくニューラルネットワークでは、重みが継続的に適応される。こうして、同様の入力パターンのその後の適用に対するデータミナントニューロンの応答が向上する。

#### 【0052】

[0061] WCに基づくニューラルネットワークの自己組織化プロセスを視覚化するやり方として、連続的な二次元入力空間内の1組のデータ入力が、1組のWCに基づくニューロン上にどのようにマップされるのかを検討されたい。WCに基づくニューロンはトポロジに従って組織化され又は接続される（例えば全てのニューロンが他の全てのニューロンに接続される）。WCに基づくニューロンはランダム割当（例えば電圧値）において開始することができ、重みがランダム初期値に又は勾配に従って初期設定される。ニューロンのそれぞれが、（例えばプリプロセッサによって）対応する電圧値に変換される第1の入力を読み取る。ニューロンの1つである「データミナントニューロン」が高値出力で応答する。様々な構成において、複数のニューロンが入力に応答することができる。データミナントニューロンはデータ入力に近づくと言われ、それはデータミナントニューロン及びその近傍に入力電圧に対して応答させるために、データミナントニューロンの重みの初期値が入力電圧に応じて調節されるからである。近傍のニューロンも、より少ない量だがデータ入力に近づく。1つ又は複数のデータミナントニューロン及び/又は関連する近傍を選択するために全てのニューロンが各ステップにおいて同じ入力を得るので、このプロセスは並列である（即ちWCに基づくニューロンがそろって動作する）。このステップの終わりに重み（全てのWCに基づくニューロンの電圧値）が調節される。次に第2のデータ入力が訓練のために選択される。この第2のラウンドでは、第1の「データミナントニューロン」と異なるニューロンがデータミナントである。新たなデータミナントニューロンの隣のニューロンが、より少ない量だけ第2のデータ入力に近づくことによって応答する。ここでもこのステップの終わりに重みが調節される。全てのニューロンの重みが安定状態に達する（例えばニューラルネットワーク内のニューロンの重み電圧において大きな変動がなくなる）まで、及び少なくとも全ての入力データが処理されるまでこのプロセスは続く。例えばこのプロセスは、所与のデータセットを使用して数回繰り返される。最終的に、WCに基づくニューロンの全出力グリッドが入力空間を表す。

#### 【0053】

[0062] 図5は、CGモジュール（不図示）からのCG信号502が追加された（図4にあるのと同様の）一連のWCを示す。一部の実装形態によれば、CGモジュールはニューラルネットワークの神経可塑性及び挙動を制御する。神経可塑性により、ニューラルネットワークは自己学習を行う。従来のネットワークはデータセットへの繰り返しの暴露によって訓練され、或る期間にわたって収束し、データセットを突き合わせて有意味の出力を生成するために接続の重みが調節される。訓練期間は学習率に依存する。一例として自

己組織化マップ( S O M )では、訓練期間が学習範囲又は訓練の影響を受けるニューロンの数にも依存する。学習範囲は、特定の入力について活性化するニューロンであるBest Matching Unit( B M U )(本明細書では「デターミナントニューロン」と呼ぶこともある)からの距離を示す。これらのパラメータは、ニューラルネットワークが刺激に所望のやり方で応答するよう完全に訓練されるまで徐々に低減される。しかし、初期訓練中に考慮されない任意の新たなデータセットは訓練されたニューラルネットワークの範囲から外れる。このことは神経可塑性を実現するニューラルネットワークの能力を限定し、ニューラルネットワークは新たなデータセットを扱うように再訓練する又は新たなデータに対応するように再設計する必要がある。

## 【 0 0 5 4 】

[0063] 従来のニューラルネットワークでのこうした限定に対処するために、図5に示すような一部の実装形態では、C G信号(例えば信号502)が入力刺激に対する応答を強化し又は抑制し、ニューロンの学習率及び/又は数を修正する。一部の実装形態では、ニューラルネットワークの挙動に影響を与えるようにC G信号がニューラルネットワークに継続的に及び/又は断続的に適用される。かかる挙動の変化は、ニューラルネットワークが刺激に応じてどの程度注意深いか、緩やかか、及び/又は反応的かを含む。一部の実装形態では、C G信号がニューラルネットワークの焦点を特定の刺激に限定し、及び/又はニューラルネットワークの全体的な学習能力を限定する。ニューラルネットワークが刺激を処理しつつも、C G信号はこうして適応学習を実装する。一部の実装形態では複数のC G変数を同時に使用し、複雑な挙動パターンをカバーする。一部の実装形態では、C G信号がW Cニューロン群の局所的な挙動/可塑性及び/又は全体的な挙動/可塑性に影響を及ぼし得る。一部の実装形態では、C G信号が比較モジュールの感度に影響を及ぼし得る。一部の実装形態では、C G信号が加重モジュールの前に入力信号に影響を及ぼし得る。図5では、例えばC G信号502がニューロン又はコンパレータW C<sub>1</sub>、W C<sub>2</sub>、及びW C<sub>N</sub>への入力に影響を及ぼす。一部の実装形態では、ニューラルネットワークの挙動に影響を及ぼすために、W Cニューロンの異なる領域又は近傍に異なるC G信号が適用される。

10

## 【 0 0 5 5 】

[0064] 一部の実装形態によれば、W V回路(例えばW V 5 0 4、W V 5 0 6、W V 5 0 8)がC G信号(例えば信号502)を受信し、そのC G信号に基づいてそれぞれのW Cへの加重入力を調節する。様々な実装形態において、W V回路は、W Cによって入力刺激と比較される加重出力をC G信号に応じて制御する電圧制御抵抗器( V C R )及び/又は可変抵抗器( 例えばポテンショメータ又はデジタルポテンショメータ、電界効果トランジスタ、抵抗ラダー、抵抗ブリッジ、抵抗回路網、接合トランジスタ、又は他の電流若しくは電圧制御回路 )を使用して構築される。

30

## 【 0 0 5 6 】

[0065] 図6は、一部の実装形態による、図5のC G信号を有する一連のW C及び追加のメモリ604(本明細書ではImplicitメモリ( I M E M )と呼ぶこともある)を示す。I M E M 6 0 4は、下位領域へのメモリポインタの高速のリダイレクトを可能にすることができる、及び/又は刺激に応答するのに必要なデータを含むメモリ領域のメモリアドレスを提供する。I M E M 6 0 4により、(図1A~図1Bの)評価システム116は、特定のデータを評価し応答114を提供するために、大きいメモリ空間を読み取って所与の入力刺激に固有のデータを検索するのを回避する。

40

## 【 0 0 5 7 】

[0066] 一部の実装形態によれば、Implicitメモリは、例えば入力刺激が過去の経験に似ているだけでも(正確に一致しなくても)応答をトリガすることにより、刺激に対して直感的な応答を有するようにニューラルネットワークを向上させることができる。一部の実装形態によれば、I M E Mと比較し、explicitメモリブロック( 例えばE M E Mブロック606、608、及び610 )は入力刺激に応答して取得される厳密なデータ( 例えば過去の入力に対する過去の応答 )を記憶するように構成され得る。例えばP N P A Iブ

50

ロセッサ 102 は、現在の入力を過去の入力（例えば人が部屋を訪れること又は映像若しくは画像を見ることと等価）と突き合わせることができ、過去に生成した仮想画像を E M E M から取得し、それを現在の入力と比較してマッチング応答を生成することができる。より詳細なデータは E M E M によってアクセス可能である一方、 I M E M はデータから抽出される情報及び概念の全般的なパターンを記憶し表す。

#### 【 0 0 5 8 】

[0067] 一部の実装形態では、1組の1つ又は複数のメモリブロックとしてメモリ 604 を視覚化することができ、各メモリブロックは取得されるデータを表す。一部の実装形態によれば、メモリブロックは I M E M ブロック並びに E M E M ブロックの両方として言及され得る。一部の実装形態では、I M E M は1つ又は複数の W C 出力（例えばニューラルネットワークのニューロンの所与のブロックからの出力）及び / 又は C G 状態の組み合わせを使用してアドレス指定することができる。例えば図 6 では、I M E M 604 は（対応する E M E M ブロック 606、608、及び 610 にそれぞれ接続する信号 618、620、及び 622 によって示す）制御信号 602 及び / 又は W C 出力 612、614、及び 616 によって直接アドレス指定することができる。かかる一部の実装形態では、C G 信号が刺激に応答するためにアクセスされるメモリブロックのサイズ又はメモリブロックの数に影響を及ぼす。I M E M ブロックとは対照的に、E M E M ブロックは W C 出力によってアドレス指定される。一部の実装形態によれば、例えば接続ライン（例えばライン 612、614、及び 616）を使用して図 6 の E M E M ブロックをアドレス指定する。

10

#### 【 0 0 5 9 】

[0068] 図 6 に示すように、一部の実装形態によれば、様々なメモリブロック（例えばブロック 624、626、及び 628）からのデータが、入力刺激に応答するために（図 1A ~ 図 1B に示す）評価システム 116 によって使用される（例えば応答プロセスへの出力 624、626、及び 628）。

20

#### 【 0 0 6 0 】

[0069] より迅速なアクセスを得るためにキャッシュメモリアーキテクチャが過去に使用された及び / 又は頻繁に使用される関数又はデータを記憶することによってメモリアクセスを改善するやり方と同様に、I M E M アーキテクチャは刺激の親密度に基づいてメモリアクセスを改善する。例えばニューラルネットワークの出力をパターンマッチングして記憶場所を指定することに依拠する必要なしに、1つ又は複数のコントロールグループ信号を使用してメモリ内の1つ又は複数のオブジェクトに直接アクセスできるように、繰り返し観測される刺激はシステムにフィードバックを与えることができる。しかしキャッシュと異なり、I M E M は追加の記憶域を必要とするこなしに又は反復型の検索の繰り返しを実行して正しい記憶場所をパーズし見つけるこなしに、（例えば C G 及び W C 出力を使用する直接アクセスによって）メモリアクセスを改善する。

30

#### 【 0 0 6 1 】

[0070] 図 6 は、それぞれの E M E M ブロックが単一の下位分類器にのみ接続されているかのように E M E M ブロックを示す（例えばライン 612 は第 1 の下位分類器を E M E M ブロック 1 に接続している）が、下位分類器は複数の E M E M ブロックにアクセスすることができる。接続ライン（例えばライン 612、614、及び 616）は、コンパレタの出力による E M E M ブロックのアドレス指定能力を示すことを意図する。

40

#### 【 0 0 6 2 】

[0071] ブロック 630 によって示すように、一部の実装形態ではマスタ分類器が複数の下位分類器、I M E M ブロック、及び / 又は C G 信号を含む。一部の実装形態では、マスタ分類器 630 が複数の下位分類器、I M E M ブロック、及び / 又は C G 信号に結合された独立したモジュール（図 6 には不図示）である。かかる一部の実装形態では、マスタ分類器 630 が1つ又は複数のクロックサイクル中に（例えばメモリ 604 により）複数の下位分類器のそれぞれから個々の出力信号のそれぞれを受信し、所定の出力閾値を上回る値を有するそれぞれの出力信号を生成する複数の下位分類器の部分集合に基づいて分類器応答を決定する。

50

**【0063】**

[0072] 図7は、一部の実装形態による、パラレルニューラルプロセッサ（例えばPNP A Iプロセッサ102）を有する代表的なシステム700を示すブロック図である。一部の実装形態では、システム700（例えば図1Aのシステムアーキテクチャ100を有する任意の装置）が1つ又は複数の処理装置（例えばCPU、ASIC、FPGA、マイクロプロセッサ等）702、1つ又は複数の通信インターフェース714、メモリ718、外部センサ704、音声／映像入力706、及びそれらのコンポーネント（チップセットと呼ぶこともある）を相互接続するための1つ又は複数の通信バス720を含む。

**【0064】**

[0073] 一部の実装形態では、システム700がユーザインタフェース708を含む。一部の実装形態では、ユーザインタフェース708は、1つ若しくは複数のスピーカ及び／又は1つ若しくは複数の表示装置を含む、メディアコンテンツの提示を可能にする1つ又は複数の出力装置710を含む。一部の実装形態では、ユーザインタフェース708は、キーボード、マウス、音声コマンド入力ユニット又はマイクロホン、タッチスクリーンディスプレイ、タッチセンス入力パッド、ジェスチャ捕捉カメラ、又は他の入力ボタン若しくはコントロール等、ユーザ入力を助けるユーザインタフェースコンポーネントを含む1つ又は複数の入力装置712も含む。更に、一部のシステムはマイクロホンと音声認識、又はカメラとジェスチャ認識を使用してキーボードを補足し又は置換する。

10

**【0065】**

[0074] 一部の実装形態では、システム700が1つ又は複数の画像／映像捕捉又は音声／映像入力装置706（例えばカメラ、ビデオカメラ、スキャナ、光センサユニット）を含む。任意選択的に、システム700はシステム装置700の位置を突き止めるための位置検出装置（不図示）を含む。

20

**【0066】**

[0075] 一部の実装形態では、システム700が1つ又は複数の組込センサ718を含む。一部の実装形態では、組込センサ718が、例えば1つ又は複数の熱放射センサ、周囲温度センサ、湿度センサ、IRセンサ、（例えばRFIDセンサを使用する）占有センサ、周囲光センサ、運動検出器、加速度計、及び／又はジャイロスコープを含む。

**【0067】**

[0076] 一部の実装形態では、システム700が1つ又は複数の外部センサ704を含む。一部の実装形態では、外部センサ704が、例えば1つ又は複数の熱放射センサ、周囲温度センサ、湿度センサ、IRセンサ、（例えばRFIDセンサを使用する）占有センサ、周囲光センサ、運動検出器、加速度計、及び／又はジャイロスコープを含む。

30

**【0068】**

[0077] 一部の実装形態によれば、システム700は図1～図6に関して上記で説明したAIタスクを実行する／オフロードするための1つ又は複数のパラレルニューラルプロセッサ716（例えば図1A又は図1BのPNP A Iプロセッサ102）を含む。

**【0069】**

[0078] 通信インターフェース720は、例えば様々な特注の又は標準の無線プロトコル（例えばIEEE 802.15.4、Wi-Fi、ZigBee、6LoWPAN、Thread、Z-Wave、Bluetooth Smart、ISA100.11a、Wireless HART、MiWi等）の何れか及び／又は様々な特注の又は標準の有線プロトコル（Ethernet、Home Plug等）の何れか、又は本明細書の出願日にまだ開発されていない通信プロトコルを含む他の任意の適切な通信プロトコルを使用してデータ通信することができるハードウェアを含む。

40

**【0070】**

[0079] メモリ721は、DRAM、SRAM、DDR RAM等の高速ランダムアクセスメモリ、又は他のランダムアクセスソリッドステートメモリ装置を含み、任意選択的に1つ又は複数の磁気ディスク記憶装置、1つ又は複数の光ディスク記憶装置、1つ又は複数のフラッシュメモリ装置、又は1つ又は複数の他の不揮発性ソリッドステート記憶装置等の不揮発性メモリを含む。メモリ721或いはメモリ721内の不揮発性メモリは非

50

一時的コンピュータ可読記憶媒体を含む。一部の実装形態では、メモリ 721 又はメモリ 721 の非一時的コンピュータ可読記憶媒体が以下のプログラム、モジュール、及びデータ構造、又はその部分集合若しくは上位集合を記憶する：

- ・ 様々な基本システムサービスを処理するための及びハードウェアに依存するタスクを実行するための手続きを含む動作ロジック 722、

- ・ 1つ又は複数の通信インターフェース 720（有線又は無線）を介して1つ又は複数のネットワークに接続される、他のネットワーク装置（例えばインターネット接続を提供するルータ、ネットワーク化された記憶装置、ネットワークルーティング装置、サーバシステム等のネットワークインターフェース）に接続するための及びそれらと通信するための装置通信モジュール 724、

- ・ 1つ又は複数の入力装置 712 からの1つ又は複数のユーザ入力又は対話を検出し、検出した入力又は対話を解釈するための入力処理モジュール 726、

- ・ 1つ又は複数の装置（不図示）に関する設定、捕捉データ、及び／又は他のデータを構成し及び／又は閲覧することができるユーザインターフェースを提供し表示するためのユーザインターフェースモジュール 728、

- ・ 装置を制御するために、及び装置が捕捉するデータ（例えばシステム 700 及び／又は他のクライアント／電子装置に関する装置の状態及び設定、捕捉データ、又は他の情報）を確認するためにシステム 700 が実行するための1つ又は複数のアプリケーションモジュール 730、

- ・ これだけに限定されないが、

- 1つ又は複数の入力装置 712、外部センサ 704、組込センサ 718、及び／又は音声／映像入力 706 から、PNP AI プロセッサ 716 によって処理されるデータを受信するためのデータ受信モジュール 7320、

- データ受信モジュール 7320 によって捕捉され又は受信されたデータを処理するための、及び処理済みデータを PNP AI プロセッサ 716 に向けて準備するための（例えば生データ入力から1組のベクトルを作成し、ベクトルをテーブルへと組織化し、及び／又は生データを電圧値に変換するための）及び送信する（例えば電流を加えることによってデータをロードする）ためのデータ前処理モジュール 7322、

- を含む、PNP AI プロセッサ 716 のためのデータを前処理するための機能を提供する PNP 前処理モジュール 732、

- ・（例えば電圧値／閾値を設定する、ニューラルネットワークを初期設定する、並びに学習率及び進捗をモニタする）1つ又は複数の PNP AI プロセッサ 716 を訓練するために、PNP 前処理モジュール 732 及び／又は（以下に記載する）PNP フィードバック及び応答モジュール 734 と連携する PNP 訓練モジュール 734、並びに

- ・ これだけに限定されないが、

- PNP AI プロセッサ 716 からデータを受信するための（例えばウィンドウコンパレータ回路の出力から電圧値を受信するための）データ受信モジュール 7360、

- PNP AI プロセッサ 716 から受信されるデータを後処理するための（例えば電圧値又はニューラルネットワークの出力をシステムによる更なる処理に有用な別の形式に変換するための）データ後処理モジュール 7362、

- （例えば制御値を再調節するために）その出力に基づいて又はシステム内の他の装置からの入力（環境の変化を含む）に基づいて PNP AI プロセッサ 716 へのフィードバックを生成するためのフィードバックモジュール 7364、及び

- PNP AI プロセッサの出力に基づいてシステム応答（例えばロボットアームを動かすこと、カメラの位置を変えること、又は警告を知らせること）を生成するための応答モジュール 7366

- を含む、PNP フィードバック及び応答モジュール 734。

#### 【0071】

[0080] 上記で識別した要素のそれぞれは前に述べたメモリ装置の1つ又は複数の中に記憶することができ、上記の機能を実行するための1組の命令に対応する。様々な実装形

10

20

30

40

50

態において、上記で識別したモジュール又はプログラム（即ち命令セット）は別個のソフトウェアプログラム、手続き、又はモジュールとして実装する必要はなく、従ってこれらのモジュールの様々な部分集合を組み合わせ又は他のやり方で再構成することができる。一部の実装形態では、メモリ 606 が、上記で識別したモジュール及びデータ構造の部分集合を任意選択的に記憶する。更にメモリ 606 は、上記で説明していない追加のモジュール及びデータ構造を任意選択的に記憶する。

#### 【0072】

[0081] 図 8 A ~ 図 8 D は、一部の実装形態による、加重入力モジュール及び加重入力モジュールに結合された比較モジュールを含む下位分類器を使用して入力信号を処理する（802）方法 800 の流れ図の表現を示す。下位分類器については図 4 に関して上記で説明した。一部の実装形態では、比較モジュールが少なくとも 1 つの演算増幅器モジュール（例えば図 2 A 及び図 2 B に関して上記で説明したアナログ WC）を含む（804）。第 1 の下位分類器が、加重入力モジュールにおいて入力信号に重みを適用して加重入力信号が生成された（806）。例えば図 4 では、加重入力モジュール 440 が入力信号 402 に重み 404 を適用してコンパレータ WC1450 への加重入力信号を生成する。一部の実装形態では、加重入力モジュールが第 2 の下位分類器から第 2 の出力信号を受信する（808）。例えば図 4 では、加重入力モジュール 442 が他の下位分類器から（例えばメモリラッチ 410 からの下位分類器出力から）出力信号 418 を受信する。

10

#### 【0073】

[0082] この方法 800 は、比較モジュールの入力ラインにおける加重入力信号を比較モジュールにおいて受信すること（810）を更に含む。例えば図 4 では、加重入力モジュール 440 をコンパレータ WC1450 と接続するように示すライン上で、コンパレータ 450 がモジュール 440 から加重入力信号を受信する。一部の実装形態では、比較モジュールが少なくとも 1 つの演算増幅器モジュールを含み（804 に関して上記で説明した）、加重入力信号を受信することが、少なくとも 1 つの演算増幅器モジュールにおいて加重入力信号を受信すること（812）を含む。

20

#### 【0074】

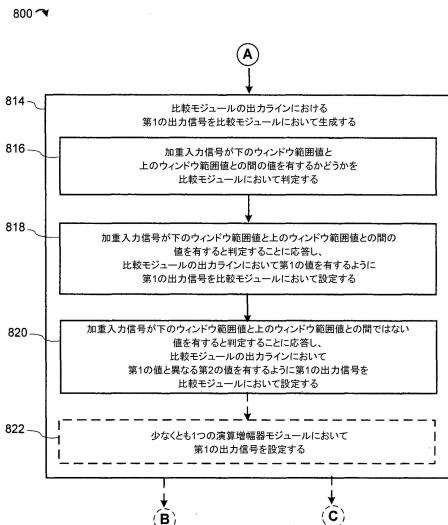

[0083] 一部の実装形態によれば、図 8 B に示すように方法 800 は、比較モジュールの出力ラインにおける第 1 の出力信号を比較モジュールにおいて生成すること（814）を更に含む。例えば図 4 では、コンパレータ WC1450 をメモリラッチ 410 と接続するライン上の出力信号 O<sup>1</sup>WC をコンパレータ WC1450 が生成する。第 1 の出力信号を生成すること（814）は、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを比較モジュールにおいて判定すること（816）を含む。比較の操作については、一部の実装形態に従って図 2 A、図 2 B、図 3、及び図 4 に関して上記で説明した。例えば図 2 A では、Op - Amp 202 及び Op - Amp 204 は、入力電圧 IW<sub>C</sub>206 が低電圧閾値 RL208 と高電圧閾値 RH210 との間にあるかどうかを判定する。第 1 の出力信号を生成すること（814）は、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、比較モジュールの出力ラインにおいて第 1 の値を有するように第 1 の出力信号を比較モジュールにおいて設定すること（818）を更に含む。例えば図 2 A では、入力電圧 IW<sub>C</sub>206 が低電圧閾値 RL208 と高電圧閾値 RH210 との間にある場合、Op - Amp 204 が出力 OW<sub>C</sub> を設定する。別の例として図 4 では、入力電圧 IW<sub>C</sub>402 が低電圧閾値 RL1 と高電圧閾値 RH1 との間にある場合、コンパレータ WC1 (450) がコンパレータをメモリラッチ 410 と接続するラインにおいて出力 O<sup>1</sup>WC を（高電圧値に）設定する。第 1 の出力信号を生成すること（814）は、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、比較モジュールの出力ラインにおいて第 1 の値と異なる第 2 の値を有するように第 1 の出力信号を比較モジュールにおいて設定すること（820）を更に含む。例えば図 2 A では、入力電圧 IW<sub>C</sub>206 が低電圧閾値 RL208 と高電圧閾値 RH210 との間にない場合、Op - Amp 202 が出力 / OW<sub>C</sub> を設定する。別の例として図 4 では、入力電圧 IW<sub>C</sub>

30

40

50

W C 4 0 2 が低電圧閾値 R L 1 と高電圧閾値 R H 1 の間にある場合、コンパレータ W C 1 ( 4 5 0 ) がコンパレータをメモリラッチ 4 1 0 と接続するラインにおいて出力 O 1 W C を ( 低電圧値に ) 設定する。一部の実装形態では、比較モジュールが ( 例えば図 2 A で説明した ) 少なくとも 1 つの演算増幅器を含み、第 1 の出力信号を生成すること ( 8 1 4 ) が、少なくとも 1 つの演算増幅器モジュールにおいて第 1 の出力信号を設定すること ( 8 2 2 ) を更に含む。

#### 【 0 0 7 5 】

[0084] 一部の実装形態では、方法 8 0 0 が、図 8 C に示すように第 1 の下位分類器から第 2 の下位分類器に第 1 の出力信号を伝送すること ( 8 2 4 ) を更に含む。例えば図 4 では、メモリラッチ 4 1 0 内にラッチされるコンパレータ W C 1 4 5 0 からの出力信号が、コンパレータ W C 2 4 5 2 及び加重入力モジュール 4 4 2 を含む第 2 の下位分類器に伝送される ( 破線として示す、入力 4 1 8 ) 。

10

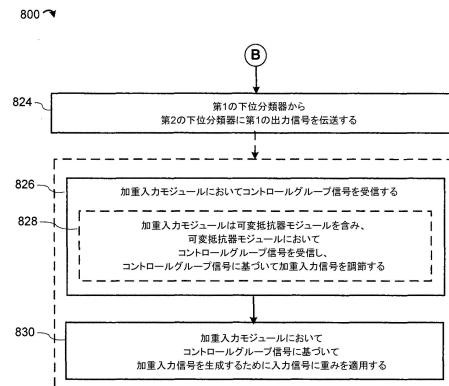

#### 【 0 0 7 6 】

[0085] 一部の実装形態では、方法 8 0 0 が、加重入力モジュールにおいてコントロールグループ信号を受信すること ( 8 2 6 ) を更に含む。かかる一部の実装形態では、加重入力モジュールが可変抵抗器モジュールを含み、この方法が可変抵抗器モジュールにおいてコントロールグループ信号を受信し ( 8 2 8 ) 、コントロールグループ信号に基づいて加重入力信号を調節することを含む。一部の実装形態では、方法 8 0 0 が加重入力モジュールにおいてコントロールグループ信号に基づいて加重入力信号を生成するために入力信号に重みを適用すること ( 8 3 0 ) を含む。コントロールグループ信号を受信し処理することについては図 5 に関して上記で説明した。例えば図 5 では、対応する加重入力モジュールによって消費される前に、コントロールグループ信号 5 0 2 が適用され、回路 5 0 4 、 5 0 6 、 5 0 8 内の重み値を調節する。

20

#### 【 0 0 7 7 】

[0086] 一部の実装形態では、図 8 D に示すように、第 1 の下位分類器が比較モジュールに結合されたメモリモジュールを含む ( 8 3 2 ) 。一部の実装形態では、メモリラッチ、コンパレータ、及び加重入力モジュールが下位分類器を含む。かかる一部の実装形態では、第 1 の下位分類器が比較モジュールからの第 1 の出力信号をメモリモジュールにおいて受信し記憶し ( 8 3 4 ) 、第 1 の出力信号を第 2 の下位分類器に与える。例えば図 4 では、一部の実装形態に従ってメモリラッチ 4 1 0 がコンパレータ W C 1 ( 4 5 0 ) に結合され、メモリラッチ 4 1 2 がコンパレータ W C 2 ( 4 5 2 ) に結合され、メモリラッチ 4 1 4 がコンパレータ W C N ( 4 5 4 ) に結合されている。

30

#### 【 0 0 7 8 】

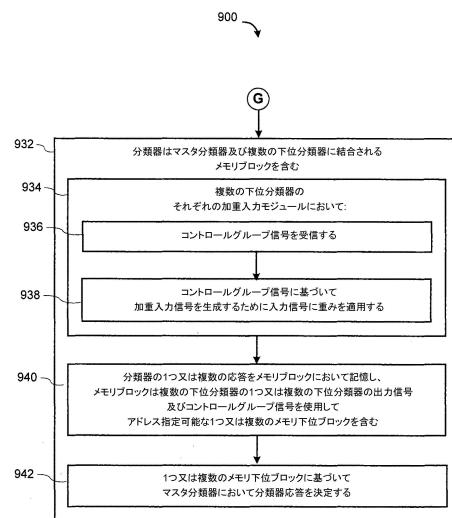

[0087] 図 9 A ~ 図 9 E は、分類器システムを使用して 1 つ又は複数のクロックサイクル中に 1 つ又は複数の入力信号を処理する方法 9 0 0 の流れ図の表現を示す。一部の実装形態によれば、分類器システムは複数の下位分類器及び複数の下位分類器に結合されたマスタ分類器を含み ( 9 0 2 ) 、複数の下位分類器は加重入力モジュール及び比較モジュールをそれぞれ含む。複数の下位分類器に結合されたマスタ分類器の例については図 6 に関して上記で論じた。方法 9 0 0 の一部の実装形態では、図 9 B の 9 2 0 に示すように、下位分類器のそれぞれが、他の任意の下位分類器の他の任意の個々のウィンドウ範囲と重複しない、下のウィンドウ範囲値と上のウィンドウ範囲値との間のそれぞれのウィンドウ範囲を有する。例えば図 3 では、対応する W V R が全て固有であるようにコンパレータ W C 1 の基準電圧 ( R L 1 3 0 2 及び R H 1 3 0 4 ) 、コンパレータ W C 2 の基準電圧 ( R L 2 3 0 6 及び R H 2 3 0 8 ) 、コンパレータ W C 3 の基準電圧 ( R L 3 3 1 0 及び R H 3 3 1 2 ) 、及びコンパレータ W C N の基準電圧 ( R L N 3 1 4 及び R H N 3 1 6 ) がそれぞれ設定される。一部の実装形態では W V R が重複しない。方法 9 0 0 の一部の実装形態では、図 9 C の 9 2 2 に示すように、分類器システムが複数の下位分類器に結合されたマルチブレクサモジュールを含む。かかる一部の実装形態では、方法 9 0 0 が、单一のクロックサイクル中に複数の下位分類器に入力信号の 1 つをマルチブレクサモジュールにおいて与えること ( 9 2 4 ) を含む。マルチブレクサ及び / 又は前処理モジュールの例は図 1

40

50

Aに関して上記で説明した。

**【0079】**

[0088] 一部の実装形態では、方法900が、各下位分類器において、加重入力信号を生成するためにそれぞれのクロックサイクルについてそれぞれの入力信号に加重入力モジュールにおいて重みを適用すること(908)を含む(906)。かかる一部の実装形態では、方法(900)が、各下位分類器において、比較モジュールの入力ラインにおける加重入力信号を比較モジュールにおいて受信すること(910)を更に含む。かかる一部の実装形態では、方法(900)が、比較モジュールの出力ラインにおける出力信号を比較モジュールにおいて生成すること(912)を更に含む。加重入力モジュールの一例については、一部の実装形態に従って図4に関して上記で説明した。

10

**【0080】**

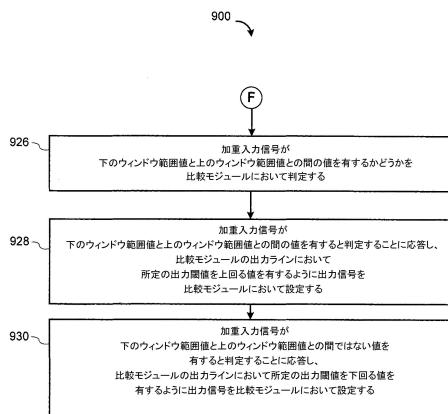

[0089] 一部の実装形態では、図9Dに示すように、出力信号を比較モジュールにおいて生成すること(912)は、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有するかどうかを比較モジュールにおいて判定すること(926)、加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間の値を有すると判定することに応答して、比較モジュールの出力ラインにおいて所定の出力閾値を上回る値を有するように出力信号を比較モジュールにおいて設定すること(928)、及び加重入力信号が下のウィンドウ範囲値と上のウィンドウ範囲値との間ではない値を有すると判定することに応答して、比較モジュールの出力ラインにおいて所定の出力閾値を下回る値を有するように出力信号を比較モジュールにおいて設定すること(930)を含む。比較モジュールの動作については上記の図8Bに関して上記で説明しており、一部の実装形態によれば図9Dに示す操作に当てはまる。

20

**【0081】**

[0090] 再び図9Aを参照し、一部の実装形態では、方法900がマスタ分類器において、1つ又は複数のクロックサイクル中に複数の下位分類器のそれから出力信号のそれぞれを受信すること(916)を含む(914)。かかる一部の実装形態では、方法900が、所定の出力閾値を上回る値を有するそれぞれの出力信号を生成する複数の下位分類器の部分集合に基づいて分類器応答をマスタ分類器において決定すること(918)を更に含む。

30

**【0082】**

[0091] 方法900の一部の実装形態では、分類器がマスタ分類器及び/又は複数の下位分類器に結合されたメモリブロックを含む(932)。かかる一部の実装形態では、この方法が、複数の下位分類器のそれぞれの加重入力モジュールにおいて(934)、コントロールグループ信号を受信すること(936)、及びコントロールグループ信号に基づいて加重入力信号を生成するために入力信号に重みを適用すること(938)を更に含む。この方法は、分類器の1つ又は複数の応答をメモリブロックにおいて記憶すること(940)を更に含み、メモリブロックは複数の下位分類器の1つ又は複数の下位分類器の出力信号及びコントロールグループ信号を使用してアドレス指定可能な1つ又は複数のメモリ下位ブロックを含む。この方法は、1つ又は複数のメモリ下位ブロックに基づいてマスタ分類器において分類器応答を決定すること(942)を更に含む。マスタ分類器の詳細については、一部の実装形態に従って図6に関して上記で論じた。更に図6に関する解説の中で示したように、一部の実装形態によれば、分類器応答を決定するためにEMEMブロックの出力(例えば出力624、626、及び628)を使用する。

40

**【0083】**

[0092] 図8A～図8D及び図9A～図9Eの中の操作を記載した特定の順序は例に過ぎず、記載した順序は操作を実行可能な唯一の順序であることを示すことは意図しないことを理解すべきである。本明細書に記載の操作を並べ替える様々なやり方を当業者なら理解されよう。加えて、方法800に関して記載した他のプロセスの詳細が、図9A～図9Eに関して上記で説明した方法900にも類似のやり方で適用できることに留意すべきである。

50

**【 0 0 8 4 】**

[0093] 様々な図面の一部は幾つかの論理段階を特定の順序で示すが、順序に依存しない段階は順序を変更することができ、他の段階は組み合わせ又は引き離すことができる。幾つかの順序変更又は他のグループ化を具体的に言及したが、他のものも当業者にとって明白であり、そのため本明細書で示した順序付け及びグループ化は代替形態の網羅的な一覧ではない。更に、それらの段階はハードウェア、ファームウェア、ソフトウェア、又はその任意の組み合わせによって実装できることを理解すべきである。

**【 0 0 8 5 】**

[0094] 上記の説明は特定の実装形態に関して説明目的で記載した。但し上記の例示的な解説は、網羅的であることも、特許請求の範囲を開示した正確な形態に限定することも意図しない。上記の教示に照らして多くの修正及び改変が可能である。実装形態は、特許請求の範囲の根底を成す原理及びその実用的応用を最も良く説明し、それにより考えられる特定の用途に適した様々な修正と共に当業者が実装形態を最も上手く利用できるようにするように選んだ。

10

20

30

40

50

【図面】

【図 1 A】

【図 1 B】

10

20

【図 2 A】

【図 2 B】

$$O_{WC} = \text{高} = 1$$

$$/O_{WC} = \text{低} = 0$$

$$(R_L < I_{WC} < R_H)$$

$$(I_{WC} < R_L) \text{ 又は } (I_{WC} > R_H)$$

30

40

Figure 2B

50

【図3】

【 四 4 】

【 四 5 】

〔 図 6 〕

10

20

30

40

50

【図 7】

【図 8 A】

10

20

【図 8 B】

【図 8 C】

30

40

50

【図 8 D】

【図 9 A】

10

20

【図 9 B】

【図 9 C】

30

40

50

【図9D】

【図9E】

10

20

30

40

50

---

フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

エヌ7, テラ コタ, サイドロード 27 16282

審査官 多賀 実

(56)参考文献

米国特許出願公開第2018/0157968 (U.S., A1)

SILVAN-CARDENAS, Jose Luis ほか, "Representing geographical objects with scale-induced indeterminate boundaries: A neural network-based data model", ResearchGate [online], 2009年03月, インターネット URL : [https://www.researchgate.net/publication/220650394\\_Representing\\_geographical\\_objects\\_with\\_scale-induced\\_indeterminate\\_boundaries\\_A\\_neural\\_network-based\\_data\\_model](https://www.researchgate.net/publication/220650394_Representing_geographical_objects_with_scale-induced_indeterminate_boundaries_A_neural_network-based_data_model), [2021年10月29日検索]

(58)調査した分野 (Int.Cl., DB名)

G 06 N 3 / 00 - 3 / 12