(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7108166号

(P7108166)

(45)発行日 令和4年7月28日(2022.7.28)

(24)登録日 令和4年7月20日(2022.7.20)

(51)国際特許分類

G 0 5 F 1/56 (2006.01)

F I

G 0 5 F

1/56

3 1 0 F

請求項の数 11 (全11頁)

|                   |                                  |          |                                                                                                                                  |

|-------------------|----------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2019-537100(P2019-537100)      | (73)特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 7 5 2 6 5<br>- 5 4 7 4 ダラス メイル ステイション<br>3 9 9 9 ピーオーボックス 6 5 5 4 7 4 |

| (86)(22)出願日       | 平成30年1月8日(2018.1.8)              |          |                                                                                                                                  |

| (65)公表番号          | 特表2020-505679(P2020-505679<br>A) |          |                                                                                                                                  |

| (43)公表日           | 令和2年2月20日(2020.2.20)             |          |                                                                                                                                  |

| (86)国際出願番号        | PCT/US2018/012803                | (74)代理人  | 230129078<br>弁護士 佐藤 仁                                                                                                            |

| (87)国際公開番号        | WO2018/129459                    | (72)発明者  | ヴァディム ヴァレリエヴィッチ イワノフ<br>アメリカ合衆国 8 5 7 4 7 アリゾナ州<br>トゥーソン, フリーマン ロード 5 1<br>9 5 エス                                                |

| (87)国際公開日         | 平成30年7月12日(2018.7.12)            |          | サハナ スリラジ<br>アメリカ合衆国 7 5 2 0 2 テキサス州<br>ダラス, エイビーティー 5 0 8, メイ                                                                    |

| 審査請求日             | 令和3年1月7日(2021.1.7)               |          | 最終頁に続く                                                                                                                           |

| (31)優先権主張番号       | 15/400,976                       |          |                                                                                                                                  |

| (32)優先日           | 平成29年1月7日(2017.1.7)              |          |                                                                                                                                  |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                                                  |

(54)【発明の名称】 低ドロップアウトレギュレータを補償する方法及び回路要素

## (57)【特許請求の範囲】

## 【請求項1】

低ドロップアウトレギュレータ(LDO)であって、

前記LDOの出力に結合される第1の入力と、基準電圧に結合される第2の入力と、出力とを含む誤差増幅器であって、前記LDOの出力電圧と前記基準電圧との間の差に比例する電圧を出力するように動作し得、前記誤差増幅器の出力に応答して設定されるテール電流を有する、前記誤差増幅器と、

前記誤差増幅器に結合される入力と、前記LDOの出力に結合される出力とを含む第2の増幅器と、

前記誤差増幅器の出力と前記第2の増幅器の入力との間に結合される差動増幅器である利得ブースト増幅器であって、前記LDOの出力上の負荷ステップに応答して前記LDOのDC利得を変化するように動作し得る、前記利得ブースト増幅器と、

前記差動増幅器の入力の間に結合されるフィルタと、

を含む、LDO。

## 【請求項2】

低ドロップアウトレギュレータ(LDO)であって、

前記LDOの出力に結合される第1の入力と、基準電圧に結合される第2の入力と、出力とを含む誤差増幅器であって、前記LDOの出力電圧と前記基準電圧との間の差に比例する電圧を出力するように動作し得、前記誤差増幅器の出力に応答して設定されるテール電流を有する、前記誤差増幅器と、

前記誤差増幅器に結合される入力と、前記 L D O の出力に結合される出力とを含む第 2 の増幅器と、

前記誤差増幅器の出力と前記第 2 の増幅器の入力との間に結合される利得ブースト増幅器であって、前記 L D O の出力上の負荷ステップに応答して前記 L D O の D C 利得を変化させるように動作し得る、前記利得ブースト増幅器と、

前記誤差増幅器の出力に結合される共通ゲート増幅器であって、トランジスタに結合される出力を含み、前記誤差増幅器のテール電流を制御するように動作し得る、前記共通ゲート増幅器と、

を含む、L D O。

【請求項 3】

請求項 1 又は 2 に記載の L D O であって、

前記利得ブースト増幅器が、前記 L D O の出力上の負荷ステップに応答して前記誤差増幅器の D C 利得を減少させるように更に動作し得る、L D O。

【請求項 4】

請求項 1 又は 2 に記載の L D O であって、

前記出力電圧と前記基準電圧との間の差を示す前記誤差増幅器に応答して前記テール電流が増加され、前記出力電圧と前記基準電圧とが実質的に同じであることを示す前記誤差増幅器に応答して前記テール電流が減少される、L D O。

【請求項 5】

請求項 1 又は 2 に記載の L D O であって、

前記誤差増幅器が、差動増幅器の入力に結合される差動出力を更に含み、前記テール電流が前記差動増幅器の出力に応答して設定される、L D O。

【請求項 6】

請求項 1 又は 2 に記載の L D O であって、

前記利得ブースト増幅器が、前記第 2 の増幅器を介する電流フローをレギュレートするように更に動作し得る、L D O。

【請求項 7】

低ドロップアウトレギュレータ ( L D O ) であって、

前記 L D O の出力に結合される第 1 の入力と、基準電圧に結合される第 2 の入力とを含む誤差増幅器であって、前記 L D O の出力電圧と前記基準電圧との差に比例する電圧を出力するように動作可能である、前記誤差増幅器と、

前記誤差増幅器に結合される入力と、前記 L D O の出力に結合される出力とを含む第 2 の増幅器と、

前記誤差増幅器の出力と前記第 2 の増幅器の入力との間に結合される利得ブースト増幅器であって、前記 L D O の出力上の負荷ステップに応答して前記 L D O の D C 利得を変化させるように動作可能である、前記利得ブースト増幅器と、

前記 L D O への電圧入力と前記 L D O の出力との間に結合されるパストランジスタであって、前記利得ブースト増幅器の第 1 の入力と前記第 2 の増幅器の第 1 の出力とに結合されるゲートと、ドレインと、ソースとを有する、前記パストランジスタと、

を含む、L D O。

【請求項 8】

請求項 7 に記載の L D O であって、

前記第 2 の増幅器が、前記利得ブースト増幅器の第 2 の入力に結合される第 2 の出力を更に含む、L D O。

【請求項 9】

低ドロップアウトレギュレータ ( L D O ) であって、

入力電圧に結合するための入力と、

出力電圧を提供するための出力と、

前記入力と前記出力との間に結合されるパストランジスタと、

前記出力電圧を基準電圧と比較し、前記出力電圧と前記基準電圧との間の差に比例する誤

10

20

30

40

50

差信号を生成するように動作し得る誤差増幅器と、

前記誤差信号に応答して前記誤差増幅器の利得を制御するための回路要素と、

前記パストランジスタのゲートへの出力を含む第2の増幅器と、

前記第2の増幅器の利得を制御するための電流レギュレータと、

前記誤差増幅器と前記第2の増幅器との間に結合される利得ブースト増幅器であって、前記電流レギュレータを制御する、前記利得ブースト増幅器と、

前記利得ブースト増幅器の差動入力の間に結合されるフィルタと、

を含む、LDO。

【請求項10】

請求項9に記載のLDOであって、

10

前記電流レギュレータが、前記利得ブースト増幅器の出力に結合されるゲートを有するトランジスタである、LDO。

【請求項11】

低ドロップアウトレギュレータ(LDO)であって、

LDO入力と、

LDO出力と、

第1のEA入力と第2のEA入力と第1のEA出力と第2のEA出力とを含む誤差増幅器(EA)であって、

第1の電流端子と、前記第1のEA出力に結合される第2の電流端子と、前記第1のEA入力に結合される第1の制御端子とを有する第1のトランジスタと、

20

前記第1の電流端子に結合される第3の電流端子と、前記第2のEA出力に結合される第4の電流端子と、前記LDO出力に結合される第2の制御端子とを有する第2のトランジスタと、

を含む、前記誤差増幅器と、

第5の電流端子と、第6の電流端子と、前記第5の電流端子に結合される第3の制御端子とを有する第3のトランジスタと、

第1の供給電位を有する第1の供給レールに結合される第7の電流端子と、前記第1の供給電位と異なる第2の供給電位を有する第2の供給レールに結合される第8の電流端子と、バス制御端子とを有するパストランジスタと、

前記第2の電流端子に結合される第1のGBA入力と、前記第4の電流端子に結合される第2のGBA入力と、GBA出力とを含む利得ブースト増幅器(GBA)であって、前記第3の制御端子における電位を前記バス制御端子における電位に追随させるように動作可能である、前記利得ブースト増幅器と、

30

を含む、LDO。

【発明の詳細な説明】

【技術分野】

【0001】

電力管理は、特に、回路及び電力供給がシステムオンチップ(SoC)回路などの単一のチップ上に位置する場合に、幾つかの電力供給を有する回路にとって問題である。これらの回路の幾つかは、一つ又は複数のDC-DCコンバータによって電力供給され、その後、多数の低ドロップアウトレギュレータ(LDO)が続き、各LDOは電力ドメインに関連する。時には、単一のSoC回路が複数の電力ドメインを有する。これらの電力ドメインは、デジタル信号処理コア、メモリ回路の幾つかのバンク、アナログユニット、ブルートゥース無線、及びオーディオユニットを含み得る。

40

【背景技術】

【0002】

LDOの負荷ステップは、LDOによって電力供給される負荷が変化するときに生じる。負荷なしからフル負荷までの負荷ステップ状況の間、LDOによる電圧出力の精度を維持することは、電力ドメインの適切なオペレーションのために重要である。負荷ステップの間の精度を維持する方法の一つは、各LDOに結合される外部負荷コンデンサを含むこと

50

によるものである。各回路上の LDO があまりに多くなり、回路が小さくなると、外部コンデンサのサイズ及びコストのため、各 LDO の外部負荷コンデンサを利用することは実用的ではなくなる。

【発明の概要】

【0003】

記載される例において、低ドロップアウトレギュレータが、第 1 の入力及び第 2 の入力を有するエラー増幅器を含む。第 1 の入力は LDO の出力への結合のためのものであり、第 2 の入力は、基準電圧に結合するためのものである。エラー増幅器は、出力電圧と基準電圧との間の差に比例する電圧を有する出力を有する。第 2 の増幅器が、エラー増幅器と LDO の出力との間に結合される。利得ブースト増幅器が、エラー増幅器と第 2 の増幅器との間に結合される。利得ブースト増幅器は、LDO の DC 利得を、出力上の負荷ステップに応答して増加させる。

10

【図面の簡単な説明】

【0004】

【図 1】低ドロップアウトレギュレータ (LDO) の概略図である。

【0005】

【図 2】A B 級入力段を備え、補償を備えない LDO の概略図である。

【0006】

【図 3】補償を有する例示の LDO のブロック図である。

20

【0007】

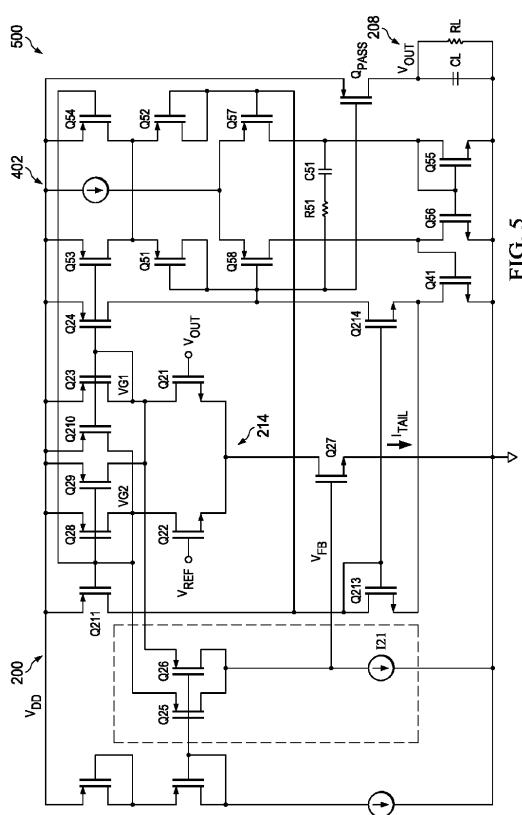

【図 4】入れ子にされた利得ブースト増幅器を有する例示の LDO の概略図である。

【0008】

【図 5】利得ブースト増幅器が入れ子にされた例示の LDO の詳細な概略図である。

【0009】

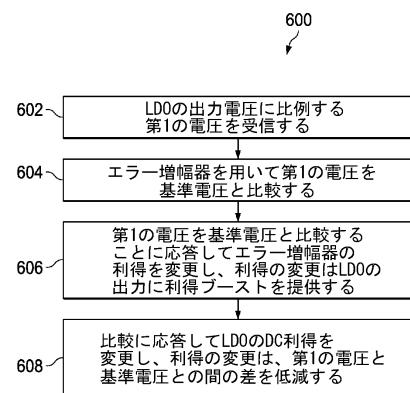

【図 6】LDO を補償する方法を説明するフローチャートであり、LDO は、第 2 の増幅器に結合されるエラー増幅器を有する。

30

【発明を実施するための形態】

【0010】

図面において、同様の参照数字は同様の又は等価の要素を示す。幾つかの行為又は事象は、異なる順で及び / 又は他の行為又は事象と同時に起こり得るので、行為又は事象の例示される順は限定的ではない。また、幾つかの例示される行為又は事象が、例示の実施例に従った手法を実装するために任意選択であり得る。

30

【0011】

回路が集積化されていくにつれて、回路は、互いに独立して又は少なくとも部分的に互いに独立して動作することが多い、多くの異なるデバイス、構成要素、及びサブ回路を有する。本明細書において用いられるように、回路という用語は、アナログ回路又は制御回路など、回路機能を実施する能動及び / 又は受動要素の集まりを含み得る。回路という用語はまた、全ての回路要素が共通基板上に製造される集積回路を含み得る。これらの異なるシステムは通常、それら自体の電源又は電力ドメインを必要とし、多くのシステムは複数の電力ドメインを必要とする。これらの異なるシステムの例には、プロセッサ、メモリデバイス、無線トランスマッタ及びレシーバ、並びにオーディオユニットが含まれる。集積回路などの回路は、これらのシステムの幾つかを有し得、1 つ又は 2 つの入力電圧のみのための入力を有し得る。これらの入力電圧は、複数の低ドロップアウトレギュレータ (LDO) に電力を提供する DC - DC コンバータに結合され、各 LDO は、システムの各々に電力を提供する。幾つかの場合において、単一の回路が、50 個程度の LDO を有し得る。

40

【0012】

LDO は、高入力電圧を一層低い出力電圧に変換及びレギュレートする。ドロップアウト電圧は、レギュレートされた出力電圧を維持するために必要なヘッドルームの量である。したがって、ドロップアウト電圧は、出力電圧のレギュレーションを維持するために必要

50

な入力電圧と出力電圧との間の最小電圧差分である。LDO内のパス要素を横切る電圧降下を引いた入力電圧は、出力電圧に等しい。例えば、1.0Vのドロップアウトを有する3.3Vのレギュレータは、入力電圧が少なくとも4.3Vであることを必要とする。LDOに関する別の例示の応用例は、3.6Vのリチウムイオンバッテリーから3.3Vを生成するためのものであり、これは、300mVより小さい更に一層低いドロップアウト電圧を必要とする。

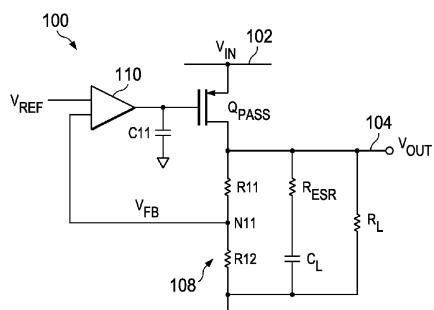

#### 【0013】

図1はLDO100の概略図である。LDO100は、LDO100のオペレーションの間、入力102において入力電圧VINを受け取る入力102を有する。出力104が、LDO100のオペレーションの間存在する出力電圧VOUTを提供する。パストランジスタQPASSが、入力102と出力104との間に結合される。パストランジスタQPASSのパス電圧が、入力電圧VINと出力電圧VOUTとの間の差である。LDO100のオペレーションを維持するための最小パス電圧は、ドロップアウト電圧である。

10

#### 【0014】

抵抗器R11とR12で構成される分圧器108が、出力104と、図1の例において接地ノードである共通ノードとの間に結合される。ノードN11が、抵抗器R11とR12との間に位置し、LDO100のオペレーションの間存在するフィードバック電圧VFBを有する。負荷コンデンサCLが、出力104と接地ノードとの間に結合される。負荷コンデンサCLの等価直列抵抗(ESR)は抵抗器RESRとして示されている。また、負荷抵抗RLが、出力104と接地ノードとの間に結合されている。

20

#### 【0015】

パストランジスタQPASSのゲートは、パスコンデンサC11と差動増幅器110の出力とに結合される。差動増幅器110は、基準電圧VREFに結合される第1の入力と、ノードN11に結合される第2の入力とを有し、これは、LDO100のオペレーションの間存在するフィードバック電圧VFBを有する。差動増幅器110の出力は、基準電圧VREFとフィードバック電圧VFBとの間の差に比例し、パストランジスタQPASSのゲートを駆動するように働く。フィードバック電圧VFBが基準電圧VREFより小さい場合、差動増幅器110は、出力電圧VOUTを増大させるためパストランジスタQPASSのゲートを一層強く駆動させる。同様に、フィードバック電圧VFBが基準電圧VREFより大きい場合、差動増幅器110は、パストランジスタQPASSのゲートに対する駆動を低減し、これにより、出力電圧VOUTが低減する。

30

#### 【0016】

LDO100などの従来のLDOは、安定性/補償のため、なんらかの最小負荷静電容量CL及び/又は最小ESRを必要とする。例えば、LDO100が負荷ステップを受けると、すなわち、LDO100の出力104に結合される負荷が変化すると、有意な整定時間を有する過渡現象が生成され得る。従来のLDOの傾向は、最大負荷電流の10パーセントより小さく制限される静止電流など、より小さい静止電流のためである。最大負荷電流は、パストランジスタQPASSを通過し得る最大電流である。これらの低静止電流は、他の要因と共に、負荷ステップの間の過渡応答時間をミリ秒範囲にするが、これは多くの応用例において許容可能ではない。負荷コンデンサCLのより大きな負荷静電容量が、LDO100の補償を改善することによって、過渡整定時間を低減する。しかしながら、シリコンダイエリアの制約に起因して、オンチップ負荷コンデンサは静電容量が低く、その結果、より長い過渡整定時間となり、これは多くの応用例において許容可能ではない。この過渡問題を解決するには、かさばるオフチップ負荷コンデンサの利用が必要であり、これは、LDO100が位置する回路のボードエリア及び構成要素数を増大させる。負荷静電容量を用いて又は用いずに動作し得、負荷ステップに応答して非常に速い反応時間を持ついくつかのLDOが開発されている。しかしながら、これらの高速応答LDOは安定性のために低利得であり、その出力電圧において低精度の欠点を有する。これらのLDOの利得を増加させることは、出力電圧の精度を増大させるが、安定性を減少させる欠点を有し、これは負荷ステップの間の安定性の問題につながる。

40

50

## 【0017】

本願において記載される LDO は、高利得での負荷ステップ状況下の補償によって安定性を提供し、これは高精度をもたらす。高利得及び高安定性が、負荷又は補償コンデンサを付加することなく達成される。LDO は、入力電圧及び出力電圧の間の差に応じて異なる利得を提供する。LDO 内に入れ子にされる利得ブースト増幅器が、負荷ステップ後の LDO の直流精度を増大させるように働く。幾つかの異なる回路概略図が、LDO の例として本願において説明されている。回路の変形が本願において説明される LDO の機能を実施することができるので、これらの概略図は限定的ではない。

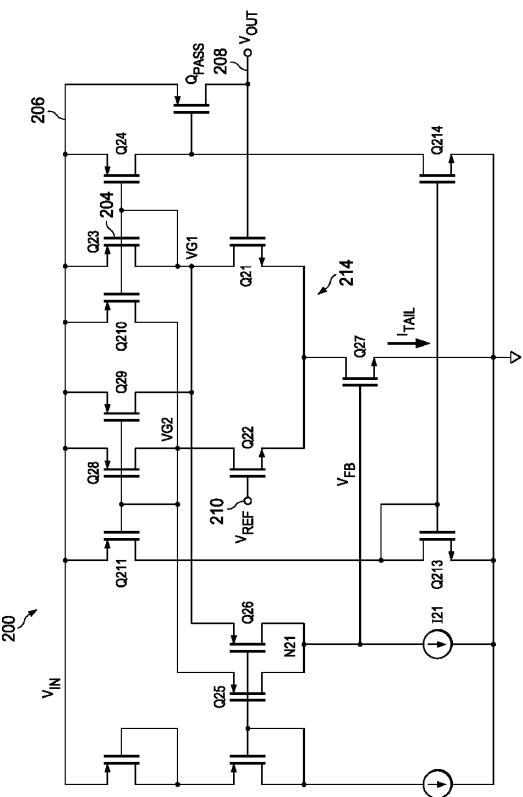

## 【0018】

図2は、AB級入力ステージ204を有し、補償を有さない、LDO200の概略図である。LDO200は、本願において記載される補償回路に結合され得る回路要素の一例である。LDO200は、LDO200のオペレーションの間、入力電圧VINに結合される入力206を有する。LDO200は、LDO200のオペレーションの間、出力208において出力電圧VOUTを生成し、レギュレートする。基準入力210が、LDO200のオペレーションの間存在する基準電圧VREFに結合される。エラー電圧VE(図2には示されていない)が、基準電圧VREFと出力電圧VOUTとの間の差である。トランジスタQ21及びQ22が、エラー増幅器214の入力を形成し、トランジスタQ22のゲートは基準電圧VREFに結合され、トランジスタQ21のゲートは出力208に結合される。幾つかの例において、出力電圧VOUTは分圧器(図示せず)を介してエラー増幅器214に結合されるので、エラー増幅器214によって受け取られる電圧は、出力電圧VOUTに比例するが、出力電圧VOUTに等しくない。エラー増幅器214は、基準電圧VREFと出力電圧VOUTによって見られるように、高入力インピーダンスを有する。エラー増幅器214の出力は、トランジスタQ21及びQ22のドレイン上の差動電圧である。トランジスタQ21及びQ22のドレイン上の電圧は、個別にVG1及びVG2と呼ばれる。パストランジスタQPASSのゲートは、第2の増幅器の一部を形成するトランジスタQ23及びQ24を介してエラー増幅器214の出力によって駆動される。

## 【0019】

エラー増幅器214の出力は、共通ゲート増幅器を形成するトランジスタQ25及びQ26のソースに結合される。従って、電圧VG1及びVG2は、LDO200オペレーションの間トランジスタQ25及びQ26のソースに存在する。トランジスタQ25及びQ26のドレインは、電流源I21に結合されるノードN21に結合されている。ノードN21は、トランジスタQ27のゲートにも結合され、トランジスタQ27のドレインが、エラー増幅器214におけるトランジスタQ21及びQ22のソースに結合される。ノードN21及びトランジスタQ27のゲート上の電圧は、フィードバック電圧VFBである。トランジスタQ27のソースは、図2に示すような接地など、ノードに結合される。トランジスタQ27を流れる電流は、エラー増幅器214のテール電流ITA1Lである。本明細書において用いられるようにテール電流ITA1Lという用語は、エラー増幅器214におけるトランジスタQ21及びQ22の差動対のソース端子の組み合わされた電流を指す。トランジスタQ23、Q24、Q28、及びQ211は、LDO200の対称的電流ミラー負荷である。トランジスタQ213及びQ214は、トランジスタQ211及びQ24の電流ミラーとして働く。

## 【0020】

パストランジスタQPASSのゲートは、本願において説明される第2の増幅器の一部として機能するトランジスタQ24を介してエラー増幅器214の出力によって駆動される。パストランジスタQPASSのゲートにおける電圧が、パストランジスタQPASSのソースドレイン抵抗を変化させる。出力208上の負荷ステップから生じるなどの遷移状況が、基準電圧VREFと出力電圧VOUTとの間の差であるエラー電圧VEを監視することによって検出される。エラー電圧VEが無視し得るとき、電圧VG1及びVG2は実質的に同じであり、これは、トランジスタQ25及びQ26を介する電流を実質的に同じ

10

20

30

40

50

にする。したがって、トランジスタ Q 2 5 及び Q 2 6 の各々を介する電流は、電流源 I 2 1 によって生成される電流の半分である。これにより、エラー増幅器 2 1 4 におけるトランジスタ Q 2 1 及び Q 2 2 を流れる電流が実質的に等しく設定される。エラー増幅器 2 1 4 は、これらの状況では休止状態で動作する。電圧 V G 1 及び V G 2 は、入力段電流を設定することによって、エラー増幅器 2 1 4 における電流を設定する。

### 【 0 0 2 1 】

エラー電圧 V E が上昇するとき、V G 1 と V G 2 の電圧は異なる。エラー電圧 V E が所定の値より大きいとき、V G 1 及び V G 2 のうち小さい方の電圧が、対応するトランジスタ Q 2 5 及び Q 2 6 において高い方の電流をトリガし、これがフィードバック電圧 V F B を増大させる。その結果、エラー増幅器 2 1 4 は静止状態のままである。フィードバック電圧 V F B のこの増大は、トランジスタ Q 2 7 を流れるテール電流 I T A I L をエラー電圧 V E に比例して増大させる。そのため、エラー増幅器 2 1 4 におけるテール電流 I T A I L は、エラー電圧 V E に比例して増加し、高速過渡応答を提供する。より具体的には、テール電流 I T A I L のこの変化が、負荷ステップの間の過渡現象を最小限に抑えるように、負荷ステップの間、パストランジスタ Q P A S S のゲートをより速く移動させるために、入力段においてより高い電流駆動をもたらす。L D O 2 0 0 における非線形性が、これらの状況の間、トランジスタ Q 2 8 / Q 2 9 及び Q 2 3 / Q 2 1 0 の組み合わせによって提供される。トランジスタが 4 の比を有する幾つかの例において、100 mV のエラー電圧 V E が、1000 倍のテール電流増大を有する。

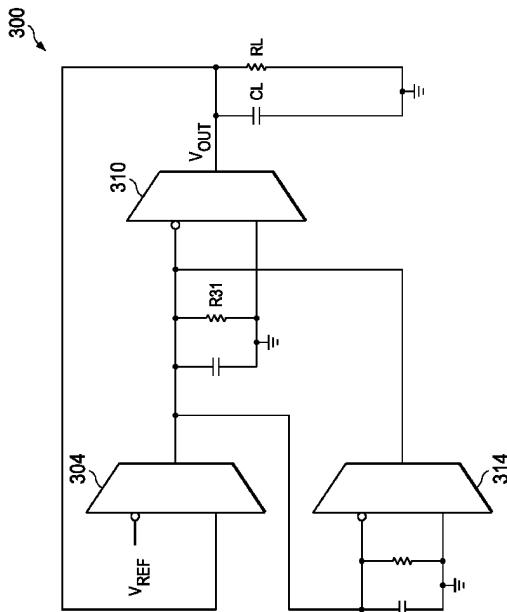

### 【 0 0 2 2 】

図 3 は、補償が入れ子にされた L D O 3 0 0 のブロック図である。L D O 3 0 0 のブロック図は、L D O 3 0 0 の最終回路に含まれても含まれなくてもよい受動構成要素を含む。図 3 に示される受動構成要素の幾つかは、L D O 3 0 0 における増幅器の入力及び出力インピーダンスを表す。L D O 3 0 0 は、図 2 のエラー増幅器 2 1 4 の入力段 2 0 4 を含む増幅器 3 0 4 を有する。第 2 の増幅器 3 1 0 が、パストランジスタ Q P A S S (図示せず) 及び関連する構成要素を含む。増幅器 3 0 4 及び 3 1 0 の組み合わせは、図 2 の L D O 2 0 0 を構成する。補償は、本明細書に記載するように抵抗器 R 3 1 の抵抗を制限することによって、増幅器 3 0 4 として示される入力段 2 0 4 の電圧利得を低減することによって達成される。幾つかの例において、抵抗 R 3 1 はパストランジスタ Q P A S S のゲートに結合される抵抗である。抵抗器 R 3 1 の抵抗を制限することが、L D O 3 0 0 の全体的な利得を低減し、その結果、直流精度は低くなるが、L D O 3 0 0 は安定化する。L D O 3 0 0 の電圧利得を回復することは、段を入れ子にし、上述したエラー増幅器 2 1 4 など、現存するすでに安定している増幅器の利得をブーストすることを含む。増幅器段を入れ子にすることは、従来の応用例で行われるように利得段を直列にカスケード接続するのではなく、L D O 3 0 0 で行われる。L D O 3 0 0 における増幅器を入れ子にすることは、直流精度のため利得を回復する利得ブースト増幅器 3 1 4 によって成される。増幅器 3 1 4 は、その入力で電圧を追跡し、電圧 V O U T が電圧 V R E F に等しいことを保証して、直流精度を達成する。

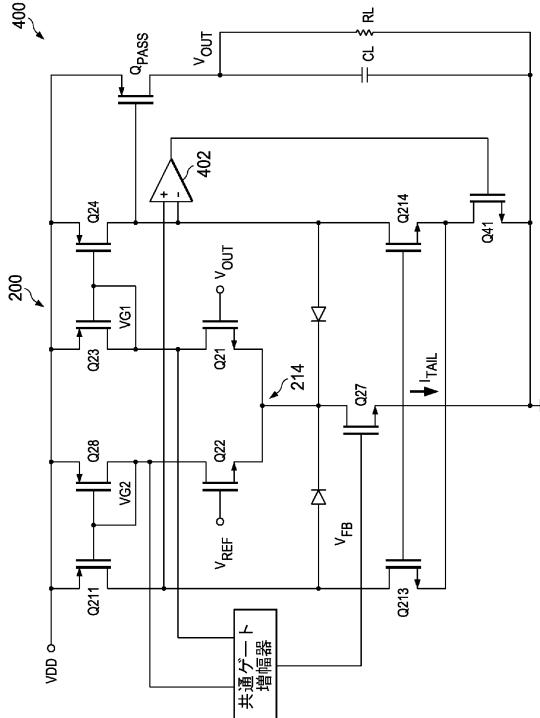

### 【 0 0 2 3 】

図 4 は利得ブースト増幅器が入れ子にされる L D O 4 0 0 の概略図である。L D O 4 0 0 は、図 2 の L D O 2 0 0 と同じ構成要素の多くを有し、これらの構成要素に適用される同じ参照符号を有する。L D O 4 0 0 は、トランジスタ Q 4 1 のゲートに結合される出力を有する利得ブースト増幅器 4 0 2 を含む。トランジスタ Q 4 1 は、トランジスタ Q 2 1 3 及び Q 2 1 4 のソースと接地ノードとの間に結合される。したがって、トランジスタ Q 2 1 3 及び Q 2 1 4 を介する電流フローは、増幅器 4 0 2 の出力に基づく。増幅器 4 0 2 の入力は、トランジスタ Q 2 1 3 のゲート及びトランジスタ Q 2 1 4 のドレインに結合され、トランジスタ Q 2 1 4 のドレインは、パストランジスタ Q P A S S のゲートに結合される。利得ブースト増幅器 4 0 2 は、その入力が常に互いを追跡することを保証するトランジスタ Q 2 1 3 のゲートにおける電圧及びパストランジスタ Q P A S S のゲートにおける電圧が互い

10

20

30

40

50

追跡することを保証する。この追跡は、トランジスタQ41のドレイン電流をレギュレートすることによって達成され、これは、増幅器402の出力によってトランジスタQ41のゲートに提供される駆動によって達成される。

【0024】

図5は、利得ブースト増幅器402が入れ子にされる例示のLDO500の概略図である。LDO500は、図2のLDO200を含み、補償及び負荷安定性を提供する図4の利得ブースト増幅器402が付加されている。LDO500は、図2のLDO200と実質的に同じ回路要素を含み、利得ブースト増幅器402が付加されている。LDO500における補償は、エラー増幅器214の電圧利得を制限することによって達成され、これは、パストランジスタQPASSのゲートにおける抵抗を制限することによって達成される。

10

【0025】

図5に示されるように、トランジスタQ51及びQ52は、トランジスタQ53及びQ54を介する電流の一部によってバイアスされ、これはエラー増幅器214の下側電圧利得を達成する。エラー増幅器214における電圧利得が小さい場合、LDO500の全体的な利得は、許容可能な負荷レギュレーションに充分でない場合がある。トランジスタQ41及びQ55～Q58は、利得ブースト増幅器を形成する。この利得ブースト増幅器により、パストランジスタQPASS及びトランジスタQ213のゲートにおける電圧は互いに追跡する。

【0026】

幾つかの例において、利得ブースト増幅器402は、LDO500の安定性に影響を与えないように、抵抗器R51及びコンデンサC51の利用によって減速されるように設計される。例えば、抵抗器R51及びコンデンサC51は、増幅器402を減速させるフィルタを形成する。幾つかの例において、フィルタはLDO500に含まれていない。

20

【0027】

図6は、LDOが第2の増幅器に結合されるエラー増幅器を有するLDOを補償する方法を説明するフローチャート600である。フローチャート600の工程602は、LDOの出力電圧に比例する第1の電圧を受け取ることを含む。工程604は、エラー増幅器を用いて第1の電圧を基準電圧と比較することを含む。工程606は、第1の電圧を基準電圧と比較することに応答してエラー増幅器の利得を変更することを含み、利得の変更はLDOの出力に利得ブーストを提供する。工程608は、比較に応答してLDOのDC利得を変更することを含み、利得の変更は、第1の電圧と基準電圧との間の差を低減する。

30

【0028】

本発明の特許請求の範囲内で、説明した例示の実施例に改変が成され得、他の実施例が可能である。

40

50

## 【図面】

## 【図 1】

FIG. 1

(従来技術)

## 【図 2】

FIG. 2

10

20

30

40

## 【図 3】

FIG. 3

## 【図 4】

FIG. 4

10

20

30

40

50

【図5】

【 四 6 】

FIG. 6

10

20

30

40

50

---

フロントページの続き

ン ストリート 1200

審査官 遠藤 尊志

(56)参考文献 特開2010-079653 (JP, A)

特開2016-162097 (JP, A)

国際公開第2016/202398 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

G 05 F 1 / 00 - 7 / 00