(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-21556

(P2004-21556A)

(43) 公開日 平成16年1月22日(2004.1.22)

(51) Int.Cl.<sup>7</sup>

F 1

テーマコード(参考)

**G06F 11/16**

G06F 11/16

310C

5B034

**G06F 3/06**

G06F 3/06

304N

5B042

**G06F 11/20**

G06F 11/20

310E

5B065

**G06F 11/30**

G06F 11/30

310H

審査請求 未請求 請求項の数 21 O L (全 18 頁)

(21) 出願番号

特願2002-174944 (P2002-174944)

(22) 出願日

平成14年6月14日 (2002. 6. 14)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(74) 代理人 100071283

弁理士 一色 健輔

(74) 代理人 100084906

弁理士 原島 典孝

(74) 代理人 100098523

弁理士 黒川 恵

(74) 代理人 100112748

弁理士 吉田 浩二

(74) 代理人 100110009

弁理士 青木 康

最終頁に続く

(54) 【発明の名称】記憶制御装置およびその制御方法

## (57) 【要約】 (修正有)

【課題】内部通信路を用いて稼動情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に移動情報の監視機能を実現する記憶制御装置を提供する。

【解決手段】本発明の記憶制御装置は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、を備える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力をを行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする記憶制御装置。

**【請求項 2】**

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示 10

を送信する複数の制御部と、

前記制御部間におけるデータ入出力指示及びデータ入出力をを行い前記記憶手段が接続する

内部通信路と、

前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続する

メモリに送信しこれを当該メモリに記憶する手段と、

前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の

前記制御部の稼働状況を監視する手段と、

を備えることを特徴とする記憶制御装置。

**【請求項 3】**

前記制御部が、

中央処理装置と、前記外部通信路に接続するための外部通信インターフェースと、

前記内部通信路と接続するための内部通信インターフェースと、

を備えることを特徴とする請求項 2 に記載の記憶制御装置。 20

**【請求項 4】**

前記稼働情報には前記制御部の障害有無を示す情報が含まれており、

前記制御部が前記監視手段により他の前記制御部に障害が生じていることを認知した場合

、障害が生じている前記制御部が行っていた処理を他の前記制御部に引き継ぐ手段を備え

ることを特徴とする請求項 1 または 2 のいずれかに記載の記憶制御装置。

**【請求項 5】**

前記メモリは前記制御部が担当する処理に関するリソース情報を記憶する手段を備え、

前記処理の引き継ぎ先となる前記制御部が、前記リソース情報にアクセスし当該制御部自身

が引き継ぐべき前記処理を認知する手段を備えることを特徴とする請求項 4 に記載の記憶制御装置。 30

**【請求項 6】**

前記リソース情報には、前記制御部が前記外部通信路もしくは前記内部通信路による通信

に必要な情報が含まれることを特徴とする請求項 5 に記載の記憶制御装置。

**【請求項 7】**

前記リソース情報には、前記データ入出力指示において指定する記憶領域指定情報が含

まれることを特徴とする請求項 5 に記載の記憶制御装置。

**【請求項 8】**

前記リソース情報には、外部通信路上における前記制御部のネットワークアドレスが含

まれることを特徴とする請求項 5 に記載の記憶制御装置。 40

**【請求項 9】**

前記稼働情報には、前記中央処理装置、前記外部通信インターフェース、前記内部通信イン

タフェースのいずれかについての障害の有無を示す情報が含まれることを特徴とする請求

項 3 に記載の記憶制御装置。

**【請求項 10】**

前記障害の有無を示す情報が、前記制御部が前記内部通信路を介して前記メモリに一定間

隔で送信され、前記制御部に対応づけて記憶されるタイムスタンプであり、

前記監視手段は、ある前記制御部に対応する前記タイムスタンプが一定時間以上更新され 50

ていない場合に、そのタイムスタンプに対応づけられている前記制御部に障害が生じていると認知することを特徴とする請求項 9 に記載の記憶制御装置。

【請求項 11】

前記監視手段が、前記稼働情報にアクセスできない場合に、前記内部通信路に障害が生じていると判断する手段を備えることを特徴とする請求項 4 に記載の記憶制御装置。

【請求項 12】

前記監視手段が、前記稼働情報にアクセスできかつ前記のある制御部の前記タイムスタンプが一定時間以上更新されていない場合に、その制御部自体に障害が生じていると判断する手段を備えることを特徴とする請求項 4 に記載の記憶制御装置。

【請求項 13】

前記記憶手段が、中央処理装置と、前記メモリと、ディスクドライブなどの記憶資源に対するデータ入出力をを行うデバイスインターフェースとを備えることを特徴とする請求項 2 に記載の記憶制御装置。

【請求項 14】

前記稼働情報、もしくは、前記リソース情報は、前記メモリに記憶されることを特徴とする請求項 13 に記載の記憶制御装置。

【請求項 15】

前記稼働情報、もしくは、前記リソース情報は、前記記憶資源に記憶されることを特徴とする請求項 13 に記載の記憶制御装置。

【請求項 16】

前記制御部が、データ入出力要求をファイル名単位で行うファイルシステムを備え、ファイル名により指定されるデータを単位として前記記憶手段に対する前記データ入出力指示を送信する手段を備えることを特徴とする請求項 2 に記載の記憶制御装置。

【請求項 17】

前記記憶手段が、ハードディスクなどの記憶資源に対するデータ入出力を制御するデバイスインターフェースと、

キャッシュメモリと、

前記キャッシュメモリを介して前記記憶資源に対するデータの読み書きを行う手段と、を備えることを特徴とする請求項 2 に記載の記憶制御装置。

【請求項 18】

前記内部通信路が、複数の通信経路により冗長構成されることを特徴とする請求項 1 に記載の記憶制御装置。

【請求項 19】

前記制御部が、前記内部通信路とは別に設けられ前記制御部間を接続する他の通信路を通じて他の前記制御部に自身の稼働情報を送信する手段を備え、

前記制御部が前記他の通信路を通じて送信しようとする前記稼働情報を前記内部通信路に対して送信する変換手段を備えることを特徴とする請求項 2 に記載の記憶制御装置。

【請求項 20】

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、を備える記憶制御装置の制御方法であって、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部同士が他の前記制御部の稼働状態を監視することを特徴とする記憶制御装置の制御方法。

【請求項 21】

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、を備える記憶制御装置の制御方法であって、前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶し、

10

20

30

40

50

前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視することを特徴とする記憶制御装置の制御方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、外部通信路から入力されるデータ入出力指示を受信して記憶デバイスに対するデータ入出力制御を行い内部通信路で接続された複数の制御部を備える記憶制御装置に関し、とくに制御部間で交換する稼働情報の通信路として内部通信路を用い、稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に制御部間での稼働情報の監視機能を提供する技術に関する。 10

【0002】

【従来の技術】

近年、ストレージ製品の一つとして、内部にファイルシステムが実装され、ファイル指定によるデータ入出力要求を取り扱うことができるようになした記憶制御装置である、いわゆる、NAS (Network Attached Storage) サーバに対するニーズが高まっている。また、このようなNASサーバとしては、処理能力の向上等を目的として、それぞれがLAN等の外部通信路に接続し、それぞれが個別に外部通信路を通じて送られてくる処理要求に応答できるようにした複数の制御部を、同一の筐体内に収容する構成の製品が存在する。 20

【0003】

【発明が解決しようとする課題】

ところで、記憶制御装置はミッションクリティカルな状況で使用される場合が多く、一般に高い可用性が要求される。

ここで、LAN上のコンピュータ同士の障害検知に際しては、従来から、LAN上のコンピュータ間でハートビートメッセージを交換して互いの稼働状態を監視し合うことで、可用性を向上させる仕組みが知られている。 30

【0004】

例えば、特開2000-222373号公報には、クラスタ化コンピュータシステムにおいて、クラスタを構成するコンピュータ同士でLANを通じて定期的にハートビートメッセージを交換し、お互いに稼働状態を監視し合うようにし、ハートビートメッセージの交換が正常に行われていない場合には、適宜制御部のデータサービスは他の正常な制御部へ引き継ぐようにした仕組みが開示されている。また、特開2001-100943号公報には、2台のPCサーバが、ハートビートを行うための通信を、ディスク装置が接続してあるSCSIバスを用いて行うようにしたクラスタシステムが開示されている。 30

【0005】

一方、前記図1の構成の記憶制御装置のように、複数の制御部を備える構成の記憶制御装置においては、各制御部は同一筐体内に実装されてはいるものの、外部通信路からの要求に対してそれが個別にサービスを提供している。

【0006】

そこで、このような構成の記憶制御装置においても、前記公報のように、制御部間で稼働状態を監視し、また、ある制御部における障害を検知した場合には、その業務を他の正常な制御部に引き継ぐ仕組みを設けることは、可用性の向上に有効であると考えられる。 40

【0007】

ここでこのような仕組みを設ける場合、稼働情報を伝達する通信路に何を用いるかが問題となる。例えば、前記公報のクラスタ化コンピュータシステムの場合には、このような稼働情報（この場合はハートビートメッセージ）の通信路として、コンピュータ間を結ぶLAN等の外部通信路や、専用の通信路を用いている。

【0008】

しかしながら、外部通信路は、経路途中の信頼性が充分で無く、また、通信速度も充分でない、もしくは、一定しないといった問題がある。また、専用の通信路を設ける場合は、 50

専用の設備が必要となり、余分なコストが発生することになる。

#### 【0009】

一方、前述した図1の構成の記憶制御装置においては、制御部間は、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力をを行うための内部通信路により互いに接続されている。そして、内部通信路は一般にLANなどの外部通信路よりも伝送能力が高く信頼性も高い。従って、内部通信路を稼働情報の通信路として用いることで、信頼性の高い制御部間で稼働状態を監視する仕組みを、容易かつ安価に実現することは可能であると考えられる。

#### 【0010】

本発明は、このような観点に基づいてなされたもので、内部通信路を用いて稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に稼働情報の監視機能を実現する記憶制御装置を提供することを目的とする。

#### 【0011】

##### 【課題を解決するための手段】

この目的を達成する本発明のうち主たる発明は、

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力をを行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする。

#### 【0012】

すなわち、一般に外部通信路に比べて信頼性が高く、高速大容量通信が可能な、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力をを行うための内部通信路を通じて稼働情報を通知するようにしたことで、記憶制御装置の部品点数の削減が図られ、装置コストを抑えて信頼性の高いシステムを実現できる。

#### 【0013】

##### 【発明の実施の形態】

＝＝＝開示の概要＝＝＝

本明細書および添付図面の記載により、少なくとも、以下の事項が明らかとなる。

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力をを行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする記憶制御装置。

この記憶制御装置によれば、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力をを行うための内部通信路を通じて稼働情報（例えば、ハートビートメッセージ）を通知することで、記憶制御装置の部品点数の削減が図られ、装置コストを抑えて信頼性の高いシステムを実現できる。

#### 【0014】

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間ににおけるデータ入出力指示及びデータ入出力をを行い前記記憶手段が接続する内部通信路と、前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶する手段と、前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視する手段と、を備えることを特徴とする記憶制御装置。

このような構成の記憶制御装置によれば、制御部とは別体の前記メモリ（例えば、後述す

10

20

30

40

50

る制御メモリ)に存在する稼働情報(例えば、後述する「稼働状態管理テーブル」)に障害の状態を管理することが可能となるため、内部通信路の稼働状態に関する情報などと組み合わせて、障害の原因や発生部分をより細かく特定することができる。

#### 【0015】

また、かかる記憶制御装置においては、例えば、前記制御部は、中央処理装置と、前記外部通信路に接続するための外部通信インターフェースと、前記内部通信路と接続するための内部通信インターフェースと、を備えることとする。

#### 【0016】

また、かかる記憶制御装置においては、前記稼働情報には前記制御部の障害有無を示す情報が含まれており、前記制御部が前記監視手段により他の前記制御部に障害が生じていることを認知した場合、障害が生じている前記制御部が行っていた処理を他の前記制御部に引き継ぐ手段を備えることとする。これにより、記憶制御装置の可用性が確保されることになる。

#### 【0017】

また、かかる記憶制御装置において、前記メモリは前記制御部が担当する処理に関するリソース情報を記憶する手段を備え、前記処理の引き継ぎ先となる前記制御部が、前記リソース情報にアクセスし当該制御部自身が引き継ぐべき前記処理を認知する手段を備えることとする。

#### 【0018】

また、かかる記憶制御装置において、前記リソース情報には、例えば、前記制御部が前記外部通信路もしくは前記内部通信路による通信に必要な情報、前記データ入出力指示において指定する記憶領域指定情報、外部通信路上における前記制御部のネットワークアドレスが含まれることとする。

#### 【0019】

また、かかる記憶制御装置において、前記稼働情報には、前記中央処理装置、前記外部通信インターフェース、前記内部通信インターフェースのいずれかについての障害の有無を示す情報が含まれることとする。

#### 【0020】

また、かかる記憶制御装置において、前記障害の有無を示す情報が、前記制御部が前記内部通信路を介して前記メモリに一定間隔で送信され、前記制御部に対応づけて記憶されるタイムスタンプであり、前記監視手段は、ある前記制御部に対応する前記タイムスタンプが一定時間以上更新されていない場合に、そのタイムスタンプに対応づけられている前記制御部に障害が生じていると認知することとする。

#### 【0021】

また、かかる記憶制御装置において、前記監視手段が、前記稼働情報にアクセスできない場合に、前記内部通信路に障害が生じていると判断する手段を備えることとする。また、前記監視手段が、前記稼働情報にアクセスできかつ前記のある制御部の前記タイムスタンプが一定時間以上更新されていない場合に、その制御部自体に障害が生じていると判断する手段を備えることとする。これにより、障害を細かく特定することが可能となる。

#### 【0022】

また、かかる記憶制御装置において、前記記憶手段が、中央処理装置と、メモリと、ディスクドライブなどの記憶資源に対するデータ入出力をを行うデバイスインターフェースとを備えることとする。

#### 【0023】

また、前記稼働情報、もしくは、前記リソース情報は、前記メモリに記憶されることとする。

#### 【0024】

また、かかる記憶制御装置において、前記稼働情報、もしくは、前記リソース情報は、前記記憶資源に記憶されることとしてもよい。

#### 【0025】

10

20

30

40

50

また、かかる記憶制御装置において、前記制御部が、データ入出力要求をファイル名単位で行うファイルシステムを備え、ファイル名により指定されるデータを単位として前記記憶手段に対する前記データ入出力指示を送信する手段を備えることとする。すなわち、記憶制御装置が、例えば、N A S サーバとして用いられる場合である。

#### 【 0 0 2 6 】

また、かかる記憶制御装置は、前記記憶手段が、ハードディスクなどの記憶資源に対するデータ入出力を制御するデバイスインターフェースと、キャッシュメモリと、キャッシュメモリを介して前記記憶資源に対するデータの読み書きを行う手段と、を備えることを特徴とする。また、かかる記憶制御装置は、前記内部通信路が、複数の通信経路により冗長構成されることとする。

10

#### 【 0 0 2 7 】

また、かかる記憶制御装置は、前記制御部が、前記内部通信路とは別に設けられ前記制御部間を接続する他の通信路（例えば、後述する専用通信路）を通じて他の前記制御部に自身の稼働情報を送信する手段を備え、前記他の通信路に対して送信される稼働情報を前記内部通信路に対して送信する変換手段（例えば、後述するエミュレーションドライバ）を備えることを特徴とする。これにより汎用のクラスタソフトウェアなどを用いて、簡単かつ安価に稼働状態監視の仕組みを実現することができる。

#### 【 0 0 2 8 】

また、本発明の記憶制御装置の制御方法は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路とを備える記憶制御装置の制御方法であって、前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部同士が他の前記制御部の稼働状態を監視することを特徴とする。

20

#### 【 0 0 2 9 】

また、本発明の他の記憶制御装置の制御方法は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、を備える記憶制御装置の制御方法であって、前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶し、前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視することとする。

30

#### 【 0 0 3 0 】

= = 第 1 実 施 例 = =

#### < 装置構成 >

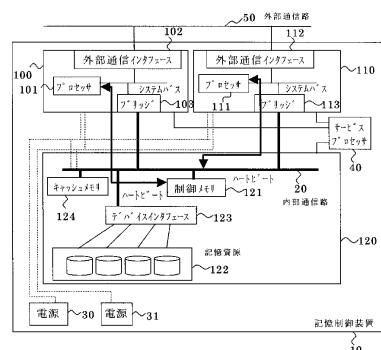

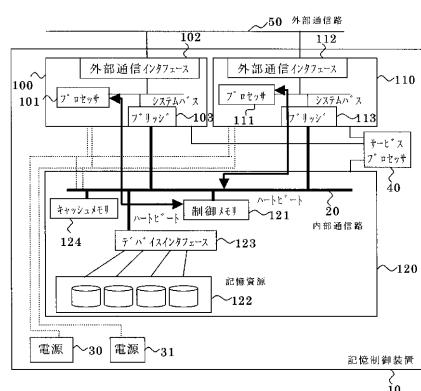

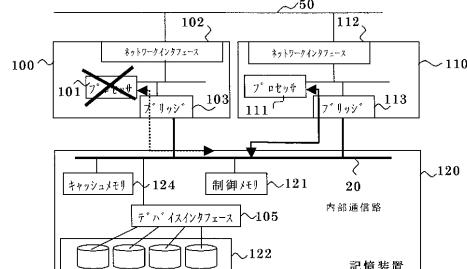

まず、本発明を前述の図 1 に示す記憶制御装置 10 に適用した実施例について説明する。

#### 【 0 0 3 1 】

記憶制御装置 10 は、例えば、回路基板上に形成され C P U とメモリを結ぶ制御バス（システムバス）のようにデータ入出力指示及びデータ入出力を行うための内部通信路 20 と、これに接続する複数の制御部 100, 110、記憶装置 120、冗長構成された電源装置 30, 31 を備える。制御部 100, 110 や記憶装置 120 に接続するサービスプロセッサ 40 は、制御部 100, 110 や記憶装置 120 の動作制御や各種設定、稼働状態監視などを行う。

40

#### 【 0 0 3 2 】

制御部 100, 110 は、C P U などで構成される中央処理装置としてのプロセッサ 101, 111、L A N などの外部通信路 50 に接続するための外部通信インターフェース 102, 112、内部通信路 20 に接続するブリッジなどで構成された内部通信インターフェース 103, 113などを備える。

#### 【 0 0 3 3 】

制御部 100, 110 では、ファイルシステム（不図示）が稼働し、制御部 100, 111 50

0は外部通信路50からファイル名指定によるデータ入出力要求を取り扱う。つまり、制御部100, 110は、それぞれLAN上のファイルサーバとして機能するコンピュータとしての機能を備え、記憶制御装置10は前述のNASサーバとして機能している。

#### 【0034】

一方、記憶装置120は、システム管理情報などが記憶される制御メモリ121、ハードディスクなどの記憶資源122、制御部100, 110から送信されてくる命令などに応じて記憶資源122に対するデータの書き込み／読み出しを実行するデバイスインターフェース123、キャッシュメモリ124などを備える。

#### 【0035】

なお、記憶資源122は、図1に示すように記憶制御装置10に内蔵されている場合もあるし、また、記憶制御装置20の外部の別筐体内に存在し、デバイスインターフェース123と適宜なインターフェースで接続していることもある。

#### 【0036】

##### <基本動作>

記憶制御装置10の基本的な動作について説明する。

記憶制御装置10がホストコンピュータなどの外部装置(不図示)から外部通信路50を通じて入力されるデータ入出力要求を受信すると、プロセッサ101, 111は、この要求に対応する指示コマンドやデータなどからなるデータ入出力指示を、内部通信路20を介して制御メモリ121に送信する。制御メモリ121はこれを受信して記憶する。

#### 【0037】

ここで、例えば、前記データ入出力指示に含まれる前記指示コマンドがライト(Write)コマンドであった場合、デバイスインターフェース123は、内部通信路20を介してプロセッサ101, 111にデータ送信要求を送信する。この要求を受信したプロセッサ101, 111は、キャッシュメモリ124にライトデータを格納し、また、デバイスインターフェース123に対して割込み要求を送信する。この割り込み要求を受信したデバイスインターフェース123は、適宜な機会に、キャッシュメモリ124上の前記ライトデータを記憶資源122に書き込む。

#### 【0038】

一方、前記指示コマンドがリード(Read)コマンドであった場合、デバイスインターフェース123は、この指示コマンドに付帯指定される記憶資源122上の記憶領域に格納されているデータを読み出し、これをキャッシュメモリ124に格納し、さらに、読み出したデータを、内部通信路20を介してプロセッサ101, 111に送信する。

#### 【0039】

割り込み要求を受信したデバイスインターフェース123は、制御メモリ121に格納されている前記指示コマンドを参照し、キャッシュメモリ124内のデータと冗長データとを記憶資源122に転送する。

#### 【0040】

##### <監視機能>

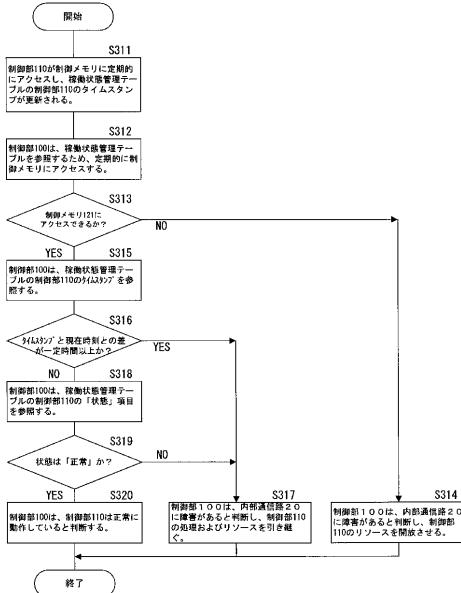

各制御部100, 110は、互いに他の制御部100, 110に障害が発生したかどうかを監視している。各制御部100, 110がどの他のどの制御部100, 110の監視を担当するかは、例えば、サービスプロセッサ40を介してオペレータなどが設定し、設定された情報は、制御メモリ121上に存在する図2に示す稼働状態管理テーブルの「監視対象の制御部」の項目251, 254に登録される。

#### 【0041】

各制御部100, 110は、自身の監視対象として割り当てられている他の制御部100, 110の稼働状態を監視する。この監視により自身が担当する制御部100, 110に何らかの障害が生じていることを検知した場合、制御部100, 110は、検知した障害の内容に応じた処理を実行する。

#### 【0042】

以下、制御部100, 110による監視機能と、異常を検知した場合に実行される記憶制

10

20

30

40

50

御装置 10 の機能について、制御部 110 の障害を制御部 100 が検知する場合を例として図 3 のフローチャートとともに説明する。

【0043】

制御部 110 は、内部通信路 20 を通じて定期的（タイミングは任意に変更できる）に制御メモリ 121 にアクセスする（もしくは、ハートビートメッセージを送信する）。一方、記憶装置 120 は、前記アクセスがあると、アクセスのあった時刻をタイムスタンプとして稼働状態管理テーブルの制御部 110 のタイムスタンプの項目 255 に書き込む（S311）。すなわち、制御部 110 に異常が無ければタイムスタンプは定期的に更新されることになる。

【0044】

一方、制御部 100 は、稼働状態管理テーブルを参照するため、内部通信路 20 を通じて定期的（定期的以外にも任意に設定してもよい）に制御メモリ 121 にアクセスする（S312）。

【0045】

ここで制御部 100 は、制御メモリ 121 にアクセスできなかった場合（S313）、内部通信路 20 に何らかの障害が発生していると判断し、また、内部通信路 20 に障害が発生している場合は、記憶装置 120 へのデータ入出力が正常に行えない状態にある可能性があるので、制御部 100 は、例えば、サービスプロセッサ 40 に指示を出すなどして、制御部 110 の記憶装置 120 に対するデータ入出力処理を停止させるとともに、この処理に関して制御部 110 が取得中のリソースを開放させる（S314）。

【0046】

ここで、リソースとは、例えば、制御部 100, 110 が外部通信路 50 もしくは内部通信路 20 による通信に際し必要となる、ネットワークアドレス（例えば、IP アドレス）などの情報、制御部 100, 110 が記憶手段に対して送信するデータ入出力指示において指定する記憶領域指定情報（例えば、制御部 110 がマウントしていた記憶領域に関する情報）などである。

【0047】

一方、制御部 100 は、制御メモリ 121 にアクセスできた場合、稼働状態管理テーブルの制御部 110 のタイムスタンプ 255 を参照し（S315）、アクセスした時刻とタイムスタンプとの差が一定時間以上であるかどうかを調べる（S316）。

【0048】

ここで差が一定時間以上の場合には、制御部 100 は、制御部 110 に障害が発生していると判断し、制御部 110 が担当している処理やリソースを制御部 100 が引き継ぐ（S317）。

【0049】

一方、差が一定時間に満たない場合には、さらに、稼働状態管理テーブル中の監視対象の制御部 110 の「状態」項目の内容 256 を参照する（S318）。ここでその内容が『正常』である場合には、制御部 100 は、制御部 110 は正常に動作していると認知する（S319, S320）。他方、「状態」項目の内容 256 が『異常』であった場合には、制御部 110 に障害が発生したと判断し、前記と同様の方法により制御部 110 が担当している処理を引き継ぐ（S319, S317）。なお、稼働状態管理テーブルにおいて、『正常』もしくは『異常』は、ビット表現等の適宜な形式で記述される。

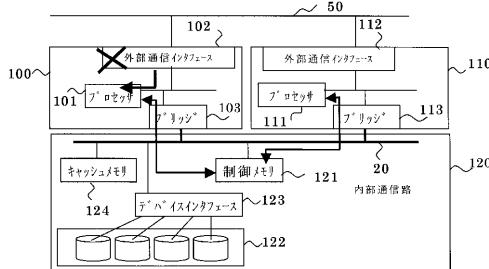

【0050】

ところで、記憶制御装置 10 において、稼働状態管理テーブルにおける「状態」項目の内容は、つぎのように管理されている。

例えば、制御部 100, 110 は、図 4 に示すように外部通信インターフェース 102 に障害が発生している場合、そのことを外部通信インターフェース 102, 112 からプロセッサ 101, 111 への直接の障害報告、もしくは、外部通信インターフェース 50 に出した処理命令がタイムアウトする、といったことで認知する。

【0051】

10

20

30

40

50

制御部 100, 110 は、外部通信インターフェース 102, 112 に障害が発生していることを認知すると、内部通信路 20 を通じて制御メモリ 121 上の稼働状態管理テーブルにアクセスし、障害が発生している制御部 100, 110 に対応する「状態」項目 253, 256 に『異常』を書き込む。

#### 【0052】

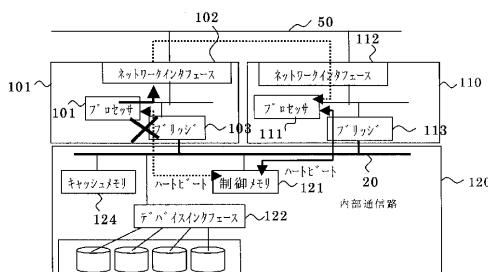

一方、制御部 100, 110 は、図 5 に示すように内部通信インターフェース 103, 113 に障害が発生している場合、そのことを内部通信インターフェース 103, 113 からプロセッサ 101, 110 への障害報告、もしくは、内部通信インターフェース 103, 113 に出した処理命令のタイムアウトなどにより認知する。

#### 【0053】

制御部 100, 110 は、内部通信インターフェース 103, 113 に障害が発生していることを認知すると、内部通信路 20 を通じて制御メモリ 121 上の稼働状態管理テーブルにアクセスし、障害が発生している制御部 100, 110 に対応する「状態」項目に『異常』を書き込む。

#### 【0054】

図 6 はプロセッサ 101 に障害が発生している場合である。この場合、制御部 100 は稼働状態管理テーブルに状態を書き込むことができない。しかしながら、制御部 110 のプロセッサ 111 が制御メモリ 121 を参照するため、プロセッサ 101 に障害している場合でも、その障害を検知することができる。

#### 【0055】

以上の実施例では、制御部 100 が制御部 110 の監視を行う場合について説明したが、当然のことながら制御部 110 が制御部 100 を監視する場合も同様の処理により行われる。

#### 【0056】

以上の実施例においては、制御メモリ 121 の稼働状態管理テーブルへの書き込みや参照などの制御部 100, 110 における障害監視のための通信を、内部通信路 20 を介して行っている。このため、従来の外部通信路 50 や専用の通信路による方式に比べ、障害監視のための通信を高速に行える。また、一般に内部通信路 20 は、LAN などの外部通信路 50 に比べ伝送能力や信頼性に優れるため、障害監視のための通信を迅速かつ確実に行うことができる。

#### 【0057】

また、本来、制御部 100, 110 間やこれらと記憶装置 120 間で行われるデータ入出力処理等のために設けられている内部通信路 20 を、障害監視のための通信に流用しているので、専用の通信路を設ける場合のように余分なハードウェアを増設する必要が無く、障害監視のための通信の仕組みを、容易かつ安価に構築できる。

#### 【0058】

内部通信路 20 を介して制御部 100, 110 に接続する、制御部 100, 110 とは別体の、記憶装置 120 の制御メモリに存在する稼働状態管理テーブルに障害の状態を管理する仕組みであるため、内部通信路 20 の稼働状態に関する情報などと組み合わせて、障害の原因や発生部分をより細かく特定することができる。

#### 【0059】

また、制御部 100, 110 が障害の発生を認知した場合における、処理引き継ぎのための各制御部 100, 110 が取得しているリソースに関する情報についても制御メモリ 121 に管理されるため、制御部 100, 110 に障害が発生した場合でも、記憶装置 120 は引き継ぐリソースを確認することができる。また、リソースの一元管理により管理負荷の軽減等が図られる。

#### 【0060】

また、内部通信路が冗長構成されている場合には、障害監視のための通信の安全性や確実性がさらに担保される。

#### 【0061】

10

20

30

40

50

なお、以上の実施例は、制御部が2つの場合であったが、これに限定されるものではなく、制御部が3つ以上の場合にも容易に拡張することができる。

【0062】

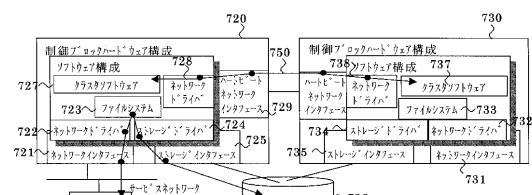

＝＝＝既存クラスタシステムの利用＝＝＝

前述の公報にも記載されているように、従来から、外部通信路や専用の通信路を利用してコンピュータ間で障害監視のための通信を行うソフトウェアが存在する。ここでは、このようなソフトウェアを用いて障害監視のための通信に、内部通信路20を利用する本発明の仕組みを実現する場合について説明する。

【0063】

図7は、本発明の制御部に対応する、コンピュータ720, 730が、専用の通信路により接続され、この専用通信路750を介してハートビートメッセージを伝送することで、コンピュータ720, 730がお互いに稼働状態を監視し合う、従来のシステム構成である。10

【0064】

コンピュータ720, 730は、それぞれ、クライアントからのファイルサービスの要求をネットワークインターフェース721、731、ネットワードライバ722, 732を経由しファイルシステム723, 733で受信する。

【0065】

ファイルシステム723, 733は、記憶装置726に対するデータ転送が必要な場合、ストレージドライバ724, 734、ストレージインターフェース725, 735を経由し記憶装置726とデータ転送を行う。クラスタソフトウェア727, 737は、ハートビート用ネットワードライバ728, 738、ハートビートネットワークインターフェース729, 739を経由し、コンピュータ730上のクラスタソフトウェア727, 737に対しハートビートメッセージを送信する。20

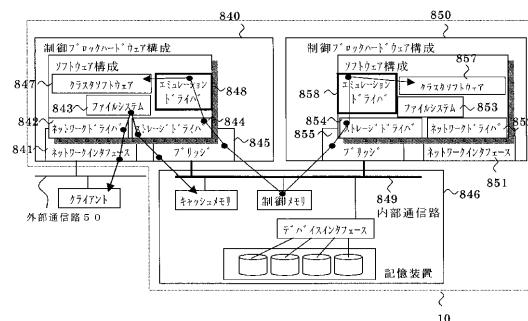

【0066】

このクラスタソフト727, 737が導入されている図7の構成に、障害監視に内部通信路を利用する本発明を適用した場合が図8である。この図において、記憶制御装置810は、クラスタソフトウェア847, 857からのアクセスを受領し、このアクセスをストレージドライバ844, 854へのアクセスに変換するエミュレーションドライバ848, 858を備えている。この構成により、汎用のクラスタソフトウェア847, 857が発行したハートビートメッセージを内部通信路849を通じて伝送される稼働状態情報に変換すること、および、その逆の変換をすることができる。具体的には、例えば、エミュレーションドライバ848, 858は、RS-232CやLANなどの他の通信路の伝送手順に従った通信によりクラスタソフトウェア847, 857からのアクセスを受領して、これを内部通信路849での通信に変換したり、逆に内部通信路849での通信を前記他の通信路の伝送手順に変換してクラスタソフトウェア847, 857に伝えるといった役割を果たす。なお、RS-232CやLANなどの他の通信路は、記憶制御装置10がハードウェア/ソフトウェアとして実際に備えていてもよいし、備えていなくてもよい。また、前記変換機能部分は、エミュレーションドライバ848, 858の内部に設けるのではなく、ストレージドライバ844, 854や記憶装置846における内部通信インターフェース(不図示)の機能を提供するファームウェア(不図示)などに設けるようにしてもよい。30

【0067】

以上に説明したように、既存のクラスタソフトウェアが導入されているシステムにおいては、エミュレーションドライバを導入するだけで本発明を実施することができる。

【0068】

また、既存のクラスタソフトウェアが導入されていない場合には、既存のクラスタソフトウェアにエミュレーションドライバを組み合わせて導入することで、クラスタソフトウェアの機能部分に対する開発費が抑えられるため、低廉なコストで本発明を実施することができる。40

**【 0 0 6 9 】**

= = = 内部通信路の他の構成 = = =

内部通信路が制御バスで無く、ファイバチャネル（Fibre Channel）、Intelligent I/O、Rapid I/Oなどの他のプロトコルに準拠した通信路で構成される場合を説明する。

図9は内部通信路をファイバチャネル（Fibre Channel）プロトコルによる通信路で構成した記憶制御装置971の構成を示す図である。制御部950，960は、内部通信インターフェースとしてファイバチャネルインターフェース953，963を備える。

**【 0 0 7 0 】**

一方、記憶装置980もファイバチャネルインターフェース986，996を備え、制御部950、960とはファイバチャネルスイッチ956，966、ファイバチャネルインターフェース986，992を介して接続する。

**【 0 0 7 1 】**

制御部950，960は、ファイバチャネルスイッチ956，966、ファイバチャネルインターフェース953，963を介して制御部950，960に接続され、制御メモリ982，992、書き込みデータ及びディスクドライブからの読み出しデータを一時バッファリングするキャッシュメモリ983，993を備える。

**【 0 0 7 2 】**

制御部950，960は、デバイスインターフェース994を介してディスクドライブ群985へ接続される。制御部950、960、記憶装置980は、同一の筐体に実装される冗長構成の電源972，973より給電され、保守機構974により、各種動作設定や稼働管理が行われる。

**【 0 0 7 3 】**

制御部950がディスクドライブ群からなる記憶資源985とライト（Write）データ転送を行う場合を例として、制御の流れ、データの流れを説明する。制御部950がサービスネットワーク970によりデータサービスの依頼を受けると、プロセッサ952は、サービス依頼を記憶装置980に対するI/Oコマンドに変換し、ファイバチャネルインターフェース953、ファイバチャネルスイッチ956、ファイバチャネルインターフェース986を介して、記憶装置980へI/Oコマンドを送信する。

**【 0 0 7 4 】**

送信されたI/Oコマンドは、制御メモリ982に格納される。I/Oコマンドがライトコマンドである場合、ファイバチャネルインターフェース986は、プロセッサ952にデータ転送を指示する。この指示によりプロセッサ952は、ファイバチャネルプロトコルに従い、記憶装置980に書き込みデータを送信する。記憶装置980は、送信されてきた書き込みデータを受信して、これを一旦キャッシュメモリ983に格納する。この書き込みデータは、デバイスインターフェース984により冗長データと共に記憶資源985に転送される。

**【 0 0 7 5 】**

つぎに、図9のシステムにおいて、制御部950が障害になった場合には制御部960で、制御部960が障害になった場合には制御部950で、それぞれ障害が発生している制御部のリソースを引継ぎ、自動的にデータサービスなどの記憶制御装置10の業務を継行できるようにした、記憶制御装置971の仕組みについて説明する。

**【 0 0 7 6 】**

記憶資源985には、図10に示す稼働状態管理テーブルが格納されている。稼働状態管理テーブルには、各制御部を特定する情報1001，1002、監視すべき対象の制御部を特定する情報1003，1004についての項目がある。これらの項目は、例えば、フェイルオーバポリシーに従って設定される。タイムスタンプ1005，1006は、制御部950，960が稼働情報（ハートビートメッセージ）のI/Oを発行する際の制御部上の時刻を示す。また、この稼働状態管理テーブルの「状態」1007，1008項目には、制御部950，960の『正常』、『異常』を示す情報がセットされている。これら

10

20

30

40

50

の項目にセットされる情報には、必要に応じてクラスタシステムを構築する際のサービスネットワーク 1070 上の制御部に割り当てられた名称などの固有の識別子が用いられる。

制御部 950 上のプロセッサ 952 は、適宜なタイミング（例えば、定期的に）で記憶資源 985 の稼働情報管理テーブルの読み出し命令を送信し、稼働情報管理テーブルに示す全データもしくは一部のデータを取得する。稼働情報管理テーブルを読み出すと、プロセッサ 952 は、全データから制御部ネーム領域 1001, 1002 を参照し、制御部 950 が有する制御部ネーム「Server A」に対応づけられている監視対象制御部の制御部ネームを参照する。そして、この例では、「Server A」の監視担当制御部として「Server B」が割り当てられているので「Server B」のタイムスタンプ 1006 と状態情報 1008 とを参照し、フェイルオーバ処理を実行する必要性の有無を判断する。10

#### 【0077】

プロセッサ 952 は、「Server B」のタイムスタンプ 1006 と現在時刻との差が一定時間以上であった場合、もしくは、「状態」項目 1008 に『異常』を示す情報がセットされていた場合には、制御部 960 に何らかの障害が発生していると認知する。また、プロセッサ 952 は、稼働状態管理テーブルにアクセスできることで、内部通信路に障害が発生していないと認知し、障害が制御部 960 におけるものであると判断して制御部 960 が行っていた処理やリソースの引き継ぎを開始する。20

#### 【0078】

なお、プロセッサ 952 は、制御部 960 の障害を検出するかどうかに関わらず、「Server A」のタイムスタンプと状態情報である図 10 の 1005, 1007 の項目の内容を適宜なタイミング（例えば定期的に）更新する。

#### 【0079】

制御部 950, 960 が定期的に以上の処理を行うことにより汎用 I/O インタフェースを通信路として用いた障害監視等の仕組みが実現されることになる。

#### 【0080】

つぎに、ファイバチャネルスイッチ 956 に障害が生じた場合についての記憶制御装置の動作について説明する。

ファイバチャネルスイッチ 956 が障害となった場合、制御部 950 は I/O 入出力が不可となるが、通常のフェイルオーバ方式により制御部 960 の処理を継続させた場合には制御部 960 に処理が集中し、性能が劣化する可能性がある。30

#### 【0081】

そこで、このような場合には、汎用 I/O 切り替えソフトウェア等により、制御部 950 の入出力経路を、ファイバチャネルインタフェース 953 ファイバチャネルスイッチ 956 ファイバチャネルインタフェース 986 という通常の経路から、ファイバチャネルインタフェース 954 ファイバチャネルスイッチ 966 ファイバチャネルインタフェース 996 という経路に変更して I/O を継続する。また、同時に、ディスクボリューム群 985 に制御部 950 から行われていた制御部 950 のアクセス状態情報を格納、確認するための I/O も経路を切り替える。40

#### 【0082】

この例では、制御部 950 は、ファイバチャネルインタフェース 954 ファイバチャネルスイッチ 966 ファイバチャネルインタフェース 996 を順に経由して、図 10 におけるタイムスタンプ 1005、制御部 950 の「状態」項目の内容 1007 をディスクボリューム群 985 に格納する。

#### 【0083】

なお、以上はファイバチャネルスイッチ 956 が障害となった場合を例として説明したが、ファイバチャネルインタフェース 953、ファイバチャネルスイッチ 956、ファイバチャネルインタフェース 986 等に障害が発生した場合においても以上の処理を拡張できる。50

**【 0 0 8 4 】**

以上のように、この実施例では、制御部 950, 960 の状態情報を搭載した稼働情報の伝送を、外部通信路や専用の通信路では無く、記憶装置 980 への汎用 I/O インタフェース上で行っている。これによりハートビート用ネットワークインタフェースの導入が必要でなく、その分、手間やコストが削減され、また、信頼性の高い汎用 I/O インタフェースの利用により、信頼性の高い稼働状態監視機能を実現できる。

**【 0 0 8 5 】**

また、制御部の稼働状態を格納するディスクドライブ上に、クラスタ動作に必要な制御部ネットワークアドレス等のネットワーク属性、データが格納されているディスクドライブ等のリソース引継ぎ情報を格納することにより、各制御部より読み出し可能となるため、リソース引継ぎの設定管理を一元化し、管理コストの削減を図ることができる。10

**【 0 0 8 6 】**

また、図 9 では 2 つのファイバチャネルスイッチ 956, 966 を含む構成であったが、ファイバチャネルスイッチを全く含まない構成や、3 つ以上のファイバチャネルスイッチを含む構成である場合にも本発明を拡張して適用することができる。また、ファイバチャネル以外の汎用 I/O インタフェースを用いる場合にも適用できる。

**【 0 0 8 7 】**

= = = 稼働情報の格納方式 = = =

つぎに、汎用クラスタソフトを使用して本発明のシステムを構築する際に、汎用クラスタソフトが送信する稼働情報を、記憶装置のディスクドライブなどの記憶資源（例えば、ディスクドライブ）上に格納するようにした実施例について説明する。20

**【 0 0 8 8 】**

図 11 はこのような構成の記憶制御装置 1000 の一例である。制御部 1110, 1150 は、クライアントからのファイルサービスの依頼をネットワークインタフェース 1111, 1151、ネットワーカードライバ 1112, 1152 を経由してファイルシステム 1113, 1153 で受信する。

**【 0 0 8 9 】**

ファイルシステム 1113, 1153 は、ストレージドライバ 1114, 1154、ファイバチャネルインタフェース 1115, 1155、ファイバチャネルスイッチ 1116, 1156 を経由して記憶装置 1119 とデータ転送を行う。ストレージドライバ 1114, 1154 内には、汎用 I/O 切り替えソフトウェアが組み込まれている。30

**【 0 0 9 0 】**

データの転送経路に障害が発生した場合、ストレージドライバ 1114, 1154 は、データ転送の経路をファイバチャネルインタフェース 1117, 1157、ファイバチャネルスイッチ 1116, 1156 を経由する経路に切り替える。

**【 0 0 9 1 】**

このシステムにおいて、汎用クラスタソフトウェアは、ネットワークに対し制御部の状態情報を含む稼働情報を送信する。ここで当該稼働情報の要求をネットワーカードライバとして受信し、汎用 I/O インタフェース経由で記憶装置へデータ転送を行う要求に変換するエミュレーションドライバ 1120, 1160 を、各制御部において稼働させることで、汎用クラスタソフトウェアに対し、透過的に汎用 I/O インタフェース上のハートビートの交換を行えるようにしている。40

**【 0 0 9 2 】**

また、ストレージドライバ 1014 は、汎用 I/O インタフェース上のハートビートである I/O に対しても、データ転送の経路障害時に経路をファイバチャネルインタフェース 1117, 1157、ファイバチャネルスイッチ 1116, 1156 を経由する経路に切り替えてデータ転送を継続する。これにより信頼性の高い稼働状態監視のための仕組みが実現される。

**【 0 0 9 3 】****【 発明の効果 】**

10

20

30

40

50

本発明の記憶制御装置にあっては、制御部間で交換する稼働情報の通信路として内部通信路を用い、稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に稼働情報の監視機能を提供することができる。

【図面の簡単な説明】

【図1】本発明の一実施例による記憶制御装置の構成を示す図である。

【図2】本発明の一実施例による稼働情報管理テーブルを示す図である。

【図3】本発明の一実施例として説明する記憶制御装置における、制御部が他の制御部が検知する処理を説明するフローチャートである。

【図4】本発明の一実施例として説明する記憶制御装置における、外部通信インターフェースに障害が発生している場合の障害認知等の処理を説明する図である。 10

【図5】本発明の一実施例として説明する記憶制御装置における、内部通信インターフェースに障害が発生している場合の障害認知等の処理を説明する図である。

【図6】本発明の一実施例として説明する記憶制御装置における、プロセッサに障害が発生している場合の障害認知等の処理を説明する図である。

【図7】従来における、コンピュータがお互いに稼働状態を監視し合う仕組みを説明する図である。

【図8】本発明の一実施例による、障害監視に内部通信路を用いた記憶制御装置の構成を示す図である。

【図9】本発明の一実施例による、内部通信路をファイバチャネルプロトコルの通信路で構成した記憶制御装置の構成を示す図である。 20

【図10】本発明の一実施例による稼働情報管理テーブルを示す図である。

【図11】本発明の一実施例による、汎用クラスタソフトを使用し、また、稼働情報をディスクドライブなどの記憶資源に格納するようにした記憶制御装置の構成を示す図である。 20

【符号の説明】

20 内部通信路

50 外部通信路

101, 110 制御部

121 制御メモリ

124 キャッシュメモリ

122 記憶資源

123 デバイスインターフェース

30

【図1】

【図2】

| 251 |          |                     |    |

|-----|----------|---------------------|----|

| 制御部 | 監視対象の制御部 | タイムスタンプ             | 状態 |

| 100 | 110      | 2001/11/13 10:05:02 | 正常 |

| 110 | 100      | 2001/11/13 10:02:15 | 正常 |

254 252 255 253 256

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

## フロントページの続き

(72)発明者 室谷 晓

神奈川県小田原市中里322番地2号 株式会社日立製作所R&Dシステム事業部内

(72)発明者 中野 俊夫

神奈川県小田原市中里322番地2号 株式会社日立製作所R&Dシステム事業部内

(72)発明者 横畠 静生

神奈川県小田原市中里322番地2号 株式会社日立製作所R&Dシステム事業部内

(72)発明者 高本 賢一

神奈川県小田原市中里322番地2号 株式会社日立製作所R&Dシステム事業部内

F ターム(参考) 5B034 BB01 CC05 DD02

5B042 GA11 JJ04

5B065 BA01 CA11 EK02