(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4640559号

(P4640559)

(45) 発行日 平成23年3月2日(2011.3.2)

(24) 登録日 平成22年12月10日(2010.12.10)

(51) Int.Cl.

F 1

H02M 7/5387 (2007.01)

H02M 7/5387

Z

G01R 15/14 (2006.01)

G01R 15/02

F

G01R 19/165 (2006.01)

G01R 19/165

J

請求項の数 7 (全 14 頁)

(21) 出願番号

特願2000-388567 (P2000-388567)

(22) 出願日

平成12年12月21日 (2000.12.21)

(65) 公開番号

特開2002-191179 (P2002-191179A)

(43) 公開日

平成14年7月5日 (2002.7.5)

審査請求日

平成19年11月14日 (2007.11.14)

(73) 特許権者 000006622

株式会社安川電機

福岡県北九州市八幡西区黒崎城石2番1号

(72) 発明者 上田 英史

福岡県北九州市八幡西区黒崎城石2番1号

株式会社 安川電機内

審査官 杉浦 貴之

最終頁に続く

(54) 【発明の名称】 インバータ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、

2以上の抵抗を並列接続してなる第1の抵抗群であり、かつインバータ装置の出力電流が流れる前記第1の抵抗群と、

インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を増幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とするインバータ装置。

## 【請求項 2】

半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、

前記直列接続体の前記接続点とインバータ装置の前記出力端子との間に挿入接続された第1の抵抗と、差動増幅器と、前記差動増幅器の負側入力端子と前記第1の抵抗の一方の側の端子との間に挿入接続された第4の抵抗と、前記差動増幅器の負側入力端子と出力端子との間に接続された第3の抵抗と、前記第1の抵抗のもう一方の側の端子と前記差動増幅

10

20

器の正側入力端子との間に挿入接続された第2の抵抗と、基準電圧と、前記基準電圧と前記差動増幅器の正側入力端子との間に接続された第5の抵抗とからなる構成体と、前記構成体を2個以上有し、かつ各構成体中の第1の抵抗を互いに並列接続し、かつ各構成体中の差動増幅器各出力を加算する加算器とからなる電流検出手段を備えたことを特徴とするインバータ装置。

**【請求項3】**

半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、

10

2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ前記直列接続体の前記接続点とインバータ装置の出力端子との間に挿入接続された前記第1の抵抗群と、

インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を増幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とするインバータ装置。

**【請求項4】**

半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、

20

2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ2個以上並列接続された前記直列接続体と前記直流電源の負極端子との間に挿入接続された前記第1の抵抗群と、

インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を増幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とするインバータ装置。

**【請求項5】**

半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、

30

2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ2個以上並列接続された前記直列接続体と前記直流電源の正極側端子との間に挿入接続された前記第1の抵抗群と、インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を増幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とするインバータ装置。

**【請求項6】**

前記各直列接続体を構成する負極側並列接続体である半導体スイッチング素子および還流ダイオードと前記第1の抵抗群との接続点において還流ダイオードのみその接続を切り放し前記直流電源の負極側端子に接続したことを特徴とする請求項4記載のインバータ装置。

40

**【請求項7】**

前記第1の抵抗群を構成する並列接続された各抵抗は、電流を導通させる端子対と電圧信号を取り出す端子対とをもつ4端子構造一体型の抵抗である請求項1ないし請求項6記載のインバータ装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明はインバータ装置の電流検出器に関するものであり、かつ被検出電流の流れる抵抗端子間電圧により電流検出を行う小型軽量のインバータ装置に関するものである。

**【0002】**

50

### 【従来の技術】

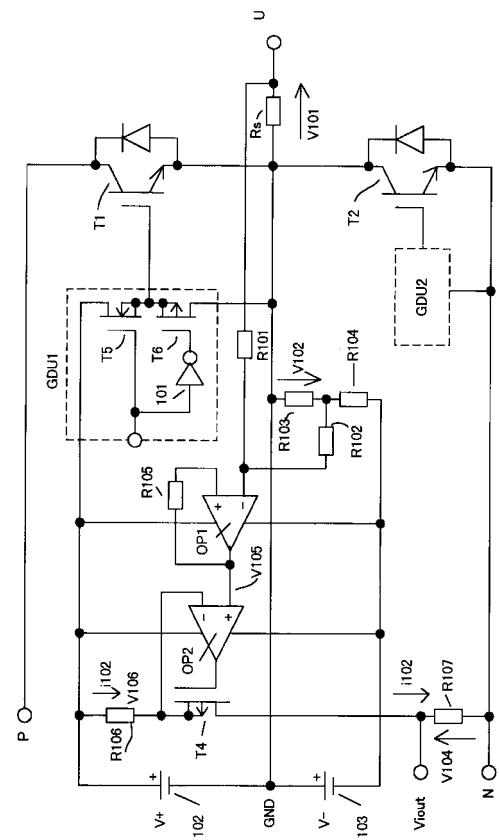

図11は特開平10-123184による従来例である電流検出回路を示したものである。

図11による従来例においては、第1のオペアンプOP1の出力端子が第2のオペアンプOP2の非反転入力端子に接続されているとともに、オペアンプOP2の帰還回路には高耐圧のPチャネルMOSFETのゲート・ソースが直列に接続されている。また、オペアンプOP1、OP2の駆動電源である正電源V+の正極とPチャネルMOSFETのソースとの間には、抵抗R106が接続されている。なおPチャネルMOSFETのドレインとインバータの主回路直流電源の負極Nとの間には、前記同様に検出抵抗R107が接続されている。

10

この回路において、シャント抵抗Rsの電圧はオペアンプOP1により増幅され、そのオペアンプ出力電圧V105がオペアンプOP2に入力される。オペアンプOP2はボルテージフォロワであるため、抵抗R106に印加される電圧V106が次の式で示される一定値になるようにPチャネルMOSFETのゲート電圧を調整する。

$$V_{106} = R_{106} \times i_{102} = (V+) - V_{105}$$

このとき、抵抗R107はMOSFETを介して抵抗R106と直列に接続されているため、抵抗R107にも抵抗R106と同じ電流i102が流れることとなり、その結果として相電流の検出電圧V104はV106と等しくなる。

つまりこの回路では相電流の検出電圧V104が、オペアンプOP2によって以下の式で示される一定値となるように調整されることとなり、このV104から逆算してV105が検出できることとなり、いいかえれば相電流が検出できることとなる。

20

$$V_{104} (= V_{106}) = R_{106} \times i_{102} = (V+) - V_{105}$$

またIGBTトランジスタT1およびT2のスイッチング動作に伴って抵抗R106と抵抗R107との間に発生する高電圧を、PチャネルパワーMOSFETのドレイン・ソース間電圧として吸収することで、高電圧側からの電圧信号V105についてのアナログ電圧信号伝送を実現している。

### 【0003】

#### 【発明が解決しようとする課題】

図11に示す従来例ではシャント抵抗Rsにおいては、出力電流にシャント抵抗Rsの抵抗端子間電圧を乗じた熱ロスが発生する。

30

このためインバータ装置の電力容量増加に伴い定格出力電流が大きくなれば同一の抵抗端子間電圧を得ようとした場合、シャント抵抗Rsで発生する熱ロスが増加するので抵抗ササイズを大型化する必要があり、インバータ装置小型化のネックとなる。

またシャント抵抗Rsの抵抗値を十分小さくして抵抗の小型化を図れば抵抗端子間電圧が大きく低下するため、抵抗端子間電圧增幅用オペアンプの入力オフセットや入力バイアス電流等の影響で電流検出誤差が大きくなるという問題がある。

また小型抵抗を並列接続して抵抗全体の放熱面積を増やし全体抵抗値をも下げれば、抵抗端子間電圧をある程度小さくするだけで抵抗の小型化を図ることはできる。しかしこの場合にも検出電圧が小さくなった分だけ前記同様に検出誤差の影響は大きくなり、また並列接続ゆえに各抵抗を相互につなぐパターン抵抗分の影響が生じ検出誤差がさらに増加してしまうという問題もある。

40

本発明は、このような問題点を解決するためになされたものであり、大きな被検出電流に対しても誤差の少ない、しかも超小型の電流検出器を備えた超小型のインバータ装置を提供することにある。

### 【0004】

#### 【課題を解決するための手段】

上記問題を解決するため本発明は請求項1記載のように、半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなる

50

インバータ装置において、2以上の抵抗を並列接続してなる第1の抵抗群であり、かつインバータ装置の出力電流が流れる前記第1の抵抗群と、インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を增幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とする。

**【0005】**

また請求項2記載のように、半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、前記直列接続体の前記接続点とインバータ装置の前記出力端子との間に挿入接続された第1の抵抗と、差動増幅器と、前記差動増幅器の負側入力端子と前記第1の抵抗の一方の側の端子との間に挿入接続された第4の抵抗と、前記差動増幅器の負側入力端子と出力端子との間に接続された第3の抵抗と、前記第1の抵抗のもう一方の側の端子と前記差動増幅器の正側入力端子との間に挿入接続された第2の抵抗と、基準電圧と、前記基準電圧と前記差動増幅器の正側入力端子との間に接続された第5の抵抗とからなる構成体と、前記構成体を2個以上有し、かつ各構成体中の第1の抵抗を互いに並列接続し、かつ各構成体中の差動増幅器各出力を加算する加算器とからなる電流検出手段を備えたことを特徴とする。

10

**【0006】**

また請求項3記載のように、半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ前記直列接続体の前記接続点とインバータ装置の出力端子との間に挿入接続された前記第1の抵抗群と、インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を增幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とする。

20

**【0007】**

また請求項4記載のように、半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ2個以上並列接続された前記直列接続体と前記直流電源の負極端子との間に挿入接続された前記第1の抵抗群と、インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を增幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とする。

30

また請求項5記載のように、半導体スイッチング素子と前記半導体スイッチング素子に逆並列接続される還流ダイオードとの並列接続体を2個直列接続してなる直列接続体と、前記並列接続体を2個直列接続した接続点がインバータ装置の出力端子に接続され、前記直列接続体を直流電源の正負極間に2個以上並列接続してなるインバータ装置において、2以上の抵抗を並列接続してなる第1の抵抗群であり、かつ2個以上並列接続された前記直列接続体と前記直流電源の正極側端子との間に挿入接続された前記第1の抵抗群と、インバータ装置の出力電流が前記第1の抵抗群を流れる際に前記並列接続された各抵抗の端子間に発生する各抵抗端子間電圧を增幅し、かつ各増幅値を加算して前記出力電流を検出する手段を備えたことを特徴とする。

40

また請求項6記載のように、前記インバータ装置において、2個以上並列接続された前記直列接続体と前記直流電源の負極側端子との間に前記第1の抵抗群を挿入接続し、かつ前記各直列接続体を構成する負極側並列接続体である半導体スイッチング素子および還流ダ

50

イオードと前記第1の抵抗群との接続点において還流ダイオードのみその接続を切り放し前記直流電源の負極側端子に接続したことを特徴とする。また請求項7のように、前記第1の抵抗群が電流を導通させる端子対と電圧信号を取り出す端子対とをもつ4端子構造一体型の抵抗としたことを特徴とする。

#### 【0008】

請求項1記載の構成において、インバータ装置の被検出電流は全て並列接続された第1の抵抗群を流れることとなる。ここで第1の抵抗群を構成する各抵抗はいずれも小型であり、そのために抵抗値も小さい。また一般的には全て同一抵抗が使用されている。各抵抗はプリント基板上に実装され、これら各抵抗の両側端子はプリント基板上の銅パターンにより同極側端子どうしがそれぞれ相互接続されている。銅パターンは小さなインピーダンスを有するが、第1の抵抗群の各抵抗値が小さいので前記銅パターンによるインピーダンスの影響は相対的に大きくなり検出誤差も増加する。10

この影響を無くそうとすれば一般的には抵抗端子から直接に端子間電圧を検出すればよいのだが、複数抵抗が並列接続された場合では全抵抗の全体共通の直接端子というものは存在しないので抵抗端子から直接に端子間電圧を検出することはできず、従って検出した抵抗端子間電圧には必ず銅パターンによるインピーダンスの影響が含まれてしまうこととなる。

#### 【0009】

ところが請求項1記載の構成では並列接続された第1の抵抗群につき、各抵抗ごとにその端子から直接に端子間電圧を検出している。従って検出された抵抗端子間電圧には銅パターンによるインピーダンスの影響が含まれることはない。20

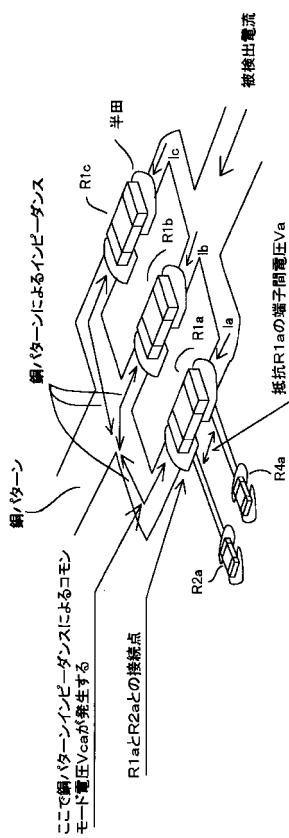

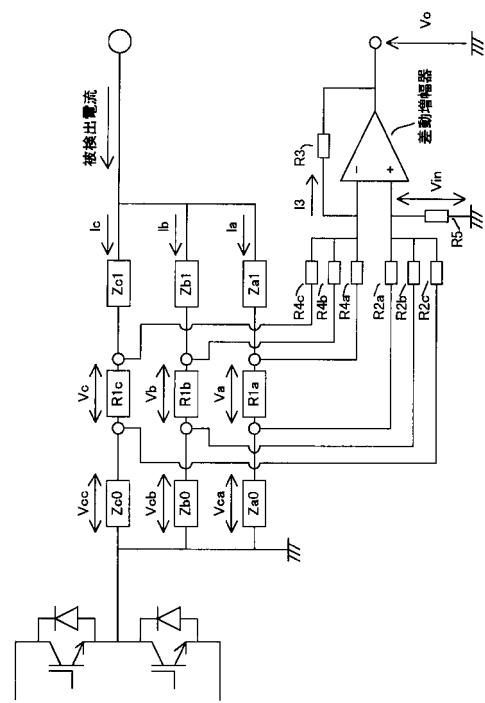

例えば並列接続された第1の抵抗群が3個の抵抗による並列接続の場合、図7で示すように銅パターンによるインピーダンスの影響で各抵抗を流れる電流はそれぞれが異なった値となってしまう。ここで図8に示すように第1の抵抗群をそれぞれR1a, R1b, R1cとし各抵抗を流れる電流をIa, Ib, Icとすると前記各抵抗の端子間電圧はVa(=R1a×Ia), Vb(=R1b×Ib), Vc(=R1c×Ic)となる。

#### 【0010】

またR1aの両端子は第2の抵抗群の一つであるR2a, 第4の抵抗群の一つであるR4aを介してそれぞれ差動増幅器の正側入力端子および負側入力端子へと接続されており、同様にR1bの両端子はR2b, R4bを介して、R1cの両端子はR2c, R4cを介してそれぞれ差動増幅器の正負各入力端子に接続されている。また差動増幅器の正側入力端子は第5の抵抗R5を介して基準電圧となるグランドに接続され、負側入力端子は第3の抵抗R3を介して差動増幅器出力端子に接続されている。そしてR2a, R2b, R2c, R4a, R4b, R4cは全て等しい抵抗値としており、またR3とR5の抵抗値も等しくしている。30

R1aとR2aとの接続点では銅パターンのインピーダンスによりコモンモード電圧Vcaが発生し、R1aとR4aとの接続点ではこのVcaに抵抗端子間電圧Vaを加えた電圧(Vca+Va)が発生している。同様にR1bとR2bとの接続点ではコモンモード電圧Vcbが発生し、R1bとR4bとの接続点ではこのVcbに抵抗端子間電圧Vbを加えた電圧(Vcb+Vb)が発生し、同じくR1cとR2cとの接続点ではコモンモード電圧Vccが発生し、R1cとR4cとの接続点ではこのVccに抵抗端子間電圧Vcを加えた電圧(Vcc+Vc)が発生している。40

#### 【0011】

ここで差動増幅器の正負両入力端子電圧は等しくなるが、この入力端子電圧をVinとすると、R3を流れる電流(I3)は

$$\begin{aligned} I_3 &= (V_{ca} + V_a - V_{in}) / R4a + (V_{cb} + V_b - V_{in}) / R4b + (V_{cc} + V_c - V_{in}) / R4c \\ &= (V_{ca} + V_{cb} + V_{cc} - 3 \times V_{in}) / R4a + (V_a + V_b + V_c) / R4a \end{aligned}$$

$\therefore R4a = R4b = R4c$

となり、また  $V_{in}$  は

$$\begin{aligned} V_{in} &= [(V_{ca} - V_{in}) / R2a + (V_{cb} - V_{in}) / R2b + (V_{cc} - V_{in}) / R2c] \times R5 \\ &= [(V_{ca} + V_{cb} + V_{cc} - 3 \times V_{in}) / R4a] \times R5 \end{aligned}$$

$\therefore R4a = R2a = R2b = R2c$

10

となるので差動増幅器出力電圧 ( $V_o$ ) は

$$V_o = V_{in} - R3 \times I_3$$

$$\begin{aligned} &= V_{in} - R5 \times I_3 (\because R3 = R5) \\ &= [( (V_{ca} + V_{cb} + V_{cc} - 3 \times V_{in}) / R4a ) - I_3 ] \times R5 \\ &= - [ (V_a + V_b + V_c) / R4a ] \times R5 \\ &= - [ (R1a \times I_a + R1b \times I_b + R1c \times I_c) / R4a ] \times R5 \\ &= - [ R1a \times (I_a + I_b + I_c) / R4a ] \times R5 (\because R1a = R1b = R1c) \\ &= - [ R1a \times (\text{被検出電流}) / R4a ] \times R5 \end{aligned}$$

20

.....(1)

となる。

#### 【0012】

この(1)式からわかるように、作動増幅器出力  $V_o$  には銅パターンによるインピーダンスの影響をまったく含まない第1の抵抗群の端子間電圧のみが電圧增幅検出されることとなり、しかもその端子間電圧に関しては第1の抵抗群の全体並列抵抗値 ( $= R1a / 3$ ) に被検出電流を乗じた値ではなく、一つ相当の抵抗値 ( $= R1a$ ) に被検出電流を乗じた端子間電圧となるので3倍もの端子間電圧を得ることが可能となる。従って銅パターンによる影響誤差がなく、また検出電圧も大きくとれるので差動増幅器の入力オフセット電圧等の影響をも低減した検出精度の高い電流検出器を構成することが可能となる。

30

#### 【0013】

請求項2記載の構成においても、インバータ装置の被検出電流は全て並列接続された第1の抵抗群を流れる事になる。ここで第1の抵抗群を構成する各抵抗は前記同様いずれも小型であり、そのために抵抗値も小さい。また一般的には全て同一抵抗値となっている。また各抵抗はプリント基板上に実装され、これら各抵抗ごとにその両側端子と差動増幅器正負入力端子間に第2の抵抗および第4の抵抗がそれぞれ挿入接続されている。また各差動増幅器の正入力端子と基準電圧であるグランドとの間には第5の抵抗が接続され、各差動増幅器負入力端子と出力端子との間には第3の抵抗が接続されている。

30

ここで抵抗値において

40

$$R2 = R4$$

$$R3 = R5$$

とし第1の抵抗群のうち例えば抵抗  $R1a$  を流れる電流を  $I_a$  とすれば、当該差動増幅器出力電圧 ( $V_{oa}$ ) は、

$$V_{oa} = - R1a \times I_a \times R3 / R4$$

となる。そしてこのような構成が第1の抵抗群の各抵抗ごとにあり、各抵抗ごとに上記のような差動増幅器出力電圧を得られるので、これらを加算器により全て加え合わせればその出力である  $V_o$  は

$$\begin{aligned}

V_o &= V_{oa} + V_{ob} + V_{oc} + \dots \\

&= -R_1 a \times (I_a + I_b + I_c + \dots) \times R_3 / R_4 \\

&= -R_1 a \times (\text{被検出電流}) \times R_3 / R_4

\end{aligned}$$

となり、請求項 1 記載の場合と同様に抵抗の小型化、銅パターンの影響の削除、大きな抵抗端子間電圧を得ることができる。

#### 【0014】

請求項 3 記載の構成においては、被検出電流が流れる第 1 の抵抗群を並列接続により構成し、この各抵抗端子間電圧を増幅して、増幅された各抵抗端子間電圧を加算器により全て加え合わせたその合計値から電流検出を行うことにより、銅パターンの影響の削除、大きな端子間電圧を得ることによる増幅器等に内在する検出誤差の低減、および抵抗の小型化とをあわせて実現することができる。請求項 4 および請求項 5 記載の構成は、請求項 3 記載の構成における電流検出器の挿入位置を変更しただけのものであり、その検出原理および作用効果は前記と同様である。

10

#### 【0015】

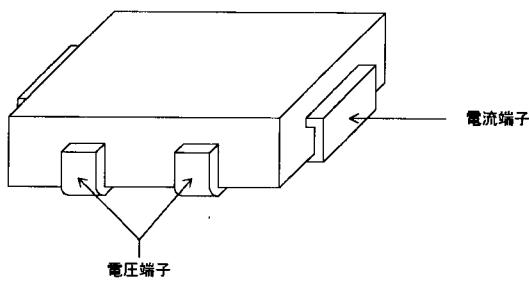

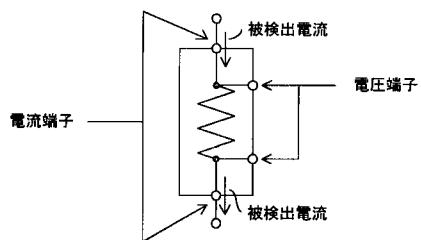

また請求項 6 記載の構成は、請求項 4 記載の構成における電流検出器の挿入位置において、かつ直流電源の負極側に接続された半導体スイッチング素子と還流ダイオードとの並列接続体においてその還流ダイオードの接続位置を変更したものである。この構成は請求項 4 または請求項 5 記載の構成に比べ、インバータ装置の出力電力が小さい場合でも、第 1 の抵抗群を流れる被検出電流の導通時間幅を十分に確保できるという効果がある。また請求項 1 ないし請求項 6 記載のいずれの構成においても並列接続された第 1 の抵抗群の各抵抗に関し、被検出電流が流れる電流端子部と被検出電圧出力部とを別々に備えた 4 端子構造の抵抗（図 9 および図 10）を使用することで、抵抗をプリント基板に実装する際に電流端子部の半田接続で発生する誤差電圧の影響をも削除した検出誤差の極めて少ない電流検出器を構成できるという効果も期待できる。

20

#### 【0016】

##### 【発明の実施の形態】

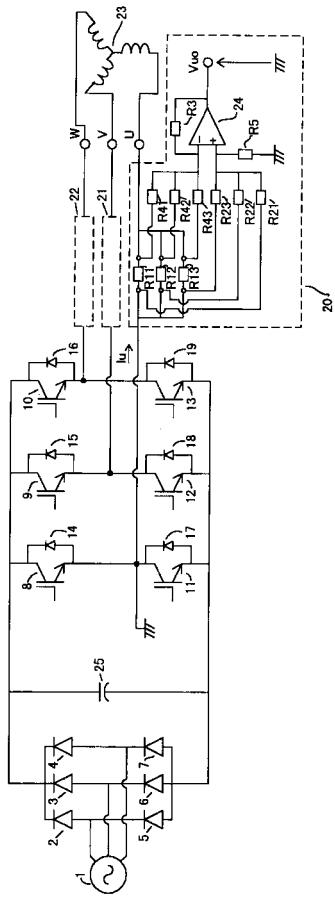

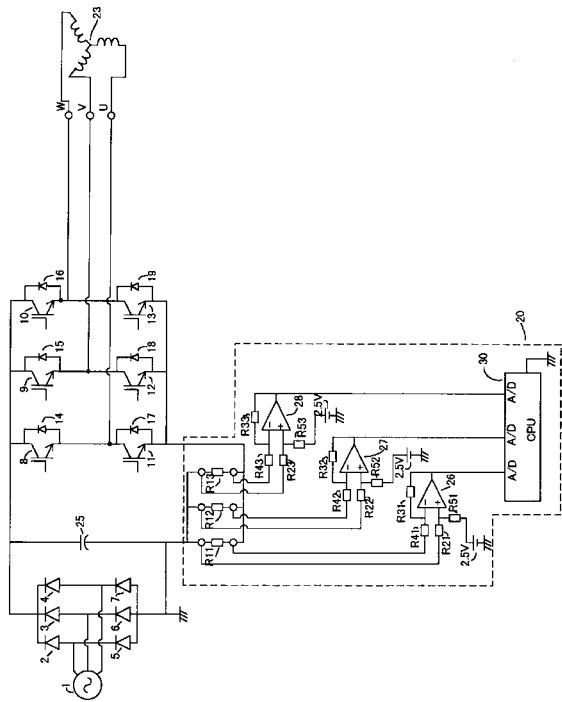

以下、本発明の第 1 の実施例を図 1 に基づいて説明する。1 は商用交流電源、2 ~ 7 は全波整流ブリッジを構成する整流用ダイオード、8 ~ 13 はインバータ主回路を構成する IGBTトランジスタ、14 ~ 19 は各 IGBTトランジスタ素子に逆並列接続される還流ダイオード、20 は U 相電流を検出する電流検出器、21 は V 相の電流検出器、22 は W 相の電流検出器、23 はモータ、24 はオペアンプ、25 は直流電源、R11、R12、R13 は U 相電流を分流する抵抗、U、V、W はインバータ装置の各々の出力端子である。

30

次に動作を説明する。図 1において、インバータの U 相出力電流（以下これを  $I_u$  とする）は抵抗値の小さい小型抵抗 R11、R12、R13 を流れて外部負荷であるモータ 23 へと供給される。この電流  $I_u$  は、抵抗 R11、R12、R13 とを分離分割して流れることとなるが、この各抵抗を流れる電流をそれぞれ  $I_{u1}$ 、 $I_{u2}$ 、 $I_{u3}$  とすると各抵抗端子間にはこの電流に比例した端子間電圧がそれぞれに発生しており、また銅パターンによるインピーダンスの影響でコモンモード端子電圧  $V_{u1}$ 、 $V_{u2}$ 、 $V_{u3}$  もそれぞれ発生している。

40

従って、例えば抵抗 R11 の両側端子では、それぞれに  $V_{u1}$  と ( $V_{u1} - I_{u1} \times R11$ ) の端子電圧が発生していることとなる。

この端子電圧は抵抗 R21、抵抗 R41 を介してそれぞれオペアンプ 24 の正負入力端子に接続されている。同様に抵抗 R12 の端子電圧は抵抗 R22、抵抗 R42 を介して、抵抗 R13 の端子電圧は抵抗 R23、抵抗 R43 を介してそれぞれオペアンプ 24 の正負入力端子に接続されている。

そして各抵抗の抵抗値を

$$R_{11} = R_{12} = R_{13}$$

50

$$R_{41} = R_{42} = R_{43} = R_{21} = R_{22} = R_{23}$$

$$R_3 = R_5$$

に設定するとオペアンプ24の出力電圧 $V_{uo}$ は

$$\begin{aligned} V_{uo} &= (I_{u1} + I_{u2} + I_{u3}) \times R_{11} \times R_3 / R_{41} \\ &= I_u \times R_{11} \times R_3 / R_{41} \end{aligned}$$

となるので、この $V_{uo}$ にはプリント基板の銅パターンによるインピーダンスの影響を含まない抵抗の端子間電圧のみが増幅抽出され、この値から被検出電流 $I_u$ を高精度で検出することが可能となる。

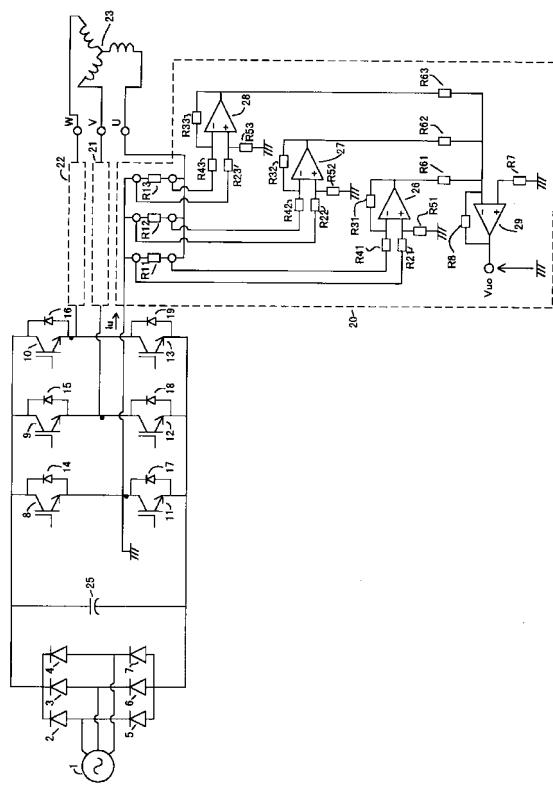

#### 【0017】

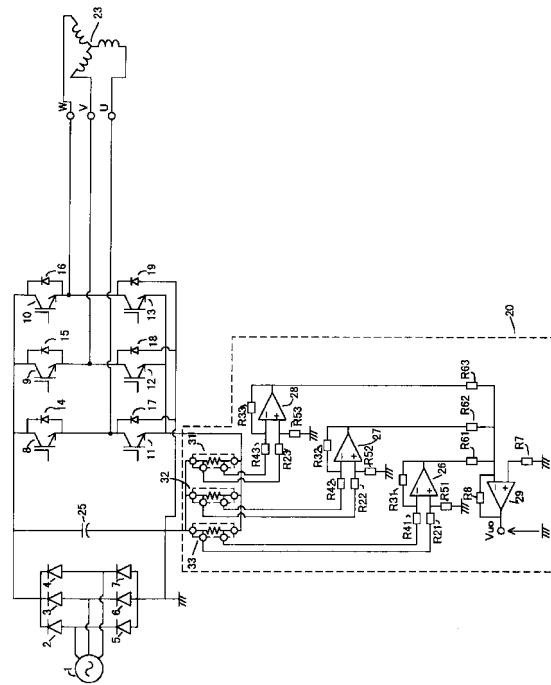

次に本発明の第2の実施例を図2に基づいて説明する。図2において、インバータのU相出力電流（以下これを $I_u$ とする）は抵抗値の小さい小型抵抗 $R_{11}$ 、抵抗 $R_{12}$ 、抵抗 $R_{13}$ を流れて外部負荷であるモータ23へと供給される。この電流 $I_u$ は、抵抗 $R_{11}$ 、 $R_{12}$ 、 $R_{13}$ とを分離分割して流れることとなるが、この各抵抗を流れる電流をそれぞれ $I_{u1}$ 、 $I_{u2}$ 、 $I_{u3}$ とすると各抵抗端子間にはこの電流に比例した端子間電圧がそれぞれに発生しており、また銅パターンによるインピーダンスの影響でコモンモード端子電圧 $V_{u1}$ 、 $V_{u2}$ 、 $V_{u3}$ もそれぞれ発生している。

従って例えば抵抗 $R_{11}$ の両側端子では、各々に $V_{u1}$ と $(V_{u1} - I_{u1} \times R_{11})$ の端子電圧とが発生していることとなる。

この端子電圧は抵抗 $R_{21}$ 、抵抗 $R_{41}$ を介してそれぞれオペアンプ26の正負入力端子に接続されている。同様に抵抗 $R_{12}$ の端子電圧は抵抗 $R_{22}$ 、抵抗 $R_{42}$ を介してそれぞれオペアンプ27の正負入力端子に、抵抗 $R_{13}$ の端子電圧は抵抗 $R_{23}$ 、抵抗 $R_{43}$ を介してそれぞれオペアンプ28の正負入力端子に接続されている。

#### 【0018】

そして各抵抗の抵抗値を

$$R_{11} = R_{12} = R_{13}$$

$$R_{41} = R_{42} = R_{43} = R_{21} = R_{22} = R_{23}$$

$$R_{31} = R_{32} = R_{33} = R_{51} = R_{52} = R_{53}$$

に設定するとオペアンプ26、27、28の各出力電圧 $V_{o1}$ 、 $V_{o2}$ 、 $V_{o3}$ は

$$V_{o1} = I_{u1} \times R_{11} \times R_{31} / R_{41}$$

$$V_{o2} = I_{u2} \times R_{12} \times R_{32} / R_{42}$$

$$= I_{u2} \times R_{11} \times R_{31} / R_{41}$$

$$V_{o3} = I_{u3} \times R_{13} \times R_{33} / R_{43}$$

$$= I_{u3} \times R_{11} \times R_{31} / R_{41}$$

となる。さらに

$$R_{61} = R_{62} = R_{63}$$

と設定することで、オペアンプ29によりこれら $V_{o1}$ 、 $V_{o2}$ 、 $V_{o3}$ とを加算しその出力電圧 $V_{uo}$ として

$$V_{uo} = -R_8 / R_{61} \times (V_{o1} + V_{o2} + V_{o3})$$

$$= - (I_{u1} + I_{u2} + I_{u3}) \times R_8 / R_{61} \times R_{11} \times R_{31} / R_{41}$$

1

$$= - I_u \times R_8 / R_{61} \times R_{11} \times R_{31} / R_{41}$$

を得ることができる。

#### 【0019】

この $V_{uo}$ にはプリント基板の銅パターン等による影響を含まない抵抗の端子間電圧のみ

10

20

30

40

50

が増幅抽出されることになり、しかも大きな端子間電圧を得ることができるので被検出電流  $I_u$  を高精度で検出することが可能となる。

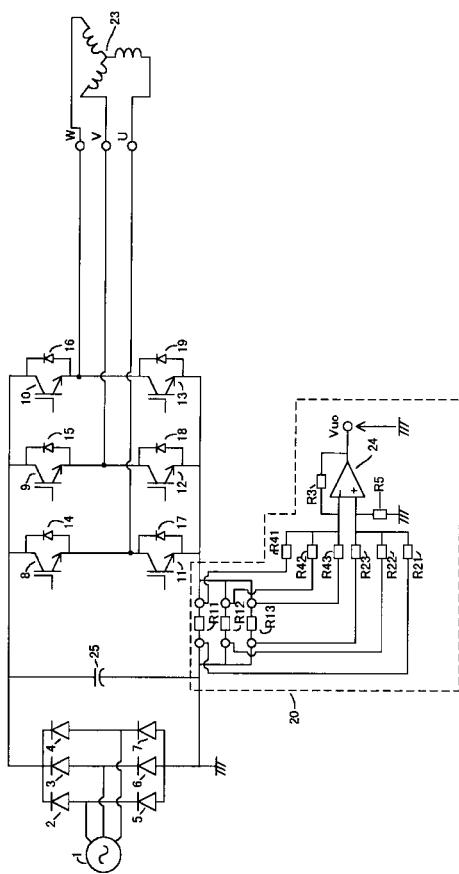

次に本発明の第 3 の実施例を図 3 に基づいて説明する。

これは第 1 の実施例である図 1 の構成に対し検出抵抗 R<sub>11</sub>, R<sub>12</sub>, R<sub>13</sub> の位置を直流電源の負極側に配置して被検出電流を変更しただけのものであり検出構成および効果は前記と同様である。

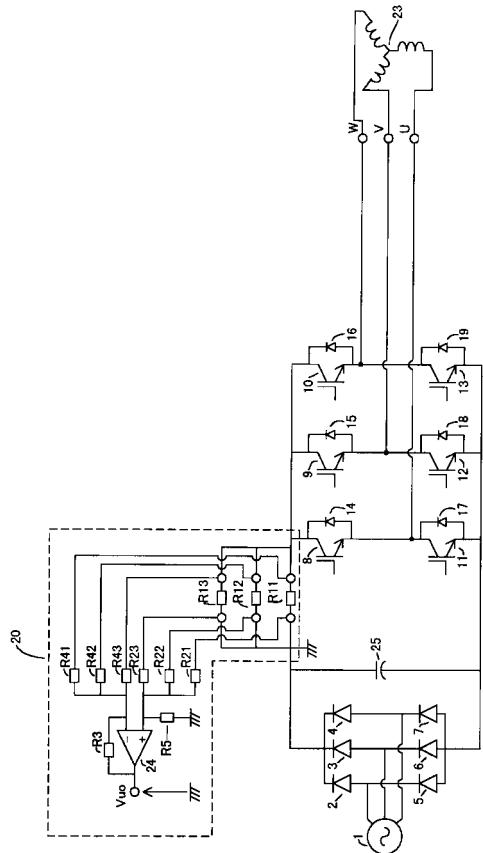

次に本発明の第 4 の実施例を図 4 に基づいて説明する。

これは第 1 の実施例である図 1 の構成に対し検出抵抗 R<sub>11</sub>, R<sub>12</sub>, R<sub>13</sub> の位置を直流電源の正極側に配置して被検出電流を変更しただけのものであり検出構成および効果は前記と同様である。

10

#### 【0020】

次に本発明の第 5 の実施例を図 5 に基づいて説明する。これは第 2 の実施例である図 2 の構成に対し検出抵抗 R<sub>11</sub>, R<sub>12</sub>, R<sub>13</sub> の位置を直流電源の負極側に配置して被検出電流を変更し、かつ加算器を第 2 の実施例におけるようなオペアンプではなくて CPU30 の A/D 変換ポートからオペアンプ 1, 2, 3 の各出力電圧を取り込み CPU30 の内部で演算加算して電流検出を行なう構成としている。

次に本発明の第 6 の実施例を図 6 に基づいて説明する。

これは第 2 の実施例である図 2 の構成に対し検出抵抗 3<sub>1</sub>, 3<sub>2</sub>, 3<sub>3</sub> に 4 端子構造の抵抗（図 9 および図 10）を使用し、また検出抵抗 3<sub>1</sub>, 3<sub>2</sub>, 3<sub>3</sub> の位置を直流電源の負極側に配置して被検出電流を変更し、かつ還流ダイオード 1<sub>7</sub>, 1<sub>8</sub>, 1<sub>9</sub> のアノード側端子を直流電源の負極側に接続変更したものである。4 端子構造の抵抗により、その電流端子部の半田接続で発生する当該部分のインピーダンスの影響を削除することができ、より精度の高い電流検出を行うことができる。またこの、電流を導通させる端子対と電圧信号を取り出す端子対とをもつ 4 端子構造一体型の抵抗は前記第 1 の実施例ないし第 5 の実施例においてもそのまま適用することが可能であり、この場合には前記同様にさらに精度の高い電流検出を行うことが可能となる。

20

#### 【0021】

##### 【発明の効果】

以上述べたように本発明によれば、被検出大電流用の検出抵抗を並列接続された小型かつ抵抗値の小さな抵抗のみで構成でき、また検出用抵抗が並列接続でありながらプリント基板の銅パターンインピーダンスによる影響を含まない、従って抵抗の端子間電圧のみを増幅抽出でき、さらには小さな抵抗値でありながら大きな抵抗端子間電圧を得ることができ、従って増幅器の入力オフセット電圧等の影響も低減できるという効果がある。すなわち大きな被検出電流に対しても誤差の少ない、しかも小型サイズの電流検出器を構成でき、超小型のインバータ装置を提供できる。

30

##### 【図面の簡単な説明】

【図 1】本発明の第 1 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

【図 2】本発明の第 2 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

40

【図 3】本発明の第 3 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

【図 4】本発明の第 4 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

【図 5】本発明の第 5 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

【図 6】本発明の第 6 の実施例におけるインバータ装置の電流検出器の構成図を示したもの

【図 7】第 1 の抵抗群を並列接続した際ににおけるプリント基板の銅パターンの影響を示したもの

50

【図8】請求項1記載の構成における本発明の作用効果の説明用構成図を示したもの

【図9】電流端子部と検出電圧出力部とを別々に備えた4端子構造による抵抗の外観図を示したもの

【図10】4端子構造による抵抗の内部回路図を示したもの

【図11】従来例におけるインバータ装置の電流検出器の構成図を示したもの

【符号の説明】

|                                                    |    |

|----------------------------------------------------|----|

| 1 商用交流電源                                           |    |

| 2、3、4、5、6、7 整流用ダイオード                               |    |

| 8、9、10、11、12、13 IGBTトランジスタ                         | 10 |

| 14、15、16、17、18、19 還流ダイオード                          |    |

| 20、21、22 電流検出器                                     |    |

| 23 モータ                                             |    |

| 24、26、27、28、29 オペアンプ                               |    |

| 25 直流電源                                            |    |

| 30 CPU                                             |    |

| 31、32、33 4端子構造の抵抗                                  |    |

| R3、R5、R7、R8、R11、R12、R13、R21R、R22、R23 抵抗            |    |

| R31、R32、R33、R41、R42、R43、R51、R52、R53、R61、R62、R63 抵抗 |    |

| R1a、R1b、R1c 並列接続された第1の抵抗群を構成する各抵抗                  | 20 |

| R2a、R4a、R2b、R4b、R2c、R4c 抵抗                         |    |

| Za0、Zb0、Zc0、Za1、Zb1、Zc1 プリント基板の銅パターンによるインピーダンス     |    |

| U インバータ装置のU相出力端子                                   |    |

| V インバータ装置のV相出力端子                                   |    |

| W インバータ装置のW相出力端子                                   |    |

| T1、T2 IGBTトランジスタ                                   |    |

| T4、T5、T6 MOSFET                                    |    |

| R101、R102、R103、R104、R105、R106、R107 抵抗              |    |

| Rs シャント抵抗                                          | 30 |

| GDU1、GDU2 ゲート駆動回路                                  |    |

| OP1、OP2 オペアンプ                                      |    |

| 101 反転ゲート                                          |    |

| 102、103 制御電源                                       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【図11】

---

フロントページの続き

(56)参考文献 特開平06-315273(JP,A)

実開平02-128964(JP,U)

特開平04-156705(JP,A)

特開平04-290965(JP,A)

特開平05-223906(JP,A)

特開平06-284747(JP,A)

特開2000-133501(JP,A)

特開平10-123184(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 7/5387

G01R 15/14

G01R 19/165