(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6523294号

(P6523294)

(45) 発行日 令和1年5月29日(2019.5.29)

(24) 登録日 令和1年5月10日(2019.5.10)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/146

A

H04N 5/369 (2011.01)

H04N 5/369

H04N 5/374 (2011.01)

H04N 5/374

請求項の数 8 (全 37 頁)

(21) 出願番号 特願2016-541737 (P2016-541737)

(86) (22) 出願日 平成27年1月14日 (2015.1.14)

(65) 公表番号 特表2017-504966 (P2017-504966A)

(43) 公表日 平成29年2月9日 (2017.2.9)

(86) 國際出願番号 PCT/JP2015/000129

(87) 國際公開番号 WO2015/111389

(87) 國際公開日 平成27年7月30日 (2015.7.30)

審査請求日 平成29年12月8日 (2017.12.8)

(31) 優先権主張番号 61/929,842

(32) 優先日 平成26年1月21日 (2014.1.21)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/567,777

(32) 優先日 平成26年12月11日 (2014.12.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 316005926

ソニーセミコンダクタソリューションズ株

式会社

神奈川県厚木市旭町四丁目14番1号

(74) 代理人 100121131

弁理士 西川 孝

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 井本 努

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 馬渕 圭司

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】撮像素子、および電子装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域と

を備え、

前記光起電力型画素は、さらに、転送ゲートおよびフローティングディフュージョンを有し、蓄積型兼光起電力型画素として動作する

撮像素子。

## 【請求項 2】

前記素子分離領域は、前記光起電力型画素の信号電荷の隣接画素への拡散を阻止する材料により構成されている

請求項1に記載の撮像素子。

## 【請求項 3】

前記光起電力型画素に隣接する位置に蓄積型画素を

さらに備える請求項1または請求項2に記載の撮像素子。

## 【請求項 4】

前記光電変換領域には、フォトセンサとしてPN接合ダイオードが形成されている

請求項1乃至請求項3の何れか一項に記載の撮像素子。

## 【請求項 5】

10

20

前記蓄積型兼光起電力型画素に隣接する位置に蓄積型画素を

さらに備える請求項1乃至請求項4の何れか一項に記載の撮像素子。

【請求項6】

各画素における前記光電変換領域と画素回路領域との間は絶縁されている

請求項1乃至請求項5の何れか一項に記載の撮像素子。

【請求項7】

撮像素子が搭載された電子装置において、

前記撮像素子は、

画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と

、

隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域と

を備え、

前記光起電力型画素は、さらに、転送ゲートおよびフローティングディフュージョンを有し、蓄積型兼光起電力型画素として動作する

電子装置。

【請求項8】

画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、

隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域と、

前記光電変換領域、転送ゲート、およびフローティングディフュージョンを有する蓄積型兼光起電力型画素と

を備え、

前記光起電力型画素と前記蓄積型兼光起電力型画素は隣接して形成されている

撮像素子。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、撮像素子、および電子装置に関し、特に、PN接合ダイオードに起因するクロストーク等の問題を解決できるようにした撮像素子、および電子装置に関する。

【背景技術】

【0002】

従来、デジタルカメラに代表される撮像機能を有する電子装置に搭載される撮像素子として電荷蓄積型撮像素子（以下、蓄積型撮像素子と称する）が知られている。

【0003】

蓄積型撮像素子では、過剰な光が入射して蓄積電荷量が飽和電荷量を超えると、信号電荷の過剰分は、オーバーフローバリアを超えてN型基板に流れ込むか、または、転送ゲート下のポテンシャルバリアを超えてフローティングディフュージョンに流れ込むことになる。したがって、該蓄積型撮像素子のダイナミックレンジは電荷蓄積領域の飽和電荷量により制限されるので、大きなダイナミックレンジを実現することが困難であり、その結果、白とびや黒潰れが起き易いという問題があった。

【0004】

そこで、そのような問題を解決可能な固体撮像として、光起電力型画素から成る対数型センサが提案されている（例えば、特許文献1または2を参照）。

【0005】

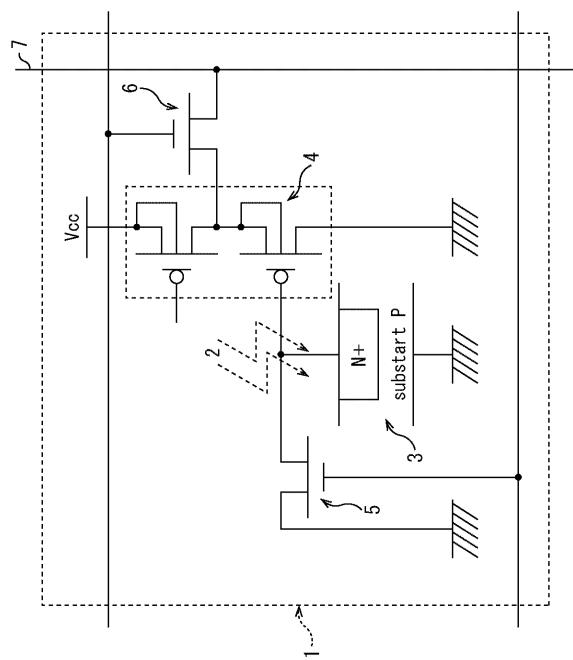

図1は、特許文献1に開示されている、対数型センサを構成する光起電力型画素の1画素分の等価回路を示している。

【0006】

該光起電力型画素1においては、PN接合ダイオード3により、入射光2に応じた光電流値の対数に比例した光起電力が発生され、発生された光起電力はアンプ4により増幅され

10

20

30

40

50

て画像信号とされ、発生された画像信号はスイッチ 6 を介して垂直信号線 7 に出力される。なお、PN接合ダイオード 3 は、スイッチ 5 によりリセットされる。

【0007】

このように、光起電力型画素 1 では、発生された画像信号が蓄積されることなく後段に出力されるので、過剰な入射光 2 が入射しても画素信号が飽和することはない。

【0008】

なお光起電力型画素 1 は、蓄積型として動作することができる。

【先行技術文献】

【特許文献】

【0009】

10

【特許文献 1】EP 1 354 360

【特許文献 2】US 2011/0025898 A1

【発明の概要】

【発明が解決しようとする課題】

【0010】

ただし、該光起電力型画素 1 を解析した結果、以下の欠点が見出された。

【0011】

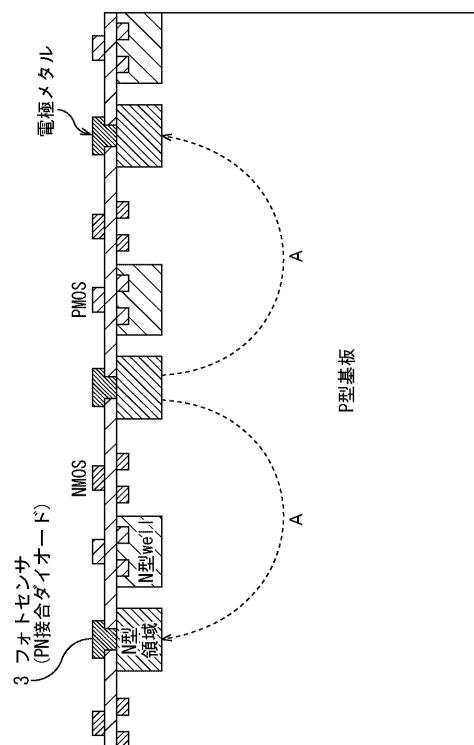

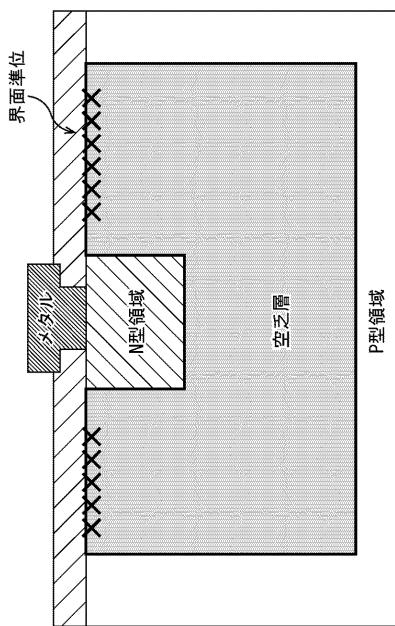

一つ目の欠点としては、いわゆるクロストークが挙げられる。図 2 は、図 1 に示された光起電力型画素の画素構造の一例を示す断面図であり、クロストークの発生の概要を示している。

20

【0012】

具体的には、入射光 2 に応じて光起電力が発生すると、フォトセンサであるPN接合ダイオードが順方向にバイアスされ、この結果、電子がN型領域からP型基板に拡散するので、図 2 の点線矢印 A に示されるように、拡散した電子が隣接するフォトセンサ (PN接合ダイオード) に到達する可能性がある。この場合、隣接画素も光起電力型画素であるのでクロストークが生じてしまう。なお、図示は省略するが、仮に該光起電力型画素 1 の隣接画素が蓄積型画素であったとしても、同様にクロストークが生じてしまう。

【0013】

二つめの欠点としては、画素信号量の温度変化が大きいことが挙げられる。画素信号電圧  $V_{PD}$  は次式 (1) によって表すことができる。

30

【数 1】

$$V_{PD} = -\frac{kT}{q} \ln \left( \frac{I_\lambda}{I_s} + 1 \right) \dots (1)$$

【0014】

ここで、 $I_\lambda$  は光電流であり、 $I_s$  はPN接合ダイオード 3 における逆方向飽和電流であって温度上昇に伴って指数的に増加する値である。よって、温度の上昇によって  $I_s$  が指数的に増加すると、画素信号電圧  $V_{PD}$  は顕著に低下する。

40

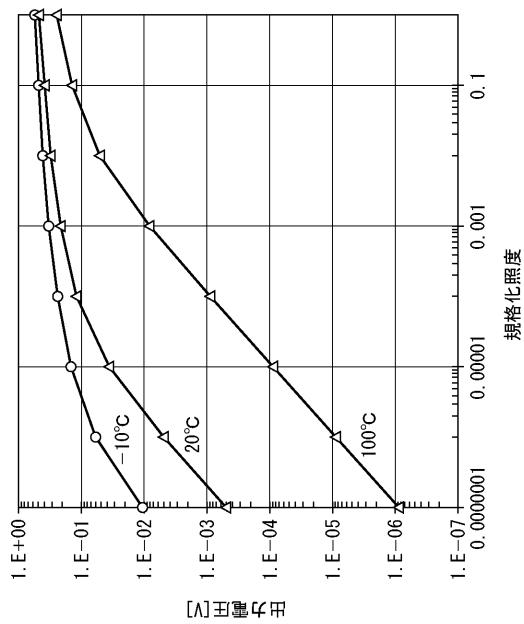

【0015】

より具体的に説明する。図 3 は、図 1 に示された光起電力型画素 1 の各温度における入射光の照度 (規格化済) と、PN接合ダイオード 3 の出力電圧の関係を示している。図 3 からも、温度が低下した場合、同じ照度であっても発生電圧が顕著に低下していることが分かる。

【0016】

三つめの欠点としては、低照度感度が低く、ばらつき抑制が困難であることが挙げられる。感度を高めるためには、式 (1) から明らかなように、 $I_s$  を下げる必要がある。しかしながら、 $I_s$  は汚染不純物や結晶欠陥によって増加することが知られており、これらの

50

抑制には、高度のプロセス制御を要するのでコスト高となってしまう。

【0017】

四つ目の欠点としては、光起電力型画素1が蓄積型として動作する場合に暗電流が大きくなってしまうことが挙げられる。

【0018】

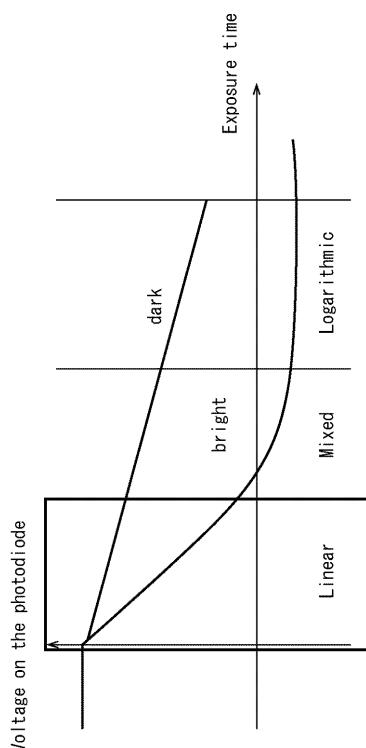

図4は、光起電力型画素1の照射時間と出力電圧の関係を示している（特許文献2、Fig.2）。

【0019】

蓄積型として動作する場合は同図のLinear領域に相当するが、暗電流の発生が確認できる。

10

【0020】

より具体的に説明する。図5は、図3に示された光起電力型画素1のフォトセンサ（PN接合ダイオード3）付近の逆バイアス時の拡大図である。光起電力型画素1を蓄積型として動作させる場合、フォトセンサを逆バイアスすることになるが、この場合、同図に示されるように空乏層が広がってSi/SiO<sub>2</sub>界面が空乏層の中に位置するため、界面準位の影響で暗電流が増加してしまうことになる。

【0021】

本開示はこのような状況に鑑みてなされたものであり、広ダイナミックレンジを実現しつつ、低照度感度と低照度S/Nに優れ、クロストークの少ない撮像素子を実現するものである。

20

【課題を解決するための手段】

【0022】

本開示の第1の側面である撮像素子は、画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域とを備え、前記光起電力型画素は、さらに、転送ゲートおよびフローティングディフュージョンを有し、蓄積型兼光起電力型画素として動作する。

【0023】

前記素子分離領域は、前記光起電力型画素の信号電荷の隣接画素への拡散を阻止する材料により構成することができる。

30

【0024】

本開示の第1の側面である撮像素子は、前記光起電力型画素に隣接する位置に蓄積型画素をさらに備えることができる。

【0025】

前記光電変換領域には、フォトセンサとしてPN接合ダイオードが形成することができる。

【0027】

本開示の第1の側面である撮像素子は、前記蓄積型兼光起電力型画素に隣接する位置に蓄積型画素をさらに備えることができる。

【0029】

各画素における前記光電変換領域と画素回路領域との間は絶縁されているようにすることができる。

【0030】

本開示の第2の側面である電子装置は、撮像素子が搭載された電子装置において、前記撮像素子が、画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域とを備え、前記光起電力型画素は、さらに、転送ゲートおよびフローティングディフュージョンを有し、蓄積型兼光起電力型画素として動作する。

40

本開示の第3の側面である撮像素子は、画素毎に照射光に応じて光起電力を発生する光

50

電変換領域を有する光起電力型画素と、隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域と、前記光電変換領域、転送ゲート、およびフローティングディフュージョンを有する蓄積型兼光起電力型画素とを備え、前記光起電力型画素と前記蓄積型兼光起電力型画素は隣接して形成されている。

【0031】

本開示の第1および第2の側面においては、画素毎に設けられた光電変換領域によって照射光に応じて光起電力が発生され、隣接する画素それぞれの前記光電変換領域の間に設けられ、前記光電変換領域を取り囲む状態で設けられた素子分離領域により、前記光起電力によって生じた拡散電流の隣接画素への到達が阻止される。また、前記光起電力型画素には、さらに、転送ゲートおよびフローティングディフュージョンが設けられ、蓄積型兼光起電力型画素として動作する。

10

本開示の第3の側面においては、画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を取り囲む状態で設けられた素子分離領域と、前記光電変換領域、転送ゲート、およびフローティングディフュージョンを有する蓄積型兼光起電力型画素とが設けられ、前記光起電力型画素と前記蓄積型兼光起電力型画素は隣接して形成される。

【発明の効果】

【0032】

本開示の第1の側面および第3の側面によれば、画素間のクロストークを抑止することができる。

20

【0033】

本開示の第2の側面によれば、低照度時の感度とS/Nに優れた画像を得ることができる。

【図面の簡単な説明】

【0034】

【図1】対数型センサを構成する光起電力型画素の1画素分の等価回路図である。

【図2】図1の等価回路に対応する画素構造の断面図である。

【図3】同じ照度に対する各温度での発生電圧を示す図である。

【図4】光起電力型画素の照射時間と出力電圧の関係を示す図である。

【図5】逆バイアス時にフォトセンサに生じる空乏層の広がりを示す図である。

30

【図6】本開示の第1の実施の形態である光起電力型画素の等価回路図である。

【図7】図6の光起電力型画素に対応する画素構造の上面図である。

【図8】図6の光起電力型画素に対応する画素構造の断面図である。

【図9】図6の光起電力型画素に対応する画素構造の断面図である。

【図10】図6の光起電力型画素を表面照射型撮像素子に適用した場合の第1の構成例を示す断面図である。

【図11】図10の第1の構成例の変形例を示す断面図である。

【図12】図6の光起電力型画素を表面照射型撮像素子に適用した場合の第2の構成例を示す断面図である。

【図13】図6の光起電力型画素を表面照射型撮像素子に適用した場合の第3の構成例を示す断面図である。

40

【図14】図6の光起電力型画素を表面照射型撮像素子に適用した場合の第4の構成例を示す断面図である。

【図15】図6の光起電力型画素を裏面照射型撮像素子に適用した場合の第5の構成例を示す断面図である。

【図16】図15に示された第5の構成例の第1の変形例を示す断面図である。

【図17】図15に示された第5の構成例の第2の変形例を示す断面図である。

【図18】図6の光起電力型画素を裏面照射型撮像素子に適用した場合の第6の構成例を示す断面図である。

【図19】図6の光起電力型画素を裏面照射型撮像素子に適用した場合の第7の構成例を

50

示す断面図である。

【図20】図19の第7の構成例の変形例を示す断面図である。

【図21】第1乃至第7の構成例の等価回路図である。

【図22】光起電力型画素と蓄積型画素を同一の垂直信号性に接続した撮像素子の構成例を示す図である。

【図23】光起電力型画素と蓄積型画素をそれぞれ異なる垂直信号性に接続した撮像素子の構成例を示す図である。

【図24】光起電力型画素の駆動タイミングの一例を示す図である。

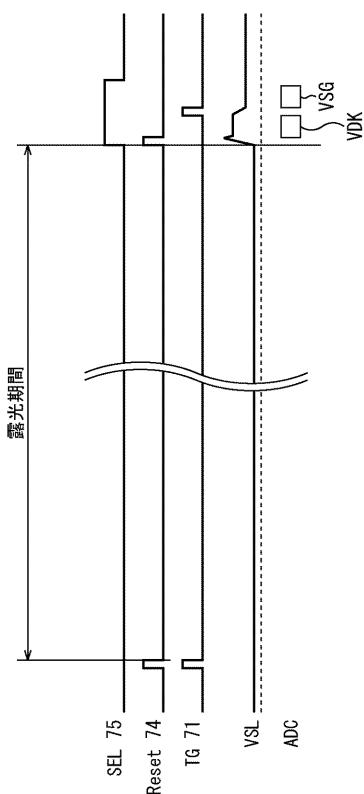

【図25】蓄積型画素の駆動タイミングの一例を示す図である。

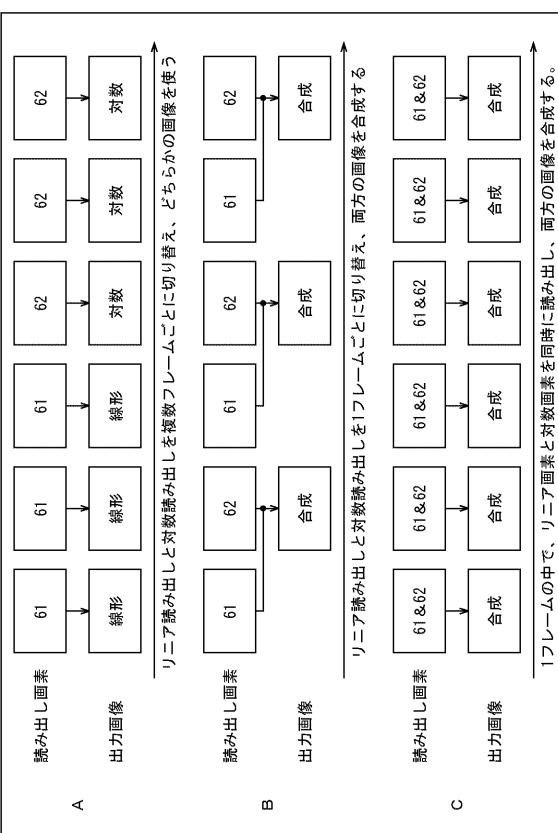

【図26】光起電力型画素と蓄積型画素が搭載された撮像素子の出力画像の例を示す図である。 10

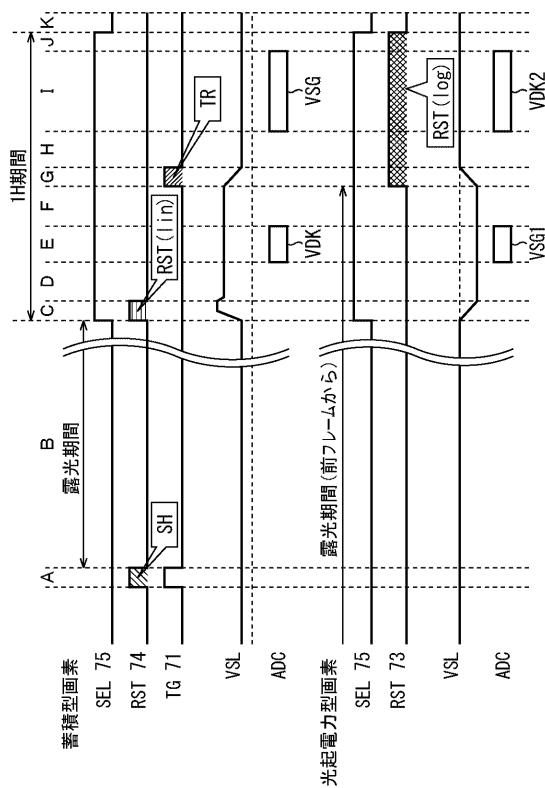

【図27】図26Cに示された出力画像を得るための駆動タイミングの一例を示す図である。

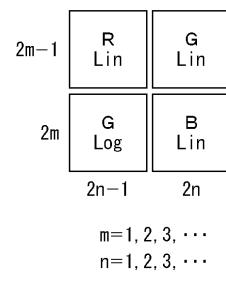

【図28】光起電力型画素と蓄積型画素の配列の一例を示す図である。

【図29】図28の配列例に対応する駆動タイミングを示す図である。

【図30】光起電力型画素と蓄積型画素の配列の他の例示す図である。

【図31】本開示の第2の実施の形態である蓄積型兼光起電力型画素の等価回路図である。

【図32】図31の蓄積型兼光起電力型画素に対応する画素構造の上面図である。

【図33】図31の蓄積型兼光起電力型画素に対応する画素構造の断面図である。 20

【図34】図31の蓄積型兼光起電力型画素のポテンシャル分布図である。

【図35】図31の蓄積型兼光起電力型画素のポテンシャル分布図である。

【図36】図31の蓄積型兼光起電力型画素を表面照射型撮像素子に適用した場合の第8の構成例を示す断面図である。

【図37】図31の蓄積型兼光起電力型画素を裏面照射型撮像素子に適用した場合の第9の構成例を示す断面図である。

【図38】図31のアンプに採用可能な第1の構成例を示す等価回路図である。

【図39】図31のアンプに採用可能な第1の構成例を示す等価回路図である。

【図40】本開示の第2の実施の形態である蓄積型兼光起電力型画素の他の等価回路図である。 30

【図41】蓄積型兼光起電力型画素が蓄積型画素として動作する場合のタイミングチャートである。

【図42】蓄積型兼光起電力型画素が光起電力型画素として動作する場合のタイミングチャートである。

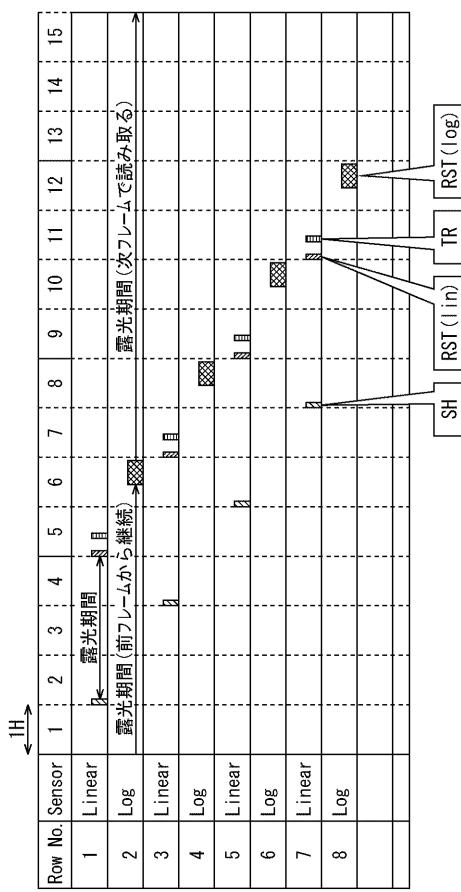

【図43】1フレーム内で蓄積型と光起電力型の画素出力を行毎に切り替える場合のタイミングチャートである。

【図44】1フレーム内で蓄積型と光起電力型の画素出力を行毎に切り替える場合のタイミングチャートである。

【図45】1フレーム内で蓄積型と光起電力型の画素出力を行毎に切り替えた場合に得られる効果を説明するための図である。 40

【図46】図46の駆動タイミングでより高いフレームレートを得るための等価回路図である。

【図47】より高いフレームレートを表すタイミングチャートである。

【図48】図46の回路構成を採用し、異なる行から同時に蓄積型の画素信号と光起電力型の画素信号を出力する場合の駆動タイミングチャートである。

【図49】1フレーム内の同じ行で列単位に蓄積型の駆動タイミングと光起電力型の駆動タイミングを選択するための選択回路の構成例を示す図である。

【図50】1フレーム内の同じ行で列単位に蓄積型の駆動タイミングと光起電力型の駆動タイミングを選択した場合に得られる効果を説明するための図である。

【図51】1フレーム内の全画素から蓄積型画素信号と光起電力型画素信号の両方を出力

50

する場合のタイミングチャートである。

【図52】1フレーム内の全画素から蓄積型画素信号と光起電力型画素信号の両方を出力する場合に得られる効果を説明するための図である。

【図53】PN接合ダイオード11の出力電圧特性を示す図である。

【図54】光起電力型画素の出力値の較正方法の概要を示す図である。

【発明を実施するための形態】

【0035】

以下、本開示を実施するための最良の形態（以下、実施の形態と称する）について、図面を参照しながら詳細に説明する。

【0036】

<1. 第1の実施の形態>

第1の実施の形態である光起電力型画素について、図面を参照しながら説明する。なお、各図面において共通する部位については適宜、同一の符号を付しているものとする。

【0037】

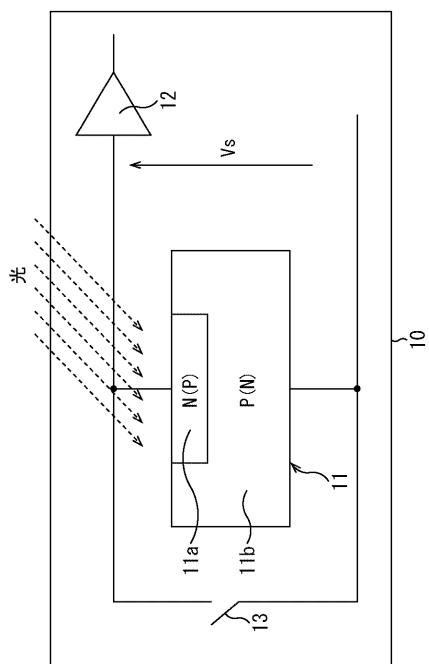

図6は、第1の実施の形態である光起電力型画素の等価回路を示している。該光起電力型画素10は、PN接合ダイオード11、アンプ12、およびスイッチ13を有する。PN接合ダイオード11は、入射光に応じた光電流値の対数に比例した光起電力を発生する。アンプ12は、発生された光起電力を増幅し、その結果得られる画素信号を後段に出力する。スイッチ13は、PN接合ダイオード11を短絡させることにより、暗時のダイオード出力電圧を発生させる。

【0038】

なお、図6の等価回路では、N型領域に発生する光起電力をアンプ12で増幅し、信号電圧としているが、図6のN型領域とP型領域の導電型をカッコ内の表示のように入れ替え、P型領域に発生する電圧を信号電圧に用いてもよい。以下の説明では、特に断らない限り、N型領域の電位を信号電圧として用いる場合を例に用いて説明する。

【0039】

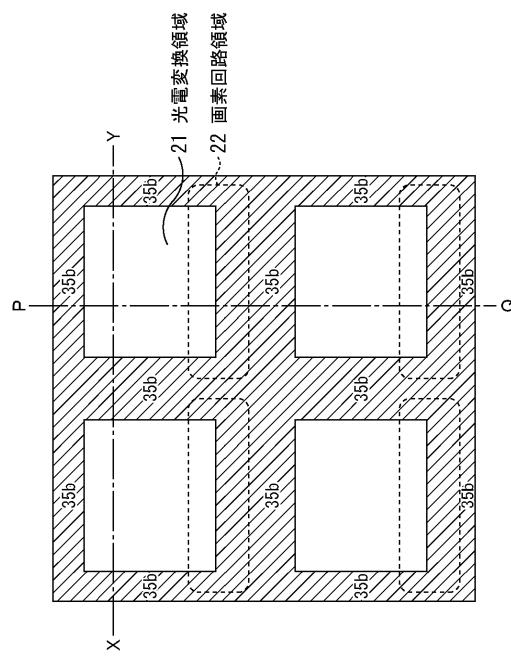

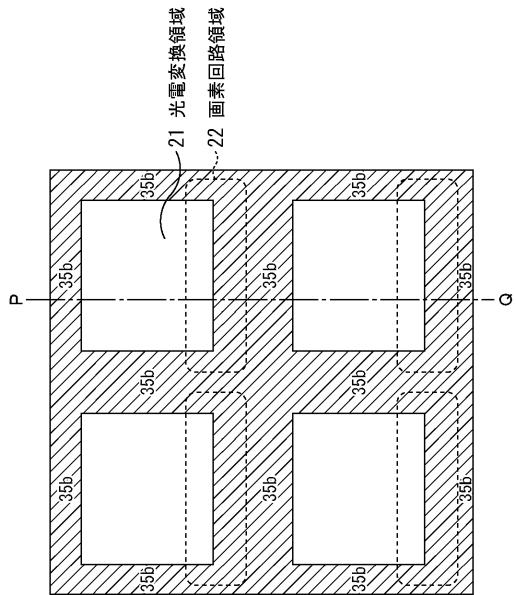

図7は、図6に等価回路が示された光起電力型画素10に対応する画素構造の2×2画素分の上面配置図を示している。

【0040】

図示されるように、光起電力型画素10は素子分離領域35によって分離される光電変換領域21を有する。光電変換領域21には、図6にしめされたPN接合ダイオード11が形成される。光電変換領域21や素子分離領域35と重なる画素内の適切な領域には画素回路領域22を設けることができ、画素回路領域22には、PN接合ダイオード11以外のアンプ12、スイッチ13などを形成することができる。

【0041】

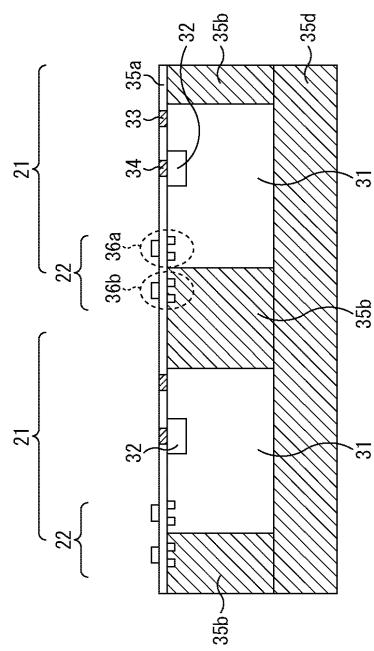

図8は図7の線分XYにおける画素構造の断面を、図9は図7の線分PQにおける画素構造の断面を示している。図8および図9の断面図からも明らかなように、光電変換領域21と光電変換領域21の間は素子分離領域35によって分離されている。

【0042】

光電変換領域21に形成されるPN接合ダイオード11は、具体的には、図9に示されるように、P型領域31、N型領域32、P型領域31にオーミック接触する電極33、およびN型領域32にオーミック接触する電極34から成る。

【0043】

P型領域31は、例えば、アクセプタ不純物が導入されたSi, Ge等のIV族半導体、GaAs, InP, InGaAs等のIII-V族半導体、または、Hg, Zn, Cd, Te等から選択されるII-VI族半導体である。

【0044】

N型領域32は、例えば、ドナー不純物が導入されたSi, Ge等のIV族半導体、GaAs, InP, InGaAs等のIII-V族半導体、または、Hg, Zn, Cd, Te等から選択されるII-VI族半導体である。

10

20

30

40

50

## 【0045】

電極33および34は、それぞれ接触されるP型領域31またはN型領域32の材料に応じて選択される。例えば、P型領域31およびN型領域32がSiである場合、電極33および34として、例えばAl, Ti/W積層膜などが選択される。

## 【0046】

素子分離領域35は、隣接する光電変換領域21(PN接合ダイオード11)間と、隣接する光電変換領域21間のリーク電流を抑制するために形成される。よって、素子分離領域35は、光電変換領域21(PN接合ダイオード11)の周囲を実質的に取り囲むように配置される。

## 【0047】

なお、P型領域31の上下に配置される素子分離領域35aまたは35dの少なくとも一方は、PN接合ダイオード11に対して入射光を到達させるために光透過性を有するものとする。

## 【0048】

素子分離領域35は、以下のいずれかの材料、または、それらを組み合わせて構成する。

絶縁性材料(SiO<sub>2</sub>, SiN, BSG, PSG, SiON等)

導電性半導体(例えば、PN接合ダイオード11がSiである場合には、P型領域31と逆導電型のn-Si等)

金属(P型領域31に対するオーム電極、ショットキー電極)

## 【0049】

なお、素子分離領域35としての導電性半導体には、PN接合ダイオード11のP型領域31またはN型領域32と同一材料であってもよいし、異種の半導体材料で構成し、ヘテロ接合を形成してもよい。同一材料とする場合は、P型領域31と逆導電型のN型領域とする。または、光電変換領域と素子分離領域をGaAsなどのIII-V族半導体で構成する場合は、素子分離領域35にホウ素などを高濃度にイオン注入し、結晶性を劣化させることで高抵抗化した材料を使うことができる。

## 【0050】

上述したように、素子分離領域35を設けたことにより、N型領域32からP型領域31に拡散した電子や、P型領域内で生成した電子が隣接画素に到達してしまうことを妨げるので、隣接画素へのクロストークを抑制することができる。

## 【0051】

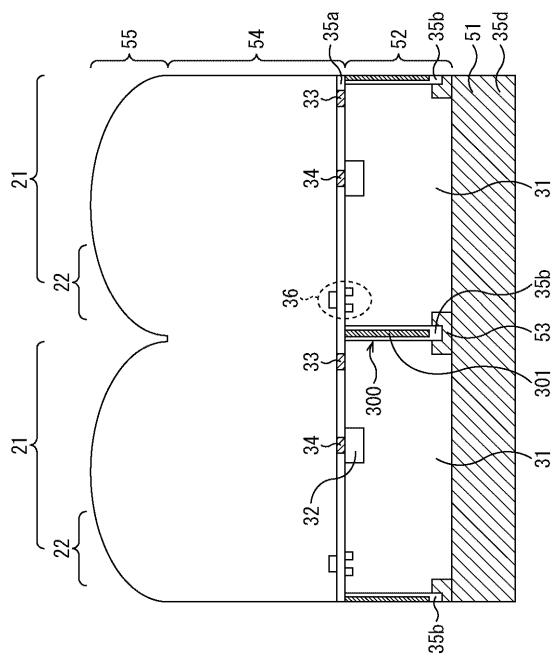

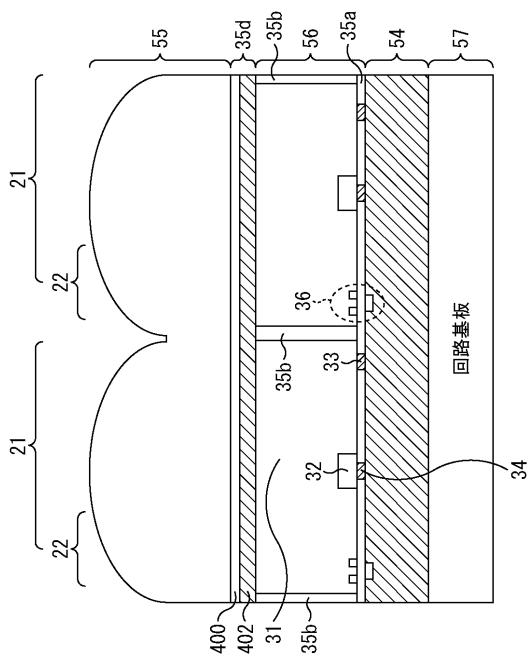

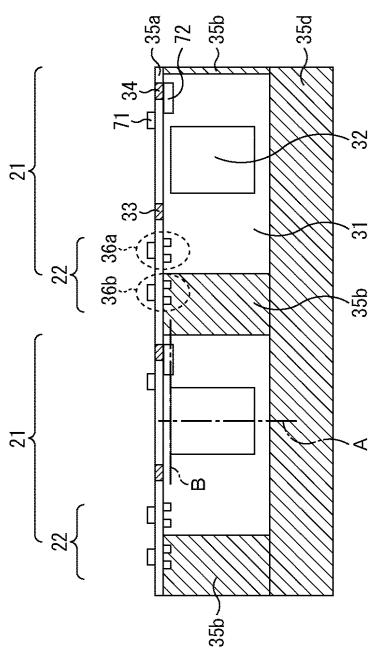

図10は、第1の実施の形態である光起電力型画素10を表面照射型撮像素子に適用した場合の構成例(以下、第1の構成例と称する)の断面図である。

## 【0052】

該第1の構成例は、N型領域32の上側を覆う素子分離領域35aにはSiO<sub>2</sub>が用いられ、素子分離領域35bには導電性半導体(n-Si)が用いられ、導電性半導体(n-Si)のN型基板51がP型領域31の下側を覆う素子分離領域35dとして機能する。

## 【0053】

画素回路領域22のNMOS Tr.36aは、光電変換領域31の中に形成され、PMOS Tr.36bは、素子分離領域35bの中に形成される。

## 【0054】

該第1の構成例においては、N型基板51と素子分離領域35bがN型領域32からP型領域31への拡散電流のコレクタとして作用し、これらの拡散電流の隣接する光電変換領域21への流入を抑制するので、クロストークを抑止することができる。

## 【0055】

該第1の構成例の製造方法について説明する。初めに、N型基板51上に、既存の方法によって、低濃度のN型エピタキシャル成長層52が積層される。次に、エピタキシャル成長層52に、既存の方法によって、N型不純物(例えば、リン、またはヒ素)、およびP型不純物(例えば、ホウ素)がイオン注入され、活性化アニールが行われて、P型領域

31、N型領域32、素子分離領域35b、および電極33、34の形成領域に、それぞれ高濃度のP型領域とN型領域（図示せず）が形成される。

【0056】

次に、エピタキシャル成長層52のSi表面が熱酸化されて素子分離領域35aが形成され、P型領域31およびN型領域32上の酸化膜がエッティング除去され、そこにメタルが埋め込まれて電極33、34が形成される。電極33、34として埋め込むメタルには、例えば、Al、Ti/W積層膜などを用いることができる。

【0057】

この後、既存の方法によって配線層54が形成され、最後に、既存の方法によって、オ

ンチップレンズを含む集光層55が形成される。

10

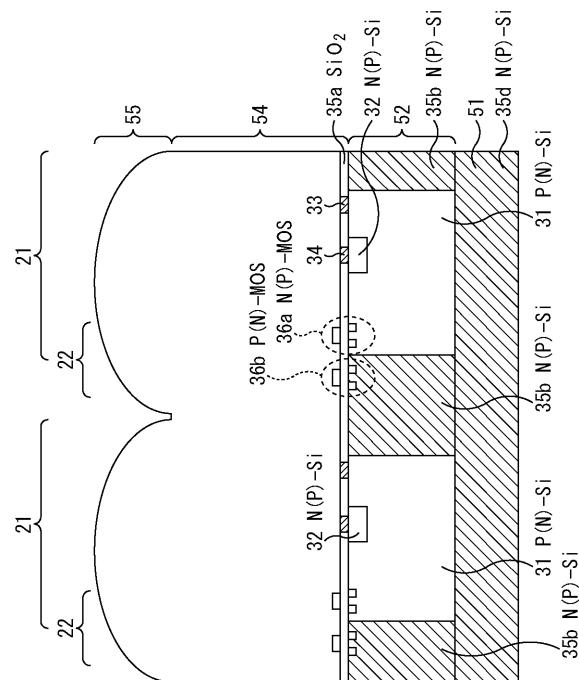

【0058】

図11は、該第1の構成例の変形例を示している。すなわち、図示するように、素子分離領域35bと素子分離領域35bの間にP型領域58を挿入し、その中にNMOS Tr.36cなどの素子を形成してもよい。P型領域58は、P型領域31にアクセプタ不純物を導入する工程の前後で、P型領域58の不純物を導入することで形成することができる。

【0059】

＜第1の実施の形態である光起電力型画素10の具体的な構成例＞

次に、図12は、第1の実施の形態である光起電力型画素10を表面照射型撮像素子に適用した場合の構成例（以下、第2の構成例と称する）の断面図である。

【0060】

該第2の構成例は、N型基板51上に、エピタキシャル成長層（エピ層）52、配線層54、および集光層55が順に積層されて構成される。

20

【0061】

該第2の構成例の、N型領域32の上側を覆う素子分離領域35aにはSiO<sub>2</sub>が用いられ、素子分離領域35bにはSiO<sub>2</sub>と導電性半導体（n-Si）の組み合わせが用いられ、導電性半導体のN型基板51がP型領域31の下側を覆う素子分離領域35dとして機能する。

【0062】

該第2の構成例の製造方法について説明する。初めに、N型基板51上に、既存の方法によって、低濃度のN型エピタキシャル成長層52が積層される。次に、エピタキシャル成長層52に、既存の方法によって、N型不純物（例えば、リン、またはヒ素）、およびP型不純物（例えば、ホウ素）がイオン注入され、活性化アニールが行われて、N型領域53、P型領域31、N型領域32、および電極33、34の形成領域に、それぞれ高濃度のP型領域とN型領域（図示せず）が形成される。

30

【0063】

次に、画素回路領域22に、既存の方法によって、MOS Tr.36などの活性素子と、MOS容量、拡散層抵抗などの受動素子が形成される。

【0064】

続いて、エピタキシャル成長層52の素子分離領域35bを形成する領域がエッティングされ、そこにSiO<sub>2</sub>が埋め込まれて素子分離領域35bが形成される。このエッティングには、反応性イオンエッティング、陽極酸化等の方法を用いることができる。また、SiO<sub>2</sub>の埋め込みには、エッティング表面のSiを熱酸化した後、原子層堆積法（ALD）、化学気相成長法（CVD）、または化学機械研磨技術（CMP）の組み合わせを用いることができる。

40

【0065】

次に、エピタキシャル成長層52のSi表面が熱酸化されて素子分離領域35aが形成され、P型領域31およびN型領域32上の酸化膜がエッティング除去され、そこにメタルが埋め込まれて電極33、34が形成される。電極33、34として埋め込むメタルには、例えば、Al、Ti/W積層膜などを用いることができる。

【0066】

この後、既存の方法によって配線層54が形成され、最後に、既存の方法によって、オ

ンチップレンズを含む集光層55が形成される。

50

## 【0067】

なお、図12には、P型領域31とN型領域32それぞれの内部の不純物分布については図示していないが、両者の間に形成される空乏層の幅を広げて感度を高めるために、両者の境界領域の不純物濃度を下げ、実効的なp-i-n接合としてもよい。この場合、i層は、低濃度のN型層、または低濃度のP型層であってもよい。ただし、図12の構成例ではP型領域31に対してN型領域32が狭く図示されているが、低濃度のN型層を設けた場合には、P型領域31に対してN型領域32が広く形成される。

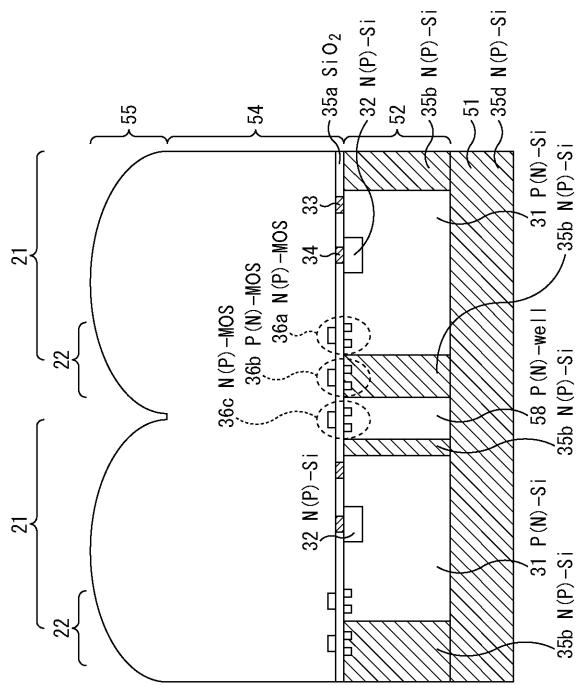

## 【0068】

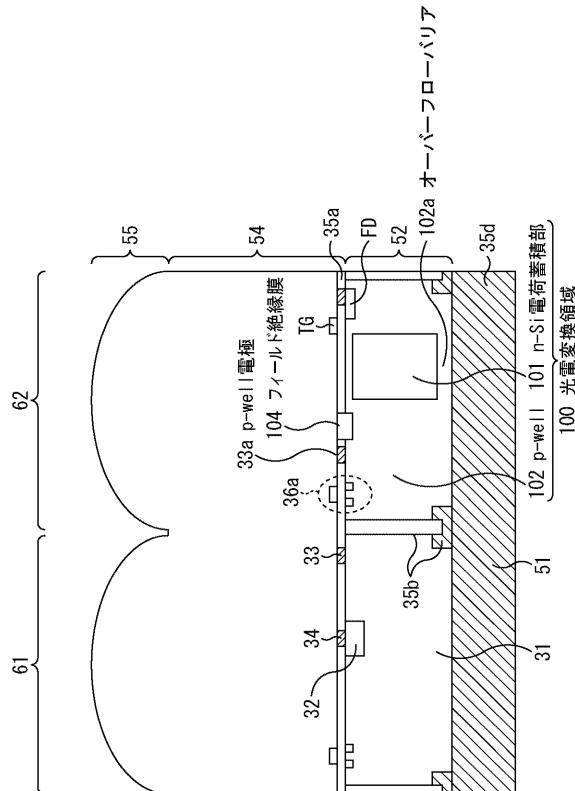

次に、図13は、該第2の構成例の変形例（以下、第3の構成例と称する）を示している。該第3の構成例では、素子分離領域35bを、SiO<sub>2</sub>層300と、その内側に埋め込まれ、SiO<sub>2</sub>層300によってP型領域31と隔てられている金属層301と、N型領域53とで構成する。金属層301が入射光に対する反射鏡として作用することにより、P型領域31から隣接画素への光漏れが抑制されるので、クロストークがさらに抑制され、感度も向上する。

図13に示された第3の構成例は、上述した第2の構成例の製造方法において、エッチング表面のSiを熱酸化した後に埋め込む材料を、SiO<sub>2</sub>からWやAlなどの金属に置き換えることによって製造することができる。

## 【0069】

次に、図14は、第1の実施の形態である光起電力型画素10を表面照射型撮像素子に適用した場合のさらに他の構成例（以下、第4の構成例と称する）の断面図である。

## 【0070】

該第4の構成例は、素子分離領域35bを挟んで隣接する光電変換領域に光起電力型画素61（光起電力型画素10に相当）と蓄積型画素62を配置している。

## 【0071】

なお、図14の光起電力型画素61は、図12に示された第2の構成例と同様であるが、図10に示された第1の構成例、図11に示された変形例、または図13に示された第3の構成例を採用してもよい。一方、蓄積型画素62の部分については、図14に示されるような既存の構成を適用することができる。

## 【0072】

図示するように、光起電力型画素61のPN接合領域は、素子分離領域35a, 35bおよび35dによって実質的に囲い込むが、蓄積型画素62の光電変換領域100と、隣接する蓄積型画素62の光電変換領域の間については、必ずしも素子分離領域35bによって囲い込む必要はない。

## 【0073】

該第4の構成例の製造方法については、既存の蓄積型画素62の製造方法に、図11に示された第1の構成例の製造工程を追加すればよい。

## 【0074】

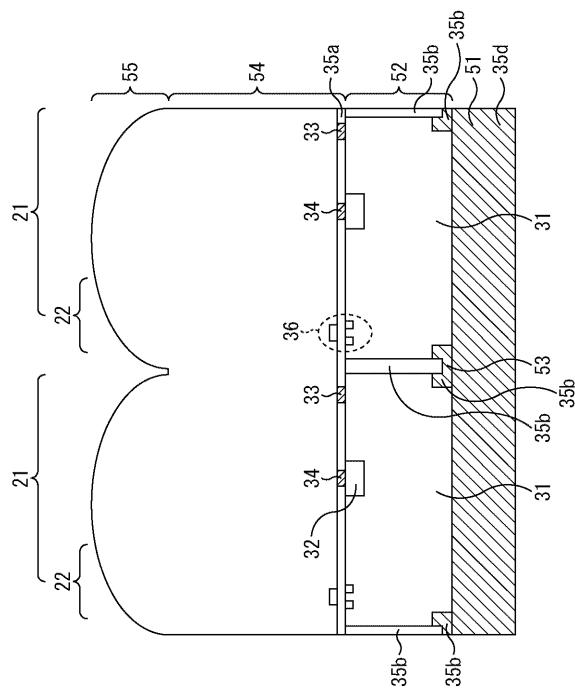

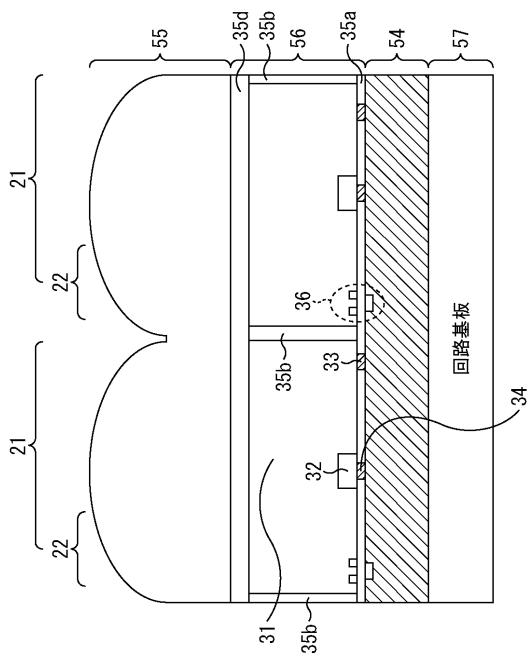

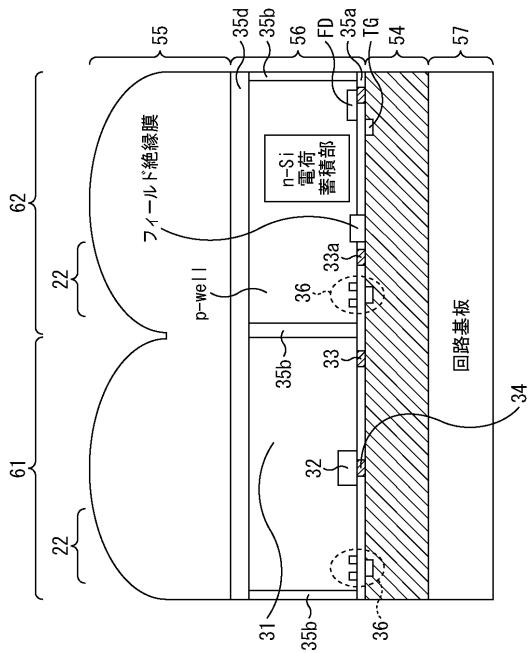

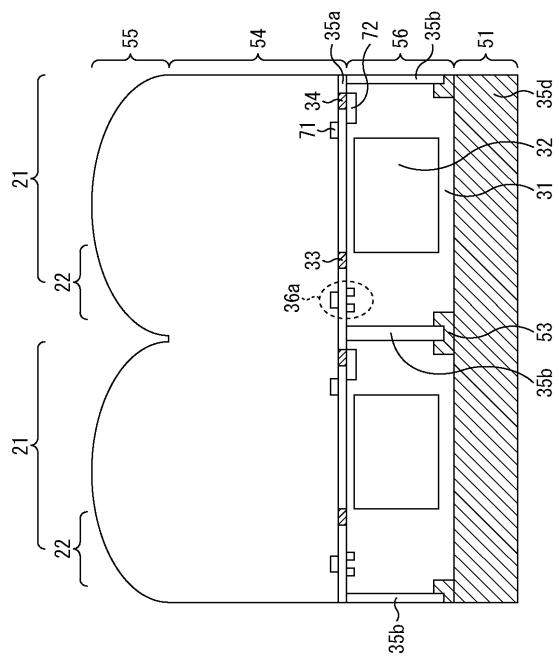

次に、図15は、第1の実施の形態である光起電力型画素10を裏面照射型撮像素子に適用した場合の構成例（以下、第5の構成例と称する）の断面図である。

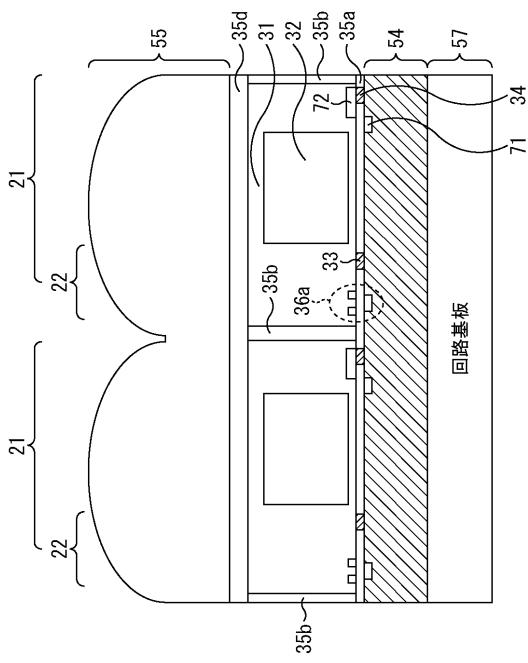

## 【0075】

該第5の構成例は、光電変換領域21と画素回路領域22が同一基板（センサ基板56）上に形成されている。各光電変換領域21は素子分離領域35a, 35b、および35dにより実質的に囲み込まれており、素子分離領域35a乃至35dはSiO<sub>2</sub>により形成される。

## 【0076】

該第5の構成例の製造方法について説明する。初めに、信号処理回路等が形成された回路基板57と、画素（光起電力型画素）が形成されたセンサ基板56とが配線層54により張り合わされ、センサ基板56の裏面が所定の厚さに研磨される。次に、センサ基板56の素子分離領域35bを形成する領域が裏面側からエッチングされて、SiO<sub>2</sub>が埋め込まれて素子分離領域35bが形成される。さらに、センサ基板56の裏面に素子分離領域3

10

20

30

40

50

5 d として  $\text{SiO}_2$  酸化膜が形成され、最後に集光層 5 5 が積層される。

【0077】

なお、センサ基板 5 6 の研磨には、例えば既存の研磨材を用いた機械研磨と CMP 法の組み合わせを適用できる。センサ基板 5 6 のエッティングには、例えば反応性イオンエッティング法を適用できる。 $\text{SiO}_2$  の埋め込みには、例えば化学気相成長法を適用できる。なお、 $\text{SiO}_2$  を埋め込む代わりに、図 13 に示された第 3 の構成例と同様に、 $\text{SiO}_2$  とメタルを埋め込むようにしてもよい。

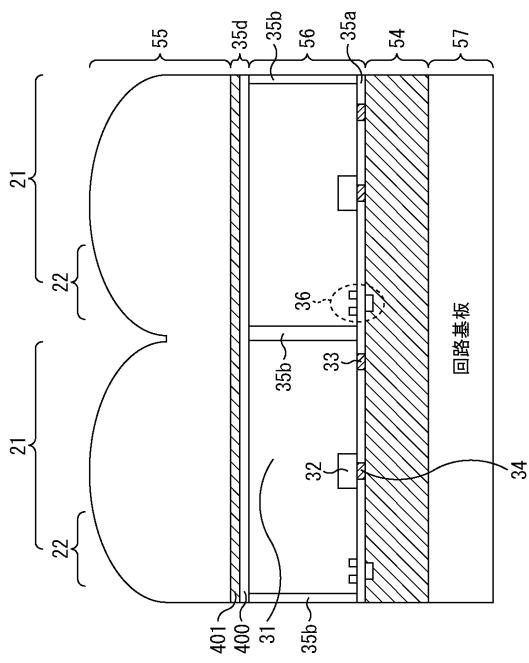

【0078】

図 15 に示された第 5 の構成例は、図 16 に示される第 1 の変形例のように、素子分離領域 3 5 d を、 $\text{SiO}_2$  層 4 0 0 と、その上に積層した  $\text{HfO}$  などの薄膜 4 0 1 とで構成し、 $\text{SiO}_2$  層 4 0 0 と P 型領域 3 1 の界面付近のホール濃度を高めてもよい。また、図 17 に示される第 2 の変形例のように、 $\text{SiO}_2$  層 4 0 0 付近の P 型領域 3 1 にアクセプタ不純物を導入し、P 型領域 3 1 よりも正孔濃度の高い P 型領域 4 0 2 を形成してもよい。

10

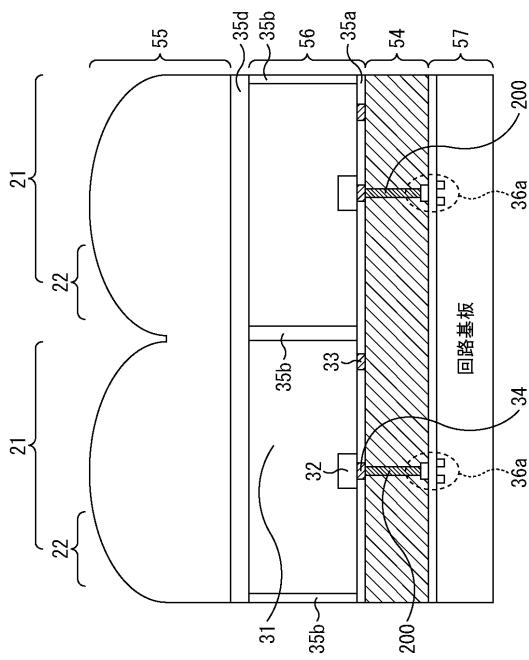

【0079】

次に、図 18 は、第 1 の実施の形態である光起電力型画素 1 0 を裏面照射型撮像素子に適用した場合の他の構成例（以下、第 6 の構成例と称する）の断面図である。

【0080】

該第 6 の構成例は、光電変換領域 2 1 と画素回路領域（MOS Tr. 3 6 等）が別基板（センサ基板 5 6 と回路基板 5 7）上に形成されている。各光電変換領域 2 1 は素子分離領域 3 5 a, 3 5 b および 3 5 d により実質的に囲み込まれており、素子分離領域 3 5 a, 3 5 b, 3 5 d は  $\text{SiO}_2$  により形成される。

20

【0081】

光起電力を発生する N 型領域 3 2 は、電極 3 4 と配線 2 0 0 によって回路基板 5 7 の MOS Tr. 3 6 a のゲートに接続される。

【0082】

該第 6 の構成例の製造方法については、図 15 に示された第 5 の構成例の製造方法を用いることができる。

【0083】

なお、該第 6 の構成例では、センサ基板 5 6 と回路基板 5 7 とを配線層 5 4 によって張り合わせた場合を図示しているが、実装技術を用いて、センサ基板 5 6 上の電極と回路基板 5 7 上の電極どうしをバンプ接続し、いわゆるハイブリッドセンサの構成を採用してもよい。

30

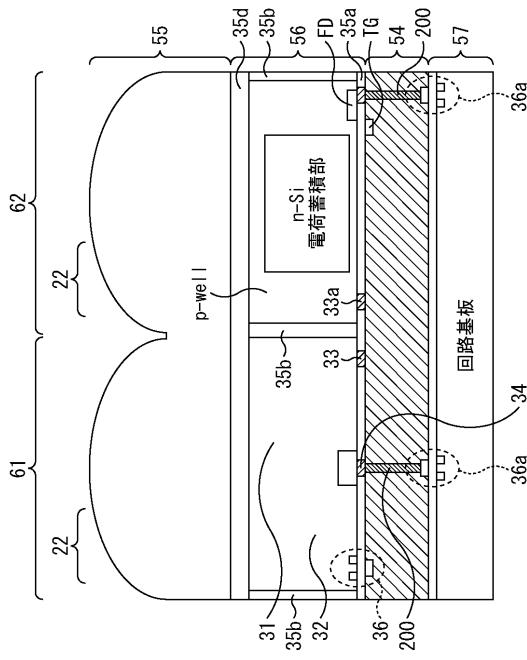

【0084】

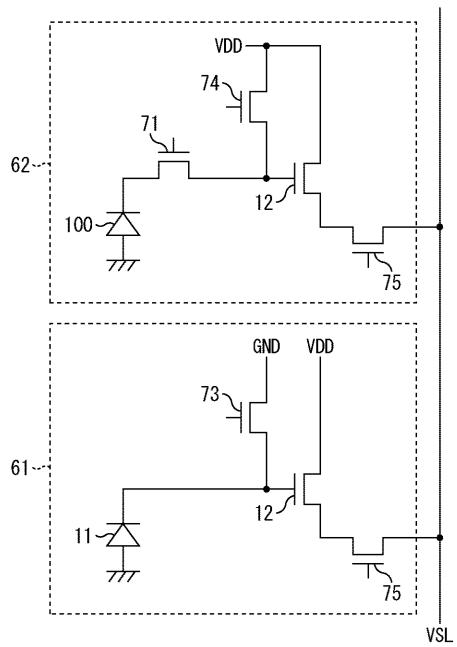

次に、図 19 は、第 1 の実施の形態である光起電力型画素 1 0 を裏面照射型撮像素子に適用した場合のさらに他の構成例（以下、第 7 の構成例と称する）の断面図である。該第 7 の構成例は、隣接する光電変換領域に光起電力型画素 6 1（光起電力型画素 1 0 に相当）と蓄積型画素 6 2 を配置している。

【0085】

なお、該第 7 の構成例における光起電力型画素 6 1 は、図 15 に示された第 5 の構成例におけるそれと同様であるが、図 18 に示された第 6 の構成例と同じものを採用してもよい。一方、蓄積型画素 6 2 の部分については、図 19 に示す既存の構成を適用することができる。

40

【0086】

図 20 は、第 1 の実施の形態である光起電力型画素 1 0 を裏面照射型撮像素子に適用した場合のさらに他の構成例（以下、第 8 の構成例と称する）の断面図である。該第 8 の構成例は、第 7 の構成例と同様に、隣接する光電変換領域に光起電力型画素 6 1（光起電力型画素 1 0 に相当）と蓄積型画素 6 2 を配置している。また、第 6 の構成例と同様に、光電変換領域 2 1 と画素回路領域（MOS Tr. 3 6 等）が別基板（センサ基板 5 6 と回路基板 5 7）上に形成され、光起電力を発生する N 型領域 3 2、および、蓄積型画素 6 2 の FD は、電極 3 4 と配線 2 0 0 によって回路基板 5 7 の MOS Tr. 3 6 a のゲートに接続され

50

る。

【0087】

上述した第1の実施の形態である光起電力型画素10の各構成例は、公知の回路（例えば、特許文献1の図1の回路、特許文献2のFig.3a, 3bの回路など）から構成することができる。もちろん、図21に示すように、PN接合ダイオードのP型領域に発生する正電位を信号として取り出し、アンプ12を構成するディプリーション型MOSFETのゲートに印加するように変形してもよい。

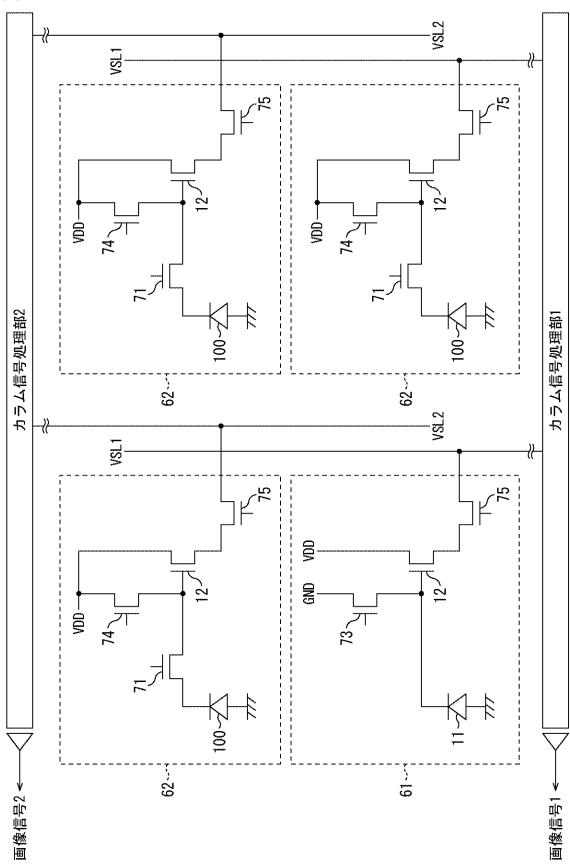

【0088】

図22は、光起電力型画素61と蓄積型画素62を、同一の垂直信号線に接続した撮像素子の構成例を示している。この構成例では、垂直信号線の本数を増やすことなく、両者を同一撮像素子に配置することにより、表面照射型では、開口率を犠牲にすることなく、両者を混在させることができる。

10

【0089】

図23は、光起電力型画素61と蓄積型画素62を、それぞれ異なる垂直信号線に接続した撮像素子の構成例である。この構成では、光起電力型画素61と蓄積型画素62の画素信号を同時に、カラム信号処理部に出力できるため、より高いフレームレートを得ることができる。また、カラム信号処理回路を、それぞれの出力電圧範囲に応じて、最適設計できるので、それぞれの画素信号に対する回路ノイズを低減でき、良好な画質を得ることができる。

【0090】

20

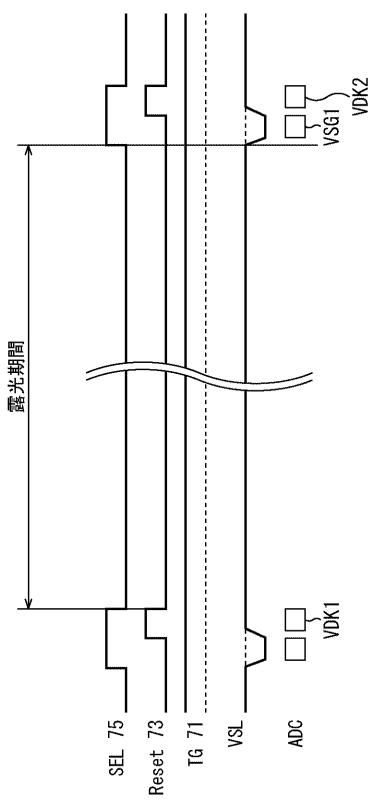

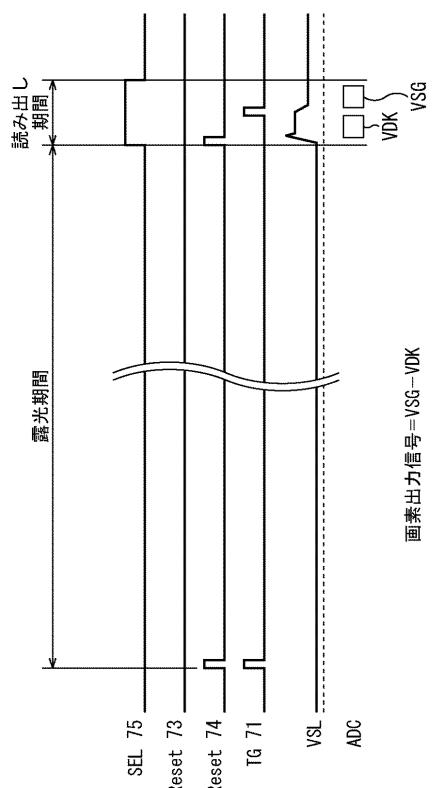

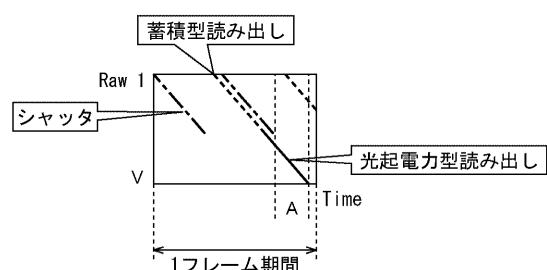

次に、図24は、光起電力型画素61の駆動タイミングの一例を示している。

【0091】

露光期間が開始されると、露光期間中はReset73がオフとされる。この結果、PN接合ダイオード11が開放され、そこで発生された光電流がPN接合ダイオード11の順方向電流によって打ち消されて、正味の直流電流がゼロになるように、順方向電圧が発生する。

【0092】

露光期間が終わると、読み出し行のSEL75に対する制御信号がオンとなり、アンプ2で増幅されたPN接合ダイオード11の順方向電圧VSG1が垂直信号線に出力される。出力された画素出力はAD変換されて、VSG1のデジタル出力値となる。

【0093】

30

次に、Reset73がオンとされ、PN接合ダイオード11が短絡されたときの出力電圧（暗時電圧）VDK2が垂直信号線に出力される。出力された画素出力はAD変換されて、VDK2のデジタル出力値となる。VSG1とVDK2のデジタル出力値を引き算した値が、画素のデジタル出力値とされる。

【0094】

なお、暗時電圧として、露光期間の前に出力電圧VDK1を読み出してもよい。露光期間の前にVDK1を読み出すか、または露光期間の後にVDK2を読み出すかにより、光起電力型画素61では、手順1と手順2の2通りの読み出し方を実行することができる。以下の説明では、手順2（露光期間後に、信号電圧VSG1と暗時電圧VDK2を順次読み出す手順）を採用する。

40

【0095】

同一撮像素子上に、光起電力型画素61とともに配置された蓄積型画素62の駆動タイミングには、図25に示すような従来知られている蓄積型画素の駆動タイミングを採用することができる。

【0096】

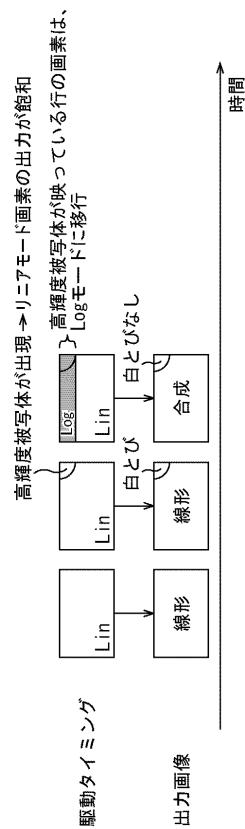

次に、図26は、光起電力型画素61と蓄積型画素62が搭載されている撮像素子からの出力画像の3種類の例を示している。

【0097】

同図Aは、複数フレームに亘って（ここでは、出力画像を、線形画像から対数画像に切り替える前後の3フレームずつだけを図示している）光起電力型画素61と蓄積型画素6

50

2のいずれか一方だけを読み出すようにした場合の出力画像を時系列で並べたものである。このような画像出力順は、図24と図25の駆動タイミングを複数フレーム毎に切り替えることにより可能となる。なお、ここでは、光起電力型画素出力で構成した画像を対数画像、蓄積型画素出力で構成した画像を線形画像と称している。

#### 【0098】

同図Bは、1フレーム毎に光起電力型画素61と蓄積型画素62を交互に読み出し、対数画像と線形画像を合成してから出力する場合の読み出し画素と出力画像を時系列で並べたものである。このような画像出力順は、図24と図25の駆動タイミングを1フレーム毎に切り替え、対数画像と線形画像を公知の方法で合成することによって得ることができる。画像の中の低輝度部分では、蓄積型画素の信号を用いることで良好な低照度感度とS/Nを得られ、蓄積画素のダイナミックレンジを超える高輝度部分では、対数型画素の信号を用いることで、より高い輝度まで階調と色再現性を得ることができる。

#### 【0099】

同図Cは、1フレーム毎に光起電力型画素61と蓄積型画素62の両方を読み出し、対数画像と線形画像を合成してから出力する場合の読み出し画素と出力画像を時系列で並べたものである。この場合、光起電力型画素61と蓄積型画素62の露光時間が重なることになり、線形画像と対数画像の撮影タイミングが近づくので、撮影時間差に起因するアーティファクトが合成画像に発生することを抑制することができる。また、同図Bの場合よりも高いフレームレートで合成画像を出力することができる。

#### 【0100】

図27は、図26Cに示された出力画像を得るための、1フレーム期間における光起電力型画素61と蓄積型画素62の駆動タイミングの一例を示している。

#### 【0101】

蓄積型画素62では、期間Aにおいてシャッタ行のSEL75とRST74、TG71がオンとされ、電荷蓄積領域(PD)とフローディング拡散層(FD)の電荷が掃き捨てられて電子シャッタが切られる。次の期間BにおいてPDに信号電荷が蓄積される。さらに、期間Cにおいて読み出し行のSEL75とRST74がオンとされ、FD内の電荷が再度掃き捨てられて、期間Eにおいて、暗時電圧(P相電圧)VDKが読み出される。さらに、期間GにおいてTG71がオンとされ、PDに蓄積された電荷がFDに転送されて、FDに信号電圧が発生し、期間Iにおいて、アンプ12で増幅された信号電圧VSGが読み出される。

#### 【0102】

一方、蓄積型画素62と同じ行に形成された光起電力型画素61では、前のフレームの期間Kから露光が開始され、PN接合ダイオード11に光起電力が発生する。次に期間Cにおいて読み出し行のSEL75がオンとされ、PN接合ダイオード11に発生していた光起電力が、アンプ12で増幅された後、垂直信号線に出力され、信号電圧VSG1として読み出される。続いて、期間G, H, I, JにおいてRST73がオンとされ、PN接合ダイオード11が短絡され、期間Iにおいて暗時電圧VDK2が読み出される。

#### 【0103】

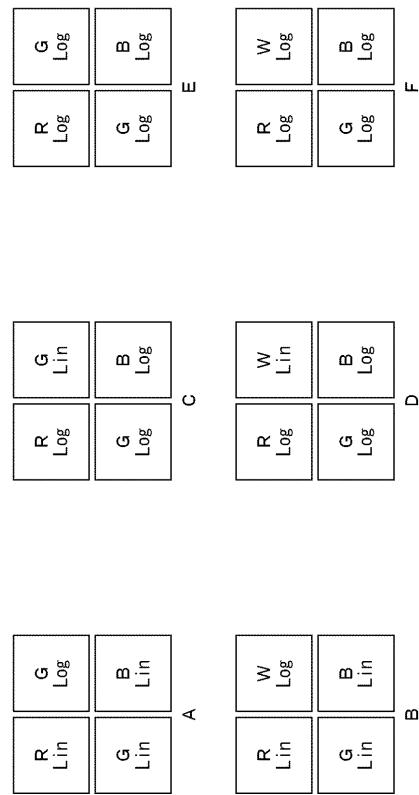

次に、図28は、撮像素子における $2 \times 2$ 画素毎の光起電力型画素61と蓄積型画素62の配列の一例を示している。なお、同図において、R(Red), G(Green), B(Blue)は各画素を覆うカラーフィルタの色を示しており、Logは光起電力型画素61を、Linは蓄積型画素62を示している。

#### 【0104】

図29は、図28の( $2n-1$ )列、( $2m-1$ )行の蓄積型画素62と、( $2n-1$ )列、 $2m$ 行の光起電力型画素61の駆動タイミングを示している。

#### 【0105】

( $2n-1$ )列目では、光起電力型画素61と蓄積型画素62が、1行読み出し期間(水平同期期間、1H期間)ごとに交互に読み出される。一方、隣接する $2n$ 列目(不図示)では、すべての読み出し期間で、蓄積型画素62が読み出される。すなわち、光起電力型画素61と蓄積型画素62とを、1フレーム内で同時に読み出すことができる。

10

20

30

40

50

## 【0106】

光起電力型画素 61 と蓄積型画素 62 とは、共通の露光期間 B が終わると同時に、同時に読み出されるため、同じ行の光起電力型画素 61 と蓄積型画素 62 の間で、露光タイミング差が生じない。よって、対数画像と線形画像の間の像ずれが生じない。その結果、両者を合成する際に、像ずれに起因するアーティファクトの発生が抑制され、画質の良好な合成画像を得ることができる。

## 【0107】

図 30 は、撮像素子における蓄積型画素 62 と光起電力型画素 61 の配列の他の例を示している。なお、同図において、R, G, B, W (無色または補色) は各画素を覆うカラーフィルタの色を示しており、Log は光起電力型画素 61 を、Lin は蓄積型画素 62 を示している。

10

## 【0108】

同図 A は、ベイヤ配列を構成する 4 画素のうち、1 画素を G の光起電力型画素 61 とし、他の 3 画素を蓄積型画素 62 とした配列例である。

## 【0109】

同図 B は、同図 A に示された配列における G の光起電力型画素 61 を、W の光起電力型画素 61 に置換した配列例である。

20

## 【0110】

同図 C は、ベイヤ配列を構成する 4 画素のうち、1 画素を G の蓄積型画素 62 とし、他の 3 画素を光起電力型画素 61 とした配列例である。

## 【0111】

同図 D は、同図 C に示された配列における G の蓄積型画素 62 を、W の蓄積型画素 62 に置換した配列例である。

## 【0112】

同図 E は、ベイヤ配列を構成する 4 画素の全てを光起電力型画素 61 とした配列例である。

## 【0113】

同図 F は、同図 E に示された配列における G の 2 画素の光起電力型画素 61 のうちの 1 画素を、W の光起電力型画素 61 に置換した配列例である。

30

## 【0114】

同図 A および同図 C に示された配列例のように、同色の蓄積型画素 62 と光起電力型画素 61 を近接配置することにより、飽和していない蓄積型画素 62 の出力値で、光起電力型画素 61 の画素出力値を較正し、光起電力型画素 61 の温度特性や、画素ごとの特性ばらつきを補償することができる。これにより、線形画像と対数画像の合成画像で、線形画像と対数画像の境界で、なめらかな階調やグラデーションを得ることができる。

## 【0115】

また、例えば同図 B に示された配列例で、仮に、R, G, B の 3 つの蓄積型画素 62 のいずれかの出力が飽和しても、飽和していない残りの蓄積型画素 62 の出力と、光起電力型画素 61 の出力を用いることにより、ある程度の色再現性と階調を得ることができる。

40

## 【0116】

同図 B、同図 D、および同図 F に示された配列例のように、W の画素を設けることにより、光起電力型画素 61 または蓄積型画素 62 の感度を高め、より低照度まで対数画像や、S/N がよい線形画像を得ることができる。

## 【0117】

< 2. 第 2 の実施の形態 >

次に、第 2 の実施の形態である、蓄積型画素としても動作することができる光起電力型画素（以下、蓄積型兼光起電力型画素と称する）について説明する。

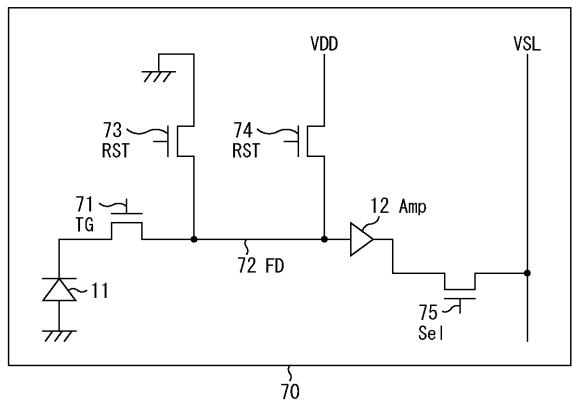

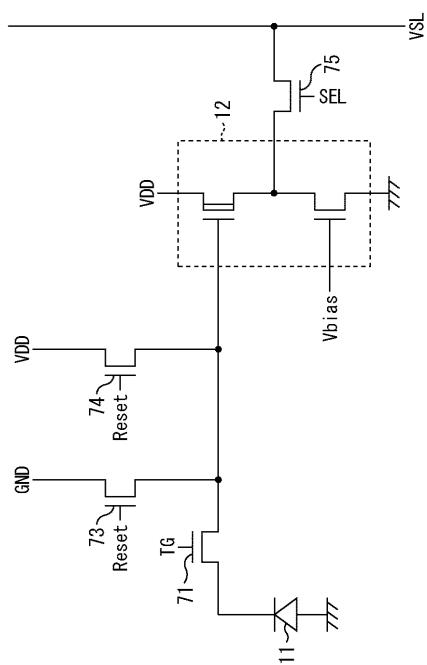

## 【0118】

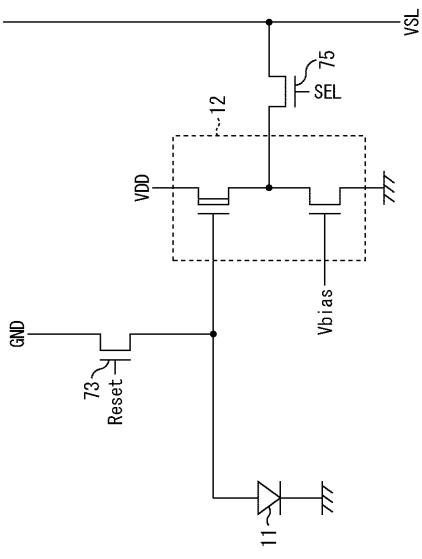

図 31 は、第 2 の実施の形態である蓄積型兼用光起電力型画素の等価回路を示している。該蓄積型兼光起電力型画素 70 は、PN接合ダイオード 11、アンプ 12、TG 71、FD 7

50

2、RST 7 3、RST 7 4、およびSel 7 5 から構成される。

【0119】

PN接合ダイオード11は、P型領域31とN型領域(電荷蓄積領域)32(いずれも図19)から成り、入射光に応じて光電変換を行い、その結果として生成された信号電荷を蓄積し、または、光起電力を発生する。

【0120】

TG71は、生成された信号電荷をFD72に転送する。また、TG71は、G71下に形成されるチャネルによって、N型領域32をTFD72に短絡することにより、発生された光起電力をFD72に伝達する。

【0121】

FD72は、N型領域であって、信号電荷を信号電圧に変換する。RST73は、FD72をGND電位にリセットする。RST74は、FD72をVDD電位にリセットする。アンプ12は、FD72の電位を増幅する。Sel75は、アンプ12の出力信号を垂直信号線VSLに伝達する。

【0122】

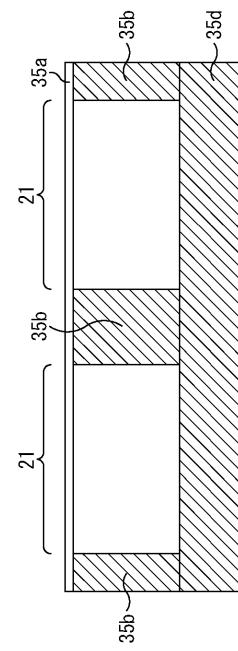

図32は、図31に等価回路が示された蓄積型兼光起電力型画素70に対応する画素構造の2×2画素分の上面配置図を示している。同図に示されるように、蓄積型兼光起電力型画素70は素子分離領域35によって実質的に分離される光電変換領域21を有する。光電変換領域21には、図31のPN接合ダイオード11、TG71、およびFD72が形成される。光電変換領域21や素子分離領域35と重なる画素内の適当な領域に設けられた画素回路領域22には、アンプ12、RST73、RST74、Sel75等などが形成される。

【0123】

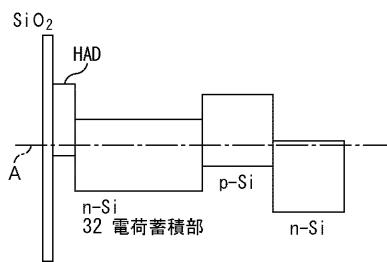

図33は、図32における線分PQにおける画素構造の断面を示している。同図からも明らかのように、光電変換領域21と光電変換領域21との間は素子分離領域35によって実質的に分離されている。

【0124】

図32と、第1の実施の形態である光起電力型画素10の断面図(図8、および図9)を比較して明らかのように、蓄積型兼光起電力型画素70は、素子分離領域35a、35b、35cおよび35dによって囲まれる内部にFD72が設けられていること、電極(オーム電極)34をFD72に接続していること、および、FD72とN型領域(電荷蓄積領域)32との間のポテンシャルバリアを制御することを目的としたTG71が設けられていることが、光起電力型画素10と構造的に相違する。

【0125】

次に、図34および図35は、蓄積型兼光起電力型画素70のポテンシャル分布図であり、図34は図33の線分Aに対応し、図35は図33の線分Bに対応する。なお、図34および図35では、素子分離領域35aをSiO<sub>2</sub>とし、35bと35dをN型領域とした場合を示している。同図に示されるように、蓄積型兼光起電力型画素70のN型領域(電荷蓄積領域)32の周囲のポテンシャルバリアの高さは、どの方向にもほぼ等しく、P型中性領域のポテンシャルの高さに分布させることが望ましい。

【0126】

このようなポテンシャル分布により、図31に示された蓄積型兼光起電力型画素70を蓄積型画素として、または光起電力型画素として動作させることができる。

【0127】

<第2の実施の形態である蓄積型兼光起電力型画素70の具体的な構成例>

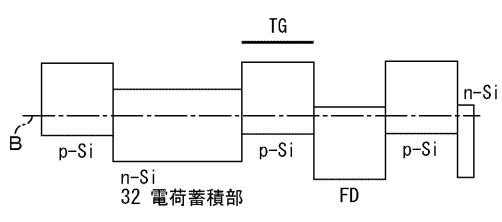

図36は、第2の実施の形態である蓄積型兼光起電力型画素70を表面照射型撮像素子に適用した場合の構成例(以下、第8の構成例と称する)の断面図である。

【0128】

なお、第8の構成例の素子分離領域35a乃至35dは、図12に示された第2の構成例の素子分離領域35a乃至35dと同じ材料を用いているが、図11に示された第1の構成例、または図13に示された第3の構成例の素子分離領域35a乃至35dと同様に構成してもよい。

10

20

30

40

50

## 【0129】

該第8の構成例の製造方法について説明する。該第8の構成例は、従来の表面照射型蓄積型画素(例えば、図14に示された第4の構成例における蓄積型画素62)の製造方法を以下のように若干修正するとともに、素子分離領域35a乃至35dの形成工程を追加することによって製造できる。

従来の蓄積型画素でオーバーフローバリアを形成する領域(P型領域32のうちの、N型基板51とN型領域32に挟まれた領域)には、P型中性領域が形成されるようにアクセプタ不純物を導入する。これにより、該第8の構成例を光起電力型画素として動作させた場合に、第1の実施の形態である光起電力型画素と同等の光起電力を生成することができる。

P型領域31と素子分離領域35bの界面付近の正孔濃度が所定濃度以上となるように、P型領域31にアクセプタ不純物を導入するか、または、素子分離領域35bのSiO<sub>2</sub>内に、負の固定電荷を生成する膜を埋め込む。該負の固定電荷を生成する膜としては、例えばハフニウム酸化膜を使用することができ、成膜方法には、化学気相成長法、スパッタリング法、原子層堆積法等を用いることができる。これにより、該第8の構成例を蓄積型画素として動作させた場合の暗電流を、従来の蓄積型画素と同等まで低減することができる。

## 【0130】

次に、図37は、第2の実施の形態である蓄積型兼光起電力型画素70を裏面照射型撮像素子に適用した場合の構成例(以下、第9の構成例と称する)の断面図である。

## 【0131】

なお、第9の構成例の素子分離領域35a乃至35dは、図15に示された第5の構成例の素子分離領域35a乃至35dと同じ材料を用いているが、図16または図17に示された第1または第2の変形例と同様の構成にしてもよい。また、図18に示された第6の構成例、または、図19に示された第7の構成例と同様の構成にしてもよい。あるいは、図13に示された第3の構成例と同様に、素子分離領域35bをSiO<sub>2</sub>と金属で構成してもよい。

## 【0132】

該第9の構成例の製造方法について説明する。該第9の構成例は、従来の裏面照射型蓄積型画素の製造方法を以下のように若干修正するとともに、素子分離領域35a乃至35dの形成工程を追加することによって製造できる。すなわち、P型領域31と素子分離領域35bの界面付近の正孔濃度が所定濃度以上となるように、P型領域31にアクセプタ不純物を導入するか、または、素子分離領域35bのSiO<sub>2</sub>内に、負の固定電荷を生成する膜を埋め込む。該負の固定電荷を生成する膜としては、例えばハフニウム酸化膜を使用することができ、成膜方法には、化学気相成長法、スパッタリング法、原子層堆積法等を用いることができる。これにより、該第9の構成例を蓄積型画素として動作させた場合の暗電流を、従来の蓄積型画素と同等まで低減することができる。

## 【0133】

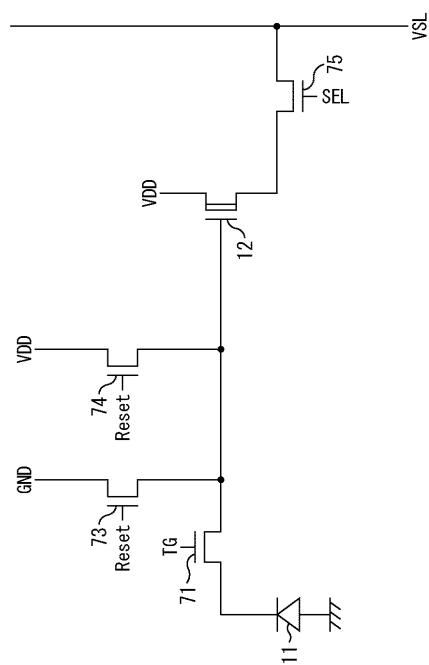

<蓄積型兼光起電力型画素70の等価回路におけるアンプ12の構成例>

次に、図38は、図31に示された蓄積型兼光起電力型画素70の等価回路におけるアンプ12に採用可能な第1の構成例を示している。

## 【0134】

該第1の構成例は、アンプ12を、ディブリーション型MOSFETを用いたソースフォロア型増幅器として構成した場合の蓄積型兼光起電力型画素70の構成例である。ディブリーション型MOSFETを用いることにより、蓄積型画素として動作させたときの正の信号電圧だけでなく、同画素を光起電力型画素として動作させたときの負の信号電圧も増幅することが可能となる。

## 【0135】

図39は、図31に示された蓄積型兼光起電力型画素70の等価回路におけるアンプ12に採用可能な第2の構成例を示している。該第2の構成例は、図38のソースフォロア

10

20

30

40

50

型増幅器の定電流源として作用させる負荷MOSFET（図示せず）を垂直信号線上に配置した場合の蓄積型兼光起電力型画素70の構成例である。負荷MOSFETを画素外に配置したことにより、従来の蓄積型画素と同等の開口率や飽和電荷量を得ることができる。

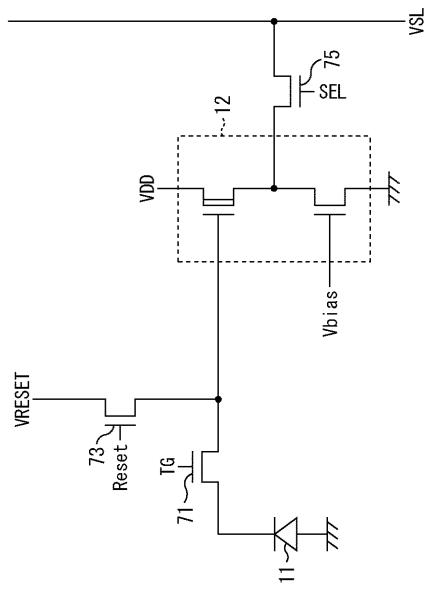

【0136】

図40は、図31の等価回路に代えることができる、蓄積型兼光起電力型画素70の等価回路を示している。該等価回路のReset73は、図31のReset73とReset74のいずれかがオンの期間にオンとする。また、図40の該等価回路においては、図31の等価回路におけるReset73をオンにする期間には、VRESETにGND電位を与え、Reset74をオンにする期間には、VRESETにVDD電位を与える。これにより、FDのリセット期間は、蓄積型兼光起電力型画素70を、光起電力型と蓄積型のどちらで動作させるかに拘わらず、Reset73に印加する信号のみで決めることができ、FD電位をVDDとGNDのどちらの電位にリセットするかは、光起電力型と蓄積型のどちらで動作させるかに応じてVRESETに印加する電圧によって決めることができる。

10

【0137】

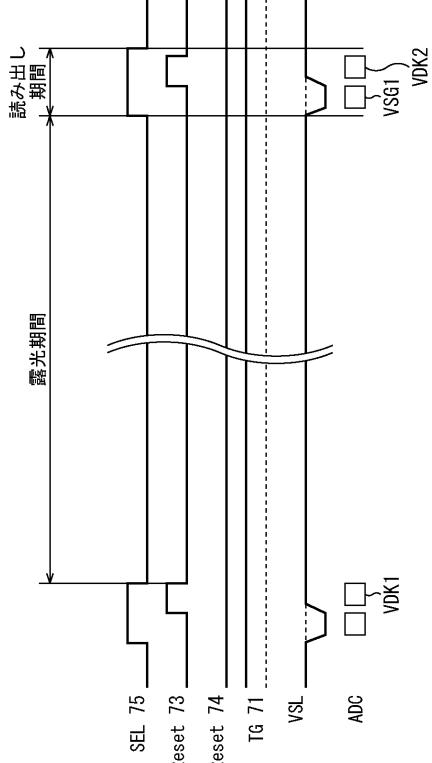

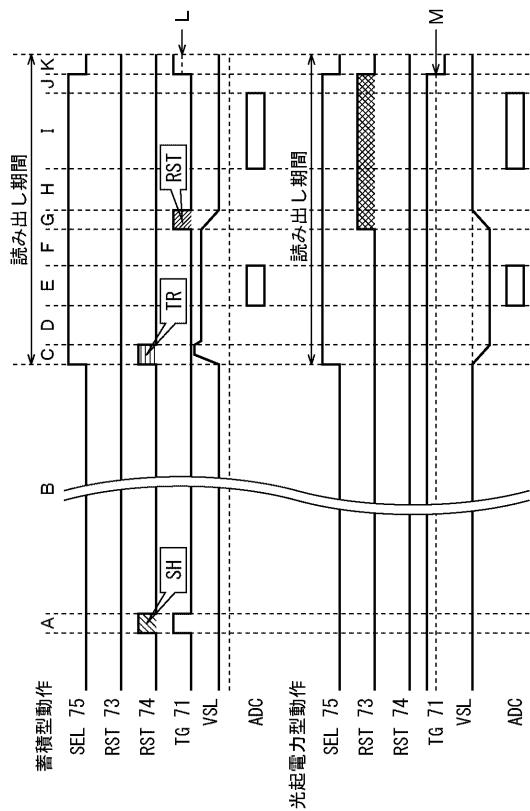

次に、図41は、蓄積型兼光起電力型画素70を、蓄積型画素として動作させる場合の駆動タイミングの一例を示している。

【0138】

この駆動タイミングは、Reset73をGNDに常時固定していることを除けば、図25に示された従来の蓄電型画素の駆動タイミングと同一である。すなわち、蓄積型兼光起電力型画素70は、Reset73をGNDに常時固定すれば、従来の蓄積型画素と同様に駆動することができる。

20

【0139】

図42は、蓄積型兼光起電力型画素70を、光起電力型画素として動作させる場合の駆動タイミングの一例を示している。

【0140】

この駆動タイミングは、Reset74をGNDに常時固定していることを除けば、図24に示された光起電力型画素61の駆動タイミングと同一である。すなわち、蓄積型兼光起電力型画素70は、Reset74をGNDに常時固定すれば、光起電力型画素61と同様に駆動することができる。

30

【0141】

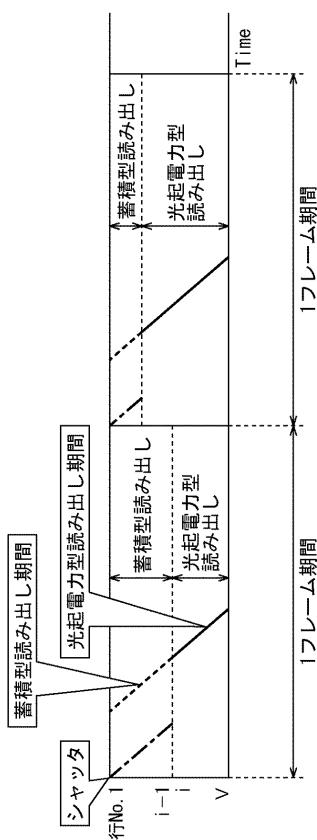

したがって、図41に示された駆動タイミングと、図42に示された駆動タイミングを、フレーム毎に適宜選択すれば、図26A、または図26Bに示された画像出力シーケンスを実現することができる。

【0142】

ただし、蓄積型兼光起電力型画素70では、全画素で対数画像と線形画像を構成できるので、いずれの画像においても、第1の実施形態を適用した撮像素子に比較して、より高い解像度の画像を得ることができる。

【0143】

また、全画素が、蓄積型と光起電力型の両方で動作する特長を活かすと、1フレーム内で蓄積型と光起電力型の画素出力を行単位で切り替えることが可能となる。

40

【0144】

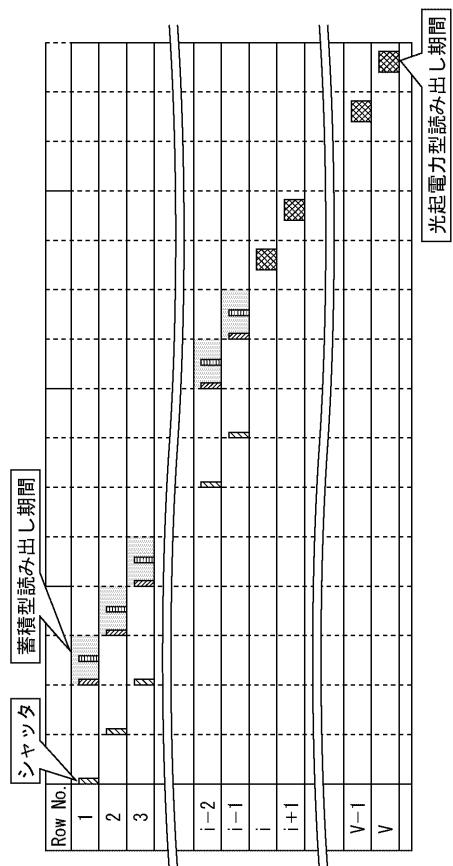

図43および図44は、1フレーム内で蓄積型と光起電力型の画素出力を毎に切り替える場合の駆動タイミングの一例を示している。すなわち、第1乃至( $i-1$ )行については図41に示された蓄積型画素として動作させる駆動タイミングを採用し、第i乃至V行については図42に示された光起電力型画素として動作させる駆動タイミングを採用する。

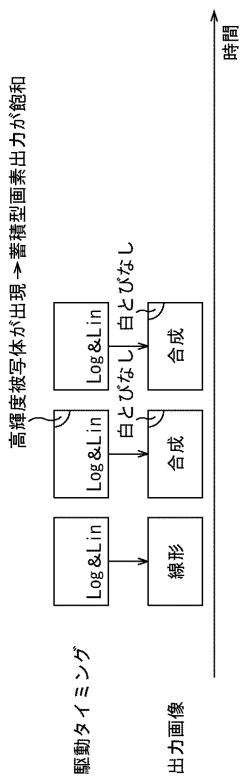

【0145】

蓄積型兼光起電力型画素70を図43および図44に示されたように駆動することにより、図45に示される効果を得ることができる。図45は、線形画像で動画撮影中のシーンに、突然、高輝度の被写体が出現した場合に得られる効果を示している。

50

## 【0146】

高輝度の被写体が出現した領域では、一部の蓄積型画素の出力が飽和する。この場合、撮像素子では、制御回路（不図示）により、蓄積型出力が飽和した画素が検出され、その画素のある行の駆動タイミングが、次のフレームでは、選択的に蓄積型から光起電力型に変更される。これにより、次フレームでは、高輝度被写体が写っている行は、光起電力型で駆動された画素で撮影されるが、高輝度被写体が写っていない行は、蓄積型タイミングで撮影される。このように撮影された対数画像と線形画像を合成することで、低輝度領域ではS/Nが良く、かつ、高輝度被写体でも良好な階調や色再現性を有する、解像度の高い合成画像を得ることができる。

## 【0147】

10

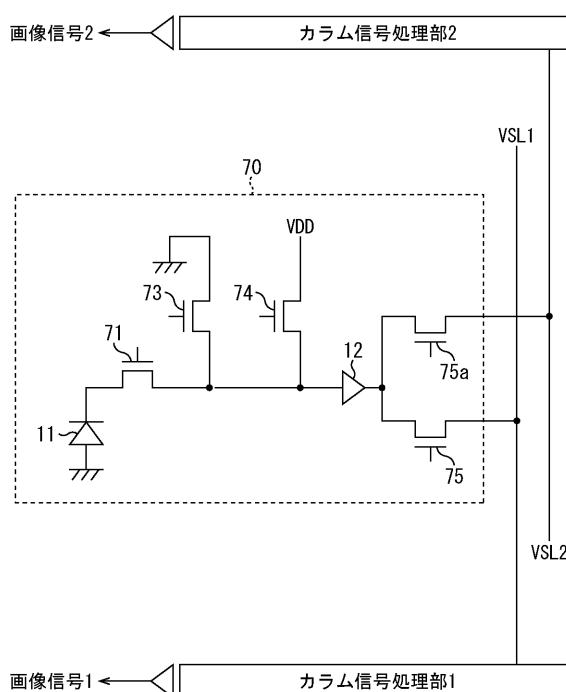

次に、図46は、図43および図44に示された駆動タイミングで、より高いフレームレートを得るための1画素分の等価回路の一例を示している。

## 【0148】

各画素は、同図に示したように、2本の垂直信号線VSL1, VSL2に接続されており、画素出力を垂直信号線VSL1, VSL2のどちらにするかは、選択トランジスタ75, 75aで選択可能とされている。2本の垂直信号線VSL1, VSL2は、それぞれ独立したカラム信号処理部1, 2に接続され、垂直信号線VSL1, VSL2からの画素出力に対して、カラム信号処理部1, 2がA/D変換などのカラム信号処理を同時に並行して行うことができる。

## 【0149】

20

図46に示された回路構成を採用することにより、蓄積型で動作させる行と、光起電力型で動作させる行とで、2本の垂直信号線VSL1, VSL2を使い分けることが可能となる。その場合、蓄積型で駆動している行と、光起電力型で駆動している行とで、同時に画素信号を出力することができる。この結果、図47に示されるタイミングチャートのように、光起電力型の読み出しが終わる前に、蓄積型の読み出しを開始することができる（同図期間A）ので、フレームレートを高めることができる。

## 【0150】

次に、図48は、図46に示された回路構成を採用し、異なる行から同時に、蓄積型の画素信号と光起電力型の画素信号を出力する場合の駆動タイミングの一例を示している。

## 【0151】

30

同図の場合、蓄積型のP相電圧と光起電力型の信号電圧が同時に読み出され、蓄積型のD相電圧と光起電力型の暗時電圧が同時に読み出される。このように同期させることにより、ある行の蓄積型画素信号と、別の行の光起電力型画素信号とを同時にA/D変換することができる。これにより、より高いフレームレートを得ることができる。なお、光起電力型駆動の露光期間中は、TG71の電圧を、VDDより低い電位（同図L, M）に設定してもよい。これにより、PN接合ダイオード11の実効的な接合容量を減少させ、PN接合ダイオード11に発生する光起電力を、より短時間で安定化させることができる。

## 【0152】

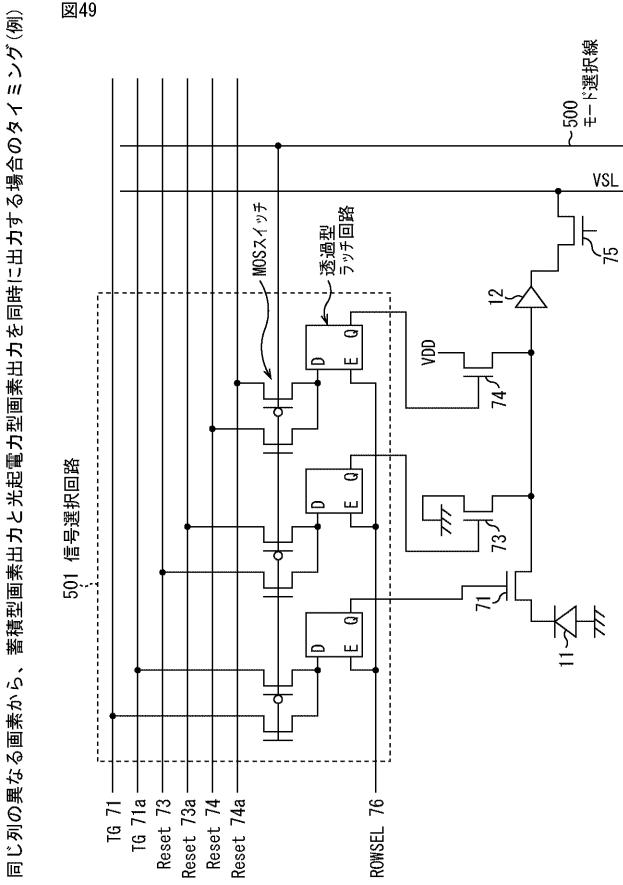

次に、図49は、1フレーム内の同じ行で列単位に蓄積型の駆動タイミングと光起電力型の駆動タイミングを選択するための選択回路の一例を示している。

## 【0153】

40

ただし、同図において、TG71は、光起電力型タイミング用転送ゲート信号を表す。TG71aは、蓄積型タイミング用転送ゲート信号を表す。Reset73および74は光起電力型タイミング用リセット信号を表す。Reset73aおよび74aは、蓄積型タイミング用リセット信号を表す。ROWSEL76は、行選択期間中、オンとされる信号である。

## 【0154】

モード選択線500は光起電力型と蓄積型のタイミング選択信号（0Vのとき蓄積型が選択され、VDDのとき光起電力型が選択される）を伝送する信号線であり、画素列毎、または所定の列間隔毎に設けられる。信号選択回路501はモード選択線の信号電圧によって、転送ゲート71、リセットゲート73、74に伝送する信号を選択するためのものである。透過型ラッチ回路は、D, E, Qの端子を有し、ROWSEL76がオンのときは、端子

50

Dの入力電圧が端子Qに出力され、ROWSEL 7 6がオフになると、次にオンになるとまで、オフ時の端子Qの電圧が保持される。

【0155】

同図に示された選択回路においては、読み出し行のROWSEL 7 6がオンとされると、モード選択線500の信号電圧に応じて、蓄積型、または、光起電力型の駆動信号がMOSスイッチによって選択され、透過型ラッチ回路を介して転送ゲート71、リセットゲート73, 74に伝送される。すなわち、ある画素が、蓄積型で駆動されるか、光起電力型で駆動されるかは、モード選択線500の信号電圧によって決定される。したがって、モード選択線500の信号電圧を列ごとに変えることにより、選択行の各画素の駆動タイミングを、列毎に任意に選択することができる。

10

【0156】

ROWSEL 7 6がオフになると、透過型ラッチ回路の出力電圧が保持されるので、その行が次に選択されるまでの間、蓄積型、または、光起電力型の信号電圧が保持される。よって、各画素は、1フレーム期間を通して、蓄積型、または、光起電力型のいずれかのタイミングで駆動される。

【0157】

なお、図49に示された選択回路は、1画素毎に設けてもよいし、例えばペイヤ配列の繰り返し周期毎に設けてもよい。または、より大きな領域ごとに設けてもよい。いずれの場合も、該選択回路が画素の開口率や蓄積電荷量を制限しないように、画素構造は裏面照射型とし、該選択回路は、回路基板57上に配置することが望ましい。

20

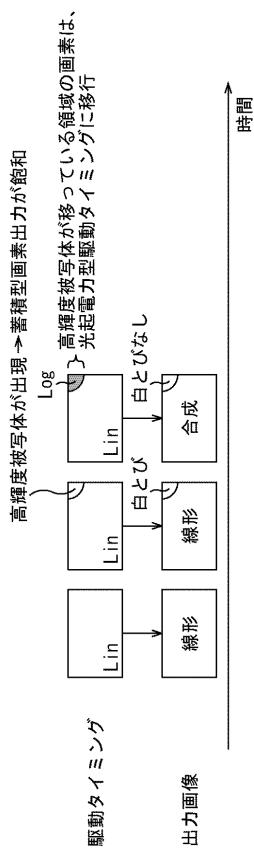

【0158】

図49の選択回路を設けることにより、図50に示される効果を得ることができる。図50は、線形画像で動画撮影中のシーンに、突然、高輝度の被写体が出現した場合に得られる効果を示している。

【0159】

高輝度被写体が写っている領域では、一部の蓄積型画素の出力が飽和する。撮像素子では、制御回路(不図示)により、出力が飽和した画素が検出され、出力が飽和した画素の領域の駆動タイミングが、次フレームでは、選択的に光起電力型に変更される。次フレームでは、高輝度被写体が写っている領域のモード選択線500に、光起電力型の選択信号が出力されるので、高輝度被写体は光起電力型の駆動タイミングで撮像され、その他の領域は、蓄積型の駆動タイミングで撮影される。

30

【0160】

このように撮影された対数画像と線形画像を合成してから出力することで、高輝度被写体が写っている領域以外ではS/Nが良く、かつ、高輝度被写体でも階調や色再現性が良好で解像度の高い合成画像を得ることができる。

【0161】

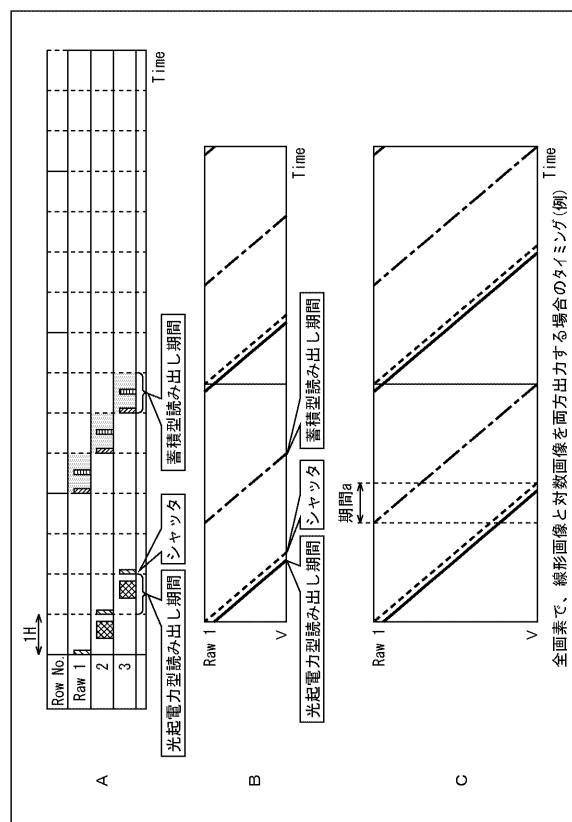

次に、図51は、1フレーム内の全画素から蓄積型画素信号と光起電力型画素信号の両方を出力する場合の駆動タイミングの例を示している。

【0162】

同図に示したように、各画素は、図48に示された光起電力型の駆動タイミングで光起電力型画素信号を出力した後、直ちに図48に示された蓄積型のタイミングで駆動され、蓄積型画素信号を出力するようにする。この結果、1フレームを構成する全画素による対数画像と線形画像の両方が得ることが可能となる。

40

【0163】

また、図51の場合、光起電力型と蓄積型の露光期間が連続しているため、両者の露光タイミングのずれが小さい。その結果、対数画像と線形画像の像ずれが軽減されるので、両者の合成画像におけるアーティファクト発生が抑制される。

【0164】

さらに、図51の駆動タイミングを用いることで、図52に示される効果を得ることができる。図52は、線形画像で動画撮影中のシーンに、突然、高輝度の被写体が出現した

50

場合に得られる効果を示している。

【0165】

高輝度被写体が写っている領域では、一部の蓄積型出力が飽和する。しかしながら、1フレーム内の全ての画素が光起電力型と蓄積型の両方の画素信号を出力しているので、それらの出力をラインバッファやフレームバッファに保存しておくことにより、蓄積型出力が飽和した画素では、光起電力型出力を参照して、対数画像と線形画像を合成することができる。この結果、図52に示されるように、高輝度被写体が出現した最初のフレームから、高輝度被写体が写っている領域以外ではS/Nが良く、かつ、高輝度被写体も良好な階調や色再現性を有する、解像度の高い合成画像を得ることができる。

【0166】

10

なお、図46に示された回路構成を図51Aに示された駆動タイミングで動作させててもよく、その場合、図51Cの期間aで実行されているように、異なる行から、それぞれ光起電力型画素信号と蓄積型画素信号を同時に出力することができる。これにより、図51の駆動タイミングでフレームレートを高めることができる。

【0167】

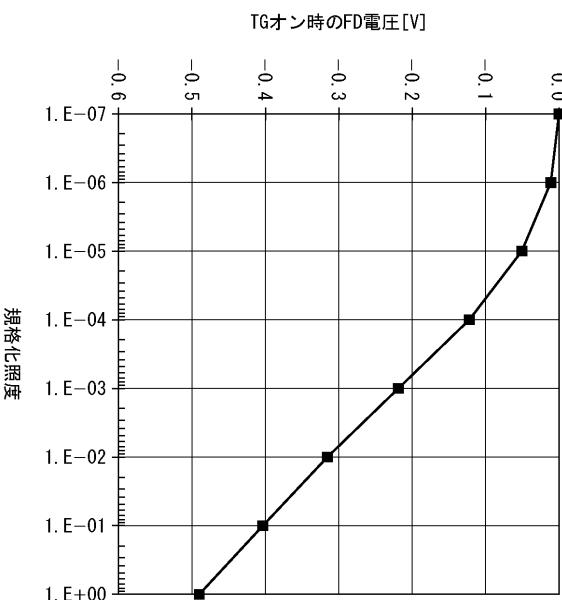

<FD37の出力電圧特性>

次に、図53は、図36に示された第8の構成例においてTG71をオンにした状態での照射光に対応するFD72の出力電圧のシミュレーション結果を示している。同図に示されるように、FD72の出力電圧は、照度に対して対数的に増加することが分かる。すなわち、第8の構成例が光起電力型画素としても動作していることがわかる。

20

【0168】

<光起電力型画素の出力値の較正>

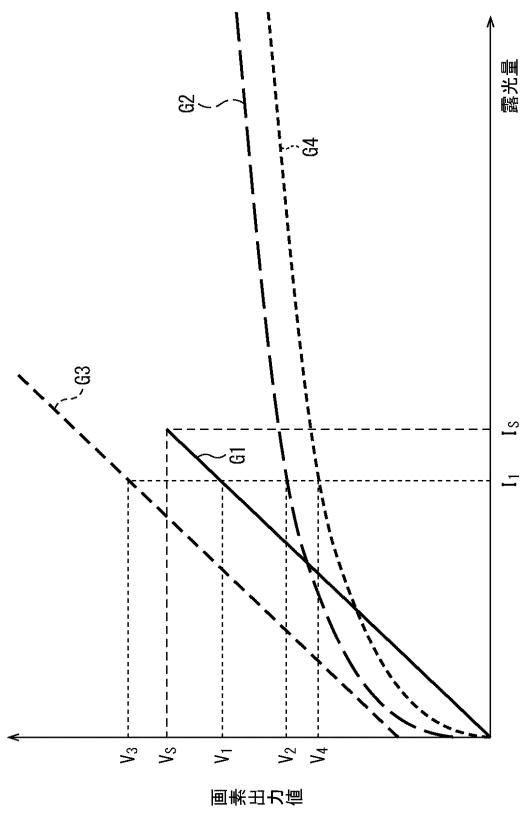

図54は、光起電力型画素出力値を、同一画素、または近傍画素の蓄積型画素出力値を用いて較正する方法の概要を示している。

【0169】

なお、同図において、 $I_s$ ,  $V_s$ は蓄積型タイミングで駆動し、蓄積電荷量が飽和するときの露光量とその時の画素出力値を表している。グラフG1は、ある画素を蓄積型タイミングで駆動したときの蓄積型出力値と露光量の関係、または、該画素を蓄積型タイミングで駆動したと仮定した場合に予想される画素出力値と露光量の関係を模式的に表したものである。グラフG2は、グラフG1の画素を光起電力型タイミングで駆動したときの較正前の光起電力型出力値と露光量の関係を模式的に表したものである。グラフG3は、グラフG2の画素出力値を対数値から線形値に変換することによって得られる画素出力値と露光量の関係を模式的に表したものである。グラフG4は、グラフG2の光起電力型出力値を、グラフG3とグラフG1の比較結果を用いて較正した後の光起電力型出力値と露光量の関係を模式的に表したものである。

30

【0170】

ここで、「ある画素の蓄積型出力値（または、その予想値）」は、撮像素子を構成する、複数の同色画素の蓄積型出力の平均値（または、その予想値）、あるいは、個々の画素の蓄積型出力値（または、その予想値）を指す。同様に、「ある画素の光起電力型出力値」は、撮像素子を構成する、複数の同色画素の光起電力型出力の平均値、または、個々の画素の光起電力型出力値を指す。

40

【0171】

初めに、蓄積型駆動時の信号量が飽和しない露光量 $I_1$ で、蓄積型画素出力 $V_1$ と、光起電力型画素出力 $V_2$ を取得する。次に、光起電力型画素出力 $V_2$ の値を、対数値から線形値に変換し、線形変換後の光起電力型出力値 $V_3$ を得て、光起電力型出力値 $V_3$ が蓄積型画素出力 $V_1$ と一致するように光起電力型出力値の較正パラメータを算出する。これ以後は、この較正パラメータを用いて光起電力型出力値を較正することにより、蓄積型画素出力となめらかにつながるような光起電力型出力を得ることができる。

【0172】

ここで、蓄積型画素出力 $V_1$ を、ある画素を蓄積型タイミングで駆動したときの信号量

50

とし、光起電力型画素出力V2を、同じ画素を光起電力型タイミングで駆動したときの信号量とすることができます。

【0173】

または、光起電力型画素出力V2を、ある画素を光起電力型タイミングで駆動したときの信号量とし、蓄積型画素出力V1を、その画素を蓄積型タイミングで駆動したと仮定したときの信号量予測値とすることができます。ここで、信号量予測値は、近傍の1つ、または、複数の同色画素の蓄積型出力値から、補間などの方法を用いて求めることができる。

【0174】

なお、上記の較正パラメータは、センサの個体毎に定めてもよいし、所定の画素領域毎に定めてもよいし、または個々の画素毎に定めてもよい。また、較正パラメータは、撮像素子出荷前の検査工程で算出してもよいし、または撮像素子出荷後に撮影した画像から算出するようにしてもよい。

10

【0175】

そして、上記のようにして求めた較正パラメータは、画素が形成される基板54、あるいは、回路基板57、または基板54と同一のパッケージに実装される別基板(不図示)に形成された記憶素子に記録するようにして、対数画像と線形画像の合成時に参照できるようとする。

【0176】

または、較正パラメータを撮像素子外部の画像処理装置(不図示)に伝送して記憶し、該画像処理装置で対数画像と線形画像を合成する際に参照できるようにする。

20

【0177】

このように光起電力型出力値を較正することにより、光起電力型画素の出力値が温度変化した場合でも、蓄積型画素出力値と連続する出力値を求めることが可能となる。よって、蓄積型画素として動作した場合の画像と光起電力型画素として動作した場合の画像を合成したときの輝度や色の段差を抑制することができる。

【0178】

<まとめ>

以上説明したように、第1および第2の実施の形態によれば、素子分離領域を設けたことにより、信号電荷の隣接画素への拡散を阻止することができる。

【0179】

30

これにより、光起電力型画素近傍へのクロストークが抑制され、第1の実施の形態では、画質や感度を劣化させることなく、光起電力型画素と蓄積型画素の隣接配置が可能となる。

【0180】

さらに、光起電力型画素と蓄積型画素の隣接配置が可能となったことにより、例えば、ハーフミラーを用いるような大掛かりで高価な光学系を用いることなく、リニア出力画像と対数出力画像を、同一撮像素子で取得できる。

【0181】

そして、線形画像と対数画像を、同一撮像素子で取得できることにより、被写体の低輝度部分が黒潰れしたり、高輝度部分が白とびしたりすることなく、ノイズの少ない画像を広い輝度範囲で得ることが可能となる。

40

【0182】

また、第2の実施の形態によれば、暗電流を増加させることなく、同一画素を光起電力型画素と蓄積型画素として動作させることができるので、被写体の低輝度部分では、蓄積型出力値を用い、高輝度部分は光起電力型出力値を用いて画像を合成することが可能となる。これにより、解像度を犠牲にすることなく、線形画像と対数画像を取得可能となる。

【0183】

さらに、蓄積型出力値を用いて光起電力型出力値を較正することにより、光起電力型出力値の温度変化をキャンセルすることができる。これにより、線形画像と対数画像の境界における輝度や色の段差を低減することが可能となる。

50

## 【0184】

なお、上述した第1および第2の実施の形態は、デジタルカメラに代表される撮像装置だけでなく、撮像機能を有するあらゆる電子装置に適用することが可能である。

## 【0185】

また、本開示の実施の形態は、上述した実施の形態に限定されるものではなく、本開示の要旨を逸脱しない範囲において種々の変更が可能である。

## 【0186】

本開示は以下のような構成も取ることができる。

(1)

画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と、

隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を実質的に取り囲む状態で設けられた素子分離領域と

を備える撮像素子。

(2)

前記素子分離領域は、前記光起電力型画素の信号電荷の隣接画素への拡散を阻止する材料により構成されている

前記(1)に記載の撮像素子。

(3)

前記光起電力型画素に隣接する位置に蓄積型画素を

さらに備える前記(1)または(2)に記載の撮像素子。

20

(4)

前記光電変換領域には、フォトセンサとしてPN接合ダイオードが形成されている

前記(1)から(3)のいずれかに記載の撮像素子。

(5)

前記光起電力型画素は、さらに、転送ゲートおよびフローティングディフュージョンを有し、蓄積型兼光起電力型画素として動作する

前記(1)から(4)のいずれかに記載の撮像素子。

(6)

前記蓄積型兼光起電力型画素に隣接する位置に蓄積型画素を

さらに備える前記(5)に記載の撮像素子。

30

(7)

前記光電変換領域、転送ゲート、およびフローティングディフュージョンを有する蓄積型兼光起電力型画素をさらに備え、

前記光起電力型画素と前記蓄積型兼光起電力型画素は隣接して形成されている

前記(1)から(4)のいずれかに記載の撮像素子。

(8)

各画素における前記光電変換領域と画素回路領域との間は絶縁されている

前記(1)から(7)のいずれかに記載の撮像素子。

(9)

撮像素子が搭載された電子装置において、

40

前記撮像素子は、

画素毎に照射光に応じて光起電力を発生する光電変換領域を有する光起電力型画素と

、

隣接する画素それぞれの前記光電変換領域の間に、前記光電変換領域を実質的に取り囲む状態で設けられた素子分離領域と備える

電子装置。

## 【符号の説明】

## 【0187】

10 光起電力型画素， 11 PN接合ダイオード， 12 アンプ， 21 光電変換領域， 22 画素回路領域， 31 P型領域， 32 N型領域， 33, 34

50

電極 , 35 素子分離領域 , 61 光起電力型画素 , 62 蓄積型画素 , 70

蓄積型兼光起電力型画素 , 71 TG , 72 FD , 73 , 74 RST , 75 Sel

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7【図8】

図8【図9】

図9【図10】

図10

【図11】

【図12】

【図13】

【図14】

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

【図20】

### 【図21】

【 図 2 2 】

【図23】

図23

【図24】

図24

手順1 (P相 → D相)の画素出力信号 = VSG1 – VDK1

手順2 (D相 → P相)の画素出力信号 = VSG1 – VDK2

【図25】

図25

【図26】

図26

【図27】

図27

【図28】

図28

1フレームの中での蓄積型画素と光起電力型画素を同時に読み出す場合のタイミング(例)

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

【図33】

図33

【図34】

図34

【図35】

図35

【図36】

図36

【図37】

図37

【図38】

図38

【図39】

図39

【図40】

図40

【図41】

図41

【図42】

図42

【図43】

図43

【図44】

図44

【図45】

図45

【図46】

図46

【図47】

図47

【図48】

図48

【図49】

図49

同じ列の異なる画素から、蓄積型画素出力と光起電力型画素出力を同時に出力する場合のタイミング(例)

【図50】

図50

【図51】

図51

全画素で、線形画像と対数画像を両方出力する場合のタイミング(例)

【図52】

図52

【図53】

図53

【図54】

図54

---

フロントページの続き

審査官 小川 将之

(56)参考文献 特開2001-156280(JP,A)

特開2010-103316(JP,A)

特表2012-520599(JP,A)

特開2011-188148(JP,A)

特開2004-336469(JP,A)

特開2013-211832(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146