(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6239683号

(P6239683)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl.

F 1

|             |               |                  |             |              |

|-------------|---------------|------------------|-------------|--------------|

| <b>G02F</b> | <b>1/136</b>  | <b>(2006.01)</b> | <b>GO2F</b> | <b>1/136</b> |

| <b>H01L</b> | <b>21/822</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/04</b> |

| <b>H01L</b> | <b>27/04</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> |

| <b>H01L</b> | <b>21/336</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/04</b> |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>GO9F</b> | <b>9/30</b>  |

請求項の数 2 (全 52 頁) 最終頁に続く

(21) 出願番号 特願2016-92860 (P2016-92860)

(22) 出願日 平成28年5月3日 (2016.5.3)

(62) 分割の表示 特願2014-204537 (P2014-204537)

原出願日 平成22年3月16日 (2010.3.16)

(65) 公開番号 特開2016-167624 (P2016-167624A)

(43) 公開日 平成28年9月15日 (2016.9.15)

審査請求日 平成28年5月5日 (2016.5.5)

(31) 優先権主張番号 特願2009-78084 (P2009-78084)

(32) 優先日 平成21年3月27日 (2009.3.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 魚地 秀貴

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 河江 大輔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】表示装置

(57) 【特許請求の範囲】

【請求項 1】

画素部と、

前記画素部を駆動する駆動回路と、

前記駆動回路と電気的に接続される端子部と、を有し、

前記端子部はフィルタ回路を有し、

前記フィルタ回路は、抵抗と容量素子とを有し、

前記抵抗の第1の端子は、前記容量素子の一方の電極と電気的に接続され、

前記抵抗の前記第1の端子は、前記駆動回路と電気的に接続され、

前記フィルタ回路は、

配線と、

前記配線上の第1の絶縁層と、

前記第1の絶縁層上の第1の酸化物半導体層と、

前記第1の酸化物半導体層上の第2の絶縁層と、

前記第2の絶縁層上の端子電極と、を有し、

前記端子電極と前記第1の酸化物半導体層とは、前記第2の絶縁層を介して重なっており、

前記容量素子は、前記端子電極と、前記第2の絶縁層と、前記第1の酸化物半導体層とを有し、

前記端子電極と前記第1の酸化物半導体層とは、前記容量素子の電極としての機能を有

10

20

することを特徴とする表示装置。

【請求項 2】

画素部と、

前記画素部を駆動する駆動回路と、

前記駆動回路と電気的に接続される端子部と、を有し、

前記端子部はフィルタ回路を有し、

前記フィルタ回路は、抵抗と容量素子とを有し、

前記抵抗の第 1 の端子は、前記容量素子の一方の電極と電気的に接続され、

前記抵抗の前記第 1 の端子は、前記駆動回路と電気的に接続され、

前記フィルタ回路は、

10

配線と、

前記配線上の第 1 の絶縁層と、

前記第 1 の絶縁層上の第 1 の酸化物半導体層と、

前記第 1 の酸化物半導体層上の第 2 の絶縁層と、

前記第 2 の絶縁層上の端子電極と、を有し、

前記抵抗は、前記配線の配線抵抗であり、

前記配線と前記第 1 の酸化物半導体層とは、前記第 1 の絶縁層を介して重なっており、

前記容量素子は、前記配線と、前記第 1 の絶縁層と、前記第 1 の酸化物半導体層とを有し、

前記配線と前記第 1 の酸化物半導体層とは、前記容量素子の電極としての機能を有する 20

ことを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置に関する。また、表示装置に関する。また、表示装置を表示部に有する電子機器に関する。

【背景技術】

【0002】

金属酸化物は多様に存在しさまざまな用途に用いられている。例えば酸化インジウムはよく知られた材料であり、液晶ディスプレイなどで必要とされる透明電極材料として用いられている。

30

【0003】

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タンクステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域とする薄膜トランジスタが既に知られている（特許文献 1 乃至 4、非特許文献 1）。

【0004】

ところで、金属酸化物は一元系酸化物のみでなく多元系酸化物も知られている。例えば、ホモロガス相を有する  $In_xGa_3(ZnO)_m$  ( $m$  : 自然数) は、In、Ga 及び Zn を有する多元系酸化物半導体として知られている（非特許文献 2 乃至 4）。

40

【0005】

そして、上記のような  $In_xGa_3(ZnO)_m$  系酸化物で構成される酸化物半導体を薄膜トランジスタのチャネル層として適用可能であることが確認されている（特許文献 5、非特許文献 5 及び 6）。

【0006】

酸化物半導体をチャネル形成層として用いた TFT は、アモルファスシリコンを用いた TFT よりも高い電界効果移動度が得られている。

【0007】

このような酸化物半導体を用いた TFT をガラス基板、プラスチック基板などに形成し、液晶ディスプレイ、エレクトロルミネセンスディスプレイ（ELディスプレイともいう）

50

または電子ペーパなどの表示装置への応用が期待されている。

**【0008】**

ところで表示装置などの半導体装置では、ノイズにより、誤動作や、表示装置内の回路が破壊されるといった問題がある。

**【0009】**

上記ノイズとしては、例えば伝導性ノイズや放射性ノイズなどがあり、伝導性ノイズとしては、例えば高速バースト波などがあり、放射性ノイズとしては、例えば静電気放電などがある。

**【0010】**

上記ノイズによる影響を低減するため、現在ノイズに対する様々な保護手段が設けられた表示装置が提案されている。（特許文献6）

10

**【先行技術文献】**

**【特許文献】**

**【0011】**

【特許文献1】特開昭60-198861号公報

【特許文献2】特開平8-264794号公報

【特許文献3】特表平11-505377号公報

【特許文献4】特開2000-150900号公報

【特許文献5】特開2004-103957号公報

【特許文献6】特開平11-150275号公報

20

**【非特許文献】**

**【0012】**

【非特許文献1】M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cillessen, J. B. Giesbers, R. P. Weening, and R. M. Wolf、「A ferroelectric transparent thin-film transistor」、Appl. Phys. Lett.、17 June 1996、Vol. 68 p. 3650-3652

【非特許文献2】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the In<sub>2</sub>O<sub>3</sub>-Ga<sub>2</sub>ZnO<sub>4</sub>-ZnO System at 1350」、J. Solid State Chem.、1991、Vol. 93, p. 298-315

30

【非特許文献3】N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single-Crystal Data of Homologous Compounds, In<sub>2</sub>O<sub>3</sub>(ZnO)<sub>m</sub>(m=3, 4, and 5), InGaO<sub>3</sub>(ZnO)<sub>3</sub>, and Ga<sub>2</sub>O<sub>3</sub>(ZnO)<sub>m</sub>(m=7, 8, 9, and 16) in the In<sub>2</sub>O<sub>3</sub>-ZnGa<sub>2</sub>O<sub>4</sub>-ZnO System」、J. Solid State Chem.、1995、Vol. 116, p. 170-178

【非特許文献4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、InFeO<sub>3</sub>(ZnO)<sub>m</sub>(m:自然数)とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol. 28、No. 5、p. 317-327

40

【非特許文献5】K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor」、SCIENCE、2003、Vol. 300、p. 1269-1272

【非特許文献6】K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room-temperature fabrication of transparent

50

flexible thin-film transistors using amorphous oxide semiconductors」、NATURE、2004、Vol. 432 p. 488 - 492

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明の一態様では、実動作の阻害を低減し、ノイズによる影響を低減することを課題の一つとする。

【課題を解決するための手段】

【0014】

本発明の一態様は、端子電極または配線となる導電層と、酸化物半導体層と、絶縁層と、を用いて構成される容量素子を有するものであり、また、該容量素子と抵抗素子によりフィルタ回路を構成することによりフィルタリングを行いノイズによる影響を低減するというものである。

【0015】

本発明の一態様は、端子電極と、端子電極に電気的に接続された配線と、平面視において端子電極と重なる酸化物半導体層と、断面視において端子電極と酸化物半導体層の間に設けられた絶縁層と、配線を介して端子電極から信号が入力され、入力された信号に応じて動作が制御される機能回路と、を有する半導体装置である。

【0016】

本発明の一態様は、端子電極と、端子電極に電気的に接続された配線と、平面視において配線と重なる酸化物半導体層と、断面視において配線と酸化物半導体層の間に設けられた絶縁層と、配線を介して端子電極から信号が入力され、入力された信号に応じて動作が制御される機能回路と、を有する半導体装置である。

【0017】

なお、本発明の一態様において、酸化物半導体層は、電源電圧が与えられる構成とすることもできる。

【0018】

本発明の一態様は、端子電極と、第1の配線と、端子電極に電気的に接続された第2の配線と、第2の配線に電気的に接続され、平面視において第1の配線と重なる酸化物半導体層と、断面視において第1の配線と酸化物半導体層の間に設けられた絶縁層と、第2の配線を介して端子電極から信号が入力され、入力された信号に応じて動作が制御される機能回路と、を有する半導体装置である。

【0019】

なお、本発明の一態様において、第1の配線は、電源電圧が与えられる構成とすることもできる。

【0020】

また、本発明の一態様において、機能回路は、酸化物半導体層を用いた半導体素子を有する構成とすることもできる。

【0021】

本発明の一態様は、基板と、基板上に設けられた配線と、配線を挟んで基板上に設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の酸化物半導体層と、酸化物半導体層を挟んで第1の絶縁層上に設けられた第2の絶縁層と、第2の絶縁層上に設けられ、第1の絶縁層及び第2の絶縁層に設けられた開口部を介して配線に電気的に接続された端子電極と、配線を介して端子電極から信号が入力され、入力された信号に応じて動作が制御される駆動回路と、駆動回路により動作が制御される画素と、を有し、駆動回路及び画素は、トランジスタを有し、トランジスタは、基板上に設けられたゲート電極と、ゲート電極を挟んで基板上に設けられたゲート絶縁層と、ゲート絶縁層上に設けられたソース電極及びドレイン電極と、ゲート絶縁層を挟んでゲート電極上に設けられ、且つソース電極及びドレイン電極を挟んでゲート絶縁層上に設けられた第2の酸化物半導体層と、ソース電

10

20

30

40

50

極及びドレイン電極、並びに第2の酸化物半導体層を挟んでゲート絶縁層上に設けられた保護層と、保護層上に設けられ、保護層に設けられた開口部を介してソース電極及びドレイン電極の一方に電気的に接続された電極と、を有する表示装置である。

【0022】

なお、本発明の一態様において、第1の酸化物半導体層は、第1の絶縁層を挟んで配線上に設けられる構成とすることもできる。

【0023】

また、本発明の一態様において、端子電極は、第2の絶縁層を挟んで第1の酸化物半導体層上に設けられる構成とすることもできる。

【0024】

また、本発明の一態様において、第1の絶縁層は、ゲート絶縁層と同一層であり、第2の絶縁層は、保護層と同一層である構成とすることもできる。

【0025】

本発明の一態様は、上記記載の表示装置を表示部に有する電子機器である。

【0026】

本発明の一態様は、基板上に第1の導電膜を形成し、第1の導電膜を選択的にエッチングすることにより、第1の導電層及び第2の導電層を形成し、第1の導電層及び第2の導電層を挟んで基板上に第1の絶縁層を形成し、第1の絶縁層を選択的にエッチングすることにより、第1の導電層の一部を露出させ、第1の絶縁層上に第2の導電膜を形成し、第2の導電膜を選択的にエッチングすることにより、第3の導電層及び第4の導電層を形成し、第3の導電層及び第4の導電層を挟んで第1の絶縁層上に酸化物半導体膜を形成し、酸化物半導体膜を選択的にエッチングすることにより、第1の絶縁層上に第1の酸化物半導体層を形成し、第2の導電層、並びに第3の導電層及び第4の導電層を挟んで第2の導電層上に第2の酸化物半導体層を形成し、第3の導電層及び第4の導電層、並びに第1の酸化物半導体層及び第2の酸化物半導体層を挟んで第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層を選択的にエッチングすることにより、第1の導電層の一部及び第4の導電層の一部を露出させ、露出した第1の導電層の一部の上、露出した第4の導電層の一部の上、及び第2の絶縁層上に第3の導電膜を形成し、第3の導電膜を選択的にエッチングすることにより、第1の導電層に電気的に接続され、端子電極としての機能を有する第5の導電層と、第4の導電層に電気的に接続された第6の導電層と、を形成する表示装置の作製方法である。

【0027】

なお、本発明の一態様において、第1の絶縁層を挟んで配線上に第1の酸化物半導体層を形成することもできる。

【0028】

また、本発明の一態様において、第2の絶縁層を挟んで酸化物半導体層上に端子電極を形成することもできる。

【発明の効果】

【0029】

本発明の一態様により、実動作の阻害を低減し、ノイズによる影響を低減することができる。

【図面の簡単な説明】

【0030】

【図1】実施の形態1における半導体装置の構造の一例を示す図である。

【図2】実施の形態1における半導体装置の構造の一例を示す図である。

【図3】実施の形態1における半導体装置の構造の一例を示す図である。

【図4】実施の形態1における半導体装置の構造の一例を示す図である。

【図5】実施の形態1における半導体装置の構造の一例を示す図である。

【図6】実施の形態1における半導体装置の構造の一例を示す図である。

【図7】実施の形態1における半導体装置の構造の一例を示す図である。

10

20

30

40

50

【図 8】図 1 乃至図 7 にそれぞれ示す半導体装置の等価回路を示す回路図である。

【図 9】実施の形態 1 における容量素子の電圧 容量特性の検証結果を示す図である。

【図 10】実施の形態 1 における機能検証を行うフィルタ回路の回路モデルを示す回路図である。

【図 11】図 10 に示す回路モデルの計算による検証における第 1 のデジタル信号が入力される場合の入出力特性を示す図である。

【図 12】図 10 に示す回路モデルの計算による検証における第 2 のデジタル信号が入力される場合の入出力特性を示す図である。

【図 13】図 10 に示す回路モデルの計算による検証における第 3 のデジタル信号が入力される場合の入出力特性を示す図である。 10

【図 14】実施の形態 2 における表示装置の構成の一例を示す図である。

【図 15】図 14 に示す表示装置の画素の回路構成の一例を示す回路図である。

【図 16】図 14 に示す表示装置の画素におけるトランジスタの構造の一例を示す断面図である。

【図 17】図 14 に示す表示装置の画素におけるトランジスタの構造の一例を示す断面図である。

【図 18】図 14 に示す表示装置の駆動回路の構成を示すブロック図である。

【図 19】図 14 に示す表示装置の端子部の構造の一例を示す図である。

【図 20】実施の形態 3 における表示装置の端子部及び半導体素子部の作製方法の一例を示す断面図である。 20

【図 21】実施の形態 3 における表示装置の端子部及び半導体素子部の作製方法の一例を示す断面図である。

【図 22】実施の形態 3 における表示装置の端子部及び半導体素子部の作製方法の一例を示す断面図である。

【図 23】実施の形態 4 における発光パネルの構造の一例を示す図である。

【図 24】実施の形態 4 における液晶パネルの構造の一例を示す図である。

【図 25】実施の形態 4 における液晶表示モジュールの一例を示す図である。

【図 26】実施の形態 5 における電子ペーパーの構造の一例を示す断面図である。

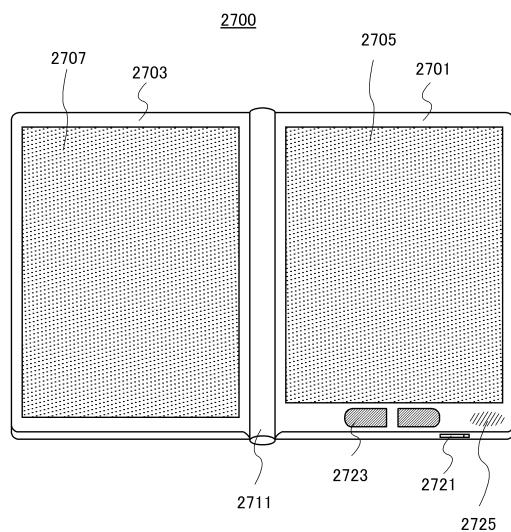

【図 27】実施の形態 5 における電子書籍の構成の一例を示す図である。

【図 28】実施の形態 6 における電子機器の構成の一例を示す図である。 30

【図 29】実施の形態 6 における電子機器の構成の一例を示す図である。

【図 30】実施の形態 6 における電子機器の構成の一例を示す図である。

#### 【発明を実施するための形態】

##### 【0031】

本発明の実施の形態例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではないとする。

##### 【0032】

##### (実施の形態 1)

本実施の形態では、本発明の一態様である半導体装置について説明する。 40

##### 【0033】

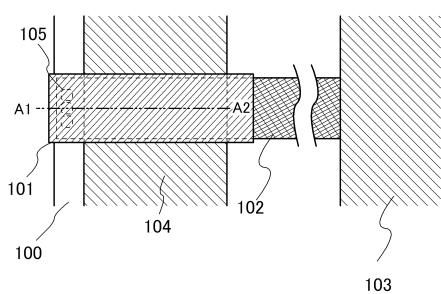

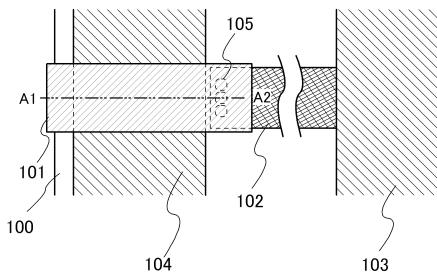

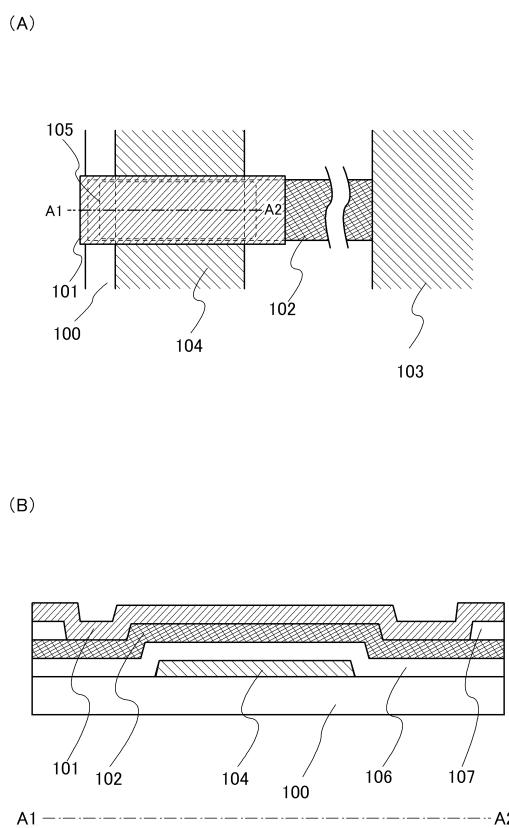

本実施の形態における半導体装置の構造の一例について図 1 を用いて説明する。図 1 は本実施の形態における半導体装置の構造の一例を示す図であり、図 1 (A) は上面図であり、図 1 (B) は、図 1 (A) の線分 A<sub>1</sub> - A<sub>2</sub> における断面図である。

##### 【0034】

図 1 に示す半導体装置は、図 1 (A) に示すように、基板 100 と、電極 101 と、配線 102 と、機能回路 103 と、酸化物半導体層 104 と、を有し、さらに図 1 (B) に示すように、絶縁層 106 と、絶縁層 107 と、を有する。

##### 【0035】

10

20

30

40

50

また、図1(B)に示すように、配線102は基板100上に設けられ、絶縁層106は配線102を挟んで基板100上に設けられ、酸化物半導体層104は絶縁層106上に設けられ、絶縁層107は酸化物半導体層104を挟んで絶縁層106上に設けられる。

#### 【0036】

なお、本明細書において、特に指定する場合を除き、AはB上に設けられる、またはAはBの上に設けられると記載した場合、Bは必ずしもAの上に直接接して設けられる必要はなく、例えば断面視においてAとBと間に別の対象物が介在する場合も含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、膜、層、など）であるとする。

#### 【0037】

また、AはBの下に設けられると記載した場合も同様に、Aは必ずしもBの下に直接接して設けられる必要はなく、例えば断面視においてAとBとの間に別の対象物が介在する場合も含むものとする。

#### 【0038】

電極101は、絶縁層106及び絶縁層107に設けられた開口部105を介して配線102に電気的に接続される。電極101は、半導体装置の端子電極としての機能を有する。端子電極は、例えば外部から信号が入力される端子（信号入力端子ともいう）、電源が与えられる端子（電源端子ともいう）、または他の素子または回路などとの接続部として用いられる端子（接続端子ともいう）としての機能を有することができる。電極101としては、例えば導電材料を用いることができる。

10

20

#### 【0039】

配線102としては、例えば導電材料を用いることができる。

#### 【0040】

機能回路103は、所定の機能を有する回路であり、例えば電極101及び配線102を介して信号が入力され、入力された信号に応じて動作が制御される。例えば機能回路103は、例えば電極101及び配線102を介して電圧が与えられる。機能回路103は、例えば半導体素子を有する電子回路を用いて構成することができ、さらに半導体素子は、例えば酸化物半導体材料を用いて構成することができる。酸化物半導体材料は、一部に透光性を有するものがあり、また例えば非晶質シリコンなどより高い移動度を有する。

30

#### 【0041】

なお、一般的に電圧とは、2点間における電位の差（電位差ともいう）のことをいい、電位とは、ある基準点から電場内の別の一点へ単位電荷を運ぶために必要な仕事量のことという。しかし、電子回路では、回路図などにおいて、一点のみであっても、例えば該一点の電位と基準となる電位（基準電位ともいう）との電位差を値として用いることがあり、また、電圧と電位の値は、回路図などにおいていずれもボルト(V)で表されることがあるため、区別が困難である。そこで、本願の書類（明細書及び特許請求の範囲）では、ある一点の電圧と示す場合、特に指定する場合を除き、ある一点の電圧とは、該一点の電位と基準電位との電位差を示すものとする。

#### 【0042】

電源電圧としては、例えば相対的に高電圧側の電圧または低電圧側の電圧を用いることができる。高電圧側の電源電圧を高電源電圧( $V_{dd}$ ともいう)といい、低電圧側の電源電圧を低電源電圧( $V_{ss}$ ともいう)という。また、接地電位を高電源電圧または低電源電圧として用いることもできる。例えば高電源電圧が接地電位の場合には、低電源電圧は接地電位より低い電圧であり、低電源電圧が接地電位の場合には、高電源電圧は接地電位より高い電圧である。

40

#### 【0043】

酸化物半導体層104としては、例えば酸化物半導体材料を用いることができる。よって例えば機能回路103に酸化物半導体材料を用いた半導体素子を適用する場合には、機能回路103の半導体素子に用いられる半導体層と、酸化物半導体層104を同一層とし、同一の酸化物半導体材料からなる半導体膜（酸化物半導体膜ともいう）を選択的にエッチ

50

ングして、機能回路 103 の半導体素子に用いられる半導体層と、酸化物半導体層 104 と、を形成することもできるため、工程数を増やさずに酸化物半導体層 104 を形成することができる。

#### 【0044】

酸化物半導体膜としては、例えば Sn、In、及び Zn のいずれかを含む酸化物半導体膜などを用いることができる。また、酸化物半導体膜を用いる場合、酸化物半導体膜にアモルファス成分を含むものを用いることもできる。また、酸化物半導体膜の中に結晶粒（ナノクリスタルともいう）を含むものを用いることもできる。このとき、酸化物半導体膜中の結晶粒（ナノクリスタルともいう）は直径 1 nm ~ 10 nm、代表的には 2 nm ~ 4 nm 程度である。

10

#### 【0045】

また、酸化物半導体としては、例えば、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される構造の酸化物半導体を用いることもできる。なお、M は、ガリウム (Ga)、鉄 (Fe)、ニッケル (Ni)、マンガン (Mn) 及びコバルト (Co) から選ばれた一の金属元素または複数の金属元素を示す。例えば M として、Ga の場合があることの他、Ga と Ni または Ga と Fe など、Ga 以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、M として含まれる金属元素の他に、不純物元素として Fe、Ni その他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。本明細書においては、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される構造の酸化物半導体のうち、M として少なくとも Ga を含む構造の酸化物半導体を In-Ga-Zn-O 系酸化物半導体と呼び、該薄膜を In-Ga-Zn-O 系非単結晶膜ともいう。

20

#### 【0046】

また、酸化物半導体膜として上記の他にも、In-Sn-Zn-O 系、Al-In-Zn-O 系、Ga-Sn-Zn-O 系、Al-Ga-Zn-O 系、Al-Sn-Zn-O 系、In-Zn-O 系、Sn-Zn-O 系、Al-Zn-O 系、In-O 系、Sn-O 系、Zn-O 系の酸化物半導体膜を用いることができる。

#### 【0047】

図 1 に一例として示すように、本実施の形態の半導体装置は、酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を有する。この容量素子は保護回路の一部としての機能を有する。また、この容量素子は、ノイズによる影響を低減するためのフィルタ回路の一部としての機能を有する。

30

#### 【0048】

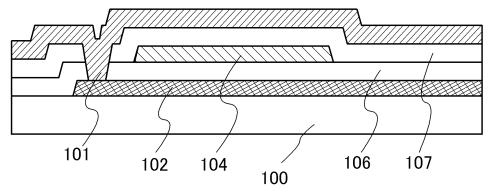

なお、図 1 では、一例として、平面視において、酸化物半導体層 104 と電極 101 が重なり、且つ酸化物半導体層 104 と配線 102 が重なる構造の半導体装置について説明しているが、図 1 に示す半導体装置の構造に限定されず、本実施の形態の半導体装置では、他の構造も適用することができる。本実施の形態における半導体装置の構造の他の一例について図 2 を用いて説明する。図 2 は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図 2 (A) は上面図であり、図 2 (B) は図 2 (A) の線分 A1-A2 における断面図である。

40

#### 【0049】

図 2 に示す半導体装置は、図 2 (A) に示すように電極 101 と、配線 102 と、機能回路 103 と、酸化物半導体層 104 と、配線 108 と、を有し、さらに図 2 (B) に示すように、絶縁層 106 と、絶縁層 107 と、を有する。

#### 【0050】

また、図 2 (B) に示すように、配線 102 は基板 100 上に設けられ、絶縁層 106 は配線 102 を挟んで基板 100 上に設けられ、酸化物半導体層 104 は絶縁層 106 上に設けられ、配線 108 は絶縁層 106 上に設けられ、絶縁層 107 は酸化物半導体層 104 及び配線 108 を挟んで絶縁層 106 上に設けられ、電極 101 は絶縁層 107 上に設けられる。すなわち図 2 (A) に示すように、平面視において、酸化物半導体層 104 と

50

配線 102 が重なる構造である。

【0051】

配線 108 は、酸化物半導体層 104 に電気的に接続され、電極 101 は、配線 108 に電気的に接続される。

【0052】

機能回路 103 は、電極 101 及び配線 108 を介して信号が入力され、入力された信号に応じて動作が制御される。または電極 101 及び配線 108 を介して電圧が与えられる。

【0053】

なお、その他の図 2 に示す半導体装置の各構造の説明は、図 1 に示す半導体装置の各構造の説明と同じであるため、図 1 に示す半導体装置の各構造の説明を適宜援用する。

10

【0054】

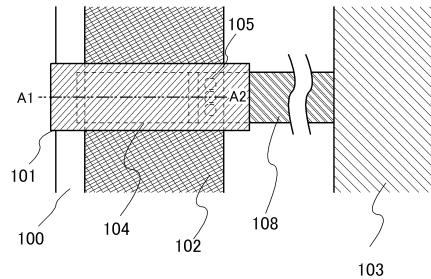

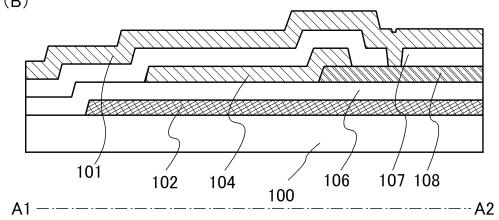

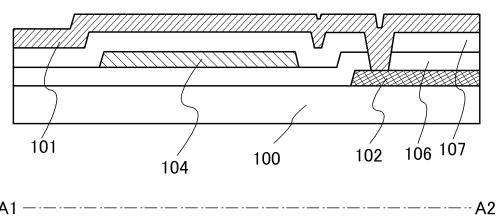

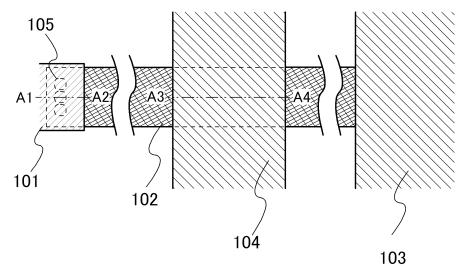

さらに、本実施の形態における半導体装置の構造の他の一例について図 3 を用いて説明する。図 3 は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図 3 (A) は上面図であり、図 3 (B) は図 3 (A) の線分 A1 - A2 における断面図である。

【0055】

図 3 に示す半導体装置は、図 3 (A) に示すように電極 101 と、配線 102 と、機能回路 103 と、酸化物半導体層 104 と、を有し、さらに図 3 (B) に示すように、絶縁層 106 と、絶縁層 107 と、を有する。

20

【0056】

また、図 3 (B) に示すように絶縁層 106 は配線 102 を挟んで基板 100 上に設けられ、酸化物半導体層 104 は絶縁層 106 上に設けられ、絶縁層 107 は酸化物半導体層 104 を挟んで絶縁層 106 上に設けられ、電極 101 は絶縁層 107 を挟んで酸化物半導体層 104 上に設けられる。すなわち図 3 (A) に示すように、平面視において、酸化物半導体層 104 と電極 101 が重なり、酸化物半導体層 104 と配線 102 が重ならない構造である。なお、その他の図 3 に示す半導体装置の各構造の説明は、図 1 に示す半導体装置の各構造の説明と同じであるため、図 1 に示す半導体装置の各構造の説明を適宜援用する。

【0057】

30

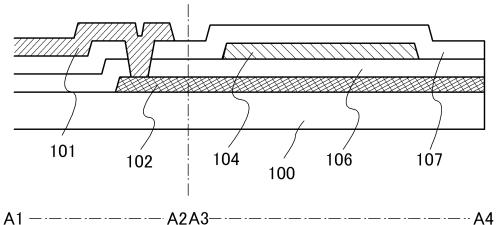

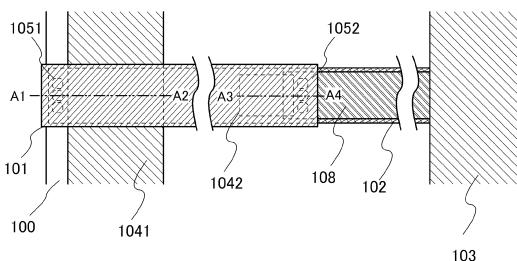

さらに、本実施の形態における半導体装置の構造の他の一例について図 4 を用いて説明する。図 4 は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図 4 (A) は上面図であり、図 4 (B) は図 4 (A) の線分 A1 - A2 及び A3 - A4 における断面図である。

【0058】

図 4 に示す半導体装置は、図 4 (A) に示すように電極 101 と、配線 102 と、機能回路 103 と、酸化物半導体層 104 と、を有し、さらに図 4 (B) に示すように、絶縁層 106 と、絶縁層 107 と、を有する。

【0059】

また、図 4 (B) に示すように、絶縁層 106 は配線 102 を挟んで基板 100 上に設けられ、酸化物半導体層 104 は絶縁層 106 を挟んで配線 102 上に設けられ、絶縁層 107 は酸化物半導体層 104 を挟んで絶縁層 106 上に設けられ、電極 101 は絶縁層 107 上に設けられる。すなわち図 4 (A) に示すように、平面視において、酸化物半導体層 104 と配線 102 が重なり、酸化物半導体層 104 と電極 101 が重ならない構造である。なお、その他の図 4 に示す半導体装置の各構造の説明は、図 1 に示す半導体装置の各構造の説明と同じであるため、図 1 に示す半導体装置の各構造の説明を適宜援用する。

40

【0060】

なお、図 1、図 2、及び図 4 に示す半導体装置は、平面視において、配線 102 と酸化物半導体層 104 が重なる構造である。本実施の形態の半導体装置を必ずしも配線と酸化物半導体層を重ねて設ける構造にする必要はないが、配線と酸化物半導体層とが重なる構造

50

にすることにより、光の入射による酸化物半導体層の劣化を抑えることができる。

#### 【0061】

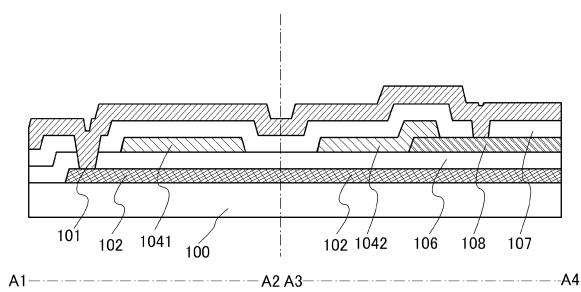

さらに、本実施の形態における半導体装置の構造の他の一例について図5を用いて説明する。図5は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図5(A)は上面図であり、図5(B)は図5(A)の線分A1-A2における断面図である。

#### 【0062】

図5に示す半導体装置は、図5(A)に示すように電極101と、配線102と、機能回路103と、酸化物半導体層1041と、酸化物半導体層1042と、配線108と、を有し、さらに図5(B)に示すように、絶縁層106と、絶縁層107と、を有する。

10

#### 【0063】

また、図5(B)に示すように、配線102は基板100上に設けられ、絶縁層106は配線102を挟んで基板100上に設けられ、配線108は、絶縁層106上に設けられ、酸化物半導体層1041は、絶縁層106を挟んで配線102上に設けられ、酸化物半導体層1042は、絶縁層106及び配線108を挟んで配線102上に設けられ、絶縁層107は、酸化物半導体層1041及び酸化物半導体層1042並びに配線108を挟んで絶縁層106上に設けられ、電極101は、絶縁層107上に設けられる。すなわち図5(A)に示すように、平面視において、酸化物半導体層1041と電極101及び配線102が重なり、酸化物半導体層1042と配線102及び電極101が重なる構造である。

20

#### 【0064】

電極101は、絶縁層106及び絶縁層107に設けられた開口部1051を介して配線102に電気的に接続される。また、電極101は、絶縁層107に設けられた開口部1052を介して配線108に電気的に接続される。

#### 【0065】

酸化物半導体層1041及び酸化物半導体層1042としては、例えば図1に示す酸化物半導体層104に適用可能な材料を用いることができる。

#### 【0066】

なお、その他の図5に示す半導体装置の各構造の説明は、図1に示す半導体装置の各構造の説明と同じであるため、図1に示す半導体装置の各構造の説明を適宜援用する。

30

#### 【0067】

図5に一例として示すように、本実施の形態の半導体装置は、酸化物半導体層を複数有し、複数の酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を複数有する構造とすることもできる。この容量素子のそれぞれは、保護回路の一部としての機能を有する。また、この容量素子は、ノイズによる影響を低減するためのフィルタ回路の一部としての機能を有する。例えば一方の容量素子を正電圧の信号が入力、または正電圧が与えられる場合に機能するフィルタ回路の一部とし、他方の容量素子を負電圧の信号が入力、または負電圧が与えられる場合に機能するフィルタ回路の一部とすることもできる。また図5に示す半導体装置では、複数の酸化物半導体層をそれぞれ同じ導電型にすることができるため、工程数の増加を防ぐことができる。

40

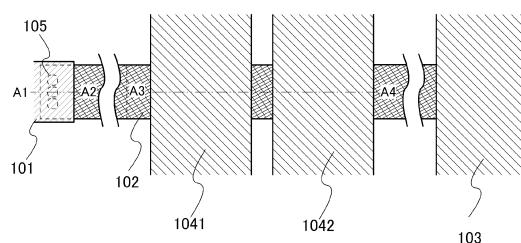

#### 【0068】

さらに、本実施の形態における半導体装置の構造の他の一例について図6を用いて説明する。図6は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図6(A)は上面図であり、図6(B)は図6(A)の線分A1-A2における断面図である。

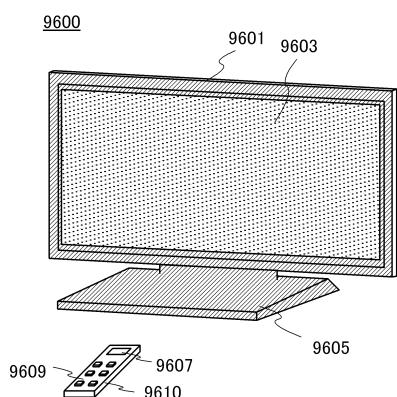

#### 【0069】

図6に示す半導体装置は、図6(A)に示すように電極101と、配線102と、機能回路103と、酸化物半導体層1041と、酸化物半導体層1042と、を有し、さらに図6(B)に示すように、絶縁層106と、絶縁層107と、を有する。

50

**【 0 0 7 0 】**

また、図6( B )に示すように、配線102は基板100上に設けられ、絶縁層106は配線102を挟んで基板100上に設けられ、酸化物半導体層1041及び酸化物半導体層1042は絶縁層106を挟んで配線102上に設けられ、絶縁層107は、酸化物半導体層1041及び酸化物半導体層1042を挟んで絶縁層106上に設けられ、電極101は、絶縁層107上に設けられる。すなわち図6( A )に示すように、図6に示す半導体装置は、平面視において、酸化物半導体層1041及び酸化物半導体層1042と配線102が重なり、酸化物半導体層1041及び酸化物半導体層1042と電極101が重ならない構造である。なお、図6( B )に示す酸化物半導体層1041と酸化物半導体層1042の平面視における間隔は、適宜設定することができる。また、本実施の形態の半導体装置は、必ずしも配線と酸化物半導体層を重ねて設ける必要はないが、配線と酸化物半導体層とが重なる構造にすることにより、光の入射による酸化物半導体層の劣化を抑えることができるため、好ましい。

10

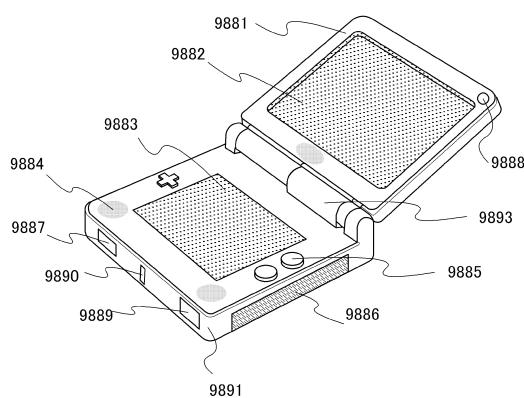

**【 0 0 7 1 】**

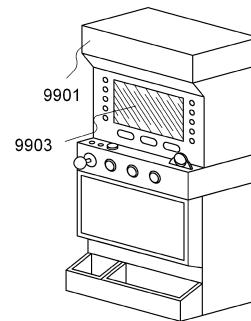

酸化物半導体層1041及び酸化物半導体層1042としては、例えば図1に示す酸化物半導体層104に適用可能な材料を用いることができる。

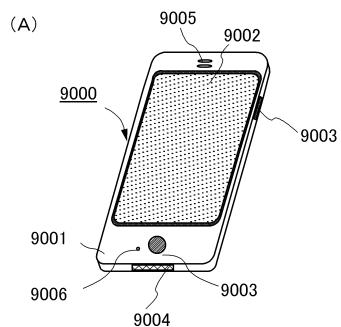

**【 0 0 7 2 】**

なお、その他の図6に示す半導体装置の各構造の説明は、図1に示す半導体装置の各構造の説明と同じであるため、図1に示す半導体装置の各構造の説明を適宜援用する。

20

**【 0 0 7 3 】**

図6に一例として示すように、本実施の形態の半導体装置は、酸化物半導体層を複数有し、複数の酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を複数有する構造とすることもできる。この容量素子はそれぞれ保護回路の一部としての機能を有する。また、この容量素子は、ノイズによる影響を低減するためのフィルタ回路の一部としての機能を有する。例えば一方の容量素子は正電圧の信号が入力、または正電圧が与えられる場合に機能するフィルタ回路の一部とし、他方の容量素子を負電圧の信号が入力または負電圧が与えられる場合に機能するフィルタ回路の一部とすることもできる。

**【 0 0 7 4 】**

さらに、本実施の形態における半導体装置の構造の他の一例について図7を用いて説明する。図7は、本実施の形態における半導体装置の構造の一例を模式的に示す図であり、図7( A )は上面図であり、図7( B )は図7( A )の線分A1-A2における断面図である。

30

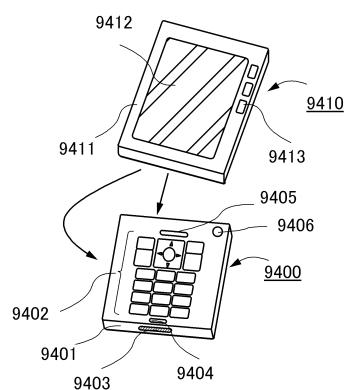

**【 0 0 7 5 】**

図7に示す半導体装置は、図7( A )に示すように電極101と、配線102と、機能回路103と、酸化物半導体層104と、を有し、さらに図7( B )に示すように、絶縁層106と、絶縁層107と、を有する。

**【 0 0 7 6 】**

また、図7( B )に示すように、酸化物半導体層104は基板100上に設けられ、絶縁層106は酸化物半導体層104を挟んで基板100上に設けられ、配線102は絶縁層106を挟んで酸化物半導体層104上に設けられ、絶縁層107は配線102上に設けられ、電極101は、配線102及び絶縁層107上に設けられる。すなわち図7( A )に示すように、平面視において、酸化物半導体層104と配線102が重なり、酸化物半導体層104と電極101が重なる構造である。なお、その他の図7に示す半導体装置の各構造の説明は、図1に示す半導体装置の各構造の説明と同じであるため、図1に示す半導体装置の各構造の説明を適宜援用する。

40

**【 0 0 7 7 】**

なお、図7に示す半導体装置は、平面視において、酸化物半導体層104と配線102が重なり、酸化物半導体層104と電極101が重なる構造であるが、本実施の形態の半導体装置は、これに限定されず、配線102と酸化物半導体層104が重なり、電極101

50

と酸化物半導体層 104 が重ならない構造、または電極 101 と酸化物半導体層 104 が重なり、配線 102 と酸化物半導体層 104 が重ならない構造とすることもできる。

#### 【0078】

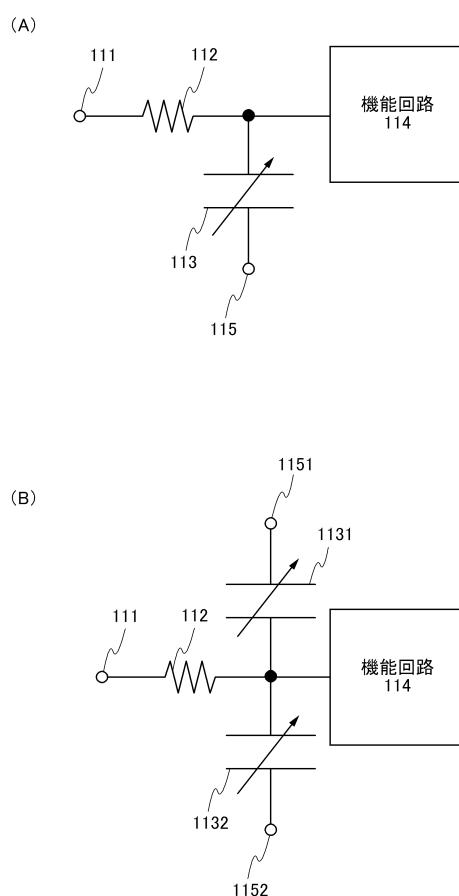

さらに図 1 乃至図 7 のそれぞれに示す半導体装置の等価回路について図 8 を用いて説明する。図 8 は、図 1 乃至図 7 のそれぞれに示す半導体装置の等価回路を示す回路図であり、図 8 (A) は、図 1、図 2、図 3、図 4、及び図 7 のそれぞれに示す半導体装置の等価回路を示し、図 8 (B) は、図 5 及び図 6 のそれぞれに示す半導体装置の等価回路を示す。

#### 【0079】

図 8 (A) に示す等価回路は、端子 111 と、抵抗素子 112 と、容量素子 113 と、機能回路 114 と、を有する。

10

#### 【0080】

端子 111 は電極 101 を一部に含み、端子 111 を介して信号が入力、または電圧が与えられる。

#### 【0081】

抵抗素子 112 は、例えば配線 102 の配線抵抗を利用して形成することができる。またこれに限定されず、本実施の形態の半導体装置では、例えば半導体材料などを用いて別途抵抗素子を形成することもできる。

#### 【0082】

容量素子 113 は、第 1 端子及び第 2 端子を有し、第 1 端子が抵抗素子 112 を介して端子 111 に電気的に接続され、且つ第 1 端子が機能回路 114 に電気的に接続され、第 2 端子には端子 115 を介して所定の電圧が与えられる。容量素子 113 の第 1 端子は、例えば、導電層及び半導体層の一方により構成される。また、容量素子 113 の第 2 端子は、導電層及び半導体層の他方により構成される。導電層としては、例えば電極 101、配線 102、また配線 108 などを用いることができ、半導体層としては、例えば酸化物半導体層 104 を用いることができる。また、容量素子 113 の第 2 端子に所定の電圧が与えられる。所定の電圧としては、例えば電源電圧が挙げられる。電源電圧の値は、入力される信号に応じて所望の機能が得られるように適宜設定することができる。ただし、これに限定されず、容量素子 113 の第 2 端子を浮遊状態とすることもできる。容量素子 113 は、可変容量としての機能を有する。

20

#### 【0083】

図 8 (A) に示すように、図 1、図 2、図 3、図 4、及び図 7 のそれぞれに示す半導体装置は、抵抗素子及び容量素子を用いたフィルタ回路を有する構成である。

30

#### 【0084】

次に本実施の形態の半導体装置の動作の一例として等価回路が図 8 (A) に示す構成である半導体装置の動作について説明する。ここでは、入力信号の電圧の絶対値が一定値以下の場合と、一定値より大きい場合に分けて説明する。なお、一定値は、例えば機能回路の仕様などを考慮して適宜設定することができる。

#### 【0085】

容量素子 113 は、入力信号の電圧に応じて容量値が変化する。入力信号の電圧の絶対値が一定値以下の場合、容量素子 113 の端子間に印加される電圧の絶対値は一定値より小さく、容量素子 113 の容量は一定値より小さいため、フィルタ回路の入力信号に対する出力信号の遅延時間は一定値より小さい。よってフィルタリング効果が小さくなる。なお、容量素子に印加される電圧、容量素子の容量、及び遅延時間は、半導体装置の仕様に応じて適宜設定することができる。

40

#### 【0086】

また、入力信号の電圧の絶対値が一定値より大きい場合、容量素子 113 の端子間に印加される電圧の絶対値は一定値より大きく、入力信号に応じて容量素子 113 の容量が一定値より大きくなるため、フィルタ回路の入力信号に対する出力信号の遅延が大きくなる。これにより入力信号の電圧の絶対値が一定値以下の場合よりノイズに対するフィルタリングの効果が大きくなる。以上が、等価回路が図 8 (A) に示す構成である半導体装置の動

50

作である。

**【0087】**

図8(B)に示す等価回路は、端子111と、抵抗素子112と、容量素子1131と、容量素子1132と、機能回路114と、を有する。

**【0088】**

端子111は電極101を一部に含み、端子111を介して信号が入力、または電圧が与えられる。

**【0089】**

抵抗素子112は、例えば配線102の配線抵抗を利用して形成することができる。またこれに限定されず、本実施の形態の半導体装置では、例えば半導体材料などを用いて別途抵抗素子を形成することもできる。10

**【0090】**

容量素子1131は、第1端子及び第2端子を有し、第1端子が抵抗素子112を介して端子111に電気的に接続され、且つ第1端子が機能回路114に電気的に接続され、第2端子には端子1151を介して高電源電圧が与えられる。容量素子1131の第1端子は、例えば導電層により構成される。また、容量素子1131の第2端子は、例えば半導体層により構成される。導電層としては、例えば電極101、配線102、また配線108などを用いることができ、半導体層としては、例えば酸化物半導体層1041を用いることができる。容量素子1131は、可変容量としての機能を有する。

**【0091】**

容量素子1132は、第1端子及び第2端子を有し、第1端子が抵抗素子112を介して端子111に電気的に接続され、且つ第1端子が機能回路114に電気的に接続され、第2端子には端子1152を介して低電源電圧が与えられる。容量素子1132の第1端子は、例えば半導体層により構成される。また、容量素子1132の第2端子は、例えば導電層により構成される。導電層としては、例えば電極101、配線102、また配線108などを用いることができ、半導体層としては、例えば酸化物半導体層1042を用いることができる。容量素子1132は、可変容量としての機能を有する。20

**【0092】**

図8(B)に示すように、図5及び図6に示す半導体装置は、抵抗素子及び2つの容量素子を用いたフィルタ回路を有する構成である。30

**【0093】**

次に本実施の形態の半導体装置の動作の一例として等価回路が図8(B)に示す構成である半導体装置の動作について説明する。ここでは、一例として端子111を介して信号が入力される場合について説明し、また入力信号の電圧の絶対値が一定値以下の場合と、一定値より大きい場合に分けて説明する。なお、一定値は、例えば機能回路の仕様などを考慮して適宜設定することができる。

**【0094】**

容量素子1131及び容量素子1132は、入力信号の電圧に応じて容量値が変化する。入力信号の電圧の絶対値が一定値以下の場合、容量素子1131及び容量素子1132の端子間に印加される電圧は一定値より小さく、容量素子1131及び容量素子1132の容量は一定値より小さいため、フィルタ回路の入力信号に対する出力信号の遅延時間は一定値より小さい。よってフィルタリング効果が小さくなる。なお、容量素子に印加される電圧、容量素子の容量、及び遅延時間は、半導体装置の仕様に応じて適宜設定することができる。40

**【0095】**

また、入力信号の電圧が一定の正の値より大きい場合、容量素子1131の端子間に印加される電圧は一定の正の値より大きく、入力信号に応じて容量素子1131の容量が一定値より大きくなるため、フィルタ回路の入力信号に対する出力信号の遅延が大きくなる。これにより入力信号の電圧が一定の正の値以下または一定の負の値以上の場合よりノイズに対するフィルタリングの効果が大きくなる。50

## 【0096】

また、入力信号の電圧が一定の負の値より小さい場合、容量素子1132の端子間に印加される電圧は一定の負の値より小さく、入力信号に応じて容量素子1132の容量が一定値より大きくなるため、フィルタ回路の入力信号に対する出力信号の遅延が大きくなる。これにより入力信号の電圧が一定の正の値以下または一定の負の値以上の場合よりノイズに対するフィルタリングの効果が大きくなる。以上が、等価回路が図8(B)に示す構成である半導体装置の動作である。

## 【0097】

以上のように、電圧の絶対値が一定値以下の信号が入力された場合に容量素子の容量を小さくし、機能回路に入力される信号の遅延を小さくし、電圧の絶対値が一定値より大きい信号が入力された場合に容量素子の容量を大きくし、機能回路に入力される信号の遅延を大きくすることにより、実動作の阻害を低減し、例えばノイズが生じた場合には、入力信号のノイズによる影響を低減することができる。なお、信号に限定されず、端子電極を介して電圧が与えられる場合であっても電圧のノイズによる影響を低減することができる。

10

## 【0098】

また、酸化物半導体を用いた半導体素子を有する機能回路は、例えば多結晶半導体を用いた半導体素子を有する機能回路と比較して比較的高い動作電圧を必要とすることが多いため、入力信号の電圧の絶対値が高い傾向にある。しかしながら本実施の形態の半導体装置のように、容量素子を用いたフィルタ回路を機能回路と端子電極との電気的接続間に設けることにより、酸化物半導体を用いた半導体素子を有する機能回路であってもノイズによる影響を低減することができる。

20

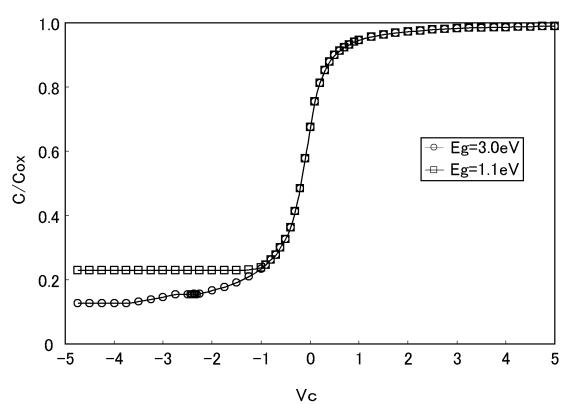

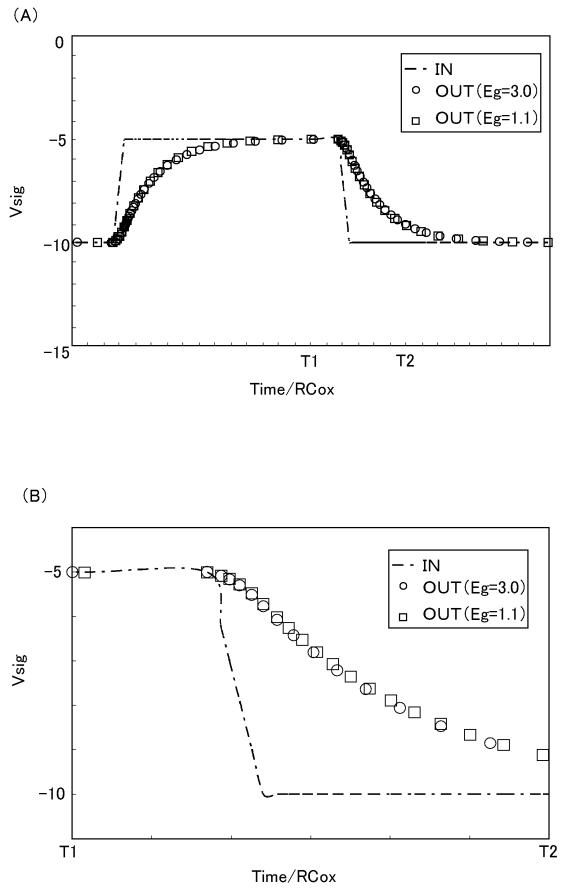

## 【0099】

さらに、半導体層を用いた容量素子の電圧 - 容量特性について計算により検証を行った。なお計算には、シミュレータとしてSilvaco社製CADソフトウェアATLASを用いた。また、計算では、容量素子を一例として半導体層を用いたMIS容量とした。また計算に使用した主なパラメータについて表1に示す。

## 【0100】

## 【表1】

|             |                                        |

|-------------|----------------------------------------|

| 絶縁層の比誘電率    | 4                                      |

| 半導体層の比誘電率   | 10                                     |

| 絶縁層の膜厚      | 0.1 [ $\mu\text{m}$ ]                  |

| 半導体層の膜厚     | 2.0 [ $\mu\text{m}$ ]                  |

| 半導体層の電子親和力  | 4.2 [eV]                               |

| バンドギャップ     | 1.1 [eV]、3.0 [eV]                      |

| 伝導帯の実効状態密度  | $2.8 \times 10^{19} [\text{cm}^3]$     |

| 価電子帯の実効状態密度 | $1.04 \times 10^{19} [\text{cm}^{-3}]$ |

30

## 【0101】

表1に示すように、バンドギャップ( $E_g$ ともいう)は3.0 eV、1.1 eVの2とおりとした。 $E_g = 3.0$  eVは半導体層に酸化物半導体の一つとして非晶質酸化物半導体を用いた場合のバンドギャップの一例であり、 $E_g = 1.1$  eVは、比較例として半導体層にシリコン半導体を用いた場合のバンドギャップの一例である。また、測定周波数は $1 \times 10^6$  kHzとした。また、半導体層はn型とした。

40

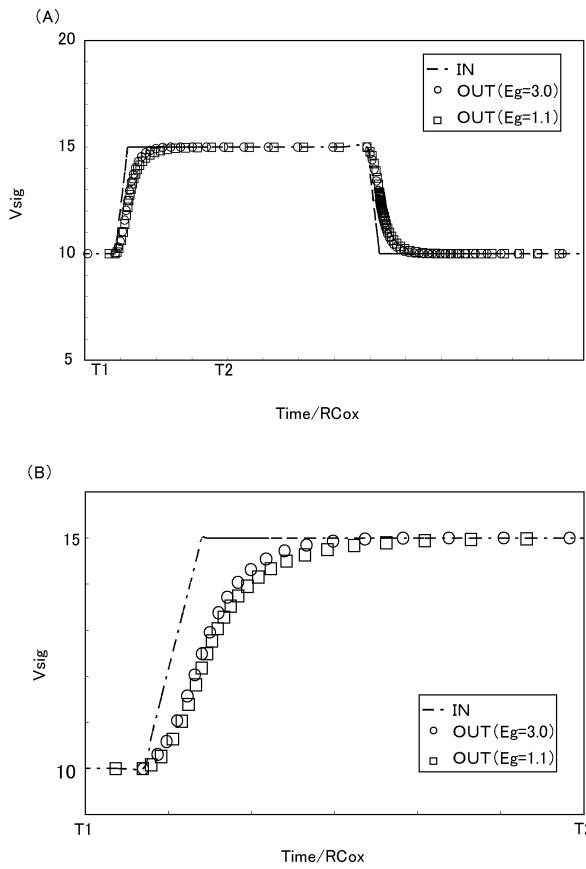

## 【0102】

容量素子の電圧 - 容量特性の検証結果について図9を用いて説明する。図9は、本実施の形態における容量素子の電圧 - 容量特性の計算結果を示す図であり、横軸が容量素子に印加される電圧( $V_c$ ともいう)であり、縦軸が全体の容量Cを絶縁層の容量 $C_x$ で割ったものである。

## 【0103】

図9に示すように、電圧 - 容量特性は、上記パラメータなどにより設計されたデバイスで想定される特性を示した。例えば-1 V以下の負電圧側において、 $E_g = 3.0$  eVのと

50

きの  $C/C_{\infty}$  は約 0.13 に収束し、 $E_g = 1.1 \text{ eV}$  のときの  $C/C_{\infty}$  は約 0.24 に収束し、 $E_g = 3.0 \text{ eV}$  のときの容量が  $E_g = 1.1 \text{ eV}$  のときの容量より小さくなる。また、正電圧側では、 $E = 3.0 \text{ eV}$  及び  $E_g = 1.1 \text{ eV}$  のときのいずれも電圧が高くなるにつれて容量が大きくなり、 $C/C_{\infty} = 1$  に収束する。このことから、半導体層を用いた容量素子は、いずれも蓄積状態のときに容量が大きくなり、反転状態のときに容量が小さくなる特性を有し、さらに反転状態のときに  $E_g = 3.0 \text{ eV}$  の半導体を用いた場合の容量は、 $E_g = 1.1 \text{ eV}$  の半導体を用いた場合の容量より小さくなることがわかる。反転状態のときの容量素子の容量は、絶縁層の容量と半導体層の空乏層容量とが直列接続されたものと等しくなる。

## 【0104】

10

このことから、半導体層を用いた容量素子をフィルタ回路に用いる場合、電圧の絶対値が一定値以下である通常の信号が入力される場合には、容量素子を反転状態にすることが好ましく、電圧の絶対値が一定値より大きい信号が入力される場合には、容量素子を蓄積状態にすることが好ましいことがわかる。ただし必ずしもこれに限定されるものではない。

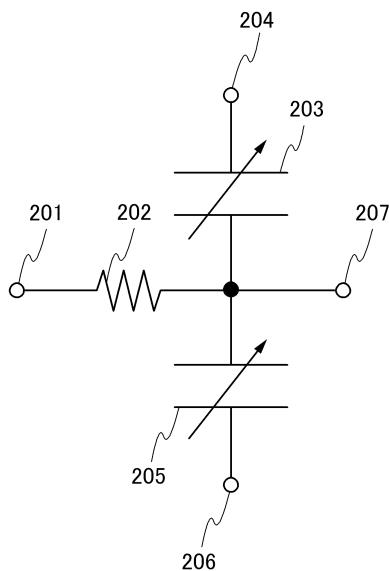

## 【0105】

さらに、半導体層を有する容量素子を用いたフィルタ回路について、計算による機能検証を行った。まず本計算に用いたフィルタ回路の回路モデルについて図 10 を用いて説明する。図 10 は、本実施の形態における機能検証を行うフィルタ回路の回路モデルを示す回路図である。

## 【0106】

20

図 10 に示す回路モデルは端子 201 と、抵抗素子 202 と、容量素子 203 と、端子 204 と、容量素子 205 と、端子 206 と、端子 207 と、を有する。

## 【0107】

図 10 に示す回路モデルでは、端子 201 を介して入力信号 (IN ともいう) が入力される。入力信号は、抵抗素子 202、容量素子 203、及び容量素子 205 により構成されるフィルタ回路に入力され、フィルタ回路の出力信号 (OUT ともいう) が端子 207 を介して出力される。

## 【0108】

さらに図 10 に示す回路モデルでは、端子 204 を介して高電源電圧が与えられ、端子 206 を介して低電源電圧が与えられるものとする。

30

## 【0109】

上記図 10 に示す回路モデルを用いて検証を行った。なお本計算には、Silvaco 社製 TCA CAD ソフトウェア ATLAS を用いた。また、本計算では、容量素子を一例として半導体層を用いた MIS 容量とした。また、本計算では、表 1 に示すパラメータを適宜使用した。

## 【0110】

さらに本計算は、入力信号として、ハイ状態 (H ともいう) の電圧が 5V、ロウ状態 (L ともいう) の電圧が 0V である ( $H = 5 \text{ V}$ 、 $L = 0 \text{ V}$ ) 第 1 のデジタル信号 (DS1 ともいう)、 $H = 15 \text{ V}$ 、 $L = 10 \text{ V}$  の第 2 のデジタル信号 (DS2 ともいう)、または  $H = -5 \text{ V}$ 、 $L = -10 \text{ V}$  の第 3 のデジタル信号 (DS3 ともいう) が入力される場合についてそれぞれ行った。また、本計算では、第 1 のデジタル信号が入力される場合には容量素子 203 及び容量素子 205 が反転状態になり、第 2 のデジタル信号が入力される場合には容量素子 203 が蓄積状態になり、第 3 のデジタル信号が入力される場合には容量素子 205 が蓄積状態になるように  $V_{dd} = 8 \text{ V}$  とし、 $V_{ss} = -3 \text{ V}$  とした。また、本計算では、反転状態時において、 $E_g = 3.0 \text{ eV}$  のときの  $C/C_{\infty}$  を 0.13 とし、 $E_g = 1.1 \text{ eV}$  のときの  $C/C_{\infty}$  を 0.24 となるように半導体層の厚さ及び半導体層のキャリア密度などを設定した。また半導体層は n 型とした。

40

## 【0111】

計算結果について図 11 乃至図 13 を用いて説明する。図 11 乃至図 13 は、図 10 に示す回路モデルの計算による検証における入出力特性を示す図である。

50

**【 0 1 1 2 】**

図 11 ( A ) は第 1 のデジタル信号が入力される場合の入出力特性を示す図であり、横軸が時間を抵抗素子 202 の抵抗 ( $R$  ともいう)  $\times$  絶縁層の容量  $C_{\text{ext}}$  で割ったものであり、縦軸が信号電圧 ( $V_{\text{sig}}$  ともいう) である。また、図 11 ( B ) は図 11 ( A ) の T1 - T2 間の拡大図である。なお、本計算では、 $RC_{\text{ext}} = 2.83 \mu\text{s}$  となるように抵抗素子 202 の抵抗と絶縁層の容量面積を設定した。

**【 0 1 1 3 】**

図 12 ( A ) は第 2 のデジタル信号が入力される場合の入出力特性を示す図であり、横軸が時間を抵抗素子 202 の抵抗  $\times$  絶縁層の容量  $C_{\text{ext}}$  で割ったものであり、縦軸が電圧である。また、図 12 ( B ) は図 12 ( A ) の T1 - T2 間の拡大図である。

10

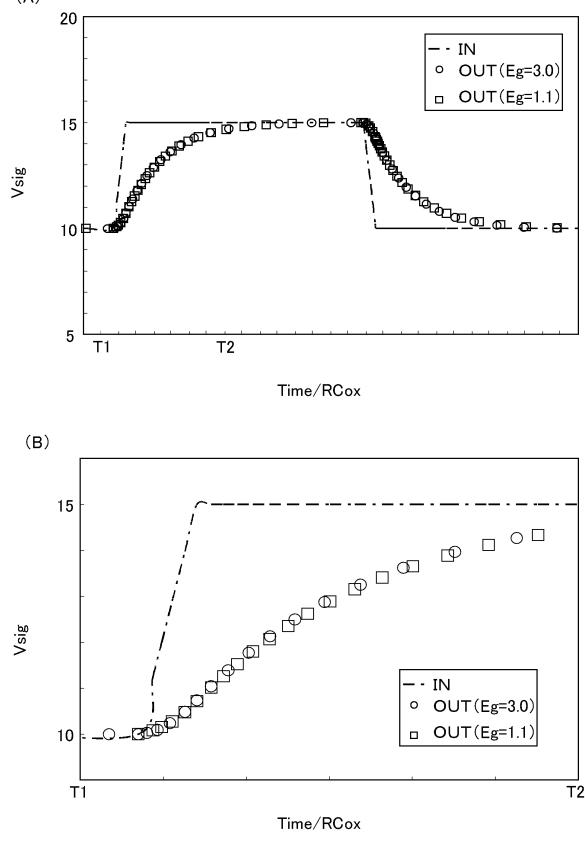

**【 0 1 1 4 】**

図 13 ( A ) は第 3 のデジタル信号が入力される場合の入出力特性を示す図であり、横軸が時間を抵抗素子 202 の抵抗  $\times$  絶縁層の容量  $C_{\text{ext}}$  で割ったものであり、縦軸が電圧である。また、図 13 ( B ) は図 13 ( A ) の T1 - T2 間の拡大図である。

**【 0 1 1 5 】**

なお、図 11 ( A )、図 12 ( A )、及び図 13 ( A ) において、横軸の各目盛間の値は同じである。また、図 11 ( B )、図 12 ( B )、及び図 13 ( B ) において、横軸の各目盛間の値は同じである。

**【 0 1 1 6 】**

第 1 のデジタル信号が入力される場合、図 11 に示すように、 $E_g = 3.0 \text{ eV}$  の場合の出力信号 (OUT ともいう) の立ち上がり時間または立ち下がり時間の遅延が  $E_g = 1.1 \text{ eV}$  の場合の出力信号の立ち上がり時間または立ち下がり時間の遅延より小さくなる。これは、上記図 9 に示すように、反転状態において、 $E_g = 3.0 \text{ eV}$  のときの容量が  $E_g = 1.1 \text{ eV}$  のときの容量より小さくなるためである。

20

**【 0 1 1 7 】**

また、第 2 のデジタル信号が入力される場合、図 12 に示すように、 $E_g = 3.0 \text{ eV}$  の場合の出力信号及び  $E_g = 1.1 \text{ eV}$  の場合の出力信号の立ち上がり時間の遅延が第 1 のデジタル信号が入力される場合に比べて大きくなる。これは、上記図 9 に示すように、蓄積状態において、 $E_g = 3.0 \text{ eV}$  のときの容量及び  $E_g = 1.1 \text{ eV}$  のときの容量とも電圧が高くなるにつれて一定値まで大きくなるためである。

30

**【 0 1 1 8 】**

また、第 3 のデジタル信号が入力される場合、図 13 に示すように、 $E_g = 3.0 \text{ eV}$  のときの出力信号及び  $E_g = 1.1 \text{ eV}$  のときの出力信号の立ち下がり時間の遅延が第 1 のデジタル信号が入力される場合に比べて大きくなる。これは、上記図 9 に示すように、蓄積状態において、 $E_g = 3.0 \text{ eV}$  のときの容量及び  $E_g = 1.1 \text{ eV}$  のときの容量のいずれの容量とも電圧が高くなるにつれて一定値まで大きくなるためである。

**【 0 1 1 9 】**

さらに第 1 のデジタル信号乃至第 3 のデジタル信号のそれぞれが入力される場合の出力信号の遅延時間について表 2 にまとめた。なお、表 2 において、 $t_f$  は立ち下がり時間を示し、 $t_r$  は立ち上がり時間を示し、さらに  $(t_f + t_r) / 2$  より平均遅延時間についても示した。なお、遅延時間は、ここでは、出力信号が入力信号の振幅の 10 % から 90 % まで変化するのに要する時間と定義した。さらに表 2 に示す値は各遅延時間を  $RC_{\text{ext}}$  で割ったものである。

40

**【 0 1 2 0 】**

【表2】

|     |             | tf    | tr    | (tf+tr)/2 |

|-----|-------------|-------|-------|-----------|

| DS1 | OUT(Eg=3.0) | 0.598 | 0.600 | 0.599     |

|     | OUT(Eg=1.1) | 0.676 | 0.712 | 0.694     |

| DS2 | OUT(Eg=3.0) | 2.396 | 2.403 | 2.399     |

|     | OUT(Eg=1.1) | 2.465 | 2.439 | 2.452     |

| DS3 | OUT(Eg=3.0) | 2.406 | 2.396 | 2.401     |

|     | OUT(Eg=1.1) | 2.438 | 2.472 | 2.455     |

## 【0121】

10

表2に示すように、平均遅延時間は、第2のデジタル信号(DS2)及び第3のデジタル信号(DS3)が入力される場合より第1のデジタル信号(DS1)が入力される場合の方が小さくなる。また、第1のデジタル信号が入力される場合、 $E_g = 3.0 \text{ eV}$ のときの平均遅延時間は、 $E_g = 1.1 \text{ eV}$ のときの出力信号の平均遅延時間より小さくなる。

## 【0122】

上記検証結果により酸化物半導体層を有する容量素子を用いたフィルタ回路は、絶対値が一定の範囲内である電圧の信号が入力された場合には、出力信号の遅延を少なくすることができます、また絶対値が一定の範囲外である電圧の信号が入力された場合には、出力信号を遅延させることができることがわかる。これにより実動作の阻害を低減し、例えばノイズなどにより一定値より高い絶対値の電圧である信号が入力される場合にノイズによる影響を低減することができる。

20

## 【0123】

なお、例えば酸化物半導体層に熱処理を施した場合であっても上記特性と同様の検証結果を得ることは当然可能である。

## 【0124】

また、遅延時間は、上記に示すように抵抗及び容量の値によって決まるため、例えば機能回路の仕様に応じて入力信号、高電源電圧、低電源電圧の値を適宜設定することにより、本計算で用いられたフィルタ回路と同等のフィルタ特性を得ることも当然可能である。

## 【0125】

## (実施の形態2)

30

本実施の形態では、本発明の一態様である表示装置について説明する。

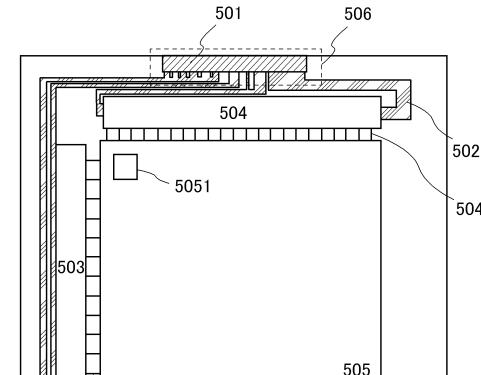

## 【0126】

本実施の形態の表示装置の構成について図14を用いて説明する。図14は本実施の形態の表示装置の構成の一例を示す図である。

## 【0127】

図14に示す表示装置は、端子電極501と、配線502と、走査線駆動回路503と、走査線5031と、信号線駆動回路504と、信号線5041と、画素部505と、を有する。

## 【0128】

端子電極501は、端子部506に設けられ、例えば走査信号及び映像信号などが入力される信号入力端子の一部、及び電源電圧が印加される電源端子の一部としての機能を有する。

40

## 【0129】

走査線駆動回路503は、配線502を介して端子電極501に電気的に接続される。走査線駆動回路503は、端子部506から例えば制御信号などの信号が入力、または電源電圧が与えられ、入力された信号に応じたタイミングで走査線5031を介して走査信号を出力する。

## 【0130】

信号線駆動回路504は、配線502を介して端子電極501に電気的に接続される。信号線駆動回路504は、端子部506から例えば制御信号及び映像信号などの信号が入力

50

、または電源電圧が与えられ、入力された信号に応じたタイミングで信号線 5041 を介して映像信号を出力する。

**【0131】**

画素部 505 は、複数の画素 5051 を有し、それぞれの画素 5051 は、走査線 5031 のいずれか及び信号線 5041 のいずれかに電気的に接続され、走査信号及び映像信号が入力される。

**【0132】**

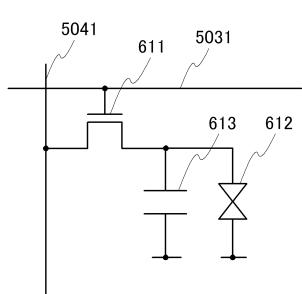

次に画素 5051 の回路構成の一例について図 15 を用いて説明する。図 15 は画素 5051 の回路構成の一例を示す図である。

**【0133】**

図 15 (A) に示す画素は、トランジスタ 611 と、液晶素子 612 と、容量素子 613 と、を有する。

10

**【0134】**

トランジスタ 611 は、ゲート端子、ソース端子、及びドレイン端子の少なくとも 3 つの端子を有する。

**【0135】**

なお、本明細書において、ゲート端子とは、ゲート電極及びゲート電極に電気的に接続される配線（ゲート配線ともいう）となる導電層の一部または全部のことをいう。また、ソース端子とは、ソース電極及びソース電極に電気的に接続される配線（ソース配線ともいう）となる層（導電層などを含む）の一部または全部のことをいう。また、ドレイン端子とは、ドレイン電極及びドレイン電極に電気的に接続される配線（ドレイン配線ともいう）となる層（導電層などを含む）の一部または全部のことをいう。

20

**【0136】**

また、本明細書において、トランジスタのソース端子とドレイン端子は、トランジスタの構造や動作条件などによって互いに入れ替わる可能性があり、ゲート端子以外のトランジスタの端子のいずれがソース端子またはドレイン端子であるかを限定することが困難である。そこで、本明細書においては、複数の端子のうち、ソース端子及びドレイン端子のいずれか一方となる端子をソース端子及びドレイン端子の一方と表し、ソース端子及びドレイン端子の他方となる端子をソース端子及びドレイン端子の他方と表す。

**【0137】**

30

トランジスタ 611 は、選択スイッチとしての機能を有する。また、トランジスタ 611 は、ゲート端子が図 15 に示す走査線 5031 に電気的に接続され、ソース端子及びドレイン端子の一方が信号線 5041 に電気的に接続される。

**【0138】**

液晶素子 612 は、第 1 端子及び第 2 端子を有し、第 1 端子がトランジスタ 611 のソース端子及びドレイン端子の他方に電気的に接続され、第 2 端子に所定の値の電圧が与えられる。液晶素子 612 は、例えば第 1 端子の一部または全部となる第 1 の電極と、第 2 端子の一部または全部となる第 2 の電極と、第 1 の電極と第 2 の電極との間に電圧が印加されることにより透過率が変化する液晶分子を有する層（液晶層という）と、により構成することができる。

40

**【0139】**

液晶層の一例、液晶層に適用可能な液晶材料の一例、または液晶層を含む液晶素子 612 に適用可能な液晶モードの一例としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶（PDL C）、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶（PALC）、バナナ型液晶、TN（Twisted Nematic）モード、STN（Super Twisted Nematic）モード、IPS（In-Plane-Switching）モード、FFS（Fringe Field Switching）モード、MVA（Multi-domain Vertical Alignment）モード、PVA（Patterned

50

Vertical Alignment)、ASV(Advanced Super View)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optical Compensated Birefringence)モード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、ゲストホストモード、ブルー相(Blue Phase)モードなどがある。

## 【0140】

10

容量素子613は、第1端子及び第2端子を有し、第1端子がトランジスタ611のソース端子及びドレイン端子の他方に電気的に接続され、第2端子に所定の電圧が与えられる。容量素子613は、第1端子の一部または全部となる第1の電極と、第2端子の一部または全部となる第2の電極と、絶縁層と、を有する構成である。容量素子613は保持容量としての機能を有する。なお、容量素子613は必ずしも設ける必要はないが、容量素子613を設けることにより、トランジスタ611のリーク電流による影響を抑制することができる。

## 【0141】

次に図15(A)に示す画素の動作について説明する。

## 【0142】

20

まず図14に示す走査線駆動回路503により走査線5031が選択されると、走査線駆動回路503から入力される走査信号によりトランジスタ611がオン状態になる。

## 【0143】

このとき液晶素子612の第1端子及び容量素子613の第1端子の電位が信号線駆動回路504により入力される映像信号に応じた電位となり、液晶素子612は、第1端子と第2端子の間に印加される電圧に応じて配向が制御され、画素は、液晶素子612の透過率に応じて表示を行う。上記動作を走査線5031毎に順次行うことにより、すべての画素においてデータが書き込まれる。以上が図15(A)に示す画素の動作である。

## 【0144】

30

なお、本実施の形態の表示装置における画素の回路構成は、図15(A)に示す画素の回路構成に限定されず、例えば図15(A)に示す画素の回路構成に別のスイッチング素子(トランジスタを含む)、抵抗素子、または容量素子などを設ける構成とすることもできる。

## 【0145】

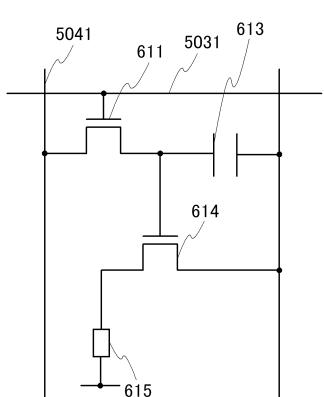

また、本実施の形態の表示装置における画素の回路構成は、図15(A)に示す画素の回路構成に限定されず、他の回路構成とすることもできる。本実施の形態の表示装置における画素の回路構成の他の一例について図15(B)を用いて説明する。図15(B)は、本実施の形態の表示装置における画素の回路構成の一例を示す回路図である。

## 【0146】

図15(B)に示す画素は、トランジスタ611と、容量素子613と、トランジスタ614と、発光素子615と、を有する。

40

## 【0147】

トランジスタ611は、ゲート端子が走査線5031に電気的に接続され、ソース端子及びドレイン端子の一方が信号線5041に電気的に接続される。

## 【0148】

容量素子613は、第1端子及び第2端子を有し、第1端子がトランジスタ611のソース端子及びドレイン端子の他方に電気的に接続され、第2端子に第1の電圧が与えられる。容量素子613は保持容量としての機能を有する。なお容量素子613は必ずしも設ける必要はないが、容量素子613を設けることにより、一定期間トランジスタ614のオン状態を維持することができる。

50

**【 0 1 4 9 】**

トランジスタ 614 は、ゲート端子がトランジスタ 611 のソース端子及びドレイン端子の他方に電気的に接続され、ソース端子及びドレイン端子の一方第 1 の電圧が与えられる。

**【 0 1 5 0 】**

発光素子 615 は、第 1 端子及び第 2 端子を有し、第 1 端子がトランジスタ 614 のソース端子及びドレイン端子の他方に電気的に接続され、第 2 端子に第 2 の電圧が与えられる。発光素子 615 は、例えば第 1 端子の一部または全部となる第 1 の電極と、第 2 端子の一部または全部となる第 2 の電極と、第 1 の電極と第 2 の電極の間に電圧が印加されることにより発光する電界発光層より構成することができる。発光素子 615 としては、例えば E L (エレクトロルミネセンスともいう) 素子を用いることができ、E L 素子としては、例えば有機 E L 素子または無機 E L 素子を用いることができる。10

**【 0 1 5 1 】**

なお第 1 の電圧は、高電源電圧及び低電源電圧のいずれか一方であり、第 2 の電圧は高電源電圧及び低電源電圧の他方である。いずれが高電源電圧か低電源電圧かであるかは例えばトランジスタ 614 の極性によって設定され、例えばトランジスタ 614 が P 型トランジスタであれば、第 1 の電圧は高電源電圧に設定され、第 2 の電圧は低電源電圧に設定されることが多い、N 型トランジスタであれば第 1 の電圧は低電源電圧に設定され、第 2 の電圧は高電源電圧に設定されることが多い。

**【 0 1 5 2 】**

発光素子 615 における第 1 の電極または第 2 の電極は、少なくとも一方が透光性を有する導電材料を用いて形成されたものであればよい。これにより、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子とすることができます。透光性を有する導電材料としては、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITO と示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることもできる。

**【 0 1 5 3 】**

電界発光層は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、第 1 の電極上に電子注入層、電子輸送層、電界発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。電界発光層としては有機化合物または無機化合物を用いて形成することができる。

**【 0 1 5 4 】**

次に図 15 (B) に示す画素の動作について説明する。

**【 0 1 5 5 】**

まず図 14 に示す走査線駆動回路 503 により走査線 5031 が選択されると、走査線駆動回路 503 から入力される走査信号によりトランジスタ 611 がオン状態になる。40

**【 0 1 5 6 】**

このときトランジスタ 614 のゲート端子及び容量素子 613 の第 1 端子の電位が信号線駆動回路 504 により入力される映像信号に応じた電位となり、トランジスタ 614 はオン状態になり、トランジスタ 614 のソース端子及びドレイン端子の間に電流が流れる。さらにトランジスタ 614 に流れる電流に応じて所定の電圧が発光素子 615 の第 1 端子及び第 2 端子の間に印加され、画素は表示を行う。上記動作を走査線 5031 毎に順次行うことにより、すべての画素においてデータが書き込まれる。以上が図 15 (B) に示す画素の動作である。

**【 0 1 5 7 】**

また信号線 5032 から画素に入力されるデータ信号がデジタル形式の場合、画素はトラ50

ンジスタのオン状態とオフ状態の切り替えによって、発光もしくは非発光の状態となる。よって、面積階調法または時間階調法を用いて階調の表示を行うことができる。面積階調法は、1画素を複数の副画素に分割し、各副画素を図15(B)に示す回路構成にして独立にデータ信号に基づいて駆動させることによって、階調表示を行う駆動法である。また時間階調法は、画素が発光する期間を制御することによって、階調表示を行う駆動法である。

#### 【0158】

発光素子615は、例えば図15(A)に示す液晶素子612などに比べて応答速度が高いので、時間階調法に適している。具体的に時間階調法で表示を行なう場合、1フレーム期間を複数のサブフレーム期間に分割する。そしてビデオ信号に従い、各サブフレーム期間において画素の発光素子を発光または非発光の状態にする。複数のサブフレーム期間に分割することによって、1フレーム期間中に画素が実際に発光する期間のトータルの長さを、ビデオ信号により制御することができ、階調を表示することができる。10

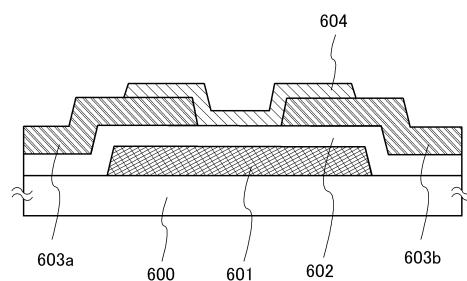

#### 【0159】

次に図14に示す表示装置の走査線駆動回路503若しくは信号線駆動回路504などの駆動回路、または画素5051におけるトランジスタの構造の一例について図16を用いて説明する。図16は図14に示す表示装置の画素におけるトランジスタの構造の一例を示す断面図である。

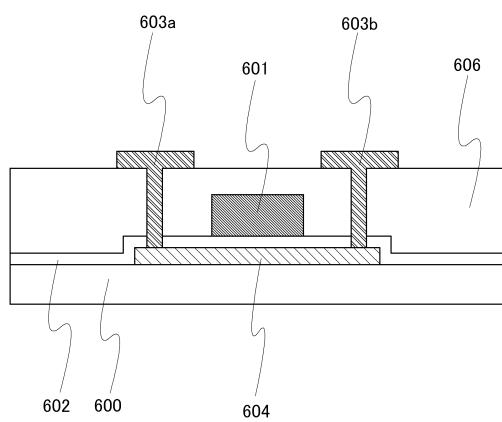

#### 【0160】

図16(A)に示すトランジスタは、導電層601と、絶縁層602と、導電層603a及び導電層603bと、半導体層604と、を有する。20

#### 【0161】

導電層601は、被形成面(図16(A)では基板600)上に設けられる。導電層601はゲート電極としての機能を有する。さらに平面視において、導電層601を半導体層604と重ねて配置することにより、半導体層604に入射する光を低減する遮光層としての機能を導電層601に持たせることもできる。導電層601が遮光層としての機能を有することにより、半導体層604の光による劣化を抑制することができる。よって半導体層604に酸化物半導体材料を用いた場合でも所望の機能を有することができる。

#### 【0162】

絶縁層602は、導電層601上に設けられる。絶縁層602はゲート絶縁層としての機能を有する。30

#### 【0163】

導電層603a及び導電層603bは、絶縁層602の一部の上に設けられる。導電層603aはソース電極及びドレイン電極の一方としての機能を有し、導電層603bはソース電極及びドレイン電極の他方としての機能を有する。例えば導電層603aがソース電極としての機能を有する場合には導電層603bはドレイン電極としての機能を有する。

#### 【0164】

なお、図16(A)に示すトランジスタにおいて、導電層603a及び導電層603bが絶縁層602を挟んで導電層601上に設けられているが、これに限定されず、本実施の形態の半導体装置は、例えば導電層601上以外の部分の絶縁層602上に導電層603a及び導電層603bを有する構成とすることもできる。40

#### 【0165】

半導体層604は、導電層603a及び導電層603bを挟んで絶縁層602の上に設けられる。半導体層604は、チャネルが形成される層(チャネル形成層ともいう)である。

#### 【0166】

また、図16(A)に示す構造に限定されず、本実施の形態のトランジスタは、図16(B)に示す構造とすることもできる。

#### 【0167】

図16(B)に示すトランジスタは、導電層601と、絶縁層602と、導電層603a50

及び導電層 603b と、半導体層 604 と、バッファ層 605a 及びバッファ層 605b と、を有する。

【0168】

図 16 (B) に示すトランジスタは、図 16 (A) に示すトランジスタの構造にバッファ層を追加した構造である。よって図 16 (A) に示すトランジスタと同じ部分については、図 16 (A) に示すトランジスタの説明を適宜援用し、図 16 (A) に示すトランジスタと異なる部分について以下に説明する。

【0169】

バッファ層 605a は導電層 603a 上に設けられ、バッファ層 605b は導電層 603b 上に設けられる。バッファ層 605a 及びバッファ層 605b は、導電層 603a または導電層 603b と半導体層 604 との電気的な接続を良好にする層としての機能を有する。なおバッファ層 605a 及びバッファ層 605b は、必ずしも導電層 603a または導電層 603b 上に設ける必要はなく、導電層 603a 及び導電層 603b と電気的に接続されればよい。

10

【0170】

バッファ層 605a 及びバッファ層 605b は、例えば半導体層 604 と同じ材料及び同じ作製方法を用いて形成することができる。また、バッファ層 605a 及びバッファ層 605b は、半導体層 604 と同じ導電率または半導体層 604 より高い導電率であることが好ましい。バッファ層 605a 及びバッファ層 605b は、例えば半導体膜を形成し、フォトリソグラフィー工程により半導体膜上にレジストマスクを選択的に形成し、半導体膜をエッチングすることにより形成することができる。

20

【0171】

図 16 (B) に示すトランジスタは、ソース電極及びドレイン電極の上層にチャネル形成層となる半導体層を有する、いわゆるボトムコンタクト構造である。ボトムコンタクト構造とすることにより、ソース電極及びドレイン電極と半導体層の接触面積を増やすことができる。なお、ボトムコンタクト構造に限定されず、本実施の形態のトランジスタは、チャネル形成層となる半導体層上にソース電極及びドレイン電極を有する、いわゆるトップコンタクト構造とすることもできる。

【0172】

図 16 (A) 及び図 16 (B) に示すトランジスタは、ゲート電極上にソース電極及びドレイン電極、並びにチャネル形成層を有する、いわゆるボトムゲート構造である。ボトムゲート構造とすることにより、ゲート絶縁層及び半導体層の連続成膜が可能になる。

30

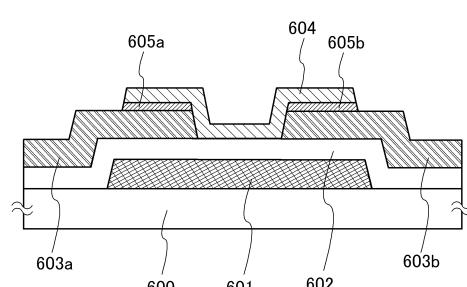

【0173】

なお、本実施の形態の半導体装置は、ボトムゲート構造に限定されず、トップゲート構造とすることもできる。トップゲート構造のトランジスタの構造について図 17 を用いて説明する。図 17 は、図 14 に示す表示装置の画素におけるトランジスタの構造の一例を示す断面図である。

【0174】

図 17 に示すトランジスタは、導電層 601 と、絶縁層 602 と、導電層 603a 及び導電層 603b と、半導体層 604 と、を有する。

40

【0175】

半導体層 604 は、被形成面（図 17 では基板 600）上に設けられる。半導体層 604 は、チャネルが形成される層（チャネル形成層ともいう）である。

【0176】

絶縁層 602 は、半導体層 604 を挟んで基板 600 上に設けられる。絶縁層 602 はゲート絶縁層としての機能を有する。

【0177】

導電層 601 は、絶縁層 602 を挟んで半導体層 604 上に設けられる。導電層 601 はゲート電極としての機能を有する。

【0178】

50

絶縁層 606 は、導電層 601 を挟んで絶縁層 602 上に設けられる。絶縁層 606 は、導電層 601 を保護する保護層としての機能を有する。

#### 【 0179 】

導電層 603a 及び導電層 603b は、絶縁層 606 の一部の上に設けられる。導電層 603a は、絶縁層 602 及び絶縁層 606 に設けられた開口部を介して半導体層 604 に電気的に接続され、導電層 603b は、絶縁層 602 及び絶縁層 606 に設けられた開口部を介して半導体層 604 に電気的に接続される。導電層 603a はソース電極及びドレイン電極のいずれか一方としての機能を有し、導電層 603b はソース電極及びドレイン電極の他方としての機能を有する。例えば導電層 603a がソース電極としての機能を有する場合には導電層 603b はドレイン電極としての機能を有する。

10

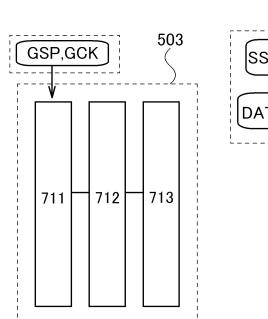

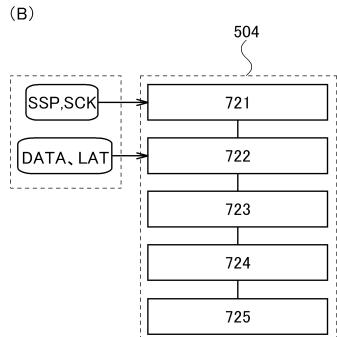

#### 【 0180 】

次に図 14 に示す表示装置における走査線駆動回路 503 及び信号線駆動回路 504 の構成の一例について図 18 を用いて説明する。図 18 は図 14 に示す表示装置における駆動回路の構成の一例を示す図であり、図 18 (A) は走査線駆動回路の構成の一例を示すブロック図であり、図 18 (B) は信号線駆動回路の構成の一例を示すブロック図である。

#### 【 0181 】

図 18 (A) に示す走査線駆動回路 503 は、シフトレジスタ 711、レベルシフタ 712、バッファ回路 713 と、を有する。

#### 【 0182 】

シフトレジスタ 711 にはゲートスタートパルス (GSP)、ゲートクロック信号 (GCK) などの信号が入力される。

20

#### 【 0183 】

レベルシフタ 712 は、入力された信号をもとに用途によって異なる複数の信号を生成する機能を有する。

#### 【 0184 】

バッファ回路 713 は、入力されたレベルシフタ 712 の出力信号を増幅する機能を有し、例えばオペアンプなどを有する構成とすることができます。

#### 【 0185 】

図 18 (B) に示す信号線駆動回路 504 は、シフトレジスタ 721、ラッチ回路 722、レベルシフタ 723、バッファ回路 724、DA 変換回路 725 と、を有する。

30

#### 【 0186 】

シフトレジスタ 721 は、ソーススタートパルス (SSP)、ソースクロック信号 (SCK) などの信号が入力される。

#### 【 0187 】

ラッチ回路 722 は、画像データ信号 (DATA) 及びラッチ信号 (LAT) が入力され、入力された画像データ信号を一定期間保持し、保持した信号を一斉に図 14 における画素部に出力する。これを線順次駆動と呼ぶ。

#### 【 0188 】

レベルシフタ 723 は、入力された信号をもとに用途によって異なる複数の信号を生成する機能を有する。

40

#### 【 0189 】

バッファ回路 724 は、入力された信号を増幅させる機能を有し、例えばオペアンプなどを有する構成とすることができます。

#### 【 0190 】

DA 変換回路 725 は、入力された信号がデジタル信号の場合にアナログ信号に変換する機能を有する。なお、入力される信号がアナログ信号の場合には必ずしも設ける必要はない。

#### 【 0191 】

上記駆動回路は、例えば酸化物半導体材料を用いた半導体素子を用いて構成することができる。半導体素子としては、例えばトランジスタ、容量素子、または抵抗素子などが挙げ

50

られる。例えばトランジスタを用いる場合には、画素と同じ構造のトランジスタを用いることもできる。

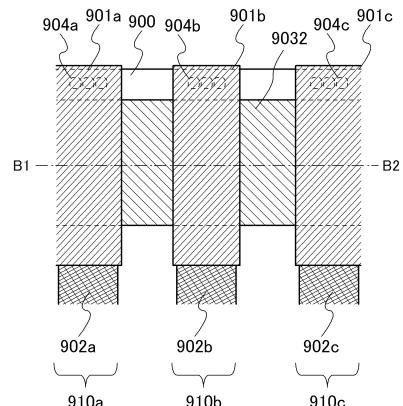

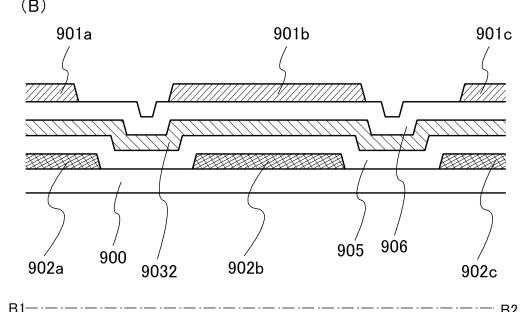

#### 【0192】

次に端子部506の構造の一例について図19を用いて説明する。図19は、図14に示す表示装置における端子部506の構造の一例を示す図であり、図19(A)は上面図であり、図19(B)は、図19(A)の線分B1-B2における断面図である。

#### 【0193】

図19(A)に示す端子部506は、端子910a、端子910b、及び端子910cを有する。さらに図19(B)に示すように半導体層9032と、絶縁層905と、絶縁層906と、を有する。

10

#### 【0194】

端子910aは導電層901aと、導電層902aと、を有し、端子910bは導電層901bと、導電層902bと、を有し、端子910cは、導電層901cと、導電層902cと、を有する。

#### 【0195】

また、図19(B)に示すように、絶縁層905は、導電層902a、導電層902b、及び導電層902c上に設けられ、半導体層9032は、絶縁層905を挟んで導電層902a、導電層902b、及び導電層902c上に設けられ、絶縁層906は半導体層9032上に設けられ、導電層901a、導電層901b、及び導電層901cは、絶縁層906を挟んで半導体層9032の上に設けられる。すなわち、平面視において、半導体層9032と導電層901a、導電層901b、及び導電層901cが重なり、且つ半導体層9032と導電層902a、導電層902b、及び導電層902cが重なる構造である。

20

#### 【0196】

導電層901a乃至導電層901cは、それぞれ例えば半導体装置の端子電極としての機能を有する。導電層901a乃至導電層901cとしては、例えば図16に示す導電層601の形成に用いられる導電膜に適用可能な材料を用いて形成することができる。よって例えば一つの導電膜を用いて導電層601、及び導電層901a乃至導電層901cを同一工程で形成することもできる。

#### 【0197】

30

導電層902aは、開口部904aを介して導電層901aに電気的に接続され、導電層902bは、開口部904bを介して導電層901bに電気的に接続され、導電層902cは、開口部904cを介して導電層901cに電気的に接続される。導電層902a乃至導電層902cは、それぞれ例えば表示装置の駆動回路や画素部に信号を供給するための配線（信号線、ソース線、またはゲート線ともいう）、または電源を供給するための配線（電源線ともいう）としての機能を有する。導電層902a乃至導電層902cとしては、例えば図16に示す導電層603a及び導電層603bの形成に用いられる導電膜に適用可能な材料を用いることができる。よって例えば一つの導電膜を用いて導電層603a及び導電層603b、並びに導電層902a乃至導電層902cを同一工程で形成することもできる。

40

#### 【0198】

半導体層9032としては、例えば図16に示す半導体層604の形成に用いられる半導体膜に適用可能な材料を用いることができる。よって例えば一つの半導体膜を用いて半導体層604及び半導体層9032を同一工程で形成することもできる。

#### 【0199】

絶縁層905及び絶縁層906としては、例えばシリコンなどを含む絶縁層などを用いることができる。よって例えば同一の絶縁膜を用いて図16に示すトランジスタのゲート絶縁層としての機能を有する絶縁層602及び誘電体層としての機能を有する絶縁層905を形成することもできる。

#### 【0200】

50

図19に一例として示すように、本実施の形態の半導体装置は、酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を有する。この容量素子はノイズによる影響を低減するためのフィルタ回路としての機能を有する。

#### 【0201】

また、本実施の形態の半導体装置は、該酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を複数有し、酸化物半導体層が複数の端子間に一続きで設けられた構造である。よって微細なパターニングを行う必要がなくなるため、製造工程を簡略にすることができる。ただし図19に示す構造に限定されず、本実施の形態の表示装置では、端子毎に酸化物半導体層を設ける構成とすることもできる。10

#### 【0202】

次に本実施の形態の表示装置における端子部の動作について説明する。ここでは、端子部に信号が入力される場合の動作について説明し、入力信号の電圧の絶対値が一定値以下の場合と、一定値より大きい場合に分けて説明する。なお、一定値は、例えば機能回路の仕様などを考慮して適宜設定することができる。

#### 【0203】

容量素子は、入力信号の電圧に応じて容量値が変化する。入力信号の電圧の絶対値が一定値以下の場合、容量素子の容量は一定値より小さいため、フィルタ回路の入力信号に対する出力信号の遅延は小さい。よってフィルタリング効果が小さくなる。なお、容量素子に印加される電圧の絶対値の一定値、容量の一定値、及び遅延時間の一定値は、半導体装置の仕様に応じて適宜設定することができる。20

#### 【0204】

また、入力信号の電圧の絶対値が一定値より大きい場合、容量素子の端子間に印加される電圧の絶対値は一定値より大きく、入力信号に応じて容量素子の容量が一定値より大きくなるため、フィルタ回路の入力信号に対する出力信号の遅延が大きくなる。これにより入力信号の電圧の絶対値が一定値以下の場合よりノイズに対するフィルタリングの効果が大きくなる。以上が本実施の形態の半導体装置の動作である。

#### 【0205】

以上のように、電圧の絶対値が一定値以下の信号が入力された場合に容量素子の容量を小さくし、機能回路に入力される信号の遅延を小さくし、電圧の絶対値が一定値以上の信号が入力された場合に容量素子の容量を大きくし、機能回路に入力される信号の遅延を大きくすることにより、実動作の阻害を低減し、例えばノイズが生じた場合には、入力信号のノイズによる影響を低減することができる。30

#### 【0206】

また、酸化物半導体を用いた半導体素子を有する駆動回路や画素部は、例えば多結晶半導体を用いた半導体素子を有する機能回路と比較して比較的高い動作電圧を必要とすることが多いため、入力信号の振幅が高い傾向にある。しかしながら本実施の形態の半導体装置のように、容量素子を用いたフィルタ回路を、表示装置の駆動回路や画素部と、端子電極との電気的接続間に設けることにより、酸化物半導体を用いた半導体素子を有する表示装置であってもノイズによる影響を低減することができる。40

#### 【0207】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

#### 【0208】

(実施の形態3)

本実施の形態では、本発明の一態様である表示装置の作製方法について説明する。

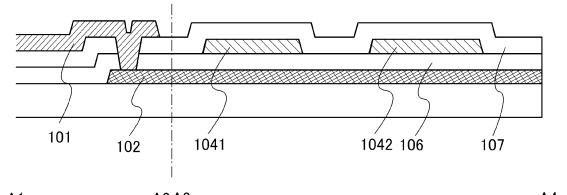

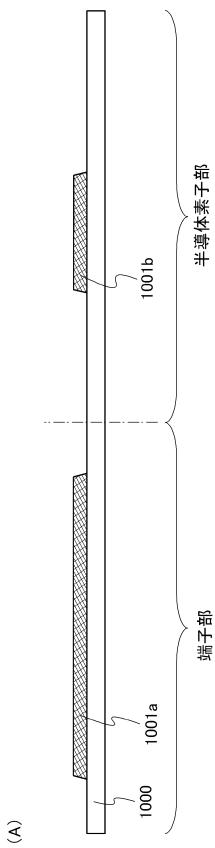

#### 【0209】

本実施の形態の表示装置の作製方法の一例として端子部並びに画素及び駆動回路などを構成する半導体素子部の作製方法について図20乃至図22を用いて説明する。図20乃至図22は、本実施の形態における表示装置の端子部及び半導体素子部の作製方法の一例を50

示す断面図である。なお、図20乃至図22に示す表示装置の端子部及び半導体素子部の作製方法では、一例として半導体素子としてトランジスタを形成する場合について説明する。

#### 【0210】

まず図20(A)に示すように、基板1000を用意し、基板1000上に導電層1001a及び導電層1001bを形成する。導電層1001a及び導電層1001bは、例えば基板1000上に導電膜を形成し、該導電膜を選択的にエッチングすることにより形成することができる。

#### 【0211】

基板1000としては、例えばガラス基板、石英基板、セラミック基板、またはサファイア基板などを用いることができる。ガラス基板としては、例えば無アルカリガラス基板などを用いることができ、無アルカリガラス基板としては、例えばバリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、またはアルミニシリケートガラスなどを用いた基板が挙げられる。また、半導体装置作製に用いられる各処理の温度に耐えうるのであれば、基板100としてプラスチック基板を用いることもできる。また、表面に絶縁処理を施すのであれば、半導体基板、金属基板、またはステンレス基板などを用いることもできる。10

#### 【0212】

導電膜としては、例えばモリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、またはスカンジウムなどの導電性材料またはこれらを主成分とする合金材料を含む導電膜を用いることができる。また導電膜の形成には、例えばスパッタ法を用いることができる。また、導電層1001a及び導電層1001bは、例えばフォトリソグラフィー工程により導電膜上にレジストマスクを形成し、導電膜を選択的にエッチングすることにより形成することができる。20

#### 【0213】

なお、スパッタ法としては、スパッタ用電源に高周波電源を用いるRFスパッタ法と、DCスパッタ法があり、さらにパルス的にバイアスを与えるパルスDCスパッタ法もある。

#### 【0214】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。30

#### 【0215】

また、チャンバー内部に磁石機構を備えたマグネットロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ法を用いるスパッタ装置がある。

#### 【0216】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてこれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

#### 【0217】

また、エッチングとしては、ドライエッチングまたはウェットエッチングを用いることができる。ドライエッチングに用いるエッチング装置としては、反応性イオンエッチング法(RIE法)を用いたエッチング装置や、ECR(Electron Cyclotron Resonance)やICP(Inductively Coupled Plasma)などの高密度プラズマ源を用いたドライエッチング装置を用いることができる。また、ICPエッチング装置と比べて広い面積に渡って一様な放電が得られやすいドライエッチング装置としては、上部電極を接地させ、下部電極に13.56MHzの周波数の電源を接続し、さらに下部電極に3.2MHzの周波数の電源を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッチング装置がある。このECCPモードのエッチング装置であれば、例えば基板として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。4050

## 【0218】

また、導電膜としては、上記に挙げた材料を含む導電膜を積層させた積層膜を用いることもできる。例えば導電膜の一つとしてアルミニウム膜を用いて導電層1001a及び導電層1001bを形成する場合、アルミニウム膜のみでは耐熱性が低く、腐蝕しやすい等の問題点があるため、耐熱性導電膜との積層膜を用いて形成することにより、アルミニウム膜のみの導電膜より耐熱性、耐蝕性などを高めることができるため、好ましい。耐熱性導電膜の材料としては、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、及びスカンジウムから選ばれた元素、上述した元素を成分とする合金、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物を用いることができる。

## 【0219】

10

積層構造の導電膜としては、例えばアルミニウム膜上にモリブデン膜を積層した導電膜、銅膜上にモリブデン膜を積層した導電膜、銅膜上に窒化チタン膜もしくは窒化タンタル膜を積層した導電膜、または窒化チタン膜とモリブデン膜とを積層した導電膜などが挙げられる。

## 【0220】

次に図20(B)に示すように、基板1000、導電層1001a、及び導電層1001b上に絶縁層1002を形成する。さらに、絶縁層1002を選択的にエッチングすることにより、絶縁層1002に開口部を形成し、導電層1001aの一部を露出させる。

## 【0221】

20

絶縁層1002としては、例えばシリコン、アルミニウム、イットリウム、タンタル、及びハフニウムのいずれかの酸化物、窒化物、酸化窒化物、若しくは窒化酸化物、またはそれらの化合物を少なくとも2種以上含む化合物からなる絶縁膜を用いることができる。

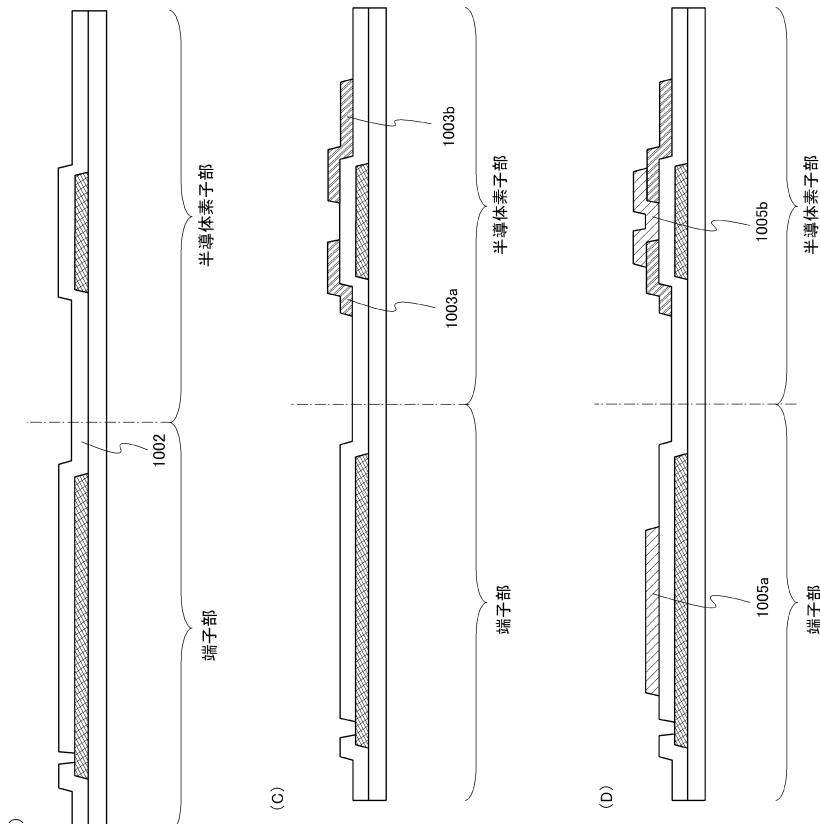

## 【0222】

次に図21(A)に示すように、絶縁層1002を挟んで導電層1001bの一部の上に導電層1003a及び導電層1003bを形成する。導電層1003a及び導電層1003bは、例えば絶縁層1002上に導電膜を形成し、該導電膜を選択的にエッチングすることにより形成することができる。

## 【0223】

導電層1003a及び導電層1003bの形成に用いることができる導電膜としては、例えばスパッタ法や真空蒸着法等を用いて、アルミニウム(A1)、銅(Cu)、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、スカンジウム(Sc)から選ばれた元素を含む金属、上述の元素を成分とする合金、または、上述の元素を成分とする窒化物等からなる材料で形成することができる。導電層1003a及び導電層1003bは、例えばフォトリソグラフィー工程により導電膜上に選択的にレジストマスクを形成し、その後導電膜をエッチングすることにより形成することができる。

30

## 【0224】

40

例えば、モリブデン膜やチタン膜の単層膜を導電膜とすることができます。また積層膜を導電膜とすることもでき、例えば、アルミニウム膜とチタン膜を積層して導電膜とすることもできる。また、チタン膜と、アルミニウム膜と、チタン膜とを順に積層した3層構造としてもよい。また、モリブデン膜とアルミニウム膜とモリブデン膜とを順に積層した3層構造としてもよい。また、これらの積層構造に用いるアルミニウム膜として、ネオジムを含むアルミニウム(A1-Nd)膜を用いてもよい。さらに、シリコンを含むアルミニウム膜を導電膜とすることもできる。

## 【0225】

また、導電膜として、透光性を有し且つ導電性が高い材料を用いて形成してもよい。このような材料として、例えば、インジウム錫酸化物(Indium Tin Oxide:ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、有機インジウム、有機スズ、酸化亜鉛(ZnO)等を用いることができる。

## 【0226】

50

次に図21(B)に示すように、絶縁層1002を挟んで導電層1001a上に半導体層1005aを形成し、導電層1003a及び導電層1003b上、並びに絶縁層1002を挟んで導電層1001b上に半導体層1005bを形成する。半導体層1005a及び半導体層1005bは、例えば絶縁層1002上に半導体膜を形成し、半導体膜を選択的にエッティングすることにより形成することができる。

#### 【0227】

半導体層1005a及び半導体層1005bの形成に用いることができる半導体膜としては、例えば酸化物半導体膜などを用いることができる。酸化物半導体膜としては、例えばSn、In、及びZnのいずれかを含む酸化物半導体膜などが挙げられる。また、酸化物半導体膜を用いる場合、酸化物半導体膜にアモルファス成分を含むものを用いることもできる。また、酸化物半導体膜の中に結晶粒(ナノクリスタル)を含むものを用いることもできる。このとき、酸化物半導体膜中の結晶粒(ナノクリスタル)は直径1nm~10nm、代表的には2nm~4nm程度である。10

#### 【0228】

また、酸化物半導体としては、例えば、 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記される構造の酸化物半導体を用いることもでき、 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記される構造の酸化物半導体の中では、特にIn-Ga-Zn-O系酸化物半導体を用いるのが好ましい。なお、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)及びコバルト(Co)から選ばれた一の金属元素または複数の金属元素を示す。例えばMとして、Gaの場合があることの他、GaとNiまたはGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。20

#### 【0229】

なお、In-Ga-Zn-O系非単結晶膜を用いる場合、In-Ga-Zn-O系非単結晶膜を形成した後、100~600、代表的には200~400の熱処理を行うと良い。例えば、大気または窒素雰囲気下で350、1時間の熱処理を行うことにより半導体膜を構成するIn-Ga-Zn-O系酸化物半導体膜の原子レベルの再配列が行われる。この熱処理(光アニール等も含む)により、酸化物半導体膜中におけるキャリアの移動を阻害する歪みを低減することができる。なお、上記の熱処理を行うタイミングは、酸化物半導体膜の形成後であれば特に限定されない。また、本実施の形態の表示装置における端子部は、平面視において酸化物半導体層が導電層に重なる構造であるため、熱処理により酸化物半導体層を効率良く加熱することができる。また、本実施の形態の表示装置における端子部は、例えば上記実施の形態1の図2に示す半導体装置と同様に、端子部を酸化物半導体層が導電層と接する構造にすることにより、熱処理により酸化物半導体層をさらに効率良く加熱することもできる。30

#### 【0230】

In-Ga-Zn-O系非単結晶膜は、例えばスパッタ法を用いて成膜した後、200~500、代表的には300~400で10分~100分の熱処理が行われる。熱処理後のXRD(X線回折)の分析では、熱処理後においてもIn-Ga-Zn-O系非単結晶膜の結晶構造としてアモルファス構造が観察される。40

#### 【0231】

また、酸化物半導体膜として上記の他にも、In-Sn-Zn-O系、Al-In-Zn-O系、Ga-Sn-Zn-O系、Al-Ga-Zn-O系、Al-Sn-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いることができる。

#### 【0232】

なお、半導体層1005a及び半導体層1005bは、例えばフォトリソグラフィー工程により半導体膜上に選択的にレジストマスクを形成し、その後半導体膜をエッティングすることにより形成することができる。50

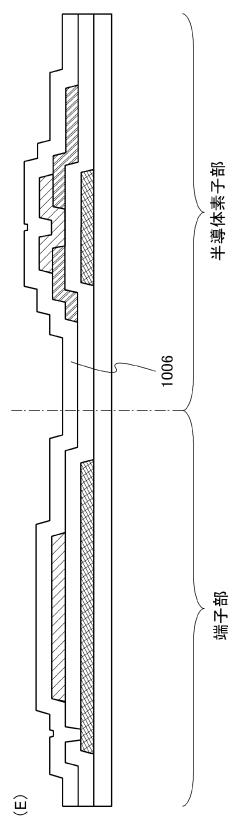

**【 0 2 3 3 】**

次に図22(A)に示すように、導電層1003a及び導電層1003b並びに半導体層1005a及び半導体層1005bを挟んで絶縁層1002上に絶縁層1006を形成する。好ましくは、導電層1003a及び導電層1003bの上面及び側面、並びに半導体層1005a及び半導体層1005bの上面及び側面上に絶縁層1006を形成する。

**【 0 2 3 4 】**

絶縁層1006は、例えば端子部において容量素子の誘電体層としての機能を有し、また、半導体素子部においてトランジスタの保護層としての機能を有することもできる。絶縁層1006としては、例えば絶縁層1002に適用可能な材料を用いて形成することができる。

10

**【 0 2 3 5 】**

次に図22(B)に示すように、絶縁層1002及び絶縁層1006に設けられた開口部を介して導電層1001aに電気的に接続されるように導電層1007aを形成し、絶縁層1006に設けられた開口部を介して導電層1003bに電気的に接続されるように導電層1007bを形成する。導電層1007a及び導電層1007bは、例えば絶縁層1006上に導電膜を形成し、該導電膜を選択的にエッチングすることにより形成することができる。

**【 0 2 3 6 】**

このとき導電層1007aは、絶縁層1006を挟んで半導体層1005a上に形成することが好ましい。絶縁層1006を挟んで半導体層1005a上に形成することにより半導体層1005a、絶縁層1006、及び導電層1007aにより容量素子を構成することができる。

20

**【 0 2 3 7 】**

導電層1007a及び導電層1007bとしては、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電膜などを用いて形成することができる。

**【 0 2 3 8 】**

なお、導電層1007a及び導電層1007bは、例えばフォトリソグラフィー工程により導電膜上に選択的にレジストマスクを形成し、その後導電膜をエッチングすることにより形成することができる。

30

**【 0 2 3 9 】**

以上の工程により端子部及び半導体素子部を形成することができる。

**【 0 2 4 0 】**

図20乃至図22に一例として示すように、本実施の形態の表示装置の作製方法により端子部における容量素子、及び画素部などの半導体素子部の半導体素子を同一工程で形成することができるため、製造工程数の増加を防止することができる。

**【 0 2 4 1 】**

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

40

**【 0 2 4 2 】****(実施の形態4)**

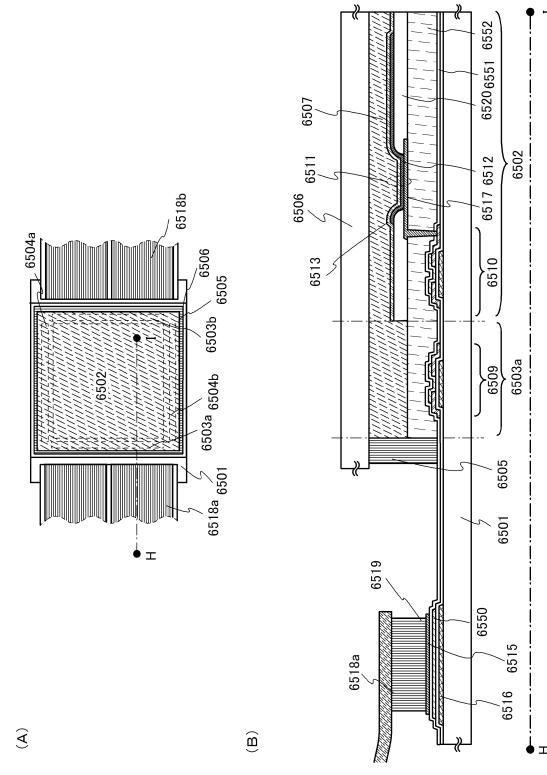

本実施の形態では、本発明の一態様である表示装置の一形態として、発光パネルの外観及び断面について、図23を用いて説明する。図23は、本実施の形態における発光パネルの構造例を示す図であり、図23(A)は上面図であり、図23(B)は、図23(A)の線分H-Iにおける断面を示す断面図である。

**【 0 2 4 3 】**

図23に示す発光パネルは、第1の基板6501上に画素部6502、信号線駆動回路6503a、6503b、及び走査線駆動回路6504a、6504bを有し、画素部6502、信号線駆動回路6503a、6503b、及び走査線駆動回路6504a、6504bを有する。

50

4 b を囲むようにシール材 6505 が設けられている。画素部 6502、信号線駆動回路 6503a、6503b、及び走査線駆動回路 6504a、6504b の上に第2の基板 6506 が設けられている。よって画素部 6502、信号線駆動回路 6503a、6503b、及び走査線駆動回路 6504a、6504b は、第1の基板 6501 とシール材 6505 と第2の基板 6506 とによって、充填材 6507 と共に密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルムなど）やカバー材でパッケージング（封入）することが好みしい。

#### 【0244】

また第1の基板 6501 上に設けられた画素部 6502、信号線駆動回路 6503a、6503b、及び走査線駆動回路 6504a、6504b は、TFT を複数有しており、図 23 (B) では、画素部 6502 に含まれる TFT 6510 と、信号線駆動回路 6503a に含まれる TFT 6509 とを例示している。画素部 6502、信号線駆動回路 6503a、6503b、及び走査線駆動回路 6504a、6504b のそれぞれが有する TFT としては、例えば上記実施の形態に示すトランジスタのいずれかを適用することができる。図 23 に示す半導体装置では、トランジスタの一例として図 16 (A) に示す構造を適用し、具体的な説明については図 16 (A) の説明を適宜援用する。なお図 23 において、TFT 6509、6510 は N 型 TFT である。

#### 【0245】

また、図 23 に示す発光パネルは、TFT の表面凹凸を低減するため、及び TFT の信頼性を向上させるため、TFT を保護層や平坦化絶縁膜としての機能を有する絶縁層（絶縁層 6551、絶縁層 6552）で覆う構成となっている。

#### 【0246】

ここでは、保護層として積層構造の絶縁層 6551 を形成する。ここでは、絶縁層 6551 の一層目として、スパッタ法を用いて酸化珪素膜を形成する。保護層として酸化珪素膜を用いると、ソース電極及びドレイン電極として用いるアルミニウム膜のヒロック防止に効果がある。

#### 【0247】

また、絶縁層 6551 の二層目として、スパッタ法を用いて窒化珪素膜を形成する。保護層として窒化珪素膜を用いると、ナトリウムなどの可動イオンが半導体領域中に侵入して、TFT の電気特性を変化させることを抑制することができる。

#### 【0248】

また、保護層を形成した後に、半導体層のアニール (250 ~ 400) を行ってもよい。

#### 【0249】

また、平坦化絶縁膜として絶縁層 6552 を形成する。絶縁層 6552 としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシなどの、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料 (low-k 材料)、シロキサン系樹脂、PSG (リンガラス)、BPSG (リンボロンガラス) などを用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、絶縁層 6552 を形成してもよい。

#### 【0250】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

#### 【0251】

絶縁層 6552 の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG 法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷など）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナ

10

20

30

40

50

イフコーダーなどを用いることができる。材料液を用いて絶縁層 6552 を形成する場合、ベークする工程で同時に、半導体層のアニール（300 ~ 400）を行ってもよい。絶縁層 6552 の焼成工程と半導体層のアニールを兼ねることで効率よく表示装置を作製することが可能となる。

#### 【0252】

また TFT6510 上に発光素子 6511 が設けられる。発光素子 6511 は、TFT6510 のソース電極またはドレイン電極に電気的に接続され、画素電極である第 1 の電極 6517、電界発光層 6512、第 2 の電極 6513 の積層構造により構成される。なお発光素子 6511 は図 23 に示す構造に限定されず、本実施の形態の表示装置では、発光素子 6511 の光を取り出す方向などに合わせて、発光素子 6511 の構造を適宜変えることができる。10

#### 【0253】

隔壁 6520 は、第 1 の電極 6517 上に設けられる。さらに図 23 に示す発光パネルは、隔壁 6520 に設けられた開口部を介して第 1 の電極 6517 に電気的に接続されるよう電界発光層 6512 を有し、電界発光層 6512 上に第 2 の電極 6513 を有する。隔壁 6520 としては、感光性の材料を用いることが好ましく、側壁が連続した曲率を持つ傾斜面となるように該感光性材料層の第 1 の電極 6517 上に開口部を形成することにより隔壁 6520 を形成することができる。

#### 【0254】

電界発光層 6512 としては、例えば図 15 (B) に示す発光素子 615 を構成する電界発光層と同じ材料を用いることができる。また、電界発光層 6512 は、単数の層で構成されていても、複数の層の積層で構成されていても良い。20

#### 【0255】

また、図 23 に示す発光パネルにおいて、発光素子 6511 に酸素、水素、水分、二酸化炭素などが侵入しないように、第 2 の電極 6513 及び隔壁 6520 上に保護層を形成してもよい。保護層としては、窒化珪素膜、窒化酸化珪素膜、DLC 膜などを用いることができる。

#### 【0256】

また、信号線駆動回路 6503a、6503b、走査線駆動回路 6504a、6504b、または画素部 6502 に与えられる各種信号及び電位は、FPC6518a、6518b から供給されている。30

#### 【0257】

また図 23 に示す発光パネルでは、接続端子電極 6515 は、発光素子 6511 が有する第 1 の電極 6517 と同じ導電膜から形成され、端子電極 6516 は、TFT6509、6510 が有するゲート電極と同じ導電膜から形成される。

#### 【0258】

また、端子電極 6516 上に半導体層 6550 が設けられている。半導体層 6550 はフィルタ回路を構成する容量素子の電極としての機能を有する。

#### 【0259】

接続端子電極 6515 は、FPC6518a が有する端子と、異方性導電膜 6519 を介して電気的に接続されている。40

#### 【0260】

発光素子 6511 からの光の取り出し方向に位置する基板としては、透光性を有する基板を用いることが好ましく、透光性を有する基板としては、ガラス板、プラスチック板、ポリエチルフィルムまたはアクリルフィルムのような透光性を有する材料を用いることができる。

#### 【0261】

また、充填材 6507 としては、窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB (ポリビニルブチラル) または E50

V A (エチレンビニルアセテート)を用いることができる。図23に示す表示装置では、一例として充填材6507として窒素を用いる。

#### 【0262】

また、必要であれば、発光素子6511からの光の射出面に偏光板、または円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板または円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

#### 【0263】

信号線駆動回路6503a、6503b、及び走査線駆動回路6504a、6504bは、図23に示す構造に限定されず、本実施の形態の表示装置では、別途用意された基板上に単結晶半導体膜または多結晶半導体膜を用いて半導体素子が形成された駆動回路を実装した構成としてもよい。また、信号線駆動回路6503a、6503bのみ、若しくは信号線駆動回路6503a、6503bの一部、または走査線駆動回路6504a、6504bのみ、若しくは走査線駆動回路6504a、6504bの一部を別途形成して実装しても良い。

10

#### 【0264】

以上の工程により、信頼性の高い発光パネルを作製することができる。

#### 【0265】

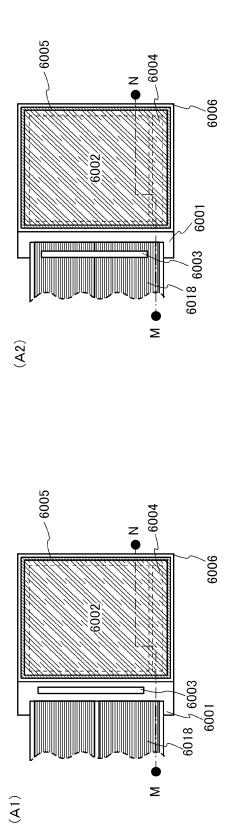

次に本実施の形態における表示装置の一形態として、液晶パネルの外観及び断面について、図24を用いて説明する。図24は本実施の形態における液晶パネルの構造例を示す図であり、図24(A1)(A2)は上面図であり、図24(B)は、図24(A1)(A2)のM-Nにおける断面図である。

20

#### 【0266】

図24に示す液晶パネルは、第1の基板6001上に画素部6002と、信号線駆動回路6003と、走査線駆動回路6004と、を有し、画素部6002、信号線駆動回路6003、及び走査線駆動回路6004を囲むようにして、シール材6000及びシール材6005が設けられている。また、画素部6002及び走査線駆動回路6004上に第2の基板6006が設けられ、画素部6002と、走査線駆動回路6004とは、第1の基板6001とシール材6000とシール材6005と第2の基板6006とによって、液晶層6008と共に封止されている。TFT6010、6011、及び液晶素子6013を有し、第1の基板6001上にTFT6010、6011、及び液晶素子6013が第1の基板6001と第2の基板6006との間にシール材6000及びシール材6005によって封止されている。また、第1の基板6001上のシール材6000及びシール材6005によって囲まれている領域とは異なる領域に、別途用意された基板上に信号線駆動回路6003が実装されている。

30

#### 【0267】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG方法、ワイヤボンディング方法、或いはTAB方法などを用いることができる。図24(A1)は、COG方法により信号線駆動回路6003を実装する例であり、図24(A2)は、TAB方法により信号線駆動回路6003を実装する例である。

40

#### 【0268】

また第1の基板6001上に設けられた画素部6002と、走査線駆動回路6004は、TFTを複数有しており、図24(B)では、画素部6002に含まれるTFT6010と、走査線駆動回路6004に含まれるTFT6011とを例示している。

#### 【0269】

TFT6010、6011としては、上記実施の形態に示す構造のTFTのいずれかを適用することができる。図24に示す液晶パネルでは、TFTの一例として図16(A)に示す構造のTFTを適用する。また図24に示す液晶パネルにおいて、TFT6010、6011はN型TFTとして説明する。

50

**【 0 2 7 0 】**

また、液晶素子 6013 が有する画素電極 6030 は、TFT6010 のソース電極またはドレイン電極に電気的に接続されている。そして液晶素子 6013 の対向電極 6031 は第 2 の基板 6006 上に形成されている。画素電極 6030 と対向電極 6031 と液晶層 6008 とが重なっている部分が、液晶素子 6013 に相当する。なお、画素電極 6030、対向電極 6031 はそれぞれ配向膜としての機能を有する絶縁層 6032、6033 が設けられ、絶縁層 6032、6033 を介して液晶層 6008 を挟持している。

**【 0 2 7 1 】**

またスペーサ 6035 は、絶縁膜を選択的にエッチングすることで得られる柱状の隔壁であり、画素電極 6030 と対向電極 6031 との間の距離（セルギャップ）を制御するために設けられている。なお球状のスペーサを用いても良い。また、対向電極 6031 は、TFT6010 と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極 6031 と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材 6005 に含有させる。

10

**【 0 2 7 2 】**

なお図 24 に示す液晶パネルは、透過型液晶表示パネルの例であるが、これに限定されず、本実施の形態の液晶表示パネルは、反射型液晶表示パネルまたは半透過型液晶表示パネルとすることもできる。

**【 0 2 7 3 】**

20

また、本実施の形態の液晶表示パネルは、基板の外側（視認側）に偏光板を設け、内側に着色層、表示素子に用いる電極という順に設ける構成、または基板の内側に偏光板を設ける構成にすることができる。また、偏光板と着色層の積層構造も偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、ブラックマトリクスとしての機能を有する遮光膜を設けてもよい。

**【 0 2 7 4 】**

また、図 24 に示す液晶表示パネルは、TFT の表面凹凸を低減するため、及び TFT の信頼性を向上させるため、TFT を保護層や平坦化絶縁膜としての機能を有する絶縁層（絶縁層 6020、絶縁層 6021）で覆う構成となっている。

**【 0 2 7 5 】**

30

ここでは、保護層として積層構造の絶縁層 6020 を形成する。ここでは、絶縁層 6020 の一層目として、スパッタ法を用いて酸化珪素膜を形成する。保護層として酸化珪素膜を用いると、ソース電極及びドレイン電極として用いるアルミニウム膜のヒロック防止に効果がある。

**【 0 2 7 6 】**

さらに、絶縁層 6020 の二層目として、スパッタ法を用いて窒化珪素膜を形成する。保護層として窒化珪素膜を用いると、ナトリウムなどの可動イオンが半導体領域中に侵入して、TFT の電気特性を変化させることを抑制することができる。

**【 0 2 7 7 】**

また、保護層を形成した後に、半導体層のアニール（250 ~ 400）を行ってもよい。

40

**【 0 2 7 8 】**

また、平坦化絶縁膜として絶縁層 6021 を形成する。絶縁層 6021 としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシなどの、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）などを用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層 6021 を形成してもよい。

**【 0 2 7 9 】**

絶縁層 6021 の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG 法

50

、スピニコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷など）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラーなどを用いることができる。絶縁層6021を材料液を用いて形成する場合、ベークする工程で同時に、半導体層のアニール（300～400）を行ってもよい。絶縁層6021の焼成工程と半導体層のアニールを兼ねることで効率よく表示装置を作製することが可能となる。

#### 【0280】

画素電極6030及び対向電極6031としては、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。10

#### 【0281】

また、画素電極6030、対向電極6031は、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

#### 【0282】

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、もしくはこれらの2種以上の共重合体などがあげられる。20

#### 【0283】

また別途形成された信号線駆動回路6003、走査線駆動回路6004または画素部6002に与えられる各種信号及び電位は、FPC6018から供給されている。

#### 【0284】

また、接続端子電極6015は、液晶素子6013が有する画素電極6030と同じ導電膜から形成され、端子電極6016は、TFT6010、6011のゲート電極と同じ導電膜で形成されている。

#### 【0285】

また、端子電極6016上に半導体層6050が設けられている。半導体層6050はフィルタ回路を構成する容量素子の電極としての機能を有する。

#### 【0286】

接続端子電極6015は、FPC6018が有する端子と、異方性導電膜6019を介して電気的に接続されている。

#### 【0287】

また図24に示す液晶パネルは、信号線駆動回路6003を別途形成し、信号線駆動回路6003を第1の基板6001に実装している構成であるが、これに限定されず、本実施の形態の液晶パネルは、走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。40

#### 【0288】

図24に一例として挙げたように、本発明の一態様である半導体装置を適用した液晶パネルを作製することができる。

#### 【0289】

さらに上記液晶パネルを用いた液晶表示モジュールの一例について図25を用いて説明する。図25は本実施の形態の液晶表示モジュールの一例を示す図である。

#### 【0290】

図25に示す液晶表示モジュールは、TFT基板2600と対向基板2601がシール材2602により固定され、その間にTFT等を含む画素部2603、液晶層を含む表示素子2604、着色層2605が設けられることにより表示領域が形成されている構造であ50

る。着色層 2605 はカラー表示を行う場合に必要であり、RGB 方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。また、TFT 基板 2600 と対向基板 2601 の外側には偏光板 2606、偏光板 2607、拡散板 2613 が配設されている。また、光源は冷陰極管 2610 と反射板 2611 により構成され、回路基板 2612 は、フレキシブル配線基板 2609 により TFT 基板 2600 の配線回路部 2608 と接続され、また、回路基板 2612 には、コントロール回路や電源回路などの外部回路が組みこまれている。また偏光板と、液晶層との間に位相差板を有した状態で積層してもよい。

#### 【0291】

以上のように、本実施の形態の液晶パネルを用いて液晶表示モジュールを構成することができる。 10

#### 【0292】

なお、本実施の形態の表示装置は、FPC との接続部に酸化物半導体層を有する容量素子を備えたフィルタ回路を有する構成であるため、例えば映像信号にノイズが生じた場合であってもノイズによる影響を低減することができる。また、本実施の形態の表示装置では、基板として例えばガラス基板、またはプラスチック基板などを用いた場合であっても基板に帯電した電荷の影響を低減することができ、また例えば第 10 世代の 3m を超えるサイズの基板を用いる場合にも同様である。

#### 【0293】

なお、本実施の形態は、他の実施の形態と、適宜組み合わせることができる。 20

#### 【0294】

##### (実施の形態 5)

本実施の形態では、本発明の一態様である表示装置の一例として電子ペーパについて説明する。

#### 【0295】

本発明の一態様である半導体装置は、電子ペーパに用いることもできる。電子ペーパは、電気泳動表示装置（電気泳動ディスプレイともいう）とも呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

#### 【0296】

電気泳動ディスプレイは、様々な形態が考えられ得るが、プラスの電荷を有する第 1 の粒子と、マイナスの電荷を有する第 2 の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第 1 の粒子または第 2 の粒子は染料を含み、電界がない場合において移動しないものである。また、第 1 の粒子の色と第 2 の粒子の色は異なるもの（無色を含む）とする。 30

#### 【0297】

このように、電気泳動ディスプレイは、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動効果を利用したディスプレイである。電気泳動ディスプレイは、液晶表示装置には必要な偏光板、対向基板も必要なく、厚さや重さが半減する。 40

#### 【0298】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

#### 【0299】

また、アクティブマトリクス基板上に適宜、二つの電極の間に挟まれるように上記マイクロカプセルを複数配置すればアクティブマトリクス型の表示装置が完成し、マイクロカプセルに電界を印加すれば表示を行うことができる。

#### 【0300】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

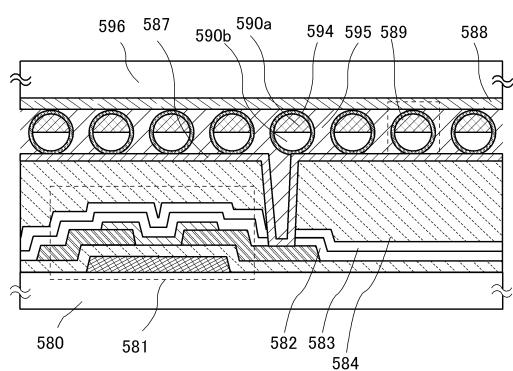

#### 【0301】

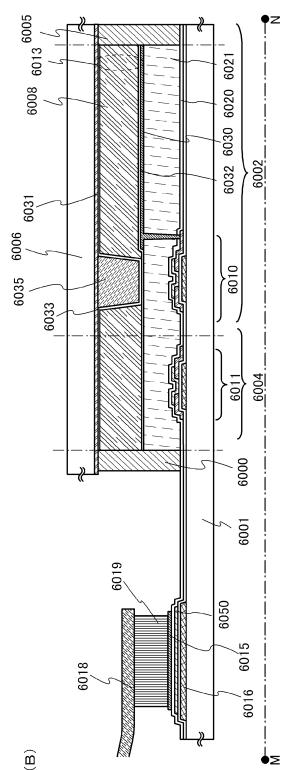

次に本実施の形態における電子ペーパの構造について図26を用いて説明する。図26は本実施の形態における電子ペーパの構造の一例を示す断面図である。

#### 【0302】

図26に示す電子ペーパは、基板580上にTFT581と、TFT581上に積層して設けられた絶縁層582、絶縁層583、及び絶縁層584と、絶縁層582乃至絶縁層584に設けられた開口部を介してTFT581のソース電極またはドレイン電極に接する電極587と、電極588と、電極587と基板596に設けられた電極588との間に黒色領域590a及び白色領域590bと、周りに液体で満たされているキャビティ594を含む球形粒子589と、球形粒子589の周りに設けられた充填剤595と、を有する。

10

#### 【0303】

TFT581としては、本発明の一態様である半導体装置を用いることができる。図26に示す電子ペーパでは、一例として図1(A)に示す構造の半導体装置を適用する。

#### 【0304】

球形粒子589を用いた方式はツイストボール表示方式といい、ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極である第1の電極及び第2の電極の間に配置し、第1の電極及び第2の電極に電位差を生じさせて球形粒子の向きを制御することにより、表示を行う方式である。

20

#### 【0305】

また、球形素子の代わりに電気泳動素子を用いることも可能である。透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径 $10\text{ }\mu\text{m} \sim 200\text{ }\mu\text{m}$ 程度のマイクロカプセルを用いる。第1の電極と第2の電極との間に設けられるマイクロカプセルは、第1の電極と第2の電極によって、電場が与えられると、白い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動表示素子である。電気泳動表示素子は、液晶表示素子に比べて反射率が高いため、補助ライトは不要であり、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能であるため、電波発信源から表示機能付き半導体装置（単に表示装置、または表示装置を具備する半導体装置ともいう）を遠ざけた場合であっても、表示された像を保存しておくことが可能となる。

30

#### 【0306】

図26に一例として挙げたように、本実施の形態における電子ペーパは、上記実施の形態に示す端子部と同様に酸化物半導体層と、配線または電極を形成する導電層と、酸化物半導体層と導電層との間に設けられた絶縁層により形成された容量素子を有する構成とすることができる。この容量素子は保護回路の一部としての機能を有する。また、この容量素子は、ノイズによる影響を低減するためのフィルタ回路の一部としての機能を有するため、電子ペーパに用いた場合も同様に実動作の阻害を低減し、ノイズによる影響を低減することができる。

40

#### 【0307】

または上記電子ペーパは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパを用いて、電子書籍（電子ブック）、ポスター、電車などの乗り物の車内広告、クレジットカードなどの各種カードにおける表示などに適用することができる。電子機器の一例を図27に示す。図27は、本実施の形態の電子書籍の一例を示す図である。

#### 【0308】

50

図27に示すように、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

#### 【0309】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、互いに異なる映像を表示する構成としてもよく、例えば一続きの映像を表示する構成としてもよい。また、互いに異なる画面を表示する構成とすることで、例えば右側の表示部(図27では表示部2705)に文章を表示し、左側の表示部(図27では表示部2707)に画像を表示することができる。10

#### 【0310】

また、図27では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。20

#### 【0311】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

#### 【0312】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

#### 【0313】

##### (実施の形態6)

本実施の形態では、本発明の一態様である表示装置を表示部に備えた電子機器について説明する。30

#### 【0314】

本実施の形態の電子機器の構成の一例について図28乃至図30を用いて説明する。図28乃至図30は、本実施の形態の電子機器の構成の一例を示す図である。

#### 【0315】

本発明の一態様である表示装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。40

#### 【0316】

図28(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することができる。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

#### 【0317】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルや音量の操作を行なうことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機50

9610から出力する情報を表示する表示部9607を設ける構成としてもよい。上記実施の形態の表示装置を表示部9603に適用することにより、例えば筐体9601が透光性を有するものであってもよい。

### 【0318】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般的なテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

### 【0319】

図28（B）は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

### 【0320】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子（USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

### 【0321】

また、デジタルフォトフレーム9700は、無線で情報を送受信できる構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

### 【0322】

図29（A）は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部9882が組み込まれ、筐体9891には表示部9883が組み込まれている。また、図29（A）に示す携帯型遊技機は、その他、スピーカ部9884、記録媒体挿入部9886、LEDランプ9890、入力手段（操作キー9885、接続端子9887、センサ9888（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい、または赤外線を測定する機能を含むもの）、マイクロフォン9889）などを備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも表示装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。図29（A）に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図29（A）に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

### 【0323】

図29（B）は大型遊技機であるスロットマシンの一例を示している。スロットマシン9900は、筐体9901に表示部9903が組み込まれている。また、スロットマシン9900は、その他、スタートレバーやストップスイッチなどの操作手段、コイン投入口、スピーカなどを備えている。もちろん、スロットマシン9900の構成は上述のものに限定されず、少なくとも本発明に係る表示装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができます。

### 【0324】

図30（A）は、携帯電話機の一例を示している。携帯電話機9000は、筐体9001に組み込まれた表示部9002の他、操作ボタン9003、外部接続ポート9004、スピーカ9005、マイク9006などを備えている。

### 【0325】

10

20

30

40

50

図30(A)に示す携帯電話機9000は、表示部9002を指などで触ることで、情報を入力ことができる。また、電話を掛ける、或いはメールを作成するなどの操作は、表示部9002を指などで触ることにより行うことができる。

#### 【0326】

表示部9002の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字などの情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

#### 【0327】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部9002を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部9002の画面のほとんどにキーボードまたは番号ボタンを表示させることができ。10

#### 【0328】

また、携帯電話機9000内部に、ジャイロ、加速度センサなどの傾きを検出するセンサを有する検出装置を設けることで、携帯電話機9000の向き(縦か横か)を判断して、表示部9002の画面表示を自動的に切り替えるようにすることができる。

#### 【0329】

また、画面モードの切り替えは、表示部9002を触れること、または筐体9001の操作ボタン9003の操作により行われる。また、表示部9002に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。20

#### 【0330】

また、入力モードにおいて、表示部9002の光センサで検出される信号を検知し、表示部9002のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

#### 【0331】

表示部9002は、イメージセンサとして機能させることもできる。例えば、表示部9002に掌や指を触ることで、掌紋、指紋などを撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。30

#### 【0332】

図30(B)も携帯電話機の一例である。図30(B)の携帯電話機は、筐体9411に、表示部9412、及び操作ボタン9413を含む表示装置9410と、筐体9401に操作ボタン9402、外部入力端子9403、マイク9404、スピーカ9405、及び着信時に発光する発光部9406を含む通信装置9400とを有しており、表示機能を有する表示装置9410は電話機能を有する通信装置9400と矢印の2方向に脱着可能である。よって、表示装置9410と通信装置9400の短軸同士を取り付けることも、表示装置9410と通信装置9400の長軸同士を取り付けることもできる。また、表示機能のみを必要とする場合、通信装置9400より表示装置9410を取り外し、表示装置9410を単独で用いることもできる。通信装置9400と表示装置9410とは無線通信または有線通信により画像または入力情報を授受することができ、通信装置9400と表示装置9410とは、それぞれ充電可能なバッテリーを有する。40

#### 【0333】

上記に一例として挙げたように、本発明の一態様である表示装置は、様々な電子機器に適用することができる。また、本発明の一態様である表示装置を搭載することにより電子機器の信頼性を向上させることができる。

#### 【0334】

また、本発明の一態様である表示装置を表示部に適用することにより、例えば筐体を透光性を有する構成にした場合であっても透光性の低下を抑制することができ、また、筐体を透光性を有する構成にした場合であっても平面視において導電層と酸化物半導体層とが重50

なる場合には光の入射による酸化物半導体層の劣化を抑制することができる。

【0335】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

【符号の説明】

【0336】

|         |         |    |

|---------|---------|----|

| 1 0 0   | 基板      |    |

| 1 0 1   | 電極      |    |

| 1 0 2   | 配線      |    |

| 1 0 3   | 機能回路    |    |

| 1 0 4   | 酸化物半導体層 | 10 |

| 1 0 5   | 開口部     |    |

| 1 0 6   | 絶縁層     |    |

| 1 0 7   | 絶縁層     |    |

| 1 0 8   | 配線      |    |

| 1 1 1   | 端子      |    |

| 1 1 2   | 抵抗素子    |    |

| 1 1 3   | 容量素子    |    |

| 1 1 4   | 機能回路    |    |

| 1 1 5   | 端子      |    |

| 2 0 1   | 端子      | 20 |

| 2 0 2   | 抵抗素子    |    |

| 2 0 3   | 容量素子    |    |

| 2 0 4   | 端子      |    |

| 2 0 5   | 容量素子    |    |

| 2 0 6   | 端子      |    |

| 2 0 7   | 端子      |    |

| 5 0 1   | 端子電極    |    |

| 5 0 2   | 配線      |    |

| 5 0 3   | 走査線駆動回路 |    |

| 5 0 4   | 信号線駆動回路 | 30 |

| 5 0 5   | 画素部     |    |

| 5 0 6   | 端子部     |    |

| 5 8 0   | 基板      |    |

| 5 8 1   | TFT     |    |

| 5 8 2   | 絶縁層     |    |

| 5 8 3   | 絶縁層     |    |

| 5 8 4   | 絶縁層     |    |

| 5 8 5   | 絶縁層     |    |

| 5 8 7   | 電極      |    |

| 5 8 8   | 電極      | 40 |

| 5 8 9   | 球形粒子    |    |

| 5 9 0 a | 黒色領域    |    |

| 5 9 0 b | 白色領域    |    |

| 5 9 4   | キャビティ   |    |

| 5 9 5   | 充填剤     |    |

| 5 9 6   | 基板      |    |

| 6 0 0   | 基板      |    |

| 6 0 1   | 導電層     |    |

| 6 0 2   | 絶縁層     |    |

| 6 0 3 a | 導電層     | 50 |

|           |          |    |

|-----------|----------|----|

| 6 0 3 b   | 導電層      |    |

| 6 0 4     | 半導体層     |    |

| 6 0 5 a   | バッファ層    |    |

| 6 0 5 b   | バッファ層    |    |

| 6 0 6     | 絶縁層      |    |

| 6 1 1     | トランジスタ   |    |

| 6 1 2     | 液晶素子     |    |

| 6 1 3     | 容量素子     |    |

| 6 1 4     | トランジスタ   |    |

| 6 1 5     | 発光素子     | 10 |

| 7 1 1     | シフトレジスタ  |    |

| 7 1 2     | レベルシフタ   |    |

| 7 1 3     | バッファ回路   |    |

| 7 2 1     | シフトレジスタ  |    |

| 7 2 2     | ラッチ回路    |    |

| 7 2 3     | レベルシフタ   |    |

| 7 2 4     | バッファ回路   |    |

| 7 2 5     | D A 変換回路 |    |

| 9 0 1     | 導電層      |    |

| 9 0 1 a   | 導電層      | 20 |

| 9 0 1 b   | 導電層      |    |

| 9 0 1 c   | 導電層      |    |

| 9 0 2 a   | 導電層      |    |

| 9 0 2 b   | 導電層      |    |

| 9 0 2 c   | 導電層      |    |

| 9 0 4 a   | 開口部      |    |

| 9 0 4 b   | 開口部      |    |

| 9 0 4 c   | 開口部      |    |

| 9 0 5     | 絶縁層      |    |

| 9 0 6     | 絶縁層      | 30 |

| 9 1 0 a   | 端子       |    |

| 9 1 0 b   | 端子       |    |

| 9 1 0 c   | 端子       |    |

| 1 0 0 0   | 基板       |    |

| 1 0 0 1 a | 導電層      |    |

| 1 0 0 1 b | 導電層      |    |

| 1 0 0 2   | 絶縁層      |    |

| 1 0 0 3 a | 導電層      |    |

| 1 0 0 3 b | 導電層      |    |

| 1 0 0 5 a | 半導体層     | 40 |

| 1 0 0 5 b | 半導体層     |    |

| 1 0 0 6   | 絶縁層      |    |

| 1 0 0 7 a | 導電層      |    |

| 1 0 0 7 b | 導電層      |    |

| 1 0 4 1   | 酸化物半導体層  |    |

| 1 0 4 2   | 酸化物半導体層  |    |

| 1 0 5 1   | 開口部      |    |

| 1 0 5 2   | 開口部      |    |

| 1 1 3 1   | 容量素子     |    |

| 1 1 3 2   | 容量素子     | 50 |

|         |            |    |

|---------|------------|----|

| 1 1 5 1 | 端子         |    |

| 1 1 5 2 | 端子         |    |

| 2 6 0 0 | TFT 基板     |    |

| 2 6 0 1 | 対向基板       |    |

| 2 6 0 2 | シール材       |    |

| 2 6 0 3 | 画素部        |    |

| 2 6 0 4 | 表示素子       |    |

| 2 6 0 5 | 着色層        |    |

| 2 6 0 6 | 偏光板        |    |

| 2 6 0 7 | 偏光板        | 10 |

| 2 6 0 8 | 配線回路部      |    |

| 2 6 0 9 | フレキシブル配線基板 |    |

| 2 6 1 0 | 冷陰極管       |    |

| 2 6 1 1 | 反射板        |    |

| 2 6 1 2 | 回路基板       |    |

| 2 6 1 3 | 拡散板        |    |

| 2 7 0 0 | 電子書籍       |    |

| 2 7 0 1 | 筐体         |    |

| 2 7 0 3 | 筐体         |    |

| 2 7 0 5 | 表示部        | 20 |

| 2 7 0 7 | 表示部        |    |

| 2 7 1 1 | 軸部         |    |

| 2 7 2 1 | 電源         |    |

| 2 7 2 3 | 操作キー       |    |

| 2 7 2 5 | スピーカ       |    |

| 5 0 3 1 | 走査線        |    |

| 5 0 3 2 | 信号線        |    |

| 5 0 4 1 | 信号線        |    |

| 5 0 5 1 | 画素         |    |

| 6 0 0 0 | シール材       | 30 |

| 6 0 0 1 | 基板         |    |

| 6 0 0 2 | 画素部        |    |

| 6 0 0 3 | 信号線駆動回路    |    |

| 6 0 0 4 | 走査線駆動回路    |    |

| 6 0 0 5 | シール材       |    |

| 6 0 0 6 | 基板         |    |

| 6 0 0 8 | 液晶層        |    |

| 6 0 1 0 | TFT        |    |

| 6 0 1 1 | TFT        |    |

| 6 0 1 3 | 液晶素子       | 40 |

| 6 0 1 5 | 接続端子電極     |    |

| 6 0 1 6 | 端子電極       |    |

| 6 0 1 8 | FPC        |    |

| 6 0 1 9 | 異方性導電膜     |    |

| 6 0 2 0 | 絶縁層        |    |

| 6 0 2 1 | 絶縁層        |    |

| 6 0 3 0 | 画素電極       |    |

| 6 0 3 1 | 対向電極       |    |

| 6 0 3 2 | 絶縁層        |    |

| 6 0 3 5 | スペーサ       | 50 |

|           |             |    |

|-----------|-------------|----|

| 6 0 5 0   | 半導体層        |    |

| 6 5 0 1   | 基板          |    |

| 6 5 0 2   | 画素部         |    |

| 6 5 0 3 a | 信号線駆動回路     |    |

| 6 5 0 4 a | 走査線駆動回路     |    |

| 6 5 0 5   | シール材        |    |

| 6 5 0 6   | 基板          |    |

| 6 5 0 7   | 充填材         |    |

| 6 5 0 9   | TFT         |    |

| 6 5 1 0   | TFT         | 10 |

| 6 5 1 1   | 発光素子        |    |

| 6 5 1 2   | 電界発光層       |    |

| 6 5 1 3   | 電極          |    |

| 6 5 1 5   | 接続端子電極      |    |

| 6 5 1 6   | 端子電極        |    |

| 6 5 1 7   | 電極          |    |

| 6 5 1 8 a | FPC         |    |

| 6 5 1 9   | 異方性導電膜      |    |

| 6 5 2 0   | 隔壁          |    |

| 6 5 5 0   | 半導体層        | 20 |

| 6 5 5 1   | 絶縁層         |    |

| 6 5 5 2   | 絶縁層         |    |

| 9 0 0 0   | 携帯電話機       |    |

| 9 0 0 1   | 筐体          |    |

| 9 0 0 2   | 表示部         |    |

| 9 0 0 3   | 操作ボタン       |    |

| 9 0 0 4   | 外部接続ポート     |    |

| 9 0 0 5   | スピーカ        |    |

| 9 0 0 6   | マイク         |    |

| 9 0 3 2   | 半導体層        | 30 |

| 9 4 0 0   | 通信装置        |    |

| 9 4 0 1   | 筐体          |    |

| 9 4 0 2   | 操作ボタン       |    |

| 9 4 0 3   | 外部入力端子      |    |

| 9 4 0 4   | マイク         |    |

| 9 4 0 5   | スピーカ        |    |

| 9 4 0 6   | 発光部         |    |

| 9 4 1 0   | 表示装置        |    |

| 9 4 1 1   | 筐体          |    |

| 9 4 1 2   | 表示部         | 40 |

| 9 4 1 3   | 操作ボタン       |    |

| 9 6 0 0   | テレビジョン装置    |    |

| 9 6 0 1   | 筐体          |    |

| 9 6 0 3   | 表示部         |    |

| 9 6 0 5   | スタンド        |    |

| 9 6 0 7   | 表示部         |    |

| 9 6 0 9   | 操作キー        |    |

| 9 6 1 0   | リモコン操作機     |    |

| 9 7 0 0   | デジタルフォトフレーム |    |

| 9 7 0 1   | 筐体          | 50 |

|         |           |    |

|---------|-----------|----|

| 9 7 0 3 | 表示部       |    |

| 9 8 8 1 | 筐体        |    |

| 9 8 8 2 | 表示部       |    |

| 9 8 8 3 | 表示部       |    |

| 9 8 8 4 | スピーカ部     |    |

| 9 8 8 5 | 操作キー      |    |

| 9 8 8 6 | 記録媒体挿入部   |    |

| 9 8 8 7 | 接続端子      |    |

| 9 8 8 8 | センサ       |    |

| 9 8 8 9 | マイクロフォン   | 10 |

| 9 8 9 0 | L E D ランプ |    |

| 9 8 9 1 | 筐体        |    |

| 9 8 9 3 | 連結部       |    |

| 9 9 0 0 | スロットマシン   |    |

| 9 9 0 1 | 筐体        |    |

| 9 9 0 3 | 表示部       |    |

【図 1】

(A)

(B)

【図 2】

(A)

(B)

【図3】

(A)

(B)

【図4】

(A)

(B)

【図5】

(A)

(B)

【図6】

(A)

(B)

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図15】

(A)

(B)

【図16】

(A)

(B)

【図17】

【図19】

(A)

【図18】

(A)

(B)

(B)

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

(A)

【図29】

(A)

(B)

(B)

【図30】

(A)

(B)

---

フロントページの続き

(51)Int.Cl. F I

G 09 F 9/30 (2006.01)

(56)参考文献 特開2007-036216 (JP, A)

特開2006-237447 (JP, A)

特開2008-033905 (JP, A)

特開2009-049399 (JP, A)

特開2007-293072 (JP, A)

特開2009-033145 (JP, A)

特開平07-092500 (JP, A)

特開2007-041571 (JP, A)

特開2007-134482 (JP, A)

特開2007-266252 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| G 02 F | 1 / 136  |

| G 09 F | 9 / 30   |

| H 01 L | 21 / 336 |

| H 01 L | 21 / 822 |

| H 01 L | 27 / 04  |

| H 01 L | 29 / 786 |