(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3659103号

(P3659103)

(45) 発行日 平成17年6月15日(2005.6.15)

(24) 登録日 平成17年3月25日(2005.3.25)

(51) Int.CI.<sup>7</sup>

F 1

|             |               |             |              |                |

|-------------|---------------|-------------|--------------|----------------|

| <b>G09G</b> | <b>3/36</b>   | <b>G09G</b> | <b>3/36</b>  |                |

| <b>G02F</b> | <b>1/1365</b> | <b>G09G</b> | <b>3/20</b>  | <b>6 1 1 A</b> |

| <b>G09G</b> | <b>3/20</b>   | <b>G09G</b> | <b>3/20</b>  | <b>6 2 1 A</b> |

|             |               | <b>GO2F</b> | <b>1/136</b> | <b>5 0 5</b>   |

請求項の数 9 (全 19 頁)

(21) 出願番号

特願平11-375304

(22) 出願日

平成11年12月28日(1999.12.28)

(65) 公開番号

特開2001-188519(P2001-188519A)

(43) 公開日

平成13年7月10日(2001.7.10)

審査請求日

平成15年7月3日(2003.7.3)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 小澤 德郎

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 濱本 穎広

(56) 参考文献 特開平08-328515 (JP, A)

特開平10-054998 (JP, A)

最終頁に続く

(54) 【発明の名称】電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のデータ線と、複数の走査線と、前記走査線と前記データ線との交差に対応する複数の画素と、各走査線に対応する複数の信号供給線とを備えた電気光学装置の駆動方法であって、

前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、

前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを有した各画素に対して

10

、

前記各走査線を順次選択する各走査信号を各々供給し、

前記各走査信号がアクティブになると、これに同期して基準信号を前記各信号供給線に順次供給し、

画像データの指示する階調値に応じた期間だけアクティブとなるパルス幅変調信号を各データ線に各々供給し、

前記画素は、当該画素に対応する走査線とデータ線とが同時にアクティブとなる期間では、当該画素に対応する信号供給線から前記基準信号を取り込み、当該画素に対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、取り込んだ前記基準信号に基づく電圧を保持する

20

ことを特徴とする電気光学装置の駆動方法。

**【請求項 2】**

一対の基板間に電気光学物質を挟持してなる電気光学装置において、

複数のデータ線と、

複数の走査線と、

前記走査線と前記データ線との交差に対応して設けられた複数の画素と、

各走査線に対応する複数の信号供給線と、

前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、

選択された信号供給線に基準信号を供給する信号供給手段と、を有し、

前記画素は、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線

にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、

前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ

素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、

前記画素電極にドレイン電極が接続される第2トランジスタ素子と、を有し、

前記走査線と前記データ線との交差に対応して各々設けられ、対応する走査線とデータ

線とが同時にアクティブとなる期間では前記信号供給線から前記基準信号を取り込み、対

応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、取り込ん

だ前記基準信号に基づく電圧を保持することを特徴とする電気光学装置。

**【請求項 3】**

前記信号供給手段は、

前記各信号供給線毎に設けられ、前記信号供給線の一端が一方の端子に接続され、対応

する走査線の信号によってオン・オフが制御されるスイッチング素子と、

前記各スイッチング素子の他方の端子に各々接続されるともに前記基準信号が供給され

る共通信号線と

を備えることを特徴とする請求項2に記載の電気光学装置。

**【請求項 4】**

請求項2に記載の電気光学装置を駆動する電気光学装置の駆動回路であって、

前記基準信号を発生する基準信号発生手段と、

画像データを線順次データに変換する変換手段と、

前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し

前記データ線に出力するパルス幅変調手段と、

前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線

駆動手段と

を備えることを特徴とする電気光学装置の駆動回路。

**【請求項 5】**

請求項4に記載の電気光学装置を駆動する電気光学装置の駆動回路であって、

前記各走査信号のローレベル電位を、前記パルス幅変調信号のローレベル電位より前記

第2トランジスタの閾値電圧だけ高電位に設定することを特徴とする電気光学装置の駆動

回路。

**【請求項 6】**

前記パルス幅変調手段は、前記パルス幅変調信号のハイレベル電位が、前記基準信号の

最大電位より少なくとも前記第2トランジスタ素子の閾値電圧だけは高くなるように前記

パルス幅変調信号を生成し、

前記走査線駆動手段は、前記走査信号のハイレベル電位が、前記パルス幅変調信号のハ

イレベル電位より少なくとも前記第1トランジスタ素子の閾値電圧だけは高くなるように

前記走査信号を生成する

ことを特徴とする請求項4に記載の電気光学装置の駆動回路。

**【請求項 7】**

前記基準信号は、ランプ波信号であることを特徴とする請求項4乃至6のいずれか1項

に記載の電気光学装置の駆動回路。

10

20

30

40

50

**【請求項 8】**

請求項 6 に記載の駆動回路を、前記一方の基板に形成したことを特徴とする請求項 2 に記載の電気光学装置。

**【請求項 9】**

請求項 8 に記載の電気光学装置を備えたとことを特徴とする電子機器。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、低消費電力な電気光学装置、電気光学装置の駆動回路および駆動方法、この電気光学装置を表示部に用いた電子機器に関する。 10

**【0002】****【従来の技術】**

従来の電気光学装置、例えば、液晶装置の駆動回路は、画像表示領域に配線されたデータ線や走査線などに、画像信号や走査信号などを所定タイミングで供給するためのデータ線駆動回路や、走査線駆動回路などから構成されている。

**【0003】**

このデータ線駆動回路の構成は、入力画像信号がアナログ信号あるいはデジタル信号かで大きく相違する。しかし、複数の階調表示を行う場合には、入力画像信号の形態に拘わらず、液晶にアナログ信号の電圧を印加する必要がある。したがって、入力画像信号がデジタル信号である場合には、入力画像信号に D A 変換を施して液晶にアナログ信号電圧を印加しなければならない。 20

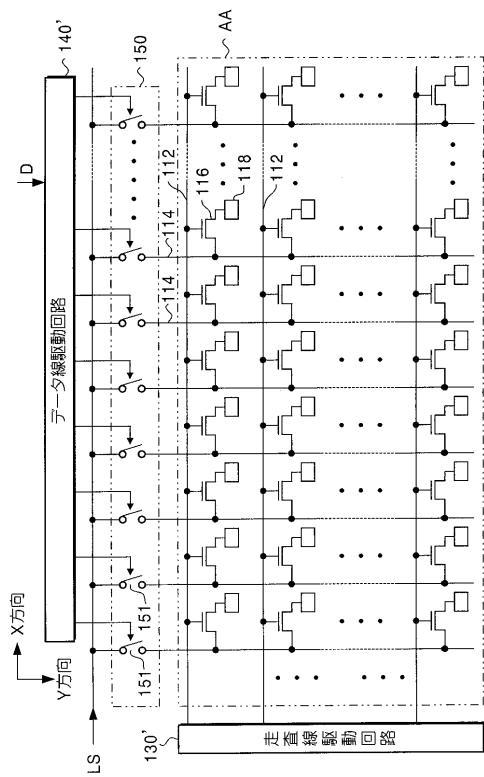

**【0004】**

この D A 変換の一手法として、P W M ( Pulse Width Modulation ) 法が知られている。図 12 は、P W M 法を適用した液晶装置の構成を示すブロック図である。この図に示すように従来の液晶装置は、データ線駆動回路 130'、走査線駆動回路 140'、スイッチ群 150、および画像表示領域 A A から構成されている。

**【0005】**

画像表示領域 A A においては、X 方向に沿って平行に複数本の走査線 112 が配列して形成され、また、これと直交する Y 方向に沿って平行に複数本のデータ線 114 が形成されている。そして、これらの走査線 112 とデータ線 114 の各交点においては、各画素を制御するためのスイッチたる薄膜トランジスタ (Thin Film Transistor: 以下 T F T と称する。) が設けられている。 30

**【0006】**

この例では、T F T 116 のゲート電極が走査線 112 に接続される一方、T F T 116 のソース電極がデータ線 114 に接続されるとともに、T F T 116 のドレン電極が画素電極 118 に接続されている。そして、各画素は、画素電極 118 と、対向基板に形成された共通電極と、これら両電極間に挟持された液晶とによって構成される結果、走査線 112 とデータ線 114 の各交点に対応して、マトリクス状に配列することとなる。なお、各データ線 114 は、液晶を介して共通電極と対向しており、また各走査線 112 と交差しているため各データ線 114 には寄生容量が付随する。 40

**【0007】**

データ線駆動回路 140' は、入力画像データ D に基づいて、各データ線 114 に対応した選択信号を線順次で出力する。各選択信号がアクティブとなる期間は、当該選択信号に対応する画素に表示すべき入力画像データ値に応じて定める。スイッチ群 150 を構成する各スイッチ 151 の入力端子には、ランプ波信号 L S が供給され、その出力端子は各データ線 114 と接続されており、その制御端子には各選択信号が供給されている。各スイッチ 151 は各選択信号がアクティブの期間中、オン状態となるように構成されている。したがって、各データ線 114 には、画素に表示すべき入力画像データ値に応じた期間だけ、ランプ波信号 L S が供給されることになる。この結果、各データ線 114 の寄生容量には、入力画像データ値に応じた期間だけランプ波信号が書き込まれることになる。一方 50

、走査線駆動回路 130'は、各水平走査期間毎にアクティブとなる走査信号を生成し、各走査信号を各走査線 112 に各々出力している。

#### 【0008】

以上の構成において、ある走査線 112 が走査信号によって選択されると、当該水平走査期間においては、当該走査線 112 に接続された各 TFT 116 がオン状態となる。このとき、各データ線 114 の寄生容量には、入力画像データ値に応じた期間だけランプ波信号 LS が書き込まれるので、画素電極 118 には入力画像データ値に応じた電圧が印加され、TFT 116 がオフ状態になると印加電圧が保持されることになる。これにより、入力画像データの指示する階調値に応じた階調を表示することが可能となる。

#### 【0009】

ところで、上述した液晶装置では、ランプ波信号 LS を各データ線 114 の寄生容量に書き込み、寄生容量の電圧を TFT 116 を介して各画素に取り込むようになっている。このため、ランプ波信号 LS の駆動回路は、寄生容量に対して書き込みが十分行えるだけの駆動能力を有する必要がある。

#### 【0010】

しかしながら、画像表示領域 AA が比較的小型のものであっても、データ線 114 の寄生容量値は 1 本当たり 20PF 程度はある。いわゆる XGA (1024 画素 × 768 画素) 形式の液晶装置では、R, G, B 各色毎に、1024 本のデータ線を備えるので、データ線 114 の寄生容量値の合計は約 61nF となってしまう。ここで、入力画像データが 6 ビットであるとすれば、61nF の容量に対して 1/64H 期間に充電を完了する必要がある。したがって、ランプ波信号 LS の駆動回路としては、大きな負荷を駆動できるものを使用しなければならず、回路規模が増大するといった問題があった。さらに、大きな負荷を駆動するため、駆動回路の消費電力が増大するといった問題があった。

#### 【0011】

本発明は、上述した事情に鑑みてなされたもので、その目的とするところは、駆動負荷を軽減した電気光学装置、その駆動回路、並びに、この電気光学装置を表示部に用いた電子機器を提供することにある。

#### 【0012】

**【課題を解決するための手段】**

上記目的を達成するため本発明に係る電気光学装置の駆動方法にあっては、複数のデータ線と、複数の走査線と、前記走査線と前記データ線との交差に対応する各画素電極と、各走査線に対応する複数の信号供給線とを備えた電気光学装置を駆動することを前提とし、前記各走査線を順次選択する各走査信号を各々供給し、前記各走査信号がアクティブになると、これに同期して基準信号を前記各信号供給線に順次供給し、画像データの指示する階調値に応じた期間だけアクティブとなるパルス幅変調信号を各データ線に各々供給し、前記各走査線と前記各データ線との交差に対応した各画素において、当該画素に対応する走査線とデータ線とが同時にアクティブとなる期間では、当該画素に対応する信号供給線から前記基準信号を取り込んで前記画素電極に印加する一方、当該画素に対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、前記画素電極の電圧を保持することを特徴とする。

#### 【0013】

この発明によれば、基準信号は、各走査信号がアクティブになると、これに同期して各信号供給線に順次供給されることになる。したがって、基準信号を駆動する駆動回路の負荷は、1 本の信号供給線に付随する寄生容量となるので、負荷を軽減することができる。この結果、基準信号を供給する工程において、消費電流を大幅に削減することができる。

#### 【0014】

次に、本発明に係る電気光学装置は、一対の基板間に電気光学物質を狭持してなることを前提とし、一方の基板上に、複数のデータ線と、複数の走査線と、前記走査線と前記データ線とが複数組含まれる。

10

20

30

40

50

タ線との交差に対応して設けられた複数の画素電極と、各走査線に対応する複数の信号供給線と、前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、選択された信号供給線に基準信号を供給する信号供給手段と、前記走査線と前記データ線との交差に対応して各々設けられ、対応する走査線とデータ線とが同時にアクティブとなる期間では前記信号供給線から前記基準信号を取り込んで前記画素電極に印加する一方、対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、前記画素電極の電圧を保持する電圧保持手段とを備えたことを特徴とする。

#### 【0015】

この発明によれば、信号供給手段は、前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、選択された信号供給線に基準信号を供給する。一方、各走査線は順次選択されるようになっている。このため、基準信号が供給される信号供給線は1本である。したがって、基準信号を駆動する駆動回路の負荷は、1本の信号供給線に付随する寄生容量となるので、負荷を大幅に軽減することができる。さらに、駆動回路の回路構成を簡易なものにすることができる、くわえて、駆動回路の消費電流を大幅に削減することが可能となる。

10

#### 【0016】

ここで、前記信号供給手段は、前記各信号供給線毎に設けられ、前記信号供給線の一端が一方の端子に接続され、対応する走査線の信号によってオン・オフが制御されるスイッチング素子と、前記各スイッチング素子の他方の端子に各々接続されるともに前記基準信号が供給される共通信号線とを備えることが好ましい。この発明では、スイッチング素子を走査線の信号によってオン・オフさせることができるので、選択しようとしている走査線に対応する信号供給線のみに基準信号を供給することが可能となる。

20

#### 【0017】

また、前記電圧保持手段は、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えることが望ましい。

#### 【0018】

30

この発明では、第1トランジスタ素子と第2トランジスタ素子がゲート線と走査線の電圧によって制御され、第1および第2トランジスタ素子が同時にオン状態となった時に、信号供給線の電圧が画素電極に印加される。ここで、信号供給線には対応する走査線が選択された場合に基準信号が供給されるので、第1および第2トランジスタ素子が同時にオン状態になると、基準信号が画素電極に印加される。これにより、画像データの階調値に応じた階調表示が可能となる。くわえて、データ線は第1トランジスタ素子のソース電極に接続されるので、データ線に付随する寄生容量の値を小さくすることができ、これにより、データ線を駆動する駆動回路の負荷を減らし消費電流を削減することができる。

#### 【0019】

40

また、前記電圧保持手段は、前記走査線と前記データ線との交差に対応して各々設けられ、前記データ線にゲート電極が接続され、前記信号供給線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がソース電極に接続され、前記走査線にゲート電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えるものであってもよい。この発明では、第1および第2トランジスタ素子が同時にオン状態となった時に、信号供給線の電圧が画素電極に印加される。ここで、信号供給線には対応する走査線が選択された場合に基準信号が供給されるので、第1および第2トランジスタ素子が同時にオン状態になると、基準信号が画素電極に印加される。これにより、画像データの階調値に応じた階調表示が可能となる。

#### 【0020】

50

次に、本発明に係る電気光学装置の駆動回路にあっては、前記基準信号を発生する基準信号発生手段と、画像データを線順次データに変換する変換手段と、前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し前記データ線に出力するパルス幅変調手段と、前記基準信号を発生する基準信号発生手段と、前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線駆動手段とを備えることを特徴とする。この発明によれば、パルス幅変調信号を各データ線に線順次で供給するとともに走査信号を生成する一方、基準信号を生成するから、電気光学装置を駆動して階調表示を行わせることができる。

#### 【0021】

また、本発明に係る電気光学装置の駆動回路にあっては、電気光学装置が、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えることを前提とし、前記基準信号を発生する基準信号発生手段と、画像データを線順次データに変換する変換手段と、前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し前記データ線に出力するパルス幅変調手段と、前記基準信号を発生する基準信号発生手段と、前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線駆動手段とを備え、前記各走査信号のローレベル電位を、前記パルス幅変調信号のローレベル電位より約前記第2トランジスタの閾値電圧だけ高電位に設定することを特徴とする。

#### 【0022】

この発明によれば、各走査信号のローレベル電位を、パルス幅変調信号のローレベル電位より約第2トランジスタの閾値電圧だけ高電位に設定したので、走査線の非選択期間において当該走査線に対応する第1トランジスタ素子をオン状態とオフ状態の境界で動作させることができ、第2トランジスタ素子のゲート電極がフローティング状態となることを回避できる。このため、第2トランジスタ素子を、走査線の非選択期間において確実にオフ状態とすることが可能となる。

#### 【0023】

くわえて、この電気光学装置の駆動回路において、前記パルス幅変調手段は、前記パルス幅変調信号のハイレベル電位が、前記基準信号の最大電位よりも前記第2トランジスタ素子の閾値電圧だけは高くなるように前記パルス幅変調信号を生成し、前記走査線駆動手段は、前記走査信号のハイレベル電位が、前記パルス幅変調信号のハイレベル電位よりも前記第1トランジスタ素子の閾値電圧だけは高くなるように前記走査信号を生成することが望ましい。この発明によれば、パルス幅変調信号がハイレベルの時に、第1トランジスタ素子と第2トランジスタ素子とを確実にオン状態にして基準信号を画素電極に印加することが可能となる。

#### 【0024】

また、前記基準信号は、ランプ波信号であることが好ましい。但し、基準信号を用いてガンマ補正を施す場合には、ガンマ補正カーブに従った基準信号を用いればよい。

#### 【0025】

さらに、上述した駆動回路を、電気光学装置の前記一方の基板に形成してもよい。この場合、駆動回路を構成するトランジスタ素子を前記第1および第2トランジスタ素子と同一の製造プロセスで作成することによって、製造コストを削減できる。

#### 【0026】

くわえて、上記目的を達成するために、本発明に係る電子機器にあっては、上記電気光学装置を備えることを特徴としているので、消費電力が削減される。

#### 【0027】

##### 【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して説明する。

10

20

20

30

40

50

**【0028】**

<第1実施形態>

まず、本発明の第1実施形態に係る電気光学装置について、電気光学材料として液晶を用いた液晶装置を例にとって説明する。

**【0029】**

<液晶装置の全体構成>

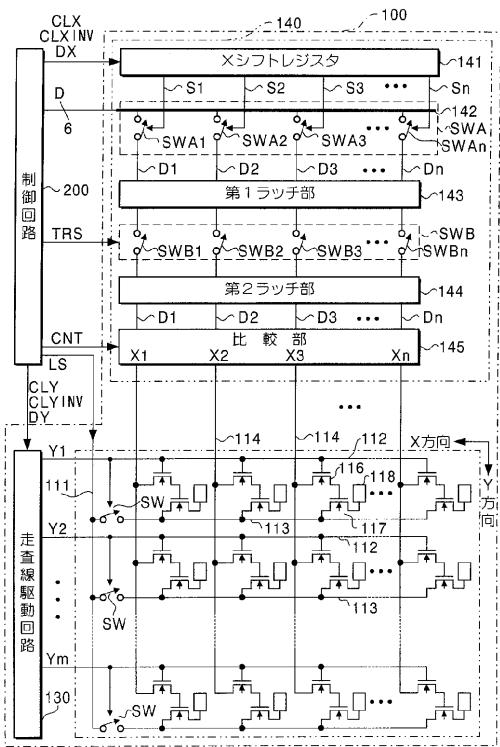

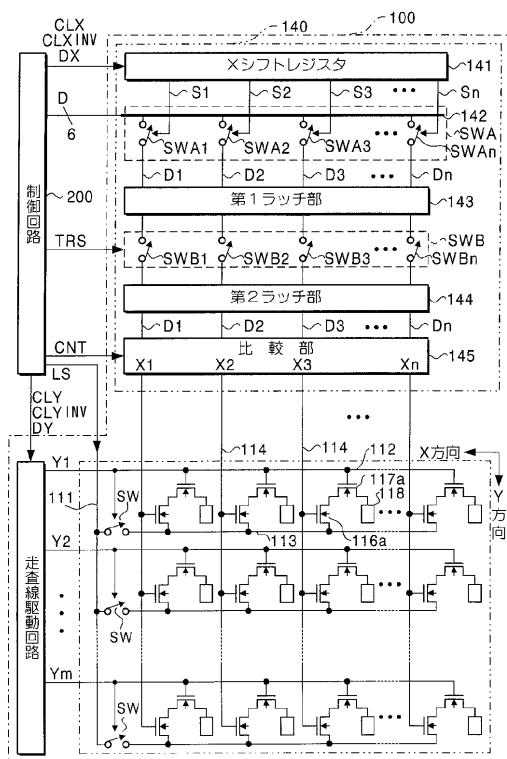

図1は、この液晶装置の電気的な構成を示すブロック図である。この図に示されるように、液晶装置は、液晶パネル100と制御回路200とを備える。このうち、制御回路200は、各部で使用されるタイミング信号や制御信号など（必要に応じて後述する）を出力するものである。10

**【0030】**

ここで、液晶パネル100は、後述するように、素子基板と対向基板とが互いに電極形成面を対向して貼付された構成となっている。そして、素子基板上に、走査線駆動回路130、データ線駆動回路140および画像表示領域AAが構成されている。以下、これらの構成について説明する。

**【0031】**

<画像表示領域の構成>

次に、画像表示領域AAの電気的な構成について説明する。素子基板にあっては、図1においてX方向に沿って平行に複数本（m本）の走査線112が配列して形成され、さらに、各走査線112に対応して複数本（m本）の信号供給線113が配列して形成されている。また、これと直交するY方向に沿って平行に複数本（n本）のデータ線114が形成されている。ここで、各画素は、画素電極118と、対向基板に形成された共通電極（後述）と、これら両電極間に挟持された液晶とによって構成される。各画素は、走査線112とデータ線114との各交点に対応して、マトリクス状に配列することとなる。なお、このほかに、蓄積容量（図示省略）が、各画素毎に、電気的にみて、画素電極118と共通電極とに挟持された液晶に対して並列に形成される構成としても良い。20

**【0032】**

走査線112とデータ線114との各交点においては、各画素を制御するためのスイッチたるTFT116およびTFT117が設けられている。TFT116のゲート電極は走査線112に接続される一方、TFT116のソース電極がデータ線114に接続されるとともに、TFT116のドレイン電極がTFT117のゲート電極に接続されている。また、TFT117のソース電極は信号供給線113に接続されるとともに、そのドレン電極は画素電極118と接続されている。したがって、TFT116とTFT117が同時にオン状態になると、信号供給線113の電圧が画素電極118に印加されることになる。30

**【0033】**

くわえて、各信号供給線113の一端は、各スイッチSWを介して共通信号線111と接続されている。この共通信号線111には、制御回路100から2H周期のランプ波信号LSが供給される。各スイッチSWは、対応する走査線112の電圧によって制御され、走査線112の走査信号Y1～Ymがアクティブとなる期間において、オン状態となるようになっている。40

**【0034】**

ここで、走査信号Y1～Ymは水平走査期間毎に順次アクティブとなる信号である。したがって、各スイッチSWのうちオン状態となるのは常に1個だけであるから、ランプ波信号LSの駆動回路は、1本の信号供給線113に接続されることになる。この結果、ランプ波信号LSの駆動回路の負荷は、主として1本の信号供給線113に付随する寄生容量となる。すなわち、上述した構成によれば、従来のようにY方向に延在する総てのデータ線114の寄生容量が負荷となるのではなく、X方向に延在する1本の信号供給線113に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができる。

**【0035】**

さて、走査線駆動回路 130 とデータ線駆動回路 140 は、後述するように、透明性および絶縁性を有するガラス等からなる素子基板の対向面にあって、表示領域の周辺部に形成されるものである。ここで、走査線駆動回路 130 とデータ線駆動回路 140 の構成素子は、画素を駆動する TFT116,117 と共に製造プロセスで形成される P チャネル型 TFT および N チャネル型 TFT を組み合わせて構成されるため、製造効率の向上や、製造コストの低下、素子特性の均一化などが図られている。

#### 【 0036 】

##### < データ線駆動回路の構成 >

次に、本実施形態に係るデータ線駆動回路 140 について説明する。データ線駆動回路 140 は、X シフトレジスタ 141、画像データ供給線 142、スイッチ群 SWA, SWB 10 、第 1 ラッチ部 143、第 2 ラッチ部 144、および比較部 145 から構成されている。

#### 【 0037 】

まず、X シフトレジスタ 141 は、水平走査期間の最初に供給される転送開始パルス DX を、クロック信号 CLX およびその反転クロック信号 CLX INV にしたがって順次シフトすることによって、各サンプリング信号 S1 ~ Sn を所定の順番で出力するよう構成されている。

#### 【 0038 】

次に、画像データ供給線 142 は、画像データをパラレル形式で供給するものである。画像データ D が 1 サンプル当たり j ビットであれば、画像データ供給線 142 は j 本の配線から構成される。なお、この例では、画像データ D は 1 サンプル当たり 6 ビットであり、画像データ供給線 142 は 6 本の配線で構成されているものとするが、例えば、画像データが“カラー”である場合には、画像データ供給線 142 の本数は 18 本 (= 6 (ビット幅) × 3 本 (R/G/B)) となる。

#### 【 0039 】

次に、スイッチ群 SWA は、n 個のスイッチ SWA1 ~ SWAn から構成されている。各スイッチ SWA1 ~ SWAn の入出力端子は、画像データ供給線 142 と第 1 ラッチ部 143 とに接続されており、さらに各スイッチ SWA1 ~ SWAn の制御端子にはサンプリング信号 S1 ~ Sn が供給されている。ここで、1 個のスイッチは、1 個のサンプリング信号によって 6 ビットの画像データを第 1 ラッチ部 143 に供給するか否かを制御できるようになっている。そして、各スイッチ SWA1 ~ SWAn は、サンプリング信号 S1 ~ Sn がアクティブの場合にオン状態となり、非アクティブの場合にオフ状態となる。

#### 【 0040 】

次に、第 1 ラッチ部 143 は、n 個のラッチ回路から構成されており、スイッチ群 SWA から供給される画像データ D1 ~ Dn をラッチする。これにより、画像データ D を点順次データに変換することができる。

#### 【 0041 】

次に、スイッチ群 SWB は、n 個のスイッチ SWB1 ~ SWBn から構成されている。各スイッチ SWB1 ~ SWBn の入出力端子は、第 1 ラッチ部 143 と第 2 ラッチ部 144 に接続されており、さらに各スイッチ SWB1 ~ SWBn の制御端子には転送信号 TRS が供給されている。そして、各スイッチ SWB1 ~ SWBn は、転送信号 TRS がアクティブの場合にオン状態となり、非アクティブの場合にオフ状態となる。ここで、転送信号 TRS は水平走査期間の終了時にアクティブとなる信号である。

#### 【 0042 】

次に、第 2 ラッチ部 144 は、n 個のラッチ回路から構成されており、スイッチ群 SWB から供給される画像データ D1 ~ Dn をラッチする。上述のように転送信号 TRS は水平走査期間の終了時にアクティブとなるので、第 2 ラッチ部 144 の各出力信号は、画像データ D を線順次データに変換したものとなる。すなわち、X シフトレジスタ 141、画像データ供給線 142、スイッチ群 SWA, SWB、第 1 ラッチ部 143、および第 2 ラッチ部 144 は、画像データ D を線順次データに変換する手段として機能する。

#### 【 0043 】

10

20

30

40

50

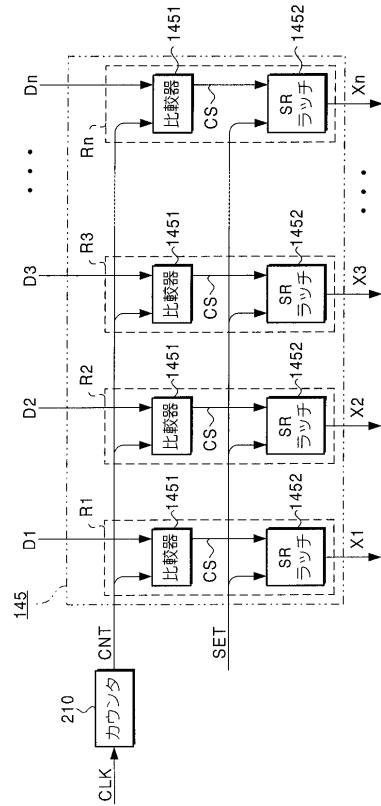

次に、比較部 145について説明する。図2は、比較部145とその周辺回路の構成を示すブロック図である。この図に示すように比較部145は、n個の単位回路R1～Rnから構成されている。各単位回路R1～Rnは、比較器1451とSRラッチ1452を備えている。また、制御部200にはカウンタ210が設けられおり、このカウンタ210は、水平走査期間の始まりからカウンタクロック信号CLKをカウントして、そのカウント結果を示すカウントデータCNTを生成し、比較部145に出力する。くわえて、制御部200は水平走査期間の始まりにおいてHレベルとなるセット信号SETを比較部145に出力する。

#### 【0044】

各単位回路R1～Rnにおいて、比較器1451は、画像データD1～DnとカウントデータCNTとを比較して、両者が一致する場合にHレベルとなる一方、不一致の場合にLレベルとなる比較信号CSを、SRラッチ1452のリセット端子に供給する。各単位回路R1～RnのSRラッチ1452は、セット端子に供給されるセット信号SETがHレベルになるとその論理レベルをHレベルに遷移させ、その後、比較信号CSがHレベルになるとその論理レベルをLレベルに遷移させて、PWM信号(パルス幅変調信号)X1～Xnを生成する。

#### 【0045】

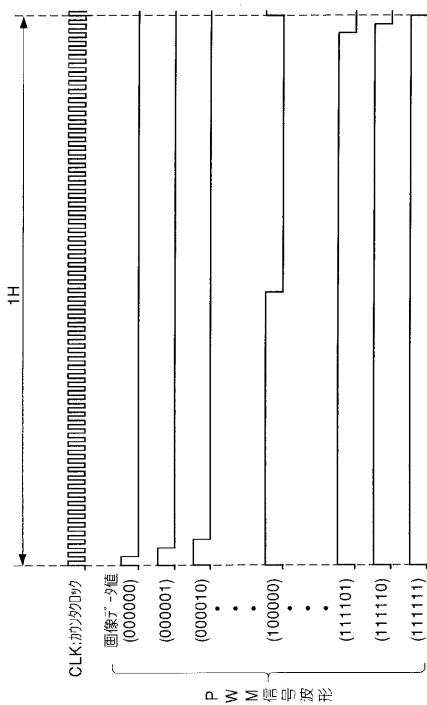

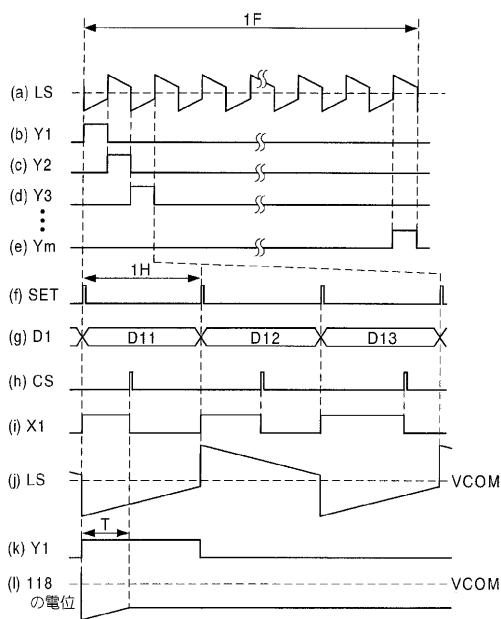

図3は、画像データの値とPWM信号の波形を示したタイミングチャートである。この図に示すように、各PWM信号のHレベル期間は、各画像データの指示する階調値に応じた期間となる。

#### 【0046】

このようにして得られたPWM信号X1～Xnは、データ線駆動回路140の各出力信号として、n本のデータ線114に各々供給される。なお、PWM信号X1～Xnは、SRラッチ1452の出力信号をレベルシフトして生成するようにしてもよい。

#### 【0047】

##### <走査線駆動回路の構成>

次に、走査線駆動回路130について説明する。走査線駆動回路130は、YSiftレジスタおよびレベルシフタ回路から構成されている。YSiftレジスタは、水平走査期間の最初に供給される転送開始パルスDYを、クロック信号CLYおよびその反転クロック信号CLYINVにしたがって順次シフトすることによって、信号y1～ymを所定の順番で出力するよう構成されている。レベルシフタ回路は、YSiftレジスタの各出力信号に所定の電圧だけレベルシフトを施すように構成されている。レベルシフタ回路の各出力信号は、走査信号Y1～Ymとしてm本の走査線に供給される。

#### 【0048】

##### <各種波形の関係>

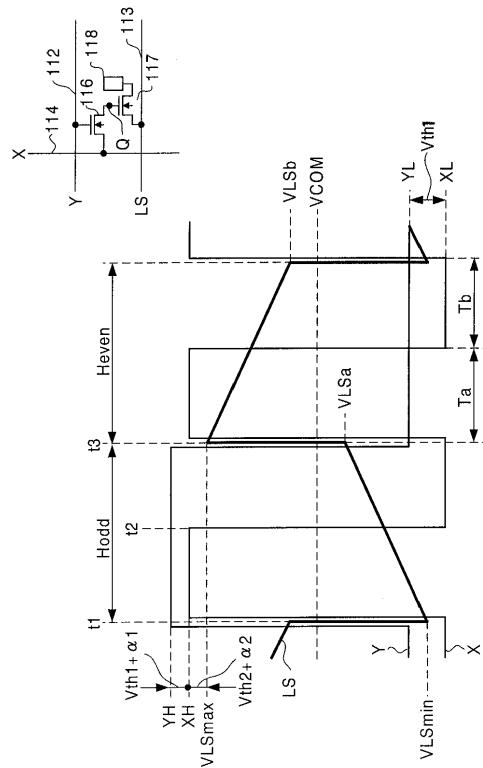

次に、上述したランプ波信号LS、PWM信号X1～Xn、走査信号Y1～Ymの電圧レベルについて説明する。図4は、1画素の周辺回路と各種信号の電圧レベルとの関係の一例を示す図である。なお、この図においてVCOMは対向電極の電位であり、Vth1はTFT116の閾値電圧、Vth2はTFT117の閾値電圧である。

#### 【0049】

この図に示すようにランプ波信号LSは、奇数番目の水平走査期間Hoddにおいて電位VLSminから電位VLSaまでの間を直線的に増加する一方、偶数番目の水平走査期間Hevenにおいては電位VLSmaxから電位VLSbまでの間を直線的に減少する。ここで、対向電極の電位VCOMと電位VLSaとの差分は電位VCOMと電位VLSbとの差分と略等しく、また、対向電極の電位VCOMと電位VLSmaxとの差分は電位VCOMと電位VLSminとの差分と略等しくなるように設定してある。奇数番目の水平走査期間Hoddと偶数番目の水平走査期間Hevenにおいて、ランプ波信号LSの波形を対向電極の電位VCOMを中心として極性反転させたのは、液晶に交流電圧を印加することにより、液晶の劣化を防止するためである。

#### 【0050】

なお、反転するか否かについては、一般には、1走査線112単位の極性反転である

10

20

30

40

50

か、 2 データ線 1 1 4 単位の極性反転であるか、 3 画素単位の極性反転であるか、 4 画面単位の極性反転であるかに応じて定められ、その反転周期は、 1 水平走査期間、 1 垂直走査期間またはドットクロック周期に設定される。ただし、本実施形態にあっては説明の便宜上、 1 走査線 1 1 2 単位の極性反転である場合を例にとって説明するが、本発明をこれに限定する趣旨ではない。

#### 【0051】

次に、走査信号 Y の H レベル電位 YH は、 PWM 信号 X の H レベル電位 XH より Vth1+ 1だけ高電位側に設定している。これは、 TFT 1 1 6において、ソース電極の電位が XH となつた場合にゲート電極の電位を XH + Vth1+ 1 にして、 TFT 1 1 6 を確実にオン状態にするためである。なお、 1 の値は 0 V ~ 5 V 程度である。

10

#### 【0052】

次に、 PWM 信号 X の H レベル電位 XH は、ランプ波信号 LS の最大電位 VLsmax より Vth2+ 2だけ高電位側に設定している。TFT 1 1 6 がオン状態になると、TFT 1 1 7 のゲート電極電位 Q は、TFT 1 1 6 のソース電極電位と等しくなる。一方、TFT 1 1 7 のソース電極電位の最大値は、信号供給線 1 1 3 にランプ波信号 LS が供給され VLsmax となつたときである。PWM 信号 X の H レベル電位 XH を、 VLsmax + Vth2+ 2としたのは、この場合にも、TFT 1 1 7 を確実にオン状態にして画素電極 1 1 8 に電位 VLsmax を印加するためである。なお、 2 の値は 0 V ~ 5 V 程度である。

#### 【0053】

この例では、時刻 t 1 から時刻 t 3 の期間において、走査信号 Y が H レベルとなり、 TFT 1 1 6 がオン状態となる。このため、当該期間に TFT 1 1 7 のゲート電極には PWM 信号 X が印加される。そして、 PWM 信号 X が H レベルとなる時刻 t 1 から時刻 t 2までの期間において、 TFT 1 1 7 がオン状態となり、画素電極 1 1 8 にランプ波信号 LS が印加される。すると、画素電極 1 1 8 を介して液晶に画像データ D の値に応じた電圧が印加されることになる。そして、時刻 t 2 に至ると、 PWM 信号 X が H レベルから L レベルに遷移するため、 TFT 1 1 7 はオフ状態となる。液晶は等価的に容量成分を有するので、 TFT 1 1 7 がオフ状態となっても電圧を保持する。これにより、画素は、画像データ D の階調値に応じた階調表示を行うことができる。

20

#### 【0054】

一方、走査信号 Y の L レベル電位 YL は、 PWM 信号 X の L レベル電位 XL より約 Vth1 だけ高電位側に設定している。これは、当該画素の非選択期間において、 TFT 1 1 7 のゲート電極がフローティングとなることを防止するためである。TFT 1 1 6 は、期間 Taにおいてはオフ状態となるが、期間 Tbにおいては、オン状態とオフ状態の境界にある。換言すれば、期間 Tbにおいては、高インピーダンスでソース電極とドレイン電極とが接続されている。ところで、 TFT 1 1 7 のゲート電極には、小さな値ではあるが浮遊容量が等価的に接続されている。このため、期間 Tb にあっては、この浮遊容量に電荷が充電されるので、期間 Taにおいて TFT 1 1 6 が完全にオフ状態になっても、 TFT 1 1 7 のゲート電極電位 Q は、非選択期間において電位 XL を維持する。したがって、非選択期間において TFT 1 1 7 は完全にオフ状態になるから、画素電極 1 1 8 と対向電極との間に蓄積された電荷が TFT 1 1 7 を介して漏れることがない。これにより、表示画像の品質を向上させることができる。

30

#### 【0055】

##### <第1実施形態の動作>

次に、上述した構成に係る液晶装置における動作について説明する。図 5 は、液晶装置の動作を説明するためのタイミングチャートである。走査線駆動回路 1 3 0 には、垂直走査期間の最初にパルス DY が供給され、クロック信号 CLY およびその反転クロック信号 CLYINV によって順次シフトされて、走査線 1 1 2 に走査信号 Y1, Y2, Y3, ..., YM が順次出力される。これにより、複数の走査線 1 1 2 が 1 本ずつ線順次に下方向に選択されることとなる。

#### 【0056】

40

一方、共通信号線 111 には、図 5 (a) に示すランプ波信号 LS が常に供給されており、各走査線 112 に対応して設けられた各スイッチ SW がオン状態になると、ランプ波信号 LS が信号供給線 113 に供給される。図 5 (b) ~ (e) に示すように走査信号 Y1, Y2, Y3, …, Ym は、アクティブとなる H レベル期間が重複しないので、各スイッチ SW は同時にオン状態となることがない。したがって、ランプ波信号 LS の駆動回路は、各スイッチ SW によって選択された 1 本の信号供給線 113 にのみ接続される。この結果、当該駆動回路の負荷は、共通信号線 111 に付随する寄生容量と 1 本の信号供給線 113 に付随する寄生容量の合計となる。

#### 【0057】

ところで、寄生容量は、共通信号線 111 や信号供給線 113 が形成される素子基板と液晶を介して対向する対向基板の対向電極との間、またはデータ線 114 との間に発生する。ここで、共通信号線 111 は、後述するシール材の部分（図 7 および図 8 参照）やあるいは走査線駆動回路 130 とともに素子基板の周辺部分に形成する。このため、共通信号線 111 の寄生容量値は信号供給線 113 の寄生容量値と比較して小さくなり、駆動回路の負荷は、主として 1 本の信号供給線 113 に付随する寄生容量によって定まる。

#### 【0058】

すなわち、本実施形態の液晶装置によれば、従来のように Y 方向に延在する全てのデータ線 114 の寄生容量が負荷となるのではなく、X 方向に延在する 1 本の信号供給線 113 に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができる。この結果、駆動回路の回路構成を簡易なものにすることができる、しかも消費電流を大幅に削減することが可能となる。

#### 【0059】

次に、図 1 に示す左上の画素に着目すると、当該画素の TFT116 のソース電極には、PWM 信号 X1（図 5 (i) 参照）が供給される。この PWM 信号 X1 は、以下のようにして生成される。

#### 【0060】

まず、第 2 ラッチ部 144 において図 5 (g) に示すように線順次の画像データ D1 が生成され、これが比較部 145 を構成する単位回路 R1 の比較器 1451 に供給される。

#### 【0061】

次に、比較器 1451 は画像データ D1 とカウントデータ CNT とを比較して両者が一致すると比較信号 CS の論理レベルを H レベルにする。上述したように SR ラッチ 1452 はセット信号 SET の立ち上がりエッジで出力信号を H レベルに遷移させるとともに比較信号 CS の立ち上がりエッジで出力信号を L レベルに遷移させるから、例えば、セット信号 SET と比較信号 CS が図 5 (f), (h) に示すものであるとすれば、PWM 信号 X1 は図 5 (i) に示すものとなる。ここで、PWM 信号 X1 の H レベル期間は、画像データ D11, D12, D13…に応じた期間となる。換言すれば、PWM 信号 X1 は、画像データ D1 の指示する階調値に応じてパルス幅が変調されたパルス幅変調信号である。

#### 【0062】

図 5 (k) に示す期間 T では走査信号 Y1 と PWM 信号 X1 がともに H レベルとなるから、図 1 に示す左上の画素の TFT116 と TFT117 は、期間 T において同時にオン状態になる。すると、図 5 (j) に示すランプ波信号 LS が TFT117 を介して画素電極 118 に印加される。そして、期間 T を過ぎると、TFT117 はオフ状態となる。このため、画素電極 118 の電位は、図 5 (l) に示すように期間 T を経過した後には一定電位が維持されることになる。これにより、画像データ D11 の階調値に応じた電圧 V11 が液晶に印加され、階調表示が行われる。

#### 【0063】

このように、本実施形態においては、ランプ波信号 LS を 1 本の信号供給線 113 にのみ供給するようにしたので、液晶装置の消費電流を大幅に削減することができる。くわえて、走査線 112 が非選択となる期間にあっては、TFT116 をオン状態とオフ状態の境界で動作させるようにしたので、TFT117 を確実にオフさせることができ、表示画像

10

20

50

30

40

50

の品質を向上させることが可能となる。

**【0064】**

<第2実施形態>

上述した第1実施形態にあっては、TFT116のゲート電極を走査線112に接続し、そのソース電極をデータ線114に接続し、そのドレイン電極をTFT117のゲート電極に接続するとともに、TFT117のソース電極を信号供給線113に接続し、そのドレイン電極を画素電極118に接続した。そして、第1実施形態の液晶装置は、スイッチSWを介してランプ波信号LSを信号供給線113に供給することによって、ランプ波信号LSの駆動回路の負荷を軽減するものであった。本発明は、これ以外の構成でも負荷を軽減して駆動回路の消費電流を減少させることができるのである。そこで、第1実施形態とは異なる第2実施形態について説明する。10

**【0065】**

図6は、第2実施形態に係る液晶装置のブロック図である。第2実施形態の液晶装置は、1画素に対応するTFTの構成を除いて、図1に示す第1実施形態の液晶装置と同様に構成されている。図6において、走査線112とデータ線114との各交点においては、各画素を制御するためのスイッチたるTFT116aおよびTFT117aが設けられている。TFT116aのゲート電極はデータ線114に接続される一方、TFT116aのソース電極が信号供給線113に接続されるとともに、TFT116aのドレイン電極がTFT117aのソース電極に接続されている。また、TFT117aのゲート電極は走査線112に接続されるとともに、そのドレイン電極は画素電極118と接続されている。20したがって、TFT116aとTFT117aが同時にオン状態になると、信号供給線113の電圧が画素電極118に印加されることになる。

**【0066】**

この例では、TFT116aとTFT117aの各ゲート電極が、データ線114と走査線112に各々接続されているので、第1実施形態のようにTFT117がフローティング状態となることを回避するためにPWM信号Xおよび走査信号Yの論理レベルについて対策を講じる必要はない。

**【0067】**

ところで、一般に、TFTのゲート電極は、CMOS構造の電界効果トランジスタと同様に、半導体層の上に極薄い酸化絶縁膜を形成し、この酸化絶縁膜の上にアルミニウム等で電極を設けることによって形成される。一方、ソース電極やドレイン電極は半導体層と直接接続されている。このため、ゲート電極は酸化絶縁膜を介して半導体層と容量結合している。したがって、ゲート容量値はソース容量値よりも大きいといえる。30

**【0068】**

第2実施形態の液晶装置では、データ線114にTFT116aのゲート電極が接続されているから、第1実施形態の液晶装置はデータ線114の寄生容量値が第2実施形態の液晶装置に比較して小さくなるという点で、有利である。

**【0069】**

しかしながら、第2実施形態の液晶装置においても、各走査線112に対応して設けられた各スイッチSWが同時にオン状態になることはないから、ランプ波信号LSの駆動回路は、各スイッチSWによって選択された1本の信号供給線113にのみ接続される。したがって、当該駆動回路の負荷は、主として1本の信号供給線113に付随する寄生容量によって定まる。40

**【0070】**

この結果、第2実施形態の液晶装置によれば、第1実施形態の液晶装置と同様に、X方向に延在する1本の信号供給線113に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができ、駆動回路の回路構成を簡易なものにすることができる、しかも消費電流を大幅に削減することができる。

**【0071】**

<液晶パネルの構成例>

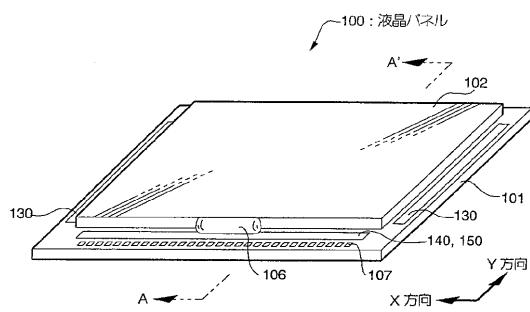

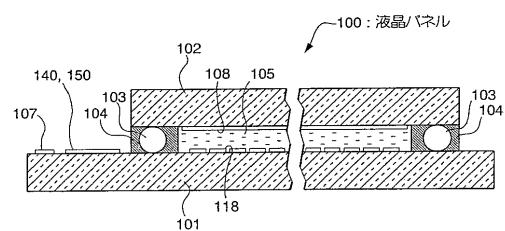

次に、上述した各実施形態に係るデータ線駆動回路 140 を有する液晶パネル 100 の全体構成について図 7 および図 8 を参照して説明する。ここで、図 11 は、液晶パネル 100 の構成を示す斜視図であり、図 8 は、図 7 における A-A' 線の断面図である。

#### 【0072】

これらの図に示されるように、液晶パネル 100 は、画素電極 118 等が形成されたガラスや、半導体、石英などの素子基板 101 と、共通電極 108 等が形成されたガラスなどの透明な対向基板 102 とが、スペーサ 103 の混入されたシール材 104 によって一定の間隙を保って、互いに電極形成面が対向するように貼り合わせられるとともに、この間隙に電気光学材料としての液晶 105 が封入された構造となっている。なお、シール材 104 は、対向基板 102 の基板周辺に沿って形成されるが、液晶 105 を封入するために一部が開口している。このため、液晶 105 の封入後に、その開口部分が封止材 106 によって封止されている。10

#### 【0073】

ここで、素子基板 101 の対向面であって、シール材 104 の外側一辺においては、上述したデータ線駆動回路 140 およびサンプリング回路 150 が形成されて、Y 方向に延在するデータ線 114 を駆動する構成となっている。さらに、この一辺には複数の外部回路接続端子 107 が形成されて、制御回路 200 からの各種信号を入力する構成となっている。また、この一辺に隣接する 2 辺には、2 個の走査線駆動回路 130 が形成されて、X 方向に延在する走査線 112 をそれぞれ両側から駆動する構成となっている。なお、走査線 112 に供給される走査信号の遅延が問題にならないのであれば、走査線駆動回路 130 を片側 1 個だけに形成する構成でも良い。20

#### 【0074】

一方、対向基板 102 の共通電極 108 は、素子基板 101 との貼合部分における 4 隅のうち、少なくとも 1 箇所において設けられた導通材によって、素子基板 101 との電気的導通が図られている。ほかに、対向基板 102 には、液晶パネル 100 の用途に応じて、例えば、第 1 に、ストライプ状や、モザイク状、トライアングル状等に配列したカラーフィルタが設けられ、第 2 に、例えば、クロムやニッケルなどの金属材料や、カーボンやチタンなどをフォトレジストに分散した樹脂ブラックなどの遮光膜が設けられ、第 3 に、液晶パネル 100 に光を照射するバックライトが設けられる。なお、色光変調の用途の場合には、カラーフィルタは形成されずに遮光膜が対向基板 102 に設けられる。30

#### 【0075】

くわえて、素子基板 101 および対向基板 102 の対向面には、それぞれ所定の方向にラビング処理された配向膜（図示省略）などが設けられる一方、その各背面側には配向方向に応じた偏光板（図示省略）がそれぞれ設けられる。ただし、液晶 105 として、高分子中に微小粒として分散させた高分子分散型液晶を用いれば、前述の配向膜や偏光板などが必要となる結果、光利用効率が高まるので、高輝度化や低消費電力化などの点において有利である。

#### 【0076】

なお、走査線駆動回路 130 やデータ線駆動回路 140 等の周辺回路の一部または全部を、素子基板 101 に形成する替わりに、例えば、TAB (Tape Automated Bonding) 技術を用いてフィルムに実装された駆動用 IC チップを、素子基板 101 の所定位置に設けられる異方性導電フィルムを介して電気的および機械的に接続する構成としても良いし、駆動用 IC チップ自体を、COG (Chip On Glass) 技術を用いて、素子基板 101 の所定位置に異方性導電フィルムを介して電気的および機械的に接続する構成としても良い。40

#### 【0077】

##### <素子基板の構成など>

また、各実施形態においては、液晶パネル 100 の素子基板 101 をガラス等の透明な絶縁性基板により構成して、当該基板上にシリコン薄膜を形成するとともに、当該薄膜上にソース、ドレイン、チャネルが形成された TFT によって、画素のスイッチング素子 (TFT 116)、走査線駆動回路 130、データ線駆動回路 140 の素子を構成するものと50

して説明したが、本発明はこれに限られるものではない。

**【0078】**

例えば、素子基板101を半導体基板により構成して、当該半導体基板の表面にソース、ドレイン、チャネルが形成された絶縁ゲート型電界効果トランジスタによって、画素のスイッチング素子や駆動回路120の素子を構成しても良い。このように素子基板101を半導体基板により構成する場合には、透過型の電気光学装置として用いることができないため、画素電極118をアルミニウムなどで形成して、反射型として用いられることとなる。また、単に、素子基板101を透明基板として、画素電極118を反射型にしても良い。

**【0079】**

さらに、電気光学材料としては、液晶のほかに、エレクトロルミネッセンス素子などを用いて、その電気光学効果により表示を行う表示装置にも適用可能である。すなわち、本発明は、上述した液晶装置と類似の構成を有するすべての電気光学装置に適用可能である。

**【0080】**

<ランプ信号およびPWM信号について>

上述した各実施形態では、図4に示すように直線的に増加または減少するランプ波信号LSを基準信号として用いることによって、PWM信号のパルス幅に応じた電圧を画素電極118に印加するようにしたが、本発明の特徴は、スイッチSWを介して基準信号を供給する点にあるので、基準信号はランプ波信号LSに限定されるものではない。例えば、基準信号を液晶のガンマ補正特性に応じたものにして、ガンマ補正を施すようにしてもよい。この場合、基準信号の波形は非線形に単調減少または単調増加させればよい。

**【0081】**

また、上述した各実施形態において画像データのLSBに対応するPWM信号のパルス幅は、画像データ値の大小に拘わらず一定であったが、本発明はこれに限定されるものではなく、ガンマ補正特性に応じた粗密を持たせるようにしてもよい。例えば、画像データ値が小さいときには、画像データのLSBに対応するPWM信号のパルス幅を広くし、画像データ値が大きくなるにつれ当該パルス幅を狭くし、画像データ値が中心値を取る時に最小となり、これを越えると次第に大きくなるように設定すればよい。

**【0082】**

<電子機器>

次に、上述した液晶装置を各種の電子機器に適用される場合について説明する。

**【0083】**

<その1：プロジェクタ>

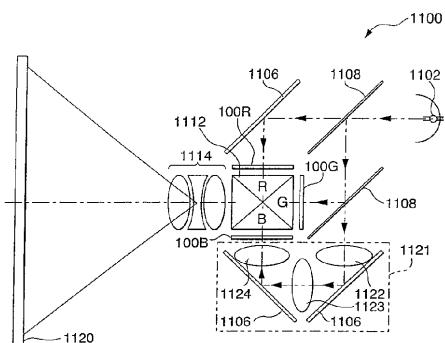

まず、この液晶パネル100をライトバルブとして用いたプロジェクタについて説明する。図9は、このプロジェクタの構成を示す平面図である。この図に示されるように、プロジェクタ1100内部には、ハロゲンランプ等の白色光源からなるランプユニット1102が設けられている。このランプユニット1102から射出された投射光は、内部に配置された3枚のミラー1106および2枚のダイクロイックミラー1108によってRGBの3原色に分離されて、各原色に対応するライトバルブとしての液晶パネル100R、100Bおよび100Gにそれぞれ導かれる。ここで、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ1122、リレーレンズ1123および出射レンズ1124からなるリレーレンズ系1121を介して導かれる。

**【0084】**

さて、液晶パネル100R、100Bおよび100Gの構成は、上述した液晶パネル100と同等であり、画像信号処理回路(図示省略)から供給されるR、G、Bの原色信号でそれぞれ駆動されるものである。そして、これらの液晶パネルによって変調された光は、ダイクロイックプリズム1112に3方向から入射される。このダイクロイックプリズム1112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成される結果、投射レンズ1114を介して、スクリーン1120にカラー画像が投射されることとなる。

10

20

30

40

50

**【0085】**

ここで、各液晶パネル100R、100Bおよび100Gによる表示像について着目すると、液晶パネル100Gによる表示像は、液晶パネル100R、100Bによる表示像に對して左右反転していることが必要となる。このため、水平走査方向は、液晶パネル100Gと、液晶パネル100R、100Bとでは互いに逆方向の關係となる。なお、液晶パネル100R、100Bおよび100Gには、ダイクロイックミラー1108によって、R、G、Bの各原色に対応する光が入射するので、カラーフィルタを設ける必要はない。

**【0086】**

<その2：モバイル型コンピュータ>

次に、この液晶パネルを、モバイル型のパソコンコンピュータに適用した例について説明する。図10は、このパソコンコンピュータの構成を示す斜視図である。図において、コンピュータ1200は、キーボード1202を備えた本体部1204と、液晶表示ユニット1206とから構成されている。この液晶表示ユニット1206は、先に述べた液晶パネル100の背面にバックライトを附加することにより構成されている。

10

**【0087】**

<その3：携帯電話>

さらに、この液晶パネルを、携帯電話に適用した例について説明する。図11は、この携帯電話の構成を示す斜視図である。図において、携帯電話1300は、複数の操作ボタン1302のほか、受話口1304、送話口1306とともに、液晶パネル100を備えるものである。この液晶パネル100にも、必要に応じてその背面にバックライトが設けられる。

20

**【0088】**

なお、電子機器としては、図9～図11を参照して説明した他にも、液晶テレビや、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ペーパージャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種電子機器に対して、各実施形態の液晶パネル、さらには電気光学装置が適用可能なのは言うまでもない。

**【0089】****【発明の効果】**

30

以上説明したように本発明によれば、基準信号が供給される信号供給線は1本である。したがって、基準信号を駆動する駆動回路の負荷は、1本の信号供給線に付随する寄生容量となるので、負荷を大幅に軽減することができる。さらに、駆動回路の回路構成を簡易なものにすることができる、くわえて、駆動回路の消費電流を大幅に削減することが可能となる。

**【図面の簡単な説明】**

**【図1】** 本発明の第1実施形態に係る液晶装置の全体構成を示すブロック図である。

**【図2】** 同液晶装置における比較部の構成を示すブロック図である。

**【図3】** 画像データの値とPWM信号の波形を示したタイミングチャートである。

**【図4】** 1画素の周辺回路と各種信号の電圧レベルとを示す図である。

40

**【図5】** 同液晶装置の動作を説明するためのタイミングチャートである。

**【図6】** 本発明の第2実施形態に係る液晶装置の全体構成を示すブロック図である。

**【図7】** 液晶パネルの構造を示す斜視図である。

**【図8】** 同液晶パネルの構造を説明するための一部断面図である。

**【図9】** 同液晶装置を適用した電子機器の一例たるプロジェクタの構成を示す断面図である。

**【図10】** 同液晶装置を適用した電子機器の一例たるパソコンコンピュータの構成を示す斜視図である。

**【図11】** 同液晶装置を適用した電子機器の一例たる携帯電話の構成を示す斜視図である。

50

【図12】 従来の液晶装置の全体構成を示すブロック図である。

【符号の説明】

- 1 0 0 ..... 液晶パネル

- 1 0 1 ..... 素子基板

- 1 0 2 ..... 対向基板

- 1 1 1 ..... 共通信号線

- 1 1 2 ..... 走査線

- 1 1 3 ..... 信号供給線

- 1 1 4 ..... データ線

- 1 1 6 , 1 1 6 a ..... TFT (第1トランジスタ素子)

- 1 1 7 , 1 1 7 a ..... TFT (第2トランジスタ素子)

- 1 3 0 ..... 走査線駆動回路

- 1 4 0 ..... データ線駆動回路

- SW ..... スイッチ (信号供給手段)

- LS ..... ランプ波信号 (基準信号)

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 9】

【図 8】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G09G3/00-3/38

G02F1/133