(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-239123

(P2010-239123A)

(43) 公開日 平成22年10月21日(2010.10.21)

(51) Int.Cl.

**H01L 29/786** (2006.01)

**H01L 21/336** (2006.01)

**H01L 21/02** (2006.01)

**H01L 27/12** (2006.01)

F 1

H01L 29/78 626C

H01L 29/78 627D

H01L 27/12 B

H01L 29/78 618B

H01L 29/78 616A

テーマコード(参考)

5 F 1 1 O

審査請求 未請求 請求項の数 11 O L (全 25 頁) 最終頁に続く

(21) 出願番号

特願2010-49103 (P2010-49103)

(22) 出願日

平成22年3月5日(2010.3.5)

(31) 優先権主張番号

特願2009-59157 (P2009-59157)

(32) 優先日

平成21年3月12日(2009.3.12)

(33) 優先権主張国

日本国(JP)

(71) 出願人

000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者

磯部 敦生

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者

郷戸 宏充

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者

篠原 聰始

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【要約】

【課題】絶縁表面を有する基板を用いる場合に生じうる課題を解決した半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有するベース基板と、絶縁表面上の導電層と、導電層上の絶縁層と、絶縁層上の、チャネル形成領域、第1の不純物領域、第2の不純物領域、およびチャネル形成領域と第2の不純物領域との間の第3の不純物領域と、を有する半導体層と、半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、第1の不純物領域に電気的に接続された第1の電極と、第2の不純物領域に電気的に接続された第2の電極とを有し、導電層は所定の電位に保持される。

【選択図】図1

(A)

(B)

**【特許請求の範囲】****【請求項 1】**

ポンド基板にイオンを添加することにより、前記ポンド基板中に脆化領域を形成し、絶縁表面を有するベース基板の一表面に導電層を形成し、前記ポンド基板と前記ベース基板を、絶縁層を介して貼り合わせ、前記ポンド基板を加熱して、前記ポンド基板を前記脆化領域において分離することにより、前記ベース基板上に、前記導電層、前記絶縁層、および半導体層の積層構造を形成し、

、前記半導体層をパターニングして、島状の半導体層を形成し、前記島状の半導体層を覆うようにゲート絶縁層を形成し、前記ゲート絶縁層上にゲート電極を形成し、前記島状の半導体層に選択的に不純物元素を添加して、チャネル形成領域、第1の不純物領域、第2の不純物領域、および前記チャネル形成領域と前記第2の不純物領域の間の第3の不純物領域を形成し、前記第1の不純物領域に電気的に接続する第1の電極と、前記第2の不純物領域に電気的に接続する第2の電極を形成することを特徴とする半導体装置の作製方法。

**【請求項 2】**

ポンド基板にイオンを添加することにより、前記ポンド基板中に脆化領域を形成し、前記ポンド基板の一表面に第1の絶縁層を形成し、前記第1の絶縁層上に導電層を形成し、前記導電層上に第2の絶縁層を形成し、絶縁表面を有するベース基板の一表面に第3の絶縁層を形成し、前記ポンド基板と前記ベース基板を、前記第2の絶縁層および前記第3の絶縁層を介して貼り合わせ、前記ポンド基板を加熱して、前記ポンド基板を前記脆化領域において分離することにより、前記ベース基板上に、前記第3の絶縁層、前記第2の絶縁層、前記導電層、前記第1の絶縁層、および半導体層の積層構造を形成し、前記半導体層をパターニングして、島状の半導体層を形成し、前記島状の半導体層を覆うようにゲート絶縁層を形成し、前記ゲート絶縁層上にゲート電極を形成し、前記島状の半導体層に選択的に不純物元素を添加して、チャネル形成領域、第1の不純物領域、第2の不純物領域、および前記チャネル形成領域と前記第2の不純物領域の間の第3の不純物領域を形成し、前記第1の不純物領域に電気的に接続される第1の電極と、前記第2の不純物領域に電気的に接続される第2の電極とを形成することを特徴とする半導体装置の作製方法。

**【請求項 3】**

請求項2において、前記ポンド基板の一表面に第1の絶縁層を形成する前、前記第1の絶縁層を形成した後、前記導電層を形成した後、または前記第2の絶縁層を形成した後のいずれかにおいて、前記ポンド基板に前記イオンを添加して前記脆化領域を形成することを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項1乃至請求項3のいずれか一において、前記脆化領域を形成する前に、前記ポンド基板の一表面に保護絶縁層を形成することを特徴とする半導体装置の作製方法。

**【請求項 5】**

請求項1乃至請求項4のいずれか一において、前記ポンド基板は、単結晶シリコン基板または単結晶炭化シリコン基板であることを特徴とする半導体装置の作製方法。

**【請求項 6】**

絶縁表面を有するベース基板と、

10

20

30

40

50

前記絶縁表面上の導電層と、

前記導電層上の絶縁層と、

前記絶縁層上の、チャネル形成領域、第1の不純物領域、第2の不純物領域、および前記チャネル形成領域と前記第2の不純物領域の間の第3の不純物領域と、を有する半導体層と、

前記半導体層を覆うゲート絶縁層と、

前記ゲート絶縁層上のゲート電極と、

前記第1の不純物領域に電気的に接続された第1の電極と、前記第2の不純物領域に電気的に接続された第2の電極とを有し、

前記導電層は所定の電位に保持されることを特徴とする半導体装置。

10

#### 【請求項7】

請求項6において

前記半導体層は、単結晶シリコン層または単結晶シリコン炭化物層であることを特徴とする半導体装置。

#### 【請求項8】

請求項6または請求項7において、

前記所定の電位は、接地電位であることを特徴とする半導体装置。

#### 【請求項9】

請求項6乃至請求項8のいずれか一において、

前記第1の不純物領域および前記第2の不純物領域における不純物濃度が $1 \times 10^{19}$  atoms/cm<sup>3</sup>以上であり、

前記第3の不純物領域における不純物濃度が $5 \times 10^{16}$  atoms/cm<sup>3</sup>以上であることを特徴とする半導体装置。

20

#### 【請求項10】

請求項6乃至請求項9のいずれか一において、

前記絶縁層の厚さは5μm以下であることを特徴とする半導体装置。

#### 【請求項11】

請求項6乃至請求項10のいずれか一において、

前記チャネル形成領域と前記導電層とは、電気的に接続されていることを特徴とする半導体装置。

30

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

開示する発明の技術分野は、半導体装置およびその作製方法に関するものである。

#### 【背景技術】

#### 【0002】

近年、バルク状のシリコンウェハに代わり、SOI(Silicon On Insulator)基板を使った集積回路が開発されている。絶縁層上に形成された薄い単結晶シリコン層の特長を生かすことで、集積回路中のトランジスタ同士を完全に分離して形成することができ、またトランジスタを完全空乏型とすることができますため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。このような、SOI基板を使ったLSIの開発においては、多層配線技術を用いてチップの面積を縮小することにより、動作周波数を向上し、処理能力の向上が実現されている。

40

#### 【0003】

このようなSOI基板の製造方法として、スマートカット法を用いて単結晶シリコン層をガラスからなる支持基板上に形成する方法が提案されている(例えば、特許文献1参照)。ガラス基板はシリコンウェハと比較して大面積化が容易であり、かつ、安価であるため、ガラス基板をベース基板として用いることにより、大面積で安価なSOI基板を作製することが可能となる。

#### 【先行技術文献】

50

【特許文献】

【0004】

【特許文献1】特開平11-163363号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述のように、ガラス基板をベース基板として用いる場合には、大面積かつ安価であるという特徴を生かして、半導体装置を低コストに提供することができるというメリットがある。

【0006】

一方で、ガラス基板をベース基板として用いる場合には、ガラス基板が絶縁材料からなることに起因して様々な問題が生じうる。例えば、SOI基板の構造として、ガラス基板と、ガラス基板上の絶縁層と、絶縁層上の半導体層、という積層構造を採用する場合には、半導体層下部の絶縁領域の厚さは、絶縁層の厚さとガラス基板の厚さとの和になるため、半導体層下部の絶縁領域の厚さは、シリコンウエハ上に形成した絶縁層の厚さと比較すると著しく大きくなる。これにより、シリコンなどの基板を用いる場合には予想されない問題が生じうる。

10

【0007】

上述に鑑み、本明細書等（少なくとも、特許請求の範囲、明細書、図面を含む）において開示する発明の一態様では、ガラス基板をはじめとする絶縁表面を有する基板を用いる場合に生じうる課題を解決した半導体装置を提供することを目的の一とする。

20

【課題を解決するための手段】

【0008】

開示する発明の一態様では、絶縁表面を有する基板上に、導電層と絶縁層と半導体層とが積層された構造の基板を用いて半導体装置を作製する。

【0009】

例えば、開示する発明の一態様に係る半導体装置の作製方法では、ボンド基板にイオンを添加することにより、ボンド基板中に脆化領域を形成し、絶縁表面を有するベース基板の一表面に導電層を形成し、ボンド基板とベース基板を、絶縁層を介して貼り合わせ、ボンド基板を加熱して、ボンド基板を脆化領域において分離することにより、ベース基板上に、導電層、絶縁層、および半導体層の積層構造を形成し、半導体層をパターニングして、島状の半導体層を形成し、島状の半導体層を覆うようにゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成し、島状の半導体層に選択的に不純物元素を添加して、チャネル形成領域、第1の不純物領域、第2の不純物領域、およびチャネル形成領域と第2の不純物領域の間の第3の不純物領域を形成し、第1の不純物領域に電気的に接続する第1の電極と、第2の不純物領域に電気的に接続する第2の電極を形成することを特徴とする。

30

【0010】

また、開示する発明の一態様に係る半導体装置の作製方法では、ボンド基板にイオンを添加することにより、ボンド基板中に脆化領域を形成し、ボンド基板の一表面に第1の絶縁層を形成し、第1の絶縁層上に導電層を形成し、導電層上に第2の絶縁層を形成し、絶縁表面を有するベース基板の一表面に第3の絶縁層を形成し、ボンド基板とベース基板を、第2の絶縁層および第3の絶縁層を介して貼り合わせ、ボンド基板を加熱して、ボンド基板を脆化領域において分離することにより、ベース基板上に、第3の絶縁層、第2の絶縁層、導電層、第1の絶縁層、および半導体層の積層構造を形成し、半導体層をパターニングして、島状の半導体層を形成し、島状の半導体層を覆うようにゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成し、島状の半導体層に選択的に不純物元素を添加して、チャネル形成領域、第1の不純物領域、第2の不純物領域、およびチャネル形成領域と第2の不純物領域の間の第3の不純物領域を形成し、第1の不純物領域に電気的に接続される第1の電極と、第2の不純物領域に電気的に接続される第2の電極を形成することを特徴とする。なお、当該一態様において、ボンド基板にイオンを添加することによる脆化

40

50

領域の形成は、ボンド基板の一表面に第1の絶縁層を形成する前、第1の絶縁層を形成した後、導電層を形成した後、または第2の絶縁層を形成した後のいずれにおいて行っても良い。

#### 【0011】

なお、上記において、脆化領域を形成する前に、ボンド基板の一表面に保護絶縁層を形成しても良い。なお、ボンド基板は、単結晶シリコン基板または単結晶炭化シリコン基板であることが望ましい。

#### 【0012】

開示する発明の一態様に係る半導体装置は、絶縁表面を有するベース基板と、絶縁表面上の導電層と、導電層上の絶縁層と、絶縁層上の、チャネル形成領域、第1の不純物領域、第2の不純物領域、およびチャネル形成領域と第2の不純物領域の間の第3の不純物領域と、を有する半導体層と、半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、第1の不純物領域に電気的に接続された第1の電極と、第2の不純物領域に電気的に接続された第2の電極とを有し、導電層は所定の電位に保持されることを特徴とする。

10

#### 【0013】

なお、上記において、半導体層は、単結晶シリコン層または単結晶シリコン炭化物層であることが望ましい。また、所定の電位は、接地電位であることが望ましい。

#### 【0014】

また、上記において、第1の不純物領域および第2の不純物領域における不純物濃度が $1 \times 10^{19}$  atoms/cm<sup>3</sup>以上であり、第3の不純物領域における不純物濃度が $5 \times 10^{16}$  atoms/cm<sup>3</sup>以上であることが望ましい。また、絶縁層の厚さは5μm以下であることが望ましい。

20

#### 【0015】

なお、上記において、チャネル形成領域と導電層とは、電気的に接続されていても良い。

#### 【発明の効果】

#### 【0016】

本明細書等において開示する発明の一態様により、絶縁表面を有する基板を用いて半導体装置を作製する場合であっても、オン電流の低下抑制とドレイン耐圧の向上を両立させることができ可能である。

#### 【図面の簡単な説明】

#### 【0017】

【図1】半導体装置について示す図である。

【図2】計算機シミュレーションの結果を示す図である。

【図3】半導体基板の作製方法について示す図である。

【図4】半導体装置の作製方法について示す図である。

【図5】半導体装置の作製方法について示す図である。

【図6】半導体基板の作製方法について示す図である。

【図7】半導体装置について示す図である。

【図8】半導体基板の作製方法について示す図である。

【図9】半導体装置の作製方法について示す図である。

#### 【発明を実施するための形態】

#### 【0018】

以下、実施の形態について、図面を用いて詳細に説明する。但し、発明は以下に示す実施の形態の記載内容に限定されず、本明細書等において開示する発明の趣旨から逸脱することなく形態および詳細を様々に変更し得ることは当業者にとって自明である。また、異なる実施の形態に係る構成は、適宜組み合わせて実施することが可能である。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を用い、その繰り返しの説明は省略する。

#### 【0019】

(実施の形態1)

10

20

30

40

50

本実施の形態では、開示する発明の一態様である半導体装置およびその作製方法の一例について、図1乃至図5を参照して説明する。より具体的には、図1および図2を用いて半導体装置の一例であるトランジスタについて説明し、図3を用いて、半導体装置に用いる半導体基板の作製方法について説明し、図4および図5を用いて半導体装置の一例であるトランジスタの作製方法について説明する。なお、本実施の形態において説明するトランジスタは、大電圧、大電流用途向けに用いるのが望ましいが、開示する発明の用途はこれに限定されない。

#### 【0020】

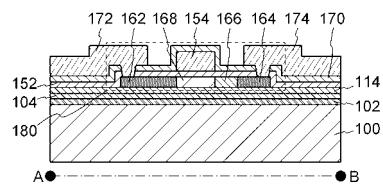

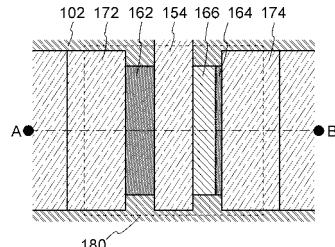

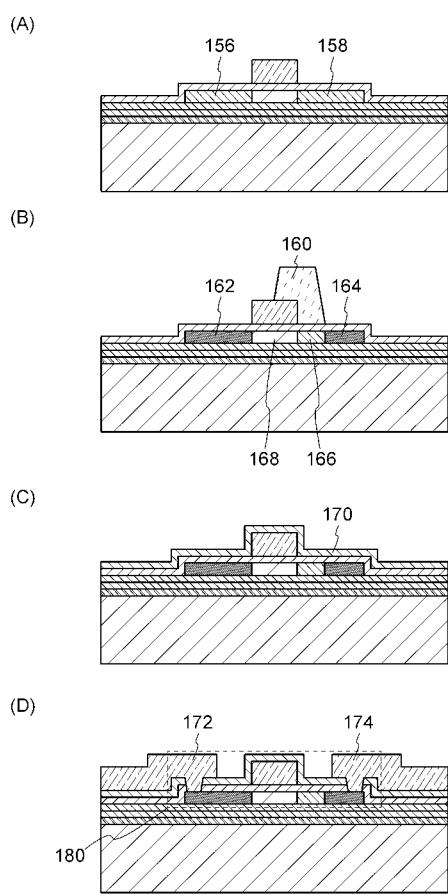

図1には、半導体装置の一例であるトランジスタを示す。ここで、図1(A)は断面図であり、図1(B)は平面図である。なお、図1(A)は図1(B)のA-Bにおける断面を表している。また、図1(B)においては簡単のため、構成要素の一部を省略して表現している。

10

#### 【0021】

図1に示すトランジスタ180は、絶縁表面を有するベース基板100上に形成されている。ここで、トランジスタ180とベース基板100との間には、ベース基板100側から順に、導電層102、絶縁層104、および絶縁層114が形成されている。

#### 【0022】

トランジスタ180は、ゲート電極154、高濃度不純物領域162(第1の不純物領域)、高濃度不純物領域164(第2の不純物領域)、低濃度不純物領域166(第3の不純物領域)、チャネル形成領域168、電極172、電極174などを有する。ゲート電極154は、ゲート絶縁層152を介してチャネル形成領域168に電圧を印加する機能を有する。高濃度不純物領域162、高濃度不純物領域164、低濃度不純物領域166、チャネル形成領域168はいずれも半導体材料を用いて形成される。素子特性の観点からは、単結晶半導体を用いることが好ましい。また、高濃度不純物領域162、高濃度不純物領域164、低濃度不純物領域166には、一導電型を付与する不純物元素が添加されている。なお、上記の高濃度不純物領域や低濃度不純物領域における不純物濃度は任意であるが、トランジスタ180のオン電流を一定以上に保つという観点からは、低濃度不純物領域166においても、ある程度の濃度で不純物元素が添加されていることが望ましい。

20

#### 【0023】

また、チャネル形成領域に不純物元素が添加されていても良い。例えば、上記の高濃度不純物領域や低濃度不純物領域の導電型とは反対の導電型を付与する不純物元素を添加することができる。もちろん、必要な場合には、上記の高濃度不純物領域や低濃度不純物領域の導電型と同じ導電型を付与する不純物元素を添加しても良い。

30

#### 【0024】

高濃度不純物領域162(第1の不純物領域)とチャネル形成領域168は隣接しており、チャネル形成領域168は低濃度不純物領域166と隣接しており、低濃度不純物領域166は高濃度不純物領域164と隣接している。さらに、高濃度不純物領域162は電極172と電気的に接続しており、高濃度不純物領域164は電極174と電気的に接続している。ここで、低濃度不純物領域はチャネル形成領域168と高濃度不純物領域162との間に設けることができるが、オン電流確保の観点からは、ドレインとして機能する高濃度不純物領域側にのみ設けることが好ましい。

40

#### 【0025】

なお、上記においては電極の称呼を用いているが、電極は配線の一部である場合があるから、電極と配線との区別は便宜的なものに過ぎない。このように、電極または配線は同一物を指す場合があるから、電極または配線をこれらの称呼に限定して解釈する必要はない。

#### 【0026】

高濃度不純物領域162は、トランジスタ180のソース領域として機能し、電極172はトランジスタ180のソース電極として機能する。また、高濃度不純物領域164は、

50

トランジスタ180のドレイン領域として機能し、電極174はトランジスタ180のドレイン電極として機能する。高濃度不純物領域164とチャネル形成領域168の間に存在する低濃度不純物領域166は、高濃度不純物領域164とチャネル形成領域168の間の電界を緩和する機能を有している。このように、トランジスタ180では、低濃度不純物領域166を設けることで、インパクトイオン化に起因するアバランシェ降伏を抑制し、ドレイン耐圧を向上させている。

#### 【0027】

さらに、開示する発明の一態様では、トランジスタ180の下部に導電層102を有している。これにより、低濃度不純物領域166における電界の緩和をより好適に行うことが可能になる。なお、導電層102は、所定の電位に保たれていることが望ましい。導電層102をフローティングとする場合には、トランジスタ180に印加される電圧などに起因して、トランジスタ特性が変動するおそれがあるためである。所定の電位としては、たとえば、接地電位がある。

10

#### 【0028】

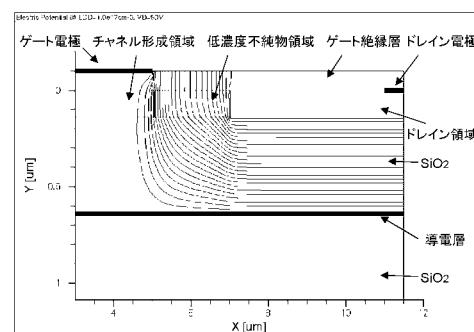

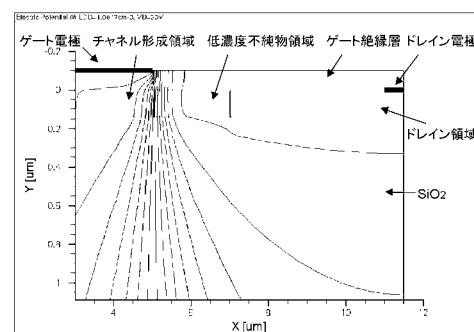

ここで、計算機シミュレーションによる効果の検証結果を図2に示す。ソフトウェアとして、二次元デバイスシミュレータであるsentaurus device (synopsys社)を用いた。また、生成再結合モデルとして、SRHモデルおよびインパクトイオン化モデル(Bologna impact ionization model)を用いた。トランジスタとしては、単結晶シリコンを用いたnチャネル型のトランジスタを想定し、単結晶シリコンの厚さを140nm、ゲート絶縁層の厚さを100nm、チャネル長(チャネル形成領域のキャリア移動方向の長さ)を10μm、チャネル幅(チャネル形成領域のキャリア移動方向と垂直な方向の長さ)を8μm、低濃度不純物領域の長さ(キャリア移動方向の長さ)を2μm、低濃度不純物領域の不純物濃度を $1 \times 10^{17}$ atoms/cm<sup>3</sup>、高濃度不純物領域(ドレイン領域)の不純物濃度を $1 \times 10^{20}$ atoms/cm<sup>3</sup>とした。

20

#### 【0029】

図2(A)には、単結晶シリコン層の下部に絶縁層(酸化シリコン:SiO<sub>2</sub>)が0.5μmの厚さで存在し、その下部に導電層が設けられ、さらにその下部がベース基板(酸化シリコン:SiO<sub>2</sub>)である場合の等電位線(ドレイン電圧は50V)を示す。また、図2(B)には、単結晶シリコン層の下部が全て酸化シリコン(厚さ700μm)である場合の等電位線(ドレイン電圧は30V)を示す。図2(A)および図2(B)において、等電位線は2V間隔で示されている。

30

#### 【0030】

図2(B)では、厚さ700μmの酸化シリコンを一層のみ設ける場合の計算結果を示しているが、これは、ベース基板(酸化シリコン)と絶縁層(酸化シリコン)をまとめて一層として考えているためである。なお、図2(A)において、導電層の電位は接地電位(0V)とした。また、図2(B)においては、酸化シリコンの裏面側の電位を接地電位(0V)とした。つまり、ベース基板裏面の電位が接地電位である場合を想定した。なお、本実施の形態において裏面とは、単結晶シリコン層が設けられている側と反対側の表面をいうものとする。

40

#### 【0031】

上述の結果から、単結晶シリコン層下部に導電層を設ける場合(図2(A)参照)には、チャネル形成領域と低濃度不純物領域の接合領域付近、および低濃度不純物領域と高濃度不純物領域の接合領域付近において等電位線の間隔が概ね等しくなっており、電界が緩和されている様子が分かる。一方で、単結晶シリコン層下部に導電層を設けない場合(図2(B)参照)には、チャネル形成領域と低濃度不純物領域の接合領域付近に等電位線が集中しており、接合領域の周辺に電界が集中していることが分かる。このため、ドレイン電圧が20Vも異なるにも関わらず、図2(A)と図2(B)とでは、チャネル形成領域と低濃度不純物領域の接合領域付近での電界が同程度になっている。

#### 【0032】

50

図2(B)に示すように、一の接合領域(この場合、チャネル形成領域と低濃度不純物領域の接合領域)の周辺に電界が集中する場合、ドレイン電圧が小さくともインパクトイオン化が生じることになる。つまり、ドレイン耐圧が低下することになる。そこで、図2(A)に示すように半導体層の下部に導電層を設けることで、接合領域周辺での電界を緩和し、ドレイン耐圧を向上させることができる。

#### 【0033】

以上のように、ベース基板100と絶縁層104の間に導電層102を設けることにより、電界の集中を低減して、トランジスタ180のドレイン耐圧をより一層向上させることが可能である。

#### 【0034】

なお、低濃度不純物領域における不純物濃度を低くする場合(例えば、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>未満とする場合)には、チャネル形成領域と高濃度不純物領域との間に導電性が比較的低い領域が形成されることになるから、導電層を形成しなくとも電界の集中を緩和することが可能である。しかし、このように低濃度不純物領域における不純物濃度を低くする場合には、トランジスタ動作時の抵抗が高まるため、オン電流が低下することになる。

#### 【0035】

本明細書等において開示する発明の一態様では、ベース基板100と絶縁層104の間に導電層102を設けることで、低濃度不純物領域における不純物濃度を低下させることなくドレイン耐圧を向上させることができる。つまり、絶縁表面を有する基板をベース基板として用いる場合に生じる、オン電流の低下抑制とドレイン耐圧の向上の両立という課題を解決することができる。なお、オン電流の低下を抑制するためには、低濃度不純物領域の不純物濃度は、例えば、 $5 \times 10^{16}$  atoms/cm<sup>3</sup>以上とすればよい。

#### 【0036】

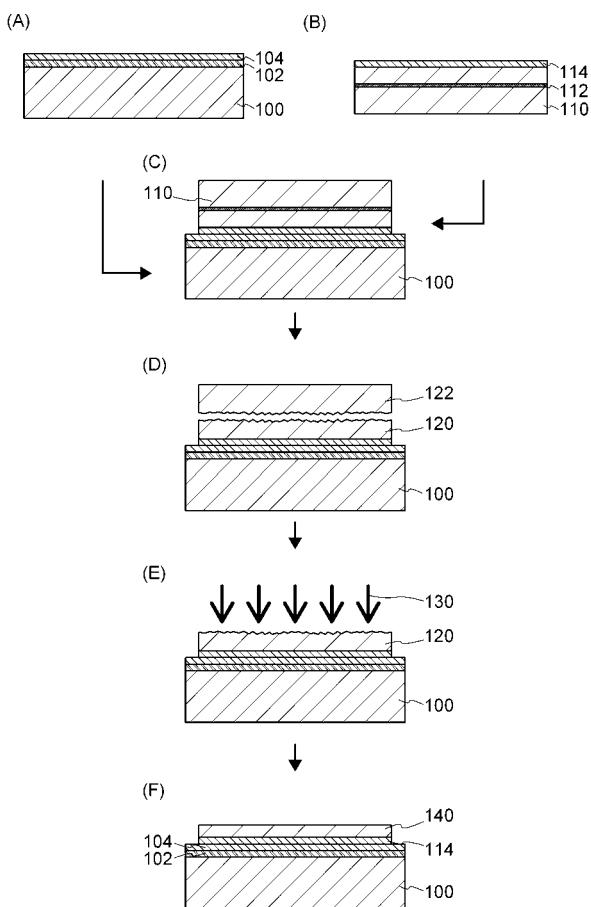

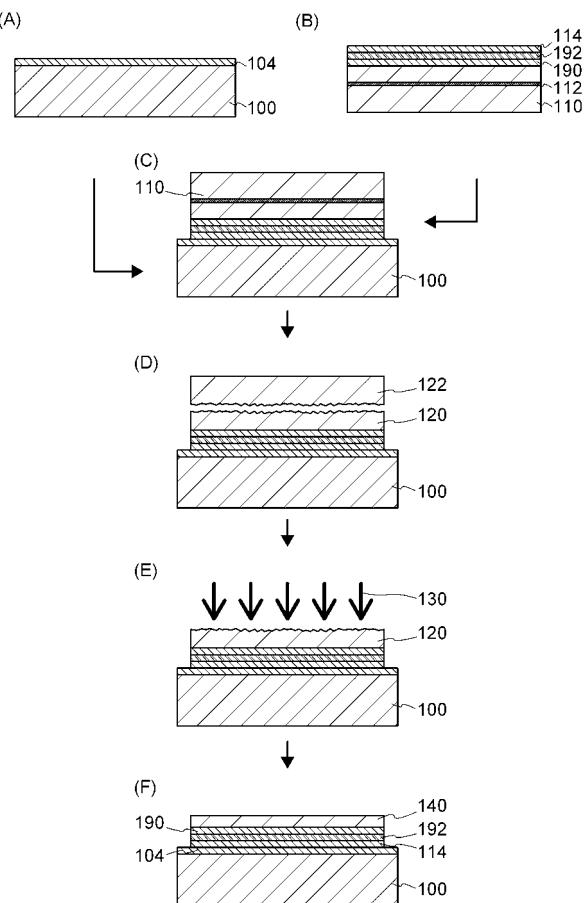

次に、半導体装置に用いる半導体基板の作製方法について図3を参照して説明する。

#### 【0037】

まず、ベース基板100を用意する(図3(A)参照)。ベース基板100としては、液晶表示装置などに使用されている透光性を有するガラス基板を用いることができる。ガラス基板としては、歪み点が580以上750以下(好ましくは、600以上)であるものを用いると良い。もちろん、ガラス基板の耐熱性が許す場合にはこの限りでない。また、ガラス基板は無アルカリガラス基板であることが好ましい。無アルカリガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。

#### 【0038】

なお、ベース基板100として、ガラス基板の他、セラミック基板、石英基板やサファイア基板などの絶縁体でなる基板、珪素などの半導体でなる基板、金属やステンレスなどの導電体でなる基板などを用いることもできる。なお、絶縁体ではない基板を用いる場合には、その表面が絶縁表面となっているものを用いることが望ましい。具体的には、例えば、最表面に絶縁層が形成されており、当該絶縁層の厚さが5μmより大きい基板を用いると良い。このような絶縁表面を有する基板を用いる場合には、導電層を設けることによるドレイン耐圧の向上の効果を、より有效地に得ることができるためである。なお、上述の最表面の絶縁層が薄い場合には、基板自身が導電層と同等の機能を果たす。つまり、導電層を用いることによる効果は、絶縁体基板、ある程度の厚みを有する絶縁層を最表面に備えた半導体基板、または、ある程度の厚みを有する絶縁層を最表面に備えた導電体基板に特有のものともいえる。なお、本明細書等においては、上述の基板を全て含む概念として、「絶縁表面を有する基板」等の称呼を用いる。

#### 【0039】

ベース基板100上には、導電層102を形成する(図3(A)参照)。導電層102の形成方法は特に限定されないが、例えば、スパッタリング法、真空蒸着法などを用いることができる。導電層102は、アルミニウム(A1)、タンゲスタン(W)、チタン(T)

10

20

30

40

50

i)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、ニオブ(Nb)、クロム(Cr)、セリウム( Ce )などの金属、またはこれらの金属を主成分とする合金、またはこれらの金属を成分とする窒化物を用いて形成することができる。インジウム錫酸化物(Indium Tin Oxide:ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)等の導電性酸化物や、導電性を付与する不純物元素を添加したシリコンなどを用いて形成しても良い。なお、導電層102は単層構造としても良いし、積層構造としても良い。

#### 【0040】

そして、導電層102上には絶縁層104を形成する(図3(A)参照)。絶縁層104の形成方法は特に限定されないが、例えば、スパッタリング法、プラズマCVD法などを用いることができる。絶縁層104は、貼り合わせに係る表面を有する層であるから、その表面が、高い平坦性を有するように形成されることが好ましい。絶縁層104は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウムなどから選ばれた一または複数の材料を用いて形成することができる。例えば、酸化珪素を用いて絶縁層104を形成する場合には、有機シランガスを用いて化学気相成長法により形成することで極めて平坦性に優れた絶縁層104を得ることができる。なお、絶縁層104は単層構造としても良いし、積層構造としても良い。

10

#### 【0041】

なお、本明細書等において、酸化窒化物とは、その組成において、窒素よりも酸素の含有量(原子数)が多いものを示し、例えば、酸化窒化シリコンとは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化物とは、その組成において、酸素よりも窒素の含有量(原子数)が多いものを示し、例えば、窒化酸化シリコンとは、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合のものである。また、構成元素の含有比率の合計は100原子%を超えない。

20

#### 【0042】

次に、ボンド基板110を用意する(図3(B)参照)。ボンド基板110としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコンなどの第14属元素でなる半導体基板を用いることができる。もちろん、ガリウムヒ素、インジウムリンなどの化合物半導体でなる基板を用いてもよい。また、ボンド基板110としては単結晶半導体基板を用いることが好ましいが、多結晶半導体基板その他の半導体基板を用いても良い。本実施の形態においては、ボンド基板110として、単結晶シリコン基板を用いることとする。ボンド基板110のサイズに制限は無いが、例えば、直径が8インチ(200mm)、12インチ(300mm)、18インチ(450mm)といったサイズの半導体基板を用いることができる。また、円形の半導体基板を、矩形に加工して用いても良い。なお、本明細書等において、単結晶とは、結晶構造が一定の規則性を持って形成されており、どの部分においても結晶軸が同じ方向を向いているものをいう。ただし、欠陥の多少については問わない。

30

#### 【0043】

ボンド基板110には、イオンを添加することにより、脆化領域112を形成する(図3(B)参照)。より具体的には、例えば、電界で加速されたイオンでなるイオンビームを照射して、ボンド基板110の表面から所定の深さの領域に脆化領域112を形成する。脆化領域112が形成される深さは、イオンビームの加速エネルギーやイオンビームの入

40

50

射角によって制御される。なお、脆化領域 112 は、イオンの平均侵入深さと同程度の深さの領域に形成されることになる。

#### 【0044】

上述の脆化領域 112 が形成される深さにより、ボンド基板 110 から分離される半導体層の厚さが決定される。脆化領域 112 が形成される深さは、ボンド基板 110 の表面から 50 nm 以上 1 μm 以下であり、好ましくは 50 nm 以上 300 nm 以下である。

#### 【0045】

イオンをボンド基板 110 に添加する際には、イオン注入装置またはイオンドーピング装置を用いることができる。イオン注入装置は、ソースガスを励起してイオン種を生成し、生成されたイオン種を質量分離して、所定の質量を有するイオン種を被処理物に照射する。イオンドーピング装置は、プロセスガスを励起してイオン種を生成し、生成されたイオン種を質量分離せずに被処理物に照射する。なお、質量分離装置を備えているイオンドーピング装置では、イオン注入装置と同様に、質量分離を伴うイオンの照射を行うことができる。

10

#### 【0046】

イオンドーピング装置を用いる場合の脆化領域 112 の形成工程は、例えば、以下の条件で行うことができる。

- ・ 加速電圧 10 kV 以上 100 kV 以下 (好ましくは 30 kV 以上 80 kV 以下)

- ・ ドーズ量  $1 \times 10^{16} / \text{cm}^2$  以上  $4 \times 10^{16} / \text{cm}^2$  以下

- ・ ビーム電流密度  $2 \mu\text{A} / \text{cm}^2$  以上 (好ましくは  $5 \mu\text{A} / \text{cm}^2$  以上、より好ましくは  $10 \mu\text{A} / \text{cm}^2$  以上)

20

#### 【0047】

イオンドーピング装置を用いる場合、ソースガスとして水素を含むガスを用いることができる。該ガスを用いることによりイオン種として  $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$  を生成することができる。水素ガスをソースガスとして用いる場合には、 $\text{H}_3^+$  を多く照射することが好ましい。具体的には、イオンビームに、 $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$  の総量に対して  $\text{H}_3^+$  イオンが 70 % 以上含まれるようにすることが好ましい。また、 $\text{H}_3^+$  イオンの割合を 80 % 以上とすることがより好ましい。このように  $\text{H}_3^+$  の割合を高めておくことで、脆化領域 112 に  $1 \times 10^{20} \text{ atoms/cm}^3$  以上の濃度で水素を含ませることが可能である。これにより、脆化領域 112 における分離が容易になる。また、 $\text{H}_3^+$  イオンを多く照射することで、 $\text{H}^+$ 、 $\text{H}_2^+$  を照射する場合より短時間で脆化領域 112 を形成することができる。また、 $\text{H}_3^+$  を用いることで、イオンの平均侵入深さを浅くするため、脆化領域 112 を深い領域に形成することができる。

30

#### 【0048】

イオン注入装置を用いる場合には、質量分離により、 $\text{H}_3^+$  イオンが照射されるようになることが好ましい。もちろん、 $\text{H}^+$  や  $\text{H}_2^+$  を照射してもよい。ただし、イオン注入装置を用いる場合には、イオン種を選択して照射するため、イオンドーピング装置を用いる場合と比較して、イオン照射の効率が低下する場合がある。

40

#### 【0049】

イオン照射工程のソースガスには水素を含むガスの他に、ヘリウムやアルゴンなどの希ガス、フッ素ガスや塩素ガスに代表されるハロゲンガス、フッ素化合物ガス（例えば、 $\text{BF}_3$ ）などのハロゲン化合物ガスから選ばれた一種または複数種類のガスを用いることができる。ソースガスにヘリウムを用いる場合は、質量分離を行わないことで、 $\text{He}^+$  イオンの割合が高いイオンビームを作り出すことができる。このようなイオンビームを用いることで、脆化領域 112 を効率よく形成することができる。

#### 【0050】

また、イオンの照射を複数回に分けて行うことで、脆化領域 112 を形成することもできる。この場合、ソースガスを異なれてイオン照射を行っても良いし、同じソースガスを用いてもよい。例えば、ソースガスとして希ガスを用いてイオン照射を行った後、水素を含むガスをソースガスとして用いてイオン照射を行うことができる。また、初めにハロゲ

50

ンガスまたはハロゲン化合物ガスを用いてイオン照射を行い、次に、水素を含むガスを用いてイオン照射を行うこともできる。

【0051】

なお、上述のイオンの照射工程前に、ボンド基板110の表面に保護絶縁層として機能する絶縁層を形成しても良い。もちろん、当該絶縁層を設けない構成とすることもできるが、後のイオン照射の際のボンド基板110の汚染やボンド基板110の表面の損傷を防ぐためには、絶縁層を設けることが好ましい。絶縁層の厚さは10nm以上400nm以下とするが、これより薄い場合は、イオンの照射工程後には除去しても良いし、そのまま残存させても良い。

10

【0052】

ボンド基板110上には絶縁層114を形成する(図3(B)参照)。絶縁層114の形成方法、材料、構造等は絶縁層104に関する記載を参照すればよい。なお、絶縁層104と絶縁層114は同じ物である必要はない。

【0053】

なお、本実施の形態においては、ベース基板100側に絶縁層104を形成し、ボンド基板110側に絶縁層114を形成する場合について説明しているが、開示する発明の一態様はこれに限定されない。貼り合わせの際に、少なくとも、ボンド基板110の表面と、導電層102の表面とが直接接触しない構成であれば、これら絶縁層の構成は特に限定されない。例えば、ベース基板100側のみに絶縁層を設けても良いし、ボンド基板110側のみに絶縁層を設けても良い。

20

【0054】

開示する発明の一態様をより効果的なものとするためには、上記絶縁層を厚くし過ぎないことが望ましい。絶縁層を厚くし過ぎると、導電層102による効果が低下するためである。なお、絶縁層の厚さは、後に形成される半導体層と導電層102との間隔と同様の意味を有する。例えば、半導体層と導電層102との間隔が5μm以下となるように絶縁層を形成することが望ましい。

【0055】

なお、上記イオンの照射工程(脆化領域112の形成工程)は、絶縁層114の形成前または形成後のいずれにおいて行っても良い。

30

【0056】

その後、ベース基板100とボンド基板110を貼り合わせる(図3(C)参照)。具体的には、絶縁層104および絶縁層114を介してベース基板100とボンド基板110を貼り合わせる。なお、貼り合わせに係る絶縁層104および絶縁層114の表面は、超音波洗浄などの方法で洗浄することが望ましい。絶縁層104の表面と絶縁層114の表面とを接触させた後、加圧処理を施すことで、ベース基板100とボンド基板110の貼り合わせが実現される。なお、貼り合わせのメカニズムとしては、ファン・デル・ワールス力が関与するメカニズムや、水素結合が関与するメカニズムなどが考えられている。

【0057】

なお、貼り合わせに係る表面を酸素プラズマまたはオゾンで処理することにより、その表面を親水性にしても良い。この処理によって、貼り合わせ表面に水酸基が付加されるため、貼り合わせ界面に水素結合を形成することができる。

40

【0058】

上記貼り合わせ後には、貼り合わせられたベース基板100およびボンド基板110に対して熱処理を施して、貼り合わせを強固なものとすると良い。この際の加熱温度は、脆化領域112における分離が進行しない温度とする必要がある。例えば、400未満、好ましくは300以下とする。熱処理時間については特に限定されず、処理時間と貼り合わせ強度との関係から最適な条件を適宜設定すればよい。例えば、200、2時間の熱処理を施すことができる。なお、貼り合わせに係る領域にマイクロ波などを照射して、該領域のみを局所的に加熱することも可能である。貼り合わせ強度に問題がない場合には、

50

上記熱処理は省略すれば良い。

#### 【0059】

次に、ボンド基板110を、脆化領域112において、半導体層120と半導体基板122とに分離する(図3(D)参照)。ボンド基板110の分離は、熱処理により行う。該熱処理の温度は、ベース基板100の耐熱温度を目安に行うことができる。例えば、ベース基板100としてガラス基板を用いる場合には、熱処理の温度は400以上750以下とすることが好ましい。ただし、ガラス基板の耐熱性が許すのであればこの限りではない。なお、本実施の形態においては、600、2時間の熱処理を施すこととする。

#### 【0060】

上述のような熱処理を行うことにより、脆化領域112に形成された微小な空孔の体積変化が生じ、脆化領域112に亀裂が生ずる。その結果、脆化領域112に沿ってボンド基板110が分離する。これにより、ベース基板100上にはボンド基板110から分離された半導体層120が残存することになる。また、この熱処理で、貼り合わせに係る界面が加熱されるため、当該界面に共有結合が形成され、貼り合わせを一層強固なものとすることができます。

10

#### 【0061】

上述のようにして形成された構造体(以下、単に「半導体基板」と呼ぶ)において、半導体層120の表面には、分離工程やイオン照射工程に起因する欠陥が存在し、また、その平坦性は損なわれている。そのため、半導体層120の欠陥を低減させる処理、または、半導体層120の表面の平坦性を向上させる処理を行う。

20

#### 【0062】

本実施の形態において、半導体層120の欠陥の低減、および、平坦性の向上は、半導体層120にレーザー光130を照射することで実現される(図3(E)参照)。レーザー光130を半導体層120に照射することで、半導体層120が溶融し、その後の冷却、固化によって、欠陥が低減され、表面の平坦性が向上した半導体層が得られるのである。本実施の形態においては、レーザー光130を用いているため、ベース基板100が直接加熱されない。つまり、ベース基板100の温度上昇を抑えることができる。このため、ガラス基板のような耐熱性の低い基板をベース基板100に用いることが可能である。もちろん、ベース基板の耐熱温度の範囲内における加熱を行っても良い。ベース基板を加熱することにより、比較的低いエネルギー密度のレーザー光を用いる場合であっても、欠陥の低減を効果的に進めることができる。

30

#### 【0063】

なお、レーザー光130の照射による半導体層120の溶融は、部分溶融とすることが好ましい。完全溶融させた場合には、液相となった後の無秩序な核発生により微結晶化する可能性が高いためである。一方で、部分溶融させる場合には、溶融されていない固相部分から結晶成長が進行する。これにより、所定の結晶性を保ったまま、半導体層中の欠陥を減少させることができる。ここで、完全溶融とは、半導体層120が下部界面付近まで溶融されて、液体状態になることをいう。他方、部分溶融とは、この場合、半導体層120の上部は溶融して液相となるが、下部は溶融せずに固相のままであることをいう。

40

#### 【0064】

上記レーザー光の照射には、パルス発振レーザー光を用いることが好ましい。これは、瞬間に高エネルギーのレーザー光を発振することができ、部分溶融状態を作り出すことが容易となるためである。発振周波数は、1Hz以上10MHz以下程度とすることが好ましい。より好ましくは、10Hz以上1MHz以下である。上述のパルス発振レーザー光の発振器としては、Arレーザー、Krレーザー、エキシマ(ArF、KrF、XeCl)レーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンドライトレーザー、Ti:サファイアレーザー、銅蒸気レーザー、金蒸気レーザーなどを用いることができる。なお、部分溶融させるためにはパルス発振レーザー光を用いることが好ましいが、これに限定して解釈する必要はない。すなわち、連続発振レーザー光の

50

使用を除外するものではない。なお、連続発振レーザー光の発振器には、Ar レーザー、Kr レーザー、CO<sub>2</sub> レーザー、YAG レーザー、YVO<sub>4</sub> レーザー、YLF レーザー、YAlO<sub>3</sub> レーザー、GdVO<sub>4</sub> レーザー、Y<sub>2</sub>O<sub>3</sub> レーザー、ルビーレーザー、アレキサンドライトレーザー、Ti : サファイアレーザー、ヘリウムカドミウムレーザーなどがある。

#### 【0065】

レーザー光 130 の波長は、半導体層 120 に吸収される波長とする必要がある。具体的な波長は、レーザー光の表皮深さ (skin depth)などを考慮して決定すればよい。例えば、半導体層 120 が単結晶シリコンの場合、250 nm 以上 700 nm 以下の波長を用いると良い。また、レーザー光 130 のエネルギー密度は、レーザー光 130 の波長、レーザー光の表皮深さ、半導体層 120 の膜厚などを考慮して決定することができる。具体的には、例えば、300 mJ / cm<sup>2</sup> 以上 800 mJ / cm<sup>2</sup> 以下の範囲とすればよい。なお、上記エネルギー密度の範囲は、パルス発振レーザーとして XeCl エキシマーレーザー (波長 : 308 nm) を用いた場合の一例である。

10

#### 【0066】

レーザー光 130 の照射は、大気雰囲気のような酸素を含む雰囲気、または窒素雰囲気のような不活性雰囲気で行うことができる。不活性雰囲気中でレーザー光 130 を照射するには、気密性のあるチャンバー内でレーザー光 130 を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、レーザー光 130 の被照射面に窒素ガスなどの不活性ガスを吹き付けることで、窒素雰囲気を形成することもできる。

20

#### 【0067】

なお、窒素などの不活性雰囲気で行うほうが、大気雰囲気よりも半導体層 120 の平坦性を向上させる効果は高い。また、大気雰囲気よりも不活性雰囲気のほうがクラックやリッジの発生を抑制する効果が高く、レーザー光 130 の使用可能なエネルギー密度の範囲が広くなる。なお、レーザー光 130 の照射は、真空中で行ってもよい。真空中でレーザー光 130 を照射した場合には、不活性雰囲気における照射と同等の効果を得ることができる。

20

#### 【0068】

上述のようにレーザー光 130 を照射した後には、半導体層の膜厚を小さくする薄膜化工程を行っても良い。半導体層の薄膜化には、ドライエッチング処理またはウェットエッチング処理の一方、または双方を組み合わせたエッチング処理を適用すればよい。例えば、半導体層がシリコンからなる場合、SF<sub>6</sub> と O<sub>2</sub> をプロセスガスに用いたドライエッチング処理で、半導体層を薄くすることができる。

30

#### 【0069】

なお、エッチング処理のタイミングは上記のものに限定する必要はない。例えば、レーザー光の照射前にエッチング処理を行ってもよい。この場合には、エッチング処理により半導体層表面の凹凸や欠陥をある程度低減することができる。また、レーザー光の照射前および照射後の両方に上記処理を適用しても良い。また、レーザー光の照射と上記処理を交互に繰り返しても良い。このように、レーザー光の照射とエッチング処理を組み合わせて用いることにより、半導体層表面の凹凸、欠陥等を効果的に低減することができる。もちろん、上述のエッチング処理や加熱処理などを常に用いる必要はない。また、必要がなければ、レーザー光の照射処理自体を省略することもできる。

40

#### 【0070】

以上により、半導体層 140 の下部に導電層 102 を有する半導体基板を作製することができる（図 3 (F) 参照）。

#### 【0071】

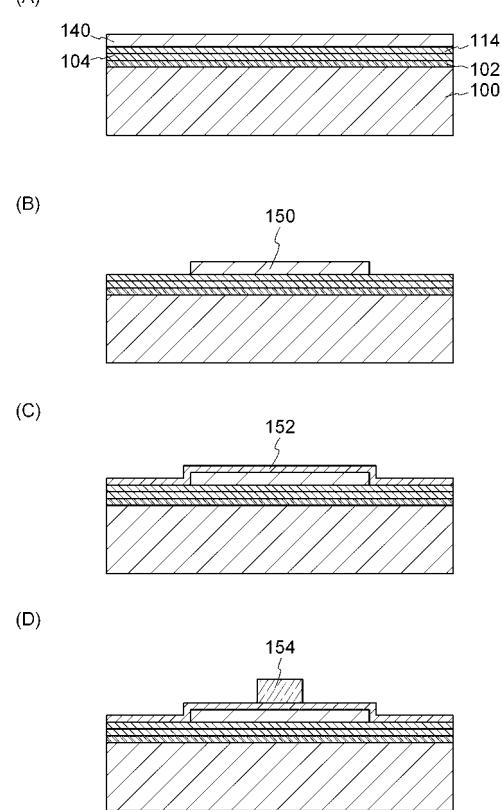

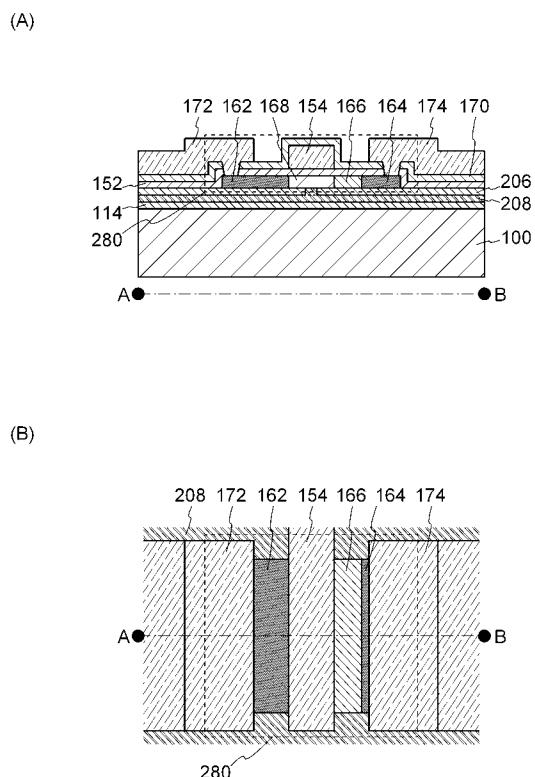

次に、上記の半導体基板を用いた半導体装置の作製方法について、図 4 および図 5 を参照して説明する。ここでは、一例として、大電圧、大電流などの用途に用いられるトランジスタを含む半導体装置の作製方法について説明することとする。

50

#### 【0072】

図4(A)は、上述の半導体基板の一部を拡大した断面図に相当する。図4(A)から分かるように、ベース基板100と絶縁層104との間には、導電層102が存在している。

#### 【0073】

半導体層140には、トランジスタのしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型を付与する不純物、または、リン、砒素などのn型を付与する不純物を添加しても良い。不純物を添加する領域、および添加する不純物の種類は、適宜変更することができる。例えば、nチャネル型トランジスタを形成する場合にはp型を付与する不純物を添加し、pチャネル型トランジスタを形成する場合にはn型を付与する不純物を添加することができる。

10

#### 【0074】

上記半導体層140に対してエッティング処理を施すことにより、半導体層140を島状に分離して島状の半導体層150を形成する(図4(B)参照)。なお、エッティング処理はウエットエッティング処理としても良いし、ドライエッティング処理としても良い。

#### 【0075】

次に、半導体層150を覆うように、ゲート絶縁層152を形成する(図4(C)参照)。ゲート絶縁層152は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、酸化タンタルなどから選ばれた一または複数の材料を用いて形成することができる。ゲート絶縁層152の形成方法は特に限定されないが、例えば、スパッタリング法、プラズマCVD法などを用いることができる。高密度プラズマ処理による酸化または窒化、熱酸化などの方法によってゲート絶縁層152を形成しても良い。ここでは、プラズマCVD法を用いて、酸化シリコンによりゲート絶縁層152を形成する。

20

#### 【0076】

次に、ゲート絶縁層152上に導電層を形成した後、該導電層を所定の形状に加工(パターニング)することで、半導体層150の上方にゲート電極154を形成する(図4(D)参照)。導電層の形成にはCVD法、スパッタリング法等を用いることができる。導電層は、タンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等の金属を用いて形成することができる。また、上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。または、導電性を付与する不純物元素を添加したシリコンなどを用いて形成しても良い。

30

#### 【0077】

なお、本実施の形態ではゲート電極154を単層の導電層で形成しているが、開示する発明の一態様に係る半導体装置はこれに限定されない。ゲート電極154を2層構造とする場合には、例えば、モリブデン、チタン、窒化チタン等を下層に用い、上層にはアルミニウムなどを用いればよい。3層構造の場合には、モリブデンとアルミニウムとモリブデンの積層構造や、チタンとアルミニウムとチタンの積層構造などを採用するとよい。また、4層以上の積層構造としても良い。

30

#### 【0078】

次に、ゲート電極154をマスクとして、一導電型を付与する不純物元素を半導体層150に添加する。これにより、低濃度不純物領域156および低濃度不純物領域158が形成される(図5(A)参照)。ここでは、低濃度不純物領域156および低濃度不純物領域158における不純物濃度が、 $5 \times 10^{16}$  atoms/cm<sup>3</sup> ~  $1 \times 10^{18}$  atoms/cm<sup>3</sup>程度となるように不純物元素を添加する。なお、本実施の形態では、半導体層150にn型を付与する不純物元素(例えばリンやヒ素など)を添加する場合について説明するが、開示する発明の一態様はこれに限定されない。半導体層150にp型を付与する不純物元素(例えばボロンなど)を添加しても良い。なお、p型を付与する不純物元素を添加する場合には、n型を付与する不純物元素を添加する場合とは適切な不純物濃度の範囲が異なる場合がある。

40

50

## 【0079】

次に、低濃度不純物領域158の一部と重畠するようにマスク160を形成する（図5（B）参照）。マスク160は、例えば、フォトマスクを用いてレジスト材料を露光、現像することにより形成することができる。ここで、マスク160は、少なくとも低濃度不純物領域158のうちの、ゲート電極154下部の半導体層と隣接する領域と重畠するよう<sup>10</sup>に形成される。

## 【0080】

そして、ゲート電極154およびマスク160をマスクとして用いて、一導電型を付与する不純物元素を半導体層に添加する。これにより、高濃度不純物領域162および高濃度不純物領域164が形成されると共に、低濃度不純物領域166およびチャネル形成領域168が形成される（図5（B）参照）。ここでは、高濃度不純物領域162および高濃度不純物領域164における不純物濃度が、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>～ $1 \times 10^{21}$  atoms/cm<sup>3</sup>程度となるように不純物元素を添加する。なお、本実施の形態においては、低濃度不純物領域166は、チャネル形成領域168および高濃度不純物領域164に隣接している。また、該工程の後に、マスク160は除去される。

10

## 【0081】

次に、半導体層150、ゲート絶縁層152、ゲート電極154などを覆うように絶縁層170を形成する（図5（C）参照）。絶縁層170は、例えば、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、窒化アルミニウム、酸化アルミニウムなどの材料を用いて形成することができる。また、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の耐熱性を有する有機材料を用いて形成してもよい。なお、絶縁層170は必須の構成ではないから、不要な場合には設けなくとも良い。<sup>20</sup>

20

## 【0082】

次に、ゲート絶縁層152および絶縁層170を選択的にエッチングして、高濃度不純物領域162および高濃度不純物領域164に達するコンタクトホールを形成する。そして、該コンタクトホールを通じて、半導体層150の高濃度不純物領域162と電気的に接続する電極172、および半導体層150の高濃度不純物領域164と電気的に接続する電極174を形成する（図5（D）参照）。なお、コンタクトホールを形成する際には、ウェットエッチング処理またはドライエッチング処理のいずれを用いても良い。

30

## 【0083】

電極172および電極174は、例えば、スパッタリング法や真空蒸着法などによって形成した導電層を選択的にエッチングすることにより形成することができる。また、電極172および電極174は、アルミニウム、タンゲステン、チタン、タンタル、モリブデン、ニッケル、白金、銅、金、銀、マンガン、ネオジム、炭素、珪素等の材料、またはこれらの材料を主成分とする合金、化合物などを用いて形成することができる。なお、電極172および電極174は、単層構造としても良いし、積層構造としても良い。

30

## 【0084】

電極172および電極174に用いることができる合金の例としては、アルミニウムを主成分として、ニッケルを含むものが挙げられる。また、アルミニウムを主成分として、ニッケルと、炭素または珪素の一方または両方を含むものを挙げることができる。アルミニウムやアルミニウムシリコン（Al-Si）は抵抗値が低く、安価であるため、電極172および電極174を形成する材料として適している。特に、アルミニウムシリコンは、ヒロックの発生を抑制することができるため好ましい。また、珪素の代わりに、アルミニウムに0.5%程度のCuを混入させた材料を用いても良い。<sup>40</sup>

40

## 【0085】

電極172および電極174を積層構造とする場合には、例えば、バリア膜とアルミニウムシリコン膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン膜と窒化チタン膜とバリア膜の積層構造などを採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、モリブデンの窒化物などを用いて形成された膜である。バリア膜の間にアルミニウムシリコン膜を挟むようにすると、ヒロックの発生をより一層抑制すること<sup>50</sup>

50

ができる。また、還元性の高い元素であるチタンを用いてバリア膜を形成すると、半導体層 150 の表面などに薄い酸化膜が形成されている場合であっても、バリア膜に含まれるチタンが該酸化膜を還元し、半導体層と電極とのコンタクトを良好なものとすることができます。

【0086】

以上により、大電圧、大電流などの用途に用いられるトランジスタ 180 を含む半導体装置を作製することができる。

【0087】

本実施の形態において開示するように、半導体層の下部に導電層を設けることで、低濃度不純物領域における不純物濃度を低下させることなく、低濃度不純物領域における電界を緩和し、ドレイン耐圧を向上させることができる。つまり、オン電流を確保しつつ、ドレイン耐圧を向上した半導体装置を提供することができる。

10

【0088】

(実施の形態 2)

本実施の形態では、半導体装置に用いることができる半導体基板の作製方法の別の一例について説明する。なお、本実施の形態における半導体基板の作製方法は、先の実施の形態において図 3 を参照して説明した半導体基板の作製方法と共通する部分が多い。このため、本実施の形態においては、主に先の実施の形態と相違する部分についてのみ図 6 を参照して説明することとする。

20

【0089】

まず、ベース基板 100 を用意する(図 6(A) 参照)。ベース基板 100 の詳細は、先の実施の形態を参酌することができる。ベース基板 100 上には、絶縁層 104 を形成する(図 6(A) 参照)。絶縁層 104 の詳細についても、先の実施の形態を参酌することができる。

【0090】

次に、ボンド基板 110 を用意する(図 6(B) 参照)。ボンド基板 110 の詳細は、先の実施の形態を参酌すればよい。

【0091】

ボンド基板 110 には、イオンを添加することにより、脆化領域 112 を形成する(図 6(B) 参照)。脆化領域 112 の詳細についても、先の実施の形態を参酌することができる。

30

【0092】

なお、イオンの照射工程前に、ボンド基板 110 の表面に保護絶縁層として機能する絶縁層を形成しても良い。もちろん、当該絶縁層を設けない構成とすることもできるが、後のイオン照射の際のボンド基板 110 の汚染やボンド基板 110 の表面の損傷を防ぐためには、絶縁層を設けることが好ましい。絶縁層の詳細についても、先の実施の形態を参酌することができる。

【0093】

ボンド基板 110 上には絶縁層 190、導電層 192、および絶縁層 114 を積層して形成する(図 6(B) 参照)。絶縁層 190 および絶縁層 114 の形成方法、材料、構造等は、先の実施の形態における絶縁層 104 に関する記載などを参酌すればよい。なお、絶縁層 190 は貼り合わせに係る層ではないから、絶縁層 104 や絶縁層 114 と同等の平坦性を有している必要はない。また、絶縁層 104 と絶縁層 114 は同じ物である必要はない。導電層 192 の詳細については、先の実施の形態の導電層 102 に関する記載を参酌することができる。

40

【0094】

なお、本実施の形態においては、ベース基板 100 側に絶縁層 104 を形成し、ボンド基板 110 側に絶縁層 114 を形成する場合について説明しているが、開示する発明の一態様はこれに限定されない。例えば、ベース基板 100 側のみに絶縁層を設けても良いし、ボンド基板 110 側のみに絶縁層を設けても良い。

50

## 【0095】

開示する発明の一態様をより効果的なものとするためには、上記絶縁層190を厚くし過ぎないことが望ましい。絶縁層190を厚くし過ぎると、導電層192による効果が低下するためである。なお、絶縁層190の厚さは、後に形成される半導体層と導電層192との間隔と同様の意味を有している。例えば、半導体層と導電層192との間隔が5μm以下となるように絶縁層を形成することが望ましい。

## 【0096】

その後、ベース基板100とボンド基板110を貼り合わせる(図6(C)参照)。貼り合わせの詳細については、先の実施の形態を参照することができる。

## 【0097】

次に、ボンド基板110を、脆化領域112において、半導体層120と半導体基板122とに分離する(図6(D)参照)。ボンド基板110の分離の詳細についても、左記の実施の形態を参照することができる。

## 【0098】

上述のようにして形成された構造体(以下、単に「半導体基板」と呼ぶ)において、半導体層120の表面には、分離工程やイオン照射工程に起因する欠陥が存在し、また、その平坦性は損なわれている。そのため、半導体層120の欠陥を低減させる処理、または、半導体層120の表面の平坦性を向上させる処理を行う。

## 【0099】

本実施の形態において、半導体層120の欠陥の低減、および、平坦性の向上は、半導体層120にレーザー光130を照射することで実現される(図6(E)参照)。詳細については先の実施の形態を参照することができる。また、欠陥や表面の平坦性の問題が深刻でない場合には、レーザー光の照射処理自体を省略しても良い。

## 【0100】

以上により、半導体層140の下部に導電層192を有する半導体基板を作製することができる(図6(F)参照)。

## 【0101】

本実施の形態では、ベース基板100側に導電層を設ける代わりに、ボンド基板110側に導電層を設ける場合について説明した。このように、最終的な半導体基板として、半導体層の下部に導電層が存在する構造を得ることができれば、どのような方法で作製した半導体基板を用いたとしても、開示する発明の一態様に係る効果を得ることができる。つまり、半導体基板の作製方法は、上述の方法に限定する必要はないと言える。

## 【0102】

なお、本実施の形態は先の実施の形態と適宜組み合わせて用いることができる。

## 【0103】

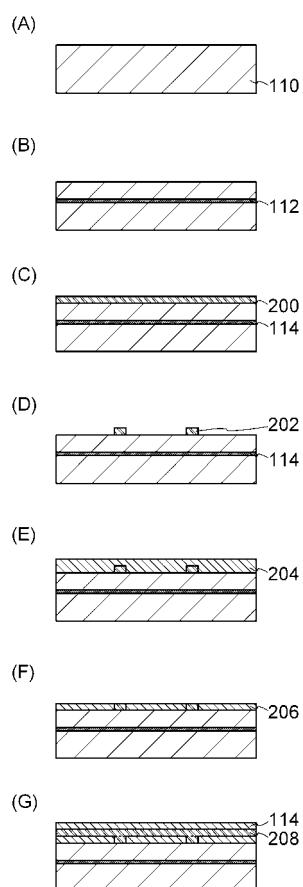

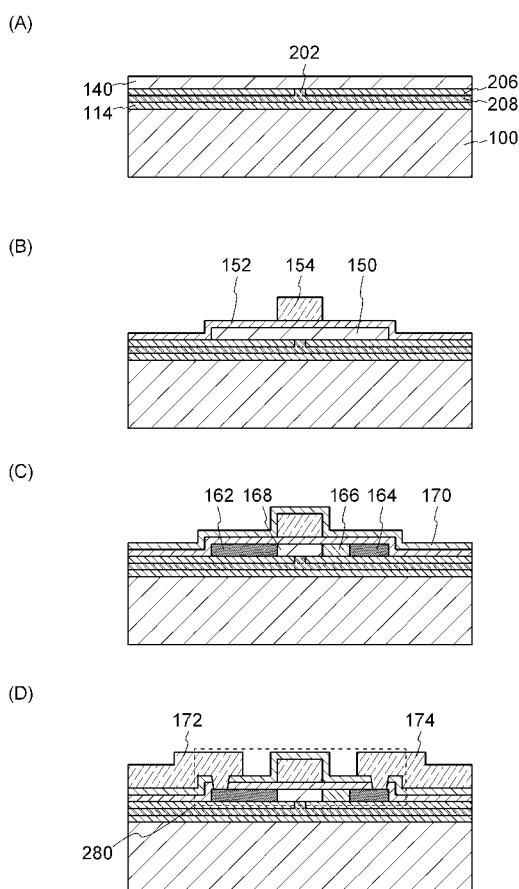

(実施の形態3)

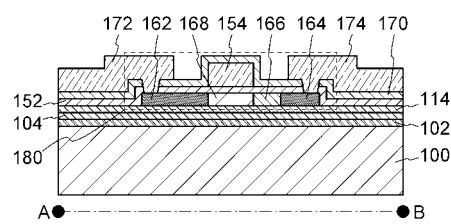

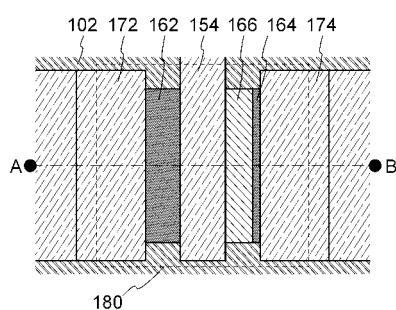

本実施の形態では、先の実施の形態と異なる半導体装置およびその作製方法の一例に関して図7乃至図9を参照して説明する。より具体的には、図7を用いて半導体装置の一例であるトランジスタについて説明し、図8を用いて、半導体装置に用いる半導体基板の作製方法について説明し、図9を用いて半導体装置の一例であるトランジスタの作製方法について説明する。なお、本実施の形態におけるトランジスタは、先の実施の形態において説明したトランジスタと共通する部分が多い。このため、本実施の形態においては、主に先の実施の形態と相違する部分についてのみ図面を参照して説明することとする。

## 【0104】

図7には、半導体装置の一例であるトランジスタを示す。ここで、図7(A)は断面図であり、図7(B)は平面図である。なお、図7(A)は図7(B)のA-Bにおける断面を表している。また、図7(B)においては簡単のため、構成要素の一部を省略して表現している。

## 【0105】

図7に示すトランジスタ280は、絶縁表面を有するベース基板100上に形成されてい

10

20

30

40

50

る。ここで、トランジスタ280とベース基板100との間には、ベース基板100側から順に、絶縁層114、導電層208、および絶縁層206が形成されている。

#### 【0106】

トランジスタ280は、ゲート電極154、高濃度不純物領域162（第1の不純物領域）、高濃度不純物領域164（第2の不純物領域）、低濃度不純物領域166（第3の不純物領域）、チャネル形成領域168、電極172、電極174などを有する。ゲート電極154は、ゲート絶縁層152を介してチャネル形成領域168に電圧を印加する機能を有する。高濃度不純物領域162、高濃度不純物領域164、低濃度不純物領域166、チャネル形成領域168はいずれも半導体材料を用いて形成される。素子特性の観点からは、単結晶半導体を用いることが好ましい。また、高濃度不純物領域162、高濃度不純物領域164、低濃度不純物領域166には、一導電型を付与する不純物元素が添加されている。なお、上記の高濃度不純物領域や低濃度不純物領域における不純物濃度は任意であるが、トランジスタ280のオン電流を一定以上に保つという観点からは、低濃度不純物領域166においても、ある程度の濃度で不純物元素が添加されていることが望ましい。

10

#### 【0107】

また、チャネル形成領域に不純物元素が添加されていても良い。例えば、上記の高濃度不純物領域や低濃度不純物領域の導電型とは反対の導電型を付与する不純物元素を添加することができる。もちろん、必要な場合には、上記の高濃度不純物領域や低濃度不純物領域の導電型と同じ導電型を付与する不純物元素を添加しても良い。

20

#### 【0108】

高濃度不純物領域162（第1の不純物領域）とチャネル形成領域168は隣接しており、チャネル形成領域168は低濃度不純物領域166と隣接しており、低濃度不純物領域166は高濃度不純物領域164と隣接している。さらに、高濃度不純物領域162は電極172と電気的に接続しており、高濃度不純物領域164は電極174と電気的に接続している。ここで、低濃度不純物領域はチャネル形成領域168と高濃度不純物領域162との間に設けることができるが、オン電流確保の観点からは、ドレインとして機能する高濃度不純物領域側にのみ設けることが好ましい。

#### 【0109】

なお、上記においては電極の称呼を用いているが、電極は配線の一部である場合があるから、電極と配線との区別は便宜的な物に過ぎない。このように、電極または配線は同一物を指す場合があるから、電極または配線をこれらの称呼に限定して解釈する必要はない。

30

#### 【0110】

高濃度不純物領域162は、トランジスタ280のソース領域として機能し、電極172はトランジスタ280のソース電極として機能する。また、高濃度不純物領域164は、トランジスタ280のドレイン領域として機能し、電極174はトランジスタ280のドレイン電極として機能する。高濃度不純物領域164とチャネル形成領域168の間に存在する低濃度不純物領域166は、高濃度不純物領域164とチャネル形成領域168の間の電界を緩和する機能を有している。このように、トランジスタ280では、低濃度不純物領域166を設けることで、インパクトイオン化に起因するアバランシェ降伏を抑制し、ドレイン耐圧を向上させている。

40

#### 【0111】

さらに、本実施の形態のトランジスタ280では、半導体層の下部に導電層208を有している。これにより、低濃度不純物領域166における電界の緩和をより好適に行うことが可能になる。

#### 【0112】

また、トランジスタ280の下部の導電層208とチャネル形成領域168が電気的に接続している。これにより、インパクトイオン化により生じる逆極性のキャリアを導電層208を通じて排出することができる。例えば、nチャネル型トランジスタでは、インパクトイオン化によって正孔（ホール）が生じ得るが、上述の構成を採用することにより、正

50

孔を除去することができる。このため、インパクトイオン化に起因するアバランシェ降伏を抑制し、トランジスタのドレイン耐圧を一層向上させることができる。

#### 【0113】

以上のように、半導体層の下部に導電層208を設けることで電界の集中を低減すると共に、逆極性キャリアに起因するドレイン耐圧の低下を防止して、トランジスタ280のドレイン耐圧をより一層向上させることができある。

#### 【0114】

なお、低濃度不純物領域における不純物濃度を低くする場合（例えば、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>未満とする場合）には、チャネル形成領域と高濃度不純物領域との間に導電性が比較的低い領域が形成されることになるから、導電層を形成しなくとも電界の集中を緩和することが可能である。しかし、このように低濃度不純物領域における不純物濃度を低くする場合には、トランジスタ動作時の抵抗が高まるため、オン電流が低下することになる。

10

#### 【0115】

本明細書等において開示する発明の一態様では、半導体層の下部に半導体層と電気的に接続する導電層208を設けることで、低濃度不純物領域における不純物濃度を低下させることなくドレイン耐圧を向上させることができる。また、逆極性キャリアに起因する問題を抑制することができる。つまり、絶縁表面を有する基板をベース基板として用いる場合に生じる、オン電流の低下抑制とドレイン耐圧の向上の両立という課題を解決することができ、また、トランジスタのドレイン耐圧低下抑制の問題を解決することができる。なお、オン電流の低下を抑制するためには、低濃度不純物領域の不純物濃度は、例えば、 $5 \times 10^{16}$  atoms/cm<sup>3</sup>以上とすればよい。

20

#### 【0116】

次に、半導体装置に用いる半導体基板の作製方法について図8を参照して説明する。具体的には、ボンド基板110の加工方法について詳細に説明する。

#### 【0117】

まず、ボンド基板110を用意する（図8（A）参照）。ボンド基板110の詳細については、先の実施の形態を参照できる。

30

#### 【0118】

次に、ボンド基板110にイオンを添加（照射）することにより、脆化領域112を形成する（図8（B）参照）。脆化領域112の形成の詳細については先の実施の形態を参照することができる。

#### 【0119】

なお、イオンの照射工程の前に、ボンド基板110の表面に保護絶縁層として機能する絶縁層を形成しても良い。もちろん、当該絶縁層を設けない構成とすることもできるが、後のイオン照射の際のボンド基板110の汚染やボンド基板110の表面の損傷を防ぐためには、絶縁層を設けることが好ましい。詳細については、先の実施の形態を参照すればよい。

#### 【0120】

脆化領域112を形成した後には、ボンド基板110の表面に導電層200を形成する（図8（C）参照）。導電層200は、スパッタリング法や真空蒸着法などにより形成することができる。詳細については、先の実施の形態の導電層102に関する記述を参照すればよい。

40

#### 【0121】

その後、導電層200を所定の形状に加工（パターニング）することで、導電層202を形成する（図8（D）参照）。

#### 【0122】

そして、導電層202を覆うように絶縁層204を形成する（図8（E）参照）。絶縁層204は、先の実施の形態の絶縁層104と同様にして形成することができる。

50

#### 【0123】

その後、絶縁層 204 を一部除去した絶縁層 206 を形成する（図 8（F）参照）。絶縁層 206 上には、後の接合に係る層を形成することになるため、平坦化処理を施しておくことが望ましい。平坦化処理の一例としては、エッティング処理（エッチバック処理）を挙げることができる。該エッティング処理は、ドライエッティングまたはウエットエッティングのいずれか一方を用いて行っても良いし、双方を組み合わせて用いても良い。また、上述のエッティング処理に加えて、研磨（CMPなど）による平坦化処理を施しておいても良い。もちろん、研磨のみを単独で用いても良い。

#### 【0124】

なお、本実施の形態においては、導電層 202 の表面と絶縁層 206 の表面が同一平面上に存在する構成を示しているが、これは、導電層 202 によって、後に形成される導電層と半導体層とを電気的に接続させるためである。よって、導電層 202 がその機能を発揮できる態様であれば、上述の構成に限定して解釈する必要はない。

10

#### 【0125】

次に、導電層 202 および絶縁層 206 上に、導電層 208 および絶縁層 114 を形成する（図 8（G）参照）。導電層 208 は、導電層 200 と同様にして形成することができる。また、絶縁層 114 の詳細については、先の実施の形態を参照すればよい。

#### 【0126】

以上により、ボンド基板 110 を半導体基板の製造に用いる態様に加工することができる。

20

#### 【0127】

ベース基板とボンド基板との貼り合わせおよび分離による半導体基板の作製工程については、先の実施の形態（例えば、図 3 や図 6 に係る説明）を参照することができる。

#### 【0128】

次に、半導体装置の作製方法について、図 9 を参照して説明する。

#### 【0129】

図 9（A）は、上述の加工工程を経たボンド基板を用いて作製された半導体基板の一部を拡大した断面図に相当する。図 9（A）から分かるように、半導体層 140 の下部には導電層 208 が存在し、これらは導電層 202 を介して電気的に接続されている。なお、図 9（A）に示す半導体基板はベース基板 100 側に絶縁層 104 を設けていないが、開示する発明の一態様はこれに限定して解釈されない。

30

#### 【0130】

半導体層 140 には、トランジスタのしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型を付与する不純物、または、リン、砒素などの n 型を付与する不純物を添加しても良い。不純物を添加する領域、および添加する不純物の種類は、適宜変更することができる。例えば、n チャネル型トランジスタを形成する場合には p 型を付与する不純物を添加し、p チャネル型トランジスタを形成する場合には n 型を付与する不純物を添加することができる。

#### 【0131】

上記半導体層 140 に対してエッティング処理を施すことにより、半導体層 140 を島状に分離して島状の半導体層 150 を形成する。なお、エッティング処理はウエットエッティング処理としても良いし、ドライエッティング処理としても良い。そして、半導体層 150 を覆うように、ゲート絶縁層 152 を形成する。ゲート絶縁層 152 の詳細は先の実施の形態を参照することができる。

40

#### 【0132】

次に、ゲート絶縁層 152 上に導電層を形成した後、該導電層を所定の形状に加工（パターニング）することで、半導体層 150 の上方にゲート電極 154 を形成する（図 9（B）参照）。ゲート電極 154 の詳細についても、先の実施の形態を参照することができる。

#### 【0133】

次に、ゲート電極 154 をマスクとして用いて、一導電型を付与する不純物元素を半導体

50

層 150 に添加し、低濃度不純物領域を形成する。そして、低濃度不純物領域の一部と重畳するようにマスクを形成した後、当該マスクを用いて一導電型を付与する不純物元素を半導体層に添加する。これにより、高濃度不純物領域 162 および高濃度不純物領域 164 が形成されると共に、低濃度不純物領域 166 およびチャネル形成領域 168 が形成される。

#### 【 0134】

次に、半導体層 150、ゲート絶縁層 152、ゲート電極 154 などを覆うように絶縁層 170 を形成する（図 9（C）参照）。絶縁層 170 については、先の実施の形態を参酌することができる。

#### 【 0135】

次に、ゲート絶縁層 152 および絶縁層 170 を選択的にエッチングして、高濃度不純物領域 162 および高濃度不純物領域 164 に達するコンタクトホールを形成する。そして、該コンタクトホールを通じて、半導体層 150 の高濃度不純物領域 162 と電気的に接続する電極 172、および半導体層 150 の高濃度不純物領域 164 と電気的に接続する電極 174 を形成する（図 9（D）参照）。なお、コンタクトホールを形成する際には、ウエットエッチング処理またはドライエッチング処理のいずれを用いても良い。また、電極 172 および電極 174 の詳細については、先の実施の形態を参酌すればよい。

10

#### 【 0136】

以上により、大電圧、大電流などの用途に用いられるトランジスタ 280 を含む半導体装置を作製することができる。

20

#### 【 0137】

本実施の形態において示すように、半導体層の下部に、半導体層と電気的に接続する導電層を設けることで、低濃度不純物領域における電界を緩和すると共に、逆極性キャリアに起因するアバランシェ降伏を抑制して、ドレイン耐圧を一層向上させることが可能である。

。

#### 【 0138】

なお、本実施の形態は先の実施の形態と適宜組み合わせて用いることができる。

#### 【 符号の説明】

#### 【 0139】

|     |          |    |

|-----|----------|----|

| 100 | ベース基板    | 30 |

| 102 | 導電層      |    |

| 104 | 絶縁層      |    |

| 110 | ボンド基板    |    |

| 112 | 脆化領域     |    |

| 114 | 絶縁層      |    |

| 120 | 半導体層     |    |

| 122 | 半導体基板    |    |

| 130 | レーザー光    |    |

| 140 | 半導体層     |    |

| 150 | 半導体層     | 40 |

| 152 | ゲート絶縁層   |    |

| 154 | ゲート電極    |    |

| 156 | 低濃度不純物領域 |    |

| 158 | 低濃度不純物領域 |    |

| 160 | マスク      |    |

| 162 | 高濃度不純物領域 |    |

| 164 | 高濃度不純物領域 |    |

| 166 | 低濃度不純物領域 |    |

| 168 | チャネル形成領域 |    |

| 170 | 絶縁層      | 50 |

|       |        |

|-------|--------|

| 1 7 2 | 電極     |

| 1 7 4 | 電極     |

| 1 8 0 | トランジスタ |

| 1 9 0 | 絶縁層    |

| 1 9 2 | 導電層    |

| 2 0 0 | 導電層    |

| 2 0 2 | 導電層    |

| 2 0 4 | 絶縁層    |

| 2 0 6 | 絶縁層    |

| 2 0 8 | 導電層    |

| 2 8 0 | トランジスタ |

10

【図1】

(A)

(B)

【図2】

(A)

(B)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51) Int.Cl.

F I

H 0 1 L 29/78 6 1 7 L

テーマコード(参考)

F ターム(参考) 5F110 AA07 AA13 CC02 DD01 DD02 DD03 DD04 DD05 DD07 DD12

DD13 DD14 DD15 DD17 DD22 EE01 EE02 EE03 EE04 EE06

EE08 EE14 EE15 EE30 EE44 EE45 FF01 FF02 FF03 FF04

FF22 FF23 FF26 FF28 FF30 GG01 GG02 GG03 GG04 GG12

GG13 GG32 GG57 GG60 HJ01 HJ04 HL01 HL02 HL03 HL04

HL06 HL08 HL11 HL12 HL22 HL23 HM12 HM15 NN02 NN22

NN23 NN24 NN27 PP03 PP04 PP13 PP26 QQ11 QQ17 QQ19