(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6087652号

(P6087652)

(45) 発行日 平成29年3月1日(2017.3.1)

(24) 登録日 平成29年2月10日(2017.2.10)

(51) Int.Cl.

F 1

|                |           |              |         |

|----------------|-----------|--------------|---------|

| G 11 C 11/412  | (2006.01) | G 11 C 11/40 | 3 O 1   |

| G 11 C 11/41   | (2006.01) | G 11 C 11/40 | Z       |

| G 06 F 12/08   | (2016.01) | G 06 F 12/08 | 5 5 3 B |

| H 01 L 21/8244 | (2006.01) | H 01 L 27/10 | 3 8 1   |

| H 01 L 27/11   | (2006.01) | H 01 L 29/78 | 6 1 3 B |

請求項の数 1 (全 29 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2013-25228 (P2013-25228)    |

| (22) 出願日     | 平成25年2月13日 (2013.2.13)        |

| (65) 公開番号    | 特開2013-191266 (P2013-191266A) |

| (43) 公開日     | 平成25年9月26日 (2013.9.26)        |

| 審査請求日        | 平成27年11月18日 (2015.11.18)      |

| (31) 優先権主張番号 | 特願2012-32437 (P2012-32437)    |

| (32) 優先日     | 平成24年2月17日 (2012.2.17)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 小山 潤                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| 審査官       | 堀田 和義               |

最終頁に続く

(54) 【発明の名称】 記憶回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第1のインバータと、第2のインバータと、第1の容量素子と、第2の容量素子と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のインバータの入力と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタを介して前記第2のインバータの出力と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第5のトランジスタを介して前記第1の容量素子と電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2のインバータの入力と電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第4のトランジスタを介して前記第1のインバータの出力と電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第6のトランジスタを介して前記第2の容量素子と電気的に接続され、

前記第3のトランジスタのゲートは、第1の配線に電気的に接続され、

前記第4のトランジスタのゲートは、第2の配線に電気的に接続され、

前記第1の配線と前記第2の配線には、異なる信号が入力され、

10

20

前記第5のトランジスタと前記第6のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタであり、チャネル幅1μmあたりのオフ電流が100zA以下であることを特徴とする記憶回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記憶回路に関する。また、本発明は、上記記憶回路を有するキャッシュメモリを含む半導体装置に関する。

【背景技術】

【0002】

近年、中央演算処理装置(CPUともいう)などを有する半導体装置において、動作の高速化に関する技術開発が活発に行われている。

10

【0003】

例えば、キャッシュメモリを用いて記憶容量を大きくしつつ、CPUの処理速度の低下を抑制する技術が知られている。

【0004】

キャッシュメモリは、メインメモリのデータを一時的に記憶する機能を有するメモリである。CPUの演算は、メインメモリの応答よりも速い。このため、キャッシュメモリを用いてキャッシュ部を構成することにより、CPUが演算待ちの状態にならず、処理速度の低下を抑制できる。また、近年では、1次キャッシュ、2次キャッシュ、さらには3次キャッシュと、記憶データの使う頻度に応じてキャッシュメモリを用いたキャッシュ部を複数の階層にしてCPUの処理速度の低下をさらに抑制する技術も知られている。

20

【0005】

上記キャッシュメモリは、例えば静态ランダムアクセスメモリ(SRAMともいう)などの記憶回路を用いて構成される(例えば特許文献1)。

【0006】

また、その他の動作の高速化に関する技術開発として、CPUの動作速度及び集積度を向上させるためにトランジスタなどの半導体素子の微細化が行われており、例えばゲート長が30nmである半導体素子を有する半導体装置が製造されている。

【0007】

30

しかし、CPUを微細化することによって、トランジスタのリーク電流が増加し、消費電力が増加している。従来は、CPUの消費電力のほとんどは演算時の動作電力であったが、近年は、微細化によって上記消費電力の1割以上をトランジスタのリーク電流が占めるようになった。

【0008】

そのため、電源供給制御スイッチであるパワーゲートを用いて、使用していない回路に対する電源電圧の供給を停止し、消費電力を下げる方法が検討されており、キャッシュメモリもその例外ではない。

【先行技術文献】

【特許文献】

40

【0009】

【特許文献1】特開2002-269987号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、キャッシュメモリを構成するSRAMは揮発性メモリであるため、電源電圧の供給が停止すると記憶データが消失してしまう。上記問題を解消するためには、電源電圧の供給を停止した場合であってもSRAMに記憶されたデータが消えないようにする必要がある。

【0011】

50

上記問題を解消する方法の一つとして、S R A Mに不揮発性記憶素子を適用することが検討されている。キャッシュメモリは本来の目的から、高速性が要求されるため、不揮発性メモリとしてフラッシュメモリは使用できない。そのため、不揮発性記憶素子としては、例えば磁気抵抗メモリ（M R A Mともいう）が検討されている。

#### 【 0 0 1 2 】

しかしながら、従来の不揮発性記憶素子を用いたS R A Mは、特性が十分ではなく、実用化されていない。

#### 【 0 0 1 3 】

例えば、M R A Mは、高速ではあるが書き込み時の電力が大きいという問題があり、電源電圧の供給の停止期間が短い場合、かえって消費電力が増えてしまうというジレンマがある。なお、M R A Mの1セルあたりの書き込み電流は $50 \sim 500 \mu A$ であるといわれている。10

#### 【 0 0 1 4 】

本発明の一態様では、電源電圧の供給を停止した場合であっても、データの保持を可能にすることを課題の一つとする。また、本発明の一態様では、消費電力を低減することを課題の一つとする。

#### 【課題を解決するための手段】

#### 【 0 0 1 5 】

本発明の一態様では、第1及び第2のインバータにより第1及び第2の記憶データを記憶する記憶回路に、オフ電流の低いトランジスタを用いた記憶部を設けることにより、電源電圧の供給を停止する場合に該記憶部に第1及び第2の記憶データを書き込んでおき、電源電圧の供給を停止した場合であっても、第1及び第2の記憶データの保持を可能にする。20

#### 【 0 0 1 6 】

また、本発明の一態様では、第1のインバータの入力端子と第2のインバータとの出力端子の導通を制御するトランジスタと、第1のインバータの出力端子と第2のインバータの入力端子との導通を制御するトランジスタを設ける。これにより、電源電圧の供給を停止する前に記憶したデータを電源電圧の供給を再開した後に読み出す際に、第1及び第2のインバータにより該データが消失することを防止する。

#### 【 0 0 1 7 】

本発明の一態様では、C P Uを設け、さらに上記記憶回路をキャッシュメモリに用いて半導体装置を構成する。これにより、非動作期間に電源電圧の供給を停止して消費電力の低減を図る。30

#### 【 0 0 1 8 】

本発明の一態様は、オン状態又はオフ状態になることにより、第1の記憶データの書き換え及び読み出しを制御する第1のトランジスタと、オン状態又はオフ状態になることにより、第2の記憶データの書き換え及び読み出しを制御する第2のトランジスタと、入力端子の電位が第1の記憶データとなる第1のインバータと、入力端子の電位が第2の記憶データとなる第2のインバータと、オン状態又はオフ状態になることにより、第2のインバータの出力端子と第1のインバータの入力端子との導通を制御する第3のトランジスタと、オン状態又はオフ状態になることにより、第1のインバータの出力端子と第2のインバータの入力端子との導通を制御する第4のトランジスタと、第1の保持データとして第1の記憶データが書き込まれる第1の容量素子と、オン状態又はオフ状態になることにより、第1の保持データの書き換え及び読み出しを制御する第5のトランジスタと、第2の保持データとして第2の記憶データが書き込まれる第2の容量素子と、オン状態又はオフ状態になることにより、第2の保持データの書き換え及び読み出しを制御する第6のトランジスタと、を有し、第5及び第6のトランジスタにおいて、チャネル幅 $1 \mu m$ あたりのオフ電流が $100 zA$ 以下である記憶回路である。40

#### 【 0 0 1 9 】

また、本発明の一態様は、上記記憶回路を有するキャッシュメモリと、入力信号に従い演50

算処理を行う機能を有し、演算処理の際に、キャッシュメモリに対してデータの読み出しを行うCPUと、CPUに対する電源電圧の供給を制御する第1の電源供給制御スイッチと、キャッシュメモリに対する電源電圧の供給を制御する第2の電源供給制御スイッチと、入力信号、及びCPUから入力される命令信号に従って第1及び第2の電源供給制御スイッチのそれぞれを個別に制御する機能を少なくとも有するコントローラと、を備える半導体装置である。

【発明の効果】

【0020】

本発明の一態様では、オフ電流の低いトランジスタを用いた記憶回路により、電源電圧の供給を停止した場合であってもデータを保持できる。また、本発明の一態様により、書き込み又は読み出し動作を行わない期間に記憶回路に対する電源電圧の供給を停止できるため、消費電力を低減できる。10

【図面の簡単な説明】

【0021】

【図1】記憶回路の例を説明するための図。

【図2】記憶回路の例を説明するための図。

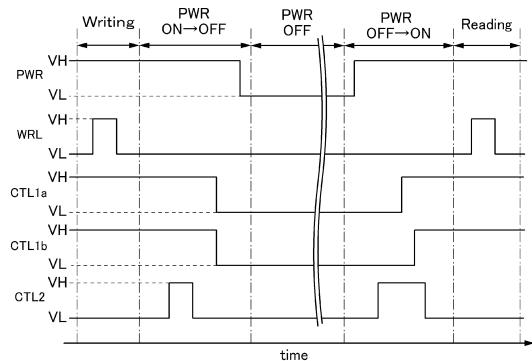

【図3】記憶回路の駆動方法例を説明するためのタイミングチャート。

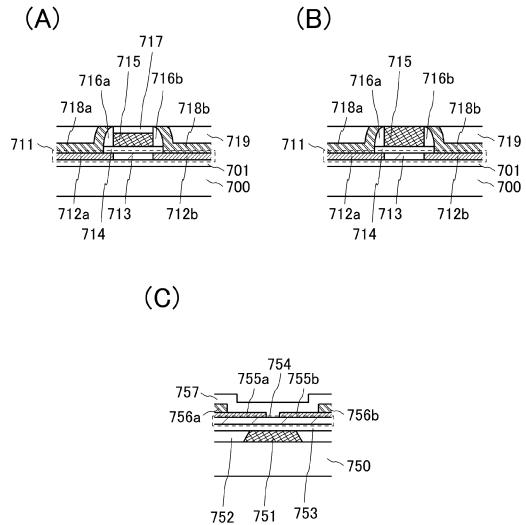

【図4】トランジスタの例を説明するための断面模式図。

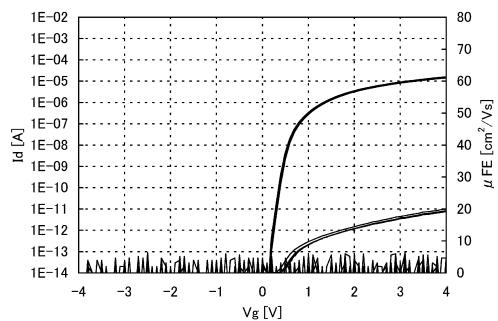

【図5】トランジスタの $I_d - V_g$ 特性を示す図。

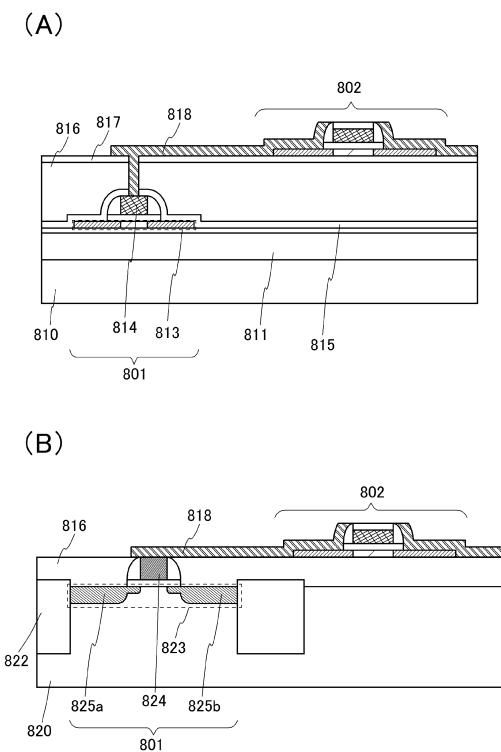

【図6】記憶回路の構造例を説明するための断面模式図。20

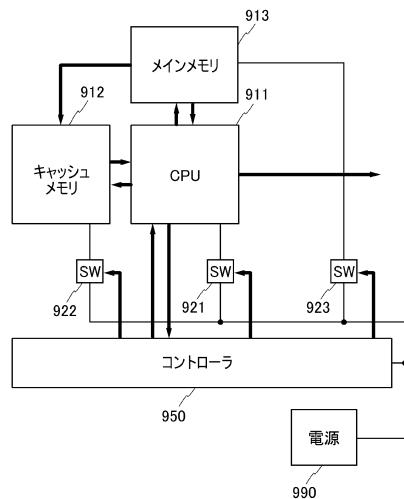

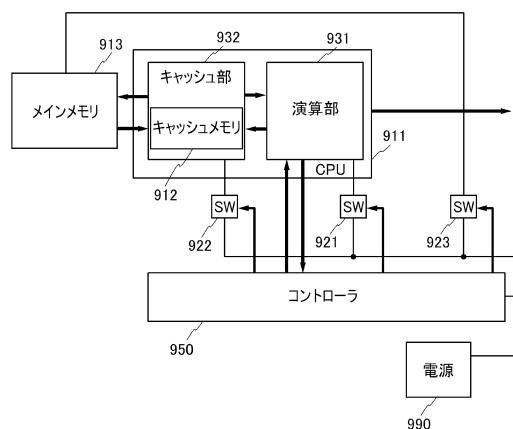

【図7】半導体装置の例を説明するための図。

【図8】半導体装置の例を説明するための図。

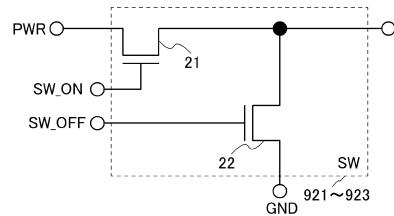

【図9】電源供給制御スイッチの構成例を説明するための図。

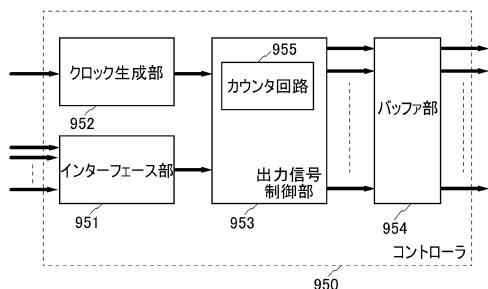

【図10】コントローラの構成例を説明するための図。

【図11】電子機器の例を説明するための図。

【発明を実施するための形態】

【0022】

本発明に係る実施の形態の例について説明する。なお、本発明の趣旨及び範囲から逸脱することなく実施の形態の内容を変更することは、当業者であれば容易である。よって、例えば本発明は、下記実施の形態の記載内容に限定されない。30

【0023】

なお、各実施の形態の内容を互いに適宜組み合わせることができる。また、各実施の形態の内容を互いに適宜置き換えることができる。

【0024】

また、構成要素の混同を避けるために第1、第2などの序数を付しているが、各構成要素の数は、序数に限定されない。

【0025】

(実施の形態1)

本実施の形態では、電源電圧の供給を停止してもデータの保持が可能な記憶回路の例について説明する。40

【0026】

本実施の形態に係る記憶回路の構成例について、図1を参照して説明する。

【0027】

図1(A)に示す記憶回路は、トランジスタ111乃至116と、トランジスタ117及び118を備えるインバータ131と、トランジスタ119及び120を備えるインバータ132と、容量素子151及び152と、を有する。

【0028】

トランジスタ111のソース及びドレインの一方は、データ信号線DL1に電気的に接続される。また、トランジスタ111のゲートは、ワード線WRLに電気的に接続される。

【0029】

10

20

30

40

50

トランジスタ 111 は、オン状態又はオフ状態になることにより、記憶データ D1 の書き換え及び読み出しを制御する機能を有する。

【0030】

トランジスタ 112 のソース及びドレインの一方は、データ信号線 D L 2 に電気的に接続される。また、トランジスタ 112 のゲートは、ワード線 W R L に電気的に接続される。

【0031】

トランジスタ 112 は、オン状態又はオフ状態になることにより、記憶データ D2 の書き換え及び読み出しを制御する機能を有する。

【0032】

インバータ 131 の入力端子は、トランジスタ 111 のソース及びドレインの他方に電気的に接続される。 10

【0033】

このとき、インバータ 131 の入力端子の電位は、記憶データ D1 となる。

【0034】

インバータ 131 は、トランジスタ 117 及び 118 により構成される。トランジスタ 117 は、P チャネル型トランジスタであり、トランジスタ 118 は、N チャネル型トランジスタである。このとき、トランジスタ 117 のソース及びドレインの一方は、電位供給線 P S L 1 に電気的に接続され、トランジスタ 118 のソース及びドレインの一方は、電位供給線 P S L 2 に電気的に接続される。電源電圧供給時には、電位供給線 P S L 1 及び P S L 2 を介して電源電圧 P W R が供給される。 20

【0035】

インバータ 132 は、トランジスタ 119 及び 120 により構成される。トランジスタ 119 は、P チャネル型トランジスタであり、トランジスタ 120 は、N チャネル型トランジスタである。このとき、トランジスタ 119 のソース及びドレインの一方は、電位供給線 P S L 1 に電気的に接続され、トランジスタ 120 のソース及びドレインの一方は、電位供給線 P S L 2 に電気的に接続される。

【0036】

なお、トランジスタ 117 及び 118 の極性、又はトランジスタ 119 及び 120 の極性を逆にしてもよい。このとき、電位供給線 P S L 1 及び P S L 2 のそれぞれに供給される電位も逆になる。 30

【0037】

インバータ 132 の入力端子は、トランジスタ 112 のソース及びドレインの他方に電気的に接続される。

【0038】

このとき、インバータ 132 の入力端子の電位は、記憶データ D2 となる。

【0039】

トランジスタ 113 のソース及びドレインの一方は、インバータ 131 の入力端子に電気的に接続され、他方はインバータ 132 の出力端子に電気的に接続される。また、トランジスタ 113 のゲートは、制御信号線 C T L 1 に電気的に接続される。制御信号線 C T L 1 には、制御信号 A が入力される。 40

【0040】

トランジスタ 113 は、インバータ 132 の出力端子とインバータ 131 の入力端子との導通を制御する機能を有する。

【0041】

トランジスタ 114 のソース及びドレインの一方は、インバータ 132 の入力端子に電気的に接続され、他方はインバータ 131 の出力端子に電気的に接続される。また、トランジスタ 114 のゲートは、制御信号線 C T L 1 に電気的に接続される。

【0042】

トランジスタ 114 は、オン状態又はオフ状態になることにより、インバータ 131 の出力端子とインバータ 132 の入力端子との導通を制御する機能を有する。 50

## 【0043】

容量素子151の一対の電極の一方は、電位供給線P S L 2に電気的に接続される。

## 【0044】

容量素子151には、保持データHLD1として記憶データD1が書き込まれる。

## 【0045】

容量素子152の一対の電極の一方は、電位供給線P S L 2に電気的に接続される。

## 【0046】

容量素子152には、保持データHLD2として記憶データD2が書き込まれる。

## 【0047】

容量素子151及び152は、データを保持する保持容量としての機能を有する。なお、

10

例えばトランジスタのゲート容量や、複数の配線間の寄生容量などを用いて容量素子15

1及び152を構成してもよい。

## 【0048】

トランジスタ115のソース及びドレインの一方は、インバータ131の入力端子に電気

的に接続され、他方は容量素子151の一対の電極の他方に電気的に接続される。また、

トランジスタ115のゲートは、制御信号線CTL2に電気的に接続される。制御信号線

CTL2には、制御信号Bが入力される。

## 【0049】

トランジスタ115は、オン状態又はオフ状態になることにより、保持データHLD1の

20

書き換え及び読み出しを制御する機能を有する。

## 【0050】

トランジスタ116のソース及びドレインの一方は、インバータ132の入力端子に電気

的に接続され、他方は容量素子152の一対の電極の他方に電気的に接続される。また、

トランジスタ116のゲートは、制御信号線CTL2に電気的に接続される。

## 【0051】

トランジスタ116は、オン状態又はオフ状態になることにより、保持データHLD2の

書き換え及び読み出しを制御する機能を有する。

## 【0052】

トランジスタ115及び116としては、例えばオフ電流が低いトランジスタを適用でき

る。

30

## 【0053】

このとき、上記オフ電流の低いトランジスタのオフ電流は、チャネル幅1μmあたり $1 \times 10^{-19} A$  ( $100 zA$ ) 以下であることが好ましい。

## 【0054】

上記オフ電流の低いトランジスタとしては、例えばシリコンよりもバンドギャップの広い

酸化物半導体材料を含むチャネル形成領域を有し、該チャネル形成領域が実質的にi型で

あるトランジスタを適用できる。上記酸化物半導体を含むトランジスタは、例えば水素又

は水などの不純物を可能な限り除去し、酸素を供給して酸素欠損を可能な限り減らすこと

により作製できる。

## 【0055】

上記酸化物半導体を含むトランジスタは、バンドギャップが広いため熱励起によるリーク

電流が低い。さらに、半導体層中のキャリアが極めて少ない。よって、オフ電流を低くで

きる。例えば、酸化物半導体層のキャリア密度を $1 \times 10^{14} / cm^3$ 未満、好ましくは

$1 \times 10^{12} / cm^3$ 未満、さらに好ましくは $1 \times 10^{11} / cm^3$ 未満にし、チャネル

幅1μmあたりのトランジスタのオフ電流を $1 \times 10^{-19} A$  ( $100 zA$ ) 以下、より

好ましくは $1 \times 10^{-22} A$  ( $100 yA$ ) 以下にすることができる。トランジスタのオ

フ電流は、低ければ低いほどよいが、トランジスタのオフ電流の下限値は、約 $1 \times 10^{-30} A / \mu m$ であると見積もられる。

## 【0056】

トランジスタ115及び116に上記オフ電流の低いトランジスタを用いることにより、

50

電源電圧の供給が停止した場合であっても容量素子 151 及び 152 にデータを保持できる。

**【0057】**

さらに、図 1 (A) に示す記憶回路の書き込み電流は低いことが好ましい。

**【0058】**

例えば、図 1 (A) に示す記憶回路の書き込み電流を、 $10 \mu A$  以下、好ましくは $1 \mu A$  以下にすることもできる。算出例について以下に説明する。

**【0059】**

例えば、線形領域におけるトランジスタのオン抵抗は、下記式 (1) により求めることができる。

10

**【0060】**

**【数1】**

$$R_d = \frac{Vd}{Id} = \frac{Vd}{\frac{W}{L} \mu Cox \left\{ (Vg - Vth)Vd - \frac{1}{2}Vd^2 \right\}} \quad (1)$$

**【0061】**

上記式 (1)において、 $R_d$  はトランジスタのオン抵抗であり、 $I_d$  はトランジスタのソースとドレインの間に流れる電流 (ドレイン電流ともいう) であり、 $V_d$  はトランジスタのソースとドレインの間の電圧 (ドレイン電圧ともいう) であり、 $L$  はトランジスタのチャネル長であり、 $W$  はトランジスタのチャネル幅であり、 $\mu$  はトランジスタの移動度であり、 $Cox$  はトランジスタのゲート容量であり、 $V_g$  はトランジスタのゲートとソースの間の電圧 (ゲート電圧ともいう) であり、 $V_{th}$  はトランジスタの閾値電圧である。

20

**【0062】**

このとき、記憶回路の仕様例に従って、例えばトランジスタ 111、112、115、及び 116 のそれぞれにおいて、移動度  $\mu$  が  $10 \text{ cm}^2 / \text{Vs}$  であり、ゲート容量  $Cox$  が  $1.82 \times 10^{-3} \text{ F/m}^2$  であり、閾値電圧  $V_{th}$  が  $0.5 \text{ V}$  であり、チャネル長  $L$  が  $1 \mu \text{m}$  であり、チャネル幅  $W$  が  $1 \mu \text{m}$  であり、ワード線  $WRL$ 、制御信号線  $CTL1$  の電位が  $3.3 \text{ V}$  であり、データ信号線  $DL1$  又は  $DL2$  の電位が  $1.8 \text{ V}$  であるとする。このときのソースとドレインの間の抵抗値  $R_d$  は約  $300 \text{ k}\Omega$  となる。さらに、データ信号線  $DL1$  又は  $DL2$  の電位が  $1.8 \text{ V}$  であるため、データ信号線  $DL1$  又は  $DL2$  に対応する書き込み電流の平均値は、 $1.8 \text{ V} / (300 \text{ k}\Omega \times 2) = 3 \mu \text{A}$  となる。また、容量素子 151 及び 152 の容量値は、 $1 \text{ fF}$  程度であればよく、このときの容量素子 151 又は 152 が定常状態になるまでの時間は、 $(1.8 \times 1 \times 10^{-15}) / 3 \times 10^{-6} = 0.6 \text{ nsec}$  である。よって、容量素子 151 又は 152 が定常状態になるまでに必要な書き込み電流は、上記平均値よりもさらに低く、例えば  $1 \mu \text{A}$  以下にすることもできる。

30

**【0063】**

上記に一例として示すように、本実施の形態の記憶回路では、書き込み電流を低くできるため、記憶回路の消費電力を低減できる。

40

**【0064】**

また、トランジスタ 111 乃至 114、トランジスタ 117 乃至 120 としては、例えばチャネルが形成され、シリコンを含有する半導体層を含むトランジスタを適用できる。また、これに限定されず、例えばトランジスタ 111 乃至 114 として、上記トランジスタ 115 及び 116 に適用可能なトランジスタを適用してもよい。

**【0065】**

以上が図 1 (A) に示す記憶回路の構成例の説明である。

**【0066】**

次に、本実施の形態に係る記憶回路の駆動方法例として、図 1 (A) に示す記憶回路の駆

50

動方法例について、図1( B )のタイミングチャートを参照して説明する。なお、トランジスタ111乃至114はNチャネル型トランジスタとする。また、ハイレベルの信号の電位を電位VHとし、ローレベルの信号の電位を電位VLとする。また、電位供給線PSL1の電位を電位VHとし、電位供給線PSL2の電位を電位VLとする。また、図1( B )の二重波線は、省略記号である。

#### 【0067】

図1( A )に示す記憶回路の駆動方法例では、書き換え期間( Writing )において、電源電圧PWRを供給し、また、データ信号線DL1及びDL2の電位を設定する。このとき、データ信号線DL1及びDL2の一方の電位は電位VHであり、他方の電位は電位VLである。また、電位VH及びVLの一方を、データ「1」とし、他方をデータ「0」とする。

10

#### 【0068】

さらに、ワード信号線WRLの電位を電位VHにしてトランジスタ111及び112をオン状態にする。また、制御信号線CTL1の電位を電位VHにしてトランジスタ113及び114をオン状態にする。また、制御信号線CTL2の電位を電位VLにしてトランジスタ115及び116をオフ状態にする。

#### 【0069】

このとき、記憶データD1としてデータ信号線DL1の電位が書き込まれ、記憶データD2としてデータ信号線DL2の電位が書き込まれる。

#### 【0070】

その後、ワード信号線WRLの電位を電位VLにしてトランジスタ111及び112をオフ状態にする。これにより、記憶データD1及びD2が保持される。

20

#### 【0071】

また、電源停止移行期間( PWR ON OFF )では、電源電圧PWRを供給したまま、ワード信号線WRLの電位を電位VLにしてトランジスタ111及び112をオフ状態にする。また、制御信号線CTL1の電位を電位VHにしてトランジスタ113及び114をオン状態にしたまま、制御信号線CTL2の電位を電位VHにしてトランジスタ115及び116をオン状態にする。

#### 【0072】

このとき、容量素子151には、保持データHLD1として記憶データD1が書き込まれる。また、容量素子152には、保持データHLD2として記憶データD2が書き込まれる。

30

#### 【0073】

さらに、制御信号線CTL2の電位を電位VLにしてトランジスタ115及び116をオフ状態にすることにより、保持データHLD1及びHLD2が保持される。

#### 【0074】

その後、制御信号線CTL1の電位を電位VLにしてトランジスタ113及び114をオフ状態にし、また、記憶回路に対する電源電圧PWRの供給を停止する。例えば、パワーゲートと呼ばれる電源供給制御スイッチを用いて電位供給線PSL1及びPSL2の少なくとも一方を介した電位の供給を停止することにより、記憶回路に対する電源電圧PWRの供給を停止できる。

40

#### 【0075】

電源停止期間( PWR OFF )では、記憶回路に対する電源電圧PWRの供給が停止していても容量素子151の保持データHLD1及び容量素子152の保持データHLD2が引き続き保持される。

#### 【0076】

電源供給再開移行期間( PWR OFF ON )では、記憶回路に対する電源電圧PWRの供給を再開した後に、ワード信号線WRL及び制御信号線CTL1の電位を電位VLにしてトランジスタ111乃至114をオフ状態にしたまま、制御信号線CTL2の電位を電位VHにしてトランジスタ115及び116をオン状態にする。

50

**【 0 0 7 7 】**

このとき、容量素子 151 の保持データ HLD1 が記憶データ D1 として読み出され、容量素子 152 の保持データ HLD2 が記憶データ D2 として読み出される。

**【 0 0 7 8 】**

なお、このとき、トランジスタ 113 及び 114 をオフ状態にすることにより、記憶回路に対する電源電圧の供給を再開した直後にインバータ 131 及び 132 の出力端子の電位が不定値になった場合であっても保持データ HLD1 及び HLD2 を消失させずに読み出すことができる。

**【 0 0 7 9 】**

このように、電源電圧の供給を再開するときにトランジスタ 113 及び 114 の導通を制御することにより、保持データ HLD1 及び HLD2 の消失を防止できる。 10

**【 0 0 8 0 】**

その後、ワード信号線 WRL の電位を電位 VL にしてトランジスタ 111 及び 112 をオフ状態にし、制御信号線 CTL1 の電位を電位 VH にしてトランジスタ 113 及び 114 をオン状態にし、制御信号線 CTL2 の電位を電位 VL にしてトランジスタ 115 及び 116 をオフ状態にすることにより、インバータ 131 及び 132 により記憶データ D1 及び D2 が再び保持される。

**【 0 0 8 1 】**

また、読み出し期間 (Reading) では、ワード信号線 WRL の電位を電位 VH にしてトランジスタ 111 及び 112 をオン状態にする。また、制御信号線 CTL1 の電位を電位 VH にしてトランジスタ 113 及び 114 をオン状態にする。また、制御信号線 CTL2 の電位を電位 VL にしてトランジスタ 115 及び 116 をオフ状態にする。 20

**【 0 0 8 2 】**

このとき、記憶データ D1 の電位に応じてデータ信号線 DL1 の電位が設定され、記憶データ D2 の電位に応じてデータ信号線 DL2 の電位が設定される。よって、記憶回路に記憶された記憶データ D1 及び D2 が読み出される。

**【 0 0 8 3 】**

なお、書き換え期間と電源停止移行期間の間に読み出し期間を設けてもよい。

**【 0 0 8 4 】**

以上が図 1 (A) に示す記憶回路の駆動方法例の説明である。 30

**【 0 0 8 5 】**

なお、本実施の形態に係る記憶回路は、図 1 (A) に示す構成に限定されない。

**【 0 0 8 6 】**

例えば、図 2 (A) に示す記憶回路は、図 1 (A) に示す記憶回路のトランジスタ 113 のゲートが制御信号線 CTL1 の代わりに制御信号線 CTL1a に電気的に接続され、トランジスタ 114 のゲートが制御信号線 CTL1 の代わりに制御信号線 CTL1b に電気的に接続される構成である。

**【 0 0 8 7 】**

このとき、トランジスタ 113 のゲートには、第 1 の制御信号 A が入力され、トランジスタ 114 のゲートには、第 2 の制御信号 A が入力される。 40

**【 0 0 8 8 】**

また、これに限定されず、図 2 (B) に示すように、トランジスタ 113 のゲートが制御信号線 CTL1b に電気的に接続され、トランジスタ 114 のゲートが制御信号線 CTL1a に電気的に接続される構成にしてもよい。このとき、トランジスタ 113 のゲートには、第 2 の制御信号 A が入力され、トランジスタ 114 のゲートには、第 1 の制御信号 A が入力される。

**【 0 0 8 9 】**

さらに、図 2 (A) 及び図 2 (B) に示す記憶回路の駆動方法例では、図 1 (A) に示す記憶回路の駆動方法例と比較して、電源供給再開移行期間の動作が異なる。ここでは、一例として図 2 (A) に示す記憶回路の駆動方法例について図 3 のタイミングチャートを参 50

照して説明する。

**【0090】**

電源供給再開移行期間では、制御信号線 C T L 1 b の電位が電位 V L のときに、制御信号線 C T L 1 a の電位を電位 V H にしてトランジスタ 113 をオン状態にする。その後、制御信号線 C T L 1 b の電位を電位 V H にしてトランジスタ 114 をオン状態にする。

**【0091】**

トランジスタ 113 をオン状態にするタイミングとトランジスタ 114 をオン状態にするタイミングをずらすことにより、電源電圧の供給を再開したときにインバータ 131 及び 132 の出力端子の電位をより安定に設定できる。

**【0092】**

以上が本実施の形態に係る記憶回路の例の説明である。

10

**【0093】**

図 1 乃至図 3 を参照して説明したように、本実施の形態に係る記憶回路の一例では、オフ電流の低いトランジスタを用いた記憶部を設けて記憶回路を構成する。

**【0094】**

これにより、記憶回路に対する電源電圧の供給を停止した場合であってもデータを保持できる。よって、記憶回路に対する書き込み動作又は読み出し動作を行わないときに記憶回路に対する電源電圧の供給を停止して消費電力を低減できる。

**【0095】**

また、本実施の形態に係る記憶回路の一例では、第 1 のインバータ（例えばインバータ 131）の入力端子と第 2 のインバータ（例えばインバータ 132）の出力端子との導通を制御するトランジスタ（例えばトランジスタ 113）と第 2 のインバータの入力端子と第 1 のインバータの出力端子との導通を制御するトランジスタ（例えばトランジスタ 114）を用いて記憶回路を構成する。

20

**【0096】**

これにより、電源電圧の供給を再開した後に第 1 の記憶データ（例えば記憶データ D 1）として第 1 の容量素子（例えば容量素子 151）の第 1 の保持データ（例えば保持データ HLD 1）を読み出し、第 2 の記憶データ（例えば記憶データ D 2）として第 2 の容量素子（例えば容量素子 152）の第 2 の保持データ（例えば保持データ HLD 2）を読み出す際に、インバータ 131 及び 132 により第 1 及び第 2 の保持データが消失してしまうのを防止できる。

30

**【0097】**

**(実施の形態 2)**

本実施の形態では、実施の形態 1 に係る記憶回路の構造例について説明する。

**【0098】**

まず、記憶回路に適用可能なトランジスタの構造の一例について、図 4 の断面模式図を参照して説明する。なお、図 4 に示す各構成要素は、実際の寸法と異なる場合がある。

**【0099】**

図 4 (A) に示すトランジスタは、半導体層 711 と、絶縁層 714 と、導電層 715 と、絶縁層 716a 及び 716b と、絶縁層 717 と、導電層 718a 及び 718b と、絶縁層 719 と、を含む。

40

**【0100】**

半導体層 711 は、絶縁層 701 を介して被素子形成層 700 の上に設けられる。なお、必ずしも絶縁層 701 の上に半導体層 711 を設けなくてもよく、被素子形成層 700 上に半導体層 711 を直接設けてよい。

**【0101】**

半導体層 711 は、互いに離間して、ドーパントが添加された領域 712a 及び 712b を有し、領域 712a 及び 712b の間にチャネル形成領域 713 を有する。

**【0102】**

絶縁層 714 は、半導体層 711 の一部の上に設けられる。

50

**【 0 1 0 3 】**

導電層 715 は、絶縁層 714 を介して半導体層 711 に重畠して設けられる。

**【 0 1 0 4 】**

絶縁層 716a は、導電層 715 の一対の側面の一方に接して設けられ、絶縁層 716b は、該一対の側面の他方に接して設けられる。

**【 0 1 0 5 】**

絶縁層 717 は、導電層 715 の上に設けられる。なお、図 4 (B) に示すように、絶縁層 717 を設けなくてもよい。

**【 0 1 0 6 】**

導電層 718a は、領域 712a に接して設けられ、導電層 718b は、領域 712b に接して設けられる。また、導電層 718a は、絶縁層 716a の側面に接し、導電層 718b は、絶縁層 716b の側面に接する。10

**【 0 1 0 7 】**

絶縁層 719 は、導電層 718a 及び 718b の上に設けられる。

**【 0 1 0 8 】**

導電層 718a 及び 718b、並びに絶縁層 719 は、例えば導電膜及び絶縁層の積層に対して平坦化処理（例えば CMP 処理）を行うことにより形成される。

**【 0 1 0 9 】**

また、図 4 (C) に示すトランジスタは、導電層 751 と、絶縁層 752 と、絶縁層 753 と、半導体層 754 と、導電層 755a 及び 755b と、導電層 756a 及び 756b と、絶縁層 757 と、を有する。20

**【 0 1 1 0 】**

導電層 751 は、被素子形成層 750 の上に設けられる。

**【 0 1 1 1 】**

絶縁層 752 は、被素子形成層 750 の上に設けられる。絶縁層 752 及び導電層 751 の表面は平坦であることが好ましい。

**【 0 1 1 2 】**

導電層 751 及び絶縁層 752 は、例えば導電膜及び絶縁層の積層に対して平坦化処理（例えば CMP 処理）を行うことにより形成される。

**【 0 1 1 3 】**

絶縁層 753 は、導電層 751 及び絶縁層 752 の上に設けられる。30

**【 0 1 1 4 】**

半導体層 754 は、絶縁層 753 を介して導電層 751 に重畠して設けられる。

**【 0 1 1 5 】**

導電層 755a 及び 755b は、互いに離間し、半導体層 754 に電気的に接続される。このとき、導電層 755a と導電層 755b の間隔は、トランジスタのチャネル長に相当し、例えば 50 nm 未満であることが好ましい。例えば、電子ビームで露光して形成したレジストマスクを用いて、導電膜の一部をエッチングすることにより、導電層 755a と 755b の間隔を 50 nm 未満にできる。また、例えば、導電層 755a と導電層 755b の間隔は、導電層 756a と導電層 756b の間隔よりも短いことが好ましい。40

**【 0 1 1 6 】**

導電層 756a は、導電層 755a の一部の上に接して設けられており、導電層 756b は、導電層 755b の一部の上に接して設けられる。また、導電層 756a 及び 756b の電気抵抗値は、導電層 755a 及び 755b の電気抵抗値よりも低いことが好ましい。

**【 0 1 1 7 】**

絶縁層 757 は、半導体層 754 の上を覆うように設けられる。

**【 0 1 1 8 】**

さらに、各構成要素について以下に説明する。各構成要素は、必ずしも単層に限定されず、積層であってもよい。

**【 0 1 1 9 】**

絶縁層 701 は、下地層である。絶縁層 701 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

【0120】

絶縁層 752 は、絶縁層 701 と同様の材料を含む層を適用できる。

【0121】

半導体層 711 及び 754 は、トランジスタのチャネルが形成される層（チャネル形成層ともいう）としての機能を有する。

【0122】

半導体層 711 及び 754 としては、例えば酸化物半導体層を適用できる。

【0123】

酸化物半導体層は、例えば非単結晶を有してもよい。非単結晶は、例えば、C A A C ( C Axis Aligned Crystal )、多結晶、微結晶、非晶質部を有する。非晶質部は、微結晶、C A A C よりも欠陥準位密度が高い。また、微結晶は、C A A C よりも欠陥準位密度が高い。また、酸化物半導体層がアモルファス層と結晶を含む層との積層であってもよい。

【0124】

酸化物半導体層に適用可能な酸化物半導体としては、例えばインジウム及びガリウムの一方若しくは両方と、亜鉛と、を含む金属酸化物、又は該金属酸化物に含まれるガリウムの一部若しくは全部の代わりに他の金属元素を含む金属酸化物などが挙げられる。

【0125】

上記金属酸化物としては、例えばIn系金属酸化物、Zn系金属酸化物、In-Zn系金属酸化物、又はIn-Ga-Zn系金属酸化物などを適用できる。また、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部若しくは全部の代わりに他の金属元素を含む金属酸化物を用いてもよい。

【0126】

上記他の金属元素としては、例えばガリウムよりも多くの酸素原子と結合が可能な金属元素を用いればよく、例えばチタン、ジルコニウム、ハフニウム、ゲルマニウム、及び錫のいずれか一つ又は複数の元素を用いればよい。また、上記他の金属元素としては、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムのいずれか一つ又は複数の元素を用いればよい。これらの金属元素は、スタビライザとしての機能を有する。なお、これらの金属元素の添加量は、金属酸化物が半導体として機能することが可能な量である。ガリウムよりも多くの酸素原子と結合が可能な金属元素を用い、さらには金属酸化物中に酸素を供給することにより、金属酸化物中の酸素欠陥を少なくできる。

【0127】

例えば、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の全部の代わりに錫を用いるとIn-Sn-Zn系金属酸化物となり、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部の代わりにチタンを用いるとIn-Ti-Ga-Zn系金属酸化物となる。

【0128】

また、上記酸化物半導体層を、C A A C - O S ( C Axis Aligned Crystalline Oxide Semiconductor ) を含む酸化物半導体層としてもよい。

【0129】

C A A C - O S を含む酸化物半導体層は、完全な非晶質ではない。C A A C - O S を含む酸化物半導体層は、例えば、結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体を有している。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる

10

20

30

40

50

大きさであることが多い。また、透過型電子顕微鏡（TEMともいう）による観察像では、CAAC-O<sub>S</sub>を含む酸化物半導体層に含まれる非晶質部と結晶部との境界、結晶部と結晶部との境界は明確ではない。また、TEMによってCAAC-O<sub>S</sub>を含む酸化物半導体層には明確な粒界（グレインバウンダリーともいう）は確認できない。そのため、CAAC-O<sub>S</sub>を含む酸化物半導体層は、粒界に起因する電子移動度の低下が抑制される。結晶部では、例えば、c軸がCAAC-O<sub>S</sub>を含む酸化物半導体層の被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向になるように揃い、且つa b面に垂直な方向から見て金属原子が三角形状又は六角形状に配列し、c軸に垂直な方向から見て金属原子が層状又は金属原子と酸素原子とが層状に配列する。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80°以上100°以下、好ましくは85°以上95°以下の範囲も含まれる。また、単に平行と記載する場合、-10°以上10°以下、好ましくは-5°以上5°以下の範囲も含まれる。

#### 【0130】

上記CAAC-O<sub>S</sub>を含む酸化物半導体層をチャネル形成層として用いた電界効果トランジスタは、可視光や紫外光の照射による電気特性の変動が低いため、信頼性が高い。

#### 【0131】

酸化物半導体層は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。微結晶酸化物半導体層は、例えば、1nm以上10nm未満のサイズの微結晶（ナノ結晶ともいう）を膜中に含む。又は、微結晶酸化物半導体層は、例えば、1nm以上10nm未満の結晶部を有する結晶-非晶質混相構造の酸化物半導体を有している。

#### 【0132】

酸化物半導体層は、例えば非晶質部を有してもよい。なお、非晶質部を有する酸化物半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体層は、例えば、原子配列が無秩序であり、結晶成分を有していない。又は、非晶質酸化物半導体層は、例えば、完全な非晶質であり、結晶部を有さない。

#### 【0133】

なお、酸化物半導体層が、CAAC-O<sub>S</sub>、微結晶酸化物半導体、非晶質酸化物半導体の混合層であってもよい。混合層は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-O<sub>S</sub>の領域と、を有する。また、混合層は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-O<sub>S</sub>の領域と、の積層構造を有してもよい。

#### 【0134】

なお、CAAC-O<sub>S</sub>を含む酸化物半導体層において、結晶部の分布が一様でなくてもよい。例えば、CAAC-O<sub>S</sub>の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-O<sub>S</sub>を含む酸化物半導体層へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【0135】

また、半導体層711及び754として酸化物半導体層を用いる場合、例えば脱水化・脱水素化を行い、酸化物半導体層中の水素、水、水酸基、又は水素化物（水素化合物ともいう）などの不純物を排除し、且つ酸化物半導体層に酸素を供給すると、酸化物半導体層を高純度化させることができる。例えば、酸化物半導体層に接する層として酸素を含む層を用い、また、加熱処理を行うことにより、酸化物半導体層を高純度化させることができる。

#### 【0136】

また、形成直後の酸化物半導体層は、化学量論的組成より酸素が多い過飽和の状態であることが好ましい。例えば、スパッタリング法を用いて酸化物半導体層を形成する場合、成膜ガスの酸素の占める割合が多い条件で形成することが好ましく、特に酸素雰囲気（例え

10

20

30

40

50

ば酸素ガス 100% ) で成膜を行うことが好ましい。

**【 0137 】**

また、スパッタリング法を用いて酸化物半導体層を成膜する際に、基板温度を 100 以上 500 以下、好ましくは 200 以上 350 以下にして酸化物半導体層を成膜してもよい。

**【 0138 】**

また、酸化物半導体層に十分な酸素が供給されて酸素を過飽和の状態するために、酸化物半導体層に接する絶縁層（例えば絶縁層 701、714、753、757など）として過剰酸素を含む絶縁層を形成してもよい。

**【 0139 】**

10 例えば、スパッタリング法を用いて膜中に酸素が多く含まれる成膜条件で絶縁膜を成膜することにより、過剰酸素を含む絶縁層を形成できる。また、より多くの過剰酸素を絶縁層に含ませたい場合には、イオン注入法やイオンドーピング法やプラズマ処理によって酸素を添加すればよい。また、酸化物半導体層に酸素を添加してもよい。

**【 0140 】**

また、スパッタリング装置において、成膜室内の残留水分は、少ないことが好ましい。このため、スパッタリング装置に吸着型の真空ポンプを用いることが好ましい。また、コードトラップを用いてもよい。

**【 0141 】**

また、トランジスタの作製において、加熱処理を行うことが好ましい。このときの加熱処理の温度は、350 以上基板の歪み点未満の温度、さらには、350 以上 450 以下であることが好ましい。なお、加熱処理を複数回行ってもよい。

**【 0142 】**

上記加熱処理に用いられる加熱処理装置としては、G R T A ( G a s R a p i d T h e r m a l A n n e a l i n g ) 装置又は L R T A ( L a m p R a p i d T h e r m a l A n n e a l i n g ) 装置などの R T A ( R a p i d T h e r m a l A n n e a l i n g ) 装置を用いてもよい。なお、これに限定されず、電気炉など、別の加熱処理装置を用いてもよい。

**【 0143 】**

また、上記加熱処理を行った後、その加熱温度を維持しつつ、又はその加熱温度から降温する過程で該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度の N<sub>2</sub>O ガス、又は超乾燥エア（露点が -40 以下、好ましくは -60 以下の雰囲気）を導入するとよい。このとき、酸素ガス又は N<sub>2</sub>O ガスは、水及び水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又は N<sub>2</sub>O ガスの純度は、6 N 以上、好ましくは 7 N 以上であると良い。すなわち、酸素ガス又は N<sub>2</sub>O ガス中の不純物濃度は、1 ppm 以下、好ましくは 0.1 ppm 以下であることが好ましい。この工程により、酸化物半導体層に酸素が供給され、酸化物半導体層中の酸素欠乏に起因する欠陥を低減できる。なお、上記高純度の酸素ガス、高純度の N<sub>2</sub>O ガス、又は超乾燥エアの導入は、上記加熱処理時に行ってもよい。

**【 0144 】**

30 高純度化させた酸化物半導体層の水素濃度は、二次イオン質量分析法 ( S I M S ともいう ) の測定値において、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、さらには  $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、さらには  $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下であることが好ましい。

**【 0145 】**

高純度化させた酸化物半導体層を電界効果トランジスタに用いることにより、酸化物半導体層のキャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満にすることができる。このように、キャリア密度を少なくすることにより、チャネル幅 1 μmあたりの電界効果トランジスタのオフ電流を  $1 \times 10^{-19} \text{ A}$  ( 100 zA ) 以下、より好ましくは  $1 \times 10^{-22} \text{ A}$  ( 100 50

$y A$ ) 以下にまで抑制できる。電界効果トランジスタのオフ電流は、低ければ低いほどよいが、電界効果トランジスタのオフ電流の下限値は、約  $1 \times 10^{-3} A / \mu m$  であると見積もられる。

#### 【0146】

領域 712a 及び 712b に含まれるドーパントとしては、例えば元素周期表における 13 族の元素（例えば硼素など）、15 族の元素（例えば窒素、リン、及び砒素の一つ又は複数）、及び希ガス元素（例えばヘリウム、アルゴン、及びキセノンの一つ又は複数）を挙げることができ、これらのいずれか一つ又は複数を適用できる。

#### 【0147】

絶縁層 714 及び 753 は、トランジスタのゲート絶縁層としての機能を有する。絶縁層 714 及び 753 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

#### 【0148】

導電層 715 及び 751 は、トランジスタのゲートとしての機能を有する。導電層 715 及び 751 としては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、又はスカンジウムなどの金属材料を含む層を適用できる。

#### 【0149】

絶縁層 716a、716b、717 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

#### 【0150】

導電層 718a 及び 718b、導電層 755a 及び 755b、並びに導電層 756a 及び 756b は、トランジスタのソース又はドレインとしての機能を有する。導電層 718a 及び 718b、導電層 755a 及び 755b、並びに導電層 756a 及び 756b としては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム、又はルテニウムなどの金属材料を含む層を適用できる。

#### 【0151】

絶縁層 719 及び 757 は、保護層としての機能を有する。絶縁層 719 及び 757 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

#### 【0152】

さらに、上記トランジスタの電気特性の一例として、図 4 (B) に示すトランジスタの一例の  $I_d - V_g$  特性について、図 5 を参照して説明する。なお、図 5 に示す  $I_d - V_g$  特性を示すトランジスタは、半導体層 711 が厚さ 20 nm の In-Ga-Zn 系酸化物半導体層であり、絶縁層 714 が厚さ 20 nm の酸化窒化シリコン層であり、導電層 715 が厚さ 30 nm の窒化タンタル層と厚さ 200 nm のタンゲステン層の積層であり、導電層 718a 及び 718b が厚さ 30 nm のタンゲステン層であるとする。また、領域 712a 及び 712b を形成するためにリンを添加し、該リンの添加量が  $1 \times 10^{15} cm^{-2}$  であり、加速電圧は 30 kV であるとする。また、チャネル長が 5  $\mu m$  あり、チャネル幅が 10  $\mu m$  であるとする。また、横軸がゲート電圧  $V_g$  であり、縦軸がドレイン電流  $I_d$  又は移動度  $\mu F E$  である。

#### 【0153】

図 5 に示す  $I_d - V_g$  特性であるトランジスタの移動度は約  $20 cm^2 / V s$  であり、オフ電流は検出限界以下であり、閾値電圧が 0 V 以上である。

#### 【0154】

10

20

30

40

50

さらに、実施の形態 1 に示す式(1)を参照して、図5に示す $I_d - V_g$ 特性であるトランジスタのオン抵抗の値を算出する。

**【0155】**

絶縁層714の比誘電率を4.1とするとゲート容量 $C_{ox}$ は $1.82 \times 10^{-3} F/m^2$ となる。さらに、図5のデータから、トランジスタの移動度 $\mu$ を $20 cm^2/Vs$ とし、閾値電圧 $V_{th}$ を $0.6 V$ とし、記憶回路の仕様例としてゲート電圧 $V_g$ を $3.3 V$ とし、ドレイン電圧 $V_d$ を $1.8 V$ とすると、実施の形態1の式(1)からオン抵抗 $R_d$ は $76.3 k\Omega$ となる。

**【0156】**

以上が図4に示すトランジスタの構造例の説明である。

10

**【0157】**

さらに、一例として図4(A)に示すトランジスタを用いた場合の記憶回路の構造例について、図6を参照して説明する。図6は、本実施の形態に係る記憶回路の構造例を説明するための断面模式図である。なお、これに限定されず、図4(B)及び図4(C)に示すトランジスタを用いて記憶回路を構成してもよい。

**【0158】**

図6(A)に示す記憶回路は、チャネル形成層である単結晶シリコン層813を含むトランジスタ801と、絶縁層815乃至817を介してトランジスタ801の上に積層され、図4(A)に示すトランジスタと同じ構造であるトランジスタ802と、を有する。なお、トランジスタ802の説明としては、図4(A)に示すトランジスタの説明を適宜援用できる。

20

**【0159】**

単結晶シリコン層813は、絶縁層811(BOX層ともいう)を介して基板810の上に設けられる。なお、基板810、絶縁層811、及び単結晶シリコン層813の代わりに、図6(B)に示すように、単結晶半導体基板820の埋め込み絶縁領域822に囲まれた半導体領域823を用いてトランジスタ801を構成してもよい。このとき、半導体領域823には、N型又はP型の導電型である不純物領域825a及び825bが設けられる。

**【0160】**

絶縁層815は、保護層としての機能を有する。絶縁層816は、保護層のみならず、平坦化層としての機能を有する。また、絶縁層817は、下地層としての機能を有する。絶縁層815乃至817としては、図4(A)に示す絶縁層701と同様の材料を含む層を適用できる。

30

**【0161】**

トランジスタ802のソース又はドレインとしての機能を有する導電層818は、トランジスタ801のゲートとしての機能を有する導電層814に接続される。なお、導電層818と導電層814は、複数の導電層を介して接続されていてもよい。なお、図6(B)に示すように、記憶回路の構造を、トランジスタ801のゲートとしての機能を有する導電層824と導電層818が直接接する構造にしてもよい。また、導電層818と導電層814を直接接続せず、別の導電層を介して導電層818と導電層814を電気的に接続させててもよい。

40

**【0162】**

また、トランジスタ802を上記オフ電流の低いトランジスタとして適用できる。

**【0163】**

また、トランジスタ801を用いて、インバータなどを構成できる。

**【0164】**

以上が図6に示す記憶回路の構造例の説明である。

**【0165】**

図4乃至図6を参照して説明したように、本実施の形態に係る記憶回路では、データの書き換え及び読み出しを制御するトランジスタを、酸化物半導体層を含むトランジスタによ

50

り構成し、インバータなどの論理回路のトランジスタを、単結晶シリコン層を含むトランジスタにより構成する。上記構成にすることにより、記憶回路の動作を高速化させつつ、データの保持時間を長くできる。

#### 【0166】

さらに、表1はM R A Mに用いられる磁気トンネル接合素子(M T J素子)と、本実施の形態に係る酸化物半導体層とシリコンの積層構造(O S / S iともいう)を用いた記憶回路との対比を示す。

#### 【0167】

【表1】

|                          | スピントロニクス(M T J素子)                                                   | O S / S i                                      |

|--------------------------|---------------------------------------------------------------------|------------------------------------------------|

| 1) 耐熱性                   | キュリー温度                                                              | プロセス温度500°C<br>(信頼性150°C)                      |

| 2) 駆動方式                  | 電流駆動                                                                | 電圧駆動                                           |

| 3) 書き込み原理                | 磁性体の спинの向きを変える                                                    | トランジスタのオン／オフ                                   |

| 4) Si LSI                | バイポーラLSI向き<br>(バイポーラは高集積化には向きなため、高集積化回路ではM O Sの方が好ましい。ただし、Wが大きくなる。) | M O S L S I向き                                  |

| 5) オーバーヘッド               | 大きい<br>(ジュール熱が大きいため)                                                | 2～3桁以上小さい<br>(寄生容量の充放電)                        |

| 6) 不揮発性                  | スピノを利用                                                              | オフ電流が小さいことを利用                                  |

| 7) 読み出し回数                | 無制限                                                                 | 無制限                                            |

| 8) 3D化                   | 難(できても二層まで)                                                         | 容易(何層でも可)                                      |

| 9) 集積化度(F <sup>2</sup> ) | 4 F <sup>2</sup> ～15 F <sup>2</sup>                                 | 3 D化の積層数で決まる<br>(上層トランジスタ工程のプロセス耐熱性の確保が必要)     |

| 10) 材料                   | 磁性を有する希土類                                                           | 酸化物半導体                                         |

| 11) ピットコスト               | 高い                                                                  | 低い<br>(酸化物半導体を構成する材料によつては(I nなど)、多少コスト高の可能性有り) |

| 12) 磁界耐性                 | 弱い                                                                  | 強い                                             |

10

20

30

#### 【0168】

M T J素子としては、磁性材料を使用する。このため、M T J素子をキュリー温度以上にすると磁性が失われてしまうという欠点がある。また、M T J素子は電流駆動であるため、シリコンのバイポーラデバイスと相性が良いが、バイポーラデバイスは集積化に向きである。さらに、M T J素子は、メモリの大容量化によって書き込み電流の量が増大し、消費電力が増大してしまうといった問題がある。

40

#### 【0169】

また、M T J素子は、磁界耐性に弱く、強磁界にさらされると磁化の向きが狂いやすい。また、M T J素子に用いる磁性体は、ナノスケールにすることにより磁化揺らぎが生じる。

#### 【0170】

また、M T J素子はピット当たりの材料コストから見ても高価である。

#### 【0171】

一方、本実施の形態で示す酸化物半導体を用いたトランジスタは、チャネルを形成する半導体材料が金属酸化物であること以外は、素子構造や動作原理がシリコンM O S F E Tと

50

同様である。また、酸化物半導体を用いたトランジスタは磁界の影響を受けず、ソフトエラーも生じにくい。このことからシリコン集積回路と非常に整合性が良いといえる。

#### 【0172】

##### (実施の形態3)

本実施の形態では、回路毎に電源電圧の供給の制御が可能な半導体装置の例について説明する。

#### 【0173】

まず、半導体装置の構成例について、図7を参照して説明する。

#### 【0174】

図7に示す半導体装置は、CPU911と、キャッシュメモリ912と、メインメモリ913と、パワーゲートとなる電源供給制御スイッチ(SWと示す)921乃至923と、コントローラ950と、を有する。CPU911、キャッシュメモリ912、メインメモリ913、コントローラ950のそれぞれは、バスにより互いに信号の入出力を行うことができる。また、CPU911、キャッシュメモリ912、及びメインメモリ913には、電源供給制御スイッチ921乃至923のいずれかを介して電源990から電源電圧PWRが供給される。なお、必ずしも半導体装置内にメインメモリ913を設けなくてもよい。

#### 【0175】

CPU911は、入力信号に従い演算処理を行う機能を有する。入力信号としては、例えばクロック信号、CPU911、キャッシュメモリ912、又はメインメモリ913の動作を制御するための信号、入力装置から入力される信号などが挙げられる。また、CPU911は、演算結果に応じた値の信号を出力する。なお、本明細書では、特に指定する場合を除き、複数種の信号であっても単に信号と表記する場合がある。

#### 【0176】

また、CPU911は、演算処理の際にキャッシュメモリ912にアドレス信号を入力し、キャッシュメモリ912に記憶されたデータの読み出しを行う機能を有する。また、CPU911は、メインメモリ913にアドレス信号を入力し、メインメモリ913に記憶されたデータを読み出し、キャッシュメモリ912に書き込む機能を有する。

#### 【0177】

CPU911のレジスタは、例えば揮発性記憶回路と不揮発性記憶回路を有する記憶回路を用いて構成できる。このとき、CPU911に対する電源電圧の供給を停止させる直前に不揮発性記憶回路にデータを退避させる。また、電源電圧の供給を再開させた直後に不揮発性記憶回路に記憶されたデータを揮発性記憶回路に入力する。これにより、電源電圧の供給を再開させたときのCPU911の状態復帰を速くできる。ただし、これに限定されず、他の記憶回路を用いてレジスタを構成してもよい。

#### 【0178】

上記不揮発性記憶回路は、例えば実施の形態1の記憶回路に適用可能なオフ電流の低いトランジスタを用いて構成される。このとき、上記オフ電流の低いトランジスタは、不揮発性記憶回路のデータの書き込み及び保持を制御する機能を有する。

#### 【0179】

キャッシュメモリ912は、CPU911の演算処理の際に、データの読み出しが行われる。例えば、CPU911の命令信号に従って、キャッシュメモリ912にメインメモリ913のデータの一部が保持される。

#### 【0180】

なお、CPU911内にキャッシュメモリ912を設けてもよい。例えば、図8に示すように、CPU911は、演算部931と、キャッシュ部932と、を含み、キャッシュ部932にキャッシュメモリ912が設けられる。このとき、キャッシュメモリ912を介して演算部931とメインメモリ913がデータ通信を行う。また、キャッシュ部932に複数のキャッシュメモリを設けることにより、データキャッシュ、命令キャッシュなどを構成してもよい。

10

20

30

40

50

**【0181】**

キャッシュメモリ912としては、例えばダイレクトマップ方式、セットアソシアティブ方式、又はフルアソシアティブ方式などのキャッシュメモリを適用できる。

**【0182】**

キャッシュメモリ912は、実施の形態1の記憶回路を用いたメモリセルにより構成される。これにより、電源電圧の供給を停止させた場合であっても、書き込まれたデータを長時間保持できる。これにより、データの書き換え及び読み出しが不要な期間にキャッシュメモリ912に対する電源電圧の供給を停止でき、消費電力を低減することができる。

**【0183】**

メインメモリ913は、例えばC P U 9 1 1での演算処理に用いられるデータが記憶される。メインメモリ913は、例えばダイナミックランダムアクセスメモリ(D R A Mともいう)などを用いて構成される。

**【0184】**

電源供給制御スイッチ921は、C P U 9 1 1に対する電源電圧の供給を制御する機能を有する。なお、図8に示す半導体装置の場合には、電源供給制御スイッチ921は、C P U 9 1 1の演算部931に対する電源電圧の供給を制御する機能を有する。

**【0185】**

電源供給制御スイッチ922は、キャッシュメモリ912に対する電源電圧の供給を制御する機能を有する。

**【0186】**

電源供給制御スイッチ923は、メインメモリ913に対する電源電圧の供給を制御する機能を有する。

**【0187】**

電源供給制御スイッチ921乃至923は、電界効果トランジスタを用いて構成される。このとき、上記電界効果トランジスタとしては、上記オフ電流の低いトランジスタを用いてよい。

**【0188】**

電源供給制御スイッチ921乃至923の構成例について、図9を参照して説明する。

**【0189】**

図9に示す電源供給制御スイッチは、トランジスタ21と、トランジスタ22と、を有する。

**【0190】**

トランジスタ21は、電源990と、C P U 9 1 1、キャッシュメモリ912、又はメインメモリ913などの各回路と、の間に設けられる。トランジスタ21のゲートには、コントローラ950から制御信号S W \_ O Nが入力される。トランジスタ21がオン状態又はオフ状態になることにより、C P U 9 1 1、キャッシュメモリ912、及びメインメモリ913などの各回路に電源電圧を供給するか否かが制御される。

**【0191】**

トランジスタ22のゲートには、コントローラ950から制御信号S W \_ O F Fが入力される。トランジスタ22がオン状態又はオフ状態になることにより、C P U 9 1 1、キャッシュメモリ912、及びメインメモリ913などの各回路に接地電位を供給するか否かが制御される。

**【0192】**

トランジスタ21がオン状態であり、トランジスタ22がオフ状態であるときに、図9に示す電源供給制御スイッチがオン状態となる。トランジスタ21がオフ状態であり、トランジスタ22がオン状態であるときに、図9に示す電源供給制御スイッチがオフ状態となる。

**【0193】**

以上が図9に示す電源供給制御スイッチの構成例の説明である。

**【0194】**

10

20

30

40

50

図7及び図8に示すコントローラ950は、上記入力信号、CPU911から入力される命令信号に従って電源供給制御スイッチ921乃至923を個別に制御する機能を少なくとも有する。また、コントローラ950には、電源電圧PWRが供給される。なお、電源供給制御スイッチ921乃至923のうちの複数を、別々のコントローラにより制御してもよい。

#### 【0195】

さらに、一例として、コントローラ950の構成例について、図10を参照して説明する。

#### 【0196】

図10に示すコントローラ950は、インターフェース部951と、クロック生成部952と、出力信号制御部953と、バッファ部954と、を含む。

10

#### 【0197】

上記入力信号、CPU911から入力される命令信号などの信号は、インターフェース部951を介して出力信号制御部953に入力される。

#### 【0198】

クロック生成部952では、入力されたクロック信号を用いてコントローラ950で使用するクロック信号を生成して出力信号制御部953を含む各回路に出力する。このとき、入力されたクロック信号を分周してコントローラ950で用いることにより、コントローラ950の消費電力を小さくすることができる。

#### 【0199】

出力信号制御部953は、カウンタ回路955を有する。出力信号制御部953は、カウンタ回路955でクロック信号をカウントし、コントローラ950に入力される信号に従って、出力する複数の信号のハイ状態又はロー状態を設定する機能を有する。上記複数の信号としては、電源供給制御スイッチ921乃至923を個別に制御するための制御信号（例えば複数の制御信号SW\_ON、複数の制御信号SW\_OFF）、CPU911の動作を制御するための信号などが挙げられる。

20

#### 【0200】

出力信号制御部953で生成された各信号は、バッファ部954を介して各回路に出力される。

#### 【0201】

以上が図10に示すコントローラの構成例の説明である。

30

#### 【0202】

図7に示す半導体装置では、電源供給制御スイッチ921乃至923を設け、入力信号、CPU911から入力される命令信号に従ってコントローラ950により、電源供給制御スイッチ921乃至923が個別に制御される。

#### 【0203】

CPU911、キャッシュメモリ912、及びメインメモリ913のそれぞれにおいて、電源電圧の供給の最適なタイミングは互いに異なる。そのため、CPU911、キャッシュメモリ912、及びメインメモリ913のそれぞれに対する電源電圧の供給を個別に最適化することにより、不要な電力の消費を抑制することができる。

40

#### 【0204】

図7乃至図10を参照して説明したように、本実施の形態に係る半導体装置の一例では、キャッシュメモリ及びCPUを有し、キャッシュメモリ及びCPUのそれぞれに対して電源供給制御スイッチを設け、入力信号、CPUから入力される命令信号に従ってコントローラにより、複数の電源供給制御スイッチを個別に制御する。これにより、各回路に対する電源電圧の供給のタイミングを個別に最適化して、不要な電力の消費を抑制できる。

#### 【0205】

また、キャッシュメモリを実施の形態1の記憶回路を用いて構成することにより、電源電圧の供給を停止した場合であっても、データを保持できる。このため、データの再書き込み動作が不要になり、消費電力を低減できる。

50

**【0206】**

(実施の形態4)

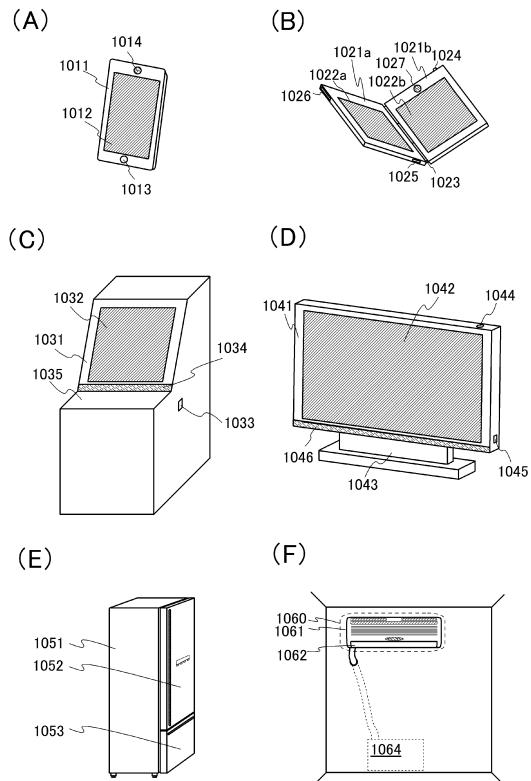

本実施の形態では、本発明の一態様である半導体装置を用いた電子機器の例について、図11を参照して説明する。

**【0207】**

図11(A)に示す電子機器は、携帯型情報端末の一例である。

**【0208】**

図11(A)に示す電子機器は、筐体1011と、筐体1011に設けられたパネル1012と、ボタン1013と、スピーカー1014と、を具備する。

**【0209】**

なお、筐体1011に、外部機器に接続するための接続端子及び操作ボタンが設けられていてもよい。

**【0210】**

パネル1012は、表示パネル(ディスプレイ)である。パネル1012は、タッチパネルの機能を有することが好ましい。

**【0211】**

ボタン1013は、筐体1011に設けられる。例えば、ボタン1013が電源ボタンであれば、ボタン1013を押すことにより、電子機器をオン状態にするか否かを制御することができる。

**【0212】**

スピーカー1014は、筐体1011に設けられる。スピーカー1014は音声を出力する。

**【0213】**

なお、筐体1011にマイクが設けられていてもよい。筐体1011にマイクを設けられることにより、例えば図11(A)に示す電子機器を電話機として機能させることができる。

**【0214】**

図11(A)に示す電子機器は、筐体1011の内部に実施の形態3に示す半導体装置などを有する。

**【0215】**

図11(A)に示す電子機器は、例えば電話機、電子書籍、パソコンコンピュータ、及び遊戯機の一つ又は複数としての機能を有する。

**【0216】**

図11(B)に示す電子機器は、折り畳み式の情報端末の一例である。

**【0217】**

図11(B)に示す電子機器は、筐体1021aと、筐体1021bと、筐体1021aに設けられたパネル1022aと、筐体1021bに設けられたパネル1022bと、軸部1023と、ボタン1024と、接続端子1025と、記録媒体挿入部1026と、スピーカー1027と、を備える。

**【0218】**

筐体1021aと筐体1021bは、軸部1023により接続される。

**【0219】**

パネル1022a及びパネル1022bは、表示パネル(ディスプレイ)である。パネル1022a及びパネル1022bは、タッチパネルとしての機能を有することが好ましい。

**【0220】**

図11(B)に示す電子機器は、軸部1023を有するため、パネル1022aとパネル1022bを対向させて折り畳むことができる。

**【0221】**

ボタン1024は、筐体1021bに設けられる。なお、筐体1021aにボタン102

10

20

30

40

50

4を設けてもよい。例えば、電源ボタンとしての機能を有するボタン1024を設けることより、ボタン1024を押すことで電子機器に対する電源電圧の供給を制御できる。

【0222】

接続端子1025は、筐体1021aに設けられる。なお、筐体1021bに接続端子1025が設けられていてもよい。また、接続端子1025が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。接続端子1025は、図11(B)に示す電子機器と他の機器を接続するための端子である。

【0223】

記録媒体挿入部1026は、筐体1021aに設けられる。筐体1021bに記録媒体挿入部1026が設けられていてもよい。また、記録媒体挿入部1026が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。例えば、記録媒体挿入部にカード型記録媒体を挿入することにより、カード型記録媒体のデータを電子機器に読み出し、又は電子機器内のデータをカード型記録媒体に書き込むことができる。

10

【0224】

スピーカー1027は、筐体1021bに設けられる。スピーカー1027は、音声を出力する。なお、筐体1021aにスピーカー1027を設けてもよい。

【0225】

なお、筐体1021a又は筐体1021bにマイクを設けてもよい。筐体1021a又は筐体1021bにマイクが設けられることにより、例えば図11(B)に示す電子機器を電話機として機能させることができる。

20

【0226】

図11(B)に示す電子機器は、筐体1021a又は筐体1021bの内部に実施の形態3に示す半導体装置などを有する。

【0227】

図11(B)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

【0228】

図11(C)に示す電子機器は、据え置き型情報端末の一例である。図11(C)に示す据え置き型情報端末は、筐体1031と、筐体1031に設けられたパネル1032と、ボタン1033と、スピーカー1034と、を具備する。

30

【0229】

パネル1032は、表示パネル(ディスプレイ)である。パネル1032は、タッチパネルとしての機能を有することが好ましい。

【0230】

なお、筐体1031の甲板部1035にパネル1032と同様のパネルを設けてもよい。上記パネルは、タッチパネルとしての機能を有することが好ましい。

【0231】

さらに、筐体1031に券などを出力する券出力部、硬貨投入部、及び紙幣挿入部などを設けてもよい。

40

【0232】

ボタン1033は、筐体1031に設けられる。例えば、ボタン1033が電源ボタンであれば、ボタン1033を押すことで電子機器に対する電源電圧の供給を制御できる。

【0233】

スピーカー1034は、筐体1031に設けられる。スピーカー1034は、音声を出力する。

【0234】

図11(C)に示す電子機器は、筐体1031の内部に実施の形態3に示す半導体装置などを有する。

【0235】

図11(C)に示す電子機器は、例えば現金自動預け払い機、チケットなどの注文をする

50

ための情報通信端末（マルチメディアステーションともいう）、又は遊技機としての機能を有する。

【0236】

図11(D)は、据え置き型情報端末の一例である。図11(D)に示す電子機器は、筐体1041と、筐体1041に設けられたパネル1042と、筐体1041を支持する支持台1043と、ボタン1044と、接続端子1045と、スピーカー1046と、を備える。

【0237】

なお、筐体1041に外部機器に接続させるための接続端子を設けてよい。

【0238】

パネル1042は、表示パネル（ディスプレイ）としての機能を有する。

10

【0239】

ボタン1044は、筐体1041に設けられる。例えば、ボタン1044が電源ボタンであれば、ボタン1044を押すことで電子機器に対する電源電圧の供給を制御できる。

【0240】

接続端子1045は、筐体1041に設けられる。接続端子1045は、図11(D)に示す電子機器と他の機器を接続するための端子である。例えば、接続端子1045により図11(D)に示す電子機器とパソコンを接続すると、パソコンから入力されるデータ信号に応じた画像をパネル1042に表示させることができる。例えば、図11(D)に示す電子機器のパネル1042が接続する他の電子機器のパネルより大きければ、当該他の電子機器の表示画像を拡大することができ、複数の人が同時に視認しやすくなる。

20

【0241】

スピーカー1046は、筐体1041に設けられる。スピーカー1046は、音声を出力する。

【0242】

図11(D)に示す電子機器は、筐体1041の内部に実施の形態3に示す半導体装置などを有する。

【0243】

図11(D)に示す電子機器は、例えば出力モニタ、パソコン、及びテレビジョン装置の一つ又は複数としての機能を有する。

30

【0244】

図11(E)は、電気冷凍冷蔵庫の一例である。図11(E)に示す電子機器は、筐体1051と、冷蔵室用扉1052と、冷凍室用扉1053と、を備える。

【0245】

図11(E)に示す電子機器は、筐体1051の内部に実施の形態3に示す半導体装置などを有する。上記構成にすることにより、例えば、冷蔵室用扉1052及び冷凍室用扉1053の開閉に従って、筐体1051内の半導体装置に対する電源電圧の供給を制御できる。

40

【0246】

図11(F)は、エアコンディショナーの一例である。図11(F)に示す電子機器は、室内機1060及び室外機1064により構成される。

【0247】

室内機1060は、筐体1061と、送風口1062と、を備える。

【0248】

図11(F)に示す電子機器は、筐体1061の内部に実施の形態3に示す半導体装置などを有する。上記構成にすることにより、例えば、リモートコントローラからの信号に従って、筐体1061内の半導体装置に対する電源電圧の供給を制御できる。

【0249】

なお、図11(F)では、室内機と室外機で構成されるセパレート型のエアコンディショ

50

ナーを例示しているが、室内機の機能と室外機の機能とを1つの筐体に有するエアコンデイショナーであってもよい。

【0250】

なお、これに限定されず、電子レンジなどの高周波加熱装置、又は電気炊飯器などにも実施の形態3の半導体装置を適用できる。

【0251】

以上が図11に示す電子機器の例の説明である。

【0252】

図11を参照して説明したように、本実施の形態に係る電子機器では、実施の形態3の半導体装置を用いることにより、消費電力を低くできる。

10

【符号の説明】

【0253】

|         |          |    |

|---------|----------|----|

| 2 1     | トランジスタ   |    |

| 2 2     | トランジスタ   |    |

| 1 1 1   | トランジスタ   |    |

| 1 1 2   | トランジスタ   |    |

| 1 1 3   | トランジスタ   |    |

| 1 1 4   | トランジスタ   |    |

| 1 1 5   | トランジスタ   |    |

| 1 1 6   | トランジスタ   | 20 |

| 1 1 7   | トランジスタ   |    |

| 1 1 8   | トランジスタ   |    |

| 1 1 9   | トランジスタ   |    |

| 1 2 0   | トランジスタ   |    |

| 1 3 1   | インバータ    |    |

| 1 3 2   | インバータ    |    |

| 1 5 1   | 容量素子     |    |

| 1 5 2   | 容量素子     |    |

| 7 0 0   | 被素子形成層   |    |

| 7 0 1   | 絶縁層      | 30 |

| 7 1 1   | 半導体層     |    |

| 7 1 2 a | 領域       |    |

| 7 1 2 b | 領域       |    |

| 7 1 3   | チャネル形成領域 |    |

| 7 1 4   | 絶縁層      |    |

| 7 1 5   | 導電層      |    |

| 7 1 6 a | 絶縁層      |    |

| 7 1 6 b | 絶縁層      |    |

| 7 1 7   | 絶縁層      |    |

| 7 1 8 a | 導電層      | 40 |

| 7 1 8 b | 導電層      |    |

| 7 1 9   | 絶縁層      |    |

| 7 5 0   | 被素子形成層   |    |

| 7 5 1   | 導電層      |    |

| 7 5 2   | 絶縁層      |    |

| 7 5 3   | 絶縁層      |    |

| 7 5 4   | 半導体層     |    |

| 7 5 5 a | 導電層      |    |

| 7 5 5 b | 導電層      |    |

| 7 5 6 a | 導電層      | 50 |

|           |            |    |

|-----------|------------|----|

| 7 5 6 b   | 導電層        |    |

| 7 5 7     | 絶縁層        |    |

| 8 0 1     | トランジスタ     |    |

| 8 0 2     | トランジスタ     |    |

| 8 1 0     | 基板         |    |

| 8 1 1     | 絶縁層        |    |

| 8 1 3     | 単結晶シリコン層   |    |

| 8 1 4     | 導電層        |    |

| 8 1 5     | 絶縁層        |    |

| 8 1 6     | 絶縁層        | 10 |

| 8 1 7     | 絶縁層        |    |

| 8 1 8     | 導電層        |    |

| 8 2 0     | 単結晶半導体基板   |    |

| 8 2 2     | 絶縁領域       |    |

| 8 2 3     | 半導体領域      |    |

| 8 2 4     | 導電層        |    |

| 8 2 5 a   | 不純物領域      |    |

| 8 2 5 b   | 不純物領域      |    |

| 9 1 1     | C P U      |    |

| 9 1 2     | キャッシュメモリ   | 20 |

| 9 1 3     | メインメモリ     |    |

| 9 2 1     | 電源供給制御スイッチ |    |

| 9 2 2     | 電源供給制御スイッチ |    |

| 9 2 3     | 電源供給制御スイッチ |    |

| 9 3 1     | 演算部        |    |

| 9 3 2     | キャッシュ部     |    |

| 9 5 0     | コントローラ     |    |

| 9 5 1     | インターフェース部  |    |

| 9 5 2     | クロック生成部    |    |

| 9 5 3     | 出力信号制御部    | 30 |

| 9 5 4     | バッファ部      |    |

| 9 5 5     | カウンタ回路     |    |

| 9 9 0     | 電源         |    |

| 1 0 1 1   | 筐体         |    |

| 1 0 1 2   | パネル        |    |

| 1 0 1 3   | ボタン        |    |

| 1 0 1 4   | スピーカー      |    |

| 1 0 2 1 a | 筐体         |    |

| 1 0 2 1 b | 筐体         |    |

| 1 0 2 2 a | パネル        | 40 |

| 1 0 2 2 b | パネル        |    |

| 1 0 2 3   | 軸部         |    |

| 1 0 2 4   | ボタン        |    |

| 1 0 2 5   | 接続端子       |    |

| 1 0 2 6   | 記録媒体挿入部    |    |

| 1 0 2 7   | スピーカー      |    |

| 1 0 3 1   | 筐体         |    |

| 1 0 3 2   | パネル        |    |

| 1 0 3 3   | ボタン        |    |

| 1 0 3 4   | スピーカー      | 50 |

|         |       |

|---------|-------|

| 1 0 3 5 | 甲板部   |

| 1 0 4 1 | 筐体    |

| 1 0 4 2 | パネル   |

| 1 0 4 3 | 支持台   |

| 1 0 4 4 | ボタン   |

| 1 0 4 5 | 接続端子  |

| 1 0 4 6 | スピーカー |

| 1 0 5 1 | 筐体    |

| 1 0 5 2 | 冷蔵室用扉 |

| 1 0 5 3 | 冷凍室用扉 |

| 1 0 6 0 | 室内機   |

| 1 0 6 1 | 筐体    |

| 1 0 6 2 | 送風口   |

| 1 0 6 4 | 室外機   |

10

【図1】

(B)

【図2】

(B)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/786 (2006.01) H 01 L 29/78 618B

(56)参考文献 特開2011-151796 (JP, A)

米国特許出願公開第2011/0156024 (US, A1)

特開2011-171723 (JP, A)

米国特許出願公開第2011/0176357 (US, A1)

特開2011-142621 (JP, A)

米国特許出願公開第2011/0187410 (US, A1)

特開平10-93423 (JP, A)

米国特許第5936879 (US, A)

## (58)調査した分野(Int.Cl., DB名)

G 11 C 11/412

G 11 C 11/41

G 06 F 12/08

H 01 L 21/8244

H 01 L 27/11

H 01 L 29/786