(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 10 2007 019 552 B4 2009.12.17

(12)

## Patentschrift

(21) Aktenzeichen: 10 2007 019 552.6

(22) Anmelddatum: 25.04.2007

(43) Offenlegungstag: 30.10.2008

(45) Veröffentlichungstag

der Patenterteilung: 17.12.2009

(51) Int Cl.<sup>8</sup>: H01L 21/60 (2006.01)

H01L 23/50 (2006.01)

H01L 23/12 (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

Infineon Technologies AG, 85579 Neubiberg, DE

(74) Vertreter:

Patentanwälte Lambsdorff & Lange, 81673

München

(72) Erfinder:

Dertinger, Stephan, 80335 München, DE; Martin,

Alfred, 81825 München, DE; Hasler, Barbara,

81737 München, DE; Sommer, Grit, 85567 Grafing,

DE; Binder, Florian, 82131 Gauting, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

|    |                |    |

|----|----------------|----|

| DE | 10 2005 042074 | A1 |

| US | 71 76 128      | B2 |

| US | 56 18 752      | A  |

| EP | 09 26 723      | A1 |

| WO | 2005/0 88 699  | A1 |

Yamamoto,S. (u.a.), "Si through-hole

interconnections filled with Au-Sn solder by

molten metal suction method", IN: Micro

Electro Mechanical Systems, 2003, MEMS-03

Kyoto, 19-23 Jan. 2003, pp. 642-645

(54) Bezeichnung: **Verfahren zur Herstellung eines Substrats mit Durchführung sowie Substrat und Halbleitermodul mit Durchführung**

(57) Hauptanspruch: Ein Verfahren umfassend:

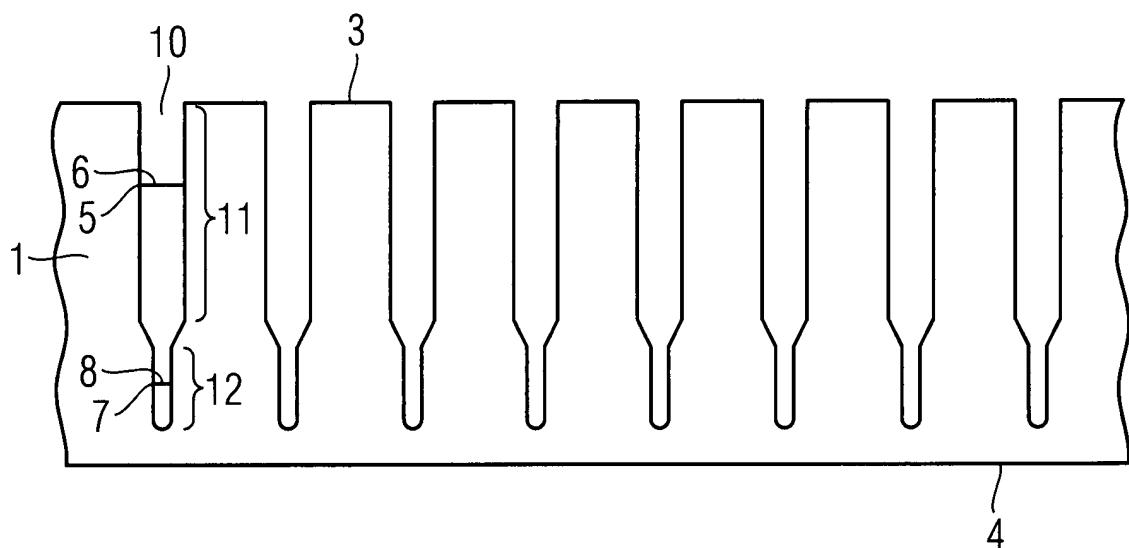

- ein Halbleitersubstrat (1) mit einer ersten Hauptoberfläche (3), einer zweiten, der ersten Hauptoberfläche (3) gegenüberliegenden, Hauptoberfläche (4) und mindestens einem von der ersten Hauptoberfläche (3) zu der zweiten Hauptoberfläche (4) reichenden Kanal (2), der in einem ersten Abschnitt (11) eine erste Querschnittsfläche (6) und in einem zweiten Abschnitt (12) eine zweite Querschnittsfläche (8) aufweist, wobei die erste Querschnittsfläche (6) größer als die zweite Querschnittsfläche (8) ist, wird bereitgestellt; und

- ein elektrisch leitendes erstes Material (9) wird unter Druck im geschmolzenen Zustand in den ersten Abschnitt (11) des mindestens einen Kanals (2) eingefüllt.

**Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Substrat mit einer Durchführung sowie auf ein Verfahren zur Herstellung eines Substrats mit einer Durchführung.

**[0002]** Integrierte Schaltungen, Sensoren oder mikromechanische Apparate werden gewöhnlich auf einem Substrat aufgebracht oder in ein solches integriert. Um integrierte Schaltungen extern anschließen zu können, kann es hilfreich sein, wenn die Substrate über elektrisch leitende Durchführungen von der Substratoberseite zur Substratunterseite verfügen.

**[0003]** Vor diesem Hintergrund werden ein Substrat gemäß dem Anspruch 14, ein Halbleitermodul gemäß dem Anspruch 25 sowie ein Verfahren gemäß dem Anspruch 1 angegeben. Weitere Aspekte des Substrats, Halbleitermoduls und Verfahrens sowie Verbesserungen oder Modifikationen sind durch die abhängigen Ansprüche, die Figuren und die Beschreibung offenbart.

**[0004]** Insbesondere wird ein Substrat bereitgestellt, das ein Halbleitersubstrat mit einer ersten Hauptoberfläche, einer zweiten Hauptoberfläche und mindestens einem von der ersten Hauptoberfläche zu der zweiten Hauptoberfläche reichenden Kanal umfasst. Der mindestens eine Kanal weist in einem ersten Abschnitt eine erste Querschnittsfläche und in einem zweiten Abschnitt eine zweite Querschnittsfläche auf, wobei die erste Querschnittsfläche größer als die zweite Querschnittsfläche ist. Der Kanal ist in dem ersten Abschnitt mit einem aus einer Schmelze eingebrachten elektrisch leitenden ersten Material gefüllt und in dem zweiten Abschnitt mit einem elektrisch leitenden zweiten Material.

**[0005]** Ferner wird ein Halbleitermodul bereitgestellt, das ein Substrat und eine integrierte Schaltung umfasst. Das Substrat ist wie das vorstehend beschriebene Substrat ausgebildet. Die integrierte Schaltung ist auf das Substrat aufgebracht.

**[0006]** Des Weiteren wird ein Verfahren angegeben, bei dem ein Halbleitersubstrat mit einer ersten Hauptoberfläche, einer zweiten Hauptoberfläche und mindestens einem von der ersten Hauptoberfläche zu der zweiten Hauptoberfläche reichenden Kanal bereitgestellt wird. Der mindestens eine Kanal weist in einem ersten Abschnitt eine erste Querschnittsfläche und in einem zweiten Abschnitt eine zweite Querschnittsfläche auf. In den ersten Abschnitt des mindestens einen Kanals wird unter Druck im geschmolzenen Zustand ein elektrisch leitendes erstes Material eingefüllt.

**[0007]** Die Druckschrift DE 10 2005 042 074 A1 be-

schreibt ein Verfahren, bei dem durch ein Substrat führende konische Sacklöcher galvanisch gefüllt werden.

**[0008]** Die Druckschrift EP 0 926 723 A1 beschreibt ein Verfahren, bei dem Sacklöcher zunächst in einem CVD-Verfahren mit einer ersten Schicht und anschließend galvanisch mit einer Metallschicht bedeckt werden.

**[0009]** Die Druckschrift US 5,618,752 A beschreibt das Füllen von zylindrischen Sacklöchern über CVD-Verfahren, Sputtern oder Aufdampfen.

**[0010]** Die Druckschrift WO 2005/088699 A1 gibt ein Verfahren an, bei dem durch ein Substrat reichende Kanäle von einer ersten Seite mittels LPCVD-Verfahren und von einer zweiten Seite mittels galvanischem Abscheiden gefüllt werden.

**[0011]** Die Druckschrift US 7,176,128 B2 beschreibt ein Verfahren, bei dem Sacklöcher mittels CVD-Verfahren und galvanischem Abscheiden gefüllt werden.

**[0012]** Die Druckschrift Yamamoto, S. et al.; „Si thorough-hole interconnections filled with Au-Sn solder by molten metal suction method”; Micro Electro Mechanical Systems, 2003, MEMS-03 Kyoto; 19–23 Jan. 2003, pp. 642–645 beschreibt ein Verfahren zur Befüllung von Sacklöchern aus einer Schmelze.

**[0013]** Die Druckschrift JP 2006-013454P beschreibt das Befüllen eines sich zur Mitte hin verbreiternden Kanals mit schmelzflüssigem Material.

**[0014]** Im Folgenden werden einige Ausführungsformen beschrieben, deren Merkmale lediglich der Illustration der Erfindung dienen und diese in keiner Weise limitieren sollen.

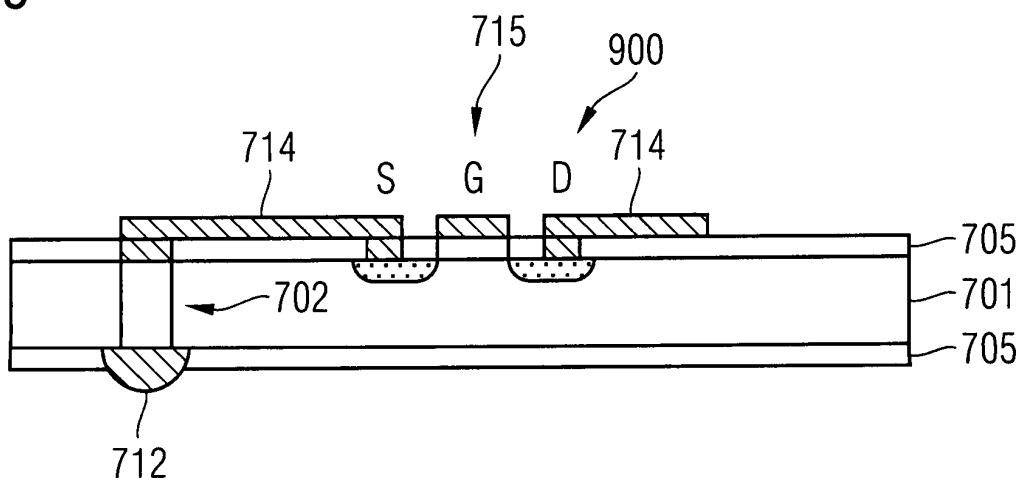

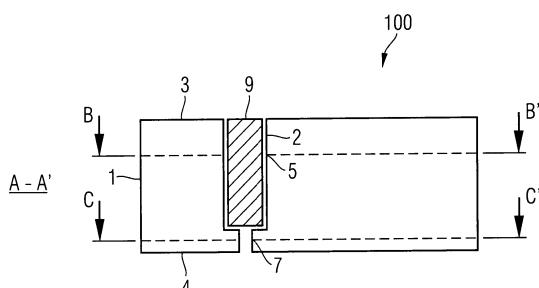

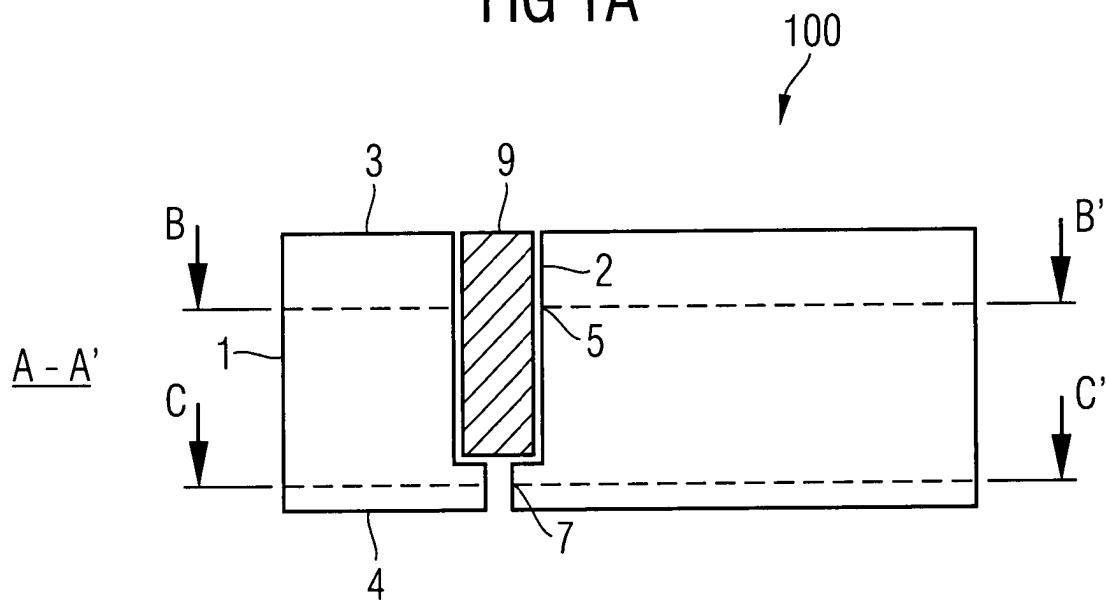

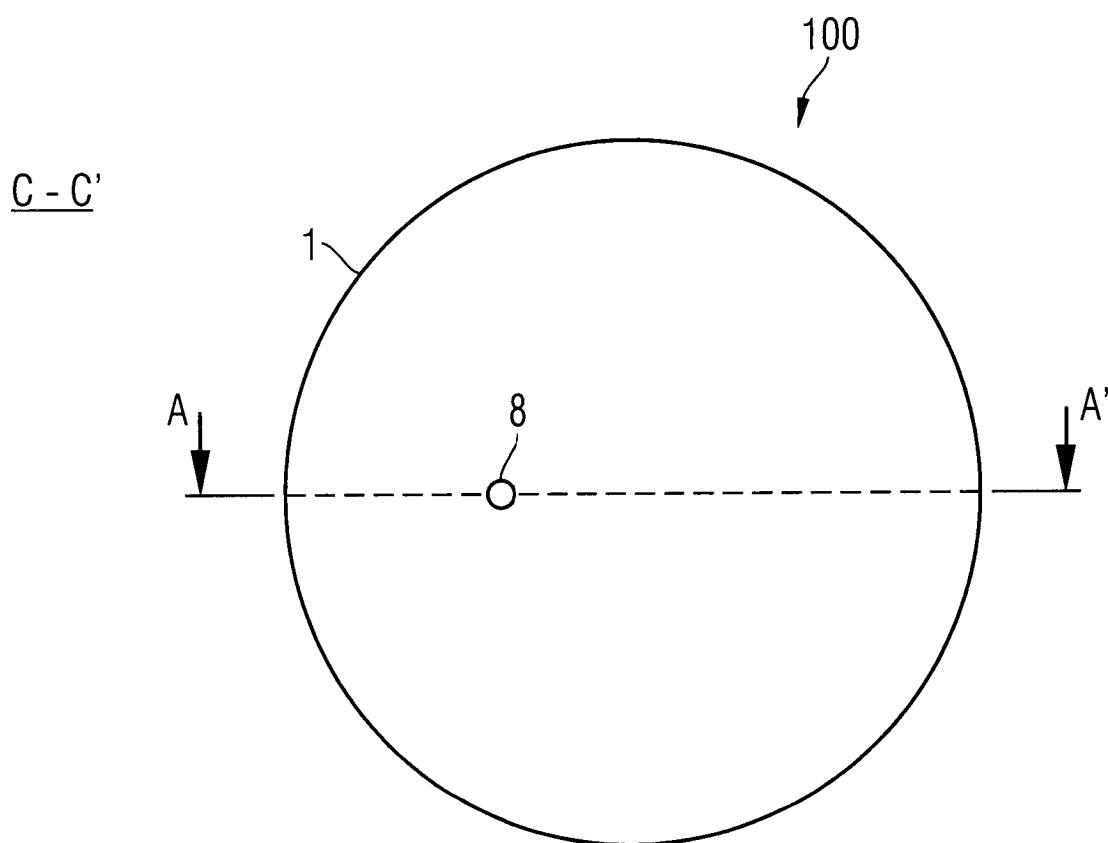

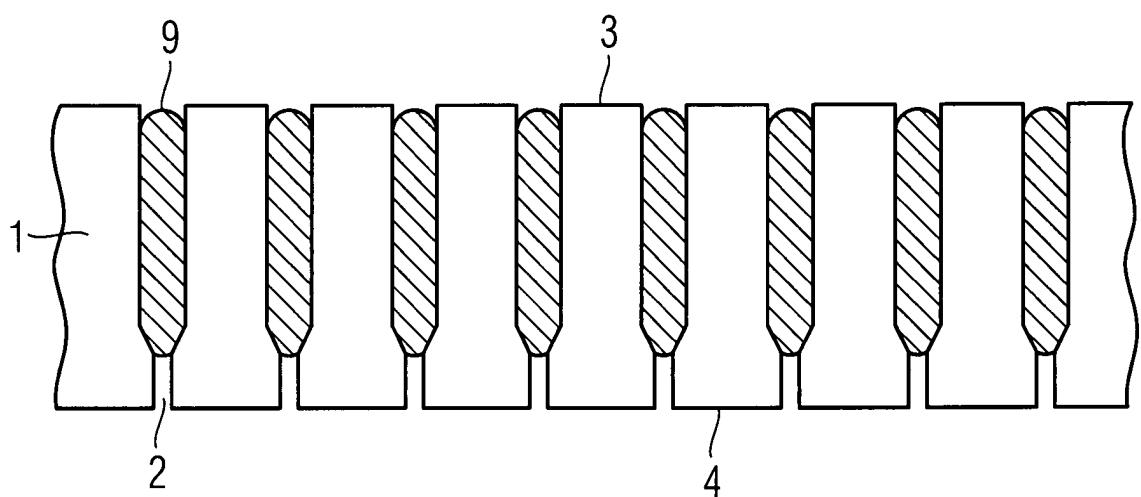

**[0015]** [Fig. 1A](#) bis [Fig. 1C](#) zeigen schematisch ein Substrat **100** und ein Verfahren zur Herstellung des Substrats **100**.

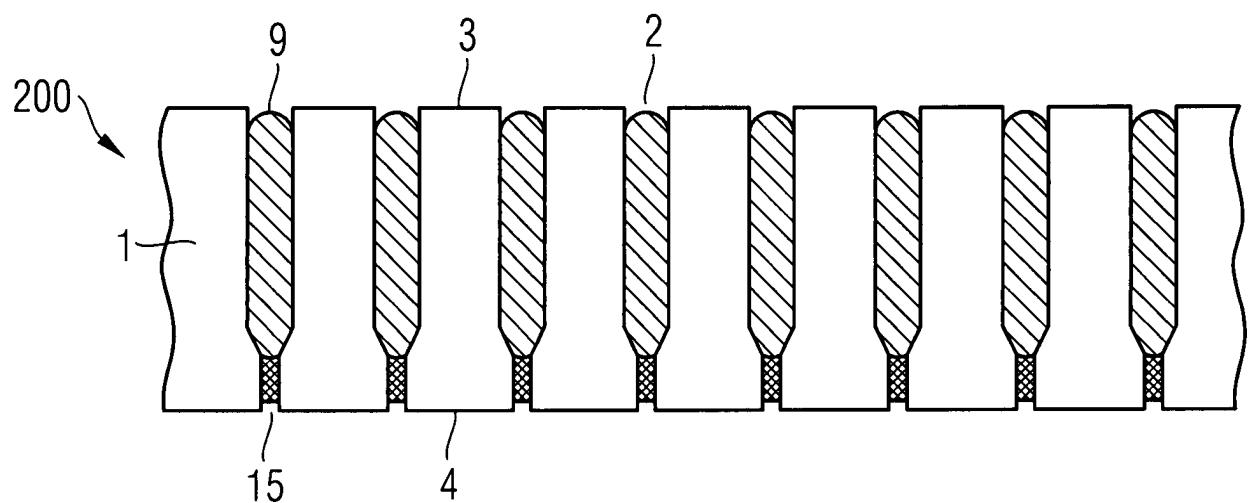

**[0016]** [Fig. 2A](#) bis [Fig. 2E](#) zeigen schematisch ein Substrat **200** und ein Verfahren zur Herstellung des Substrats **200**.

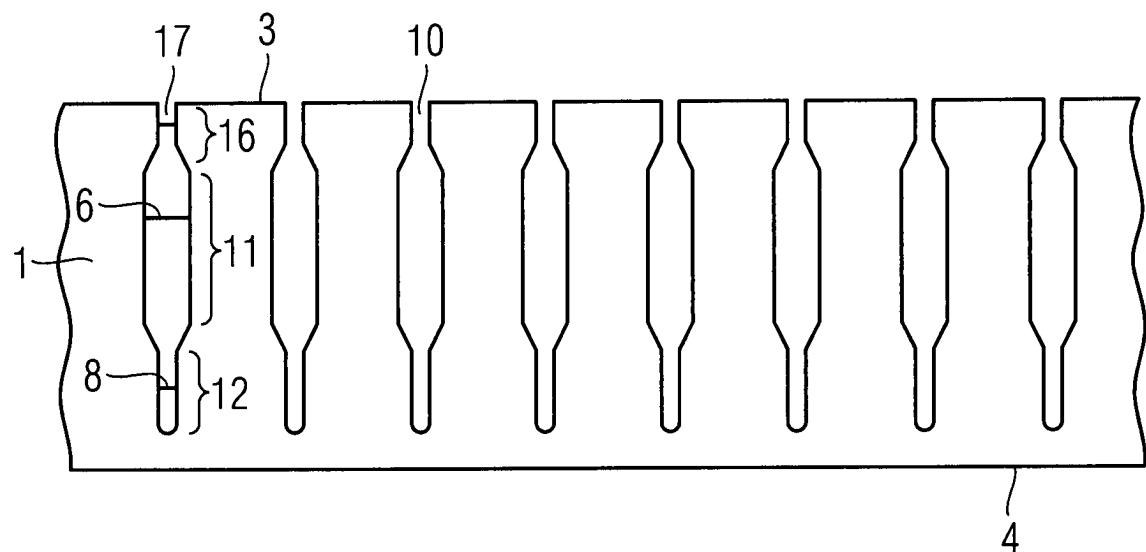

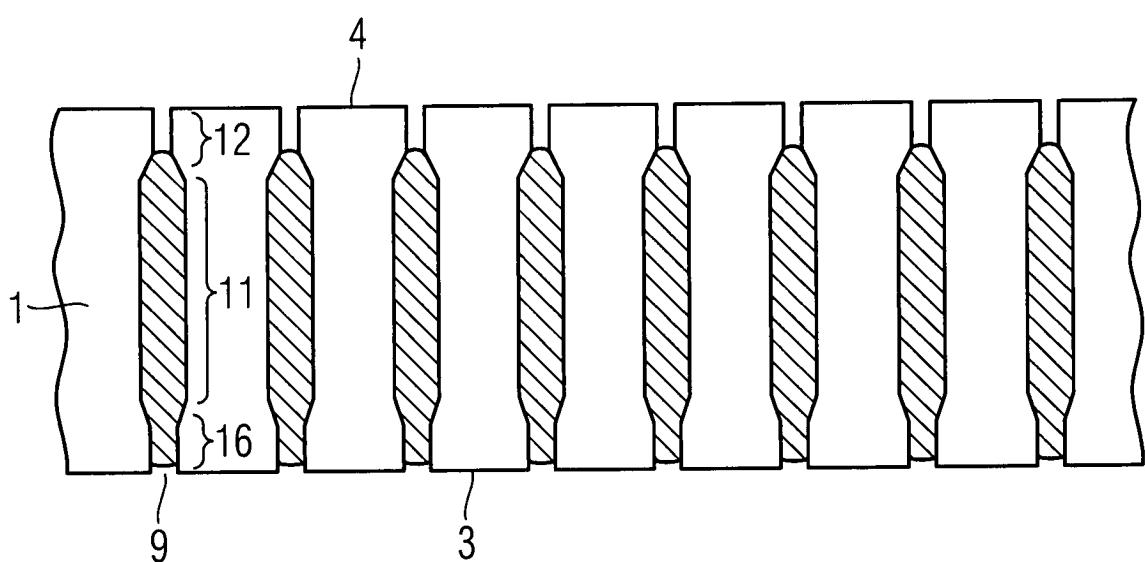

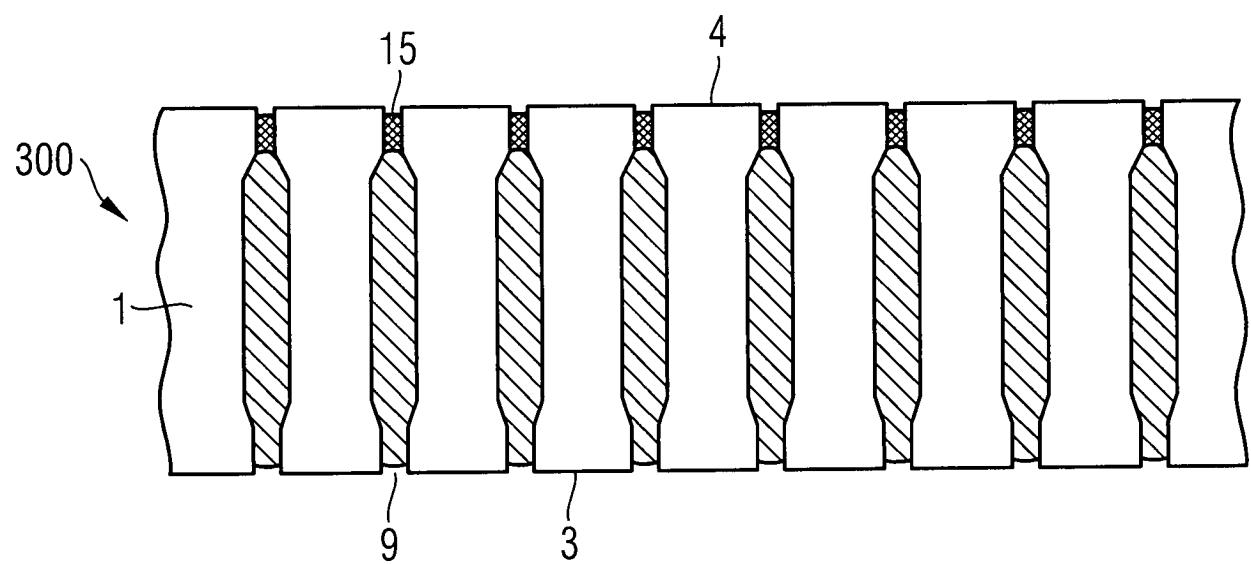

**[0017]** [Fig. 3A](#) bis [Fig. 3D](#) zeigen schematisch ein Substrat **300** und ein Verfahren zur Herstellung des Substrats **300**.

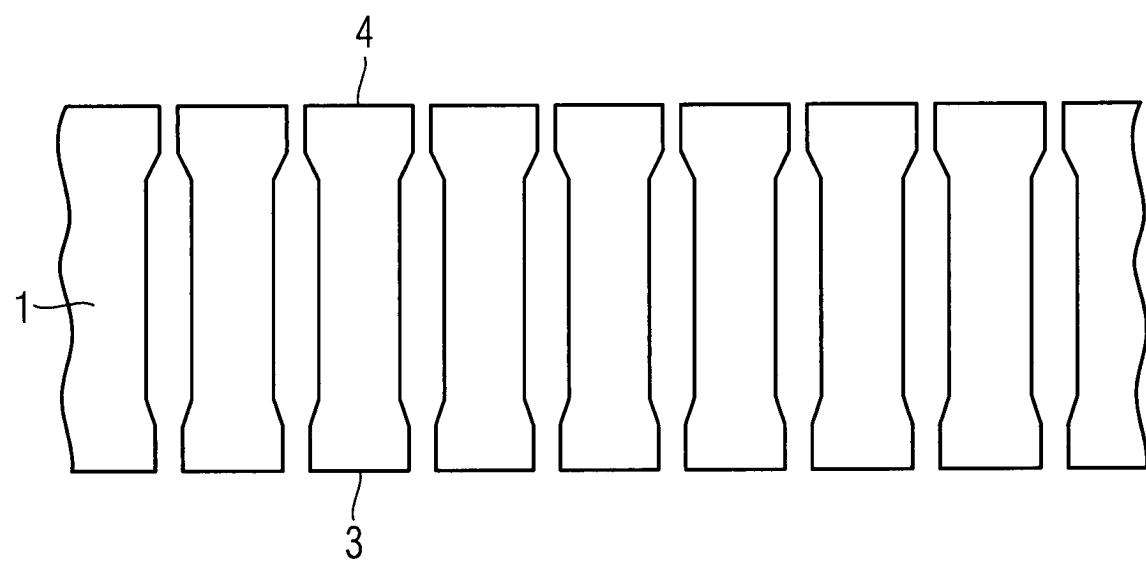

**[0018]** [Fig. 4A](#) bis [Fig. 4D](#) zeigen schematisch ein Substrat **400** und ein Verfahren zur Herstellung des Substrats **400**.

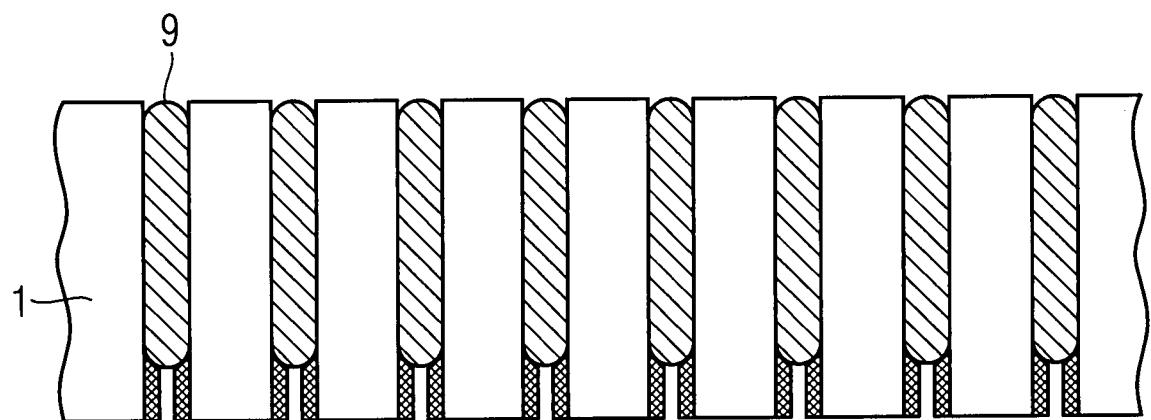

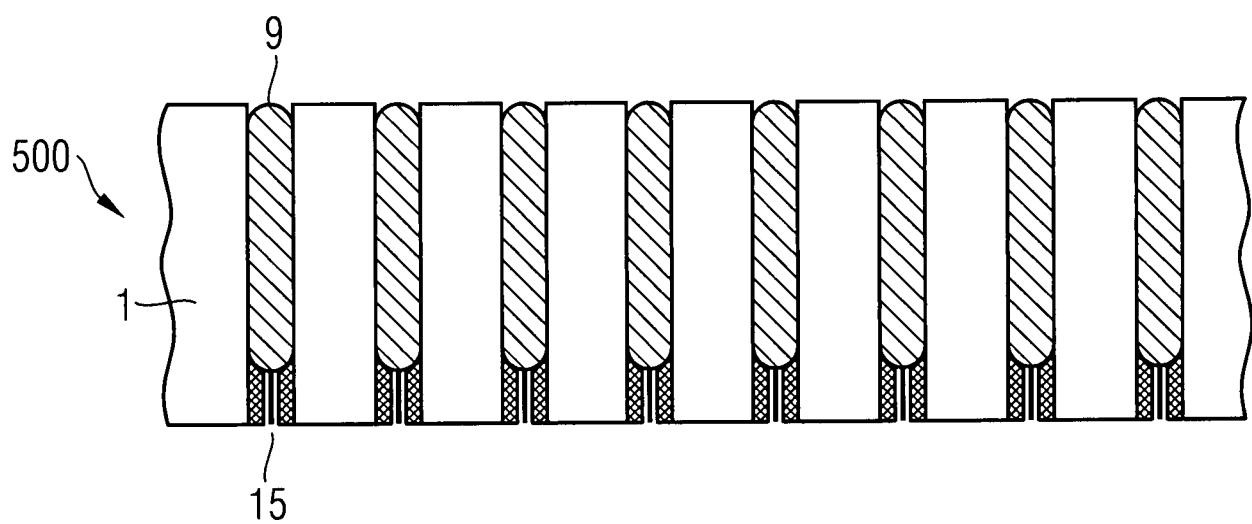

**[0019]** [Fig. 5A](#) bis [Fig. 5D](#) zeigen schematisch ein Substrat **500** und ein Verfahren zur Herstellung des Substrats **500**.

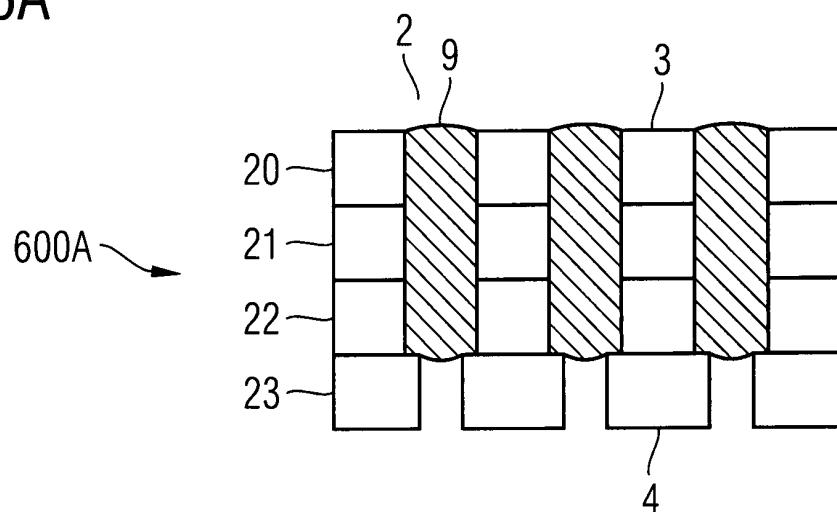

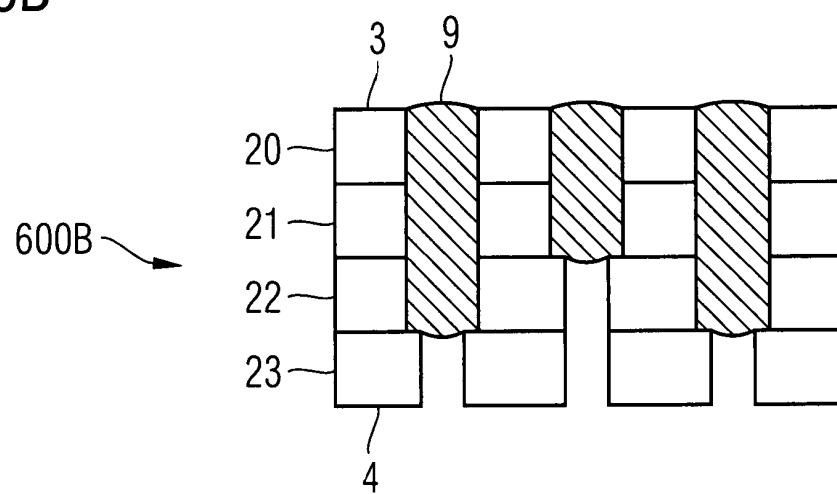

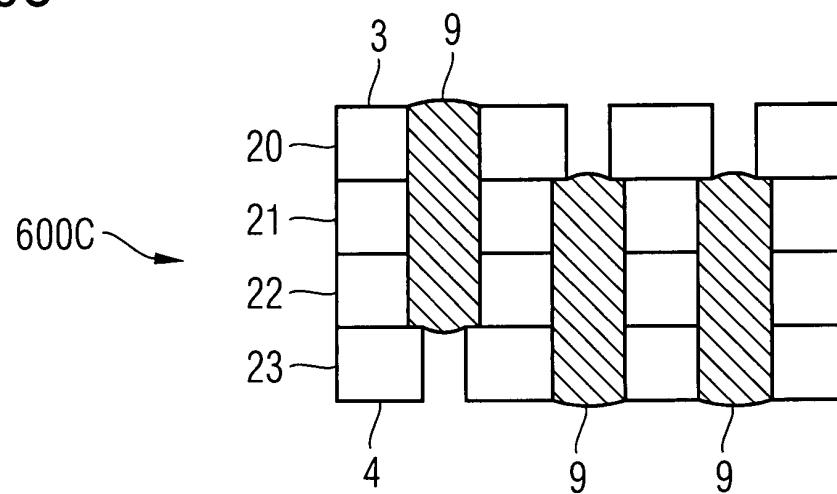

[0020] [Fig. 6A](#) bis [Fig. 6C](#) zeigen schematisch Substrate 600A, 600B und 600C.

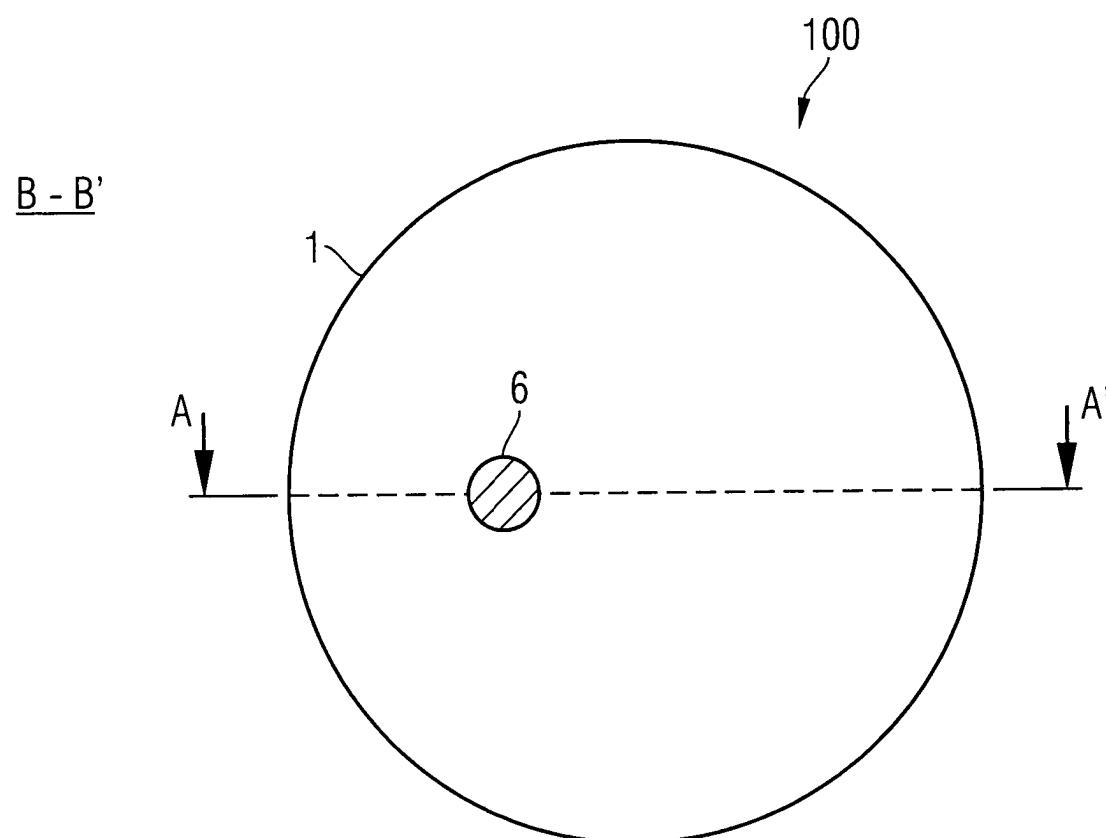

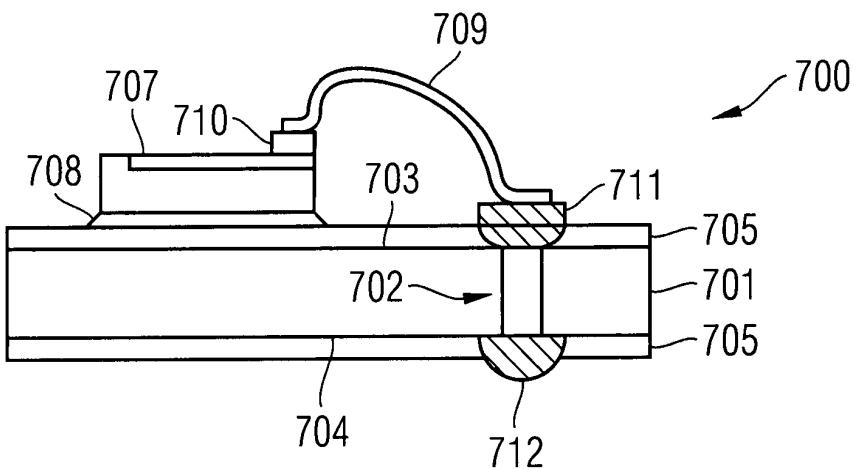

[0021] [Fig. 7](#) zeigt schematisch ein Halbleitermodul 700.

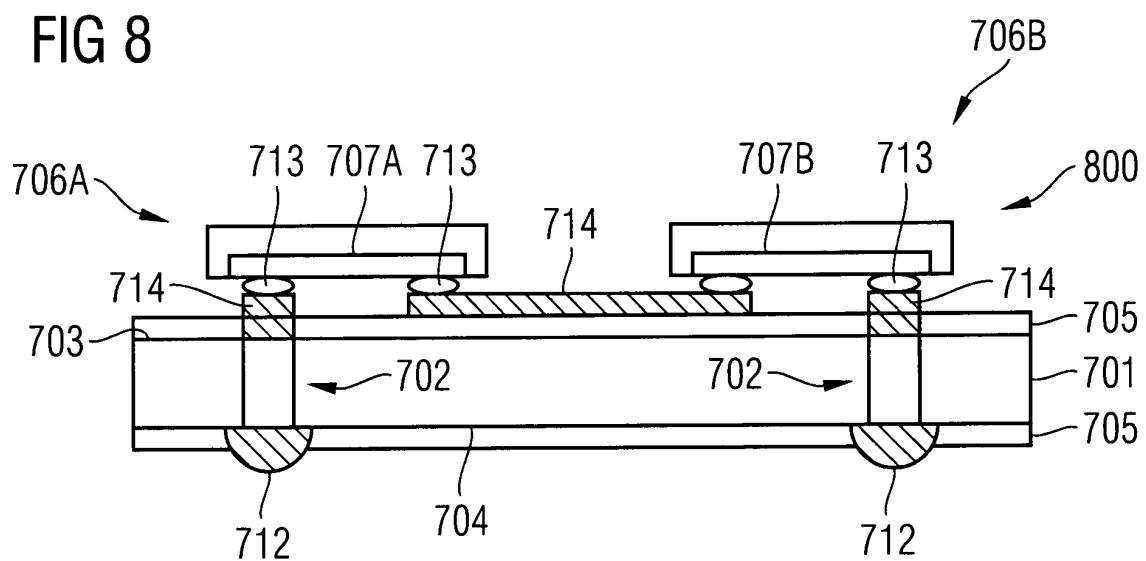

[0022] [Fig. 8](#) zeigt schematisch ein Halbleitermodul 800.

[0023] [Fig. 9](#) zeigt schematisch ein Halbleitermodul 900.

[0024] Im Folgenden werden Substrate sowie Verfahren zur Herstellung der Substrate beschrieben. Die Substrate können als Träger dazu dienen, auf der Mikro- oder Nanometerskala strukturierte Vorrichtungen, z. B. integrierte elektrische oder elektrooptische Schaltungen, Sensoren oder mikromechanische Apparate, in Position zu halten und/oder in Verbindung mit der Außenwelt zu setzen. Die Substrate können Halbleitersubstrate enthalten, insbesondere Siliziumsubstrate, Germaniumsubstrate, GaAs-Substrate, SiC-Substrate, vollständig oder partiell oxidiertes makroporöses Silizium etc. Die Halbleitersubstrate können aufgrund ihrer guten Strukturierbarkeit und der Halbleitern innewohnenden elektronischen Eigenschaften sowohl als Träger als auch als Bauelemente mit integrierten aktiven Komponenten, z. B. Transistoren, Dioden, beweglichen Strukturelementen, Sensorslementen etc., dienen. Aufgrund der hoch entwickelten Halbleiterprozesstechnologie können die aktiven Komponenten mit sehr hoher Dichte in ein Halbleitersubstrat integriert werden.

[0025] Sofern die Halbleitersubstrate als Träger verwendet werden, können sie ein oder mehrere weitere Halbleitersubstrate („Chips“) aufnehmen, welche selber sowohl als Träger dienen können und/oder in welche aktive Komponenten integriert sind. Die Chips können auf das Trägersubstrat geklebt oder gelötet werden oder auf ähnliche Weise befestigt sein. Die elektrisch leitenden Kontakte zwischen den Chips bzw. zwischen den Chips und der Außenwelt können ggf. durch Bonddrähte, Flip-Chip-Bonden oder zusätzlich aufgebrachte Leiterbahnen hergestellt werden. Auf diese Weise lässt sich ein Halbleitersubstrat als Träger zur Herstellung kompakter, hochintegrierter „System in Package“ (SiP)-Module verwenden. Diese Module können im Bereich Kommunikationstechnik sowie Automobil-, Industrie- und Konsumentenelektronik (z. B. Hochfrequenzmodul für Mobiltelefone, Basisstation oder auch Radarmodule für Automobile) verwendet werden.

[0026] Die Verwendung von Silizium als Substraträger hat den weiteren Vorteil, dass die meisten integrierten Bauelemente ebenfalls in Silizium integriert sind. In diesem Fall hätte ein Substraträger aus Silizium den gleichen Temperaturausdehnungskoeffizienten (CTE) wie die auf ihn montierten Bauelemente.

Das reduziert die destruktiven mechanischen Kräfte, die sich zwischen Träger und Bauelement aufgrund von thermischen Zyklen während des Betriebs bilden können. Aufgrund der guten Strukturierbarkeit von Halbleitern und der hoch entwickelten Halbleitertechnologie können die Kanäle in den Halbleitersubstraten besonders kleine Querschnittsflächen haben. Dadurch kann eine Kanaldichte auf der Substratoberfläche erzeugt werden, die den Strukturbreiten eines integrierten Halbleiterbauelements entspricht, z. B. einige 100 nm.

[0027] Für eine hohe Systemintegration ist es hilfreich, wenn das Substrat elektrisch leitende Durchführungen von einer Hauptoberfläche zu der anderen Hauptoberfläche des Substrats aufweist. Damit können Leiterbahnen auf beiden Seiten des Substrats miteinander elektrisch leitend verbunden werden. Auf diese Weise lassen sich kurze elektronische Verbindungen zwischen elektronischen Komponenten und Bauelementen herstellen, die auf gegenüberliegenden Hauptoberflächen des Substrats angeordnet sind. Dadurch kann eine vorgegebene Substratoberfläche ökonomisch genutzt, Packungsgrößen minimiert und der Aufwand zusätzlicher Leiterbahnebenen vermieden werden.

[0028] Beispielsweise können direkte Verbindungen zwischen einem auf der einen Hauptoberfläche des Halbleitersubstrats Flip-Chip-montierten integrierten Bauelement und auf der anderen Hauptoberfläche des Substrats angeordneten Kontaktlementen hergestellt werden. Sind die Positionen der elektrisch leitenden Durchführungen an den Positionen der Chip-Kontakte ausgerichtet, können die Durchführungen für kurze Verbindungen zu den Kontaktlementen sorgen, um z. B. schnelle Signale, (z. B. HF-Signale) möglichst störungs- und verzögerungsfrei nach außen zu führen.

[0029] Wenn ein Substrat über eine integrierte Schaltung auf einer Vorderseite verfügt und darüber hinaus elektrisch leitende Durchführungen vorhanden sind, können diese dazu verwendet werden, Signale des integrierten Bauelements direkt auf die Substratrückseite zu führen. Auf diese Weise können mit Hilfe von auf die elektrisch leitenden Durchführungen gelöteten Kontaktlementen besonders kurze elektrische Verbindungen zwischen der integrierten Schaltung und der Außenwelt hergestellt werden. Die rückseitigen Kontaktlemente erlauben zudem einen Stapelaufbau, bei dem integrierte Bauelemente übereinander gestapelt und direkt kontaktiert werden können.

[0030] Die elektrisch leitenden Durchführungen sind in Kanäle durch das Halbleitersubstrat eingebracht. Die Kanäle erstrecken sich jeweils von einer ersten Hauptoberfläche des Halbleitersubstrats zu einer zweiten Hauptoberfläche des Halbleitersubstrats.

Gewöhnlich sind die erste und die zweite Hauptoberfläche die zwei großen gegenüberliegenden Flächen des Halbleitersubstrats. Insbesondere sind die Hauptoberflächen die beiden Oberflächen einer runden monokristallinen Halbleiterscheibe („Wafer“) oder deren gesägten Teile („Chip“). Die Flächen einer Halbleiterscheibe sind i. A. standardisiert entsprechend vorgegebener Scheibendurchmesser, z. B. 4-Zoll, 8-Zoll, 10-Zoll, 12-Zoll (300 mm). Die Dicken der Scheiben können variieren in Bereichen von typischerweise 100 bis 1000 µm, wobei diese Werte bei speziellen Anwendungen auch kleiner oder größer sein können.

**[0031]** Der mindestens eine oder die mehrfachen Kanäle weisen jeweils eine erste Öffnung auf der ersten Hauptoberfläche und eine zweite Öffnung auf der zweiten Hauptoberfläche des Halbleitersubstrats auf. Liegen die beiden Öffnungen übereinander, so kann der Kanal in einer zur ersten oder zweiten Hauptoberfläche weitgehend senkrechten Richtung die erste Öffnung mit der zweiten Öffnung verbinden. In diesem Fall entspricht die Kanallänge im Wesentlichen der Dicke des Halbleitersubstrats.

**[0032]** In den mindestens einen Kanal ist ein elektrisch leitendes erstes Material und insbesondere ein elektrisch leitendes zweites Material eingebracht. Die elektrisch leitenden ersten und zweiten Materialien sowie evtl. weitere elektrisch leitende Materialien bilden die elektrisch leitende Durchführung durch den mindestens einen Kanal. Die elektrisch leitenden Materialien können beispielsweise Metalle, wie z. B. Kupfer, Silber oder Gold, oder Legierungen oder auch Hartlote, z. B. auf Silberbasis (z. B. AgCu28), Weichlote, z. B. auf Zinnbasis, etc. sein. Die Wahl der elektrisch leitenden Materialien kann den gewünschten Anforderungen bzw. Einsatzgebieten des Substrats angepasst werden.

**[0033]** Der mindestens eine Kanal durch das Halbleitersubstrat weist an einer ersten Stelle eine erste Querschnittsfläche auf und an einer zweiten Stelle eine zweite Querschnittsfläche. Die erste und die zweite Querschnittsfläche sind unterschiedlich groß. Ferner kann der mindestens eine Kanal an weiteren Stellen die erste oder zweite Querschnittsfläche aufweisen. Beispielsweise kann innerhalb eines ersten Abschnitts die erste Querschnittsfläche vorliegen und innerhalb eines zweiten Abschnitts die zweite Querschnittsfläche. Darüber hinaus ist es auch möglich, dass der mindestens eine Kanal an einer dritten Stelle bzw. in einem dritten Abschnitt eine dritte Querschnittsfläche aufweist, die sich von der ersten und/oder zweiten Querschnittsfläche unterscheidet. In entsprechender Weise kann der mindestens eine Kanal an weiteren Stellen auch andere Querschnittsflächen aufweisen. In Abhängigkeit von dem Herstellungsverfahren, mit welchem der mindestens eine Kanal in dem Halbleitersubstrat hergestellt wird, kann

es zu mehr oder weniger scharfen Übergängen zwischen verschiedenen Querschnittsflächen kommen.

**[0034]** Die Querschnittsflächen des mindestens einen Kanals können beispielsweise im Wesentlichen kreisförmig ausgebildet sein, sie können aber auch andere geometrische Formen annehmen. Im Fall kreisförmiger Querschnittsflächen haben die erste und die zweite Querschnittsfläche unterschiedliche Durchmesser. Je nach Anwendung und Substratmaterial können die Querschnittsflächen Werte annehmen, die zwischen einigen 100 Quadratnanometern bis hin zu einigen Quadratmillimetern liegen. Größere oder kleinere Werte können jedoch nicht ausgeschlossen werden. Die Größe der Querschnittsflächen kann davon abhängen, wie viel Strom durch die elektrisch leitende Durchführung fließen soll, ob die elektrisch leitende Durchführung auch zur thermischen Ableitung der Wärme von, z. B., Wärme erzeugenden integrierten Schaltungen dienen soll, ob gewisse Induktions- oder Kapazitätsanforderungen erfüllt werden sollen, etc. Schließlich hängt die Querschnittsfläche auch davon ab, wie viele Durchführungen erzeugt werden und wie groß die Dichte der Durchführungen sein sollen.

**[0035]** Es folgen nun detaillierte Beschreibungen von Ausführungsbeispielen, die in den beiliegenden Figuren schematisch und keineswegs maßstabsgetreu illustriert sind.

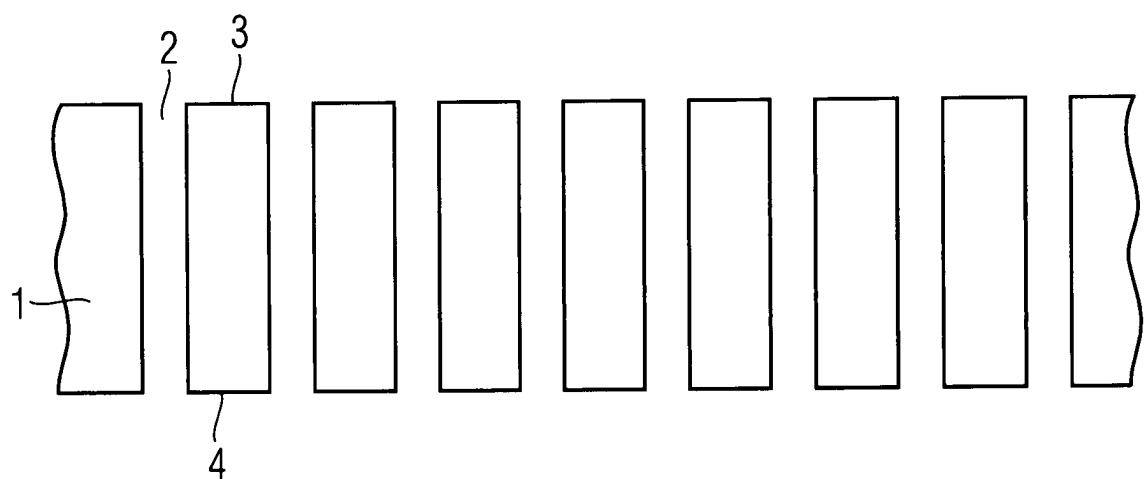

**[0036]** [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#) zeigen Schnitte A-A', B-B' bzw. C-C' durch ein Substrat **100**. Die Schnitte B-B' und C-C' verlaufen parallel zueinander und senkrecht zu dem Schnitt A-A'. Das Substrat **100** besteht aus einem beispielsweise kreisrunden Halbleitersubstrat **1**, in das mindestens ein Kanal **2** eingebracht worden ist. Der Kanal **2** erstrecken sich von einer ersten Hauptoberfläche **3** zu einer zweiten Hauptoberfläche **4** des Halbleitersubstrats **1**. An einer ersten Stelle **5**, durch die der Schnitt B-B' verläuft, weist der Kanal **2** eine erste Querschnittsfläche **6** und an einer zweiten Stelle **7**, durch die der Schnitt C-C' verläuft, weist der Kanal **2** eine zweite Querschnittsfläche **8** auf. Beispielsweise ist die zweite Querschnittsfläche **8** kleiner als die erste Querschnittsfläche **6**. In den Kanal **2** ist ein elektrisch leitendes erstes Material **9** eingebracht.

**[0037]** Nachfolgend werden anhand der [Fig. 2](#) bis [6](#) weitere Substrate **200** bis **600** und deren Herstellungsverfahren beschrieben. Die Substrate **200** bis **600** stellen Weiterbildungen des in [Fig. 1](#) gezeigten Substrats **100** dar. Die nachfolgend beschriebenen Ausgestaltungen der Substrate **200** bis **600** und deren Herstellungsverfahren können in entsprechender Weise auf das Substrat **100** bezogen werden.

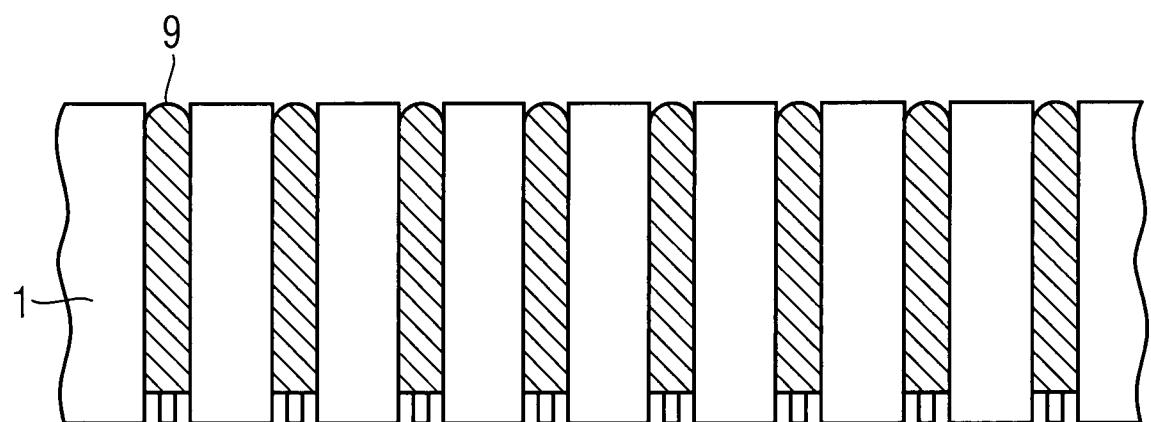

**[0038]** In [Fig. 2E](#) ist das Substrat **200** schematisch dargestellt, das eine Mehrzahl von Kanäle **2** enthält.

In den [Fig. 2A](#) bis [Fig. 2E](#) sind Schritte zur Herstellung des Substrats **200** gezeigt.

**[0039]** Zur Herstellung des Substrats **200** wird zunächst das Halbleitersubstrat **1** bereitgestellt, in welches an den Stellen, an denen später die Kanäle **2** durch das Halbleitersubstrat **1** verlaufen sollen, Sacklöcher **10** erzeugt werden. Die Herstellung der Sacklöcher **10** kann auf vielerlei Wegen geschehen. Eine mögliche Herstellungsvariante stellt das elektrochemische Ätzen dar. Zur Vorbereitung auf das elektrochemische Ätzen wird die erste Hauptoberfläche **3** des Halbleitersubstrats **1** selektiv zu einer Maske mit z. B. 10%-iger Kalilauge für z. B. 10 Minuten angeätzt. Anschließend wird die erste Hauptoberfläche **3** mit einem Elektrolyten, z. B. HF-Säure, bedeckt und eine Spannung zwischen der zweiten Hauptoberfläche **4** und dem Elektrolyten angelegt. Gleichzeitig wird die zweite Hauptoberfläche **4** mit einer Lichtquelle, z. B. mit 800 nm Wellenlänge, bestrahlt. Die Intensität der Lichtquelle wird so eingestellt, dass eine vorgegebene Stromdichte, z. B. 10 nA pro Sackloch, zwischen dem Halbleitersubstrat **1** und dem Elektrolyten fließt. Durch den Strom zwischen der angeätzten ersten Hauptoberfläche **3** des Halbleitersubstrats **1** und dem Elektrolyten bilden sich an den angeätzten Stellen Poren, die in das Halbleitersubstrat **1** hineinwachsen und die Sacklöcher **10** ausbilden.

**[0040]** Das elektrochemische Ätzen kann an p-dotierten oder an n-dotierten Halbleitersubstraten **1**, insbesondere Siliziumhalbleitersubstraten, durchgeführt werden, wobei deren Resistivität typischerweise in einem Bereich von 1 bis 2000 Ohm-cm und insbesondere in einem Bereich von 800 bis 1200 Ohm-cm liegt. Die Form, der Durchmesser, die Tiefe und die Dichte der erzeugten Sacklöcher **10** hängen stark von der Stromdichte, der Dotierung, der Säurestärke und der Ätzzeit ab und müssen dementsprechend für jede neue Anwendung neu bestimmt werden.

**[0041]** Das elektrochemische Ätzen eröffnet die Möglichkeit, durch eine Änderung von Ätzparametern während des Ätzvorgangs die Querschnittsflächen innerhalb der einzelnen Sacklöcher **10** zu variieren. Beispielsweise bildet sich in den Sacklöchern **10** eine umso größere Querschnittsfläche aus, je größer der Ätzstrom ist. Insbesondere besteht zwischen dem Ätzstrom und der durch das elektrochemische Ätzen erzeugten Querschnittsfläche eine quadratische Abhängigkeit. So wurde beispielsweise während des Ätzens eines in [Fig. 2A](#) gezeigten ersten Abschnitts **11** der Sacklöcher **10** ein größerer Ätzstrom eingestellt als für das Ätzen eines zweiten Abschnitts **12**. Dadurch hat sich in dem ersten Abschnitt **11** eine größere Querschnittsfläche ausgebildet als in dem zweiten Abschnitt **12**. Der erste Abschnitt **11** enthält die erste Stelle **5** und der zweite Abschnitt **12** enthält die zweite Stelle **7** der Kanäle **2**.

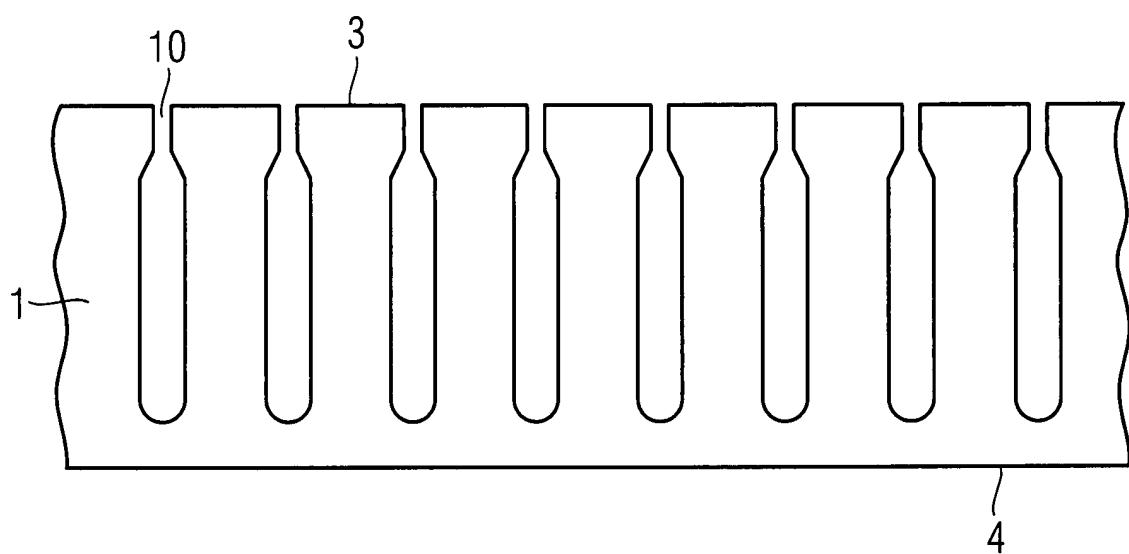

**[0042]** In [Fig. 2B](#) ist als Alternative zu [Fig. 2A](#) gezeigt, dass der Ätzstrom auch so eingestellt werden kann, dass die Sacklöcher **10** anfänglich mit einem kleinen Durchmesser erzeugt werden, und nach einer gewissen Zeit der Ätzstrom so eingestellt wird, dass die Sacklöcher **10** aufgeweitet werden.

**[0043]** Um aus den Sacklöchern **10** jeweils einen vollständigen Kanal **2** von der ersten Hauptoberfläche **3** zu der zweiten Hauptoberfläche **4** auszubilden, können die Sacklöcher **10** in einem weiteren Ätzschritt, z. B. mittels eines trocken- oder nasschemischen Ätzverfahrens, weitergeätzt werden, bis diese die zweite Hauptoberfläche **4** des Halbleitersubstrats **1** erreichen. Alternativ können die Sacklöcher **10** durch eine Materialabtragung von der zweiten Hauptoberfläche **4** her geöffnet werden. Beispielsweise kann die zweite Hauptoberfläche **4** durch Planarisierung mittels chemisch-mechanischen Polierens (CMP) geöffnet werden.

**[0044]** Für die Herstellung der Sacklöcher **10** und der Kanäle **2** können anstelle des oben beschriebenen elektrochemischen Ätzens auch andere Ätztechniken angewendet werden. Grundsätzlich können dazu die in der Mikromechanik bekannten Ätzverfahren, wie z. B. RIE (Reactive Ion Etching)-Verfahren, Laserbohren, Sandstrahlen oder Ultraschallbohren, herangezogen werden, solange diese Ätzverfahren erlauben, die Querschnittsfläche der Kanäle **2** in Abhängigkeit von der Tiefe zu variieren. Weiter unten werden im Zusammenhang mit der Beschreibung der [Fig. 4](#) bis [6](#) weitere Verfahren zur Herstellung der Sacklöcher **10** und Kanäle **2** vorgestellt.

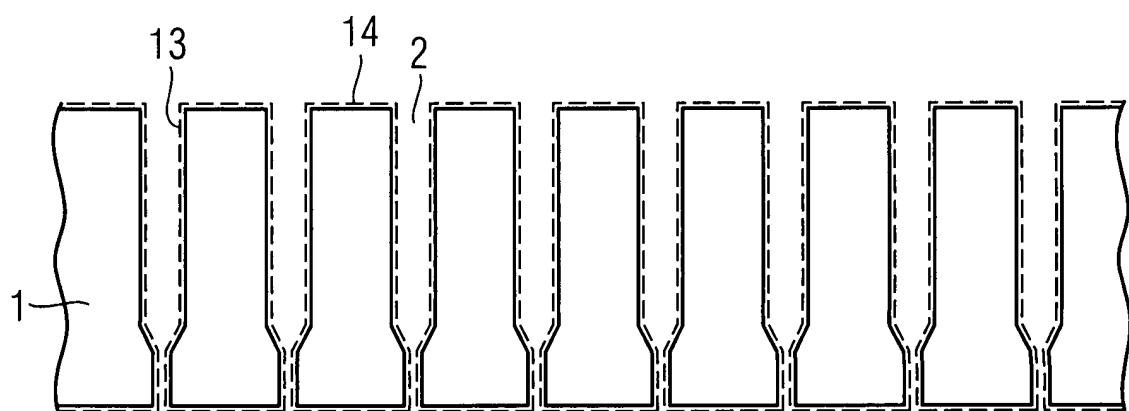

**[0045]** Die sich vollständig durch das Halbleitersubstrat **1** erstreckenden Kanäle **2** sind in [Fig. 2C](#) dargestellt. Das Halbleitersubstrat **1** kann eine Dicke im Bereich von 25 bis 2000 µm, insbesondere im Bereich von 100 bis 250 µm aufweisen. Die Kanäle **2** können einen Durchmesser im Bereich von 2 bis 150 µm und insbesondere im Bereich von 10 bis 30 µm aufweisen. Das Verhältnis von Kanallänge zu Kanaldurchmesser (Aspekt-Verhältnis) kann in einem Bereich von 2 bis 1000 liegen, insbesondere können relativ große Aspekt-Verhältnisse oberhalb von z. B. 100 vorliegen.

**[0046]** Um die Durchführungen benachbarter Kanäle **2** elektrisch voneinander zu isolieren, können die Oberflächen der Kanäle **2** mit einer ersten Isolationsschicht **13** versehen werden, die in [Fig. 2C](#) durch eine dickere Linie dargestellt ist. Die erste Isolationsschicht **13** kann eine Oxid- und/oder eine Nitridschicht sein. Sofern das Halbleitersubstrat **1** aus Silizium gefertigt ist, kann die erste Isolationsschicht **13** z. B. eine SiO<sub>2</sub>-Schicht sein, die beispielsweise mittels eines CVD (Chemical Vapour Deposition)-Prozesses aus TEOS (Tetra-Ethyl-Ortho-Silicat) erzeugt wird oder gesputtert wird, oder eine Si<sub>3</sub>N<sub>4</sub>-Schicht, die

aus Silan ( $\text{SiH}_4$ ) und Ammoniak ( $\text{NH}_3$ ) erzeugt wird. Die erste Isolationsschicht **13** kann auch eine Kombination verschiedener Isolationsschichten sein, z. B. eine ONO-Schicht, die eine Kombination der oben genannten Oxid-Nitrid-Oxid-Schichten ist.

**[0047]** Des Weiteren kann die Isolationsschicht **13** eine thermisch erzeugte  $\text{SiO}_2$ -Schicht sein. Bei der thermischen Oxidation wird die  $\text{SiO}_2$ -Schicht nicht abgeschieden, sondern das bereits an der Siliziumoberfläche freiliegende Silizium wird durch Erwärmung (ca. 900 bis 1200°C) und Sauerstoffzufuhr in Siliziumdioxid umgewandelt. Thermisch erzeugtes Siliziumdioxid bildet im Unterschied zu auf andere Weise erzeugtem Siliziumdioxid eine sehr störstellenfreie Grenzfläche mit dem Siliziumgitter. Dadurch werden Leckströme im Silizium an der  $\text{Si}/\text{SiO}_2$ -Grenzfläche reduziert. Ferner wird die parasitäre Kapazität zwischen den später in die Kanäle **2** einzubringenden elektrisch leitenden Materialien und dem Silizium minimiert. Minimale parasitäre Kapazitäten sind insbesondere wichtig für Hochfrequenz-Anwendungen.

**[0048]** Die Dicke der ersten Isolationsschicht **13** liegt je nach Anwendung im Bereich von 5 bis 1000 nm, insbesondere zwischen 100 und 200 nm.

**[0049]** Insbesondere wird nicht nur die Oberfläche in den Kanälen **2** sondern die gesamte Oberfläche des Halbleitersubstrats **1**, d. h. die in den Kanälen **2** und die auf den beiden Hauptoberflächen **3** und **4** des Halbleitersubstrats **1**, mit der ersten Isolationsschicht **13** versehen. Im Falle eines Siliziumsubstrats **1** kann dies in einem einzigen Schritt geschehen, z. B. durch eine thermische Oxidation oder eine Nitridisierung des mit den Kanälen **2** versehenen Siliziumsubstrats **1**. Dies ist eine verfahrensökonomische Weise, um das Halbleitersubstrat **1** sowohl in den Kanälen **2** als auch an den Hauptoberflächen **3** und **4** von den später in die Kanäle **2** einzubringenden leitenden Materialien elektrisch zu isolieren. Insbesondere wird die erste Isolationsschicht **13** so aufgebracht, dass die Schichtdicke der ersten Isolationsschicht **13** in den Kanälen **2** von der Schichtdicke auf der ersten oder zweiten Hauptoberfläche **3**, **4** um weniger als 50% und insbesondere um weniger als 20% abweicht.

**[0050]** Sofern die erste Isolationsschicht **13** aus einem thermisch erzeugten Siliziumdioxid besteht, kann dieses an der ersten und/oder zweiten Hauptoberfläche **3**, **4** als Oxid für die Gates von MOS-Transistoren verwendet werden. Das thermisch erzeugte Siliziumdioxid bietet auch hier den Vorteil einer sehr störstellenfreien  $\text{Si}/\text{SiO}_2$ -Grenzfläche, wodurch Leckströme im Silizium minimiert werden. Durch die Verwendung eines thermischen Oxids als erster Isolationsschicht **13** ist der Herstellungsprozess der Durchführungen durch das Halbleitersubstrat **1** kompatibel mit Standard-CMOS-Prozessen. Dies ermöglicht es, einen Siliziumchip bzw. -wafer mit integrierten Schal-

tungen und mit beliebig vielen Durchführungen kostengünstig auszustatten.

**[0051]** Optional kann auf die erste Isolationsschicht **13** eine Barrierenschicht **14** aufgebracht werden, die eine Diffusion der später in die Kanäle **2** einzubringenden elektrisch leitenden Materialien in das Halbleitersubstrat **1** verhindert. Die Barrierenschicht **14** kann z. B. eine TiN- oder TaN-Schicht sein, die durch Bedampfen oder einen CVD-Prozess auf die Oberflächen der Kanäle **2** aufgebracht wird. Die Schichtdicke der Barrierenschicht **14** beträgt z. B. 100 nm. Die Barrierenschicht **14** ist beispielhaft nur in [Fig. 2C](#) durch eine gestrichelte Linie dargestellt und, da optional, in den folgenden Figuren nicht mehr angedeutet.

**[0052]** [Fig. 2D](#) zeigt das Substrat **200**, nachdem die Kanäle **2** mit dem elektrisch leitenden ersten Material **9** gefüllt worden sind. Das Füllen der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** dient dazu, das für eine elektrisch leitende Durchführung erforderliche Material oder zumindest einen Teil davon zur Verfügung zu stellen. Das elektrisch leitende erste Material **9** wird bevorzugt oberhalb seiner Schmelztemperatur in die Kanäle gefüllt. Das elektrisch leitende erste Material **9** ist insbesondere so gewählt, dass es eine Schmelzpunkttemperatur hat, die kleiner ist als diejenige des Halbleitersubstrats **1**. Ein Vorteil des Füllens der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** in flüssigem Zustand kann sein, dass dieser Prozess einen höheren Durchsatz und geringere Prozesskosten als herkömmliche Arten der Metallfüllung aufweisen kann, insbesondere im Vergleich zu aus der Gasphase (CVD) erfolgten Abscheidungen oder elektrochemischem oder chemischem Plating (electroless plating).

**[0053]** Als elektrisch leitendes erstes Material **9** können beispielsweise Kupfer (Schmelzpunkt: 1084°C), Silber (Schmelzpunkt: 962°C) oder Gold (Schmelzpunkt: 1064°C) verwendet werden. Diese Materialien weisen sehr gute elektrische Leitfähigkeiten und einen niedrigeren Schmelzpunkt als Silizium (Schmelzpunkt: 1410°C) auf.

**[0054]** Denkbar sind ferner auch Hartlote, z. B. auf Silberbasis (z. B. AgCu28), Weichlote, z. B. auf Zinnbasis, und weitere Metalle, wie z. B. Aluminium, Blei, Zink etc. Die Wahl des elektrisch leitenden ersten Materials **9** kann den gewünschten Anforderungen bzw. Einsatzgebieten des Substrats **200** angepasst werden.

**[0055]** Das Füllen mit dem elektrisch leitenden ersten Material **9** kann Kanalweise oder parallel erfolgen. Zum Füllen der Kanäle **2** kann das Halbleitersubstrat **1** beispielsweise in die Schmelze des elektrisch leitenden ersten Materials **9** eingetaucht werden, sodass die Schmelze im Wesentlichen gleichzeitig in die Kanäle **2** eindringen kann.

**[0056]** Insbesondere wird das elektrisch leitende erste Material **9** bei einem relativen Unterdruck in die Kanäle **2** eingebracht. Durch die Anwendung eines relativen Unterdrucks ist es möglich, auch schlecht benetzende Materialien in enge Kanäle einzubringen. Dabei gilt, dass je kleiner die Querschnittsfläche, je länger der Kanal und je schlechter die Benetzung, um so größer der für die Füllung des Kanals erforderliche relative Unterdruck ist. Ein relativer Unterdruck in den Kanälen **2** kann durch einen Überdruck, der beim Füllen des elektrisch leitenden ersten Materials **9** von außen auf die Schmelze ausgeübt wird, erzeugt werden.

**[0057]** Aufgrund der in **Fig. 2** gezeigten abschnittsweisen Verengung bzw. Verbreiterung der Kanäle **2** sind innerhalb eines Kanals **2** Bereiche vorhanden, die verschiedene Fülldrücke aufweisen. Für die Füllung des in **Fig. 2** gezeigten zweiten Abschnitts **12** der Kanäle **2** mit einer Metall- oder Legierungsschmelze wird aufgrund seiner geringeren zweiten Querschnittsfläche **8** ein größerer Fülldruck benötigt als für den ersten Abschnitt **11** mit der größeren ersten Querschnittsfläche **6**.

**[0058]** Beim Füllen der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** kann man sich das vorstehend beschriebene unterschiedliche Füllverhalten der ersten und zweiten Abschnitte **11** und **12** zunutzen machen. Bei einem bestimmten Fülldruck wird lediglich der erste Abschnitt **11** mit der Schmelze des elektrisch leitenden ersten Materials **9** gefüllt. Mit zunehmender Erhöhung des Drucks wird ein Grenzdruck erreicht, bei dem schließlich auch die Füllung des zweiten Abschnitts **12** erfolgt und der gesamte Kanal **2** mit Schmelze gefüllt ist. Der Zustand, bei dem der gesamte Kanal **2** mit der Schmelze des elektrisch leitenden ersten Materials **9** gefüllt ist, ist jedoch unerwünscht, da sich der Kanal **2** beim Herausziehen aus der Schmelze entleeren würde. Stattdessen sollte der Fülldruck derart eingestellt sein, dass der erste Abschnitt **11** mit der Schmelze gefüllt wird, der zweite Abschnitt **12** aber noch nicht gefüllt wird. In diesem Fall fungiert der zweite Abschnitt **12** als Ppropfen, der die vollständige Befüllung des Kanals **2** mit Schmelze verhindert. Dies hat den Vorteil, dass sich die Kanäle **2** beim Herausziehen des Halbleitersubstrats **1** aus der Schmelze nicht entleeren. Durch die Verengung der Kanäle **2** im zweiten Abschnitt **12** verhalten sich die Kanäle **2** beim Füllen mit dem elektrisch leitenden ersten Material **9** genauso wie Sacklöcher. Auch bei als Sacklöchern ausgestalteten Kanälen in einem Halbleitersubstrat muss ein relativer Unterdruck angewendet werden, um eine Schmelze in die Sacklöcher zu bringen. Jedoch müssen Sacklöcher nach dem Einbringen der Schmelze zu durchgehenden Kanälen geöffnet werden, um letztlich eine elektrisch leitende Durchführung durch das Halbleitersubstrat zu schaffen. Dieser Prozessschritt kann bei dem in **Fig. 2** gezeigten Vorgehen eingespart werden.

**[0059]** Der Prozessschritt zur Füllung der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** kann beispielsweise folgendermaßen ausgestaltet sein. Zunächst wird das Halbleitersubstrat **1** in eine gasdichte Prozesskammer eingeführt, welche die Schmelze des elektrisch leitenden ersten Materials **9** enthält. Während die Prozesskammer evakuiert wird, befindet sich das Halbleitersubstrat **1** außerhalb der Schmelze. Nachdem ein vorgegebener Druck im Bereich von 0,001 bis 100 mbar, insbesondere kleiner als 1 mbar, erreicht ist, wird das Halbleitersubstrat **1** in die Schmelze getaucht und die Prozesskammer anschließend mit Druck beaufschlagt. Der Druck liegt im Bereich von 1 bis 20 bar, insbesondere im Bereich von 5 bis 10 bar. Der zum Füllen der ersten Abschnitte **11** der Kanäle **2** erforderliche Druck hängt neben den Querschnittsflächen **6** und **8** der Kanäle **2** insbesondere von der Prozesstemperatur und der Oberflächenspannung des elektrisch leitenden ersten Materials **9** ab. Das Halbleitersubstrat **1** wird unter dem zum Füllen der Kanäle **2** eingestellten Druck aus der Schmelze gezogen. Nach dem Erstarren der Schmelze in den Kanälen **2** wird der Druck in der Prozesskammer wieder auf Normaldruck reduziert.

**[0060]** Durch den beim Füllen der Kanäle **2** aufgewendeten Druck braucht die Oberfläche in den Kanälen **2** auch bei einem schlecht benetzenden elektrisch leitenden ersten Material **9** nicht mit einer Haftschicht versehen werden. Durch das Weglassen von Haftschichtmaterialien in den Kanälen **2** können kostspielige zusätzliche Prozessierungsschritte eingespart werden.

**[0061]** Eine Befüllung der Kanäle **2** mit einem schlecht benetzenden elektrisch leitenden ersten Material **9** unter Druck kann bewirken, dass einerseits das elektrisch leitende erste Material **9** in die Kanäle **2** eindringt und dort nach dem Erstarren eine elektrisch leitende Durchführung oder einen Teil davon bildet und andererseits von den beiden Hauptoberflächen **3** und **4** des Halbleitersubstrats **1** abperlt. Durch das Abperlen kann eine Schichtbildung des durch eine Abkühlung erstarrenden ersten Materials **9** auf den beiden Hauptoberflächen **3** und **4** vermieden werden. Die Vermeidung einer solchen Schichtbildung auf den Hauptoberflächen **3** und **4** kann hindern, dass das Halbleitersubstrat **1** beim Abkühlen und Erstarren des flüssigen elektrisch leitenden ersten Materials **9** aufgrund unterschiedlicher Temperaturausdehnungskoeffizienten so großen mechanischen Spannungen ausgesetzt wird, dass es beschädigt würde.

**[0062]** Wie in **Fig. 2E** gezeigt ist, werden nach dem Füllen der ersten Abschnitte **11** mit dem elektrisch leitenden ersten Material **9** die zweiten Abschnitte **12** mit einem elektrisch leitenden zweiten Material **15** gefüllt. Dadurch wird in jedem der Kanäle **2** eine elektrisch leitende Durchführung erzeugt, die sich aus

den elektrisch leitenden ersten und zweiten Materialien **9** und **15** zusammensetzt und sich von der ersten Hauptoberfläche **3** bis zu der zweiten Hauptoberfläche **4** des Halbleitersubstrats **1** erstreckt.

**[0063]** Das elektrisch leitende zweite Material **15** wird oberhalb seiner Schmelztemperatur in die Kanäle **2** gefüllt. Das Füllen der zweiten Abschnitte **12** mit dem elektrisch leitenden zweiten Material **15** erfolgt ebenfalls bei einem relativen Unterdruck. Die oben im Zusammenhang mit dem Füllen der ersten Abschnitte **11** beschriebenen Prozessschritte können in entsprechender Weise beim Füllen der zweiten Abschnitte **12** durchgeführt werden. Dabei ist zu beachten, dass aufgrund der geringeren zweiten Querschnittsfläche **8** in den zweiten Abschnitten **12** ein höherer Fülldruck eingestellt werden muss.

**[0064]** Für das elektrisch leitende zweite Material **15** eignen sich insbesondere Metalle und Legierungen. Das elektrisch leitende zweite Material **15** wird insbesondere so gewählt, dass es eine Schmelzpunkttemperatur hat, die kleiner ist als diejenige des elektrisch leitenden ersten Materials **9**. Damit kann vermieden werden, dass das elektrisch leitende erste Material **9** während des Einfüllens des elektrisch leitenden zweiten Materials **15** in die zweiten Abschnitte **12** durch eine zu starke Erhitzung schmilzt. Das elektrisch leitende zweite Material **15** wird insbesondere derart gewählt, dass es kein niedrigerschmelzendes Eutektikum oder Legierung mit dem elektrisch leitenden ersten Material **9** bildet. Grundsätzlich eignen sich für das elektrisch leitende zweite Material **15** die Metalle, Legierungen, Hart- und Weichlote, die oben für das elektrisch leitende erste Material **9** genannt wurden. Beispielhaft sei die folgende Kombination genannt: Für das elektrisch leitende erste Material **9** wird z. B. AgCu (Schmelzpunkt: ca. 780°C) verwendet und für das elektrisch leitende zweite Material **15** z. B. SnAgCu (Schmelzpunkt: ca. 250°C).

**[0065]** Das Halbleitersubstrat **1** kann während der in **Fig. 2** gezeigten Prozessschritte Teil eines Halbleiterwafers sein. Dies ermöglicht es, die elektrisch leitenden Durchführungen für mehrere Halbleiterchips gleichzeitig herzustellen. Erst in einem späteren Prozessschritt wird der Halbleiterwafer in mehrere Halbleiterchips unterteilt, beispielsweise durch Sägen.

**[0066]** Vor oder nach der Herstellung der aus den beiden elektrisch leitenden Materialien **9** und **15** bestehenden Durchführungen können auf das Halbleitersubstrat **1** integrierte Bauelemente aufgebracht werden. Es können Prozessschritte durchgeführt werden, durch die Transistoren, Dioden oder sonstige Schaltungselemente oder Sensorelemente oder mikromechanische Elemente auf dem Halbleitersubstrat **1** integriert werden.

**[0067]** Alternativ oder zusätzlich können weitere

Substrate mit oder ohne integrierten Schaltungen auf das Substrat **200** aufgebracht werden. Auf diese Weise kann eine hohe Packungsdichte erzielt werden.

**[0068]** In **Fig. 3D** ist schematisch das Substrat **300** als weiteres Ausführungsbeispiel dargestellt. In den **Fig. 3A** bis **Fig. 3D** sind Schritte zur Herstellung des Substrats **300** gezeigt. Das Substrat **300** und dessen Herstellung entsprechen im Wesentlichen dem in **Fig. 2** gezeigten Substrat **200** und dessen Herstellung. Im Unterschied zu dem Substrat **200** weisen die Kanäle **2** des Substrats **300** jedoch nicht nur erste und zweite Abschnitte **11** und **12**, sondern darüber hinaus jeweils einen dritten Abschnitt **16** mit einer dritten Querschnittsfläche **17** auf. Die dritte Querschnittsfläche **17** kann sich von den ersten und zweiten Querschnittsflächen **6** und **8** der ersten und zweiten Abschnitte **11** und **12** unterscheiden. Dabei ist die dritte Querschnittsfläche **17** insbesondere größer als die zweite Querschnittsfläche **8**, aber kleiner als die erste Querschnittsfläche **6**. Sofern das oben beschriebene elektrochemische Ätzen zur Herstellung der Sacklöcher **10** angewendet wird, wird der Ätzstrom zur Erzeugung der dritten Abschnitte **17** entsprechend variiert.

**[0069]** Das Füllen der Kanäle **2** des Substrats **300** mit dem elektrisch leitenden ersten Material **9** erfolgt wie oben beschrieben bei einem relativen Unterdruck. Dabei wird der Druck in der Prozesskammer so eingestellt, dass die Schmelze des elektrisch leitenden ersten Materials **9** von der ersten Hauptoberfläche **3** des Halbleitersubstrats **1**, an welche die dritten Abschnitte **16** angrenzen, in die Kanäle **2** her ein dringt und die zweiten Abschnitte **12** nicht mit der Schmelze gefüllt werden (vgl. **Fig. 3C**). Der Druck beim Füllen der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** muss demnach derart eingestellt sein, dass der Grenzdruck zum Füllen der dritten Abschnitte **16** bereits überschritten ist, der Grenzdruck zum Füllen der zweiten Abschnitte **12** jedoch noch nicht erreicht ist.

**[0070]** Ein Vorteil des Substrats **300** gegenüber dem Substrat **200** ist, dass das elektrisch leitende erste Material **9** nach dem Einbringen in die Kanäle **2** erneut aufgeschmolzen werden kann. Bei einer Unterteilung der Kanäle **2** in nur zwei Abschnitte wie bei dem Substrat **200** würde ein Aufschmelzen des elektrisch leitenden ersten Materials **9** in den Kanälen **2** dazu führen, dass die Schmelze aus den Kanälen **2** herausfließt. Aufgrund der Verengungen der Kanäle **2** in dem Substrat **300** zu beiden Hauptoberflächen **3** und **4** hin, kann das elektrisch leitende erste Material **9** bei einem erneuten Aufschmelzen aus den Kanälen **2** nicht austreten. Ein derartiges Aufschmelzen des elektrisch leitenden ersten Materials **9** kann bei verschiedenen Prozessschritten auftreten, bei denen eine Temperatur oberhalb der Schmelztemperatur des elektrisch leitenden ersten Materials **9** herrscht.

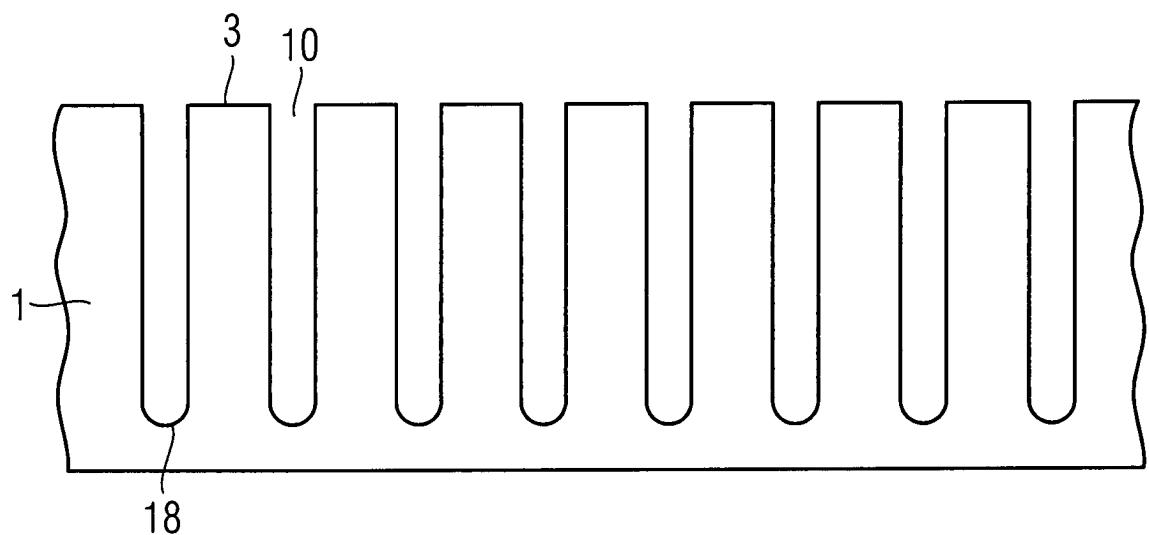

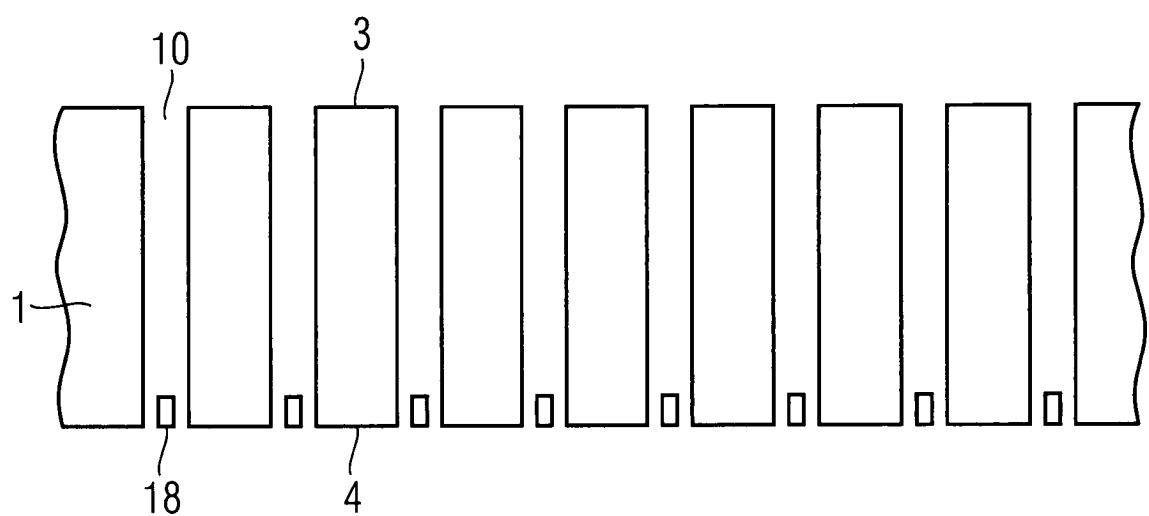

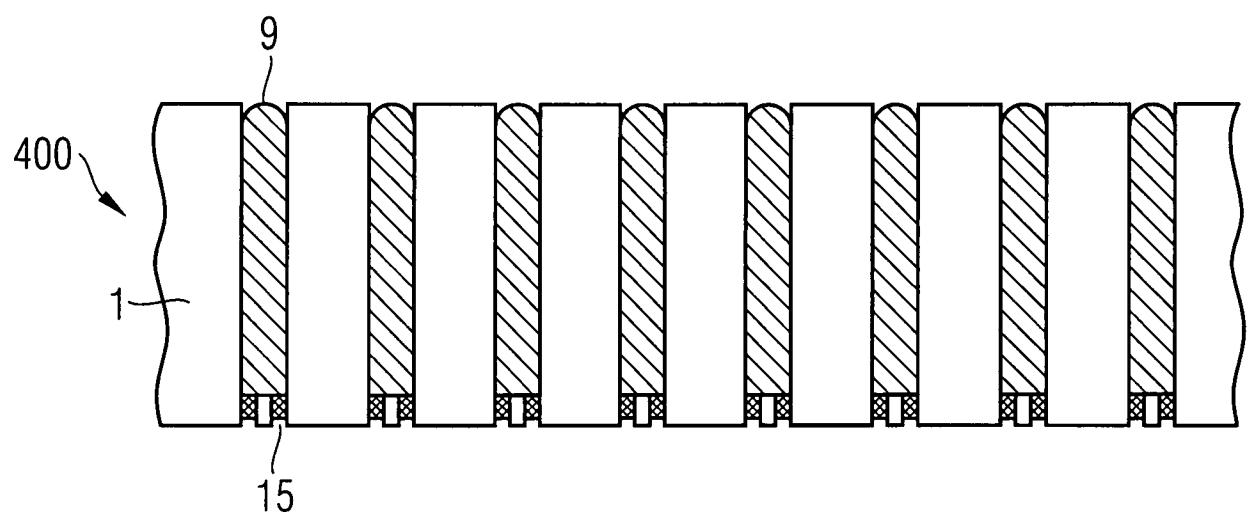

[0071] In [Fig. 4D](#) ist schematisch das Substrat **400** als weiteres Ausführungsbeispiel dargestellt. In den [Fig. 4A](#) bis [Fig. 4D](#) sind Schritte zur Herstellung des Substrats **400** gezeigt. Im Unterschied zu den Substraten **200** und **300** werden bei dem Substrat **400** keine Sacklöcher **10** mit variierten Querschnitten in das Halbleitersubstrat **1** eingebracht. Vielmehr weisen die Sacklöcher **10** eine konstante Querschnittsfläche auf. Lediglich die Spitze **18** der Sacklöcher **10** ist verjüngt. Die Verjüngung der Spitze **18** kann herstellungsbedingt sein, beispielsweise ergibt sich eine derartige Verjüngung bei einem Ätzprozess oder durch Bohren, und kann für die Herstellung des Substrats **400** ausgenutzt werden. Nach der Erzeugung der Sacklöcher **10** werden diese durch eine Materialabtragung von der zweiten Hauptoberfläche **4** hergeöffnet. Wie in [Fig. 4B](#) gezeigt ist, wird dabei nur so viel Halbleitermaterial auf der zweiten Hauptoberfläche **4** abgetragen, bis die Spitzen **18** der Sacklöcher **10** erreicht sind. Da die Spitzen **18** verjüngt sind, ergibt sich im Bereich der Spitzen **18** ein Abschnitt mit einer kleineren Querschnittsfläche. Diese kleinere Querschnittsfläche kann genauso wie bei dem Substrat **200** als druckabhängige Barriere während der Füllung der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** genutzt werden (vgl. [Fig. 4C](#)).

[0072] Das Öffnen der Sacklöcher **10** von der zweiten Hauptoberfläche **4** aus kann beispielsweise mittels eines CVD-Prozesses und evtl. einer vorherigen lithografischen Strukturierung durchgeführt werden. Alternativ kann auch das Halbleitermaterial auf der zweiten Hauptoberfläche **4** mechanisch soweit abgeschliffen werden, bis die Spitzen **18** der Sacklöcher **10** erreicht sind.

[0073] Da es bei der Herstellung des Substrats **400** nicht erforderlich ist, die Querschnittsfläche der Sacklöcher **10** zu variieren, können neben dem elektrochemischen Ätzen auch Techniken zur Erstellung der Sacklöcher **10** angewendet werden, die außer der Verjüngung in der Spitze **18** des Sacklochs **10** keine Querschnittsflächenvariation gestatten würden. Neben Ätztechniken zählen hierzu beispielsweise mechanisches Bohren, Sandstrahlen, Ultraschall-Bohren und Laser-Bohren.

[0074] Wie in [Fig. 4D](#) gezeigt ist, können die freigelegten Spitzen **18** der Sacklöcher **10** genauso wie bei dem Substrat **200** mit dem elektrisch leitenden zweiten Material **15** gefüllt werden.

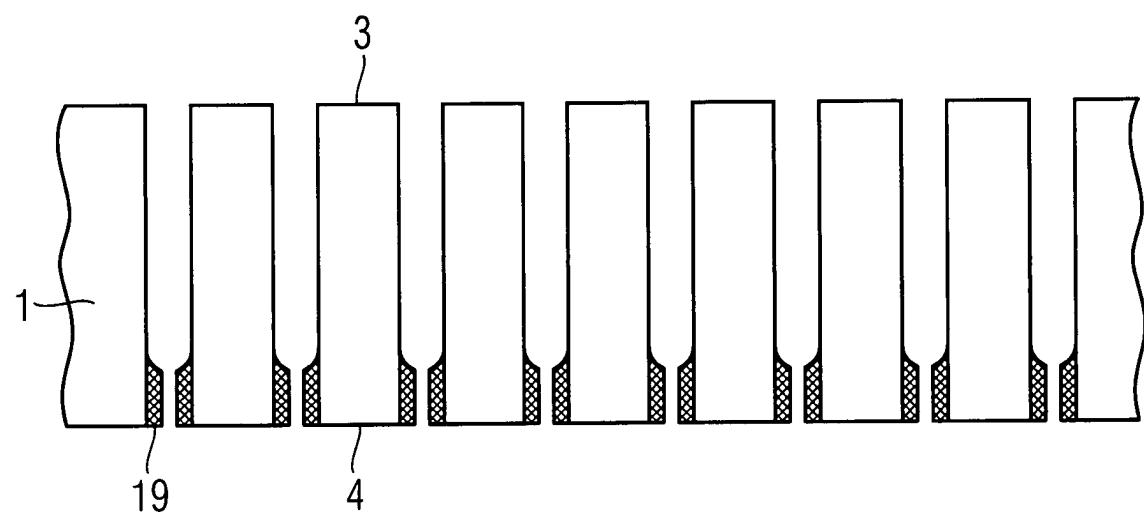

[0075] In [Fig. 5D](#) ist schematisch das Substrat **500** als weiteres Ausführungsbeispiel dargestellt. In den [Fig. 5A](#) bis [Fig. 5D](#) sind Schritte zur Herstellung des Substrats **500** gezeigt. Wie in [Fig. 5A](#) gezeigt ist, werden zur Herstellung des Substrats **500** gleichförmige Kanäle **2** ohne Variation ihrer Querschnittsfläche in das Halbleitersubstrat **1** eingebracht. Die Kanäle können beispielsweise durch Bohren, Stanzen,

Ätzen oder andere Techniken erzeugt werden. Anschließend wird auf der zweiten Hauptoberfläche **4** des Halbleitersubstrats **1** ein isolierendes Material **19**, z. B.  $\text{SiO}_2$  oder  $\text{Si}_3\text{N}_4$ , abgeschieden. Dies kann beispielsweise mittels Sputtern oder einem CVD-Prozess geschehen. Während der Abscheidung des isolierenden Materials **19** lagert sich das isolierende Material **19** nicht nur auf der zweiten Hauptoberfläche **4** sondern auch im Randbereich zu der zweiten Hauptoberfläche **4** an den Oberflächen der Kanäle **2** ab und erzeugt in dem Randbereich zu der zweiten Hauptoberfläche **4** eine Verengung der Kanäle **2**. Diese Verengung kann, wie in den [Fig. 5C](#) und [Fig. 5D](#) gezeigt ist, wieder als druckabhängige Barriere bei der Füllung der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** genutzt werden. Als Ausgangssubstrat **1** kann in dem vorliegenden Fall z. B. auch Mikrokanalglas oder partiell oxidiertes Silizium verwendet werden.

[0076] In den [Fig. 6A](#), [Fig. 6B](#) und [Fig. 6C](#) sind schematisch die Substrate **600A**, **600B** und **600C** als weitere Ausführungsbeispiele dargestellt. Die Substrate **600A** bis **600C** bestehen jeweils aus Stäben aus Halbleitersubstratschichten **20** bis **23**. In den einzelnen Halbleitersubstratschichten **20** bis **23** sind jeweils Kanäle, beispielsweise durch Ätzen, Bohren, Stanzen oder andere Techniken, erzeugt worden und die Halbleitersubstratschichten **20** bis **23** sind derart übereinander gestapelt worden, dass deren jeweilige Kanäle übereinander liegen und Kanäle erzeugen, die sich von der ersten Hauptoberfläche **3** durch den Stapel zu der zweiten Hauptoberfläche **4** hin erstrecken.

[0077] Dabei kann vorgesehen sein, dass die Kanäle in den Halbleitersubstratschichten **20** bis **23** unterschiedliche Querschnittsflächen aufweisen. Z. B. ist bei dem Substrat **600A** die Querschnittsfläche der Kanäle in der Halbleitersubstratschicht **23** kleiner als in den übrigen Halbleitersubstratschichten **20** bis **22**. Dadurch wird zu der Hauptoberfläche **4** hin eine Verengung der sich durch den Stapel erstreckenden Kanäle **2** erzeugt, die als druckabhängige Barriere beim Befüllen der Kanäle **2** mit dem elektrisch leitenden ersten Material **9** verwendet werden kann.

[0078] Ferner kann wie bei dem Substrat **600B** eine Halbleitersubstratschicht **22** unterschiedliche Querschnittsflächen aufweisen. In dem in [Fig. 6B](#) gezeigten Beispiel bewirkt dies, dass der mittlere Kanal **2** nur bis zur Halbleitersubstratschicht **21** mit dem elektrisch leitenden ersten Material **9** gefüllt wird.

[0079] Des Weiteren kann wie bei dem Substrat **600C** vorgesehen sein, dass die Verengung der Kanäle **2** entweder auf der Seite der ersten Hauptoberfläche **3** (mittlerer und rechter Kanal in [Fig. 6C](#)) oder auf der Seite der zweiten Hauptoberfläche **4** (linker Kanal in [Fig. 6C](#)) angeordnet ist. Dementsprechend

werden die Kanäle **2** entweder von der ersten Hauptoberfläche **3** (linker Kanal in [Fig. 6C](#)) oder von der zweiten Hauptoberfläche **4** (mittlerer und rechter Kanal in [Fig. 6C](#)) aus mit dem elektrisch leitenden ersten Material **9** gefüllt.

**[0080]** Die Befestigung der Halbleitersubstratschichten **20** bis **23** untereinander kann beispielsweise durch Kleben, Diffusionslöten oder andere Techniken erfolgen.

**[0081]** In den [Fig. 6A](#) bis [Fig. 6C](#) ist die Füllung der verengten Bereiche der Kanäle **2** mit dem elektrisch leitenden zweiten Material **15** nicht dargestellt. Dies kann in entsprechender Weise wie bei dem Substrat **200** geschehen.

**[0082]** [Fig. 7](#) zeigt schematisch ein Halbleitermodul **700** mit einem Substrat **701**, das eine Durchführung **702** von der ersten Hauptoberfläche **703** zur zweiten Hauptoberfläche **704** aufweist. Die Durchführung **702** ist durch eines der oben beschriebenen Verfahren hergestellt worden, z. B. wie bei dem in den [Fig. 2A](#) bis [Fig. 2E](#) gezeigten Substrat **200** (die Verengung des Kanals und der Durchführung **702** ist in [Fig. 7](#) nicht dargestellt). Das Substrat **701** ist z. B. ein Silizium-Chip und die auf die erste und zweite Hauptoberflächen **703**, **704** des Substrats **701** aufgebrachten Isolationsschichten **705** ein Oxid.

**[0083]** Auf die Oxidschicht **705** ist die Rückseite eines integrierten Halbleiterbauelements **706**, das auf der Vorderseite eine integrierte Schaltung **707** aufweist, mit einem Kleber **708** aufgeklebt worden. Das Halbleiterbauelement **706** ist durch einen Bonddraht **709**, der von einer Bondkontaktstelle **710** des Halbleiterbauelements **706** zu einer Bondkontaktstelle **711** des Substrats **701** führt, mit dem Substrat **701** elektrisch verbunden. Die Bondkontaktstelle **711** des Substrats **701** ist im vorliegenden Fall direkt auf die Durchführung **702** des Substrats **701** aufgebracht worden. Durch diese ist der Bonddraht **709** direkt mit einem Außenkontakt **712**, im vorliegenden Fall einer Lotkugel **712**, verbunden.

**[0084]** Die Kontaktierung der Bondkontaktstelle **711** mit der Durchführung **702** geschieht auf eine dem Fachmann wohlbekannte Weise: zunächst muss die Oxidschicht **705** auf der ersten Hauptoberfläche **703** an der Stelle der Durchführung **702** geöffnet werden. Dies kann durch eine Ätzung selektiv zu einer photolithographisch erzeugten Maske (nicht gezeigt) geschehen. Anschließend wird eine Metallschicht, z. B. Aluminium, auf die Oxidschicht **705** aufgebracht und photolithographisch so strukturiert, dass ein für eine Drahtverbindung **711** ausreichend großes Schichtelement **711** zurückbleibt.

**[0085]** Die Kontaktierung der Lotkugel **712** geschieht analog in einer dem Fachmann bekannten

Weise: zunächst muss die Oxidschicht **705** auf der zweiten Hauptoberfläche **704** an der Stelle der Durchführung **702** geöffnet werden. Dies kann durch eine Ätzung selektiv zu einer photolithographisch erzeugten Maske (nicht gezeigt) geschehen. Anschließend wird die zweite Hauptoberfläche **704** mit einer Kupferlotschmelze in Kontakt gebracht, sodass das Kupferlot die Oberfläche der Durchführung **702** benetzt. Nach der Abkühlung bleibt eine kugelförmige Lotkugel **712** zurück.

**[0086]** [Fig. 8](#) zeigt schematisch ein weiteres Halbleitermodul **800** mit einem Substrat **701**, das zwei Durchführungen **702** von der ersten Hauptoberfläche **703** zur zweiten Hauptoberfläche **704** aufweist. Das Halbleitermodul **800** ist wie das von [Fig. 7](#) aufgebaut. Jedoch hat das vorliegende Halbleitermodul **800** im Unterschied zur [Fig. 7](#) zwei integrierte Bauelemente **706A**, **706B**, die mit ihren Vorderseiten, d. h. mit der Seite mit den integrierten Schaltungen **707A**, **707B**, auf das Substrat **701** aufgebracht worden sind. Die elektrische Verbindung mit dem Substrat **701** erfolgt in diesem Fall nicht über Bonddrähte sondern über Lotkugelkontakte **713**, welche die Bondkontaktstellen der integrierten Bauelemente **706A**, **706B** mit auf dem Substrat **701** aufgebrachten Leiterbahnen **714** verbinden. Dieses Bond-Verfahren ist auch unter dem Begriff „Flip-Chip-Ronden“ bekannt und soll hier nicht weiter erläutert werden.

**[0087]** Wie man [Fig. 8](#) entnehmen kann, verlaufen einige Leiterbahnen **714** direkt über Durchführungen **702** und sind mit diesen elektrisch leitend verbunden. Auf diese Weise ist es möglich, Bondkontaktstellen der integrierten Bauelemente **706A**, **706B** über die Durchführungen **702** direkt zu einem der Außenkontakte **712** zu führen. Dies erspart lange Leiterbahnen und verbessert die Signalübertragung, insbesondere bei hohen Frequenzen.

**[0088]** Weiterhin kann man [Fig. 8](#) entnehmen, dass einige Leiterbahnen **714** so verlaufen, dass sie die Bondkontaktstellen des einen integrierten Bauelements **706A** mit denen des anderen integrierten Bauelements **706B** verbinden. Auf diese Weise können verschiedene integrierte Schaltungen **706A**, **706B** miteinander verbunden werden, ohne dass diese weitere Außenkontakte **712** erfordern. Damit lassen sich integrierte Schaltungen noch dichter packen.

**[0089]** Es sei darauf hingewiesen, dass die Ausführungsformen von [Fig. 7](#) und [Fig. 8](#) Siliziumscheiben oder Silizium-Chips als Substrat **701** haben. Dies hat den Vorteil, dass der Temperaturausdehnungskoeffizient (CTE) des Substrats **702** der gleiche ist wie der der meist ebenfalls auf Siliziumbasis hergestellten integrierten Schaltungen. Dies hilft, mechanische Spannungen zwischen dem Substrat **702** und dem integrierten Bauelement **706** zu reduzieren. Weiterhin hat Silizium, im Vergleich zu z. B. einer Keramik,

eine gute Temperaturleitfähigkeit, um die durch die integrierten Schaltungen erzeugte Wärme effektiv abzuführen. Weiterhin lässt sich das Ätzen von Sacklöchern auf elektrochemischen Wege mit Silizium besonders effektiv durchführen.

[0090] [Fig. 9](#) zeigt schematisch ein weiteres Halbleitermodul 900 mit einem Substrat 701, das eine Durchführung 702 von der ersten Hauptoberfläche 703 zur zweiten Hauptoberfläche 704 aufweist.

[0091] Das Halbleitermodul 900 ist wie das von [Fig. 7](#) aufgebaut. Jedoch ist im Unterschied zur [Fig. 7](#) die integrierte Schaltung 707 in das Substrat 701 selbst integriert. In [Fig. 9](#) ist beispielsweise ein Transistor 715 gezeigt. Source S und Drain D des Transistors 715 sind durch Dotierungen des monokristallinen Siliziumsubstrats 701 erzeugt, während das Gate G durch eine thermische Oxidation, die z. B. bei der Herstellung der Isolationsschicht 705 entstanden ist, erzeugt wird. [Fig. 9](#) zeigt weiterhin Leiterbahnen 714, die die Source S mit der Durchführung 702 verbinden und/oder jeweils das Gate G und die Drain D kontaktieren. Die Durchführung 702 ermöglicht auf diese Weise kurze Anbindungen der aktiven und passiven Bauelemente der integrierten Schaltungen (Widerstände, Transistoren, Dioden, Spulen, Kondensatoren etc.) an die externen Anschlüsse. Dies erspart lange Leitungsbahnen und somit die Notwendigkeit für mehrfache Leiterbahnebenen.

## Patentansprüche

### 1. Ein Verfahren umfassend:

- ein Halbleitersubstrat (1) mit einer ersten Hauptoberfläche (3), einer zweiten, der ersten Hauptoberfläche (3) gegenüberliegenden, Hauptoberfläche (4) und mindestens einem von der ersten Hauptoberfläche (3) zu der zweiten Hauptoberfläche (4) reichen den Kanal (2), der in einem ersten Abschnitt (11) eine erste Querschnittsfläche (6) und in einem zweiten Abschnitt (12) eine zweite Querschnittsfläche (8) aufweist, wobei die erste Querschnittsfläche (6) größer als die zweite Querschnittsfläche (8) ist, wird bereitgestellt; und

- ein elektrisch leitendes erstes Material (9) wird unter Druck im geschmolzenen Zustand in den ersten Abschnitt (11) des mindestens einen Kanals (2) eingefüllt.

2. Das Verfahren nach Anspruch 1, wobei der mindestens eine Kanal (2) mittels elektrochemischen Ätzens des Halbleitersubstrats (1) erzeugt wird.

3. Das Verfahren nach Anspruch 2, wobei die erste Querschnittsfläche (6) und die zweite Querschnittsfläche (8) durch Ätzparameter erzeugt werden, die von Ätzparametern des elektrochemischen Ätzens unterschiedlich sind.

4. Das Verfahren nach Anspruch 3, wobei die erste Querschnittsfläche (6) und die zweite Querschnittsfläche (8) durch unterschiedliche Ätzströme erzeugt werden, die während des elektrochemischen Ätzens durch das Halbleitersubstrat (2) fließen.

5. Das Verfahren nach Anspruch 1, wobei der mindestens eine Kanal (2) erzeugt wird, indem ein Sackloch (10) mit einem sich verengenden Endbereich (18) auf der ersten Hauptoberfläche (3) des Halbleitersubstrats (1) erzeugt wird und auf der zweiten Hauptoberfläche (4) des Halbleitersubstrats (1) Halbleitersubstratmaterial bis zu dem sich verengenden Endbereich (12) des Sacklochs (10) abgetragen wird.

6. Das Verfahren nach einem der Ansprüche 1 bis 5, wobei der mindestens eine Kanal eine Oberfläche aufweist und wobei an der ersten und zweiten Hauptoberfläche des Halbleitersubstrats (1) und der Oberfläche des mindestens einen Kanals (2) eine erste Isolationsschicht (13) erzeugt wird.

7. Das Verfahren nach Anspruch 6, wobei die erste Isolationsschicht (13) durch Erwärmung erzeugt wird.

8. Das Verfahren nach Anspruch 6, wobei die erste Isolationsschicht (13) durch Abscheidung eines isolierenden ersten Materials erzeugt wird.

9. Das Verfahren nach Anspruch 1, wobei der mindestens eine Kanal (2) erzeugt wird, indem ein Durchgangsloch mit einer Oberfläche in dem Halbleitersubstrat (1) erzeugt wird und auf der Oberfläche des Durchgangslochs in einem an einer der Hauptoberflächen (4) des Halbleitersubstrats (1) angrenzenden Bereich ein isolierendes zweites Material (19) abgeschieden wird.

10. Das Verfahren nach einem der Ansprüche 1 bis 9, wobei das elektrisch leitende erste Material (9) mittels Unterdruck und/oder Überdruck eingefüllt wird.

11. Das Verfahren nach einem der Ansprüche 1 bis 10, wobei nach dem Einfüllen des elektrisch leitenden ersten Materials (9) ein elektrisch leitendes zweites Material (15) in den mindestens einen Kanal (2) eingefüllt wird.

12. Das Verfahren nach einem der Ansprüche 1 bis 11, wobei der mindestens eine Kanal (2) in einem dritten Abschnitt (16) eine dritte Querschnittsfläche (17) aufweist.

13. Das Verfahren nach Anspruch 12, wobei nach einem Erstarren des elektrisch leitenden ersten Materials (9) das elektrisch leitende erste Material (9) in dem mindestens einen Kanal (2) erneut geschmol-

zen wird.

14. Ein Substrat (**100–600**) umfassend:

- ein Halbleitersubstrat (**1**) mit einer ersten Hauptoberfläche (**3**), einer zweiten, der ersten Hauptoberfläche (**3**) gegenüberliegenden, Hauptoberfläche (**4**) und mindestens einem von der ersten Hauptoberfläche (**3**) zu der zweiten Hauptoberfläche (**4**) reichen den Kanal (**2**), wobei der mindestens eine Kanal (**2**) in einem ersten Abschnitt (**11**) eine erste Querschnittsfläche (**6**) und in einem zweiten Abschnitt (**12**) eine zweite Querschnittsfläche (**8**) aufweist, wobei die erste Querschnittsfläche (**6**) größer als die zweite Querschnittsfläche (**8**) ist und wobei

- der Kanal (**2**) in dem ersten Abschnitt (**11**) mit einem aus einer Schmelze eingebrachten elektrisch leitenden ersten Material (**9**) gefüllt ist und

- der Kanal (**2**) in dem zweiten Abschnitt (**12**) mit einem elektrisch leitenden zweiten Material (**15**) gefüllt ist.

15. Das Substrat (**100–600**) nach Anspruch 14, wobei das elektrisch leitende erste Material (**9**) einen höheren Schmelzpunkt als das elektrisch leitende zweite Material (**15**) hat.

16. Das Substrat (**300**) nach einem der Ansprüche 14 oder 15, wobei der mindestens eine Kanal (**2**) in einem dritten Abschnitt (**16**) eine dritte Querschnittsfläche (**17**) aufweist.

17. Das Substrat (**300**) nach Anspruch 16, wobei die dritte Querschnittsfläche (**17**) kleiner als die erste Querschnittsfläche (**6**) und größer als die zweite Querschnittsfläche (**8**) ist und in dem dritten Abschnitt (**16**) das elektrisch leitende erste Material (**9**) in den mindestens einen Kanal (**2**) eingebracht ist.

18. Das Substrat (**100–600**) nach einem der Ansprüche 14 bis 17, wobei der mindestens eine Kanal eine Oberfläche aufweist und wobei eine erste Isolationsschicht (**13**) die erste und zweite Hauptoberfläche des Halbleitersubstrats (**1**) und die Oberfläche des mindestens einen Kanals (**2**) bedeckt.

19. Das Substrat (**100–400, 600**) nach einem der Ansprüche 14 bis 18, wobei der mindestens eine Kanal (**2**) in dem zweiten Abschnitt (**12**) durch das Material des Halbleitersubstrats (**1**) zu der zweiten Querschnittsfläche (**8**) verengt ist.

20. Das Substrat (**500**) nach einem der Ansprüche 14 bis 18, wobei der mindestens eine Kanal (**2**) in dem zweiten Abschnitt (**12**) mittels einer zweiten Isolationsschicht (**19**) zu der zweiten Querschnittsfläche (**8**) verengt ist.

21. Das Substrat (**600**) nach einem der Ansprüche 14 bis 18, wobei das Halbleitersubstrat (**1**) eine erste Halbleitersubstratschicht (**20**) und eine über der

ersten Halbleitersubstratschicht (**20**) angeordnete zweite Halbleitersubstratschicht (**21**) umfasst.

22. Das Substrat (**600**) nach Anspruch 21, wobei sich der mindestens eine Kanal (**2**) durch die erste und die zweite Halbleitersubstratschicht (**20, 21**) erstreckt und der mindestens eine Kanal (**2**) in der ersten Halbleitersubstratschicht (**20**) die erste Querschnittsfläche (**6**) und in der zweiten Halbleitersubstratschicht (**21**) die zweite Querschnittsfläche (**8**) aufweist.

23. Das Substrat (**100–600**) nach einem der Ansprüche 14 bis 22, wobei der Quotient aus der Kanallänge des mindestens einen Kanals (**2**) und dem in dem ersten Abschnitt (**11**) vorliegenden Kanaldurchmesser größer als 2 ist.

24. Das Substrat (**100–600**) nach einem der Ansprüche 14 bis 23, wobei der Quotient aus der Kanallänge des mindestens einen Kanals (**2**) und dem in dem ersten Abschnitt (**11**) vorliegenden Kanaldurchmesser kleiner als 1000 ist.

25. Ein Halbleitermodul (**700–900**) umfassend:

- ein Substrat (**100–600**) gemäß einem der Ansprüche 14 bis 24; und

- eine auf das Substrat (**100–600**) aufgebrachte integrierte Schaltung (**707**).

26. Das Halbleitermodul (**900**) nach Anspruch 25, wobei die integrierte Schaltung (**707**) in eine Oberfläche des Substrats (**100–600**) integriert ist.

27. Das Halbleitermodul (**700, 800**) nach Anspruch 25, wobei die integrierte Schaltung (**707**) in ein Bauelement (**706**) integriert ist und das Bauelement (**706**) mit dem Substrat (**100–600**) durch mindestens einen Verbindungsdräht (**709**) und/oder mindestens einen Lotkontakt (**713**) verbunden ist.

Es folgen 12 Blatt Zeichnungen

Anhängende Zeichnungen

FIG 1A

FIG 1B

FIG 1C

FIG 2A

FIG 2B

FIG 2C

FIG 2D

FIG 2E

FIG 3A

FIG 3B

FIG 3C

FIG 3D

FIG 4A

FIG 4B

FIG 4C

FIG 4D

FIG 5A

FIG 5B

FIG 5C

FIG 5D

FIG 6A

FIG 6B

FIG 6C

FIG 7

FIG 8

FIG 9