(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 695 32 863 T2 2005.03.31

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 799 530 B1

(21) Deutsches Aktenzeichen: 695 32 863.8

(86) PCT-Aktenzeichen: PCT/US95/16363

(96) Europäisches Aktenzeichen: 95 944 116.3

(87) PCT-Veröffentlichungs-Nr.: WO 96/020540

(86) PCT-Anmeldetag: 19.12.1995

(87) Veröffentlichungstag

der PCT-Anmeldung: 04.07.1996

(97) Erstveröffentlichung durch das EPA: 08.10.1997

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 07.04.2004

(47) Veröffentlichungstag im Patentblatt: 31.03.2005

(51) Int Cl.<sup>7</sup>: H04B 1/40

H04J 15/00, H04L 25/49, H04L 27/14

(30) Unionspriorität:

373122 23.12.1994 US

(84) Benannte Vertragsstaaten:

AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LI, LU,

MC, NL, PT, SE

(73) Patentinhaber:

Qualcomm, Inc., San Diego, Calif., US

(72) Erfinder:

BLACK, J., Peter, St. Lucia, AU; WILSON, B.,

Nathaniel, San Diego, US

(74) Vertreter:

WAGNER & GEYER Partnerschaft Patent- und

Rechtsanwälte, 80538 München

(54) Bezeichnung: DIGITAL-FM-KOMMUNIKATIONSSYSTEM MIT DUALBETRIEBSART

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### HINTERGRUND DER ERFINDUNG

#### I. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich am Allgemeinen auf frequenzmodulierte (FM) Kommunikationssysteme. Insbesondere bezieht sich die vorliegende Erfindung auf ein neues Dualbetriebsartkommunikationssystem, das wahlweise in entweder FM oder Codemultiplexvielfachzugriffs-(code division multiple access (CDMA))-Modi bzw. -betriebsarten betrieben werden kann.

#### II. Beschreibung des Standes der Technik

**[0002]** Die Demodulation von empfangenen FM-Kommunikationssignalen wird routinemäßig mittels analoger Signalverarbeitungstechniken ausgeführt. Jedoch wurden in letzter Zeit Verfahren entwickelt, die es erlauben, analoge Kommunikationssignale mittels digitaler Signalverarbeitungstechniken zu verarbeiten. Verfahren des Phasenabtastens und Diskriminierung eines ankommenden Signals um Nachrichteninformation wieder herzustellen gehören zu diesen Techniken. Die Nachrichteninformation wird oft mittels z. B. Quadraturdetektionsprozessen wiedergewonnen.

**[0003]** Eine FM-Demodulationstechnik, die für die Digitalimplementierung geeignet ist, ist als „Direktumwandlung“ bzw. „Direktkonvertierung“ (direct conversion) bekannt. Mittels dieser Technik mischt ein Direktumwandlungs- oder „Null-ZF“-(zero-IF)-Empfänger das ankommende HF-Signal direkt herunter auf das Basisband. Der Vorteil der Direktumwandlung ist der, dass Kanalselektivitätsfilterung auf dem Basisband ausgeführt werden kann und somit auf bequeme Weise mittels integrierter Schaltkreistechnologie implementiert werden kann.

**[0004]** Ein Nachteil der Direktumwandlungsdemodulation sind ungewollte DC- bzw. Gleichstrom-Offsetspannungen, die an dem Ausgang des Mischers zusammen mit dem gewünschten Basisbandsignal auftreten können, wobei das Basisbandsignal ebenfalls Gleichstromspektralkomponenten beinhaltet kann. Die ungewollte Gleichstromoffsetspannung bzw. Gleichstromversatzspannung (DC offset voltage) röhrt von Gleichstrom-Offsets innerhalb der Mischerstufe her, so wie von HF-Lokaloszillatorverlust bzw. -leckage, die auf den Gleichstrom herunter gemischt wird. Die Wirkung solcher unerwünschten Gleichstrom-Offsets auf den FM-Demodulationsprozess kann z. B. als eine auf das ideal-demodulierte Signal angewendete Nicht-Linearität modelliert bzw. simuliert werden. Der Betrag der resultierenden Verzerrung, d. h. der „Offset-Fehler“, ist eine Funktion des Betrags des Gleichstrom-Offsets (DC offset) relativ zu der FM-Signalumhüllenden. Für typische Audioanwendungen setzt eine akzeptable Tonwiedergabe Offsetfehler von weniger als einigen wenigen Prozentpunkten voraus. Daher besteht ein Bedarf nach einem digitalen FM-Empfänger, der in der Lage ist das gewünschte Basisbandsignal von den ungewünschten Gleichstrom-Offsets zu extrahieren.

**[0005]** Direktumwandlungsdigitalempfänger tendieren ebenfalls dazu einen relativ engen dynamischen Bereich aufzuweisen. Um den dynamischen Bereich des empfangenen FM-Signals Rechnung zu tragen, muss eine zusätzliche Schaltung zur automatischen Verstärkungsfaktorsteuerung (automatic gain control (AGC)) vorgesehen werden. Typischerweise beinhaltet in Digitalempfängern der automatische Verstärkungssteuerungsprozess die Detektierung, Analog-zu-Digital-Umwandlung und Basisbandmessung der ankommenden Signalleistung. Der gemessene Wert wird mit einem gewünschten Referenzwert verglichen und ein Fehlerwert wird generiert. Der Fehlerwert wird über einen Schleifenfilter gefiltert und die gefilterte Digitalausgabe wird verwendet um den Verstärkungsfaktor des Verstärkers zu steuern, so dass die Signalstärke so angepasst wird, dass sie mit der gewünschten Signalleistung überein stimmt. Um eine digitale Demodulation mit einem optimalen Signal-zu-Rausch-Verhältnis zu bewirken, wird eine automatische Verstärkungs- bzw. Verstärkungsfaktorsteuerung verwendet um die Beträge der Basisbandwellenformen in der Nähe des vollständigen Bereichs der Basisband-Analog-zu-Digital-Wandler zu halten. Dies benötigt jedoch im Allgemeinen das Vorsehen eines Verstärkers mit automatischer Verstärkungssteuerung um den vollen dynamischen Bereich der empfangenen Signalleistung abzudecken.

**[0006]** In bestimmten Betriebsumgebungen kann ein Digitalempfänger ein Signal empfangen, das schnelle und große bzw. breite Variationen in der Signalleistung erfährt. Zum Beispiel ist es in Digitalempfängern, wie solchen, die in Codemultiplexvielfachzugriff-(code division multiple access (CDMA))-Mobilfunkzelltelefonen verwendet werden, nötig, die Leistung des empfangenen Signals für eine geeignete Verarbeitung des empfangenen Signals zu begrenzen. Ähnlich ist es bei Digitalempfängern, die CDMA-kompatibel und kompatibel zu herkömmlichen FM sind, d. h. Dualbetriebs-CDMA/FM-Empfänger, nötig, eine Leistungsbegrenzung von bei-

den, den Breitband-CDMA-Signalen und den engbandigen FM-Signalen, vorzusehen. Der Begrenzungsprozess wird durch die unterschiedlichen dynamischen Bereiche, die der empfangenen FM- und CDMA-Signalleistung zugeordnet sind, erschwert. Dies bedeutet, dass der Betrag der empfangenen FM-Signale über einen dynamischen Bereich von bis zu 110 dB in Zellsystemen bzw. zellularen Systemen (cellular systems) variieren kann, wobei existierende Leistungsstörungstechniken innerhalb vom CDMA-System typischerweise zu einem viel begrenzteren dynamischen Bereich führen, d. h. ungefähr 80 dB.

**[0007]** Das Vorsehen einer separaten AGC-Schaltung für jeden dieser Betriebsmodi der Dualbetriebsart-CDMA-FM-Empfänger erhöht die Hardwarekomplexität und die Kosten für solche Empfänger. Demgemäß wäre es wünschenswert eine AGC-Schaltung vorzusehen, die in der Lage ist hinsichtlich beiden Signalen zu operieren, nämlich auf engbandigen, mit einem weiten dynamischen Bereich versehenen FM-Signalen, sowie auf breitbandigen CDMA-Signalen, die einen begrenzteren dynamischen Bereich besitzen. Die WO-A-92 21195 beschreibt einen Dualbetriebsartsender mit einer Antenne, einer Betriebsartsteuerung, einem Quellcodierer, einem Synthesizer mit einstellbarer Frequenz, einem Chipcodegenerator, einem Spreizspektrummodulator, einem Engbandmodulator, einem Leistungsverstärker und einem anpassbaren Bandpassfilter. Weiterhin wird ein Dualbetriebsartempfänger vorgesehen mit einer Betriebsartsteuerung, einem Synthesizer mit einstellbarer Frequenz, einem Chipcodegenerator, einer Antenne und einem anpassbaren Bandpassfilter, einem Vorverstärker, einem Frequenzumwandler, einem ZF-Verstärker, einem Spreizspektrumentspreizer, einem Spreizspektrumdemodulator, einem Engbandmodulator und einem Quelldecodierer. Für den Sender und den Empfänger wählt die Betriebsartsteuerung eine Engbandmodulation oder eine Spreizspektrummodulation. Der Synthesizer mit einstellbarer Frequenz generiert ein Lokaloszillatorsignal für den Empfänger und ein Trägersignal für den Sender. Der Chipcodegenerator generiert ein Chipcodesignal für beide, den Sender und den Empfänger. Bei einer Engbandmodulationseinstellung der Betriebsartsteuerung haben der Sender und der Empfänger die anpassbaren Bandpassfilter auf eine Engbandbreite für Telefonkommunikationen angepasst. Bei einer Spreizspektrumeinstellung durch die Betriebsartsteuerung sind die anpassbaren Bandpassfilter und das System zum Senden und Empfangen einer weiten Bandbreite zum Durchlauf des Spreizspektrumsignals angepasst.

**[0008]** Innerhalb von Digital-FM-Empfängern wurde eine Anzahl von Techniken verwendet, um eine Digital-FM-Demodulation zu bewirken. Die im Allgemeinen verwendeten Techniken beinhalten ZF-Demodulation mittels Nulldurchgangszählungen (zero crossing counts) oder eine Basisbanddemodulation mittels Quadraturdetektierung (quadrature detection). Ein ausschließlich digitaler Ansatz zur Quadratur-FM-Demodulation ist in dem U.S. Patent Nr. 4,675,882, betitelt „FM Demodulator“, Motorola, Inc. zugewiesen, beschrieben. Das '882 Patent beschreibt eine Vorrichtung, die konstruiert ist um abgetastete Eingabevektoren zu verarbeiten, die ein Quadratur-FM-Signal zentriert im wesentlichen auf Nullfrequenz, aufweist. Die Quadratureingabevektoren werden skaliert, um innerhalb eines vorbestimmten Betragsbereiches zu liegen. Zusätzlich wird der Eingabevektor auf einen vorbestimmten Quadranten basiert auf einem groben (coarse) Phasenwert rotiert, wobei der Phasenwert durch einen Phasenakkumulator bzw. -akkumulierer erzeugt wird. Innerhalb des vordefinierten Quadranten wird ein feiner bzw. hoch aufgelöster Phasenwert basierend auf den rotierten Vektor bestimmt, wobei die hoch aufgelösten und groben Phasenwerte summiert werden und als zusammengesetzter Phasenwert ausgegeben werden. Aufeinander folgende zusammengesetzte Phasenabtastungen werden dann subtrahiert um eine demodulierte Nachrichtenabtastsequenz zu erzeugen.

**[0009]** Verschiedene Charakteristiken der Demodulationsvorrichtung des '882 Patents favorisieren in hohem Maße die Implementierung der Vorrichtung innerhalb digitaler Signalprozessoren statt der Verwendung einer hierfür zugeordneten digitalen Hardware. Zum Beispiel verlässt sich die '882 Vorrichtung auf einen Digitalreziprokerator um ein Inverses einer In-Phasenbasisbandsignalkomponente vor der Multiplikation mit einer Nicht-In-Phasenbasisbandkomponente zu erzeugen. In einem bevorzugten Ansatz nähert der Reziprokerator die Funktion  $F(x) = 1/x$  mittels einer Chebyshev'schen Polynomnäherung, die am einfachsten auf einem Digitalsignalprozessor ausgeführt wird. Leider ist der relativ hohe Leistungsverbrauch eines solchen Digitalsignalprozessors ein Nachteil im Vergleich zu hierfür zugeordneter Digitalhardware in verschiedenen Typen von tragbaren Kommunikationstransceivern wie z. B. persönlichen Kommunikationsvorrichtungen (personal communication devices).

**[0010]** Weiterhin wird davon ausgegangen, dass die Demodulationsvorrichtung in dem '882 Patent anfällig gegenüber Gleichstromoffsetfehlern (DC offset errors) ist, die von einer Leckage des Lokaloszillators, sowie von verschiedenen anderen Quellen von unerwünschtem Gleichstromdurchfluss herrühren. Dies bedeutet, dass die Vorrichtung des '882 Gleichstromsignalenergie innerhalb der Eingabewellenform direkt auf das Nullfrequenzbasisband abbildet, auf dem ebenso die gewünschten Quadraturbasisbandkomponenten vorliegen. Demgemäß kann beim Vorliegen einer signifikanten externen Gleichstromsignalenergie die resultierende Pha-

senwinkelschätzung korripiert bzw. fehlerbehaftet werden.

**[0011]** Eine Signalfilterung wird oft mittels Zwischenfrequenz-(ZF)-Filtern (intermediate frequency (IF) filters) ausgeführt werden um eine adäquate Außerbandsignalzurückweisung zu erlangen. Obwohl die verlangte Signalzurückweisungsfähigkeit durch die Verwendung von Keramik-ZF-Filtern erreicht werden kann, tendieren diese dazu relativ groß und teuer zu sein. Kleinere und weniger teure ZF-Filter sind im Allgemeinen nicht in der Lage, so realisiert zu werden, dass sie die gewünschten Signalzurückweisungscharakteristiken besitzen, und werden daher im Allgemeinen in FM-Zelltelefonempfängern nicht verwendet.

**[0012]** Wie es allgemein bekannt ist, haben Fortschritte bei der Technologie von integrierten Schaltkreisen (IC) es möglich gemacht, Aktivbasisbandfilter zu realisieren, die sehr klein und kostengünstig sind. Daraus folgt, dass es wünschenswert wäre, Aktiv-IC-Basisbandfilter zu verwenden um signifikante Außerbandsignalzurückweisung (out of band signal rejection) zu bewirken, wodurch es kleinen und kostengünstigen ZF-Filtern ermöglicht wird, verwendet zu werden um jegliche zusätzliche benötigte Signalzurückweisung vorzusehen. Es ist ebenfalls bekannt, dass die Zurückweisungsfähigkeit von Aktivfiltern eine Funktion des Filterverstärkungsfaktors ist, wobei Aktivbasisband-IC-Filter mit hohem Verstärkungsfaktor eine erhöhte Anfälligkeit gegenüber unerwünschten Gleichstrom-Bias-Offsets bzw. Gleichstrom-Vorspannungs-Versätzen (DC bias offsets) aufweisen. Diese erhöhte Anfälligkeit kann der erhöhten Verstärkung von Offsetquellen zugewiesen werden. Dies bedeutet, dass störende (spurious) Gleichstromsignalkomponenten durch die Aktivbasisband-IC-Filter verstärkt werden und sich als Rauschquelle in dem FM-Demodulator verhalten.

**[0013]** Demgemäß führt die Verwendung von Aktivbasisband-IC-Filtern zu der Notwendigkeit einen Mechanismus zur Unterdrückung von ungewünschten Gleichstrom-Offsets bzw. -versätzen vorzusehen. Leider beinhaltet die ZF-Verarbeitungskette von herkömmlichen Digitalempfängern typischerweise einen Lokaloszillator (L. O.) mit einer Frequenz, die so ausgewählt ist, dass die HF-Trägerfrequenz abwärts umgesetzt bzw. herabkonvertiert wird auf DC bzw. Gleichstrom, wodurch ein Zerstören der Amplituden- und Phaseninformation auf der Trägerfrequenz während des Prozesses der Gleichstrom-Offset-Unterdrückung resultiert. Dies stellt nicht ein Problem für die Digitaldemodulation von unterdrückten Trägersignalen dar, und zwar, wie z. B. solche Signale, die mittels Quadrature-Phase-Shift-Keying-(QPSK)-Techniken gesendet werden. In FM-Zelltelefonsystemen liegt jedoch signifikante Amplituden- und Phaseninformation oft auf der Trägerfrequenz vor, und die Performance würde negativ beeinflusst werden, wenn solche Information zerstört werden würde.

**[0014]** Im Standard-FM-Zelltelefonsystem wird die Sprachinformation typischerweise durch einen Hochpassfilter geführt um Signalenergie auf Frequenzen unterhalb von 300 Hz zu unterdrücken und zwar vor einer Anlegung an den FM-Modulator. Obwohl eine gewisse Sprachinformation in der FM-Wellenform auf Frequenz-Offsets bzw. -versätzen von weniger als 300 Hz vorliegen kann, sind solche Intermodulationsprodukte bzw. Erzeugnisse nicht-stationär. Demgemäß resultiert die Unterdrückung von Niedrigfrequenzintermodulationsprodukten nicht im Allgemeinen in dem Verlust von wahrnehmbarer Sprachinformation.

**[0015]** Es ist daher ein weiteres Ziel der vorliegenden Erfindung eine AGC-Vorrichtung vorzusehen, die innerhalb eines Dualbetriebsartempfängers eingebaut werden kann, wobei die Vorrichtung in der Lage ist, eine Basisbandfilterung ohne den Verlust von Trägerfrequenzinformation auszuführen.

## ZUSAMMENFASSUNG DER ERFINDUNG

**[0016]** Gemäß einem ersten Aspekt der vorliegenden Erfindung wird ein Dualbetriebsartsender gemäß Anspruch 1 vorgesehen und gemäß einem zweiten Aspekt wird ein Dualbetriebsartempfänger gemäß Anspruch 3 vorgesehen.

**[0017]** Die vorliegende Erfindung bezieht sich auf ein neues Dualbetriebsartdigalkommunikationssystem zum Kommunizieren eines Informationssignals während des Betriebes in einer frequenzmodulierten (FM) Betriebsart und einer Codemultiplexvielfachzugriffs-(CDMA)-Betriebsart. Das Digalkommunikationssystem beinhaltet einen Dualbetriebsartsender zum Senden des Informationssignals mittels eines FM-Kommunikationssignals während des Betriebes in der FM-Betriebsart, und zum Senden des Informationssignals mittels eines Spreizspektrum-QPSK-Signals während des Betriebes in der CDMA-Betriebsart.

**[0018]** Das Kommunikationssystem beinhaltet weiterhin einen Doppelbetriebsartempfänger zum Empfangen des FM-Kommunikationssignals, während des Betriebes in der FM-Betriebsart und zum Empfangen des Spreizspektrum-QPSK-Signals während des Betriebes in der CDMA-Betriebsart. Der Dualbetriebsartempfänger beinhaltet weiterhin einen Digitaldemodulator zum Wiedergewinnen des Informationssignals von dem

empfangenen FM-Signal während des Betriebes in der FM-Betriebsart und zum Wiedergewinnen des Informationssignals von dem empfangenen QPSK-Signal während des Betriebes in der CDMA-Betriebsart.

**[0019]** Bezuglich des Dualbetriebsartempfängers kann ein FM-Demodulator innerhalb des Digitaldemodulators beinhaltet sein, um das digitalisierte empfangene Basisband-FM-Kommunikationssignal, sogar bevorzugterweise um einen vordefinierten Basisbandfrequenzversatz von der Nullfrequenz zentriert in das wieder gewonnene Informationssignal zu konvertieren. Die Konvertierung wird so ausgeführt, dass jede digitale Abtastung bzw. Sample des empfangenen Basisbandsignals erste und zweite Abtastkomponenten in der Phasenquadratur beinhaltet. In einer bevorzugten Implementierung berechnet der FM-Demodulator anfänglich ein Verhältnis der ersten und zweiten Abtastkomponenten einer jeden Digitalabtastung des Eingabesignals. Ein phasendemoduliertes Signal wird berechnet durch Bestimmen des Arcustangens eines jeden Digitalabtastungsverhältnisses. Ein frequenzdemoduliertes Signal, das äquivalent ist zu dem demodulierten Informationsignal, wird durch Filtern der demodulierten Phasensequenz mittels eines digitalen Differenzberechners berechnet.

#### KURZE BESCHREIBUNG DER ZEICHUNGEN

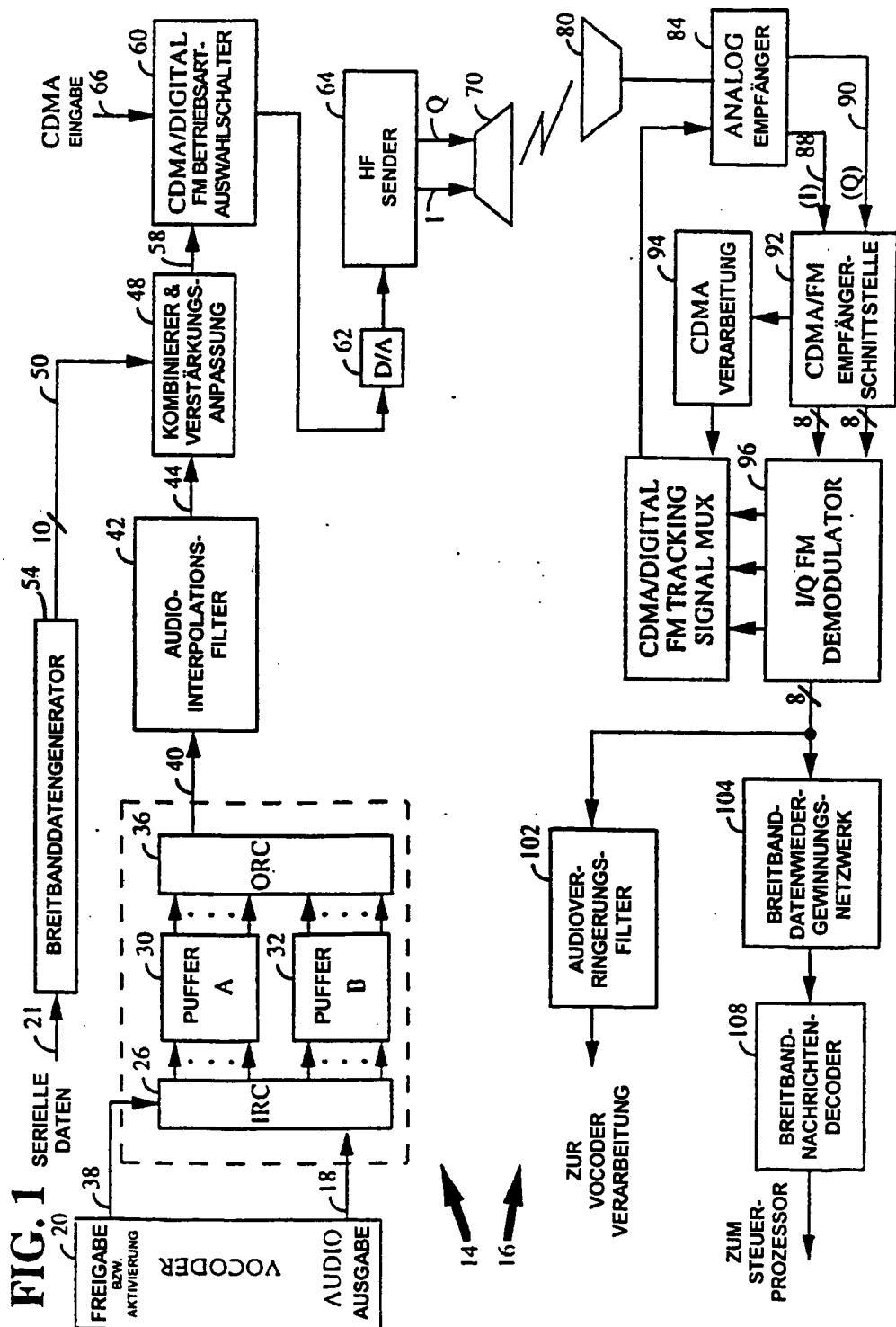

**[0020]** **Fig.** 1 sieht eine beschreibende Darstellung eines Dualbetriebsart-Digitalkommunikationssystems gemäß Ausführungsbeispielen der Erfindung vor.

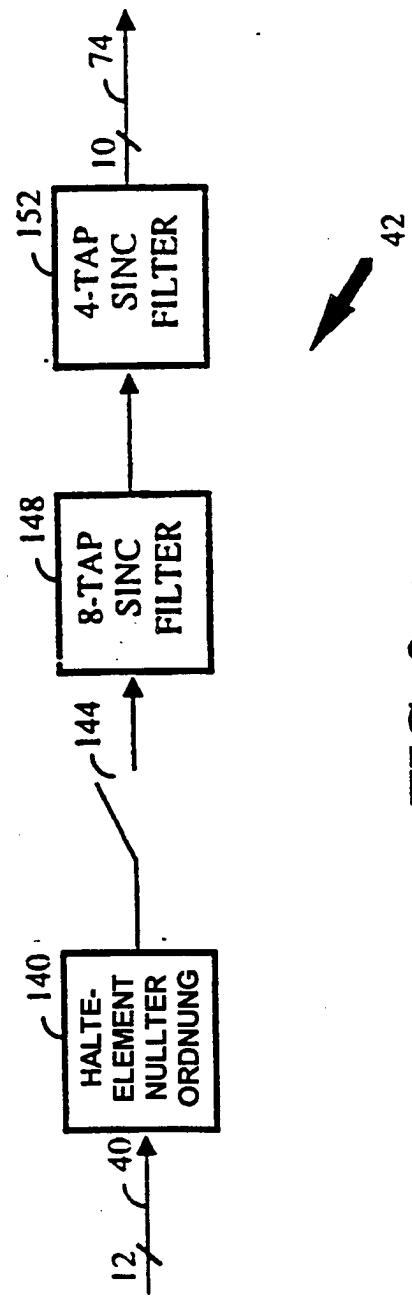

**[0021]** **Fig.** 2 zeigt eine Blockdiagrammdarstellung eines Audiointerpolationsfilters, der bzw. das innerhalb eines Dualbetriebsartsenders von Ausführungsbeispielen des Kommunikationssystems enthalten ist.

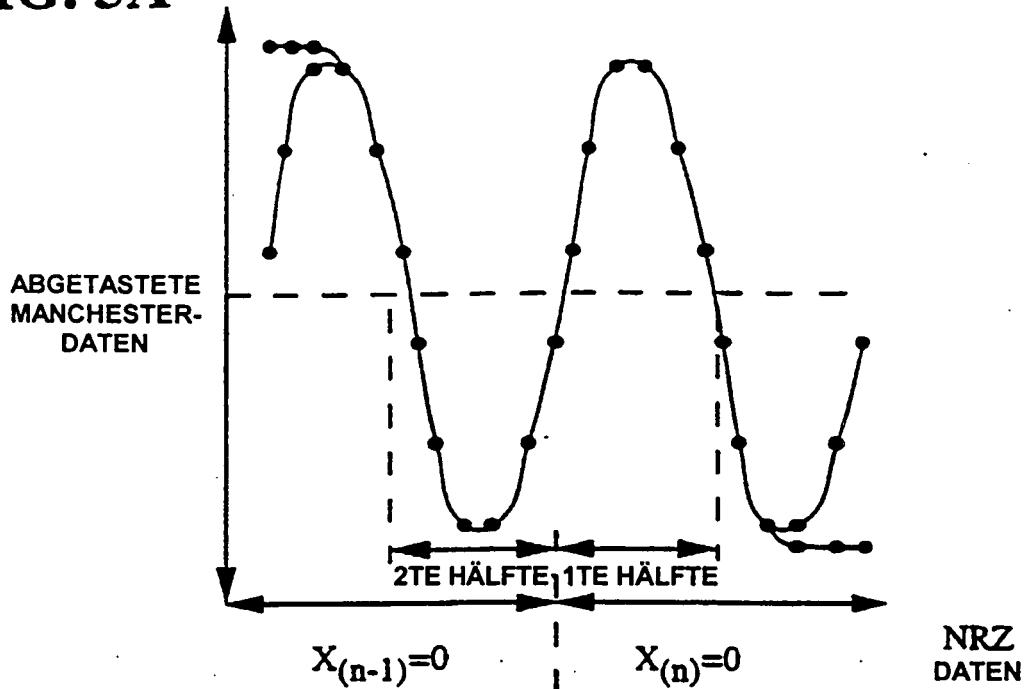

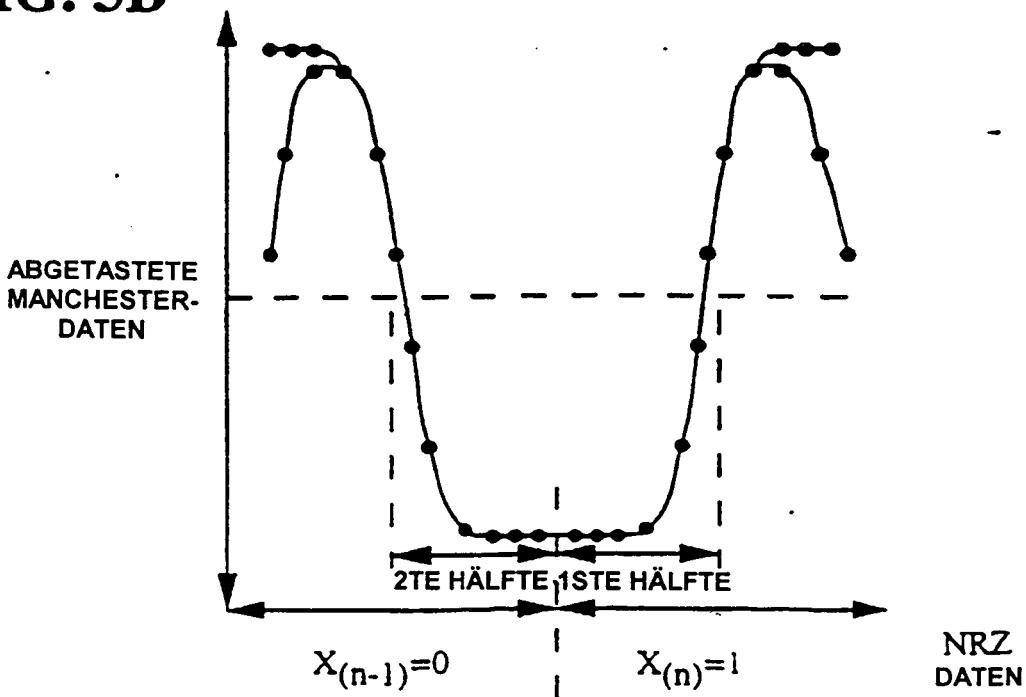

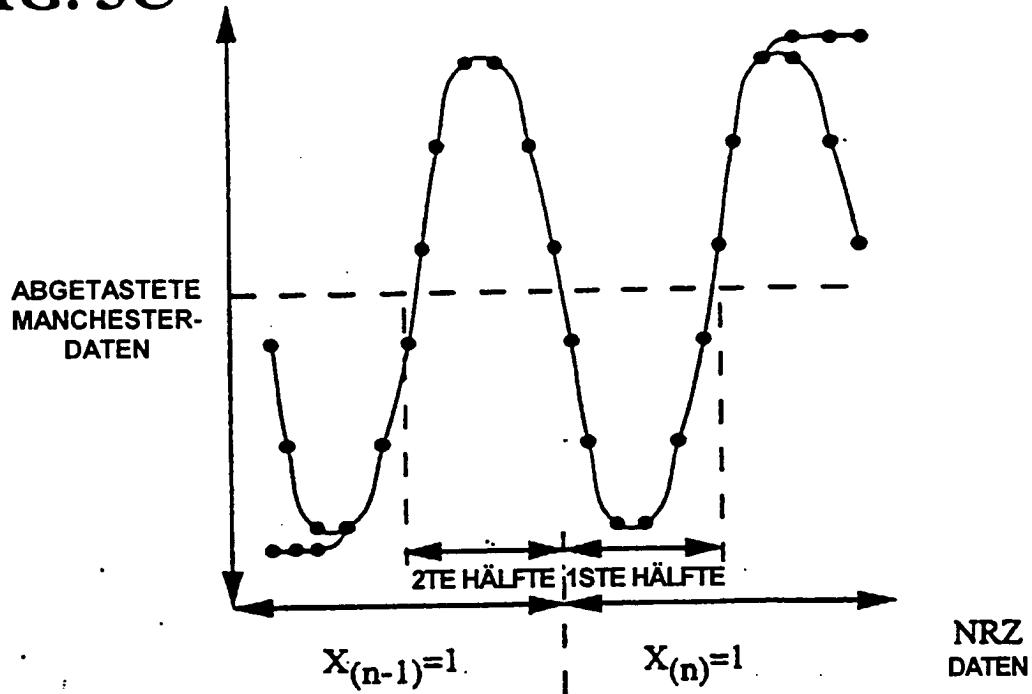

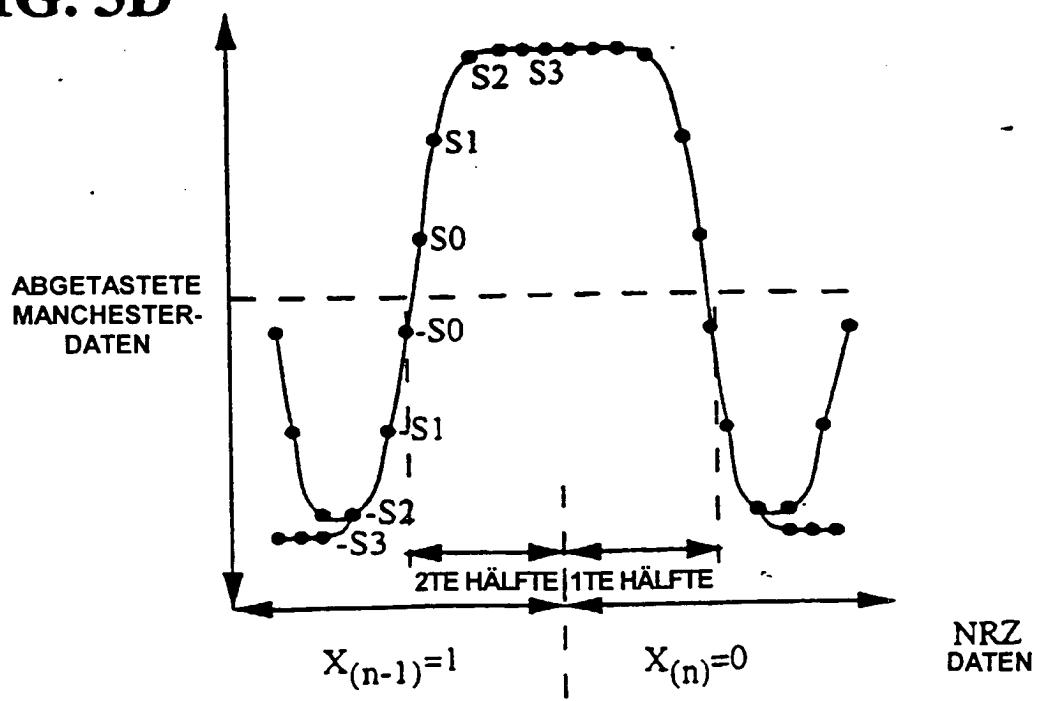

**[0022]** **Fig.** 3A–3D stellen beschreibend einen Satz von abgetasteten, sinusförmigen bzw. sinusähnlichen Breitbandwellenformen dar, die durch einen Breitbandwellenformgenerator erzeugt werden, der in einem Dualbetriebsartsender in der FM-Betriebsart enthalten ist.

**[0023]** **Fig.** 3E stellt in Tabellenform die Information dar, die beschreibend in den **Fig.** 3A–3D dargestellt ist.

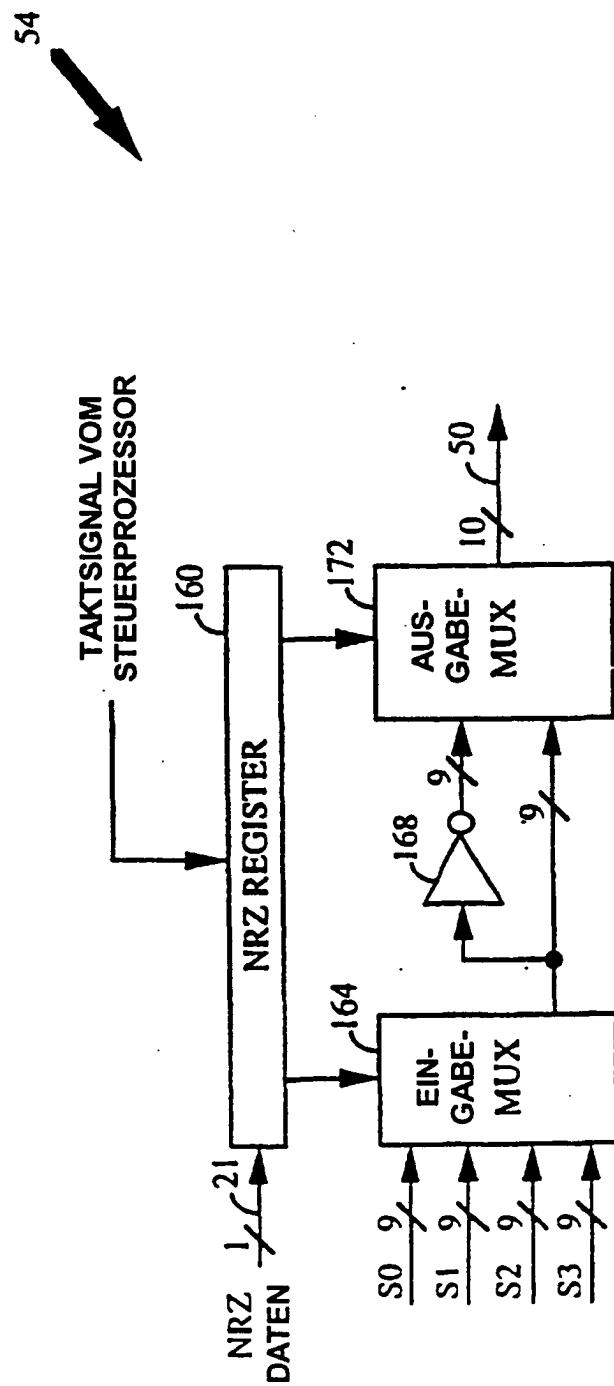

**[0024]** **Fig.** 4 liefert eine Blockdiagrammdarstellung einer bevorzugten Implementierung des Breitbanddatenwellenformgenerators.

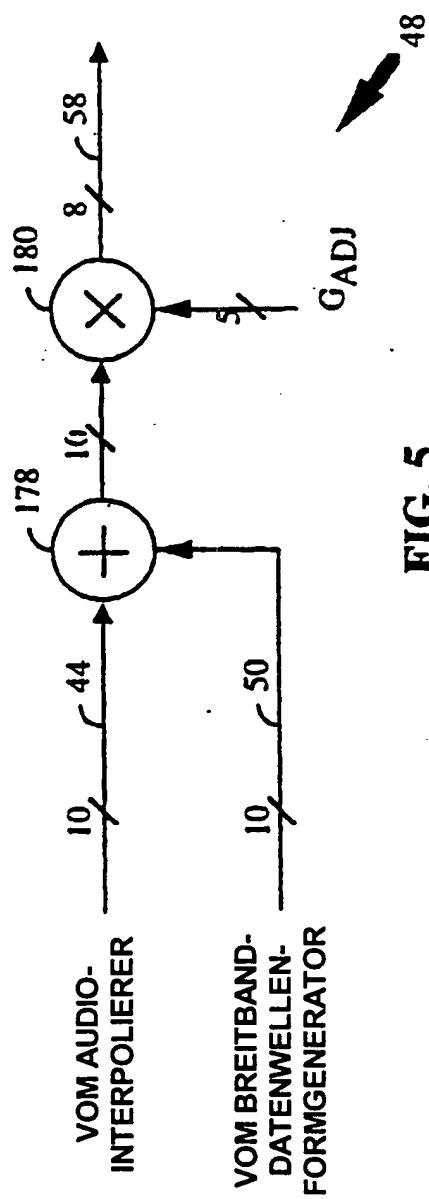

**[0025]** **Fig.** 5 zeigt ein Blockdiagramm eines Kombinierer- und Verstärkungsanpassnetzwerkes, das innerhalb eines Dualbetriebsartsenders beinhaltet ist.

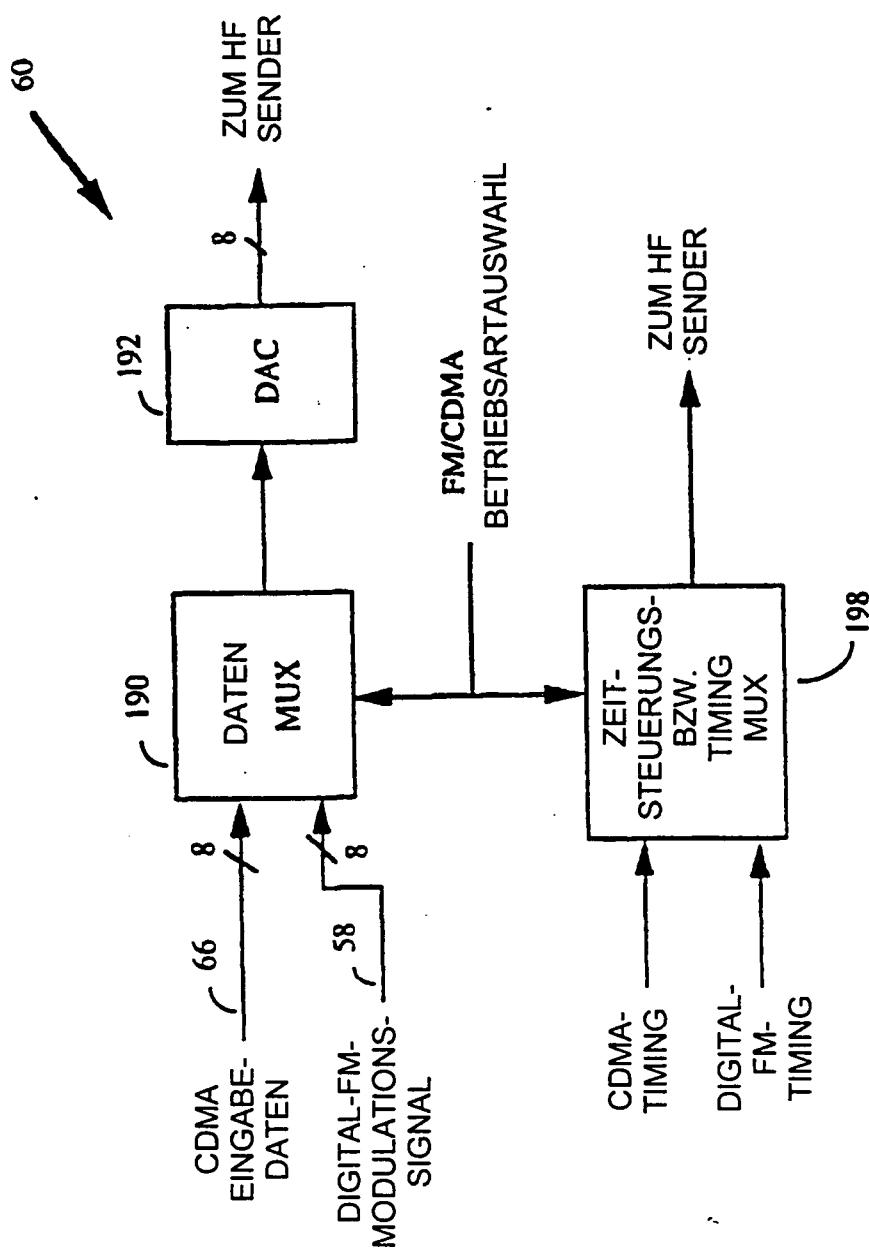

**[0026]** **Fig.** 6 zeigt ein Blockdiagramm eines CDMA/FM-Multiplexers, der betriebsmäßig in der Lage ist, selektiv CDMA- und Digital-FM-Modulationssignale an einen HF-Sender vorzusehen.

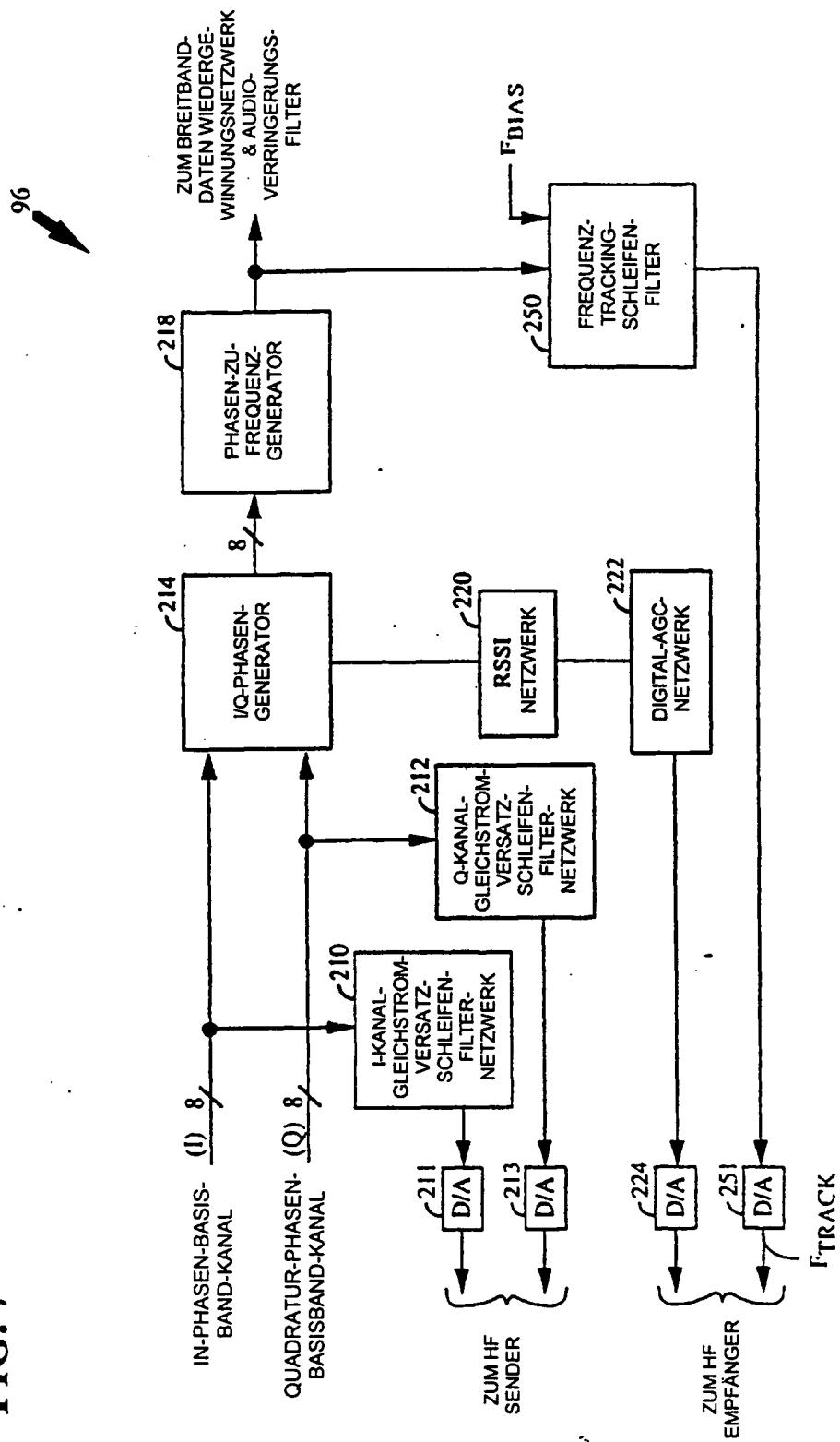

**[0027]** **Fig.** 7 zeigt ein Blockdiagramm einer bevorzugten Implementierung eines I/Q-FM-Demodulators, der innerhalb eines Dualbetriebsartempfängers gemäß Ausführungsbeispielen der vorliegenden Erfindung enthalten ist.

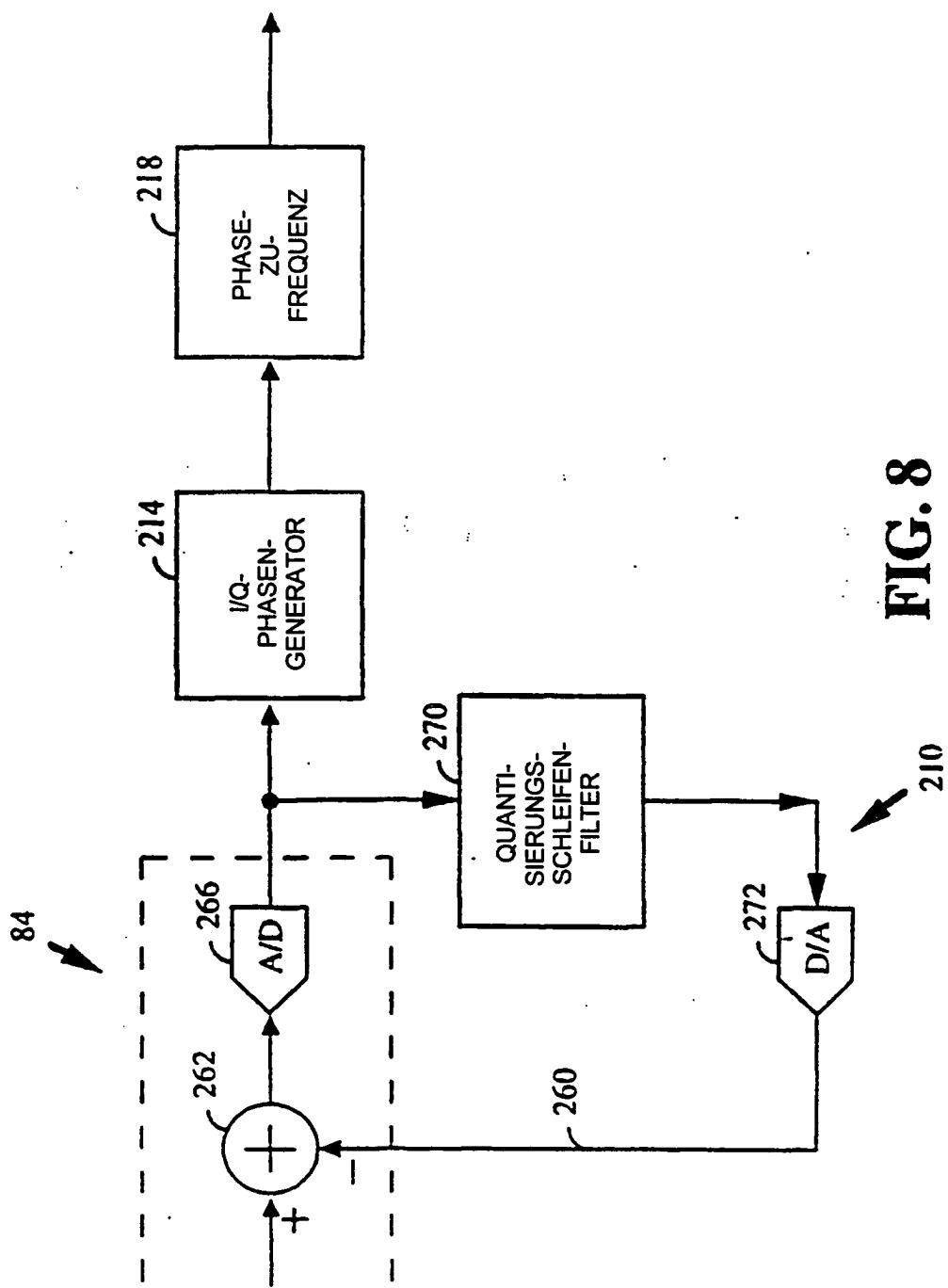

**[0028]** **Fig.** 8 zeigt eine Blockdiagrammdarstellung eines I-Kanal-Gleichstromversatzauslöschungssystems.

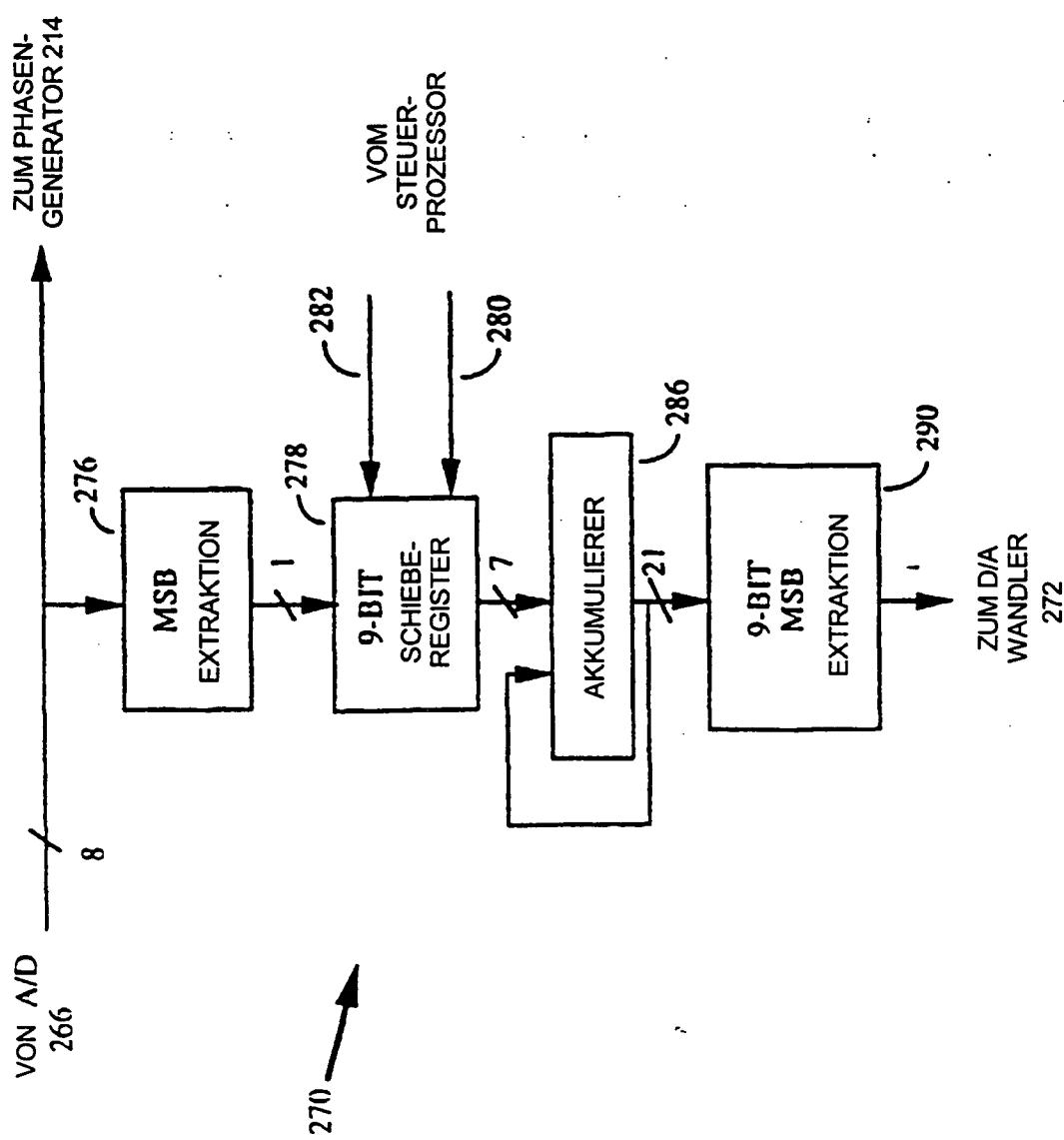

**[0029]** **Fig.** 9A sieht ein Blockdiagramm einer bevorzugten Implementierung eines Quantisierungsschleifen-filters vor, der innerhalb des I-Kanal-Gleichstromversatzschleifenfilternetzwerks enthalten ist.

**[0030]** **Fig.** 9B ist eine Tabelle, die einen Satz von Zeitkonstanten auflistet, bei denen die Gleichstromversatzkorrekturschleife eingestellt wird, und zwar während Betriebes in den Tracking- bzw. Nachführ- und Akquisitionsbetriebsarten.

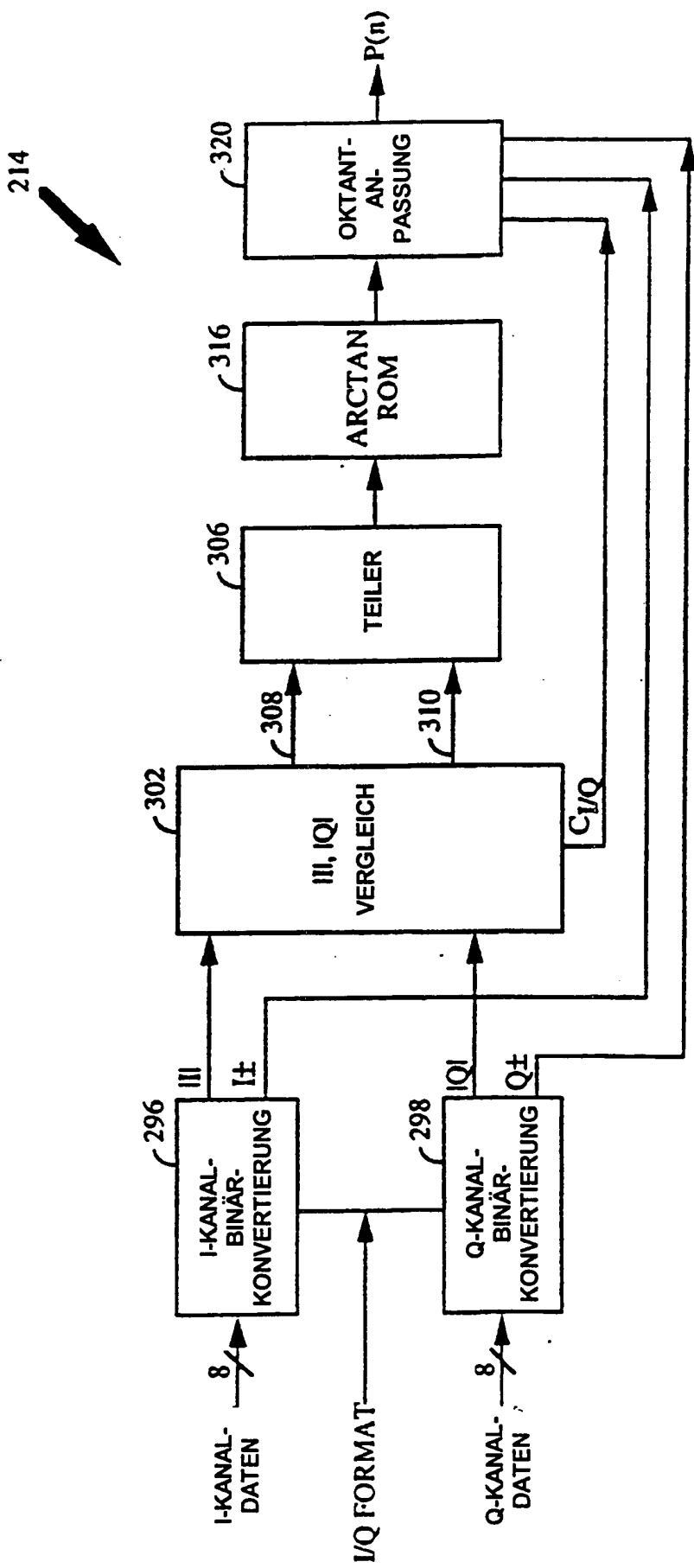

**[0031]** **Fig.** 10 liefert eine Blockdiagrammdarstellung eines I/Q-Phasengenerators, der in dem I/Q-FMDemodulator enthalten ist.

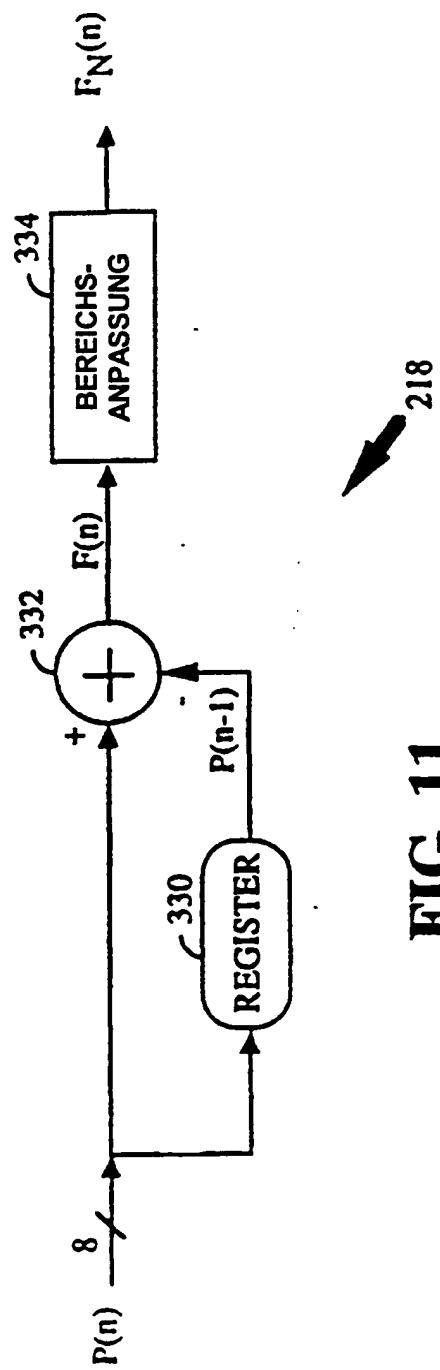

**[0032]** **Fig.** 11 ist ein Blockdiagramm einer bevorzugten Implementierung eines Phasen-zu-Frequenzgenerators, der ebenfalls innerhalb des I/Q-FM-Demodulators enthalten ist.

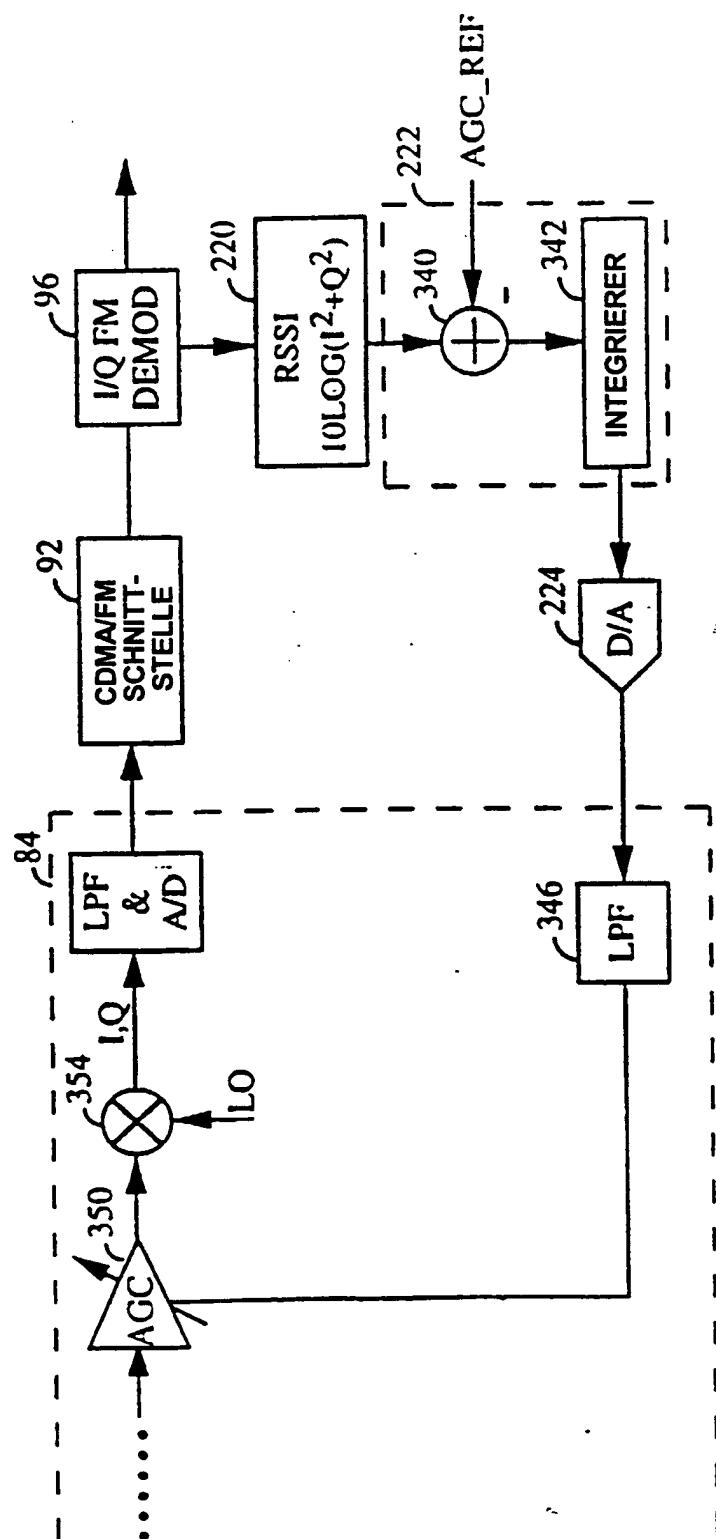

**[0033]** **Fig.** 12A zeigt die Architektur einer digitalen AGC-Schleife, die operativ ist zur Steuerung der ZF-Signalverstärkung.

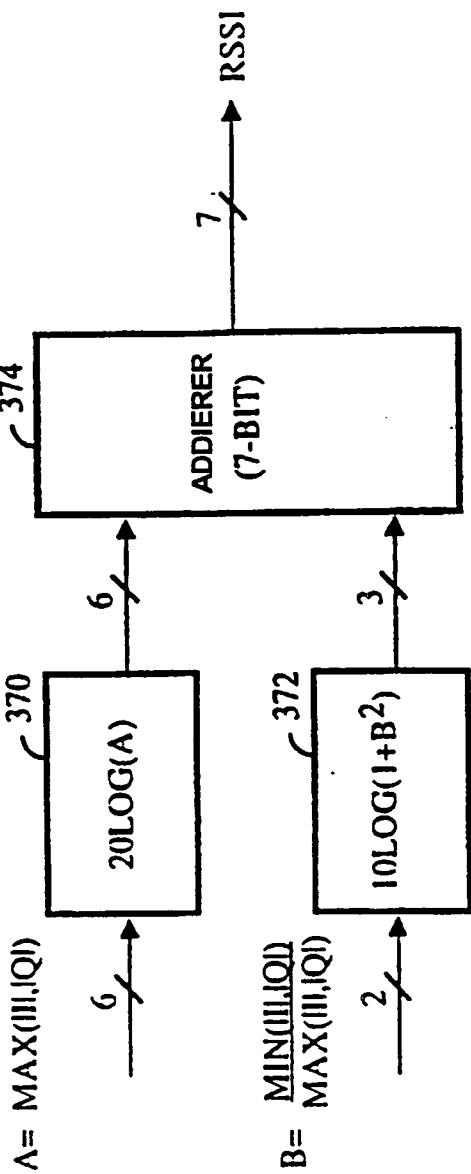

[0034] **Fig.** 12B ist eine Blockdiagrammdarstellung einer bevorzugten Implementierung eines RSSI-Netzwerkes der Digital-AGC-Schleife.

[0035] **Fig.** 13 zeigt eine bevorzugte Implementierung eines Digital-AGC-Netzwerks, das einen Integrieren und einen Subtrahieren beinhaltet.

[0036] **Fig.** 13B ist eine Tabelle von AGC-Schleifenzeitkonstanten, die verschiedenen Kombinationen von ausgewählten AGC-Schleifenverstärkungsparametern entsprechen.

[0037] **Fig.** 14A stellt beschreibend die Architektur einer bevorzugten Implementierung einer Frequenznachführungs- bzw. -trackingschleife dar, die innerhalb des Dualbetriebsartempfängers enthalten ist.

[0038] **Fig.** 14B ist eine Tabelle von Zeitkonstanten der Frequenz-Tracking-Schleife, die ausgewählten Schleifenverstärkungskonstanten zugeordnet sind.

[0039] **Fig.** 15 sieht ein Blockdiagramm einer bevorzugten Implementierung eines Audiodezimierungs- bzw. Verringerungsfilters vor, der in dem Dualbetriebsartempfänger enthalten ist.

[0040] **Fig.** 16 stellt beschreibend die Architektur einer Beispielimplementierung eines Breitbanddatenwiedergewinnungsnetzwerkes dar.

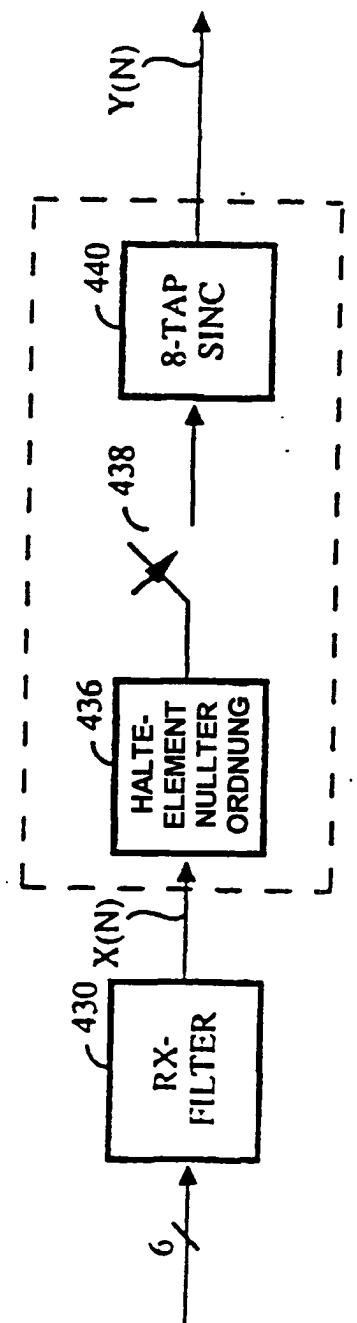

[0041] **Fig.** 17 ist ein Blockdiagramm eines Interpolationsfilters, der in dem Breitbanddatenwiedergewinnungsnetzwerk enthalten ist.

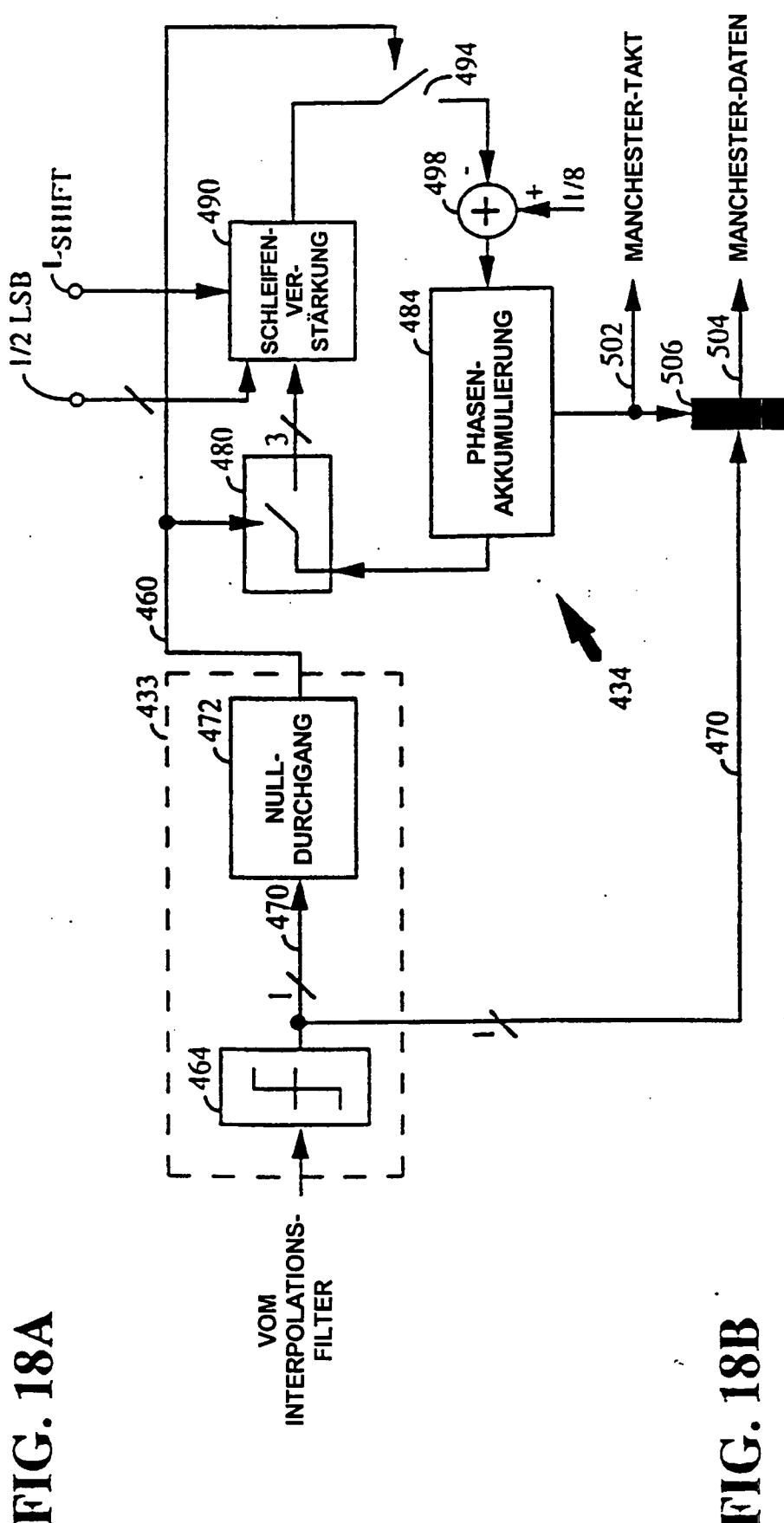

[0042] **Fig.** 18A zeigt Blockdiagramme der Timing-Wiedergewinnungs- und Manchester-Decodierungsnetzwerke.

[0043] **Fig.** 18B zeigt die Zeitkonstanten und Schleifenbandbreiten, die einer phasenverriegelten Schleife innerhalb des Manchester-Decodierungsnetzwerkes zugeordnet sind.

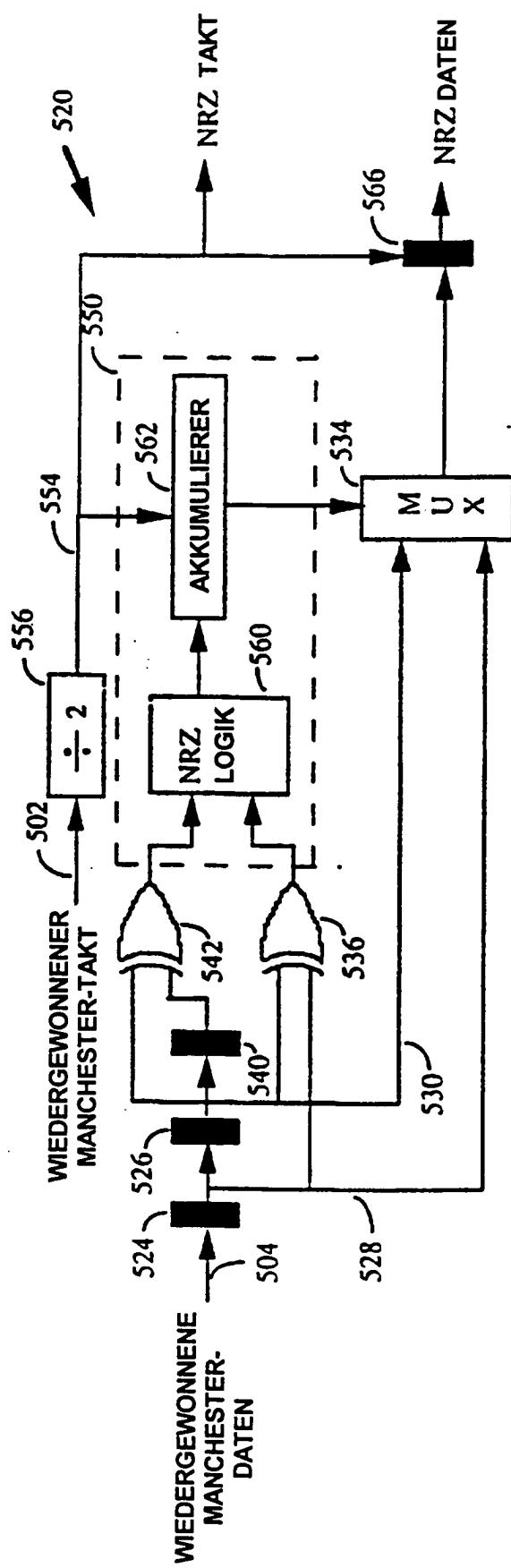

[0044] **Fig.** 19A sieht eine teilweise schematische Darstellung eines NRZ-Decoders vor, der in dem Breitbanddatenwiedergewinnungsnetzwerk enthalten ist.

[0045] **Fig.** 19B sieht eine Tabelle vor, die den Betrieb einer NRZ-Logikschaltung, die in dem NRZ-Decoder enthalten ist, zusammenfasst.

## DETAILLIERTE BESCHREIBUNG DES BEVORZUGTEN AUSFÜHRUNGSBEISPIELS

[0046] **Fig.** 1 sieht eine beschreibende Darstellung eines Dualbetriebsartdigitaalkommunikationssystems gemäß Ausführungsbeispielen der Erfindung vor. Das Dualbetriebsartkommunikationssystem beinhaltet einen Dualbetriebsartsender **14**, der angeordnet ist zum Senden von Digitalinformationssignalen zu einem Dualbetriebsartdigitalempfänger **16**. In einer Digital-FM-Betriebsart werden die gesendeten Digitalinformationssignale innerhalb des Dualbetriebsartsenders durch FM-Modulation eines HF-Trägers auf der Basis von digitalisierten Audio- und Breitbanddatensignalen generiert. Während des Betriebes in der Mehrfach-Zugriffsbetriebsart (multiple access mode) beinhalten die gesendeten Informationssignale z. B. Codemultiplex-Vielfachzugriffs-Informationssignale bzw. CDMA-Informationssignale. Ein FM-CDMA-Betriebsartauswahlsignal, das durch einen Steuerprozessor (nicht dargestellt) an den Sender **14** geliefert wird, ermöglicht eine Auswahl entweder des Betriebes in der Digital-FM-Betriebsart oder des Betriebes in der CDMA-Betriebsart.

### I. Übersicht über Dualbetriebsartsender

[0047] Es wird nun auf **Fig.** 1 Bezug genommen. Die Digital-FM-Verarbeitungskette des Senders **14** ist konfiguriert für den Empfang von Abtastaudioinformationssignalen **18** von einem digitalen Signalprozessor (DSP **20**) sowie konfiguriert für den Empfang eines seriellen Stroms von binären Nachrichtendaten **21** von einem Steuerprozessor (nicht dargestellt). In einem beispielhaften Ausführungsbeispiel werden die abgetasteten (z. B. 12-Bit) Audioinformationssignale **18** an einen Audiointerpolationsfilter **42** des Senders **14** mit einer Rate von 20 Kilosamples/Sekunde (ksps) geliefert. Wie im Folgenden beschrieben wird, wandelt der Interpolationsfilter **42** die 20 ksps abgetasteten Audiodaten in einen 120 ksps Strom von gesampelten Audiodaten **44** um, wobei jedes Audiosample bzw. -abtastung **44** aus 10 Bits besteht. Die abgetasteten Audiodaten **44** werden dann innerhalb eines Kombinierer- und Verstärkungsanpassnetzwerks **48** mit einer abgetasteten Breitbanddatenwel-

lenform **50**, die durch einen Breitbanddatenwellenformgenerator **54** vorgesehen wird, kombiniert.

**[0048]** Das zusammengesetzte Digital-FM-Modulationssignal **58**, das durch das Kombinierer- und Verstärkungsanpassnetzwerk **48** produziert wird, wird an einen Betriebsartauswahlschalter **60** innerhalb des CDMA/FM-Sendeinterface bzw. -schnittstelle vorgesehen. Während des Betriebes in der Digital-FM-Betriebsart liefert der CDMA/FM-Betriebsartauswahlschalter **60** das Digital-FM-Modulationssignal an einen Digital-zu-Analog-Wandler (digital to analog converter (DAC)) **62**. Innerhalb eines HF-Senders **64** moduliert das resultierende Analog-FM-Modulationssignal direkt die Frequenz eines Zwischenfrequenzträgers. Weitere Details einer bevorzugten Art und Weise, wie das Digital-FM-Modulationssignal gemäß der vorliegenden Erfindung generiert wird, werden unten unter Bezugnahme auf die **Fig. 2-4** vorgesehen.

**[0049]** Bei einem Schalten des Betriebes gemäß der Digital-FM-Betriebsart zu dem Betrieb in der CDMA-Betriebsart, wird ein CDMA-Datensignal, das durch eine CDMA-Eingabeleitung **66** getragen wird, an den HF-Sender **64** geliefert, und zwar anstelle des Digital-FM-Betriebsartmodulationssignals. Während des Betriebes in der CDMA-Betriebsart generiert der Sender **64** In-Phasen-(I)- und Quadratur-Phasen-(Q)-Pseudozufallsrauschsequenzen PNI und PNQ, die typischerweise einem bestimmten Gebiet (d. h. Zelle) entsprechen, in das Information während des Betriebes in der CDMA-Betriebsart gesendet wird. Innerhalb des Senders **64** wird das CDMA-Datensignal XOR-verknüpft mit den PNI- und PNQ-Sequenzen um so das CDMA-Datensignal vor der Übertragung zu spreizen. Die resultierende I-Kanal-Codespreizsequenz und Q-Kanal-Codespreizsequenzen werden verwendet, um ein Quadraturpaar von Sinusformen bzw. Sinusfunktionen biphasenzumodulieren. Die modulierten Sinusformen werden summiert, bandpassgefiltert, auf eine HF-Frequenz verschoben und wieder gefiltert und verstärkt bevor sie über Antenne **70** über einen Kommunikationskanal an dem Dualbetriebsartempfänger **16** abgestrahlt werden. Ein beispielhafter CDMA-Sender und Wellenformgenerator wird z. B. in dem U.S. Patent Nr. 5,103,459 beschrieben, das 1992 erteilt wurde, betitelt „System and Method for Generating Signal Waveforms in a CDMA Cellular Telephone System“, und das dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen ist.

## II. Übersicht über Dualbetriebsartempfänger

**[0050]** Bezug nehmend auf **Fig. 1** beinhaltet der Dualbetriebsartempfänger **16** eine Empfangsantenne **80** zum Empfangen der I- und Q-Kanal-Informationssignale, die durch einen Dualbetriebsartsender **14** gesendet wurden. Während beider Betriebsarten, der CDMA- und der Digital-FM-Betriebsarten, werden die I- und Q-Kanal-Informationssignale, die durch Antenne **80** empfangen werden, mittels eines Direktumwandlungsanalogempfängers **84** (direct conversion analog receiver) verarbeitet. Innerhalb des Analogempfängers **84** werden die I- und Q-Kanal-Informationssignale mit einem Lokaloszillatorsignal gemischt, um In-Phasen-(I)- und Quadratur-Phasen-(Q)-Basisbandsignale zu erzeugen. Während des Betriebes in der Digital-FM-Betriebsart wird die Lokaloszillatorkreisfrequenz so ausgewählt, dass sie um einen vorbestimmten Bereich bzw. Spanne von der HF-Trägerfrequenz versetzt ist. Auf diese Art und Weise werden die empfangenen I- und Q-Informationssignale auf die I- und Q-Digital-FM-Basisbandsignale konvertiert, und zwar versetzt von der Nullfrequenz, d. h. von einer „Null-ZF“ bzw. „Zero-IF“ um einen vorbestimmten Bereich.

**[0051]** Wie zuvor erwähnt wird innerhalb herkömmlicher Direktumwandlungs- bzw. Direktkonvertierungs-FM-Empfängern jegliche ungewünschte DC- bzw. Gleichstromsignalenergie, die in der Eingabewellenform enthalten ist, direkt auf das Nullfrequenzbasisband abgebildet, um das die gewünschten Quadraturbasisbandsignalkomponenten zentriert sind. Als Ergebnis hiervon können die nachfolgenden Schätzungen des Phasenwinkels beim Vorliegen von signifikanter externer Gleichstromsignalenergie korrumiert werden. Gemäß Ausführungsbeispielen der Erfindung erlaubt es der Frequenzversatz, der zweckmäßig innerhalb des Analogempfängers **84** eingeführt wird, die ungewünschte Gleichstromsignalenergie während der Verarbeitung der Basisband-I- und -Q-Signale zu entfernen.

**[0052]** Während des Betriebes in der CDMA-Betriebsart ist zu sehen, dass die I- und Q-Kanalbasisband-CDMA-Signalkomponenten über Empfängerausgabeleitung **88** und **90** an die Analog-zu-Digitalwandler (analog to digital converters (ADCs)) **92** der CDMA/FM-Empfängerschnittstelle geliefert werden. Die Basisband-CDMA-Signalkomponenten werden dann von den ADCs **92** zu einem CDMA-Verarbeitungsnetzwerk **94** transferiert. Innerhalb des CDMA-Verarbeitungsnetzwerkes **94** werden die Basisband-CDMA-Signalkomponenten demoduliert, entschachtelt bzw. deinterleaved und decodiert, und zwar z. B. auf eine Art und Weise wie es in dem oben erwähnten U.S. Patent Nr. 5,103,459 beschrieben ist.

**[0053]** Während des Betriebes in der Digital-FM-Betriebsart werden die Basisband-I- und -Q-Signale an die ADCs **92** über die Empfängerausgabeleitung **88** und **90** geliefert. Innerhalb der ADCs **92** werden die Basis-

band-I- und -Q-Signale mit einer beispielhaften Rate von 40 Kilosamples/Sekunde (kspS) digitalisiert, um 8-Bit In-Phasen-(I)- und 8-Bit Quadratur-Phasen-(Q)-Samples bzw. Abtastungen zu bilden. Die 8-Bit I- und Q-Abtastungen werden mit der beispielhaften Rate von 40 kspS an den I/Q-FM-Demodulator **96** ausgegeben. Innerhalb des digitalen FM-Demodulators **96** werden die I- und Q-Basisbandsignale in ein Phasensignal demoduliert und werden dann weiter in ein demoduliertes Frequenzsignal konvertiert. Wie im Folgenden in größerem Detail beschrieben wird, beinhaltet der Digital-FM-Demodulator **96** ebenfalls eine Gleichstromversatz-Tracking bzw. Nachführungsschleife zum Entfernen des Gleichstromversatzes der durch die HF-Verarbeitung innerhalb des Empfängers **84** eingeführt wird, so wie eine automatische Verstärkungssteuerungsschleife (automatic gain control (AGC) loop) und eine Frequenz-Tracking-Schleife. Wiederum Bezug nehmend auf **Fig. 1** wird während des Betriebes in der Digital-FM-Betriebsart das demodulierte Frequenzsignal mit einer beispielhaften 40 kspS Datenrate an einen Audioverringerungsfilter (audio decimation filter) **102** so wie an ein Breitbanddatenwiedergewinnungsnetzwerk **104** geliefert. Nach der Verarbeitung durch den Verringerungsfilter **102** wird das herunter abgetastete Audiosignal an einen Vocoder (nicht dargestellt) für die Wiedergewinnung der empfangenen Audioinformation gegeben. Gleichzeitig wird das Breitbanddatenwiedergewinnungsnetzwerk **104** betriebsmäßig eingesetzt um die empfangenen Breitbanddaten und Timinginformation von dem demodulierten Frequenzsignal zu extrahieren. Diese extrahierte Breitbandsignalinformation wird dann verwendet von einem Breitbanddatennachrichtendecoder **108**, der dazu dient, Breitbanddatenwortrahmen zu empfangen, Bit-Fehler zu korrigieren und die identifizierten Datenwörter und Nachrichten an einen Steuerprozessor für die weitere Bewertung weiterzuleiten.

### III. Detaillierte Beschreibung des Dualbetriebsartsenders

#### A. Audiointerpolationsfilter

**[0054]** Nun Bezug nehmend auf **Fig. 2** wird hier eine Blockdiagrammdarstellung des Audiointerpolationsfilters **42** gezeigt. Wie durch **Fig. 2** angezeigt wird, wird jede 12-Bit Abtastung von Audiodaten von dem Digitalen Signalprozessor **20** mit einer 20 kspS Rate über Leitung **18** an ein Halterregister nullter Ordnung **140** innerhalb des Audiointerpolationsfilters **42** geliefert. Die Ausgabe des Halterregisters nullter Ordnung **140** wird dann durch einen interpolierenden Switch bzw. Schalter **144** mit einer Rate, die gleich einem vordefinierten Mehrfachen der Eingabedatenrate ist, abgetastet. In dem bevorzugten Ausführungsbeispiel wird der Schalter **144** mit 120 kHz umge, d. h. dem Sechsachen der Audiodateneingaberate. Die resultierenden 120 kspS abgetasteten Audiodaten werden dann sequentiell durch einen 8-tap- bzw. -Abgriff-SINC-Filter **148** und durch einen 4-tap-SINC-Filter **152** verarbeitet. Die 8-tap und 4-tap SINC Filter **148**, **152** können durch die folgende Z-Domaintransferfunktion T8 bzw. T4 charakterisiert werden:

$$T8 = (1 + z^{-1} + \dots + z^{-7})/8, \text{ und}$$

$$T4 = (1 + z^{-1} + \dots + z^{-3})/4.$$

**[0055]** Der 4-tap-SINC-Filter **152** liefert, wie zu sehen, den 120 kbps Strom von abgetasteten Audiodaten **44**, wobei jede Audioabtastung **44** aus 10 Bits besteht.

#### B. Breitbanddatenwellenformgenerator

**[0056]** In einem bevorzugten Ausführungsbeispiel ist der Breitbanddatenwellenformgenerator **54** betriebsmäßig in der Lage, direkt eine Frequenz-Shift-Keyed-FSK-Modulationswellenform von den binären Nachrichtendaten **21** zu generieren bzw. synthetisieren. Wenn die Nachrichtendaten **21** aus einer Sequenz von nicht zu Null zurückkehrenden (Non Return To Zero, NRZ) Binärdaten bestehen, Manchester-codiert der Wellenformgenerator **54** die NRZ Datensequenz sowie synthetisiert die FSK-Modulationswellenform. Jede NRZ logische Eins wird als eine Null-Eins-Sequenz Manchester-codiert, und jede NRZ logische Null wird als Eins-Null-Sequenz Manchester-codiert. Um die Spektralbandbreite der resultierenden FSK-modulierten Wellenform zu begrenzen, werden die idealisierten Übergänge der Manchester-Sequenz als sinusähnliche Übergänge synthetisiert. Der Breitbanddatenwellenformgenerator ist Vorteilhafterweise so konstruiert, dass die Anforderung einer Tiefpassfilterung des Breitbanddatenmodulationssignals vor der Frequenzmodulation des Trägers überflüssig wird.

**[0057]** **Fig. 3A–3D** stellen beschreibend einen Satz von abgetasteten Breitbandübergangswellenformen (wide band transition waveforms) dar, die durch den Wellenformgenerator **54** ansprechend auf verschiedene Paare von NRZ-Datenbits erzeugt werden. Das erste NRZ Bit innerhalb eines jeden Paares wird entlang der horizontalen Achsen der **Fig. 3A–3D** durch die Notation X(n – 1) identifiziert, und das zweite Bit wird durch die No-

tation X(n) identifiziert. In den Darstellungen der **Fig. 3A–3D** werden zwölf Abtastungen ansprechend auf jedes Bit von NRZ-Daten generiert um die sinusähnliche Darstellung entsprechend eines jeden der Manchester-Datenbits zu erzeugen. In jeder der **Fig. 3A–3D** sind zwölf Abtastpunkte entsprechend den letzten sechs Abtastungen der Manchester-Wellenform für NRZ-Bit X(n – 1) und die ersten sechs Abtastungen der Manchester-Wellenform für NRZ-Bit X(n) dargestellt. Die synthetisierten Wellenformwerte sind durch die vordefinierten festen Konstanten  $\pm s_0$ ,  $s_1$ ,  $s_2$  und  $s_3$  definiert. Die Information, die in den **Fig. 3A–3D** dargestellt ist, ist in Tabellenform in der **Fig. 3E** präsentiert.

**[0058]** Nun Bezug nehmend auf **Fig. 4** wird ein Blockdiagramm einer bevorzugten Implementierung des Breitbanddatenwellenformgenerators **54** gezeigt. In dem Ausführungsbeispiel der **Fig. 4** werden die Eingabe-NRZ-Binärdaten mit einer beispielhaften Rate von 10 Kilobits/s (kbps) vorgesehen und die abgetastete Manchester-Darstellungsform wird mit einer Rate von 120 Kilosamples/Sekunde (ksps) mit einer Abtastrate von 10 Bits generiert. Der Wellenformgenerator **54** beinhaltet ein NRZ-Datenregister **160** zum Speichern von aufeinander folgenden Paaren von NRZ-Binärdaten X(n – 1) und X(n). Ein Eingabemultiplexer **164** generiert eine Sequenz bestehend aus den Werten  $s_0$ ,  $s_1$ ,  $s_2$  und/oder  $s_3$ , basierend auf den Werten X(n – 1) und X(n), die in dem Register **160** gespeichert sind. Zum Beispiel deutet **Fig. 3E** an, dass für  $X(n – 1) = 0$  und  $X(n) = 1$  der Multiplexer **164** die Sequenz  $s_0$ ,  $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_3$ ,  $s_3$  gefolgt von der Sequenz  $s_3$ ,  $s_3$ ,  $s_3$ ,  $s_2$ ,  $s_1$ ,  $s_0$  generiert. Diese Sequenzen und die Negativen dieser Sequenzen, die durch den Invertierer **168** erzeugt werden, werden dann an den Ausgabemultiplexer **172** geliefert. Für den beispielhaften Fall von  $X(n – 1) = 0$  und  $X(n) = 1$  erzeugt der Ausgabemultiplexer **172** die Sequenz  $-s_0$ ,  $-s_1$ ,  $-s_2$ ,  $-s_3$ ,  $-s_3$ ,  $-s_3$  entsprechend der zweiten Hälfte von  $X(n – 1) = 0$  und die Sequenz  $-s_3$ ,  $-s_3$ ,  $-s_3$ ,  $-s_2$ ,  $-s_1$ ,  $-s_0$  entspricht der ersten Hälfte von  $X(n) = 1$ . In dem allgemeinen Fall wählt der Ausgabemultiplexer **172** zwischen der Sequenz, die von dem Eingabemultiplexer **164** produziert wird und der komplementären Sequenz, die durch den Invertierer **168** produziert wird, aus, um die abgetastete Wellenform zu generieren, die dem Paar von NRZ-Werten X(n) und X(n – 1), die momentan in dem Register **160** gespeichert sind, zugeordnet ist.

#### C. Kombinierer und Verstärkungsanpassnetzwerk

**[0059]** **Fig. 5** zeigt ein Blockdiagramm des Kombinierers und Verstärkungsanpassnetzwerks **48**. Das Netzwerk **48** beinhaltet einen Digitaladdierer **178** zum Kombinieren der abgetasteten Audiodaten **44** mit der abgetasteten Breitbanddatenwellenform **50** (**Fig. 4**).

**[0060]** Das resultierende 10-Bit abgetastete FM-Modulationssignal wird dann skaliert, und zwar innerhalb eines Multiplizierers **180**, durch eine 6-Bit Verstärkungsanpasskonstante  $G_{ADJ}$ . Die Konstante  $G_{ADJ}$  wird ausgewählt um jegliche Abweichung von einer gewünschten Spannungs-Frequenzantwort, und zwar aufgezeigt durch einen spannungsgesteuerten Oszillator (nicht dargestellt) innerhalb des HF-Senders **64** zu kompensieren. Das verstärkungsangepasste Digital-FM-Modulationssignal **58** von dem Multiplizieren **180** wird dann an den CDMA/FM-Multiplexer **60** geliefert.

#### D. CDMA/FM-Schnittstellen-Digital-zu-Analog-Wandler

**[0061]** Bezug nehmend auf **Fig. 6** wird hier ein Blockdiagramm des CDMA/FM-Multiplexers **60** gezeigt. Wie in der **Fig. 6** angezeigt ist, empfängt der Datenmultiplexer **190** beide, die CDMA-Daten **66** und das Digital-FM-Modulationssignal **58**. Der geeignete Datenstrom wird zu einem Digital-zu-Analog-Wandler (digital to analog converter (DAC)) **192** für die Konvertierung zu einem Analogsignal vor der Ausgabe zu dem HF-Sender (**64**) (**Fig. 1**) gemultiplext. Eine Auswahl des Digitaleingabestroms für die Ausgabe wird durch das FM/CDMA-Betriebsartauswahlsignal gesteuert, das an den Datenmultiplexer **190** angelegt wird. Ähnlich wird entweder ein CDMA-Taktsignal oder ein digitales FM-Taktsignal an den DAC **192** geliefert, um den Datenkonvertierungsprozess mit dem Timing der Eingabedatensequenz (d. h. FM oder CDMA-Datensequenz) zu synchronisieren.

### IV. Detaillierte Beschreibung des Dualbetriebsartempfängers

#### A. Basisbanddigital-FM-Demodulator

##### 1. Strukturelle Übersicht

**[0062]** Wiederum Bezug nehmend auf **Fig. 1** werden während des Betriebes in der FM-Betriebsart die 8-Bit In-Phasen-(I)- und 8-Bit Quadratur-Phasen-(Q)-Abtastungen von den ADCs der CDMA/FM-Empfangsschnittstelle **92** mit einer Rate von 40 ksps an den I/Q-FM-Demodulator **96** ausgegeben. Ein Blockdiagramm einer

bevorzugten Implementierung des I/Q-FM-Demodulators **96** ist in der **Fig. 7** gezeigt. Die I- und Q-Abtastungen sind jeweils repräsentativ für die Real- und Imaginärbestandteile einer Komplexvektordarstellung einer Basisbandentsprechung bzw. -äquivalent des empfangenen FM-Signals. In einer beispielhaften Implementierung wird das Basisbandäquivalentsignal auf eine Basisbandfrequenz übersetzt, das von der Nullfrequenz (d. h. 0 Hz) um einen vorbestimmten Bereich bzw. Spanne versetzt ist. Wie oben angemerkt wurde ist der Analogempfänger **84** so konstruiert, dass die empfangenen Signale, die von der HF-Mittelfrequenz um einen vorbestimmten Frequenzbereich (z. B. 150 Hz) versetzt sind, auf die Nullfrequenz abgebildet (map) werden. Solch ein Gleichstromversatzbereich (DC offset margin) erlaubt eine Differenzierung zwischen einem unmodulierten FM-Signal, d. h. einem kontinuierlichen Wellensignal bzw. CW-Signal (Continuous-Wave-signal) und Gleichstromversatzfehlern, die während der Analogverarbeitung eingeführt wurden. Gemäß einem Ausführungsbeispiel der Erfindung verbleiben die Gleichstromversatzfehler an der Nullfrequenz, während das Frequenz-übersetzte CW-Signal auf eine von Null verschiedene Basisbandfrequenz, und zwar äquivalent zu dem vordefinierten Frequenzbereich (d. h. 150 Hz) abgebildet wird. Wie unten unter Bezug auf **Fig. 8** beschrieben ist, sind I-Kanal- und Q-Kanal-Gleichstromversatzkorrekturschleifen **210** und **212** dafür konstruiert, diesen Gleichstromversatz (DC offset) aus dem Empfangssignalweg zu entfernen, und zwar vor der weiteren Verarbeitung durch den I/Q-Demodulator **96**. Die Gleichstromversatzkorrekturschleifen **210** und **212** erlauben Vor teilhafterweise die Entfernung der Gleichstromversatzfehler ohne dabei die CW-Signalinformation zu zerstören.

**[0063]** Der FM-Demodulator **96** beinhaltet weiterhin einen I/Q-Phasengenerator **214**, der konstruiert ist, um eine Schätzung des Phasenwinkels des empfangenen FM-Signalvektors zu schätzen. Die Funktion, die durch den I/Q-Phasengenerator **214** ausgeführt wird, kann wie folgt ausgedrückt werden:

$$P(n) = \arctan\{I(n)/Q(n)\},$$

wobei  $P(n)$  den Phasenwinkel, der der Abtastung des FM-Signalvektors definiert durch  $I(n)$  und  $Q(n)$  zugeordnet ist, bezeichnet. Eine beispielhafte 4-Quadranten-Arcustangensberechnung ergibt eine Schätzung des Phasenwinkels  $P(n)$  wie folgt:

- (i) berechne  $B = \min(|I|, |Q|)/\max(|I|/|Q|)$

- (ii) bestimme einen geschätzten Phasenwert  $P_e(n)$  innerhalb des Bereichs 0 bis  $\pi/4$ , wobei  $P_e(n) = \text{TAN}^{-1}(B)$  ist, und

- (iii) Remappen bzw. erneutes Abbilden der Phasenschätzung  $P_e(n)$  in dem Bereich  $-\pi$  bis  $+\pi$ , basierend auf den relativen Beträgen von  $|I|$  und  $|Q|$ , und den Vorzeichen von  $I$  und  $Q$ .

**[0064]** Das Vorhergehende identifiziert eine Technik zur Durchführung einer 4-Quadranten-Arcustangensberechnung. Es ist jedoch offensichtlich, dass alternative Versionen dieses Algorithmus durch den Fachmann verwendet werden könnten.

**[0065]** Die Sequenz von Phasenschätzungen des I/Q-Phasengenerators **214** wird dann auf ein Frequenzsignal durch einen Phasen-zu-Frequenzgenerator **218** konvertiert. In einer beispielhaften Implementierung besteht die Eingabe an den Phasen-zu-Frequenz-Generator **218** aus einem 8-Bit normalisierten Phasensignal  $P(n)$ , wobei  $0 < P(n) < 2$  ist. Die Differenzierungsfunktion, die durch den Phasen-zu-Frequenz-Generator **218** ausgeführt wird, kann wie folgt mathematisch ausgedrückt werden:

$$F(n) = P(n) - P(n - 1)$$

wobei  $F(n)$  die Frequenzabtastung ist, die von den normalisierten Phasenabtastungen  $P(n)$  und  $P(n - 1)$  abgeleitet wird. In einer bevorzugten Implementierung werden die Frequenzabtastungen  $F(n)$  auf eine Sequenz von Abtastungen  $F_N(n)$  normalisiert, so dass  $-1 < F_N(n) < 1$  ist. Der I/Q-Phasengenerator **214** und der Phasen-Zu-Frequenz-Generator **218** werden in größerem Detail unten mit Bezug auf **Fig. 10** und **11** beschrieben.

**[0066]** Bezug nehmend wiederum auf **Fig. 7** berechnet ein RSSI-Nachschlagenetzwerk **220** (RSSI look up network) eine Schätzung der empfangenen Signalstärke basierend auf den Parametern  $\max(|I|, |Q|)$  und  $\min(|I|, |Q|)/\max(|I|, |Q|)$ , wobei beide durch den I/Q-Phasengenerator **214** vorgesehen werden. Das resultierende RSSI-Signal wird dann innerhalb eines digitalen automatischen Verstärkungssteuerungs- bzw. Automatic-Gain-Control-(AGC)-Netzwerks **222** verwendet, um ein digitales AGC-Steuerungssignal zu kreieren, das nachfolgend auf ein analoges AGC-Signal durch D/A-Wandler **224** konvertiert wird.

**[0067]** Wie es in **Fig. 7** angezeigt ist, empfängt ein Frequenz-Tracking-Schleifenfilter **250** die Frequenzabtastungen  $F_N(n)$  erzeugt durch den Phasen-zu-Frequenz-Generator **218**. Der Frequenz-Tracking-Schleifenfilter

**250** generiert ein digitales Signal, das in ein analoges Frequenz-Tracking-Signal ( $F_{\text{TRACK}}$ ) durch D/A-Wandler **251** konvertiert wird. Das Signal  $F_{\text{TRACK}}$  wird in dem Analogempfänger **84** zur Frequenzanpassung des Lokaloszillatorsignals, was in der Frequenzabwärtskonvertierung des empfangenen HF-Signals verwendet wird, eingesetzt. Wie oben angemerkt wurde, wird die empfangene I-Kanal- und Q-Kanal-FM-Signalenergie Frequenz-übersetzt innerhalb des Analogempfängers **84**, und zwar auf eine Basisbandfrequenz, die sich von 0 Hz unterscheidet um ein Entfernen von unerwünschten Gleichstromversatzfehlern zu ermöglichen bzw. zu erleichtern. Demgemäß wird eine vordefinierte konstante Frequenzvorspannung (constant frequency bias ( $F_{\text{BIAS}}$ )) an den Frequenz-Tracking-Schleifenfilter **250** vorgesehen und von den Frequenzabtastungen  $F_N(n)$ , die hierdurch verarbeitet werden, subtrahiert, und zwar um hinsichtlich des Basisbandversatzes, der innerhalb des Analogempfängers **84** eingeführt wird, zu kompensieren.

## 2. Betriebsbeschreibung des FM-Demodulators

**[0068]** Nun Bezug nehmend auf **Fig. 8** wird hier eine Blockdiagrammdarstellung des I-Kanal-Gleichstromversatzschleifenfilternetzwerkes **210** gezeigt, wobei anzumerken sei, dass das Q-Kanal-Gleichstromversatzschleifenfilternetzwerk **212** hierzu identisch ist. Wie es in der **Fig. 8** angezeigt ist, wird das I-Kanal-Versatzkorrektursignal **260**, das durch das Schleifenfilternetzwerk **210** erzeugt wird, an eine Subtraktionsschaltung **262** innerhalb des Basisband-I-Kanalweges geliefert. Das Schleifenfilternetzwerk **210** ist so konstruiert, dass das I-Kanal-Korrektursignal **260** jeden unerwünschten Gleichstromversatz, der in dem I-Kanalweg vorliegt, annähernd. Auf diese Art und Weise ist das komensierte Signal, dass durch die Subtraktionsschaltung **262** produziert wird, im Wesentlichen frei von Gleichstromversatzfehlern.

**[0069]** Im Betrieb wird das digitalisierte I-Kanal-Signal von einem A/D-Wandler **266** innerhalb des Empfängers **84** quantisiert und gefiltert, und zwar innerhalb eines Quantisierungsschleifenfilters **270**. Das resultierende digitale I-Kanal-Korrektursignal wird dann in das analoge I-Kanal-Korrektursignal **260** durch D/A-Wandler **272** konvertiert und an die Subtraktionsschaltung **262** geliefert.

**[0070]** Nun Bezug nehmend auf **Fig. 9A** wird eine teilweise schematische Darstellung einer bevorzugten Implementierung des Quantisierungsschleifenfilters **270** vorgesehen. Der Filter **270** beinhaltet ein MSB-Extraktionsregister **276** zum Liefern des höchststelligen Bits bzw. Most Significant Bit (MSB), d. h. dem Vorzeichenbit der 8-Bit Ausgabe des A/D-Wandlers an das Schieberegister **278**. Die Zeitkonstante des I-Kanal-Gleichstromversatzkorrekturschleifenfilternetzwerkes **210** kann durch Anpassen der Anzahl von Schiebebits **280** gesteuert werden, wobei die Bits zusammen mit einem Zweier-Komplement-Vorspannignal **282** an das Schieberegister **278** durch den Empfängersteuerprozessor geliefert werden. Die 11-Bit Ausgabe des Schieberegisters **278** wird an einen Akkumulator **286** geliefert, der betrieben wird, um eine 21-Bit Vorzeichen-erweiterte (sign extended) akkumulierte Ausgabe an eine 9-Bit MSB-Extrahier-Schaltung **290** vorzusehen. Die Extrahierschaltung **290** sendet die neuen MSBs des 21-Bit akkumulierten Digitalversatzkorrektursignals an den D/A-Wandler **272** (**Fig. 8**), der das analoge I-Kanal-Korrektursignal **260** produziert.

**[0071]** Insbesondere die Tabelle der **Fig. 9B** zeigt die Art und Weise an, wie die Bit-Verschiebungen, die innerhalb des Schieberegisters **278** ausgeführt werden, die Zeitkonstante der Gleichstromversatzkorrekturschleife setzen. Wie es durch **Fig. 9B** angezeigt wird, ist die Gleichstromversatzkorrekturschleife in der Lage, in beiden, den TRACKING- und den ACQUISITION-Betriebsarten zu operieren. Der Betrieb in der ACQUISITION-Betriebsart ist durch kürzere Schleifenzeitkonstanten charakterisiert, was eine schnelle anfängliche Konvergenz der Versatzkorrektur erlaubt. Die relativ kurzen Schleifenzeitkonstanten, die in der ACQUISITION-Betriebsart verwendet werden, erhöhen die Schleifenbandbreite relativ zu der Bandbreite in der TRACKING-Betriebsart, was die Existenz von größeren Versatzfehlern während der ACQUISITION-Betriebsart als in der TRACKING-Betriebsart erlaubt. Umgekehrt werden längere Schleifenzeitkonstanten, und damit eine engere Schleifenbandbreite, während der TRACKING-Betriebsart verwendet, um Versatzfehler im Dauerzustand bzw. Beharrungszustand (steady state offset errors) zu minimieren. Solch ein Betrieb mit Dualbetriebsarten erlaubt es, eine anfängliche Konvergenz mit einer minimalen Verzögerung zu erhalten, ermöglicht jedoch gleichzeitig eine Optimierung der Performance im Dauer- bzw. eingeschwungenen Zustand.

**[0072]** Nun Bezug nehmend auf **Fig. 10** wird eine Blockdiagrammdarstellung des I/Q-Phasengenerators **214** gezeigt. Der I/Q-Phasengenerator **214** beinhaltet I-Kanal- und Q-Kanal-Binärkonvertierungsschaltungen **296** und **298** zum Bestimmen des Vorzeichens und des Betrages der I-Kanal- und Q-Kanal-Basisbanddaten. In einer bevorzugten Implementierung werden die I-Kanal- und Q-Kanal-Basisbanddaten in Versatz binärer Form (offset binary form), den I-Kanal- und Q-Kanal-Binärkonvertierungsschaltungen **296** und **298** präsentiert.

**[0073]** Für die Basisbanddaten in einem Versatzbinärformat führen die Konvertierungsschaltungen **296** und

**298** die Funktion, wie sie in TABELLE 1 angeführt ist, aus. Im Detail ist, wenn das MSB der Eingabebasisbanddatenabtastung eine logische Eins ist, der absolute Wert (d. h. entweder  $|I|$  oder  $|Q|$ ) der Abtastung äquivalent zu den 8-Bits mit dem niedrigsten Stellenwert bzw. Least-Significant-Bits (LSBs) der Abtastung; anderenfalls wird der Absolutwert durch Invertieren der 8 LSBs erhalten. Die Konvertierungsschaltungen erzeugen ebenso Vorzeichenwerte,  $I\pm$  bzw.  $Q\pm$ , die anzeigen sind für die Vorzeichen der momentanen I- und Q-Kanal-Basisbanddatenabtastungen.

TABELLE 1

| Offset bzw. Versatz binär | Vorzeichen | Binärer Absolutwert | Dezimalabsolutwert |

|---------------------------|------------|---------------------|--------------------|

| 1,1111,1111               | +          | 1111,1111           | 255.5              |

| 1,1111,1110               | +          | 1111,1110           | 254.5              |

| .....                     | +          | .....               | .....              |

| 1,0000,0001               | +          | 0000,0001           | 1.5                |

| 1,0000,0000               | +          | 0000,0000           | 0.5                |

| 0,1111,1111               | -          | 0000,0000           | -0.5               |

| 0,1111,1110               | -          | 0000,0001           | -1.5               |

| .....                     | -          | .....               | .....              |

| 0,0000,0001               | -          | 1111,1110           | -245.5             |

| 0,0000,0000               | -          | 1111,1111           | -255.5             |

**[0074]** Wiederum Bezug nehmend auf Fig. 10 vergleicht ein Digitalvergleicher 302 die  $|I|$  und  $|Q|$  Werte und liefert min ( $|I|$ ,  $|Q|$ ) bzw. max ( $|I|$ ,  $|Q|$ ) an Digitalteiler 306 auf Signalleitung 308 und 310. Der Vergleicher 302 generiert ebenfalls das Steuersignal  $C_{I/Q}$ . Für einen  $|I| > |Q|$  wird das Steuersignal  $C_{I/Q}$  auf Eins gesetzt; anderenfalls wird  $C_{I/Q}$  auf Null gesetzt.

**[0075]** Der Teiler 306 erzeugt ein 6-Bit RATIO- bzw. Verhältnissignal, wobei das RATIO-Signal äquivalent ist zu  $\min(|I|, |Q|)/\max(|I|, |Q|)$ . Das RATIO-Signal wird an eine ARCTAN ROM Tabelle geliefert und dient als ein Index in Tabelle 316. Insbesondere wird die Funktion  $\text{THETA} = \arctan(\text{RATIO})$  innerhalb der Tabelle 316 gespeichert. Der Index RATIO reicht von 0 bis 63 entsprechend dem Dezimalbereich von 0 bis 1 und der berechnete Wert THETA reicht von 0 bis 31 entsprechend dem Dezimalbereich von 0 bis  $\pi/4$ . In einer beispielhaften Implementierung besteht die ARCTAN ROM Tabelle 316 aus dem Satz von vierundsechzig 5-Bit Phasenschätzungen, wie in TABELLE II angeführt.

TABELLE II

| Adresse | THETA | Adresse | THETA | Adresse | THETA | Adresse | THETA |

|---------|-------|---------|-------|---------|-------|---------|-------|

| 0       | 0     | 1       | 0     | 2       | 1     | 3       | 2     |

| 4       | 2     | 5       | 3     | 6       | 4     | 7       | 4     |

| 8       | 5     | 9       | 6     | 10      | 6     | 11      | 7     |

| 12      | 7     | 13      | 8     | 14      | 9     | 15      | 9     |

| 16      | 10    | 17      | 10    | 18      | 11    | 19      | 12    |

| 20      | 12    | 21      | 13    | 22      | 13    | 23      | 14    |

| 24      | 14    | 25      | 15    | 26      | 15    | 27      | 16    |

| 28      | 17    | 29      | 17    | 30      | 18    | 31      | 18    |

| 32      | 19    | 33      | 19    | 34      | 20    | 35      | 20    |

| 36      | 21    | 37      | 21    | 38      | 22    | 39      | 22    |

| 40      | 22    | 41      | 23    | 42      | 23    | 43      | 24    |

| 44      | 24    | 45      | 25    | 46      | 25    | 47      | 26    |

| 48      | 26    | 49      | 26    | 50      | 27    | 51      | 27    |

| 52      | 27    | 53      | 28    | 54      | 28    | 55      | 29    |

| 56      | 29    | 57      | 29    | 58      | 30    | 59      | 30    |

| 60      | 30    | 61      | 31    | 62      | 31    | 63      | 31    |

**[0076]** Wie es durch TABELLE II angezeigt ist, wird nur „Hauptwert“- bzw. „principal value“-Phaseninformation in der ARCTAN ROM Tabelle 316 gespeichert. D.h., dass um Speicherplatz zu sparen die ARCTAN ROM Tabelle nur Werte beinhaltet von einem Achtel der Polarebene, d. h. von 0 bis  $\pi/4$ . Demgemäß erzeugt betriebsmäßig ein Oktant-Anpassmodul **320** eine Ausgabesequenz P(n) der PHASE-Werte, und zwar durch Rotieren eines jeden THETA-Wertes abgefragt von der ARCTAN ROM Tabelle 316 in den geeigneten Oktanten. Der Oktant-Anpassungsprozess wird basierend darauf, ob  $I > 0$ ,  $Q > 0$  ist, und darauf, ob  $|I| > |Q|$  ist, ausgeführt, d. h. basierend auf den Werten von  $I\pm$ ,  $Q\pm$  und  $C_{I/Q}$ . TABELLE III führt die Anpassungen an, die durch das Oktant-Anpassungsnetzwerk **320** an den THETA-Werten, die jeder Kombination von  $I\pm$ ,  $Q\pm$  und  $C_{I/Q}$  zugeordnet sind, durchgeführt werden.

TABELLE III

| <b>C<sub>I/Q</sub></b> | <b>I<sub>+/−</sub></b> | <b>Q<sub>+/−</sub></b> | <b>PHASE</b>    |

|------------------------|------------------------|------------------------|-----------------|

| 0                      | 0                      | 0                      | 1100,0000-THETA |

| 0                      | 0                      | 1                      | 0100,0000+THETA |

| 0                      | 1                      | 0                      | 1100,0000+THETA |

| 0                      | 1                      | 1                      | 0100,0000-THETA |

| 1                      | 0                      | 0                      | 1000,0000+THETA |

| 1                      | 0                      | 1                      | 1000,0000-THETA |

| 1                      | 1                      | 0                      | 0000,0000-THETA |

| 1                      | 1                      | 1                      | 0000,0000+THETA |

**[0077]** Die logischen Operationen, die ausgeführt werden um die PHASE bzw. PHASEN-Werte, die in der TABELLE III aufgelistet sind, zu berechnen, können auf äquivalente Weise wie folgt ausgedrückt werden:

$$\text{PHASE}[7] = \sim Q_{+/-}$$

$$\text{PHASE}[6] = I_{+/-} \text{ XOR } Q_{+/-}$$

$$\text{PHASE}[5] = \sim C_{I/Q} \text{ XOR } I_{+/-} \text{ XOR } Q_{+/-}$$

$\text{PHASE}[4...0] = \sim C_{I/Q} \text{ XOR } I_{+/-} \text{ XOR } Q_{+/-} \text{ XOR } \text{THETA}[4...0]$ , wobei PHASE [i] das i-te Bit des nicht mit Vorzeichen versehenen 8-Bit Phasenwertes identifiziert, wobei das Bit 0 dem Bit mit niedrigsten Stellenwert entspricht.

**[0078]** Nun Bezug nehmend auf Fig. 11 wird hier ein Blockdiagramm einer bevorzugten Implementierung des Phasen-zu-Frequenz-Generators **218** gezeigt. Der Generator **218** ist angeordnet um die Sequenz der Phasenwerte P(n) generiert durch den I/Q-Phasengenerator **214** in eine normalisierte Sequenz von Frequenzwerten  $F_N(n)$  zu konvertieren. Wiederum kann die Differenzierungsfunktion, die durch das Schieberegister **330** und den Digitaladdierer **332** innerhalb des Phasen-zu-Frequenz-Generators **218** ausgeführt wird, mathematisch wie folgt repräsentiert werden:  $F(n) = P(n) - P(n - 1)$ . Ein Bereichsanpassungsmodul **234** wird vorgesehen um die Abtastungssequenz F(n) auf eine Sequenz von Abtastungen  $F_N(n)$  zu normalisieren, so dass  $-1 < F_N(n) < 1$  ist. In einem beispielhaften Ausführungsbeispiel wird diese Bereichsanpassung modulo 2 berechnet. Zum Beispiel resultiert eine modulo 2 Bereichsanpassung von  $P(n) = 1,1$  darin, dass diese Größe auf die normalisierte Frequenz  $F_N(n) = -0,9$  umabgebildet bzw. geremapped wird. Die modulo-Arithmetik entfernt jegliche Unklarheit in der Phasendifferenzberechnung, die von der „Phasen-Umwicklung“ bzw. „Phasenüberschlag“ (phase-wrapping) um den Einheitskreis herrührt. Die Frequenzabtastungen werden dann durch den Audioverringungsfilter **102** und das Breitbanddatenwiedergewinnungsnetzwerk **104** verarbeitet, die beide weiter unten beschrieben werden.

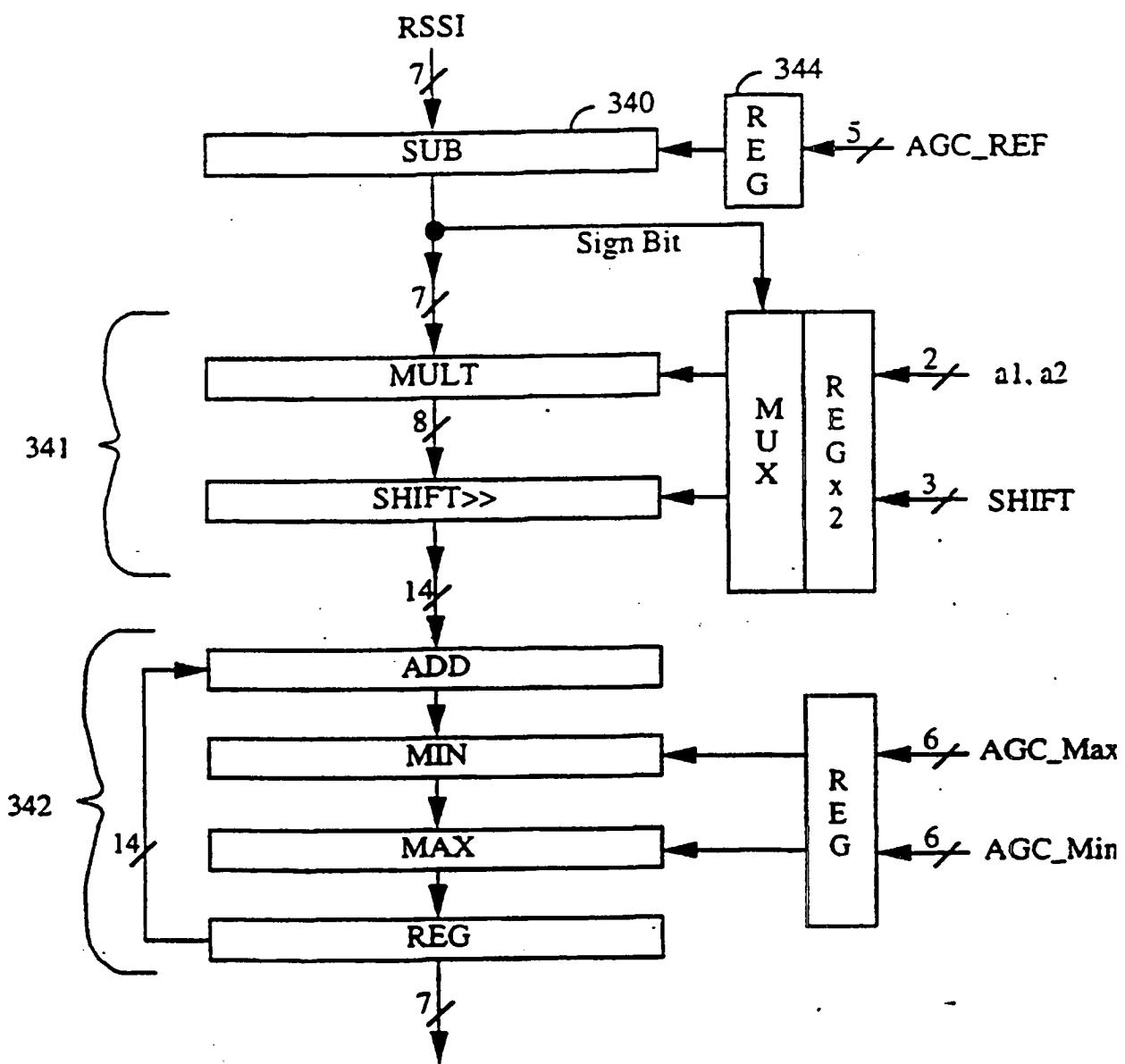

**[0079]** Bezug nehmend nun auf Fig. 12A wird hier das Blockdiagramm einer Digital-AGC-Schleife gezeigt, die betrieben wird, um die Verstärkung des Zwischenfrequenz-(ZF)-Signals (intermediate frequency (IF) signal), das innerhalb des Empfängers **84** generiert wird, zu steuern. Die Digital-AGC-Schleife beinhaltet, wie dargestellt, das RSSI-Netzwerk **220**, das Digital-AGC-Netzwerk **222**, und den D/A-Konvertierer **224**. Während des AGC-Schleifenbetriebes werden RSSI-Signale durch das RSSI-Netzwerk **220** generiert, und zwar auf der Basis von den  $|I|$  und den  $|Q|$  Werten, die innerhalb des I/Q-FM-Demodulators **96** generiert werden. Wie in der Fig. 12A angezeigt ist, wird ein Digitalsubtrahierer **340** innerhalb des AGC-Netzwerks **220** vorgesehen, und zwar zum Subtrahieren des Referenz- bzw. Bezugspegels AGC\_REF von dem RSSI-Signal ausgegeben durch die RSSI-Tabelle 220. Das resultierende Fehlersignal wird innerhalb des Schleifenfilters integriert (**342**)

und wird darin an den D/A-Wandler **224** geliefert.

**[0080]** Das analoge AGC-Signal von dem D/A-Wandler **224** wird durch einen Tiefpassfilter **346** innerhalb des Empfängers **84** gefiltert und wird dann in der Anpassung der Verstärkung eines AGC-Verstärkers **350** innerhalb des Empfänger-ZF-Signalweges verwendet. Der Verstärker **350** ist in der Lage, eine lineare (dB) Verstärkungs- bzw. Verstärkungsfaktorsteuerung über einen hohen dynamischen Bereich vorzusehen. Verstärker **350** kann eine Konstruktion besitzen, wie sie z. B. in dem U.S. Patent Nr. 5,099,204 beschrieben ist, das betitelt ist mit „Linear Gain Control Amplifier“ und dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen ist.

**[0081]** Um ein AGC-System mit geschlossener Schleife in der **Fig. 12A** darzustellen, wird eine verallgemeinerte Darstellung der Basisbandverarbeitung, die in dem Empfänger **84** ausgeführt wird, dargestellt. Im Detail wird das pegelgesteuerte ZF-Signal vom AGC-Verstärker **350** auf eine Basisbandfrequenz innerhalb des Mischers **354** übersetzt. Wie oben angemerkt wurde, wird die Frequenz des LO-Signals, das an den Mischer **354** angelegt ist, so ausgewählt, dass die Zentrale- bzw. Mittel-ZF-Frequenz auf eine Basisbandfrequenz abgebildet wird, die von Null Hz-versetzt ist. Die Basisbandsignale I und Q, die durch Mischer **354** produziert werden, werden dann in einem Basisband LPF & A/D Netzwerk **358** gefiltert und digitalisiert, und zwar bevor sie an die CDMA/FM-Empfängerschnittstelle **92** gesendet werden.

**[0082]** Nun Bezug nehmend auf **Fig. 12B** wird eine Blockdiagrammdarstellung einer bevorzugten Implementierung des RSSI-Netzwerks **220** vorgesehen. Das RSSI-Netzwerk **220** ist operativ um die Funktion  $10\log_{10}(I^2 + Q^2)$  auszuführen. Diese Funktion kann alternativ wie folgt ausgedrückt werden:

$$\text{RSSI} = 20\log_{10}[\max(|I|, |Q|)] + 10\log_{10}[1 + \min(|I|, |Q|)^2/\max(|I|, |Q|)^2]$$

**[0083]** Die Werte von  $\max(|I|, |Q|)$  und  $\min(|I|, |Q|)/\max(|I|, |Q|)$  kann auf effiziente Weise von dem I/Q-Phasen generator **214** erhalten werden, da diese Zwischenergebnisse ebenfalls während des Phasendemodulationsprozesses bestimmt werden müssen. Die Berechnungen von  $20\log_{10}[\max(|I|, |Q|)]$  und  $10\log_{10}[1 + \min(|I|, |Q|)^2/\max(|I|, |Q|)^2]$  wird innerhalb von ersten und zweiten LOG Funktionsblöcken **370** und **372** ausgeführt, die z. B. unter Verwendung von ROM Nachschlagetabellen programmierten Logikanordnungen (programmed logic arrays (PLAs)) oder herkömmlichen Logikgattern implementiert werden können. Das RSSI-Signal wird dann durch Kombinieren der Ausgaben der LOG-Funktionsblöcke **370** und **372** innerhalb eines digitalen Addierers **374** erhalten. **Fig. 13A** stellt eine bevorzugte Implementierung des Digitalsubtrahierers **340** und Integrierers **342** des Digital-AGC-Netzwerks **222** dar. Bezug nehmend auf **Fig. 13A** wird das AGC\_REF Signal vom Register **344** an den Subtrahierer **340** zusammen mit dem RSSI-Signal von dem RSSI-Netzwerk **220** geliefert. In einer beispielhaften Implementierung ist der AGC\_REF-Parameter eine 5-Bit Konstante, die in das Register **344** durch den Empfängersteuerprozessor geladen wird. Bezug nehmend auf **Fig. 13A** wird das 5-Bit vordefinierte Konstantensignal AGC\_REF von dem Steuerprozessor zusammen mit dem 7-Bit RSSI-Signal von dem RSSI-Netzwerk **220** an den Subtrahierer **340** geliefert. Die resultierende Betragsdifferenz (d. h. Signalpegelfehler) zwischen dem geschätzten RSSI-Signal und dem gewünschten Signalpegel (AGC\_Ref) wird durch das Schleifenfilterverstärkungsnetzwerk **341** skaliert. Die Schleifenfilterverstärkung wird durch einen Verstärkungs- bzw. Verstärkungsfaktorwert G spezifiziert, wobei  $G = 0.a_1a_2 \times 2^{\text{SHIFT}}$ . In einem beispielhaften Ausführungsbeispiel weisen die Teil- bzw. Bruchteileskomponenten ( $a_1a_2$ ) 2-Bit Werte auf und die arithmetische Linksverschiebung, die durch den Parameter SHIFT bzw. VERSCHIEBUNG spezifiziert ist, ist: ein 3-Bit Wert. Zum Beispiel ist bei  $a_1 = 1$ ,  $a_2 = 1$  und SHIFT = 3 die äquivalente Schleifenverstärkung  $0.11 \times 2^{-3}$  (binär) oder 3/32 (dezimal).

**[0084]** In der **Fig. 13A** ist der Bruchteilsskalierungsprozess (fractional scaling process) als eine Voll-Multiplikation (full multiply) implementiert, und der Schiebeprozess wird als eine arithmetische Linksverschiebung ausgeführt. Zwei vordefinierte Konstantschleifenverstärkungssignale, die als AGC\_Attack und AGC\_Decay identifiziert sind, werden an das AGC-Netzwerk vorgesehen. AGC\_Attack und AGC\_Decay bestehen jeweils aus einem 2-Bit Segment, das die Verstärkungskomponenten  $a_1$  und  $a_2$  repräsentiert und ein 3-Bit Segment, das den Parameter SHIFT repräsentiert. Das Vorzeichenbit des Signalpegelfehlersignals bestimmt die Skalierung hiervon durch AGC\_Attack und AGC\_Decay. Wenn das Vorzeichenbit positiv ist (d. h. logische „0“) wird der Fehler um bzw. durch die Verstärkung, spezifiziert durch AGC\_Decay, skaliert. Umgekehrt, wenn der Fehler negativ ist, wird der Fehler um die Verstärkung spezifiziert durch AGC\_Attack skaliert. Für positive Signalpegelfehler ist die AGC-Schleife operativ um den Signalpegel zu reduzieren, und zwar durch Reduzieren der Verstärkung durch den AGC-Verstärker. In diesem Fall wird die Schleifenverstärkung bzw. der Schleifenverstärkungsfaktor, und somit die entsprechende Schleifenzeitkonstante, durch den Wert AGC\_Decay definiert. Ähnlich ist beim Vorliegen von negativen Signalpegelfehlern die AGC-Schleife operativ um den Signalpegel durch Erhöhen der Verstärkung des AGC-Verstärkers zu erhöhen. Unter diesen Umständen sind die Schleifenver-

stärkung und die Zeitkonstanten durch den Wert von AGC\_Attack definiert.

**[0085]** Die Auswahl der Schleifenzeitkonstanten wird ausgeführt gemäß dem gewünschten Gleichgewicht, das es zu erreichen gilt, und zwar zwischen der Signalpegeltrackingfähigkeit der AGC-Schleife und dem Umfang in dem der Basisbandsignalpegel innerhalb des dynamischen Bereichs der DACs des AGC-Empfängers begrenzt verbleiben soll. **Fig. 13B** liefert eine Darstellung der Parameterwerte entsprechend einem beispielhaften Satz von Schleifenzeitkonstanten.

**[0086]** Nun Bezug nehmend auf **Fig. 13A** wird der skalierte 8-Bit Signalpegelfehler an den 14-Bit Sättigungs-integrierer **342** geliefert. Zusätzlich werden durch den Empfängersteuerprozessor 6-Bit vordefinierte obere und untere Sättigungsgrenzen bzw. Limits für Sättigung (AGC\_Max, AGC\_Min) des Integrieres **342** an das AGC-Netzwerk geliefert. Der Integrierer **342** ist operativ um den durchschnittlichen Signalfehler auf Null zu zwingen, was äquivalent ist zur Minimierung der Differenz zwischen dem durchschnittlichen geschätzten Signalpegel RSSI und dem gewünschten Signalpegel (AGC\_Ref). Die Sättigungsgrenzen (AGC\_Max, AGC\_Min) werden typischerweise so gewählt, dass sie den oberen und unteren Grenzen des Bereichs der AGC-Verstärkersteuerspannung entsprechen. Die sieben höchswertigen Bits (Most Significant Bits (MSBs)) werden von der Ausgabe des Integrierers **342** extrahiert und an den DAC **224** (**Fig. 12A**) geliefert, der wiederum operiert bzw. betrieben wird um die Verstärkung des AGC-Verstärkers anzupassen.

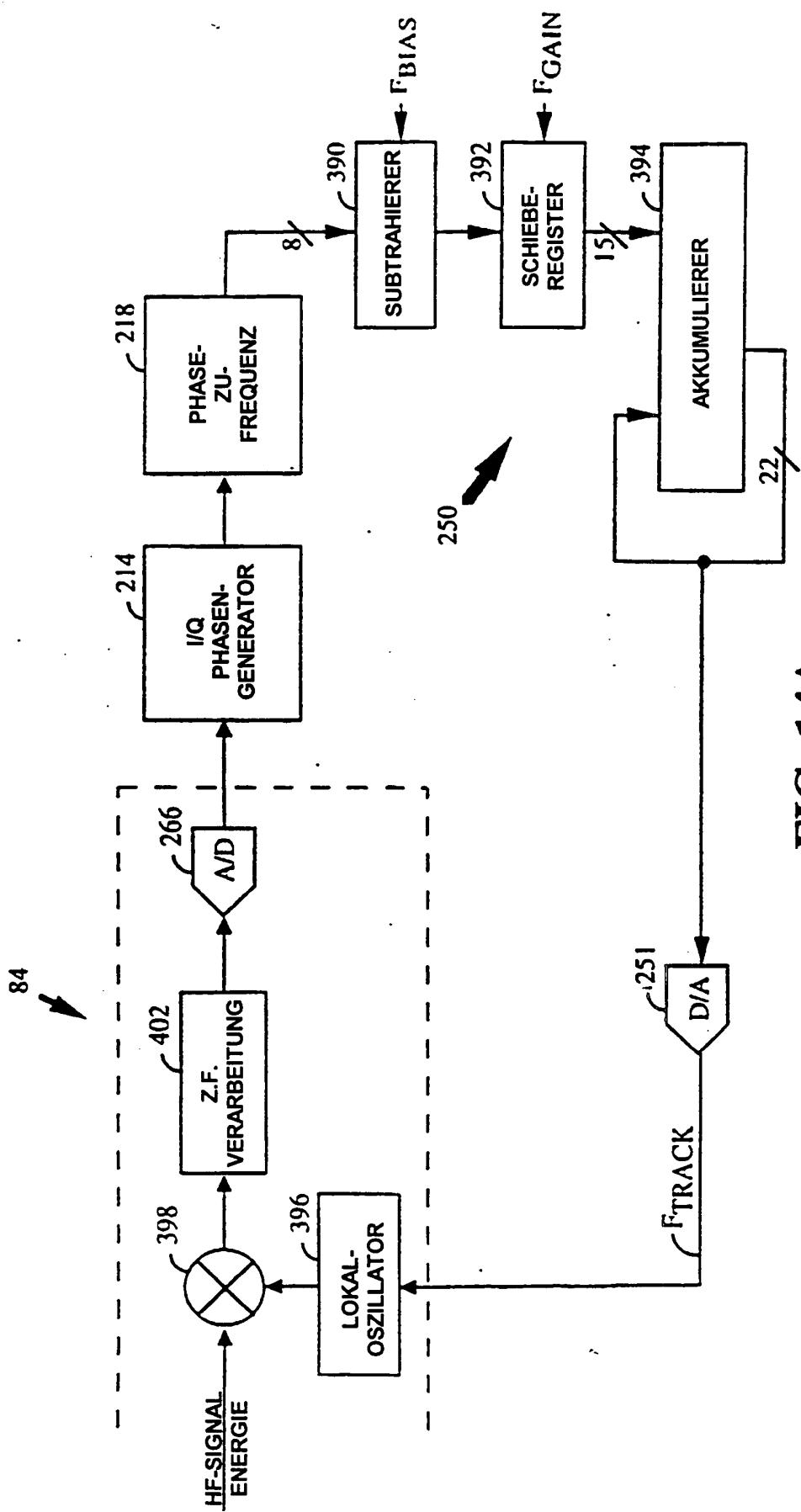

**[0087]** **Fig. 14A** repräsentiert darstellend die Architektur einer bevorzugten Implementierung einer Frequenz-Tracking-Schleife, die in dem Dualbetriebsartempfänger enthalten ist. Bezug nehmend auf **Fig. 14A** beinhaltet der Frequenz-Tracking-Schleifenfilter **250** einen Digitalsubtrahierer **390**, an den das 8-Bit FM-demodulierte Frequenzsignal von dem Phasen-zu-Frequenz-Generator **218** geliefert wird. Der Subtrahierer **390** ist konstruiert, um das Frequenz-Bias bzw. Vorspannignal ( $F_{BIAS}$ ) zu subtrahieren, was in einer beispielhaften Implementierung ungefähr äquivalent ist zu einem Frequenz-LSB (d. h. zu 156 Hz), und zwar von dem 8-Bit demodulierten Frequenzsignal. Das resultierende Differenzsignal wird an ein Schieberegister **392** geliefert und wird gemäß einer Frequenz-Tracking-Schleifenverstärkungskonstante  $F_{GAIN}$  Bit-verschoben. In der Tabelle der **Fig. 14B** sind die Zeitkonstanten der Frequenz-Tracking-Schleife, die verschiedenen Verstärkungskonstanten  $F_{GAIN}$  zugeordnet sind, kompiliert bzw. aufgestellt.

**[0088]** Die vorzeichenerweiterte Ausgabe des Schieberegisters **392** wird dann an einen Digitalakkumulierer bzw. -akkumulator **394** gesendet. In einer beispielhaften Implementierung hat die Ausgabe des Schieberegisters **392** eine 15-Bit Genauigkeit und der Akkumulierer **394** ist 22-Bit breit. Wie durch **Fig. 14A** aufgezeigt wird, wird die 8 MSB-Ausgabe durch den Akkumulierer **394** an den D/A-Wandler **251** geliefert. Es ist ebenso zu verstehen, dass während des Betriebes in der CDMA-Betriebsart ein CDMA-Frequenztrackingsignal an D/A-Wandler **251** gemultiplext werden kann anstatt der Ausgabe von dem Akkumulierer **394**.

**[0089]** Das Frequenz-Tracking-Signal  $F_{TRACK}$ , das durch den D/A-Wandler **251** erzeugt wird, wird benutzt um die Frequenz eines Lokaloszillators **396**, der in einem HF-Teil des Empfängers **84** enthalten ist, anzupassen. Der Empfänger **84** beinhaltet weiterhin einen Mischer **398** zum Übersetzen der Frequenz des empfangenen HF-Signals ansprechend auf die angelegte Frequenz des Lokaloszillators **396**. Das resultierende ZF-Signal wird dann an einen ZF-Verarbeitungsteil **402** geliefert, dessen Ausgabe durch einen A/D-Wandler **266** abgetastet und an den I/Q-Phasengenerator **214** geliefert wird. Auf diese Art und Weise ermöglicht die Frequenz-Tracking-Schleife der **Fig. 14A** ein „Closed-Loop“- bzw. geschlossenes Schleifendigital-Tracking der empfangenen HF-Trägerfrequenz. Zusätzlich ermöglicht die digitale Realisierung der **Fig. 14A** auf vorteilhafte Weise die Programmierung des Parameters  $F_{GAIN}$  auf eine Art und Weise, um eine gewünschte Schleifenantwort zu erlangen.

#### B. Audioverringerungsfilter

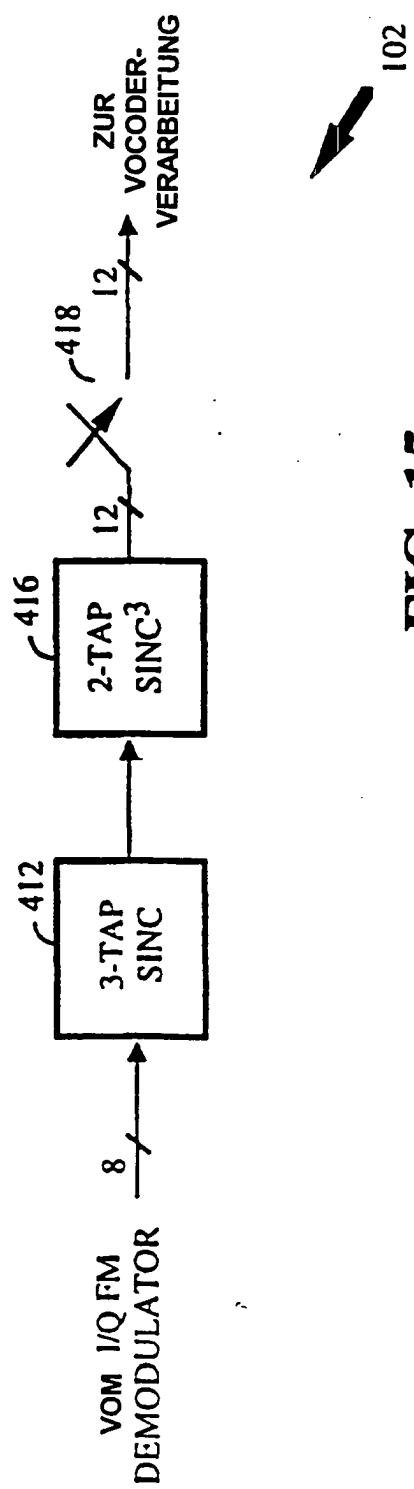

**[0090]** Nun Bezug nehmend auf **Fig. 15** wird ein Blockdiagramm einer bevorzugten Implementierung des Audio-Verringerungsfilters **102** vorgesehen. Der Verringerungsfilter wird betrieben um das demodulierte Frequenzsignal von dem I/Q-FM-Demodulator **96** auf eine niedrigere Datenrate zu konvertieren. In einem beispielhaften Ausführungsbeispiel werden die 8-Bit Daten, die mit 40 Kilosamples/Sekunde (ksps) durch den I/Q-FM-Demodulator erzeugt werden, innerhalb des Filters **102** auf 12-Bit Daten mit 20 ksps konvertiert.

**[0091]** Die Filterarchitektur der **Fig. 15** basiert auf einem Satz von kaskadierten SINC-Filtern (d. h.  $\text{sinc}(x) = \sin(x)/x$ ) um eine Hardwareimplementierungseffizienz zu erreichen. Insbesondere beinhaltet der Filter **102** einen Eingabe-3-tap-SINC-Filter **412**, der mit einem 2-tap-SINC<sup>3</sup>-Filter **416** kaskadiert ist. Die Ausgabe des SINC<sup>3</sup>-Filters **416** wird durch Schalter **418** mit der beispielhaften Rate von 20 ksps unter-abgetastet bzw.

sub-sampled. Der Filter **102** wird typischerweise konstruiert, um zumindest eine 40 dB Dämpfung über den Frequenzbereich von 16 bis 20 kHz vorzusehen. Dieser Dämpfungsgrad kann durch Realisierung der SINC-Filter gemäß der folgenden Z-Domain-Transferfunktionen bewirkt werden:

|                                        |                                       |

|----------------------------------------|---------------------------------------|

| SINC                                   | Filter Transferfunktion               |

| 3-tap-SINC ( <b>412</b> )              | $(1 + z - 1 + z - 2)/4$               |

| 2-tap-SINC <sup>3</sup> ( <b>416</b> ) | $(1 + z - 1)(1 + z - 1)(1 + z - 1)/8$ |

### C. Breitbandwellenform-Timing/-Datenwiedergewinnung

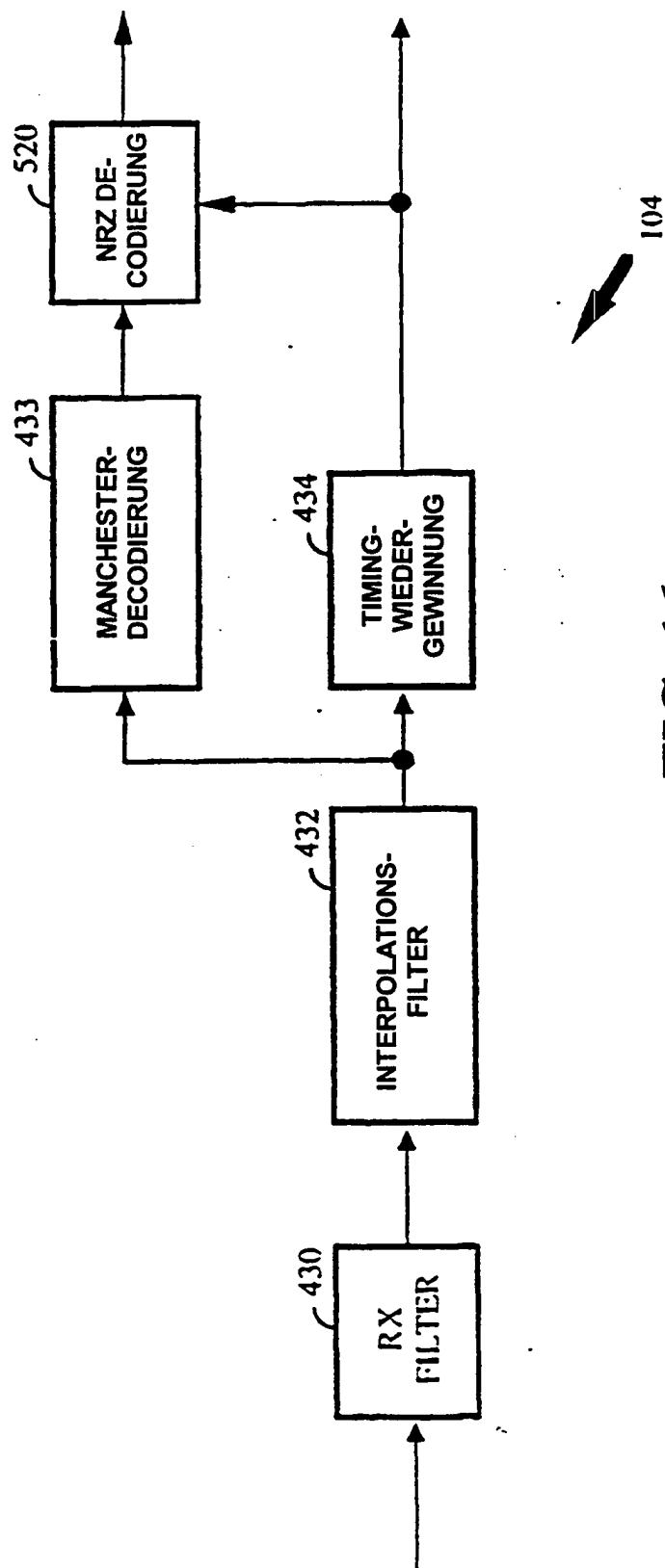

**[0092]** Nun Bezug nehmend auf **Fig. 16** wird hier darstellend die Architektur einer beispielhaften Implementierung des Breitbanddatenwiedergewinnungsnetzwerkes **104** dargestellt. Das Breitbanddatenwiedergewinnungsnetzwerk **104** ist angeordnet, um Timing-Wiedergewinnungs- und Decodierungsoperationen auf den Manchester-codierten Datenstrom, der durch den Dualbetriebsartempfänger **16** empfangen wird, auszuführen. Das Netzwerk **104** beinhaltet einen Empfängerfilter bzw. RX-Filter **430**, der einen abgestimmten Filter (matched filter) für den Manchester-Symbolstrom annähert. Zusätzlich bandbegrenzt der RX-Filter **430** das demodulierte FM-Signal und weist jegliches Hochfrequenzrauschen, das durch den Phasen-zu-Frequenzgenerator **218** erzeugt wird, zurück. In einer beispielhaften Implementierung ist der RX-Filter **430** so konstruiert, dass er die Charakteristiken eines analogen Butterworth-Tiefpassfilters 4ter Ordnung mit einer Cut-Off-Frequenz von ungefähr 13 kHz demoduliert bzw. wiedergibt. Angenommen das demodulierte FM-Signal wird durch den I/Q-Demodulator mit einer beispielhaften 40 ksps Rate generiert, kann der RX-Filter **430** als ein 2-tap-SINC-Filter (Null bei 20 ksps) realisiert werden, und zwar mit einer Z-Domain-Transferfunktion von  $(1 + z - 1)/2$ .

**[0093]** Nun Bezug nehmend auf **Fig. 16** wird ein Interpolationsfilter **432** zum Erhöhen der Abtastrate des gefilterten Signals erzeugt durch den RX-Filter **430** vorgesehen, um so eine Abtastauflösung zu erreichen, die für die Verarbeitung durch die Timing-Wiedergewinnungs- und Manchester-Decodierungsnetzwerke **433** und **434** geeignet ist. Der Interpolationsfilter **432** wird in größerem Detail in der **Fig. 17** dargestellt, und wie zu sehen, beinhaltet ein Halteelement nullter Ordnung (zero order hold) **436** zum Empfangen des 40 ksps Stromes von Abtastungen von dem RX-Filter **430**. Einschalter **438** ist vorgesehen, um die Ausgabe des Halteelements nullter Ordnung **436** mit einer beispielhaften Rate von 320 ksps erneut abzutasten bzw. zu resamplen um die geforderte Zeitauflösung für die Timing-Wiedergewinnung und Detektierung des 20 kbps Manchester-Stroms vorzusehen. Der resultierende erneut abgetastete 320 ksps Abtaststrom wird durch einen 8-tap-SINC-Filter **440** mit einer Transferfunktion von  $(1 + z - 1 + \dots + z - 7)/8$  gefiltert. Die resultierende linearinterpolierte Sequenz  $y(n)$ , die durch den 8-tap-SINC-Filter **440** ansprechend auf eine von dem RX-Filter **430** generierte Sequenz  $x(n)$  produziert wird, kann wie folgt dargestellt werden:

$$y(8n + k) = x(n)$$

für  $k = 0$ ; und

$$y(8n + k) = y(8n + k - 1) + (x(n) - x(n - 1))/8$$

für  $k = 1, \dots, 7$

**[0094]** Nun Bezug nehmend auf **Fig. 18A** werden Darstellungen in Blockdiagrammform der Timing-Wiedergewinnungs- und Manchester-Decodierungsnetzwerke **433** und **434** vorgesehen. In einem beispielhaften Ausführungsbeispiel wird das Manchester-Decodierungsnetzwerk **434** mittels einer digitalen Phasenverriegelungsschleife erster Ordnung (1st order digital phase locked loop (DPLL)) realisiert, wobei das Timing hiervon durch die Null-Durchgänge (zero crossings) **460**, die von dem Timing-Wiedergewinnungsnetzwerk **433** produziert werden bestimmt bzw. geregelt wird. Wie es in der **Fig. 18A** angezeigt ist, beinhaltet das Timing-Wiedergewinnungsnetzwerk **433** eine Datenschwellenwertschaltung **464** zum Vorsehen von mit Schwellenwert verglichenen (thresholded) Datenbits **470** mit der interpolierten Rate von 320 ksps an eine Null-Durchgangsschaltung **472**. Die am Schwellenwert verglichenen Datenbits **470** werden basierend auf dem Vorzeichen der Eingabeabtastsequenz produziert. Im Detail wird jeder Nulldurchgang **460** innerhalb der Nulldurchgangsschaltung **472** durch XOR-Verknüpfung von aufeinander folgenden am Schwellenwert gemessenen Datenbits **470** erzeugt.

**[0095]** Die DPLL des Manchester-Decodierungsnetzwerks **434** ist konstruiert, um die beispielhafte Manchester-Symbolrate von 20 ksps zu verriegeln. Das Decodierungsnetzwerk **434** beinhaltet einen Nulldurchgangs abgetasteten Phasendetektor **480**, der operativ ist, um die Ausgabe eines Phasenakkumulierers **484**

bei Generierung eines jeden Null-Durchgangs **460** abzutasten. In einem bevorzugten Ausführungsbeispiel produziert der Phasendetektor **480** ein 3-Bit Fehlersignal, das von den drei höchstststelligen Bits (Most Significant Bits (MSBs)) des Phasenakkumulierers extrahiert wird, wobei hierzu ein 1/2 niedrigstwertiger Bit-Versatz (Least Significant Bit (LSB) offset) addiert wird, um eine unvorgespannte 4-Bit Phasenfehlerschätzung zu erzeugen. Jede detektierte Phasenabtastung, die durch den Phasendetektor **480** produziert wird, wird innerhalb eines Schleifenverstärkungsskalierungsregisters **490** Bitverschoben, und zwar gemäß einer Schleifenverstärkungsverschiebung ( $L_{\text{SHIFT}}$ ), die von dem Empfängersteuerprozessor befehligt wird. Der Betrag der Bitverschiebung, die innerhalb des Skalierungsregisters **490** ausgeführt wird, bestimmt die Zeitkonstante, und somit die Bandbreite der DPLL innerhalb des Netzwerks **434**. Die Zeitkonstanten und Schleifenbandbreiten, die einen Beispielsatz von  $L_{\text{SHIFT}}$ -Werten zugeordnet sind, werden in der **Fig. 18B** angeführt.

**[0096]** Wie in **Fig. 18B** angezeigt ist, reichen in einem bevorzugten Ausführungsbeispiel die  $L_{\text{SHIFT}}$ -Werte von 5 bis 8, was einem Schleifenbandbreitenbereich von zwischen 80 Hz bis 10 Hz entspricht.

**[0097]** Wiederum Bezug nehmend auf **Fig. 18A** wird der Phasenakkumulierer **484** in identischen Phaseninkrementen mit einer beispielhaften Rate von 320 kHz aktualisiert.

**[0098]** In einer beispielhaften Implementierung wird jedes festgelegte Phaseninkrement als 1/8 ausgewählt, was dazu führt, dass der Akkumulierer **484** von -1 bis +1 durchläuft, und zwar einmal für jedes Manchester-Symbol von 16 Taktzyklen bei 320 kHz. Der Phasenakkumulierer **484** wird im Allgemeinen so implementiert, dass er bei Überlauf von  $\pm 1$  umspringt (wrap).

**[0099]** Im Betrieb wird die DPLL der **Fig. 18A** so phasenverriegelt, dass die Nulldurchgänge **460** des Eingabesignals mit den Nulldurchgängen der  $\pm 1$  Ausgabe vom Phasenakkumulierer **484** zusammenfallen. Obwohl im Prinzip dieses in einem durchschnittlichen abgetasteten Phasenfehler von Null von dem Phasendetektor **480** resultiert, stellen verschiedene Faktoren (wie z. B. quantisierte Zeitauflösung und Signalrauschen) einen kontinuierlichen Schleifenbetrieb dadurch sicher, dass ein von Null verschiedener abgetaster Phasenfehler bewirkt wird. Als spezifisches Betriebsbeispiel wird der Fall angenommen, wo die  $\pm 1$  Signalübergänge von dem Phasenakkumulierer **484** die Nulldurchgänge **460** des Eingabesignals anführen bzw. vorweglaufen. In diesem Fall wird das resultierende positive Fehlersignal von dem nächsten 1/8 Phaseninkrement, das an den Subtrahierer **498** vorgesehen wird, subtrahiert, wodurch der Phasenvorlauf der Ausgabe des Akkumulierers **484** relativ zu den Eingabenulldurchgängen **460** reduziert wird.