(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4792691号

(P4792691)

(45) 発行日 平成23年10月12日(2011.10.12)

(24) 登録日 平成23年8月5日(2011.8.5)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 21/82  | (2006.01)    |

| HO 1 L 27/04  | (2006.01)    |

| HO 1 L 21/822 | (2006.01)    |

|               | HO 1 L 21/82 |

|               | HO 1 L 21/82 |

|               | HO 1 L 27/04 |

|               | B            |

|               | P            |

|               | A            |

請求項の数 9 (全 26 頁)

|            |                                     |

|------------|-------------------------------------|

| (21) 出願番号  | 特願2003-297107 (P2003-297107)        |

| (22) 出願日   | 平成15年8月21日 (2003.8.21)              |

| (62) 分割の表示 | 特願2001-141998 (P2001-141998)<br>の分割 |

| 原出願日       | 平成13年5月11日 (2001.5.11)              |

| (65) 公開番号  | 特開2004-6987 (P2004-6987A)           |

| (43) 公開日   | 平成16年1月8日 (2004.1.8)                |

| 審査請求日      | 平成20年5月2日 (2008.5.2)                |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (74) 代理人  | 100104710<br>弁理士 竹腰 昇                         |

| (74) 代理人  | 100124682<br>弁理士 黒田 泰                         |

| (74) 代理人  | 100090479<br>弁理士 井上 一                         |

| (74) 代理人  | 100090387<br>弁理士 布施 行夫                        |

| (74) 代理人  | 100090398<br>弁理士 大渕 美千栄                       |

最終頁に続く

(54) 【発明の名称】集積回路装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のマクロセルを含む集積回路装置であって、

バスを介してデータ転送を行う所与のインターフェース規格の物理層の回路を少なくとも含む第1のマクロセルと、

前記物理層よりも上位層の回路を含む第2のマクロセルとを含み、

前記第1のマクロセルの第1、第2の辺が交差する部分であるコーナ部分が、集積回路装置のコーナ部分に位置するように、前記第1のマクロセルが配置され、

前記第1のマクロセルは、

前記所与のインターフェース規格のバスに接続されるデータ端子であって差動信号を用いてデータを送受信するための第1のデータ端子及び第2のデータ端子に接続され、前記第1のデータ端子及び前記第2のデータ端子を介してデータを受信する受信回路と、

前記第1のデータ端子及び前記第2のデータ端子に接続され、前記第1のデータ端子及び前記第2のデータ端子を介してデータを送信する送信回路とを含み、

前記第1のマクロセルの前記第1の辺から対向する第3の辺へと向かう方向を第1の方向とし、前記第1のマクロセルの前記第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、

前記受信回路と送信回路は前記第2の方向に沿って配置され、

前記送信回路は、前記第1のデータ端子及び前記第2のデータ端子の前記第1の方向側であって、且つ、前記受信回路の前記第2の方向側に配置され、

10

20

前記送信回路と前記第1のデータ端子及び前記第2のデータ端子との間の第1の距離は、前記受信回路と前記第1のデータ端子及び前記第2のデータ端子との間の第2の距離よりも短いことを特徴とする集積回路装置。

**【請求項2】**

請求項1において、

前記送信回路は、

前記第1のデータ端子に接続される第1のN型トランジスタと、

前記第2のデータ端子に接続される第2のN型トランジスタと、

前記第1のN型トランジスタ、前記第2のN型トランジスタを介して前記第1のデータ端子、前記第2のデータ端子に定電流を流すための定電流源とを含み、

前記第1のN型トランジスタは、前記第1のデータ端子の前記第1の方向側に配置され、

前記第2のN型トランジスタは、前記第2のデータ端子の前記第1の方向側に配置されることを特徴とする集積回路装置。

**【請求項3】**

請求項2において、

送信期間以外の期間において前記定電流源からの定電流を流すための電源端子が設けられ、

前記送信回路は、

前記電源端子に接続される第3のN型トランジスタを含み、

前記送信期間以外の期間においては、前記定電流源からの定電流が前記第3のN型トランジスタを介して前記電源端子に流れることを特徴とする集積回路装置。

**【請求項4】**

請求項3において、

前記電源端子が、前記第1のデータ端子と前記第2のデータ端子の間に配置されることを特徴とする集積回路装置。

**【請求項5】**

請求項1乃至4のいずれかにおいて、

前記第1のデータ端子及び前記第2のデータ端子に接続され、前記第1のデータ端子及び前記第2のデータ端子を介して受信されるデータが有効か否かを検出する検出回路を含み、

前記検出回路は、

前記受信回路と前記送信回路の間に配置されることを特徴とする集積回路装置。

**【請求項6】**

請求項1乃至5のいずれかにおいて、

前記第1のマクロセルの前記第1の辺に沿って配置される第1のI/O領域に、前記所とのインターフェース規格のバスに接続される前記第1、第2のデータ端子が配置され、

前記第1のマクロセルの前記第2の辺に沿って配置される第2のI/O領域に、前記第1、第2のデータ端子を介したデータ転送のためのクロックを生成する回路の電源端子、及びクロック端子の少なくとも一方が配置されることを特徴とする集積回路装置。

**【請求項7】**

請求項1乃至6のいずれかにおいて、

前記第1のマクロセルが、配線及び回路セル配置が固定化されるマクロセルであり、

前記第2のマクロセルが、配線及び回路セル配置が自動配置配線されるマクロセルであることを特徴とする集積回路装置。

**【請求項8】**

請求項1乃至7のいずれかにおいて、

前記所とのインターフェース規格が、USB (Universal Serial Bus) 規格であることを特徴とする集積回路装置。

**【請求項9】**

10

20

30

40

50

請求項 1 乃至 8 のいずれかの集積回路装置と、

前記集積回路装置及び前記バスを介して転送されるデータの出力処理又は取り込み処理

又は記憶処理を行う装置と、

を含むことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路装置及び電子機器に関する。

【背景技術】

【0002】

近年、パーソナルコンピュータと周辺機器（広義には電子機器）とを接続するためのインターフェース規格として、USB (Universal Serial Bus)が注目を集めている。このUSBには、従来は別々の規格のコネクタで接続されていたマウスやキーボードやプリンタなどの周辺機器を、同じ規格のコネクタで接続できると共にいわゆるプラグ&プレイやホットプラグも実現できるという利点がある。

【0003】

一方、このUSBには、同じくシリアルバスインターフェース規格として脚光を浴びているIEEE 1394に比べて、転送速度が遅い。そこで、従来のUSB 1.1の規格に対する下位互換性を持ちながら、USB 1.1に比べて格段に高速な480Mbps (HSモード)のデータ転送速度を実現できるUSB 2.0規格が策定され、注目を浴びている。また、USB 2.0の物理層回路や、論理層回路の一部についてのインターフェース仕様を定義したUTMI (USB2.0 Transceiver Macrocell Interface)も策定されている。

【0004】

さて、このUSB 2.0では、従来のUSB 1.1で定義されていたFS (Full Speed)モードに加えて、HS (High Speed)モードと呼ばれる転送モードが用意されている。このHSモードでは480Mbpsでデータ転送が行われるため、12Mbpsでデータ転送が行われるFSモードに比べて格段に高速なデータ転送を実現できる。従って、USB 2.0によれば、高速な転送速度が要求されるハードディスクドライブや光ディスクドライブなどのストレージ機器に最適なインターフェースを提供できるようになる。

【0005】

しかしながら、USB 2.0では、小振幅の信号を、USB 1.1よりも格段に高速に送受信する必要がある。従って、この小振幅の信号を処理する物理層の回路には高性能が要求され、この物理層の回路を含むUTMI準拠のマクロセル（メガセル、マクロブロック）では、セル配置や配線についても手作業で行うことが望まれる。

【0006】

一方、UTMI準拠のマクロセルを含む集積回路装置には、SIE (Serial Interface Engine) やユーザロジックなどの論理層の回路が組み込まれ、この論理層の回路の構成や規模は、集積回路装置を使用するユーザに応じて異なるものになる。従って、このようなマクロセルを含む集積回路装置の設計や製造においては、物理層の回路の高性能を維持しながら、多様なユーザの要望に応えなければならないという技術的課題がある。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、物理層の回路の高性能を維持しながら、種々の構成の上層の回路を組み込むことができる集積回路装置及びこれを用いた電子機器を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために本発明に係る集積回路装置は、複数のマクロセルを含む集積

10

20

30

40

50

回路装置であって、バスを介してデータ転送を行う所与のインターフェース規格の物理層の回路を少なくとも含む第1のマクロセルと、前記物理層よりも上位層の回路を含む第2のマクロセルとを含み、前記第1のマクロセルの第1、第2の辺が交差する部分であるコーナ部分が、集積回路装置のコーナ部分に位置するように、前記第1のマクロセルが配置されることを特徴とする。

【0009】

本発明では、物理層（例えば最下位層）の回路を含む第1のマクロセルのコーナ部分が集積回路装置のコーナ部分に位置するように（コーナ部分が略一致する場合も含む）、第1のマクロセルが配置される。そして、例えば第1のマクロセルとは異なる配置領域に、物理層よりも上位層の回路を含む第2のマクロセルが配置される。このようにすれば、第1のマクロセルが含む物理層の回路の高性能を維持しながら、種々の構成の上位層回路を第2のマクロセルとして集積回路装置に組み込むことが可能となる。

【0010】

なお、第1のマクロセルに上位層の回路の一部を含ませてもよい。また、集積回路装置に、第1、第2のマクロセル以外のマクロセルを含ませることもできる。

【0011】

また本発明は、前記第1のマクロセルの前記第1の辺に沿って配置される第1のI/O領域に、前記所与のインターフェース規格のバスに接続されるデータ端子が配置され、前記第1のマクロセルの前記第2の辺に沿って配置される第2のI/O領域に、前記データ端子を介したデータ転送のためのクロックを生成する回路の電源端子、及びクロック端子の少なくとも一方が配置されることを特徴とする。

【0012】

このようにすれば、例えば、第1の辺から第3の辺に向かって流れるデータを、第2の辺から第4の辺に向かって入力されるクロックを利用してサンプリングすることなどが可能となり、無駄の無い合理的なデータ転送を実現できる。

【0013】

また本発明は、前記第1のマクロセルの前記第1の辺に対向する第3の辺又は前記第2の辺に対向する第4の辺の少なくとも一方に沿って、前記第1、第2のマクロセル間で信号をやり取りするためのインターフェース領域が設けられていることを特徴とする。

【0014】

このようにすれば、例えば、第1、第2のマクロセル間でやり取りされる信号の遅延や受け渡しタイミングを適正な範囲に收めることを、容易化できる。

【0015】

なお、インターフェース領域には、第1のマクロセルからの信号を第2のマクロセルに伝えるためのバッファや、第2のマクロセルからの信号を第1のマクロセルに伝えるためのバッファなどを含ませることができる。

【0016】

また本発明は、前記第1のマクロセルが、前記所与のインターフェース規格のバスに接続されるデータ端子に接続され、前記データ端子を介してデータを受信する受信回路と、所与の周波数のクロックを生成するクロック生成回路と、前記クロック生成回路により生成されたクロックに基づいて、前記データ端子を介して転送されるデータのサンプリングクロックを生成するサンプリングクロック生成回路とを含み、前記第1のマクロセルの前記第1の辺から対向する第3の辺へと向かう方向を第1の方向とした場合に、前記第1の辺に沿って配置される第1のI/O領域の前記第1の方向側に、前記受信回路が配置され、前記第1のマクロセルの前記第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記第2の辺に沿って配置される第2のI/O領域の前記第2の方向側に、前記クロック生成回路が配置され、前記受信回路の前記第1の方向側であり前記クロック生成回路の前記第2の方向側に、前記サンプリングクロック生成回路が配置されることを特徴とする。

【0017】

10

20

30

40

50

このようにすれば、受信回路とサンプリングクロック生成回路との間の距離や、クロック生成回路とサンプリングクロック生成回路との間の距離を短くできるようになり、配線の寄生容量や寄生抵抗が回路動作に与える悪影響を軽減できる。

【0018】

なお、サンプリングクロック生成回路を、第1の方向において受信回路に隣接し、第2の方向においてクロック生成回路に隣接するように配置してもよい。

【0019】

また本発明は、前記クロック生成回路が、周波数が同一で位相が互いに異なる第1～第Nのクロックを生成し、前記サンプリングクロック生成回路が、生成された第1～第Nのクロックのエッジの中のいずれのエッジ間にデータのエッジがあるかを検出するエッジ検出回路と、前記エッジ検出回路でのエッジ検出情報に基づいて、前記第1～第Nのクロックの中からいずれかのクロックを選択し、選択したクロックを前記サンプリングクロックとして出力するクロック選択回路とを含むことを特徴とする。

10

【0020】

本発明によれば、多相の第1～第Nのクロックのエッジの中のいずれのエッジ間にデータのエッジがあるのかが検出される。例えば、データのエッジが、第1、第2のクロックのエッジ間にあるのか、第2、第3のクロックのエッジ間にあるのか等が検出される。そして、得られたエッジ検出情報（どのクロックのエッジ間にデータのエッジがあるのかを示す情報）に基づいて、第1～第Nのクロックの中からいずれかのクロックが選択され、そのクロックがサンプリングクロックとして出力される。

20

【0021】

このように本発明によれば、エッジ検出情報に基づいて第1～第Nのクロックの中からクロックを選択するという簡素な構成で、データのサンプリングクロックを生成できる。従って、高速なクロックに同期して入力されるデータであっても、そのデータをサンプリングするための適正なサンプリングクロックを、小規模な回路構成で生成できるようになる。

【0022】

また本発明は、前記クロック生成回路に電源を供給する第1の電源端子と、前記サンプリングクロック生成回路に電源を供給する第2の電源端子とが、前記第2のI/O領域に配置され、前記クロック生成回路が、前記第2の方向において前記第1の電源端子に隣接して配置され、前記第2の電源端子の高電位側の電源端子に一端が接続され低電位側の電源端子に他端が接続されるキャパシタ素子の領域が、前記第2の方向において前記第2の電源端子に隣接して配置されることを特徴とする。

30

【0023】

このようにすれば、第1の電源端子とクロック生成回路との間の電源配線の長さを短くできるため、電源の電圧ドロップを最小限に抑えることが可能になる。

【0024】

また、第1の電源端子の電源電圧変動を、第1の電源端子に近い場所で効果的に安定化できるようになり、サンプリングクロック生成回路などの回路の安定動作を保証できるようになる。

40

【0025】

また本発明は、前記第1のマクロセルが、前記所与のインターフェース規格のバスに接続されるデータ端子に接続され、前記データ端子を介してデータを受信する受信回路と、前記データ端子に接続され、前記データ端子を介して受信されるデータが有効か否かを検出する検出回路とを含み、前記第1のマクロセルの前記第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記受信回路と前記検出回路とが、前記第2の方向において隣接して配置されることを特徴とする。

【0026】

このようにすれば、誤った受信データが後段の回路に伝えられたりするなどの不具合を効果的に防止でき、安定した回路動作を実現できる。

50

**【 0 0 2 7 】**

また本発明は、前記第1のマクロセルが、前記所与のインターフェース規格のバスに接続されるデータ端子に接続され、前記データ端子を介してデータを受信する受信回路と、前記データ端子に接続され、前記データ端子を介してデータを送信する送信回路とを含み、前記第1のマクロセルの前記第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記送信回路が、前記受信回路の前記第2の方向側に配置されることを特徴とする。

**【 0 0 2 8 】**

このようにすれば、例えば、受信データのサンプリングに使用されるクロックの経路等を短くできる一方で、そのクロックの経路と送信データの経路とが重なってしまうなどの事態を防止できる。

10

**【 0 0 2 9 】**

また本発明は、前記第1のマクロセルが、前記所与のインターフェース規格のバスに接続されるデータ端子に接続され、前記データ端子を介してデータを受信する受信回路と、前記データ端子に接続され、前記データ端子を介してデータを送信する送信回路とを含み、前記第1のマクロセルの前記第1の辺から対向する第3の辺へと向かう方向を第1の方向とした場合に、前記送信回路と前記データ端子とが、前記第1の方向において隣接して配置されることを特徴とする。

**【 0 0 3 0 】**

このようにすれば、送信回路とデータ端子との距離を短くできるようになり、データ端子の配線経路に寄生する抵抗・容量・インダクタンスが回路動作に与える悪影響等を最小限に抑えることができる。

20

**【 0 0 3 1 】**

また本発明は、前記第1のマクロセルが、配線及び回路セル配置が固定化されるマクロセルであり、前記第2のマクロセルが、配線及び回路セル配置が自動配置配線されるマクロセルであることを特徴とする。

**【 0 0 3 2 】**

このようにすれば、第1のマクロセルが含む物理層の高性能を維持しながら、自動配置配線を用いて種々の構成の回路を、第2のマクロセルとして集積回路装置に組み込むことが可能になる。

30

**【 0 0 3 3 】**

また本発明は、前記所与のインターフェース規格が、U S B (Universal Serial Bus) 規格であることを特徴とする。

**【 0 0 3 4 】**

この場合に所与のインターフェース規格として、U S B 2 . 0 規格やU S B 2 . 0 規格を更に発展させた規格を用いることができる。

**【 0 0 3 5 】**

また本発明に係る電子機器は、上記のいずれかの集積回路装置と、前記集積回路装置及び前記バスを介して転送されるデータの出力処理又は取り込み処理又は記憶処理を行う装置とを含むことを特徴とする。

40

**【 0 0 3 6 】**

このようにすれば、高性能な物理層の回路を含む集積回路装置を電子機器に組み込むことができるため、電子機器の性能を向上できる。一方、第2のマクロセルの回路構成を変えることで、種々の回路構成の集積回路装置を電子機器に組み込むことが可能となり、多様なユーザの要望に応えることができる。

**【発明を実施するための最良の形態】****【 0 0 3 7 】**

以下、本発明の実施形態について図面を用いて詳細に説明する。

**【 0 0 3 8 】**

なお、以下に説明する本実施形態は、特許請求の範囲に記載された本発明の内容を何ら

50

限定するものではない。また本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

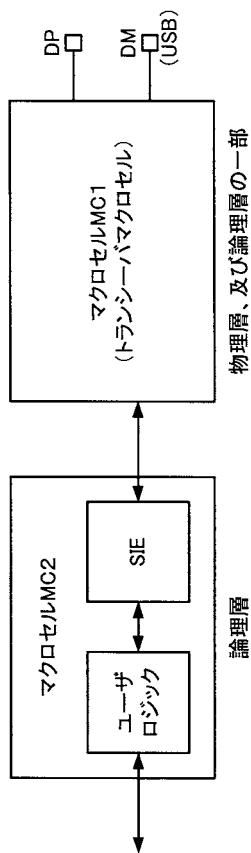

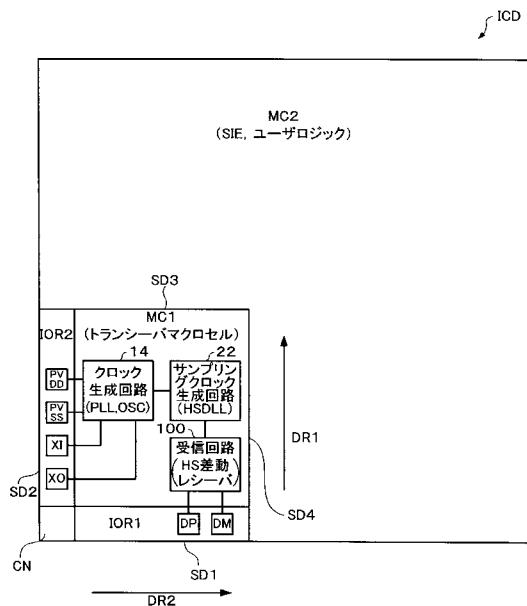

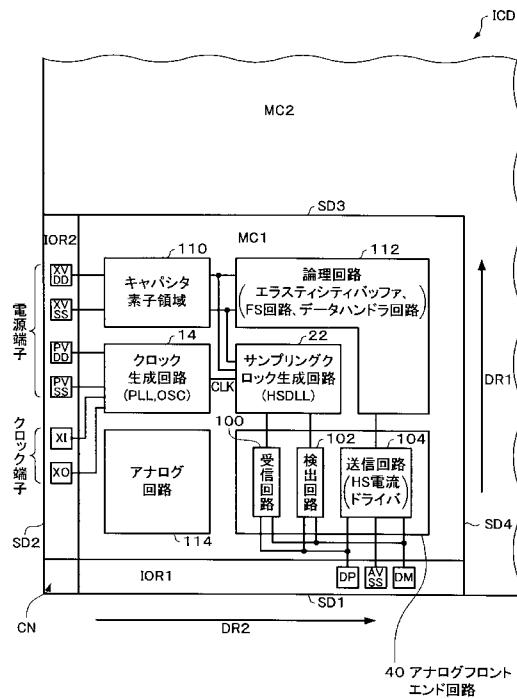

【0039】

1. 回路構成

図1に示すように本実施形態の集積回路装置（データ転送制御装置）は、マクロセルMC1（第1のマクロセル）とマクロセルMC2（第2のマクロセル）を含む。なお、これらのマクロセルMC1、MC2（メガセル、マクロブロック）は、論理機能を有する中規模又は大規模な回路の単位である。また、本実施形態の集積回路装置は3個以上のマクロセルを含むようにしてもよい。

【0040】

図1においてMC1は、バス（例えばシリアルバス）を介してデータ転送を行うインターフェース規格（例えばUSB又はIEEE1394等）の物理層の回路を少なくとも含むマクロセルである。USB2.0（或いはUSB2.0を発展させた規格）を例にとれば、MC1として、UTMI（USB2.0 Transceiver Macrocell Interface）の仕様に準拠したトランシーバマクロセルを用いることができる。この場合には、MC1は、物理層回路、及び論理層回路の一部を含むことになる。

10

【0041】

一方、MC2は、物理層よりも上位層（論理層、プロトコル層又はアプリケーション層等）の回路を含むマクロセルである。USB2.0を例にとれば、MC2は、SIE（Serial Interface Engine）やユーザロジック（デバイス固有の回路）などの論理層回路（MC1が含む論理層回路の他の部分）を含むことになる。

20

【0042】

なお、図1において、MC1として、物理層の回路のみを含むマクロセルを用いてよい。また、MC2は、少なくとも物理層よりも上位の層の回路を含むものであればよい。

【0043】

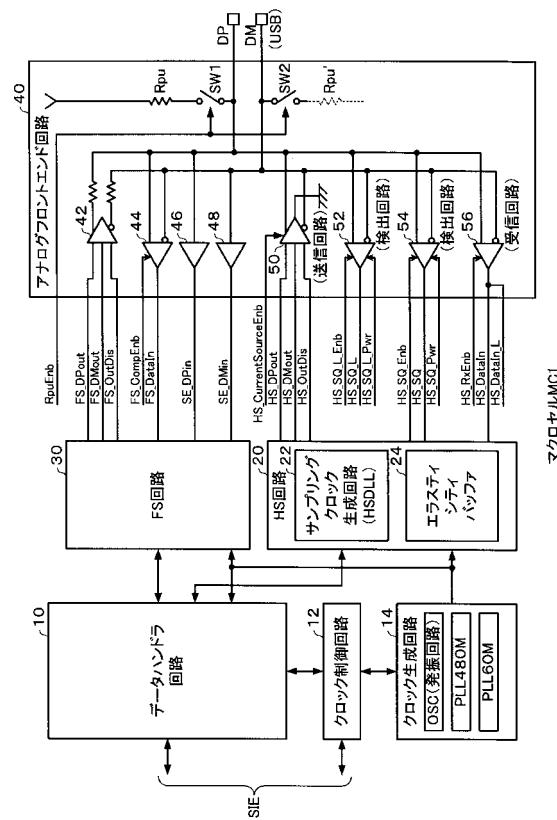

図2に、マクロセルMC1の回路構成の一例を示す。

【0044】

マクロセルMC1（第1のマクロセル）は、データハンドラ回路10、クロック制御回路12、クロック生成回路14、HS（High Speed）回路20、FS（Full Speed）回路30を含む。これらの回路は論理層回路である。また、MC1は、物理層回路であるアナログフロントエンド回路40（送受信回路）を含む。なお、マクロセルMC1は、図2に示す回路ブロックの全てを含む必要はなく、それらの一部を省略する構成としてもよい。

30

【0045】

データハンドラ回路10（広義には、データ転送を行うための所与の回路）は、USB2.0に準拠したデータ転送のための種々の処理を行う。より具体的には、送信時には、送信データにSYNC（SYNChronization）、SOP（Start Of Packet）、EOP（End Of Packet）を附加する処理や、ビットスタッフィング処理等を行う。一方、受信時には、受信データのSYNC、SOP、EOPを検出し、削除する処理や、ビットアンスタッフィング処理などを行う。更に、データハンドラ回路10は、データの送受信を制御するための各種のタイミング信号を生成する処理も行う。

40

【0046】

なお、受信データはデータハンドラ回路10から後段の回路であるSIE（Serial Interface Engine）に出力され、送信データはSIEからデータハンドラ回路10に入力されることになる。そして、このSIEは、USBパケットIDやアドレスを識別するためのSIE制御ロジックと、エンドポイント番号の識別や FIFO制御などのエンドポイント処理を行うためのエンドポイントロジックとを含む。

【0047】

クロック制御回路12は、SIEからの各種の制御信号を受け、クロック生成回路14を制御する処理などを行う。

【0048】

50

クロック生成回路 14 は、装置内部で使用する 480 MHz のクロックや、装置内部及び SIE で使用する 60 MHz のクロックを生成する回路であり、OSC、PLL480M、PLL60M を含む。

【0049】

ここで OSC (発振回路) は、例えば外部振動子との組み合わせによりベースクロックを生成する。

【0050】

PLL480M は、OSC (発振回路) で生成されたベースクロックに基づいて、HS (High Speed) モードで必要な 480 MHz のクロックと、FS (Full Speed) モード、装置内部及び SIE で必要な 60 MHz のクロックを生成する PLL (Phase Locked Loop) である。

10

【0051】

PLL60M は、OSC (発振回路) で生成されたベースクロックに基づいて、FS モード、装置内部及び SIE で必要な 60 MHz のクロックを生成する。

【0052】

HS 回路 20 は、データ転送速度が 480 Mbps となる HS モードでのデータの送受信を行うためのロジック回路であり、FS 回路 30 は、データ転送速度が 12 Mbps となる FS モードでのデータの送受信を行うためのロジック回路である。

【0053】

HS 回路 20 は、サンプリングクロック生成回路 22 (HSDL L。High Speed Delay Line PLL)、エラスティシティバッファ (elasticity buffer) 24 を含む。

20

【0054】

ここで、サンプリングクロック生成回路 22 は、クロック生成回路 14 によって生成されたクロックと、受信データとに基づいて、受信データのサンプリングクロックを生成する。

【0055】

また、エラスティシティバッファ 24 は、装置内部と、外部装置 (バスに接続される外部装置) とのクロック周波数差 (クロックドリフト) 等を吸収するための回路である。

【0056】

アナログフロントエンド回路 40 (送受信回路) は、FS や HS モードでの送受信を行うためのドライバやレシーバを含むアナログ回路である。USB では、データ端子 DP (Data+) 及び DM (Data-) を用いた差動信号によりデータを送受信する。

30

【0057】

USB 2.0 では、HS モード (広義には、第 1 のモード) と FS モード (広義には、第 2 のモード) が、転送モードとして定義されている。HS モードは、USB 2.0 により新たに定義された転送モードである。FS モードは、従来の USB 1.1 で既に定義されている転送モードである。

【0058】

このため、本実施形態の集積回路装置では、アナログフロントエンド回路 40 が、HS モードでの送受信を行うための HS モード用ドライバ及びレシーバと、FS モードで送受信を行うための FS モード用ドライバ及びレシーバを含む。

40

【0059】

より具体的には、アナログフロントエンド回路 40 は、FS ドライバ 42、FS 差動レシーバ 44、シングルエンド (Single ended) DP レシーバ 46、シングルエンド DM レシーバ 48、HS 電流ドライバ 50 (送信回路)、低速用スケルチ (Squelch) 回路 52 (検出回路)、高速用スケルチ回路 54 (検出回路)、HS 差動レシーバ 56 (受信回路) を含む。

【0060】

FS ドライバ 42 は、FS モードにおいて、FS 回路 30 からの FS\_DPo ut 及び FS\_DMout からなる差動信号を、データ端子 DP、DM を用いて差動出力する。

50

のFSドライバ42は、FS回路30からのFS\_Out\_Disにより出力制御される。

【0061】

FS差動レシーバ44は、FSモードにおいて、DP、DMを介して入力される差動信号を増幅し、FS\_DataInとしてFS回路30に対して出力する。このFS差動レシーバ44は、FS\_CompEnbにより増幅制御される。

【0062】

シングルエンドDPレシーバ46は、FSモードにおいて、DPを介して入力されるシングルエンドの信号を増幅し、SE\_DPinとしてFS回路30に対して出力する。

【0063】

シングルエンドDMレシーバ48は、FSモードにおいて、DMを介して入力されるシングルエンドの信号を増幅し、SE\_DMInとしてFS回路30に対して出力する。

【0064】

HS電流ドライバ50（送信回路）は、HSモードにおいて、HS回路20からのHS\_DPut及びHS\_DMoutからなる差動の入力信号を増幅し、DP、DMを介して出力する。即ち、HS電流ドライバ50は、DP又はDMの信号ラインを一定の電流値でドライブすることにより、J（DPが400mV、DMが0V）或いはK（DPが0V、DMが400mV）の状態を生成する。このHS電流ドライバ50は、HS回路20からのHS\_Out\_Disにより出力制御されると共に、HS\_CurrentSourceEnbにより駆動電流の制御が行われる。

【0065】

低速用スケルチ回路52（検出回路。低速用トランスマッショントンベロープ・ディテクタ）は、FSモードにおいて、DP、DMを介して入力される差動信号（データの有無）を検出し、HS\_SQ\_Lとして出力する。即ち、データとノイズを区別して検出する。この低速用スケルチ回路52は、HS\_SQ\_L\_Enbにより動作制御され、HS\_SQ\_L\_Pwrにより省電力制御される。

【0066】

高速用スケルチ回路54（検出回路。高速用トランスマッショントンベロープ・ディテクタ）は、HSモードにおいて、DP、DMを介して入力される差動信号（データの有無）を検出し、HS\_SQとしてHS回路20に対して出力する。即ち、データとノイズを区別して検出する。この高速用HS\_SQ回路54は、HS回路20からのHS\_SQ\_Enbにより動作制御され、HS\_SQ\_Pwrにより省電力制御される。

【0067】

HS差動レシーバ56（受信回路）は、HSモードにおいて、DP、DMを介して入力される差動信号を増幅し、HS\_DataIn、HS\_DataIn\_Lを出力する。即ち、HSモードにおいて、DP、DMのラインがJ或いはKのいずれの状態なのかを検出する。このHS差動レシーバ56は、HS\_RXEnbにより増幅制御される。

【0068】

差動のデータ端子のうちのDPは、スイッチ素子（トランジスタ）SW1及びプルアップ抵抗RpUを介して、高電位側の電源電圧（例えば3.3V）と接続される。また、差動のデータ端子のうちのDMは、スイッチ素子SW2に接続される。これらのSW1、SW2は、RpUEnbにより制御される。即ち、RpUEnbをアクティブにして、SW1及びRpUを介してDPをプルアップすることで、HSデバイスをFSデバイスとして使用できるようになる。

【0069】

なお本実施形態では、DP、DM間での負荷バランスを保つために、DMについても、SW2を介してダミーの抵抗RpU'が接続されている。

【0070】

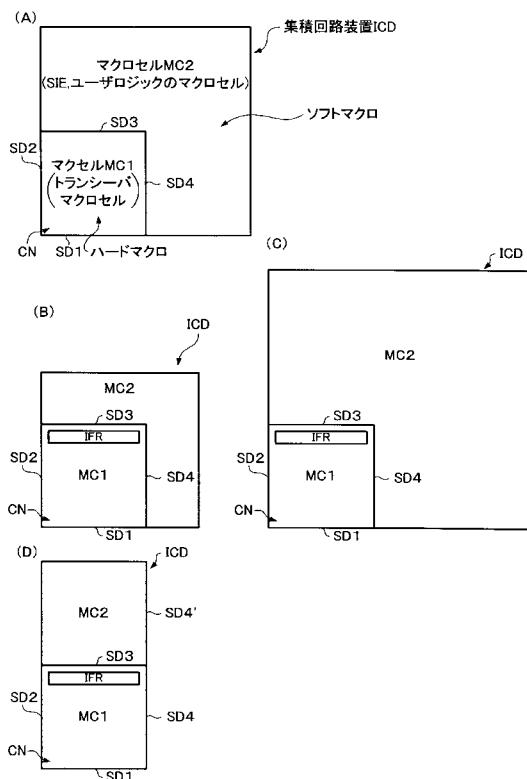

2. マクロセルの配置

本実施形態では図3（A）に示すように、マクロセルMC1（第1のマクロセル。トランシーバマクロ）の辺SD1、SD2（第1、第2の辺）の交差部分であるコーナ部分C

10

20

30

40

50

Nが、集積回路装置ICD（半導体チップ）のコーナ部分に一致（ほぼ一致する場合も含む）するように、MC1を配置している。そして、マクロセルMC1の配置領域以外の領域に、マクロセルMC2（第2のマクロセル。SIE、ユーザロジックのマクロセル）を配置している。

【0071】

ここで、図3(A)において、MC1は、配線及び回路セル配置が固定化されるハードマクロになっている。より具体的には、例えば、配線や回路セル配置が手作業のレイアウトにより行われる（配線、配置の一部を自動化してもよい）。

【0072】

一方、MC2は、配線及び回路セル配置が自動配置配線されるソフトマクロになっている。より具体的には、例えば、ゲートアレイの自動配置配線ツールにより基本セル間の配線等が自動的に行われる（配置、配線の一部を固定化してもよい）。

【0073】

マクロセルMC1は、図2に示すように、微少信号で高速に動作することが要求されるアナログフロントエンド回路40や、480MHzで動作することが要求されるHS回路20や、480MHzのクロックを生成することが要求されるクロック生成回路14などを含む。従って、マクロセルMC1のこれらの回路の配置、配線を、ゲートアレイなどで用いられている自動配置配線ツールで行うと、マクロセルMC1の高性能を維持できない。従って、マクロセルMC1での回路セルの配置、配線は、手作業のレイアウトで行うことが望ましい。

【0074】

一方、マクロセルMC2は、物理層回路（アナログフロントエンド回路）を含まず、マクロセルMC1ほどには高速な動作が要求されない。そして、マクロセルMC2の回路構成は、集積回路装置を使用するユーザの要望や集積回路装置が組み込まれる電子機器の用途に応じて多様に変化する。従って、マクロセルMC2での回路セルの配置、配線は、自動配置配線ツールにより行うことが望ましい。

【0075】

そこで本実施形態では、図3(A)に示すように、マクロセルMC1のコーナ部分CNが、集積回路装置ICDのコーナ部分に位置するように、MC1を配置している。このようにすれば、例えば、マクロセルMC2の回路の構成や規模が変化した場合にも、これに容易に対処できるようになる。

【0076】

例えば、マクロセルMC2の回路が小規模の場合には、MC1、MC2を図3(B)に示すように配置すればよく、MC2の回路が大規模の場合には、MC1、MC2を図3(C)に示すように配置すればよい。

【0077】

そして、この場合に本実施形態では、集積回路装置ICDのコーナにマクロセルMC1が配置されているため、マクロセルMC2の回路構成や規模がユーザの要望に応じて変化しても、マクロセルMC1のコア内での回路セルの配置、配線やI/O領域での端子（パッド）の配置をほぼ固定化できる。従って、多様なユーザの要望に応えながらも、マクロセルMC1の高性能を維持できる。

【0078】

また本実施形態では、集積回路装置ICDのコーナにマクロセルMC1を固定配置しているため、図3(B)、(C)に示すように、マクロセルMC1、MC2間でデータをやり取りするためのインターフェース領域IFR（信号をバッファリングするためのバッファが配置される領域）についても、辺SD1に対向する辺SD3（或いは辺SD2に対向する辺SD4）の場所に固定配置できるようになる。ここで、インターフェース領域IFRとは、マクロセルMC1からの信号をバッファリングしてマクロセルMC2に出力するバッファや、MC2からの信号をバッファリングしてMC1に入力するバッファなどを含む領域である。

10

20

30

40

50

## 【0079】

このようにインターフェース領域 IFR を固定配置することで、マクロセル MC1、MC2 間でやり取りされる信号の遅延や受け渡しタイミングを許容範囲内に收めることができ、容易になり、マクロセル MC2 の回路構成や規模が変化した場合にも、安定した回路動作を保証できるようになる。

## 【0080】

即ち、インターフェース領域 IFR の場所が固定化されていれば、マクロセル MC1、MC2 間の信号線の寄生容量を容易に見積もることが可能になる。従って、これらの信号線の寄生容量が許容範囲内に収まるように設定して、ソフトマクロであるマクロセル MC2 の自動配置配線を行うことが可能になり、信号タイミングの設計を容易化できる。

10

## 【0081】

なお、信号タイミングの設計を更に容易化するために、マクロセル MC2 側のインターフェース領域（バッファ領域）についても、マクロセル MC1 側のインターフェース領域 IFR に隣接した領域（辺 SD3 に沿った領域）に固定配置することが望ましい。

## 【0082】

また本実施形態では、図 3 (D) に示すようにマクロセル MC1、MC2 を配置してもよい。即ち、図 3 (A)、(B)、(C) ではマクロセル MC1 の辺 SD4（第 4 の辺）の右側（第 2 の方向側）にマクロセル MC2 の領域が存在するが、図 3 (D) では存在しない。即ち、マクロセル MC2 の辺 SD4'（第 4 の辺）の位置に、マクロセル MC1 の辺 SD4（第 4 の辺）が位置している。図 3 (D) の配置は、マクロセル MC1 の回路規模が小さい場合や端子数が少ない場合に、有効である。

20

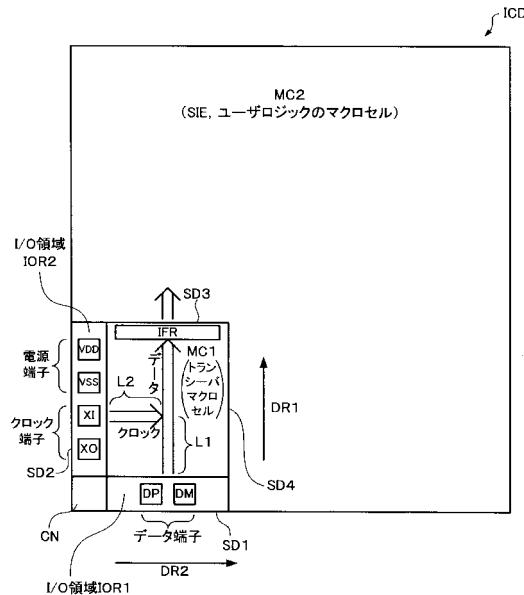

## 【0083】

## 3. データ端子、電源端子、クロック端子の配置

本実施形態では図 4 に示すように、マクロセル MC1 の辺 SD1（第 1 の辺）に沿った I/O 領域 IOR1（第 1 の I/O 領域）に、データ端子 DP、DM（パッド）を配置し、辺 SD2（第 2 の辺）に沿った I/O 領域 IOR2 に、電源端子 VDD、VSS やクロック端子 XI、XO を配置している。

## 【0084】

ここで、DP、DM は USB のバスに接続されるデータ端子である。USB では、これらの差動のデータ端子 DP、DM を用いてデータの送受信が行われる。

30

## 【0085】

また、VDD、VSS (PVDD、PVSS、XVDD、XVSS) は、DP、DM を介したデータ転送のためのクロックを生成する回路（例えば図 2 のクロック生成回路 14 又はサンプリングクロック生成回路 22 等）の電源端子であり、XI、XO はクロック端子である。例えば、図 2 のクロック生成回路 14 やサンプリングクロック生成回路 22 は、これらの電源端子 VDD、VSS から供給される電源により動作する。また、XI、XO は、各々、図 2 の発振回路 OSC の入力端子、出力端子である。なお、外部クロックを XI を介して入力するようにしてもよい。

## 【0086】

このように、DP、DM を辺 SD1 に沿った IOR1 に配置し、VDD、VSS、XI、XO を辺 SD2 に沿った IOR2 に配置すれば、方向 DR1（辺 SD1 から対向する辺 SD3 へと向かう第 1 の方向）に沿って流れるデータを、方向 DR2（辺 SD2 から対向する辺 SD4 へと向かう第 2 の方向）に沿って入力されるクロックを利用してサンプリングすることが可能となる。そして、サンプリングされたデータを、辺 SD3 に沿った領域であるインターフェース領域 IFR を介してマクロセル MC2 に出力できる。これにより、無駄の無い合理的なデータ転送を実現できる。

40

## 【0087】

特に、USB 2.0 の HS モードでのサンプリングクロックの周波数は 480MHz であり、非常に高速である。従って、クロックスキュー等を引き起こさないためには、DP、DM を介して受信されたデータをなるべく早い段階でサンプリングすることが望ましい

50

。

## 【0088】

本実施形態では図4に示すように、集積回路装置ICDのコーナにマクロセルMC1を配置し、辺SD1に沿ったIOR1にDP、DMを配置し、辺SD2に沿ったIOR2にサンプリングクロック生成のためのVDD、VSS、XI、XOを配置している。従って、データがサンプリングされる場所までの距離である図4のL1、L2を短くすることが可能になり、DP、DMを介して入力されたデータを早い段階でサンプリングできるようになる。これにより、USB2.0のHSモードのように周波数の速い転送モードにおいても、受信エラーの発生を効果的に防止できる。

## 【0089】

10

なお、インターフェース領域IFRは、辺SD4に沿った方向に配置してもよいが、データの流れる方向がDR1であることを考慮すると、辺SD3に沿った方向にIFRを配置することが望ましい。

## 【0090】

## 4. クロック生成回路等の配置

本実施形態では図5に示すように、I/O領域IOR1のDR1側（辺SD1からSD3へと向かう第1の方向側）に、受信回路100（図2のHS差動レシーバ56）を配置している。

## 【0091】

20

また、I/O領域IOR2のDR2側（辺SD2から対向する辺SD4に向かう第2の方向側）に、図2のクロック生成回路14を配置している。

## 【0092】

そして、受信回路100のDR1側（上側）であり、クロック生成回路14のDR2側（右側）に、サンプリングクロック生成回路22を配置している。

## 【0093】

30

図5に示すような配置にすれば、受信回路100とサンプリングクロック生成回路22の間の距離を短くできる。従って、受信回路100とサンプリングクロック生成回路22を結ぶ配線の長さを短くでき、DP、DMを介して受信回路100により受信されるデータの配線に不要な容量が寄生するのを防止できる。この結果、データの立ち上がり・立ち下がり波形になまりが生るのを防止できると共に、受信回路100からのデータを少ない信号遅延でサンプリングクロック生成回路22に伝えることが可能になる。

## 【0094】

また図5に示すような配置にすれば、クロック生成回路14とサンプリングクロック生成回路22の間の距離も短くできる。従って、クロック生成回路14とサンプリングクロック生成回路22を結ぶ配線の長さを短くでき、クロック生成回路14で生成された高周波数（480MHz）のクロック（周波数が同一で位相が異なる多相の第1～第Nのクロック）の配線に不要な容量が寄生するのを防止できる。この結果、クロック信号の立ち上がり・立ち下がり波形になまりが生じたり、多相のクロック間に信号遅延差が生じたりするなどの事態を防止できる。

## 【0095】

40

そして、このように受信回路100とサンプリングクロック生成回路22の間の距離やクロック生成回路14とサンプリングクロック生成回路22の間の距離を短くすることで、USB2.0のHSモードで要求されるような高周波数のサンプリングクロックを生成する回路を、最新の半導体プロセスを用いなくても、実現することが可能になる。

## 【0096】

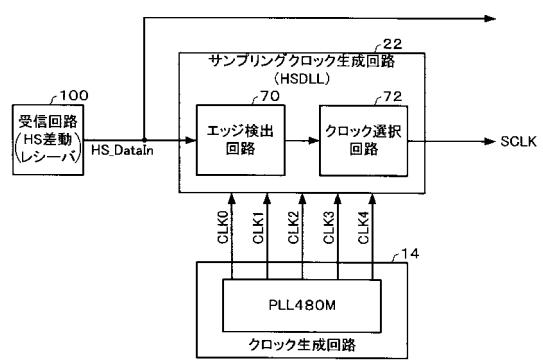

図6に、本実施形態のサンプリングクロック生成回路22（HSDL回）の構成例を示す。

## 【0097】

クロック生成回路14が含むPLL480Mは、周波数が同一で位相が互いに異なるクロックCLK0、CLK1、CLK2、CLK3、CLK4（広義には第1～第Nのクロ

50

ック)を出力する。より具体的には、PLL480MのVCO(発振周波数が可変に制御される発振手段)が含む5個の差動出力コンパレータ(広義には奇数段の第1~第Nの反転回路)の出力が、クロックCLK0~4として用いられることになる。

#### 【0098】

サンプリングクロック生成回路22はエッジ検出回路70、クロック選択回路72を含む。そして、このエッジ検出回路70は、受信回路100(図2のHS差動レシーバ56)から入力されるデータのエッジを検出し、そのエッジ検出情報をクロック選択回路72に出力する。

#### 【0099】

より具体的には、PLL480MからのCLK0~4のエッジ(立ち上がり又は立ち下がりエッジ)の中のいずれのエッジ間にデータHS\_DataInのエッジがあるかを検出し、そのエッジ検出情報をクロック選択回路72に出力する。 10

#### 【0100】

すると、クロック選択回路72は、このエッジ検出情報に基づいて、クロックCLK0~4の中からいずれかのクロックを選択し、選択したクロックをサンプリングクロックSCLKとして後段のエラスティシティバッファ24に出力する。

#### 【0101】

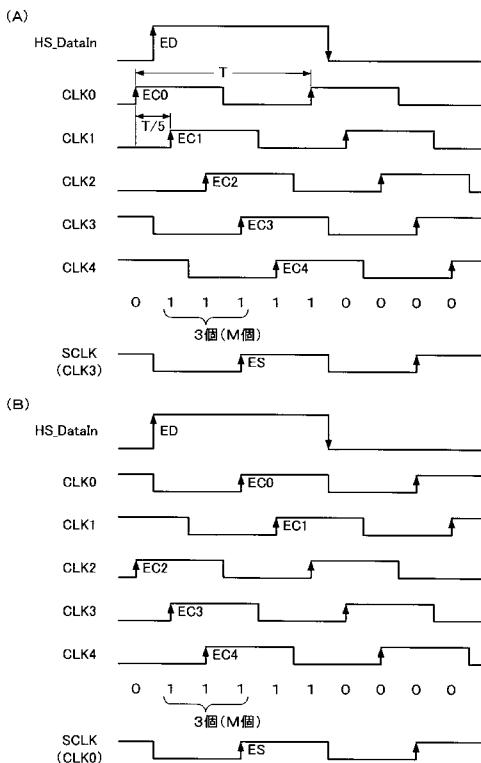

図7(A)、(B)にサンプリングクロック生成回路22の動作を説明するためのタイミング波形図を示す。

#### 【0102】

図7(A)、(B)に示すように、CLK0~4は周波数が同一の480MHzとなるクロックである。また、クロックの周期をTとした場合に、各クロック間の位相がT/5(広義にはT/N)だけシフトしている。 20

#### 【0103】

そして図7(A)では、サンプリング対象となるHS\_DataIn(受信データ)のエッジEDが、クロックCLK0とCLK1の間にあることが図6のエッジ検出回路70により検出される。すると、HS\_DataInのエッジEDから例えば3個(広義には設定数M個)だけずれたエッジEC3を有するクロックCLK3が図6のクロック選択回路72により選択され、この選択されたCLK3が、HS\_DataInのサンプリングクロックSCLKとして後段の回路(エラスティシティバッファ24)に出力される。 30

#### 【0104】

一方、図7(B)では、HS\_DataInのエッジEDが、CLK2とCLK3の間にあることがエッジ検出回路70により検出される。すると、HS\_DataInのエッジEDから例えば3個(広義には設定数M個)だけずれたエッジEC0を有するクロックCLK0がクロック選択回路72により選択され、この選択されたCLK0が、HS\_DataInのサンプリングクロックSCLKとして後段の回路(エラスティシティバッファ24)に出力される。

#### 【0105】

このように本実施形態のサンプリングクロック生成回路22によれば、HS\_DataInのエッジEDを検出し、得られたエッジ検出情報に基づいてCLK0~CLK4からクロックを選択するという簡素な構成で、HS\_DataInのサンプリングクロックSCLKを生成できる。従って、USB2.0のHSモードのように、HS\_DataInが外部装置の480MHzに同期する高速な転送データである場合にも、このHS\_DataInを適正にサンプリングできるクロックSCLKを生成できる。 40

#### 【0106】

また本実施形態によれば、図7(A)、(B)に示すように、生成されたサンプリングクロックSCLKのエッジESをHS\_DataInのエッジ間の真ん中付近に位置させることができる。従って、後段の回路(エラスティシティバッファ24)は、データの保持のためのセットアップタイムやホールドタイムを十分に確保できるようになり、データ受信の信頼性を格段に高めることができる。 50

## 【0107】

また本実施形態によれば、HS\_DataInのエッジ検出やSCLKの生成のために使用する5相(多相)のクロックCLK0~4として、PLL480MのVCOが含む差動出力コンパレータ(反転回路)の出力を有効利用している。従って、CLK0~4を生成するために別の新たな回路を設ける必要が無いため、回路の小規模化を図れる。

## 【0108】

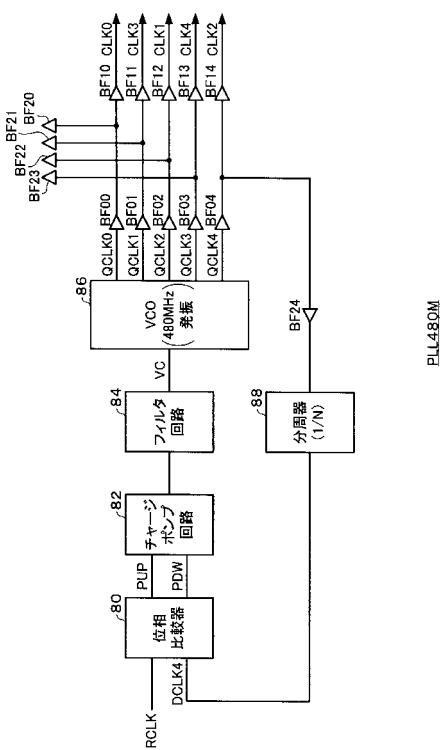

図8に、クロック生成回路14が含むPLL480Mの詳細な構成例を示す。

## 【0109】

このPLL480Mは、位相比較器80、チャージポンプ回路82、フィルタ回路84、VCO(Voltage Controlled Oscillator)86、分周器88などを含む。

10

## 【0110】

ここで位相比較器80は、ベースクロックRCLK(例えば12~24MHz)と分周器88からのクロックDCLK4の位相を比較し、位相誤差信号PUP、PDWを出力する(PUPは位相進み信号、PDWは位相遅れ信号)。

## 【0111】

チャージポンプ回路82は、位相比較器80からのPUP、PDWに基づいてチャージポンプ動作を行う。より具体的には、PUPがアクティブになると、フィルタ回路84が含むコンデンサを充電する動作を行い、PDWがアクティブになると、コンデンサを放電する動作を行う。そして、フィルタ回路84により平滑化された制御電圧VCがVCO86に与えられる。

20

## 【0112】

VCO86は、制御電圧VCに応じてその発振周波数が可変に制御される発振動作を行い、480MHzのクロックQCLK0~4を生成する。例えば、制御電圧VCが高くなると発振周波数も高くなり、制御電圧VCが低くなると発振周波数も低くなる。

## 【0113】

VCO86により生成されたクロックQCLK0、1、2、3、4は、バッファBF00~04、BF10~14を介して、各々、CLK0、3、1、4、2として外部に出力される。なお、BF20~23はBF24との負荷合わせのためのダミーのバッファである。

## 【0114】

30

分周器88は、バッファBF04、BF24を介してVCO86から入力されるクロックQCLK4を分周(1/N)して、分周後のクロックDCLK4を位相比較器80に出力する。

## 【0115】

図8の構成のPLL480Mによれば、ベースクロックRCLK(発振回路OSCにより生成されたクロック)に位相同期した高周波数の480MHzのクロックCLK0~4を生成できるようになる。

## 【0116】

以上のように図6のサンプリングクロック生成回路22では、受信回路100(差動レシーバ56)からのHS\_DataInのエッジ情報とクロック生成回路14(PLL480M)からの多相の480MHzのクロックCLK0~4に基づいて、サンプリングクロックSCLKを生成している。従って、HS\_DataInやクロックCLK0~4の配線に不要な容量が寄生してしまうと、適正なサンプリングクロックを生成できなくなるおそれがある。

40

## 【0117】

本実施形態によれば、マクロセルMC1を集積回路装置ICDのコーナに配置し、受信回路100、クロック生成回路14、サンプリングクロック生成回路22を図5に示すように配置している。従って、受信回路100とサンプリングクロック生成回路22の間の配線長やクロック生成回路14とサンプリングクロック生成回路22の間の配線長を極力短くすることが可能となる。この結果、図6のような構成のサンプリングクロック生成回

50

路 2 2 を採用した場合にも、適正なサンプリングクロックを生成できるようになる。

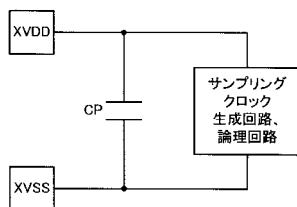

【 0 1 1 8 】

5 . キャパシタ領域の配置

本実施形態では図 9 に示すように、クロック生成回路 1 4 に電源を供給する電源端子 P V D D 、 P V S S ( 第 1 の電源端子 ) と、サンプリングクロック生成回路 2 2 や他の論理回路 1 1 2 ( 図 2 のエラスティシティバッファ 2 4 、 F S 回路 3 0 、データハンドラ回路 1 0 ) に電源を供給する電源端子 X V D D 、 X V S S ( 第 2 の電源端子 ) を、辺 S D 2 に沿った I / O 領域 I O R 2 に配置している。

【 0 1 1 9 】

そして本実施形態では、クロック生成回路 1 4 を、方向 D R 2 ( 第 2 の方向 ) において 10 電源端子 P V D D 、 P V S S に隣接して配置している。

【 0 1 2 0 】

一方、電源端子 X V D D 、 X V S S の電源電圧の変動を安定化させるためのキャパシタ素子領域 1 1 0 を、方向 D R 2 において電源端子 X V D D 、 X V S S に隣接して配置している。ここでキャパシタ素子 C P は、図 1 0 に示すように、一端 ( 正極側 ) が X V D D に接続され、他端 ( 負極側 ) が X V S S に接続される素子であり、基板電位を安定化させるガードリング ( 環状電源 ) などを利用して構成される。

【 0 1 2 1 】

図 9 に示すように電源端子 P V D D 、 P V S S に隣接してクロック生成回路 1 4 を配置すれば、 P V D D 、 P V S S とクロック生成回路 1 4 の間の電源配線の長さを短くできる 20 。従って、クロック生成回路 1 4 で流れる電流による電圧ドロップを最小限に抑えることができ、クロック生成回路 1 4 の安定動作を保証できる。

【 0 1 2 2 】

特に、クロック生成回路 1 4 が含む P L L 4 8 0 M ( 図 8 参照 ) は、高周波数 ( 4 8 0 M H z ) のクロックを生成する必要があるため、消費電流が非常に多い。そして、この消費電流により、電源に大きな電圧ドロップが生じると、 P L L 4 8 0 M が含む反転回路のゲインが低下してしまい、 4 8 0 M H z の発振動作を保証できなくなる事態が生じる。

【 0 1 2 3 】

本実施形態のように 電源端子 P V D D 、 P V S S に隣接してクロック生成回路 1 4 を配置すれば、このような事態が生じるのを効果的に防止できる。 30

【 0 1 2 4 】

また、図 9 に示すように電源端子 X V D D 、 X V S S に隣接してキャパシタ素子領域 1 1 0 を配置すれば、 X V D D 、 X V S S の電源電圧変動を、 X V D D 、 X V S S に近い場所で効果的に安定化できる。

【 0 1 2 5 】

特に、サンプリングクロック生成回路 2 2 や論理回路 1 1 2 が含むエラスティシティバッファは、高周波数 ( 4 8 0 M H z ) で動作する。従って、 M O S トランジスタのゲート容量の充放電に起因する電源電圧変動により、これらのサンプリングクロック生成回路 2 2 やエラスティシティバッファが誤動作する事態が生じるおそれがある。

【 0 1 2 6 】

本実施形態のように 電源端子 X V D D 、 X V S S の直ぐ近くにキャパシタ素子領域 1 1 0 を配置すれば、このような事態が生じるのを効果的に防止できる。また、クロック生成回路 1 4 の D R 1 側 ( 上側 ) のデッドスペース ( 空き領域 ) を有効利用できるという効果もある。

【 0 1 2 7 】

なお図 9 において、アナログ回路 1 1 4 は、基準電圧や基準電流を生成するための回路である。また、例えば、クロック生成回路 1 4 の発振回路 O S C を、アナログ回路 1 1 4 が配置されている領域付近に配置してもよい。

【 0 1 2 8 】

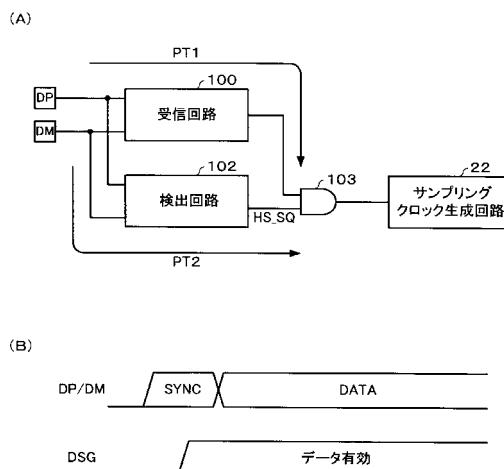

6 . 受信回路と検出回路の配置関係

10

20

30

40

50

本実施形態では図9に示すように、アナログフロントエンド回路40が、バス上の信号が有効なデータなのかノイズなのかを区別するための検出回路102（図2の高速用スケルチ回路54。エンベロープディテクタ）を含む。

【0129】

この検出回路102は、バスの信号のピーク値を保持し、信号の包絡線を検波することで、バスの信号の振幅を検出する。そして例えば、その振幅が100mV以下であれば信号はノイズであると判断し、150mV以上であれば有効なデータであると判断する。そして、有効なデータであると判断した場合には、検出回路102は図11（A）の検出信号HS\_SQをHレベル（アクティブ）にする。これにより、AND回路103が導通状態になり、受信回路100からの受信データがサンプリングクロック生成回路22に伝わるようになる。

【0130】

さて、USB2.0においては、この検出回路102の信号検出動作を非常に高速に行わなければならないことが判明した。

【0131】

即ち、USB2.0では、ハブ装置を通過するたびに、図11（B）のSYNCのビットが削られて行く。このため、末端のデバイスがデータを受信した時には、SYNCのビット数が非常に少なくなっている可能性がある。従って、検出回路102の信号検出動作が遅いと、HS\_SQがHレベルになるタイミングが遅れてしまい、受信データが喪失してしまうおそれがある。

【0132】

そこで本実施形態では図9に示すように、マクロセルMC1の辺SD2からSD4に向かう方向DR2において、受信回路100と検出回路102（スケルチ回路）を隣接して配置している。

【0133】

このようにすれば、図11（A）の経路PT1、PT2での配線の寄生容量、寄生抵抗を同等にすることが可能になる。従って、例えば、バスの信号がノイズであると検出された場合には、検出回路102の出力HS\_SQが即座にLレベルになることで、誤ったデータが経路PT1及びAND回路103を介してサンプリングクロック生成回路22に伝わるのを防止できる。一方、バスの信号が有効なデータであると検出された場合には、検出回路102の出力HS\_SQがHレベルになることで、受信回路100で受信されたデータが経路PT1及びAND回路103を介してサンプリングクロック生成回路22に即座に伝わるようになる。このように本実施形態では、経路PT1、PT2での配線の寄生容量、寄生抵抗を同等にすることで、安定した回路動作を実現することに成功している。

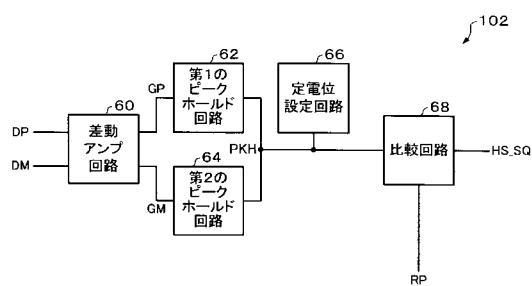

【0134】

図12に、検出回路102（スケルチ回路）の構成例を示す。

【0135】

図12の検出回路102は、差動アンプ回路60、第1及び第2のピークホールド回路62、64、定電位設定回路66、比較回路68を含む。

【0136】

差動アンプ回路60は、DP、DMからの差動入力信号の差分の電圧を増幅し、差動出力信号GP、GMを生成する。

【0137】

第1のピークホールド回路62は、差動出力信号の一方の出力信号GPのピーク値を検出し、ノードPKHに保持する。

【0138】

第2のピークホールド回路64は、差動出力信号の他方の出力信号GMのピーク値を検出し、ノードPKHに保持する。

【0139】

定電位設定回路66は、ノードPKHの電位変化速度よりもゆっくり変化するような時

10

20

30

40

50

定数で、ノード P K H の電位を、信号の未検出状態に対応した一定電位に戻す。

【0140】

比較回路 68 は、基準電位 R P とノード P K H の電位を比較し、その結果を H S \_ S Q として出力する。

【0141】

このように図 12 の検出回路 102 は、D P 、 D M に基づき得られた差動出力信号 G P 、 G M のピーク値をノード P K H に保持し、この P K H の電位を、信号未検出状態に関連付けられた一定電位に、ゆっくりとした時定数で戻すようにした。そして、このノード P K H の電位を、基準レベル R P と比較するようにしたので、D P 、 D M の差動入力信号が微小振幅かつ高速の場合でも、受信データの有無を精度良く判別できるようになる。

10

【0142】

7. 受信回路と送信回路の配置関係

本実施形態では図 9 に示すように、送信回路 104 ( 図 2 の H S 電流ドライバ 50 ) を、受信回路 100 ( H S 差動レシーバ 56 ) の D R 2 側 ( S D 2 から S D 4 へと向かう第 2 の方向側。右側 ) に配置している。

【0143】

例えば本実施形態の比較例となるレイアウト手法として、図 13 ( A ) に示すように、送信回路 104 を、受信回路 100 の方向 X D R 2 側 ( D R 2 の反対側。左側 ) に配置する手法も考えることができる。

【0144】

しかしながら、この手法では図 13 ( A ) に示すように、クロック生成回路 14 からのクロックの配線領域と、送信回路 104 に送信データを供給する論理回路 112 の領域とが重なってしまう。このため、レイアウト効率が悪くなるという問題がある。

20

【0145】

特に、図 6 、図 7 ( A ) 、 ( B ) の手法でサンプリングクロックを生成する場合には、クロック生成回路 14 からのクロック ( 多相クロック ) の配線に寄生する容量や抵抗は、なるべく小さくなることが望ましい。しかしながら、図 13 ( A ) のレイアウト手法では、クロック生成回路 14 とサンプリングクロック生成回路 22 との間の距離が離れてしまい、クロック生成回路 14 からのクロック配線に、無駄な寄生容量、寄生抵抗が付加されてしまう。

30

【0146】

更に図 13 ( A ) のレイアウト手法では、送信回路 104 の下側に配置されるデータ端子 D P 、 D M も、コーナ部分 C N に近い場所に配置されてしまう。このため、データ端子 D P 、 D M のボンディングワイヤが斜めに配線されてしまい、 D P 、 D M のボンディングワイヤの長さに差が生じてしまう。この結果、 D P 、 D M のボンディングワイヤに寄生するインダクタンスにも差が生じてしまい、 D P 、 D M の負荷バランスが崩れ、送信回路 104 の性能が低下するおそれがある。

【0147】

これに対して図 13 ( B ) に示すように、送信回路 104 を受信回路 100 の D R 2 側 ( 右側 ) に配置すれば、受信回路 100 を、コーナ部分 C N から近い場所に配置できる。この結果、クロック生成回路 14 からのクロックの配線領域と論理回路 112 の領域とが重なってしまう事態を防止でき、レイアウト効率を高めることができる。

40

【0148】

また、図 13 ( B ) のレイアウト手法によれば、クロック生成回路 14 とサンプリングクロック生成回路 22 との間の距離を近づけることができ、クロック生成回路 14 からのクロック配線に寄生する容量や抵抗を最小限に抑えることができる。

【0149】

更に図 13 ( B ) のレイアウト手法では、データ端子 D P 、 D M を、コーナ部分 C N から遠い場所に配置できる。これにより、データ端子 D P 、 D M のボンディングワイヤを真っ直ぐに配線でき、 D P 、 D M のボンディングワイヤの長さの差を最小限に抑えることができる。

50

できる。この結果、D P、D Mのボンディングワイヤの寄生インダクタンスの差も最小限に抑えることができ、D P、D Mの負荷バランスを同等にでき、高性能な送信回路104を実現できるようになる。

#### 【0150】

##### 8. 送信回路とデータ端子の配置関係

本実施形態の送信回路104は、図14(A)に示すように、定電流源I S(ゲート電極が定電位に設定されたP型トランジスタ)と、N型トランジスタ(スイッチ素子)N T P、N T A、N T Mとにより構成される電流ドライバを含む。ここで、N型トランジスタN T P、N T A、N T Mのゲート電極は、D P G、A V G、D M Gにより制御される。そして図14(B)に示すように、D P GをHレベル(アクティブ)に設定することで、定電流源I SからN型トランジスタN T Pを介してD Pに定電流が流れ、バスのステートがJ状態になる。一方、D M GをHレベルに設定することで、定電流源I SからN型トランジスタN T Mを介してD Mに定電流が流れ、バスのステートがK状態になる。そして、送信データに応じてバスをJ又はK状態にすることで、H Sモードでの送信が可能になる。

10

#### 【0151】

一方、送信(H S送信)期間以外の期間では、図14(B)に示すように、A V GをHレベルに設定することで、定電流源I SからN型トランジスタN T Aを介してA V S Sに定電流が流れる(I Sからの定電流が破棄される)。このように送信期間以外の期間においても、定電流源I Sの定電流をN型トランジスタN T Aを介してA V S Sに流し続けることで、送信開始時に直ぐに、安定した定電流をN T P又はN T Mを介してD P又はD Mに流すことが可能となり、送信回路104のレスポンスを高めることができる。

20

#### 【0152】

さて、このように送信回路104として電流ドライバを用いる場合には、図14(A)の経路P T P、P T Mに寄生する抵抗・容量・インダクタンスを互いに整合させて、D P、D Mの負荷バランスを保つことが望ましい。

#### 【0153】

そこで本実施形態では、図9に示すように、送信回路104とデータ端子D P、D Mを、方向D R 1(S D 1からS D 3へと向かう第1の方向。上方向)において隣接して配置している。

30

#### 【0154】

より具体的には図15に示すように、データ端子D P、D Mの真上(方向D R 1)に、送信回路104(図14(A)の電流ドライバ)のN型トランジスタN T P、N T Mを配置している。また、送信期間以外の期間において定電流源I Sからの定電流を流す電源端子A V S Sを、データ端子D P、D Mの間の領域に配置し、このA V S Sの真上(方向D R 1)にN型トランジスタN T Aを配置している。

#### 【0155】

このように配置すれば、D P、N T P間の配線の寄生抵抗・容量・インダクタンスと、D M、N T M間の配線の寄生抵抗・容量・インダクタンスを整合させて、D P、D Mの負荷バランスを保つことが容易になる。これにより、送信回路104の性能を高めること可能になる。

40

#### 【0156】

特に本実施形態では、図13(B)で説明したように、送信回路104を、受信回路100のD R 2側(右側)に配置している。そして図15で説明したように、送信回路104は、データ端子D P、D MのD R 1側(上側)に隣接して配置される。従って、結局、データ端子D P、D Mの配置位置がコーナ部分C Nから離れることになり、図13(B)で説明したように、D P、D Mのボンディングワイヤに寄生するインダクタンスの差も少なくできる。これにより、D P、D Mの負荷バランスを更に良好に保つことができる。

#### 【0157】

なお、図15では、N T P、N T A、N T MのD R 1側(上側)に、図2の抵抗R p u、R p u'及びスイッチ素子S W 1、S W 2を配置している。即ち、N T P、S W 1、R

50

$p_u$  のレイアウトと、NTM、SW2、R $p_u'$  のレイアウトとが対称になるようにしている。これにより、DP、DM に寄生する抵抗・容量・インダクタンスを等価にすることが可能になる。なお、図15において、定電流源ISを、NTP、NTA、NTMのDR1側（上側）や、R $p_u$ 、R $p_u'$  のDR1側に配置してもよい。

【0158】

9. 電子機器

次に、本実施形態の集積回路装置（データ転送制御装置）を含む電子機器の例について説明する。

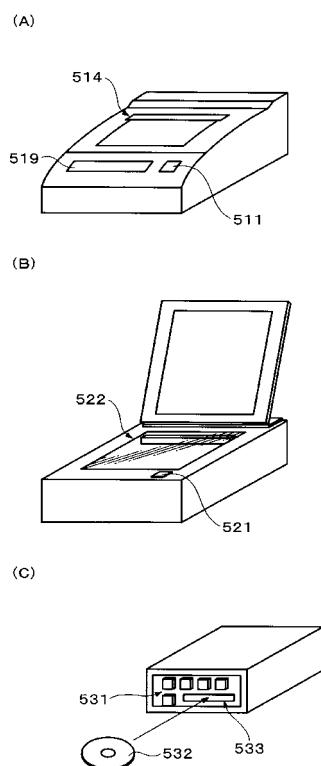

【0159】

例えは図16（A）に電子機器の1つであるプリンタの内部ブロック図を示し、図17（A）にその外観図を示す。CPU（マイクロコンピュータ）510はシステム全体の制御などを行う。操作部511はプリンタをユーザが操作するためのものである。ROM516には、制御プログラム、フォントなどが格納され、RAM517はCPU510のワーク領域として機能する。DMAC518は、CPU510を介さずにデータ転送を行うためのDMAコントローラである。表示パネル519はプリンタの動作状態をユーザに知らせるためのものである。

【0160】

USBを介してパーソナルコンピュータなどの他のデバイスから送られてきたシリアルの印字データは、集積回路装置500によりパラレルの印字データに変換される。そして、変換後のパラレル印字データは、CPU510又はDMAC518により、印字処理部（プリンタエンジン）512に送られる。そして、印字処理部512においてパラレル印字データに対して所与の処理が施され、プリントヘッダなどからなる印字部（データの出力処理を行う装置）514により紙に印字されて出力される。

【0161】

図16（B）に電子機器の1つであるスキャナの内部ブロック図を示し、図17（B）にその外観図を示す。CPU520はシステム全体の制御などを行う。操作部521はスキャナをユーザが操作するためのものである。ROM526には制御プログラムなどが格納され、RAM527はCPU520のワーク領域として機能する。DMAC528はDMAコントローラである。

【0162】

光源、光電変換器などからなる画像読み取り部（データの取り込み処理を行う装置）522により原稿の画像が読み取られ、読み取られた画像のデータは画像処理部（スキャナエンジン）524により処理される。そして、処理後の画像データは、CPU520又はDMAC528により集積回路装置500に送られる。集積回路装置500は、このパラレルの画像データをシリアルデータに変換し、USBを介してパーソナルコンピュータなどの他のデバイスに送信する。

【0163】

図16（C）に電子機器の1つであるCD-RWドライブの内部ブロック図を示し、図17（C）にその外観図を示す。CPU530はシステム全体の制御などを行う。操作部531はCD-RWをユーザが操作するためのものである。ROM536には制御プログラムなどが格納され、RAM537はCPU530のワーク領域として機能する。DMAC538はDMAコントローラである。

【0164】

レーザ、モータ、光学系などからなる読み取り＆書き込み部（データの取り込み処理を行う装置又はデータの記憶処理を行うための装置）533によりCD-RW532から読み取られたデータは、信号処理部534に入力され、エラー訂正処理などの所与の信号処理が施される。そして、信号処理が施されたデータが、CPU530又はDMAC538により集積回路装置500に送られる。集積回路装置500は、このパラレルのデータをシリアルデータに変換し、USBを介してパーソナルコンピュータなどの他のデバイスに送信する。

10

20

30

40

50

## 【0165】

一方、U S Bを介して他のデバイスから送られてきたシリアルのデータは、集積回路装置500によりパラレルのデータに変換される。そして、このパラレルデータは、C P U 530又はD M A C 538により信号処理部534に送られる。そして、信号処理部534においてこのパラレルデータに対して所与の信号処理が施され、読み取り&書き込み部533によりC D - R W 532に記憶される。

## 【0166】

なお、図16(A)、(B)、(C)において、C P U 510、520、530の他に、集積回路装置500でのデータ転送制御のためのC P Uを別に設けるようにしてもよい。

10

## 【0167】

本実施形態の集積回路装置を電子機器に用いれば、U S B 2 . 0におけるH Sモードでのデータ転送を実現できるようになる。従って、ユーザがパーソナルコンピュータなどによりプリントアウトの指示を行った場合に、少ないタイムラグで印字が完了するようになる。また、スキャナへの画像取り込みの指示の後に、少ないタイムラグで読み取り画像をユーザは見ることができるようになる。また、C D - R Wからのデータの読み取りや、C D - R Wへのデータの書き込みを高速に行うことができるようになる。

## 【0168】

また、本実施形態の集積回路装置を電子機器に用いれば、製造コストが安い通常の半導体プロセスでも、H Sモードでのデータ転送が可能な集積回路装置を製造できるようになる。従って、データ転送制御装置の低コスト化を図れ、電子機器の低コスト化も図れるようになる。また、データ転送の信頼性を向上でき、電子機器の信頼性も向上できるようになる。

20

## 【0169】

また、本実施形態の集積回路装置を電子機器に用いれば、集積回路装置の高性能を維持しながらも、電子機器を製造する多様なユーザの要望に応えることが可能となり、電子機器の付加価値を高めることができる。

## 【0170】

なお本実施形態の集積回路装置を適用できる電子機器としては、上記以外にも例えば、種々の光ディスクドライブ(C D - R O M、D V D)、光磁気ディスクドライブ(M O)、ハードディスクドライブ、T V、V T R、ビデオカメラ、オーディオ機器、電話機、プロジェクタ、パーソナルコンピュータ、電子手帳、ワードプロセッサなど種々のものを考えることができる。

30

## 【0171】

なお、本発明は本実施形態に限定されず、本発明の要旨の範囲内で種々の変形実施が可能である。

## 【0172】

例えば、本発明の集積回路装置の第1のマクロセルの回路構成は、図2に示す構成に限定されるものではなく、種々の変形実施が可能である。

40

## 【0173】

また、本発明の集積回路装置の各回路の配置も、図3(A)～図15で説明したものに限定されず、種々の変形実施が可能である。

## 【0174】

また、本発明は、U S B 2 . 0のインターフェース(データ転送)に適用されることが特に望ましいが、これに限定されるものではない。例えばU S B 2 . 0と同様の思想に基づく規格やU S B 2 . 0を発展させた規格のインターフェースにも本発明は適用できる。

## 【図面の簡単な説明】

## 【0175】

【図1】本実施形態の集積回路装置の概念的な機能ブロック図の例である。

【図2】マクロセルM C 1の回路構成例を示す図である

50

【図3】図3(A)、(B)、(C)は、マクロセルMC1、MC2の配置例を示す図である。

【図4】データ端子等の配置例を示す図である。

【図5】クロック生成回路等の配置例を示す図である。

【図6】サンプリングクロック生成回路の構成例を示す図である。

【図7】図7(A)、(B)は、サンプリングクロック生成回路の動作について説明するためのタイミング波形図である。

【図8】PLL480Mの構成例を示す図である。

【図9】キャパシタ素子領域、受信回路、検出回路、送信回路の配置例を示す図である。

【図10】キャパシタ素子CPについて説明するための図である。 10

【図11】図11(A)、(B)は、検出回路(スケルチ回路)の動作について説明するための図である。

【図12】検出回路の構成例を示す図である。

【図13】図13(A)、(B)は、送信回路と受信回路の配置関係について説明するための図である。

【図14】図14(A)、(B)は、送信回路の電流ドライバについて説明するための図である。

【図15】端子DP、AVSS、DM、N型トランジスタNTP、NTA、NTMの配置例について示す図である。

【図16】図16(A)、(B)、(C)は、種々の電子機器の内部ブロック図の例である。 20

【図17】図17(A)、(B)、(C)は、種々の電子機器の外観図の例である。

【符号の説明】

【0176】

I C D 集積回路装置、MC1、2 第1、第2のマクロセル、CN コーナ部分、

SD1～4 第1～4の辺、DR1、2 第1、第2の方向、

I F R インターフェース領域、I OR1、2 I/O領域、

DP、DM データ端子、VDD、VSS 電源端子、

PVDD、PVSS 第1の電源端子、XVDD、XVSS 第2の電源端子、

AVDD、AVSS 電源端子、XI、XO クロック端子、

10 データハンドラ回路、12 クロック制御回路、14 クロック生成回路、

20 HS回路、30 FS回路、40 アナログフロントエンド回路、

42 FSドライバ、44 FS差動レシーバ、

46 シングルエンドDPレシーバ、48 シングルエンドDMレシーバ、

50 HS電流ドライバ(送信回路)、52 低速用スケルチ回路(検出回路)、

54 高速用スケルチ回路(検出回路)、56 HS差動レシーバ(受信回路)、

70 エッジ検出回路、72 クロック選択回路、100 受信回路、

102 検出回路、104 送信回路、110 キャパシタ素子領域、

112 論理回路 30

【 四 1 】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 笠原 昌一郎

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 秋山 千里

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 小松 史和

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 須原 宏光

(56)参考文献 特開平09-232437(JP,A)

特開平07-271703(JP,A)

特開平11-176940(JP,A)

特開2000-148716(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82

H01L 21/822

H01L 27/04