## (19) World Intellectual Property Organization

International Bureau

##

(43) International Publication Date 20 April 2006 (20.04.2006)

**PCT**

# (10) International Publication Number $WO\ 2006/041793\ A1$

(51) International Patent Classification<sup>7</sup>:

H01L 21/469

(21) International Application Number:

PCT/US2005/035547

(22) International Filing Date: 3 October 2005 (03.10.2005)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

10/711,764

4 October 2004 (04.10.2004) U

- (71) Applicant (for all designated States except US): INTER-NATIONAL BUSINESS MACHINES CORPORA-TION [US/US]; New Orchard Road, Armonk, NJ 10504 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): FURUKAWA, Toshiharu [JP/US]; Nine Oakwood Lane, Essex Junction, VT 05452 (US). HAKEY, Mark, C. [US/US]; 15 Bellows Street, Fairfax, VT 05454 (US). HOLMES, Steven, J. [US/US]; 103 Guilder Lane Apt. 11, Guilderland, NY 12084 (US). HORAK, David, V. [US/US]; 47 Briar Lane, Essex Junction, VT 05452 (US). KOBURGER, Charles, W., III [US/US]; 40 Roweland Avenue, Delmar, NY 12054 (US).

- (74) Agent: CANALE, Anthony, J.; International Business Machines Corporation, Intellectual Property Law--Zip 972E, 1000 River Street, Essex Junction, VT 05452 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

[Continued on next page]

(54) Title: LOW-K DIELECTRIC MATERIAL BASED UPON CARBON NANOTUBRES AND METHODS OF FORMING SUCH LOW-K DIELECTRIC MATERIALS

(57) Abstract: A low-k dielectric material for use in the manufacture of semiconductor devices, semiconductor structures using the low-k dielectric material, and methods of forming such dielectric materials and fabricating such structures. The low-k dielectric material (14) comprises carbon nanostructures (16), like carbon nanotubes or carbon buckyballs, that are characterized by an insulating electronic state. The carbon nanostructures may be converted to the insulating electronic state either before or after a layer containing the carbon nanostructures is formed on a substrate (10). One approach for converting the carbon nanostructures to the insulating electronic state is fluorination.

####

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# LOW-K DIELECTRIC MATERIAL BASED UPON CARBON NANOTUBES AND METHODS OF FORMING SUCH LOW-K DIELECTRIC MATERIALS

#### TECHNICAL FIELD

The invention relates generally to semiconductor materials, structures, devices, and fabrication methods and, more particularly, to dielectric materials for forming a structure for an integrated circuit, structures formed with the dielectric materials, and methods for forming such dielectric materials and structures.

#### **BACKGROUND ART**

Progressive miniaturization of feature sizes in circuit elements has improved the performance and increased the functional capability of integrated circuits (IC's). Back-end-of-line (BEOL) multilevel interconnect structures have been developed that complement advances in circuit element density realized by size reductions by more effectively routing signal paths between the constituent circuit elements of the IC. Circuit performance and functional capability of the circuit elements are eventually limited by the signal-transmission effectiveness and efficiency of the BEOL interconnect structure.

Damascene processes are routinely used to fabricate such BEOL multilevel interconnect structures. In a single damascene process, vias are etched in a patterned layer of dielectric material and filled with metal to establish interlevel contacts with a lower conductor. The lower conductor may be the metallization lines of an underlying level of the interconnect structure. Trenches are then etched in another patterned layer of dielectric material and filled with metal to define intralevel metallization lines. In a dual-damascene process, trenches and vias are etched in a patterned layer of dielectric material and filled simultaneously by a single blanket deposition of metal. In single and dual-damascene processes, any excess overburden of metal on the dielectric layer is removed from the top of the structure in a planarization process, such as chemical mechanical polishing (CMP). Silicon oxide and fluorine-doped silicon glass (FSG) are common materials used to form the dielectric layer(s).

Increases in circuit element density as achieved by reducing the line-to-line spacings between adjacent, on-pitch metallization lines in each interconnect level and

between metallization lines in adjacent interconnect levels. The reduction in line-to-line spacing serves to increase the line-to-line capacitance, which causes propagation delay by slowing the speed of the signals carried by the metallization lines, and results in cross talk noise. This increase in line-to-line capacitance may be offset by reducing the dielectric constant of the dielectric material constituting the dielectric layer(s). Conversely, a reduction in line-to-line capacitance by reducing the dielectric constant permits concomitant reductions in line-to-line spacing.

The reduction or elimination of these adverse capacitive couplings could advantageously lead to enhanced device speed and reduced power consumption. Consequently, a trend in interconnect structures is to form the dielectric layer from a dielectric material characterized by a relative permittivity or dielectric constant smaller than the dielectric constant of traditional materials. Candidate low-k materials include inorganic polymers, organic polymers such as polyamides and SiLK® from Dow Chemical Company, organo-inorganic materials like spin-on glasses, and silsesquioxane-based materials. Generally, these candidate low-k materials are characterized by a dielectric constant smaller than three (3).

Damascene processes place stringent requirements on the properties of the candidate low-k dielectric materials, which has limited the integration of low-k dielectrics into damascene processes. In particular, a suitable low-k dielectric material must have sufficient mechanical strength and adequate chemical stability to withstand the cleaning, etching, polishing, and thermal treatments imposed by damascene processing. After manufacture, BEOL interconnect structures formed using organic dielectric materials have experienced significant reliability problems resulting from mismatches in the thermal coefficient of expansion with neighboring inorganic materials.

What is needed, therefore, is a low-k dielectric material suitable for use in forming a structure in an integrated circuit, such as for use as a low-k dielectric layer in a BEOL interconnect structure for an integrated circuit, that is fully compatible with processes for forming such interconnect structures.

### DISCLOSURE OF THE INVENTION

In accordance with an embodiment of the invention, a dielectric material for forming a structure of an integrated circuit is comprised of a plurality of carbon

nanostructures, such as carbon nanotubes or carbon buckyballs. In one embodiment of the invention, the nanostructures forming the dielectric material may be fluorinated. In another embodiment of the invention, the dielectric material may have a dielectric constant less than about three (3). The dielectric material may be used to form a dielectric layer in a semiconductor structure that includes at least one conductive feature electrically isolated from nearby conductive features by portions of the dielectric layer.

In accordance with another embodiment of the invention, a method for forming a dielectric layer includes forming a dielectric layer comprising a plurality of carbon nanostructures on a substrate. The dielectric layer, which may be applied to the substrate by a spin-on process, may be either formed in an insulating electronic state or converted to the insulating electronic state after formation.

In accordance with another embodiment of the invention, a method for forming a structure for an integrated circuit includes forming a dielectric layer including a plurality of carbon nanostructures on a substrate. The method further includes forming at least one conductive feature in the dielectric layer.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate embodiments of the invention and, together with a general description of the invention given above and the detailed description of the embodiments given below, serve to explain the principles of the invention.

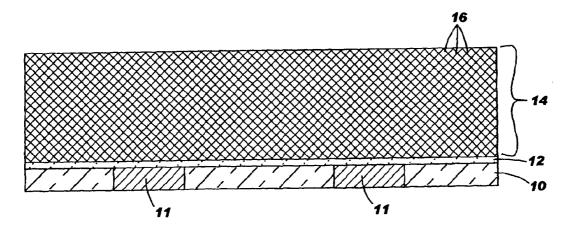

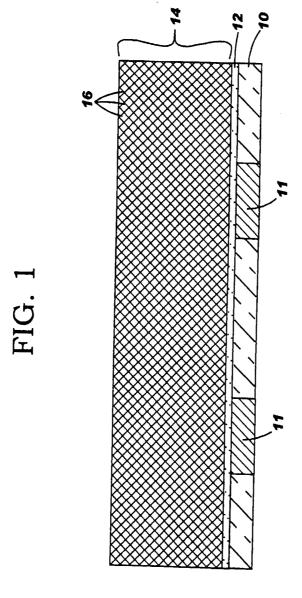

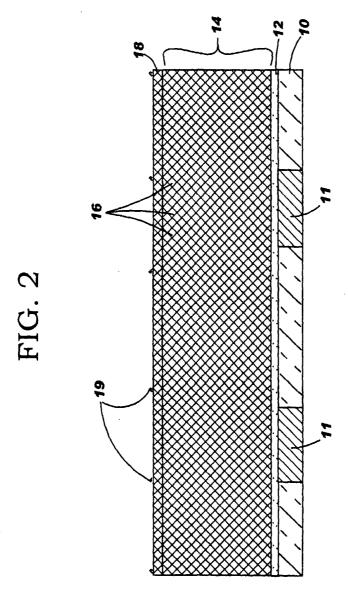

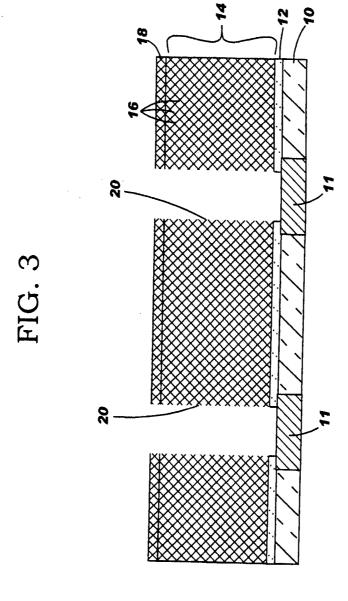

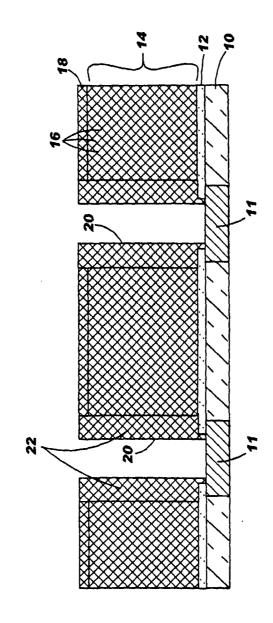

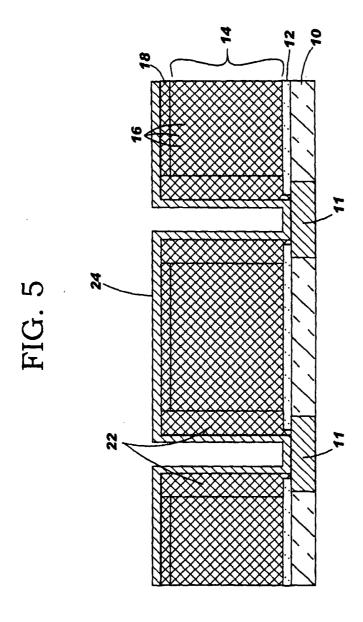

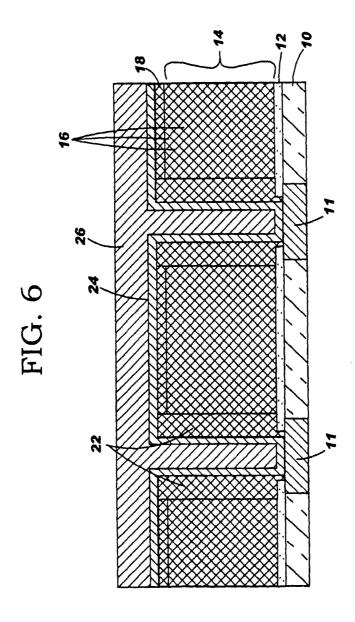

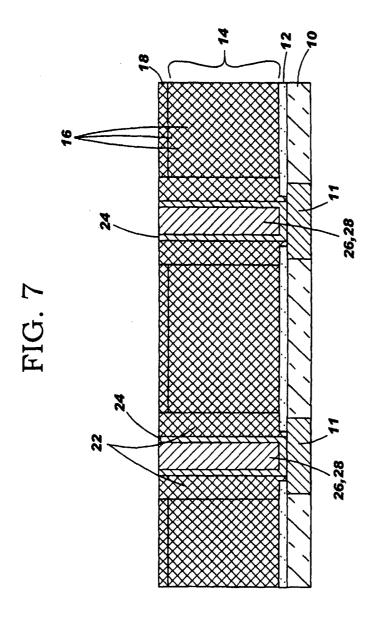

- FIGS. 1-7 are diagrammatic cross-sectional views of a portion of a substrate at various stages of a processing method in accordance with an embodiment of the invention;

- FIG. 8 is a diagrammatic cross-sectional view similar to FIG. 1 of a portion of a substrate at an initial processing stage in accordance with an alternative embodiment of the invention;

- FIG. 9 is a diagrammatic view of a portion of a substrate having mandrels configured to grow carbon nanotubes to form the dielectric layer of FIG. 1 in accordance with another alternative embodiment of the invention; and

- FIG. 9A is an enlarged diagrammatic cross-sectional view detailing one of the mandrels shown in FIG. 9.

## BEST MODE FOR CARRYING OUT THE INVENTION

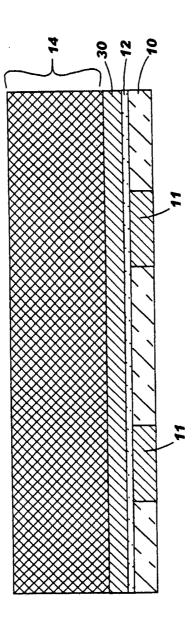

With reference to FIG. 1, a substrate 10 is covered by a layer 12 of a suitable cap material, such as silicon nitride (Si<sub>3</sub>N<sub>4</sub>). Substrate 10 contains features 11 that are to be contacted, like a silicon diffusion region (e.g., a source or drain for a semiconductor device) or an underlying wiring or metallization structure. Substrate 10 may be a semiconductor wafer composed of any semiconductor material including, but not limited to, silicon (Si), silicon germanium (SiGe), silicon-on-insulator, and other like Si-containing semiconductor materials. The substrate 10 may be doped with either n-type or p-type impurities, depending on the desired device or circuit element to be fabricated, and may contain various isolation and/or device regions either formed in the substrate 10 or on a surface thereof. Substrate 10 may also be one of the interconnect levels of a multilevel interconnect structure, a dielectric material, a buried barrier layer, a metallization line, or another substrate that a person of ordinary skill would recognize as present in integrated circuits.

A layer 14 of a dielectric material overlies the cap layer 12, which promotes adhesion between interlevel dielectric 14 and substrate 10. The dielectric layer 14 is constituted by a network of multiple carbon nanotubes 16 that are individually and collectively characterized by an electrically-insulating electronic state and, hence, are non-conducting of electrical current. The carbon nanotubes 16 of dielectric layer 14 may be applied across substrate 10 in an electrically-insulating electronic state or may be converted to an electrically-insulating electronic state after layer 14 is formed. The precise arrangement and orientation of the carbon nanotubes 16 is not shown in the Figures, which are understood by those of ordinary skill to be diagrammatic. As non-limiting examples, the carbon nanotubes 16 may be randomly oriented, substantially parallel and preferentially aligned, or a tangled mat. Generally, carbon nanotubes 16 are hollow cylindrical tubes formed from precisely-arranged hexagonal rings of bonded carbon atoms. The carbon nanotubes 16 may, without limitation, be multiwall nanotubes having a structure resembling nested concentric cylinders or, alternatively, may constitute single-wall nanotubes.

In accordance with one embodiment of the invention, dielectric layer 14 may be formed by mixing the carbon nanotubes 16 with a solvent-diluted copolymer and then depositing the mixture in a liquid form across the surface of cap layer 12 by a

spin-coating process. To that end, a mixture of the carbon nanotubes 16, the copolymer, and an appropriate solvent, such as an alcohol, is dispensed onto cap layer 12 in a predetermined amount and the substrate 10 is rapidly rotated or spun. The spin-on process uniformly distributes the liquid across the cap layer 12 by centrifugal forces and results in a uniform applied film of a controlled thickness. The liquid film is solidified by a low-temperature hot plate bake that removes residual solvent and cures the copolymer. Typically, the hot plate bake is performed at a temperature of from about 90°C to about 400°C for a time period ranging from about 10 seconds to about 300 seconds. The residual copolymer operates as a binder for the carbon nanotubes 16 after the solvent is removed. Suitable spin on organic copolymers include SiLK® sold by Dow Chemical Company, the fluorinated aromatic resin FLARE® sold by Honeywell Electronic Materials, perfluorocyclobutane (PFCB) aromatic ether polymers commercially available from Dow Chemical Company, each of which has a dielectric constant less than about three (3), and other high temperature stable materials such as polyimides. Even if the contribution of the binding copolymer to the effective dielectric constant of dielectric layer 14 is taken into consideration, dielectric layer 14 has a dielectric constant of less than about three (3) when the carbon nanotubes 16 are in the electrically-insulating electronic state, as described below.

In an alternative embodiment of the invention, the dielectric layer 14 may be formed from electrically-insulating C<sub>60</sub> or C<sub>70</sub> buckyballs or multi-wall buckyballs, instead of carbon nanotubes 16 or in a mixture with carbon nanotubes 16, that are deposited by spin coating, as described above. Buckyballs typically have a shape resembling a soccer ball with a lattice formed primarily from six-fold rings (hexagonal structure), with occasional five-fold rings and seven-fold rings. Buckyballs may be formed by a conventional process, such as those processes disclosed in United States Patent No. 5,227,038 (Smalley et al.) and United States Patent No. 5,300,203 (Smalley), each of which is hereby incorporated by reference herein in its entirety. The buckyballs are converted to the insulating electronic state by, for example, fluorination, as described herein, so that the buckyballs are nonconducting electrically. The invention contemplates that other types of carbon-based nanostructures similar to carbon nanotubes 16 and carbon buckyballs may be used for forming the dielectric layer 14.

The carbon nanotubes 16 may be converted from their as-applied electronic state to an electrically-insulating electronic state after dielectric layer 14 is formed. In one embodiment of the invention, the conversion to an electrically-insulating electronic state may occur immediately after the dielectric layer 14 is formed. In another embodiment of the invention, the conversion may occur during a subsequent processing stage. Alternatively, the carbon nanotubes 16 may be converted to the electrically-insulating state before the dielectric layer 14 is formed by the spin-on process. The carbon nanotubes 16 may also be grown on substrate 10 in either a semiconducting or conducting electronic state, as described below with regard to FIGS. 8 and 9, and converted to an insulating electronic state. Regardless of the formation technique, the resultant dielectric layer 14 constructed from carbon nanotubes 16 will have a dielectric constant of less than about three (3) when the carbon nanotubes 16 are in the electrically-insulating electronic state.

One approach for converting the carbon nanotubes 16 from a semiconducting or conducting electronic state to an electrically-insulating electronic state involves fluorination. An exemplary conversion process involves exposing the carbon nanotubes 16 to a fluorine-containing atmosphere (e.g., fluorine gas (F2)) at an elevated temperature (e.g., 50°C to 250°C) and for a duration sufficient to provide a suitable degree of fluorination. The fluorine-containing atmosphere may be diluted with a gaseous diluent including, but not limited to, nitrogen (N2) and inert gases, such as argon (Ar). Treatment of carbon nanotubes by fluorination at elevated temperatures is disclosed, for example, in Mickelson et al., Chem. Phys. Lett. 296 (1998) pp. 188-194, Bahr et al., J. Mater. Chem. 12 (2002) pp. 1952-1958, Mickelson et al., J. Phys. Chem. B (1999) pp. 4318-4312, Boul et al., Chem. Phys. Lett. 310 (1999) 367-372, and United States Patent No. 6,645,455 (Margrave et al.), each of which is hereby incorporated by reference herein in its entirety. The fluorinecontaining gas will permeate the dielectric layer 14 and react with the carbon nanotubes 16 at the elevated temperature to provide the electrically-insulating electronic state. The carbon nanotubes 16 may be fluorinated before being applied by the spin-coating process, immediately after the dielectric layer 14 is formed, or during a subsequent process stage. Alternatively, the carbon nanotubes 16 may be hydrogenated or alkylated to convert to an insulating electronic state.

With reference to FIG. 2 in which like reference numerals refer to like features in FIG. 1 and at a subsequent fabrication stage, a cap layer 18 is deposited on the dielectric layer 14. The cap layer 18 operates to seal the upper horizontal surface of the dielectric layer 14 by filling the open spaces or gaps between adjacent carbon nanotubes 16. The cap layer 18 may have an upper boundary that is coplanar with the horizontal upper surface of the dielectric layer 14, as shown in FIG. 2. Alternatively, cap layer 18 may project partially above the horizontal upper surface of dielectric layer 14 or may reside entirely on top of the dielectric layer 14. The tips or free ends of some of the carbon nanotubes 16, of which carbon nanotubes 19 are representative, may project above the horizontal upper surface of cap layer 18. These projecting nanotubes 19 are preferably removed by a planarization technique, such as a chemical-mechanical polishing (CMP) process, so that the upper horizontal surface of cap layer 18 is polished flat and planarized. Any residual metal catalyst exposed by polishing cap layer 18 may be oxidized with an aqueous peroxide wash or with a brief oxygen plasma treatment. This oxidizing step applies to those embodiments of the invention described in FIGS. 8 and 9 in which the dielectric layer 14 is grown using a catalyst.

With reference to FIG. 3 in which like reference numerals refer to like features in FIG. 2 and at a subsequent fabrication stage, openings 20 characteristic of a pattern of vias and trenches are formed in cap layer 18 and the dielectric layer 14. The openings 20 are defined using conventional lithography, including applying a photoresist to a surface of the cap layer 18 and patterning the photoresist, and then etching using the patterned photoresist. Suitable etching processes include any conventional dry etching process, such as reactive-ion etching and plasma etching. The etching process stops vertically on the cap layer 12. However, the invention does not require that all of the openings 20 formed across the substrate 10 extend to the depth of the cap layer 12.

The openings 20 of the pattern may include, for example, an interconnect structure of features, such as vias and trenches, that are filled with a conductive material and thereby coupled with underlying conductive features (not shown), such as metallization lines or underlying circuit elements previously formed in the substrate 10. The interconnect structure may be, for example, a damascene structure or a double damascene structure but the invention is not so limited. The pattern can

include any desired pattern of trenches, vias and other features conventionally designed into such interconnect structures as demanded by design requirements.

If the carbon nanotubes 16 have not been previously converted to an insulating electronic state, the openings 20 afford access for performing the conversion at this stage of the fabrication process. More specifically, fluorination gas vertically accesses the full thickness of the dielectric layer 14 through the openings 20 and diffuses laterally through the dielectric layer 14.

With reference to FIG. 4 in which like reference numerals refer to like features in FIG. 3 and at a subsequent fabrication stage, the carbon nanotubes 16 of dielectric layer 14 bordering the vertical sidewalls of openings 20 are sealed with a layer 22 of a diffusion limited dielectric, like Si<sub>3</sub>N<sub>4</sub> or silicon dioxide (SiO<sub>2</sub>). Dielectric layer 22 prevents migration of metal from the subsequent contacts formed in openings 20 into the dielectric layer 14. The dielectric layer 22 may be formed, for example, by a chemical vapor deposition (CVD) process. The dielectric layer 22 may have a vertical boundary that is substantially coplanar with the vertical sidewalls of openings 20, as shown in FIG. 4. Alternatively, dielectric layer 22 may partially or totally cover the vertical sidewalls of openings 20. A directional dry etch process, such as RIE, is used to remove portions (not shown) of the dielectric layer 22 from the horizontal floor of each opening 20.

With reference to FIG. 5 in which like reference numerals refer to like features in FIG. 4 and at a subsequent fabrication stage, an optional but preferred liner 24 is applied to the exposed vertical and horizontal surfaces of the openings 20. Liner 24 is typically comprised of one or more layers of tantalum (Ta), titanium (Ti), tungsten (W), or nitrides of these metals. The liner material of liner 24 may be formed in the openings 20 utilizing conventional deposition processes well known to persons of ordinary skill in the art, including but not limited to CVD, plasma-enhanced CVD, and physical vapor deposition (PVD). The process applying the liner 24 inside openings 20 may also cover cap layer 18 with excess liner material that is subsequently removed.

With reference to FIG. 6 in which like reference numerals refer to like features in FIG. 5 and at a subsequent fabrication stage, a layer of a conductor 26 is deposited across the substrate 10 so that the openings 20 (Fig. 3) are filled by conductive material. The conductive material may be a metal that will serve as contacts with the

metal conductive lines of underlying circuit elements or devices previously formed in the substrate 10 and as metal conductive lines. The optional liner 24, along with the dielectric layer 22, separate the dielectric layer 14 from portions of the conductor layer 26 filling openings 20. Suitable conductors include but are not limited to aluminum (Al), copper (Cu), tungsten (W), silver (Ag), alloys of these metals, and other like metals. The metal is formed in the openings 20 utilizing a conventional deposition process such as CVD, plasma-enhanced CVD, an electrochemical process such as electroplating or electroless plating, PVD, direct current (DC) or radio frequency (RF) sputtering, and the like.

With reference to FIG. 7 in which like reference numerals refer to like features in FIG. 6 and at a subsequent fabrication stage, the top surface of conductor layer 26 is made substantially coplanar with the upper horizontal surface of cap layer 18, usually by a CMP process, to define individual conductive features or contacts 28 inside openings 20. The CMP process combines abrasion and dissolution to flatten and smoothen the surface relief. Abrasion occurs when higher portions of the conductive layer 26 contact a polish pad and abrasive particles in a polish slurry and become subject to mechanical forces. Dissolution occurs when conductive material at the exposed surface of layer 26 contacts chemicals in the slurry and becomes susceptible to chemical or electrochemical reactions. The planarization removes the overburden of excess conductive material from layer 26 and portions of the optional liner 24 covering the cap layer 12 outside of openings 20 (Fig. 4).

The cap layer 18 remains on the surface of the interconnect structure after planarization. For this reason, the dielectric constant of the cap layer 18 should be relatively low so as to not significantly increase the effective dielectric constant of the dielectric layer 14. Accordingly, the dielectric layer 14 and the cap layer 18 should collectively have a dielectric constant of less than about three (3). However, in certain embodiments, the dielectric layer 14 alone has a dielectric constant of about three (3) with the presence of the cap layer 18 resulting in an effective dielectric constant marginally greater than about three (3). After planarization, an upper horizontal surface of each conductive contact 28 is approximately flat and level with the upper horizontal surface of cap layer 12 across the substrate 10.

The completed interconnect structure of FIG. 7 is reproduced or replicated across the surface of substrate 10 by the fabrication procedure described in FIGS. 1-7

to define an interconnect level. Additional interconnect levels, similar or identical to the completed interconnect level, may be stacked above the completed interconnect level by following a fabrication process identical or similar to that illustrated in FIGS. 1-7. The invention contemplates that access passages (not shown) may be provided in such multilevel interconnect structures for converting the constituent carbon nanotubes 16 to an insulating electronic state after all levels are formed. For example, a fluorination gas may be routed to the dielectric layer 14 of the various levels through the access passages. Regardless of the processing stage at which the conversion of carbon nanotubes 16 to an insulating electronic state occurs, the temperature of the substrate 10 after conversion and during subsequent processing stages should not exceed a temperature that would otherwise degrade the electrical insulating properties of the converted carbon nanotubes 16.

The spin-coating process offers benefits of a low-temperature process and simplicity. However, the carbon nanotubes 16 of dielectric layer 14 may be formed by other techniques. For example, the carbon nanotubes 16 may be grown using any suitable growth technique, as described below.

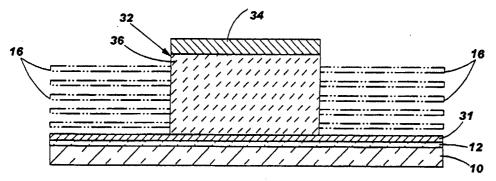

With reference to FIG. 8 in which like reference numerals refer to like features in FIG. 1 and in accordance with an alterative embodiment of the invention, the carbon nanotubes 16 may be grown by a CVD process or a plasma-enhanced CVD process. To that end, a thin layer 30 of a catalyst is formed on the cap layer 12. The catalyst layer 30 may include any material capable of nucleating and supporting the synthesis or growth of carbon nanotubes 16 when exposed to appropriate reactants under chemical reaction conditions suitable to promote nanotube growth. Suitable catalyst materials for catalyst layer 30 include, but are not limited to, iron (Fe), nickel (Ni), cobalt (Co), compounds of these metals such as metal oxides, and alloys of these metals. In the case of metal oxides, it may be necessary to perform a reduction to access or activate the catalyst material. The catalyst layer 30 is formed by depositing the catalytic material by any conventional deposition technique including, but not limited to, a CVD process or plasma-enhanced CVD process, DC or RF sputtering, and PVD.

The catalyst layer 30 catalyzes the growth of carbon nanotubes 16 from a carbon-containing reactant gas when contacted by the reactant gas under appropriate growth conditions. Suitable carbon-containing reactant gases for such catalyzed

nanotube growth include, but are not limited to, carbon monoxide and hydrocarbon precursors. The hydrocarbon precursor may be an aromatic hydrocarbon, such as benzene, toluene, xylene, cumene, ethylbenzene, naphthalene, phenanthrene, anthracene, and their mixtures. Alternatively, the hydrocarbon precursor may be a non-aromatic hydrocarbon, such as methane, ethane, propane, ethylene, propylene, acetylene, and their mixtures, or an oxygen-containing hydrocarbon, such as methanol, ethanol and other alcohols, acetone and other ketones, formaldehyde, acetaldehyde and other aldehydes, and their mixtures. Other suitable reactant gases include a mixture of carbon monoxide and hydrogen, a mixture of acetylene and ammonia, a mixture of acetylene and hydrogen, and a mixture of ethanol and nitrogen.

The catalyst layer 30 promotes carbon nanotube synthesis by reducing the activation energy of the reaction with the carbon-containing reactant gas forming carbon nanotubes 16. Carbon atoms originating from the reactant gas are incorporated into the lengthening carbon nanotubes 16. Substrate 10 may be heated to a temperature adequate to promote and/or hasten CVD growth. The carbon nanotubes 16 will tend to grow vertically from the catalyst layer 30. Growth is halted when the carbon nanotubes 16 have a desired height. The carbon nanotubes 16 grow on substrate 10 in either a semiconducting or conducting electronic state and are converted to an insulating electronic state by, for example, fluorination or hydrogenation as described herein. Conversion of the carbon nanotubes 16 by fluorination would also fluorinate the remaining portions of catalyst layer 30 to produce a metal fluoride.

After the carbon nanotubes 16 are grown, processing of substrate 10 continues as described herein with regard to FIGS. 1-7 to form the completed interconnect structure shown in FIG. 7. Of course, it is understood by person of ordinary skill that, after the carbon nanotubes 16 are formed, the catalyst layer 30 is converted to a nonconductive form by, for example, oxidation or fluorination.

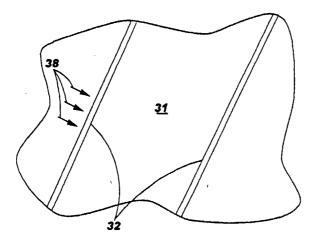

With reference to FIGS. 9 and 9A in which like reference numerals refer to like features in FIG. 1 and in accordance with an alterative embodiment of the invention, the dielectric layer 14 may be formed by another approach. Specifically, a thin layer 31 of a material that does not support the growth of carbon nanotubes 16 is deposited across substrate 10 on the cap layer 12 and an oxide layer having a

thickness in the range of about 200 nm to about 800 nm is formed on layer 31. Then, a thin layer 34 of a material that does not support the growth of carbon nanotubes 16 is deposited on the oxide layer. Layers 31 and 34 may be formed from materials such as silicon, tungsten, titanium, zirconium, hafnium, and aluminum, and may have a thickness in the range of about 10 nm to about 20 nm.

A plurality of parallel mandrels 32 are formed from the oxide layer on the metal layer 31 using a conventional lithography and etch process that removes patterned portions of the oxide layer and layer 34. Adjacent parallel mandrels 32 in the pattern may be separated, for example, by about 300 microns to about 1000 microns. After etching, an upper horizontal surface of an oxide body 36 of each mandrel 32 is covered by a residual cap that represents residual material left after etching layer 34 and the vertical sidewalls of the oxide body 36 are exposed oxide. This structure is best shown in FIG. 9A. The remaining material of layers 31 and 34 may be rendered non-conducting, after the carbon nanotubes 16 are grown, by either fluorinating simultaneously with the fluorination of the carbon nanotubes 16 or oxidizing with either oxygen or ozone at a low temperature that does not cause significant oxidation of the carbon nanotubes 16.

Carbon nanotube growth is initiated by a CVD process that supplies a flow of a gas mixture of a catalyst vapor or gas, such as ferrocene (Fe( $C_5H_5$ )<sub>2</sub>), and a carbon-containing vapor of gas, such as xylene ( $C_6H_4(CH_3)_2$ ), that is directed approximately horizontally across the surface of substrate 10, as generally indicated by the arrows labeled with reference numeral 38. The layers 31 and 34 do not support carbon nanotube growth. However, the reactant gas reacts with the catalyst atoms deposited from the catalyst gas on the exposed vertical sidewalls of the oxide body 36 to nucleate and grow carbon nanotubes 16. The presence of the catalyst gas in the gas mixture permits nucleation and growth of carbon nanotubes 16 without incorporating a metal nucleating layer 30 (Fig. 8) into the interconnect structure. During the chemical vapor decomposition, metal atoms from the catalyst gas in the gas mixture serve to nucleate the nanotubes 16 on the vertical sidewalls of the oxide body 36.

Carbon nanotubes 16 grow outwardly from the sidewalls with a substantially horizontal orientation that extends approximately laterally across the substrate surface, as shown in dashed lines in FIG. 9A. The CVD process is sustained to continue nanotube growth until the length of carbon nanotubes 16 is suitable for

forming the dielectric layer 14. The carbon nanotubes 16 grow on substrate 10 in either a semiconducting or conducting electronic state and are converted to an insulating electronic state by, for example, fluorination or hydrogenation as described herein. A dielectric layer 14 formed with carbon nanotubes 16 grown in this manner may solve the problem of thermal expansion of conventional organic materials as dielectric layer 14 is not constrained vertically, which permits expansion without the introduction of stress.

After the carbon nanotubes 16 are grown, processing of substrate 10 continues as described herein with regard to FIGS. 1-7 to form the completed interconnect structure shown in FIG. 7. Of course, it is understood by person of ordinary skill that the metal capped mandrels 32 will be present in the completed interconnect structure or may be removed, if desired, from the completed interconnect structure by a dry etch process like RIE.

References herein to terms such as "vertical", "horizontal", etc. are made by way of example, and not by way of limitation, to establish a frame of reference. The term "horizontal" as used herein is defined as a plane parallel to the conventional plane or surface of substrate 10, regardless of orientation. The term "vertical" refers to a direction perpendicular to the horizontal, as just defined. Terms, such as "on", "above", "below", "side" (as in "sidewall"), "higher", "lower", "over", "beneath" and "under", are defined with respect to the horizontal plane. It is understood that various other frames of reference may be employed without departing from the spirit and scope of the invention.

The fabrication of the semiconductor device has been described by a specific order of fabrication stages and steps. However, it is understood that the order may differ from that described. For example, the order of two or more steps may be altered relative to the order shown. Also, two or more steps may be carried out concurrently or with partial concurrence. In addition, various steps may be omitted and other steps may be added. It is understood that all such variations are within the scope of the invention.

While the present invention has been illustrated by a description of various embodiments and while these embodiments have been described in considerable detail, it is not the intention of the applicants to restrict or in any way limit the scope of the appended claims to such detail. Additional advantages and modifications will

readily appear to those skilled in the art. Thus, the invention in its broader aspects is therefore not limited to the specific details, representative apparatus and method, and illustrative example shown and described. Accordingly, departures may be made from such details without departing from the spirit or scope of applicants' general inventive concept.

#### **CLAIMS**

1. A dielectric material for forming a structure of an integrated circuit, said dielectric material comprising a plurality of carbon nanostructures.

- 2. The dielectric material of claim 1 wherein said carbon nanostructures comprise a plurality of carbon nanotubes.

- 3. The dielectric material of claim 1 wherein said carbon nanostructures comprise a plurality of fluorinated carbon nanotubes.

- 4. The dielectric material of claim 1 wherein said dielectric material has a dielectric constant of less than about 3.

- 5. The dielectric material of claim 1 wherein said structure further comprises at least one conductive feature disposed in said dielectric material.

- 6. The dielectric material of claim 1 wherein said carbon nanostructures comprise a plurality of fluorinated carbon buckyballs.

- 7. The dielectric material of claim 1 further comprising a cap layer on said dielectric material.

- 8. The dielectric material of claim 7 wherein said carbon nanotubes and said cap layer have an effective dielectric constant of less than about 3.

- The dielectric material of claim 1 further comprising:

a copolymer layer binding said carbon nanotubes to define the dielectric material.

- 10. The dielectric material of claim 7 wherein said carbon nanotubes and said copolymer layer have an effective dielectric constant of less than about 3.

11. A semiconductor structure formed on a substrate, comprising: a dielectric layer comprising a plurality of carbon nanostructures; and at least one conductive feature in said dielectric layer, said conductive feature electrically isolated from nearby conductive features by portions of said dielectric layer.

- 12. The semiconductor structure of claim 11 wherein said dielectric layer has an exposed surface, and further comprising:

- a cap layer of an insulating material at least partially covering said exposed surface, said cap layer having a top surface, and said conductive feature having a top surface substantially coplanar with said top surface of said cap layer.

- 13. The semiconductor structure of claim 11 wherein said carbon nanostructures comprise a plurality of carbon nanotubes.

- 14. The semiconductor structure of claim 11 wherein said carbon nanostructures comprise a plurality of fluorinated carbon nanotubes.

- 15. The semiconductor structure of claim 11 wherein said dielectric layer has a dielectric constant of less than about 3.

- 16. The semiconductor structure of claim 11 wherein said structure comprises a plurality of conductors electrically isolated by said layer of said dielectric material.

- 17. The semiconductor structure of claim 11 wherein said carbon nanostructures comprise a plurality of fluorinated carbon buckyballs.

18. The semiconductor structure of claim 11 further comprising: a cap layer disposed on said carbon nanostructures.

- 19. The semiconductor structure of claim 18 wherein said carbon nanostructures and said cap layer collectively have a dielectric constant of less than about 3.

- 20. The semiconductor structure of claim 11 further comprising:

a substrate selected from the group consisting of an interconnect level, a

dielectric material, a buried barrier layer, a metallization line, and a semiconductor

wafer.

- 21. An integrated circuit comprising a plurality of circuit elements and the semiconductor structure of claim 11, said conductive feature being electrically coupled with at least one of said circuit elements.

- 22. The dielectric material of claim 11 further comprising:

a copolymer layer binding said carbon nanotubes to define said dielectric layer.

- 23. The dielectric material of claim 22 wherein said carbon nanotubes and said copolymer layer have an effective dielectric constant of less than about 3.

24. A method for forming a semiconductor structure on a substrate, comprising: forming a dielectric layer comprising a plurality of carbon nanostructures on a surface of the substrate.

- 25. The method of claim 24 wherein forming the dielectric layer comprises: applying the carbon nanostructures on the substrate by a spin-on coating process.

- 26. The method of claim 24 wherein forming the dielectric layer further comprises:

converting the carbon nanostructures to an insulating electronic state.

- 27. The method of claim 26 wherein the carbon nanostructures are converted to the insulating electronic state after the carbon nanostructures are applied.

- 28. The method of claim 26 wherein the carbon nanostructures are converted to the insulating electronic state before the carbon nanostructures are applied.

- 29. The method of claim 24 wherein the carbon nanostructures comprise a plurality of carbon nanotubes, and forming the dielectric layer further comprises: growing the carbon nanotubes on the substrate by a chemical vapor deposition process.

- 30. The method of claim 29 wherein forming the dielectric layer further comprises:

converting the carbon nanotubes to an insulating electronic state.

31. The method of claim 30 wherein the carbon nanotubes are converted to the insulating electronic state after the carbon nanotubes are grown.

32. The method of claim 29 wherein growing the carbon nanotubes further comprises:

depositing a layer of a catalyst material capable of supporting nanotube growth on the substrate; and

supplying a flow of a carbon-containing reactant gas in contact with the catalyst material layer to the substrate under conditions adequate to grow the carbon nanotubes.

33. The method of claim 29 wherein growing the carbon nanotubes further comprises:

supplying a flow of a gas mixture comprising a carbon-containing reactant gas and a catalyst-containing gas across the substrate under conditions adequate to grow the carbon nanotubes.

34. The method of claim 33 wherein growing the carbon nanotubes further comprises:

forming a plurality of mandrels projecting from the substrate at spaced apart locations across the substrate, each of said mandrels including a vertical sidewall capable of supporting carbon-nanotube growth and an upper horizontal surface incapable of supporting carbon nanotube growth; and

directing the gas flow with a substantially horizontal relationship across a horizontal surface of the substrate, the carbon nanotubes growing laterally from the vertical sidewall across the horizontal surface of the substrate.

35. A method for forming a semiconductor structure for an integrated circuit on a substrate, comprising:

forming a dielectric layer including a plurality of carbon nanostructures on the substrate; and

forming at least one conductive feature in the dielectric layer.

36. The method of claim 35 wherein forming the conductive feature further comprises:

patterning the dielectric layer to form at least one opening; and filling the opening with a conductive material to define the conductive feature.

- 37. The method of claim 35 wherein forming the dielectric layer comprises: applying the carbon nanostructures on the substrate by a spin-on coating process.

- 38. The method of claim 35 wherein forming the dielectric layer further comprises:

converting the carbon nanostructures to an insulating electronic state.

- 39. The method of claim 38 wherein the carbon nanostructures are converted to the insulating electronic state after the carbon nanostructures are applied on the substrate.

- 40. The method of claim 38 wherein the carbon nanostructures are converted to the insulating electronic state before the plurality of carbon nanostructures are applied.

- 41. The method of claim 38 wherein the carbon nanostructures comprise carbon nanotubes, and forming the dielectric layer further comprises:

growing the carbon nanotubes on the substrate by a chemical vapor deposition process.

42. The method of claim 41 wherein forming the dielectric layer further comprises:

converting the carbon nanotubes to an insulating electronic state.

43. The method of claim 41 wherein growing the carbon nanotubes further comprises:

depositing a layer of a catalyst capable of supporting nanotube growth on the substrate; and

supplying a flow of a carbon-containing reactant gas in contact with the catalyst layer to the substrate under conditions adequate to grow the of carbon nanotubes.

44. The method of claim 41 wherein growing the carbon nanotubes further comprises:

supplying a flow of a gas mixture comprising a carbon-containing reactant gas and a catalyst-containing gas across the substrate under conditions adequate to grow the carbon nanotubes.

45. The method of claim 44 wherein growing the carbon nanotubes further comprises:

forming a plurality of mandrels projecting from the substrate at spaced apart locations across the substrate, each of said mandrels including a vertical sidewall capable of supporting carbon nanotube growth and an upper horizontal surface incapable of supporting carbon nanotube growth; and

directing the gas flow with a substantially horizontal relationship across a horizontal surface of the substrate, the carbon nanotubes growing laterally from the vertical sidewall across the horizontal surface of the substrate.

4/9

7IG. 4

8/9

9/9

FIG. 9

FIG. 9A

### INTERNATIONAL SEARCH REPORT

International application No.

PCT/US05/35547

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(7) : H01L 21/469  US CL : 438/780: 257/758                                                                                                                                                                                         |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                           |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| B. FIELDS SEARCHED                                                                                                                                                                                                                                                          |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Minimum documentation searched (classification system followed by classification symbols)  U.S.: 438/780: 257/758                                                                                                                                                           |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                               |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) Please See Continuation Sheet                                                                                                                  |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| C. DOC                                                                                                                                                                                                                                                                      | UMENTS CONSIDERED TO BE RELEVANT                                              |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Category *                                                                                                                                                                                                                                                                  | Citation of document, with indication, where a                                | ppropriate, of the relevant passages                                                                                                                                                                | Relevant to claim No.                                                                                                  |  |  |

| X                                                                                                                                                                                                                                                                           | US 6,790,790 (Lyons et al.) 14 September 2004 (14                             | 09.2004) Col. 2 lines 61-67                                                                                                                                                                         | 1, 2, 4, 5, 9, 10                                                                                                      |  |  |

| Y                                                                                                                                                                                                                                                                           | US 2004//0169281(Nguyen et al.) 2 September 2004 (2.09.2004) paragraph [0035] |                                                                                                                                                                                                     | 7,8, 11 - 13,15,16,18-<br>23 23                                                                                        |  |  |

| Y                                                                                                                                                                                                                                                                           | US 2004//0169281(Nguyen et al.) 2 September 2004 (2.09.2004)                  |                                                                                                                                                                                                     | 7, 8, 11-23                                                                                                            |  |  |

| Y                                                                                                                                                                                                                                                                           | US 20020130407 A1 (Dahl et al.) 19 September 2002 (19.09.2002)                |                                                                                                                                                                                                     | 3, 6, 14, 17                                                                                                           |  |  |

|                                                                                                                                                                                                                                                                             |                                                                               |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Further                                                                                                                                                                                                                                                                     | documents are listed in the continuation of Box C.                            | See patent family annex.                                                                                                                                                                            |                                                                                                                        |  |  |

| <ul> <li>Special categories of cited documents:</li> <li>"A" document defining the general state of the art which is not considered to be of particular relevance</li> <li>"E" earlier application or patent published on or after the international filing date</li> </ul> |                                                                               | date and not in conflict with the applic<br>principle or theory underlying the invo<br>"X" document of particular relevance; the<br>considered novel or cannot be considered.                       | date and not in conflict with the application but cited to understand the principle or theory underlying the invention |  |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                                                     |                                                                               | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination |                                                                                                                        |  |  |

| "O" document                                                                                                                                                                                                                                                                | t referring to an oral disclosure, use, exhibition or other means             | being obvious to a person skilled in th                                                                                                                                                             |                                                                                                                        |  |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                      |                                                                               | "&" document member of the same patent family                                                                                                                                                       |                                                                                                                        |  |  |

| Date of the actual completion of the international search                                                                                                                                                                                                                   |                                                                               | Date of mailing of the international search report  17 FEB 2006                                                                                                                                     |                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                             | 006 (18.01.2006) ailing address of the ISA/US                                 |                                                                                                                                                                                                     |                                                                                                                        |  |  |

| Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450                                                                                                                                                                                                    |                                                                               | Authorized officer  Matthew Smith  Telephone No. x                                                                                                                                                  |                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                             | xandria, Virginia 22313-1450<br>b. (571) 273-3201                             |                                                                                                                                                                                                     |                                                                                                                        |  |  |

Form PCT/ISA/210 (second sheet) (April 2005)

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US05/35547

| Box No. II                                                                                                                               | Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1.                                                                                                                                       | Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 2.                                                                                                                                       | Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 3.                                                                                                                                       | Claims Nos.:  because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Box No. III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                          | ional Searching Authority found multiple inventions in this international application, as follows: ontinuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1.                                                                                                                                       | As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.  As all searchable claims could be searched without effort justifying additional fees, this Authority did not invite payment of any additional fees.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:                                                                                               |  |  |

| 4. Remark on                                                                                                                             | No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.: 1-23  Protest  The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.  The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.  No protest accompanied the payment of additional search fees. |  |  |

Form PCT/ISA/210 (continuation of first sheet(2)) (April 2005)

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PCT/US05/35547 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101/0803/3334/ |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ·              |  |  |  |

| BOX III. OBSERVATIONS WHERE UNITY OF INVENTION IS LAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | KING           |  |  |  |

| This application contains the following inventions or groups of inventions which are not so linked as to form a single general inventive concept under PCT Rule 13.1. In order for all inventions to be examined, the appropriate additional examination fees must be paid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |  |  |  |

| Group 1, claim(s) 1-23, drawn to a semiconductor device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |  |  |  |

| Group 2, claim(s) 24-45, drawn to method of forming a semiconductor device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |  |  |  |

| The inventions listed as Groups 1 and 2 do not relate to a single general inventive concept under PCT Rule 13.1 because, under PCT Rule 13.2, they lack the same or corresponding special technical features for the following reasons: The inventions are distinct if either or both of the following can be shown: (1) that the process as claimed can be used to make other and materially different product or (2) that the product as claimed can be made by another and materially different process (MPEP j 806.05(9). In the instant case the product as claimed can be made by another and materially different process. For example, instead of forming at least one conductive feature in the dielectric layer, at least one conductive feature could be pre-formed before the dielectric layer is formed.  Because these inventions are distinct for the reasons given above and have acquired a separate status in the art as shown by their different classification, restriction for examination purposes as indicated is proper. |                |  |  |  |