(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년12월02일

(11) 등록번호 10-1460141

(24) 등록일자 2014년11월04일

(51) 국제특허분류(Int. Cl.)

H01L 27/146 (2006.01) H01L 23/28 (2006.01)

H01L 23/48 (2006.01)

(21) 출원번호 10-2009-7020378

(22) 출원일자(국제) 2008년02월26일

심사청구일자 2013년02월26일

(85) 번역문제출일자 2009년09월29일

(65) 공개번호 10-2010-0014677

(43) 공개일자 2010년02월10일

(86) 국제출원번호 PCT/US2008/002659

(87) 국제공개번호 WO 2008/108970

국제공개일자 2008년09월12일

(30) 우선권주장

60/905,096 2007년03월05일 미국(US)

(56) 선행기술조사문현

US6031274 A

US20060175697 A1

US20060068580 A1

EP1482553 A

전체 청구항 수 : 총 46 항

심사관 : 계원호

(54) 발명의 명칭 관통 비아에 의해 전면 컨택트에 연결되는 배면 컨택트를 갖는 칩

**(57) 요 약**

반도체 요소(100)의 전면(102) 및 배면(114)이 제1 두께를 갖는 얇은 영역(105) 및 제1 두께의 대략 2배 이상의 두께를 갖는 두꺼운 영역을 형성하는 미소전자 유닛이 제공된다. 반도체 소자(112)가 전면에 제공될 수 있으며, 전면에 있는 복수의 제1 도전성 컨택트(116)가 반도체 소자에 접속된다. 복수의 도전성 비아(125)가 배면으로부터 반도체 요소의 얇은 영역(105)을 통하여 제1 도전성 컨택트(116)까지 연장할 수 있다. 복수의 제2 도전성 컨택트(134)가 반도체 요소(100)의 외부에 배치될 수 있다. 복수의 도전성 트레이스(126)가 제2 도전성 컨택트(134)를 도전성 비아(125)에 접속시킬 수 있다.

**대 표 도** - 도1

(72) 발명자

터커맨 레이비드 비.

미국 캘리포니아주 95134 샌 호제 오처드 파크웨이

3025 테세라, 인코포레이티드 내

오가네시안 베이그

미국 캘리포니아주 95134 샌 호제 오처드 파크웨이

3025 테세라, 인코포레이티드

---

## 특허청구의 범위

### 청구항 1

미소전자 유닛에 있어서,

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소로서, 상기 반도체 요소는, 상기 전면에 인접하는 반도체 소자, 상기 전면에 있는 제1 도전성 컨택트, 상기 배면으로부터 부분적으로 상기 반도체 요소를 통해 상기 전면을 향해 연장되는 하나 이상의 제1 개구, 및 상기 전면을 향해 상기 하나 이상의 제1 개구 사이에 연장되는 하나 이상의 제2 개구를 포함하는, 상기 반도체 요소;

상기 하나 이상의 제1 개구 내에 연장되는 하나 이상의 제1 도전성 요소;

상기 하나 이상의 제2 개구 내에 배치되고, 하나 이상의 상기 제1 도전성 컨택트 및 상기 하나 이상의 제1 도전성 요소와 연결되는, 하나 이상의 제2 도전성 요소; 및

상기 하나 이상의 제1 도전성 요소와 접속되는 하나 이상의 제2 도전성 컨택트로서, 상기 제2 도전성 컨택트는 상기 반도체 요소의 외부에 배치되는, 하나 이상의 제2 도전성 컨택트

를 포함하는, 미소전자 유닛.

### 청구항 2

제1항에 있어서,

상기 제1 도전성 컨택트는 전면으로부터 떨어져 바라보는 배면을 가지며, 상기 하나 이상의 제1 개구는 상기 반도체 요소의 두께의 대부분을 통해 연장되고, 복수의 제2 개구 중 하나 이상의 제2 개구는 상기 하나 이상의 제1 개구로부터 연장하여 상기 제1 도전성 컨택트 중 하나의 도전성 컨택트의 표면에 접촉하는,

미소전자 유닛.

### 청구항 3

제1항에 있어서,

상기 반도체 소자가 배치되는 상기 전면의 적어도 일부분 상에 위치하는 커버 요소를 더 포함하는, 미소전자 유닛.

### 청구항 4

제1항에 있어서,

상기 반도체 요소는 상기 전면에 인접하고 상기 배면을 향해 연장되는 트렌치 커패시터의 어레이를 포함하며, 하나 이상의 제1 구멍부가 상기 어레이와 정합(registration)하지 않는, 미소전자 유닛.

### 청구항 5

제1항에 있어서,

상기 하나 이상의 제2 개구는 상기 전면으로부터의 깊이가 증가함에 따라 작아지는 폭을 갖도록 상기 전면으로부터 상기 배면을 향하는 방향으로 테이퍼되는, 미소전자 유닛.

### 청구항 6

제1항에 있어서,

상기 하나 이상의 제2 개구는 상기 전면으로부터의 깊이가 증가함에 따라 커지는 폭을 갖도록 상기 배면으로부터 상기 전면을 향하는 방향으로 테이퍼되는, 미소전자 유닛.

### 청구항 7

제1항에 있어서,

상기 하나 이상의 제1 개구는 상기 전면을 따라가는 방향의 제1 치수를 갖고, 상기 하나 이상의 제2 개구는 상기 전면을 따라가는 방향의 제2 치수를 갖고, 상기 제2 치수는 상기 제1 치수보다 작은, 미소전자 유닛.

#### 청구항 8

각 미소전자 유닛이 청구항 1에서 청구된 바와 같은 복수의 미소전자 유닛을 포함하는 적층된 미소전자 조립체로서,

적어도 일부의 미소전자 유닛의 제1 도전성 컨택트가 나머지의 미소전자 유닛의 배면에 노출된 제2 도전성 컨택트와 도전 접속되는,

적층된 미소전자 조립체.

#### 청구항 9

제8항에 있어서,

상기 적어도 일부의 미소전자 유닛의 상기 제1 도전성 컨택트는 하나 이상의 스터드 범프(stud bump) 또는 하나 이상의 솔더(solder)를 통해 나머지의 미소전자 유닛의 제2 도전성 컨택트와 도전 접속되는,

적층된 미소전자 조립체.

#### 청구항 10

미소전자 유닛에 있어서,

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소로서, 상기 전면 및 상기 배면은 제1 두께를 갖는 얇은 영역 및 상기 제1 두께의 2배 이상인 제2 두께를 갖는 두꺼운 영역을 형성하고, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자, 상기 반도체 소자와 연결되는 상기 전면에 있는 복수의 제1 도전성 컨택트, 및 상기 반도체 요소의 배면으로부터 상기 반도체 요소의 얇은 영역을 통해 상기 제1 도전성 컨택트로 연장되는 복수의 도전성 비아(via)를 포함하며, 상기 복수의 제1 도전성 컨택트의 각각은 상기 반도체 요소의 상기 전면으로부터 떨어져 바라보는 표면을 가지고, 상기 도전성 비아는 상기 제1 도전성 컨택트의 상기 표면에 접촉하는 금속을 포함하는, 상기 반도체 요소;

상기 반도체 요소의 외부에 노출되는 복수의 제2 도전성 컨택트; 및

상기 제2 도전성 컨택트를 상기 도전성 비아로 연결시키는 복수의 도전성 트레이스

를 포함하는, 미소전자 유닛.

#### 청구항 11

제10항에 있어서,

상기 제2 도전성 컨택트는 상기 배면에 있는 상기 두꺼운 영역 상에 위치하는, 미소전자 유닛.

#### 청구항 12

제10항에 있어서,

상기 반도체 요소의 상기 배면 상에 위치하는 유전체층을 더 포함하는, 미소전자 유닛.

#### 청구항 13

제12항에 있어서,

상기 제2 도전성 컨택트 및 도전성 트레이스는 상기 유전체층 상에 위치하는, 미소전자 유닛.

#### 청구항 14

제10항에 있어서,

상기 반도체 소자가 배치되는 상기 전면의 적어도 일부분 상에 위치하는 커버 요소를 더 포함하는, 미소전자 유

닛.

### 청구항 15

청구항 10에서 청구된 바와 같은 미소전자 유닛을 포함하는 조립체로서,

상기 반도체 요소의 상기 배면 상에 위치하는 컴플라이언트 유전체층(compliant dielectric layer)을 더 포함하고, 상기 제2 도전성 컨택트에 결합되는 단자를 갖는 회로 패널을 더 포함하고,

상기 유전체층의 탄성 계수와 상기 유전체층의 두께는 상기 미소전자 유닛과 상기 회로 패널 간의 열팽창 불일치를 보상하기에 충분한 정도로 형성되는,

조립체.

### 청구항 16

청구항 10에 청구된 바와 같은 미소전자 유닛을 포함하는 카메라 모듈로서,

상기 반도체 소자가 활성 영역을 포함하며, 상기 카메라 모듈이 상기 전면의 적어도 일부분 상에 위치하는 커버 요소 및 상기 활성 영역에 정합하여 상기 커버 요소에 탑재된 광학 요소를 갖는 광학 유닛을 더 포함하는, 카메라 모듈.

### 청구항 17

청구항 10에 청구된 바와 같은 미소전자 유닛을 제조하는 방법으로서,

상기 반도체 요소는 상기 전면으로부터 이격된 배면을 갖고,

상기 미소전자 유닛을 제조하는 방법은, 상기 제2 도전성 컨택트 및 도전성 트레이스를 형성하기 전에, 상기 배면 상에 위치하는 유전체층을 전해도금(electrodeposition)하는 단계를 포함하고, 상기 제2 도전성 컨택트 및 도전성 트레이스는 상기 유전체층 상에 위치하도록 형성되는,

미소전자 유닛을 제조하는 방법.

### 청구항 18

청구항 10에 청구된 바와 같은 미소전자 유닛을 제조하는 방법으로서,

상기 배면으로부터 상기 제2 두께와 적어도 실질적으로 동일한 두께 아래로 박막화하는 단계를 포함하고,

(a) 단계 이후에, (b) 상기 얇은 영역을 형성하도록 상기 반도체 요소의 일부의 두께를 상기 반도체 요소의 전체의 두께보다 얇게 박막화시키는 단계를 수행하는,

미소전자 유닛을 제조하는 방법.

### 청구항 19

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소로서, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자, 상기 전면에서 노출되어 있는 도전성 전면 컨택트, 및 상기 배면에서 노출되어 있는 도전성 배면 컨택트를 갖는, 상기 반도체 요소;

상기 도전성 전면 컨택트에 접속되고, 상기 전면으로부터 하방향으로 연장하는 복수의 도전성 비아;

하나 이상의 상기 도전성 비아와 정합(registration)하여 상기 배면으로부터 하방향으로 연장하는 개구; 및

상기 개구의 벽부를 따라 하나 이상의 상기 도전성 비아로부터 상방향으로 연장하고, 하나 이상의 상기 도전성 배면 컨택트에 접속되는 도전성 트레이스

를 포함하는 미소전자 유닛.

### 청구항 20

제19항에 있어서,

상기 전면으로부터의 상기 복수의 도전성 비아의 최대 깊이는 상기 배면으로부터의 상기 개구의 최대 깊이보다

작은, 미소전자 유닛.

### 청구항 21

제19항에 있어서,

상기 개구는 상기 복수의 도전성 비아와 정합하고 있으며, 상기 미소전자 유닛은 복수의 도전성 트레이스를 포함하며, 각각의 상기 도전성 트레이스는 상기 복수의 도전성 비아 중의 하나를 상기 복수의 도전성 배면 컨택트 중의 하나에 접속시키는, 미소전자 유닛.

### 청구항 22

청구항 19에서 청구된 바와 같은 미소전자 유닛을 복수 개로 포함하는 적층된 미소전자 조립체로서, 상기 미소전자 유닛의 일부의 미소전자 유닛의 도전성 전면 컨택트가 상기 미소전자 유닛의 다른 미소전자 유닛의 도전성 배면 컨택트에 도전 가능하게 접속되는, 적층된 미소전자 조립체.

### 청구항 23

제19항에 있어서,

상기 도전성 트레이스 및 상기 개구의 벽부 상에 위치하는 유전체 재료를 더 포함하는, 미소전자 유닛.

### 청구항 24

제19항에 있어서,

상기 반도체 요소는 상기 전면으로부터 하방향으로 연장하는 트렌치 커페시터의 어레이를 포함하며, 상기 개구는 상기 어레이와 정합하지 않는, 미소전자 유닛.

### 청구항 25

제19항에 있어서,

좌측 도전성 트레이스 및 우측 도전성 트레이스를 갖는 복수의 도전성 트레이스를 더 포함하며, 각각의 상기 좌측 도전성 트레이스는 상기 도전성 비아를 좌측의 도전성 배면 컨택트에 접속시키고, 각각의 우측 도전성 트레이스는 상기 도전성 비아를 우측의 도전성 배면 컨택트에 접속시키는, 미소전자 유닛.

### 청구항 26

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소로서, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자 및 상기 배면에서 노출되어 있는 도전성 배면 컨택트를 갖는, 상기 반도체 요소;

상기 전면으로부터 하방향으로 연장하는 복수의 도전성 비아;

하나 이상의 상기 복수의 도전성 비아와 정합하여 상기 배면으로부터 하방향으로 연장하는 개구; 및

상기 개구 내의 상기 복수의 도전성 비아 중의 하나에 결합(join)되고, 상기 도전성 비아로부터 상기 배면에 의해 정해진 평면 위의 위치까지 연장하는 도전성 범프

를 포함하는 미소전자 유닛.

### 청구항 27

제26항에 있어서,

상기 도전성 범프는 솔더 범프를 포함하는, 미소전자 유닛.

### 청구항 28

제26항에 있어서,

상기 도전성 범프는 스터드 범프(stud bump)를 포함하는, 미소전자 유닛.

### 청구항 29

청구항 26에서 청구된 바와 같은 미소전자 유닛을 복수 개로 포함하는 적층된 미소전자 조립체로서, 상기 미소전자 유닛의 일부의 미소전자 유닛의 도전성 범프가, 상기 일부의 미소전자 유닛의 전면에 있는 도전성 비아를 상기 미소전자 유닛의 다른 미소전자 유닛의 개구 내의 도전성 비아에 접속시키는, 적층된 미소전자 조립체.

### 청구항 30

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소로서, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자 및 상기 배면에 노출되어 있는 도전성 배면 컨택트를 갖는, 상기 반도체 요소;

상기 전면으로부터 하방향으로 연장하는 복수의 도전성 비아;

하나 이상의 상기 도전성 비아와 정합하여 상기 배면으로부터 하방향으로 연장하는 개구; 및

상기 전면에서 상기 도전성 비아 중의 하나에 결합되고, 상기 전면으로부터 상방향으로 연장하는 도전성 범프를 포함하는 미소전자 유닛.

### 청구항 31

청구항 30에서 청구된 바와 같은 미소전자 유닛을 복수 개로 포함하는 적층된 미소전자 조립체로서, 상기 미소전자 유닛의 일부의 미소전자 유닛의 도전성 범프가, 상기 일부의 미소전자 유닛의 전면에 있는 도전성 비아를 상기 미소전자 유닛의 다른 미소전자 유닛의 개구 내의 도전성 비아에 접속시키는, 적층된 미소전자 조립체.

### 청구항 32

미소전자 유닛을 제조하는 방법에 있어서,

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소를 제공하는 단계로서, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자, 상기 전면에서 상기 반도체 소자에 접속되는 제1 도전성 컨택트, 및 상기 배면으로부터 상기 반도체 요소를 통해 상기 제1 도전성 컨택트까지 연장하는 복수의 도전성 비아를 포함하는, 상기 반도체 요소 제공 단계; 및

상기 배면 상에 위치하는 복수의 제2 도전성 컨택트와, 상기 제2 도전성 컨택트를 상기 도전성 비아에 접속시키는 복수의 도전성 트레이스를 형성하는 단계

를 포함하는 미소전자 유닛의 제조 방법.

### 청구항 33

제32항에 있어서,

상기 반도체 요소는, 상기 제1 도전성 컨택트 상에 위치하는 제1 두께를 갖는 얇은 영역과, 상기 제1 두께의 2 배 이상인 제2 두께를 갖는 두꺼운 영역을 포함하는, 미소전자 유닛의 제조 방법.

### 청구항 34

제33항에 있어서,

상기 제2 도전성 컨택트를 형성하기 전에, 상기 반도체 요소를 상기 전면 상에 위치하는 커버 요소와 함께 조립하는 단계를 더 포함하는, 미소전자 유닛의 제조 방법.

### 청구항 35

제34항에 있어서,

상기 제2 도전성 컨택트 및 상기 도전성 트레이스를 형성하기 전에 상기 배면 상에 위치하는 유전체층을 형성하는 단계를 더 포함하며, 상기 제2 도전성 컨택트 및 상기 도전성 트레이스는 상기 유전체층 상에 위치하도록 형성되는, 미소전자 유닛의 제조 방법.

### 청구항 36

미소전자 유닛을 제조하는 방법에 있어서,

전면 및 상기 전면으로부터 이격되어 있는 배면을 갖는 반도체 요소를 제공하는 단계로서, 상기 반도체 요소는, 상기 전면에 있는 반도체 소자, 상기 전면에서 상기 반도체 소자에 접속되는 제1 도전성 컨택트, 상기 배면에서 노출되어 있는 반도체 재료, 및 상기 배면으로부터 반도체 요소를 통하여 상기 제1 도전성 컨택트까지 연장하는 복수의 관통 구멍부를 포함하는, 상기 반도체 요소 제공 단계;

상기 배면에 노출되어 있는 상기 반도체 재료 상에 또한 상기 관통 구멍부를 따라 배면 유전체층을 전해도금 (electrodeposition)하는 단계; 및

상기 배면 상에 위치하는 제2 도전성 컨택트를 형성하고, 상기 관통 구멍부 내에 상기 제1 도전성 컨택트와 접촉하는 복수의 도전성 비아를 형성하며, 상기 제2 도전성 컨택트를 상기 도전성 비아에 접속시키는 복수의 도전성 트레이스를 형성하는 단계

를 포함하는 미소전자 유닛의 제조 방법.

### 청구항 37

미소전자 유닛을 제조하는 방법에 있어서,

(a) 반도체 요소의 전면에서 반도체 소자에 접속되는 제1 도전성 컨택트, 상기 전면으로부터 떨어져 있는 배면, 상기 배면으로부터 상기 반도체 요소를 통하여 상기 제1 도전성 컨택트까지 연장하는 복수의 관통 구멍부, 및 상기 배면 및 상기 관통 구멍부의 벽부에 노출되어 있는 반도체 재료를 갖는 반도체 요소의 전면 상에 위치하는 커버 요소와 함께 상기 반도체 요소를 조립하여, 유닛을 형성하는 단계;

(b) 상기 배면에 노출되어 있는 상기 반도체 재료 상에 또한 상기 관통 구멍부의 벽부를 따라 유전체층을 전해도금 (electrodeposition)하는 단계; 및

(c) 상기 유전체층 위에, (i) 상기 관통 구멍부 내에서 상기 제1 도전성 컨택트와 접촉하는 도전성 비아, (ii) 상기 배면 상에 위치하는 복수의 제2 도전성 컨택트, 및 (iii) 상기 도전성 비아를 상기 제2 도전성 컨택트에 접속시키는 복수의 도전성 트레이스를 형성하는 단계

를 포함하는 미소전자 유닛의 제조 방법.

### 청구항 38

제37항에 있어서,

상기 커버 요소는 상기 반도체 요소의 상기 전면으로부터 떨어져 있는 외부면을 가지며, 상기 커버 요소는 상기 외부면에 노출된 유전체 재료를 포함하는, 미소전자 유닛의 제조 방법.

### 청구항 39

제37항에 있어서,

상기 반도체 요소는 상기 전면과 상기 배면 사이에 제1 두께를 갖는 제1 부분을 포함하며,

상기 미소전자 유닛의 제조 방법은,

상기 (a) 단계와 상기 (b) 단계 사이에, 상기 제1 부분보다 얇은 박막화 부분을 형성하기 위해 상기 제1 도전성 컨택트 상에 위치하는 상기 반도체 요소의 부분을 박막화하는 단계를 더 포함하며,

상기 관통 구멍부가 상기 박막화 부분을 관통하여 연장하는,

미소전자 유닛의 제조 방법.

### 청구항 40

제39항에 있어서,

(d) 상기 미소전자 유닛을 복수의 다이싱 레인을 따라 복수의 괴복된 칩 단위로 절단하는 단계를 더 포함하는, 미소전자 유닛의 제조 방법.

### 청구항 41

제39항에 있어서,

상기 박막화 부분을 형성하기 위한 박막화하는 단계를 수행하기 전에, 상기 제1 부분의 두께를 감소시키기 위해 상기 배면으로부터 상기 반도체 요소를 그라인딩하는 단계를 더 포함하는, 미소전자 유닛의 제조 방법.

#### 청구항 42

제41항에 있어서,

상기 반도체 요소는 제1 도전성 컨택트와 상기 반도체 요소의 반도체 재료 사이에 배치된 전면 유전체층을 포함하며,

상기 미소전자 유닛의 제조 방법은, 상기 (c) 단계를 수행하기 전에, 상기 전면 유전체층이 노출될 때까지 상기 반도체 요소를 에칭하고, 상기 관통 구멍부 내의 상기 제1 도전성 컨택트 상에 위치하는 상기 전면 유전체층의 부분을 제거함으로써, 복수의 관통 구멍부를 형성하는 단계를 더 포함하는,

미소전자 유닛의 제조 방법.

#### 청구항 43

제42항에 있어서,

상기 전면 유전체층의 부분은 상기 (b) 단계 후에 제거되는, 미소전자 유닛의 제조 방법.

#### 청구항 44

제40항에 있어서,

복수의 외부 컨택트를 형성하는 단계는 복수의 금속성 범프를 형성하는 단계를 포함하는, 미소전자 유닛의 제조 방법.

#### 청구항 45

제37항에 있어서,

상기 배면 유전체층을 전해도금하는 단계는, 상기 미소전자 유닛의 외부면을 유체 중합성 조성물과 접촉시키고, 상기 배면 유전체층을 전기 영동 방식으로 증착시키기 위해 상기 유체 중합성 조성물을 통해 전류를 인가하는 단계를 포함하는, 미소전자 유닛의 제조 방법.

#### 청구항 46

제39항에 있어서,

반도체칩은 촬상 영역을 포함하며,

상기 미소전자 유닛의 제조 방법은, 카메라 모듈을 형성하기 위해 상기 촬상 영역과 정합하여 광학 요소를 갖는 광학 유닛과 함께 상기 유닛을 조립하는 단계를 더 포함하며, 상기 광학 요소는 커버 요소에 의해 상기 반도체 요소로부터 분리되는, 미소전자 유닛의 제조 방법.

## 명세서

### 기술 분야

[0001]

본 출원은 2007년 3월 5일자로 출원된 미국 가출원 번호 60/905,096호를 우선권으로 주장하며, 상기 특허 출원은 그 개시 내용이 본 명세서에 원용되어 있다.

[0002]

본 발명은 미소전자 소자의 패키징에 관한 것으로, 보다 구체적으로는 반도체 소자의 패키징에 관한 것이다.

### 배경 기술

[0003]

특정 유형의 미소전자 소자 및 반도체칩은 음향 트랜스듀서(acoustic transducer), 무선 주파수 에미터, 무선

주파수 검출기, 광전 소자, 또는 이들 소자의 조합 등의 소자를 포함한다. 이러한 소자는 통상적으로 음향, 무선 주파수 또는 광파장 에너지를 반도체칩의 면에 있는 소자에 통과시키고 또한 반도체칩의 면에 있는 소자로부터 음향, 무선 주파수 또는 광파장 에너지를 통과시킬 수 있는 패키징을 필요로 한다.

[0004] 이러한 소자가 미소전자 소자의 전면에서 노출되는 경우도 있기 때문에, 이들 소자들은 일반적으로 먼지, 다른 입자, 오염물 또는 습기 등의 요소로부터 보호할 필요가 있다. 이러한 이유로, 초기 처리 단계에서 이러한 미소전자 소자의 전면을 덮는 리드(lid) 또는 다른 구성요소와 함께 미소전자 소자를 조립하는 것이 이롭다.

[0005] 일부 유형의 미소전자 시스템에서는 칩 및 매우 작은 패키지, 즉 칩 스케일 패키지를 갖는 패키징된 칩을 회로 패널에 탑재하는 것이 바람직하다. 일부 경우에는, 하나의 칩 위에 다른 칩이 위치하도록 칩을 서로 적층 및 상호접속시켜 조립체의 회로 밀도를 증가시키는 것이 요망된다.

[0006] 일부 유형의 대량 생산 칩은 또한 패키징 비용을 엄격하게 통제할 필요가 있다. 이러한 반도체칩을 패키징하기 위해 사용되는 처리는 칩을 웨이퍼 또는 웨이퍼의 일부분의 형태로 서로에 대해 부착된 상태를 유지하면서 다수의 칩에 대해 동시에 수행될 수 있다. 이러한 "웨이퍼 레벨" 처리는 통상적으로 전체 웨이퍼에 가해지는 일련의 공정에 의해 수행되며, 그 후에 웨이퍼가 개별 칩으로 다이싱(dicing)된다. 웨이퍼 레벨 패키징 공정은 원래의 반도체칩과 동일한 면적 치수를 갖는 패키징된 칩을 생성하므로, 회로 패널 등의 위의 이들의 상호접속부를 소형화한다.

### 발명의 상세한 설명

[0007] 본 발명의 특징에 따라, 미소전자 유닛은 전면 및 전면으로부터 떨어져 있는 배면을 갖는 반도체 요소가 제공된다. 전면 및 배면은 제1 두께를 갖는 얇은 영역 및 제1 두께의 대략 2배 이상인 제2 두께를 갖는 두꺼운 영역을 형성할 수 있다. 이러한 미소전자 유닛에서, 반도체 요소는 전면에 있는 반도체 소자 및 전면에서 반도체 소자에 연결되는 복수의 제1 도전성 컨택트를 포함할 수 있다. 배면으로부터 반도체 요소의 얇은 영역을 관통하여 제1 도전성 컨택트까지 복수의 도전성 비아(via)가 연장할 수도 있다. 복수의 제2 도전성 컨택트가 반도체 요소의 외부에 노출될 수 있으며, 복수의 도전성 트레이스가 제2 도전성 컨택트를 도전성 비아에 연결할 수 있다.

[0008] 본 발명의 다른 특징에 따라 미소전자 유닛에서, 반도체 요소는 전면, 전면에 있는 반도체 소자, 및 전면으로부터 떨어져 있는 배면을 갖는다. 전면에는 제1 도전성 컨택트가 제공될 수도 있다. 반도체 요소는 또한 배면으로부터 부분적으로 반도체 요소를 관통하여 전면을 향해 연장하는 제1 깊이의 제1 구멍부를 가질 수도 있다. 제2 구멍부는 제1 구멍부로부터 제1 도전성 컨택트까지 연장하는 제2 깊이를 가질 수 있다. 복수의 제1 도전성 비아는 제2 구멍부의 벽부를 따라 연장하여 제1 도전성 컨택트에 접촉할 것이다. 제1 도전성 비아에는 복수의 도전성 상호접속부가 접속될 것이다. 일실시예에서, 이러한 도전성 상호접속부는 제1 구멍부의 벽부를 따라 연장할 수도 있다. 복수의 제2 도전성 컨택트가 도전성 상호접속부에 접속될 수도 있다. 일례에서, 제2 컨택트는 반도체 요소의 외부에서 노출될 수도 있다.

[0009] 본 발명의 특징에 따라, 전면, 전면에 있는 반도체 소자, 및 전면에서 반도체 소자에 연결되는 복수의 제1 도전성 컨택트를 갖는 반도체 요소를 포함하는 미소전자 유닛이 제공된다. 반도체 요소의 전면을 마주보는 내부면 및 내부면으로부터 떨어져 있는 외부면을 갖는 리드가 제공될 수도 있다. 제1 깊이를 갖는 제1 구멍부는 외부면으로부터 적어도 부분적으로 리드를 관통하여 내부면을 향해 연장할 수도 있다. 반도체 요소의 전면 위에서 리드의 내부면을 지지하는 지지 구조가 제공될 수도 있다. 일례에서, 지지 구조는 제1 구멍부와 정렬되는 제2 구멍부를 갖는다. 제2 구멍부는 지지 구조를 통해 제1 도전성 컨택트까지 연장할 수도 있다. 복수의 제1 도전성 비아가 제2 구멍부의 벽부를 따라 연장하여 제1 도전성 컨택트에 접촉할 수도 있다. 복수의 제2 도전성 비아가 제1 구멍부의 벽부를 따라 연장할 수도 있다. 복수의 제2 도전성 컨택트가 리드의 외부에서 노출될 수도 있다. 일례에서, 복수의 도전성 트레이스가 이러한 제2 도전성 컨택트를 도전성 비아에 연결한다.

[0010] 본 발명의 특징에 따라, 전면 및 전면에 있는 반도체 소자를 갖는 반도체 요소를 포함하는 미소전자 유닛이 제공된다. 반도체 소자에 연결되는 복수의 제1 도전성 컨택트가 전면에 제공될 수도 있다. 미소전자 유닛은, 또한, 반도체 요소의 전면을 마주보는 내부면 및 이 내부면으로부터 떨어져 있는 외부면을 갖는 리드를 포함할 수도 있다. 리드의 내부면 및 외부면은 제1 두께를 갖는 얇은 영역과 제1 두께의 대략 2배인 제2 두께를 갖는 두꺼운 영역을 형성할 수도 있다. 이러한 리드는, 또한, 외부면으로부터 리드의 얇은 영역을 통해 연장하여 제1 도전성 컨택트에 접속하는 복수의 도전성 비아를 포함할 수도 있다. 이러한 미소전자 유닛은 또한 복수의 제2 도전성 컨택트를 포함할 수 있다. 복수의 도전성 트레이스가 제2 도전성 컨택트를 도전성 비아에 접속시킬 수

도 있다.

[0011] 본 발명의 특징에 따라, 반도체 요소의 전면을 마주보는 내부면 및 내부면으로부터 떨어져 있는 외부면을 갖는 리드를 포함하는 미소전자 유닛이 제공된다. 복수의 도전성 비아는 리드를 통해 연장하여 제1 도전성 컨택트에 접촉할 수도 있다. 이러한 미소전자 유닛은 또한 리드의 외부면 위에 위치하는 복수의 제2 도전성 컨택트를 포함할 수 있다. 복수의 도전성 트레이스는 제2 도전성 컨택트를 도전성 비아에 연결할 수 있다.

[0012] 본 발명의 특징에 따라, 전면, 전면에 있는 반도체 소자, 및 전면으로부터 떨어져 있는 배면을 갖는 반도체 요소를 포함하는 미소전자 유닛이 제공된다. 전면에는 도전성 전면 컨택트가 노출될 수도 있다. 배면에는 도전성 배면 컨택트가 노출될 수도 있다. 도전성 전면 컨택트에는, 전면으로부터 하방향으로 연장하는 복수의 도전성 비아가 접속될 수도 있다. 하나 이상의 도전성 비아와 정합(registration)하여 배면으로부터 하방향으로 개구가 연장할 수 있다. 개구의 벽부를 따라 하나 이상의 도전성 비아로부터 상방향으로 도전성 트레이스가 연장할 수 있다. 이러한 도전성 트레이스는 도전성 배면 컨택트 중의 하나 이상에 접속될 수 있다.

[0013] 본 발명의 특징에 따라, 전면, 전면에 있는 반도체 소자, 및 전면으로부터 떨어져 있는 배면을 갖는 반도체 요소를 포함하는 미소전자 유닛이 제공된다. 배면에는 도전성 배면 컨택트가 노출될 수도 있다. 이러한 미소전자 유닛에서, 복수의 도전성 비아가 전면으로부터 하방향으로 연장할 수도 있다. 하나 이상의 도전성 비아와 정합하여 배면으로부터 하방향으로 개구가 연장할 수 있다. 개구 내의 도전성 비아 중의 하나에 도전성 범프가 결합(join)될 수 있다. 이러한 경우, 도전성 범프는 도전성 비아로부터 배면에 의해 정해진 평면 위의 위치까지 연장할 것이다.

[0014] 본 발명의 특징에 따라, 전면, 전면에 있는 반도체 소자, 및 전면으로부터 떨어져 있는 배면을 갖는 반도체 요소를 포함하는 미소전자 유닛이 제공된다. 배면에는 도전성 배면 컨택트가 노출될 수도 있다. 복수의 도전성 비아가 전면으로부터 하방향으로 연장할 수 있다. 도전성 비아의 적어도 하나와 정합하여 배면으로부터 하방향으로 개구가 연장할 수 있다. 전면에 있는 도전성 비아 중의 하나에 도전성 범프가 결합될 수 있다. 도전성 범프는 예컨대 전면으로부터 상방향으로 연장할 것이다.

[0015] 본 발명의 다른 특징에 따라 미소전자 유닛을 제조하는 방법이 제공된다. 이러한 방법은, 전면, 전면으로부터 떨어져 있는 배면, 및 전면에 있는 반도체 소자를 갖는 반도체 요소를 제공하는 단계를 포함할 것이다. 반도체 소자에 접속되는 제1 도전성 컨택트는 반도체 요소의 전면에 제공될 것이다. 복수의 도전성 비아가 배면으로부터 반도체 요소를 통해 제1 도전성 컨택트까지 연장할 것이다. 이러한 방법은, 배면 위에 위치하는 복수의 제2 도전성 컨택트와, 제2 도전성 컨택트를 도전성 비아에 접속시키는 복수의 도전성 트레이스를 형성하는 단계를 더 포함할 것이다.

[0016] 본 발명의 다른 특징에 따라, 전면 및 전면에 있는 반도체 소자를 포함하는 반도체 요소가 제공되는 미소전자 유닛을 제조하는 방법이 제공된다. 전면에 있는 제1 도전성 컨택트는 반도체 소자에 접속될 것이다. 반도체 요소는 또한 전면으로부터 떨어져 있는 배면 및 배면에 노출되어 있는 반도체 재료를 더 포함할 것이다. 배면으로부터 반도체 요소를 통하여 제1 도전성 컨택트까지 복수의 관통 구멍부가 연장할 수도 있다. 배면에 노출되어 있는 반도체 재료 상으로, 관통 구멍부의 벽부 또는 양자를 따라, 배면 유전체층이 전해도금(electrodeposition)될 수도 있다. 제2 도전성 컨택트가 배면 상에 위치할 수도 있다. 관통 구멍부 내에는, 제1 도전성 컨택트와 접촉하는 복수의 도전성 비아가 형성될 수도 있다. 제2 도전성 컨택트를 도전성 비아에 접속시키는 복수의 도전성 트레이스가 형성될 수도 있다.

[0017] 본 발명의 다른 실시예에 따라 미소전자 유닛을 제조하는 방법이 제공된다. 이러한 방법은, 반도체 요소를 반도체 요소의 전면 위에 위치하는 커버 요소와 함께 조립하여 유닛을 형성하는 단계를 포함할 것이다. 반도체 요소는 또한 전면에서 반도체 소자에 접속된 제1 도전성 컨택트를 가질 것이다. 전면으로부터 떨어져 있는 배면이 제공될 수 있다. 배면으로부터 반도체 요소를 통하여 제1 도전성 컨택트까지 복수의 관통 구멍부가 연장할 수도 있다. 일실시예에서는, 배면 및 관통 구멍부의 벽부에서 반도체 재료가 노출된다.

[0018] 유전체층이 배면에 노출되어 있고 또한 관통 구멍부를 따라 노출되어 있는 반도체 재료 상에 위치하도록 전해도금될 수 있다. 또한, 유전체층이 그 유전체층 위에 전해도금될 수 있으며, 이로써 제1 도전성 컨택트와 접촉하는 도전성 비아가 관통 구멍부 내에 형성된다. 복수의 제2 도전성 컨택트가 배면 위에 위치할 수도 있으며, 복수의 도전성 트레이스가 도전성 비아를 제2 도전성 컨택트에 접속시킬 수도 있다.

## 실시예

[0063]

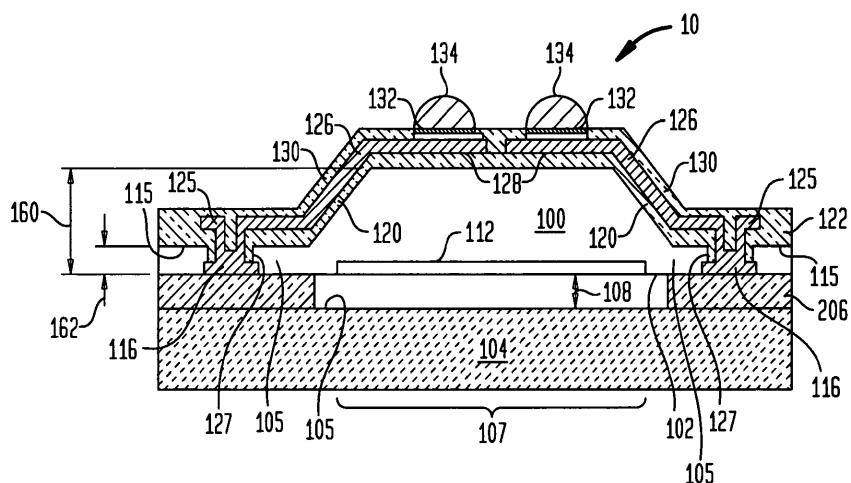

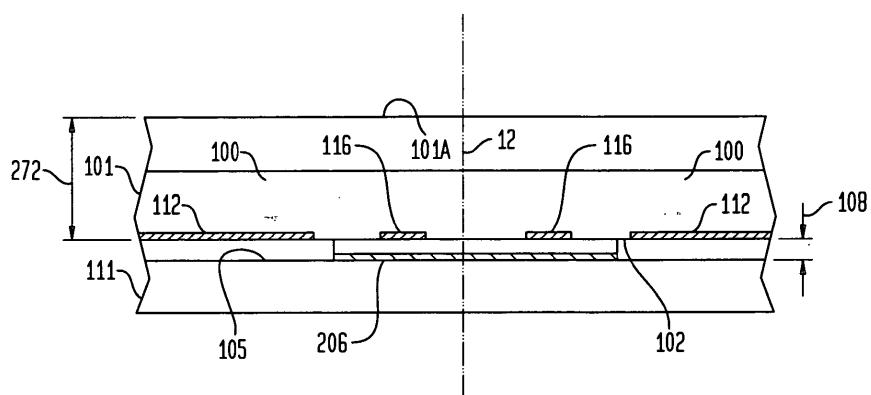

도 1은 본 발명의 실시예에 따른 패키징된 반도체칩(10)의 단면도이다. 도 1에 예시된 바와 같이, 패키징된 반도체칩은 반도체칩의 전면(102)이 아래로 향하는 배향으로 도시되어 있다. 도 1에 예시된 바와 같이, 패키징된 반도체칩은 전면(102) 및 전면으로부터 떨어져 있는 배면(114)을 갖는 반도체칩(100)을 포함한다. 반도체칩(100)의 전면은 반도체칩(100)과 함께 조립되는 리드 또는 커버(104)에 의해 덮여져, 패키징된 반도체칩(10)을 형성한다. 도 1에 예시된 바와 같이, 반도체칩(100)의 전면(102)은 리드(104)의 상방향으로 향하는 내부면(105)을 향해 하방향으로 지향된다. 반도체칩(100)은 통상적으로 하나 또는 복수의 반도체 소자(112)가 전면(102) 아래에 있는 소자 영역에 배치되는 반도체 기판을 포함한다. 반도체칩(100)은 또한 기판 위에 위치하는 복수의 유전체층을 포함하며, 그 안에 도전성 금속 배선층 및 비아(도시하지 않음)가 배치된다. 반도체 소자(112)는 반도체칩의 전면에 및/또는 반도체칩의 전면과 배면 사이에 배치된다. 패키징된 반도체칩(10)의 외부측면 치수(예컨대, 화살표 102의 방향에서의)가 패키징되지 않은 반도체칩에 대한 외부측면 치수와 대략 동일하기 때문에, 패키징된 반도체칩은 칩-스케일 패키지("CSP")로도 지칭될 수 있다.

[0064]

반도체칩(100)은 통상적으로 접착제, 무기 또는 유기 재료, 및/또는 결합 금속(joining metal)을 포함할 수도 있는 하나 이상의 스탠드오프 구조(standoff structure)(124)를 통해 리드(104)에 접속된다. 반도체칩으로부터 일정한 이격을 두고 리드를 지지하기 위한 구조는, 2006년 1월 23일자로 출원되어 공동 소유된 US 출원 번호 60/761,171, 및 2006년 2월 21일자로 출원된 US 출원 60/775,068에 개시되어 있으며, 상기 특허 출원의 개시 내용은 본 명세서에 원용되어 있다. 패키징된 반도체칩은, 도 1에 예시된 바와 같이, 반도체칩의 전면(102)과 리드(104)의 내부면(105) 사이에 내부 캐비티(106)를 포함할 수도 있다. 이와 달리, 패키징된 반도체칩(10)은 내부 캐비티 없이 구성될 수도 있다. 캐비티가 존재할 때, 캐비티의 높이(108)와 측면 치수(110)를 포함한 측면 치수들은 예컨대 리드(104)와 반도체칩(100)을 조립하기 위해 사용된 스탠드오프 구조(124)의 높이 및 치수에 의해 결정된다. 특정의 실시예에서, 리드(104)는 글래스 또는 중합성 재료로 구성될 필요가 있으며, 대상으로 하는 주파수에서의 전자기 스펙트럼에 적어도 부분적으로 투명하다. 리드(104)는 필터 기능을 제공하기 위해 부분적으로만 투명하게 될 수도 있고, 또는 대상으로 하는 주파수의 범위에 대해 필수적으로 투명하게 될 수도 있다.

[0065]

반도체칩(100) 내의 반도체 소자(112)는 통상적으로 전자기 방사를 검출하거나 출력하는 중의 하나를 행하는 전자기 소자 또는 전자-광학 소자와 같은 전자기 트랜스듀서 소자를 포함한다. 반도체 소자는 무선 주파수 및/또는 광파장을 방출하거나 수신하도록 설계될 수도 있으며, 이러한 광파장으로는 적외선, 가시광선 및/또는 자외선의 광파장, 또는 x-선 광장(이것으로만 한정되지는 않음)을 포함하는 더 높은 광장 스펙트럼의 광파장이 있다. 이와 달리, 반도체 소자(112)는 예컨대 공기 및/또는 다른 유체 매질(기체 또는 액체)을 통해 수신된 음압파(sound pressure wave)를 하나 이상의 전기 신호로 변환하거나 또는 하나 이상의 전기 신호를 음압파로 변환하도록 설계되는 음향 트랜스듀서 소자를 포함할 수 있다.

[0066]

특정의 실시예에서, 패키징된 반도체칩은 반도체칩(100)의 반도체 소자(112)가 이미지 캡처를 위한 활상 영역(107)을 포함하는 센서 유닛이다. 반도체칩(100) 내의 전자 회로(도시하지 않음)는 활상 영역(107)에 의해 캡처된 이미지를 나타내는 하나 이상의 전기 신호를 생성하기 위한 활상 영역(107) 내의 반도체 소자에 접속된다. 이러한 용도를 위해 활상 분야에는 다수의 전기 회로가 널리 알려져 있다. 예컨대, 반도체칩(100)으로는 클록킹 회로(clocking circuit) 및 전하-전압 변환 회로와 같은 종래의 회로를 갖는 일반적인 종래의 전하 결합 소자(CCD)가 가능하다.

[0067]

도 1에 도시된 바와 같이, 반도체칩은 반도체칩의 전면에 있는 복수의 전면 접촉 패드(116)를 포함한다. 도 1에 구체적으로 도시하지는 않았지만, 소자 영역 내의 반도체 소자(112)는 전면 접촉 패드(116)에 도전 가능하게 접속된다. 그러므로, 반도체 소자는 반도체칩(100)의 하나 이상의 유전체층 내에 또는 그 위에 연장하는 통합된 배선을 통해 도전 가능하게 액세스될 수 있다.

[0068]

반도체칩은 배면으로부터 떨어져 각도를 이루며 설정되는 표면(120)을 갖는다. 도 1에 예시된 바와 같이, 표면(120)은 직각이 아닌 각도로 배면으로부터 떨어지도록 경사질 수 있으며, 이 경사는 예컨대 배면의 법선에 대하여  $45^{\circ}$  미만의 각도와 같은 완만한 경사일 수도 있고, 또는 이러한 각도가 법선에 대하여  $45^{\circ}$  보다 큰 더욱 급격한 경사일 수도 있다. 이와 달리, 표면(120)은 배면에 대해 직각을 이룰 수도 있다. 표면(120)은 하위 배면(lowered rear surface)(115)에서 종료한다. 하위 배면(115)은 전면(102)으로부터 떨어져 바라보며, 반도체칩(100)의 박막화된 영역(105)에 의해 전면으로부터 이격된다.

[0069]

도전성 비아(125)는 반도체칩(100)의 전면(102)과 하위 배면(115) 사이에 연장한다. 도전성 비아는, 하위 배면(115) 및 표면(120) 상에 위치하는 도전성 트레이스(126)와 전면 접촉 패드(116) 간의 도전성 상호접속을 제공

한다. 도전성 비아(125)는 전면과 하위 배면 사이에 연장하는 구멍부(127) 내에 배치된 유전체층(122) 위에 위치하는 도전층을 포함한다. 전면(102)과 하위 배면 사이에는, 구멍부(127)의 벽부가 수직으로, 즉 전면에 대하여 직각으로 연장할 수 있다. 이와 달리, 구멍부(127)는, 구멍부가 하위 배면으로부터의 거리가 증가함에 따라 더 작게 되도록, 하위 배면으로부터 전면을 향하는 방향으로 테이퍼될 수 있다. 또 다른 실시예에서, 구멍부(127)는, 구멍부가 전면으로부터의 깊이가 증가함에 따라 더 작게 되도록, 전면으로부터 하위 배면을 향해 테이퍼될 수 있다. 이하에 개시되는 각각의 실시예는 이들 이용 가능한 구멍부 지오메트리 중의 어느 하나의 지오메트리를 갖는 구멍부를 포함할 수 있다.

[0070] 도 1에 도시된 예에서, 도전성 비아(125)는 반도체칩의 접촉 패드(116)로부터 구멍부(127)의 벽부를 따라 상방향으로 연장하는 도전성 트레이스의 형태이며, 이 트레이스는 벽부(120)를 따라 배면(114) 상으로 상방향으로 연속된다. 이와 달리, 도전성 비아(125)는 도전성 재료, 예컨대 금속으로 충전된 구멍부(127)의 형태로 될 수 있다. 이러한 경우, 트레이스(126)는 비아의 개별 비아로부터 벽부(120)를 따라 연장하는 동시에 배면(114) 상으로 연장할 수 있다.

[0071] 유전체층(122)은 등각 코팅된 유전체 재료(*conformally coated dielectric material*)를 포함하는 것이 바람직하다. 등각 코팅에 결함(*break*)이 없으며, 유전체층(122)이 반도체칩(100)에 대하여 우수한 유전성 고립(*dielectric isolation*)을 제공하는 것이 바람직하다. 유전체층(122)은, 충분히 낮은 탄성 계수 및 충분한 두께를 갖고, 이 탄성 계수와 두께의 곱(*product*)이 컴플라이언스(*compliance*)를 제공하는, 컴플라이언트 층(*compliant layer*)인 것이 바람직하다. 구체적으로, 이러한 컴플라이언트 층은 여기에 부착된 컨택트(128) 및 트레이스(126)가 다소 회도록 할 수 있다. 이로써, 패키징된 반도체칩(10)의 외부 도전성 범프(134)와 회로 패널(도시하지 않음)의 단자 간의 접합이, 패키징된 반도체칩(10)과 회로 패널(도시하지 않음) 간의 열팽창 계수("CTE")의 부조화로 인한 열적 스트레인(*thermal strain*)을 더 우수하게 견뎌낼 수 있게 된다. 유전체층(122)의 두께와 그 탄성 계수의 곱에 의해 제공된 컴플라이언스의 정도는, 반도체칩(100)과 회로 패널 간의 열팽창 부조화로 인해 도전성 범프에 가해지는 스트레인을 보상하기에 충분한 것이 바람직하다. 유전체층(130)의 노출 표면과 이러한 회로 패널 사이에는, 열팽창 계수 부조화로 인해 열적 스트레인에 대한 저항을 향상시키기 위해, 언더필(*underfill*)(도시하지 않음)이 제공될 수 있다.

[0072] 도 1을 참조하면, 도전성 트레이스(126)는 도전성 비아(125)를 패키징된 반도체칩(10)의 외표면 상에 위치하는 대응하는 패키지 접촉 패드(128)에 도전 가능하게 접속시킨다. 도 1에 구체적으로 도시된 바와 같이, 패키지 접촉 패드(128)는 반도체칩(100)의 배면(114) 상에 위치한다. 도전성 트레이스(126)는 제2 유전체층(122) 상에 위치하고, 반도체칩의 배면(114) 및 표면(120)의 일부분 위에 연장한다. 도전성 트레이스(126)는 개별적으로 반도체칩(100)의 전면 접촉 패드(116)와 이에 대응하는 개별 패키지 접촉 패드(128)를 접속시키는 것이 바람직하다. 도전성 범프(134)가 접촉 패드(128) 상에 제공될 수도 있다. 통상적으로 전면과 배면 사이의 미소전자 장치(100)의 두께(160)는 예컨대 130 nm, 70 nm 또는 그 미만과 같이 현저하게 작게 될 수 있다. 하위 표면(115)과 전면(102) 사이의 미소전자 장치의 두께(162)는 통상적으로 두께(160)의 절반 이하로 될 것이다. 하위 표면에서의 미소전자 요소의 두께(162)는 두께(160)의 절반보다 훨씬 작은 것이 바람직하다. 일례에서, 두께(162)는 대략 10  $\mu\text{m}$ 이다.

[0073] 도 1에 도시된 바와 같이, 제2 유전체층(130)은 도전성 트레이스(126) 상에 위치하고, 도전성 트레이스에 대한 외부 고립을 제공한다. 이 층은 패키징된 반도체칩(10)의 "외부 패시베이션 층(*external passivation layer*)"(130)으로서 지칭될 수 있다. 제2 유전체층은 유기 또는 무기 유전체 재료 또는 이를 양자를 포함할 수 있다. 제2 유전체는 전해도금된 등각 코팅, 또는 예컨대 솔더 마스크 재료와 같은 포토이미지어블 중합성 재료(*photoimageable polymeric material*) 등의 다른 유전체 재료를 포함할 수 있다. 포토이미지어블 솔더 마스크 재료는 다른 것 중에서도 "Shipley" 및 "Toyo"를 포함한 여러 제조업체로부터 획득될 수 있다.

[0074] 특정의 실시예에서, 금속층을 포함하는 금속 구조체(132) 또는 습윤 가능한 금속층을 포함하는 금속층의 적층체가 패키지 접촉 패드(128) 상에 위치하고, 도전성 범프(134)가 금속 구조체(132) 상에 위치한다. 통상적으로, 도전성 범프(134)는 땜납, 주석 등의 비교적 낮은 용융 온도를 갖는 가용 금속(*fusible metal*), 또는 복수의 금속을 포함하는 공융 혼합물(*eutectic mixture*)을 포함한다. 이와 달리, 도전성 범프(134)는 땜납 또는 다른 가용 금속보다 높은 용융 온도를 갖는 구리, 기타 회금속, 또는 비회금속과 같은 습윤 가능한 금속을 포함한다. 이러한 습윤 가능한 금속은 예컨대 회로 패널과 같은 상호접속 요소의 가용 금속의 외형적 특징(*fusible metal feature*)과 같은 대응하는 외형적 특징과 결합되어, 패키징된 반도체칩(10)을 이러한 상호접속 요소에 외부적으로 상호접속시킬 수 있다. 다른 예에서, 도전성 범프(134)는 예컨대 금속 충전 페이스트(*metal-filled paste*), 땜납 충전 페이스트, 등방성의 도전성 접착제, 또는 이방성의 도전성 접착제와 같은 도전성 페이스트 등의 매개

물(medium)에 분산된 도전성 물질을 포함한다.

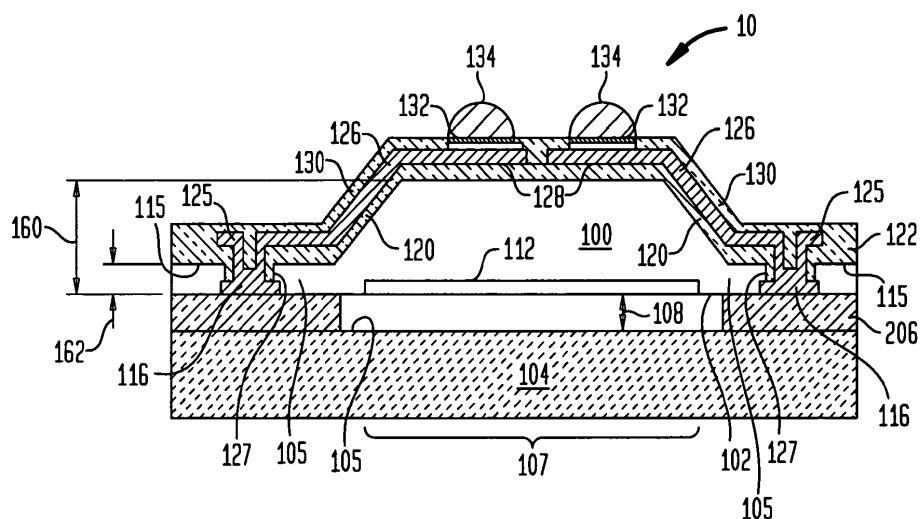

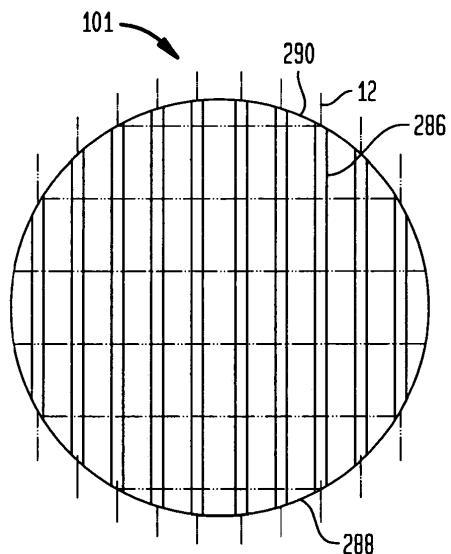

[0075] 도 2를 참조하면, 반도체칩(100)은 웨이퍼-레벨 가공에 의해, 즉 복수의 반도체칩(100)을 웨이퍼의 일부분으로서 또는 전체 반도체 소자 웨이퍼(101)로서 함께 연결된 채로 유지하면서 복수의 반도체칩(100)에 대해 동시에 수행되는 가공에 의해 동시에 패키징된다. 도 2에 예시된 제조 단계에 도달한 후, 부착된 리드(104)를 갖는 웨이퍼의 조립체는 다이싱 레인(dicing lane)(12) 또는 도 2의 도면에 보이지 않는 다른 다이싱 레인을 따라 개별 패키징된 반도체칩으로 절단된다.

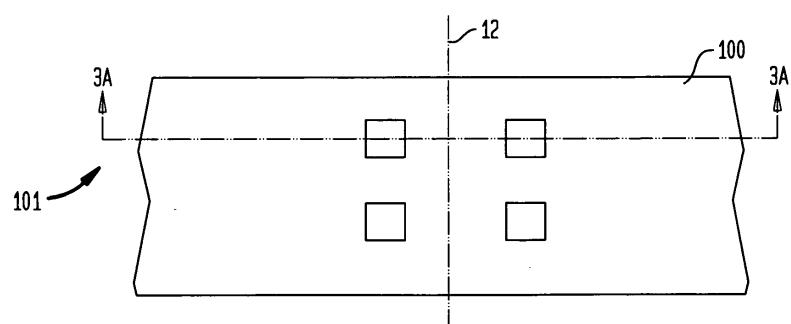

[0076] 이하에서는 도 3a 내지 도 10b를 참조하여 복수의 반도체칩(100)(도 1)을 동시에 제조하는 방법에 대하여 설명한다. 도 3a에 도시된 바와 같이, 소자 영역(112) 및 전면 컨택트(116)를 그 위에 갖는 반도체칩(100)의 전면(102)이 리드 부재(111)를 마주보도록, 반도체 소자 웨이퍼 또는 복수의 반도체칩(100)을 포함하는 소자 웨이퍼의 부분이 리드 부재(111)에 탑재된다. 리드 부재(111)는 반도체 소자 웨이퍼(101)의 측면 방향의 치수와 동일한 측면 방향(내부면(105)에 의해 정해진 평면으로 연장하는 방향)의 치수를 갖는 것이 바람직하다. 도면부호 "12"는 개별 반도체칩(100)들 사이의 경계에 있는 다이싱 레인의 위치를 나타낸다. 웨이퍼의 다이싱 레인(12)은 매우 넓을 필요는 없다. 반도체칩(100)의 접착 패드(116)의 위치는 특별하게 정해질 필요는 없으며, 접착 패드는 일반적으로 다이싱 레인으로부터 떨어져 있는 것이 좋다. 다이싱 레인의 대표적인 폭은 대략 40  $\mu\text{m}$ 이다. 도 3b에 평면도로 예시된 바와 같이, 소자 웨이퍼의 배면(101A)은 반도체칩(100)의 전면(102) 상에 위치한다. 이 제조 단계에서, 배면(101A)은 소자 웨이퍼의 초기 두께(272)만큼 반도체칩(100)의 전면(102)으로부터 균일하게 이격되는 것이 바람직하다. 접착 패드(116) 및 그 아래의 소자 웨이퍼와 다이싱 레인(12)의 위치는 소자 웨이퍼의 배면(101A)을 향해 바라보는 대응 평면도(도 3b)에 나타내어져 있다.

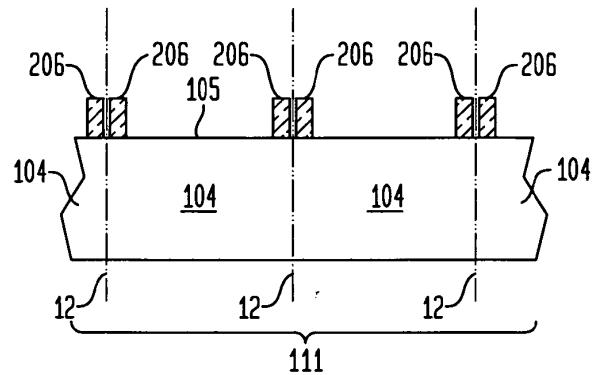

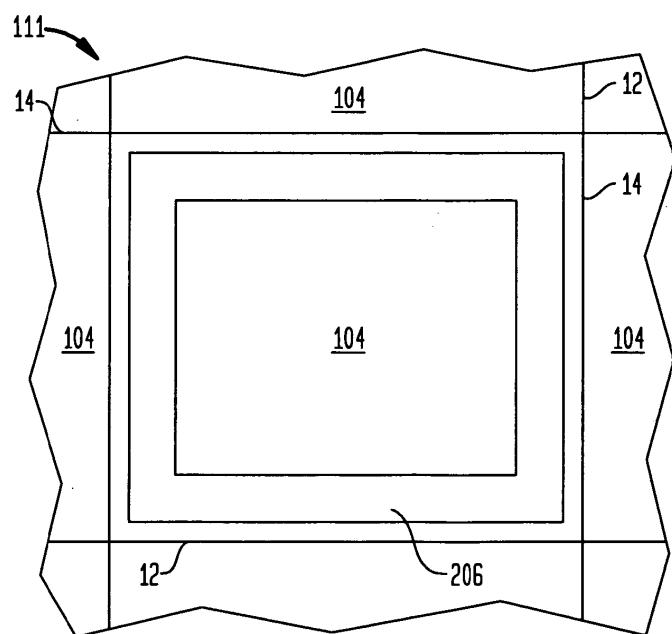

[0077] 또한 도 3a에 예시된 바와 같이, 스텐드오프 구조(206)는 리드 부재(111)의 내부면(105) 위에 일정 간격(108)을 두고 소자 웨이퍼(101)를 지지한다. 도 3c는 다이싱 레인(12)에서 함께 부착된 개별 리드 요소(104)를 포함하는 리드 부재(111)의 주표면으로부터 외측으로 연장하는 복수의 스텐드오프 구조(206)가 형성될 수 있는 사전 제조 단계를 예시하고 있다. 도 3d에서 명확하게 볼 수 있는 바와 같이, 각각의 스텐드오프 구조(206)는 통상적으로 수직으로 지향된 다이싱 레인(12) 및 원래의 리드 부재(111)로부터 절단될 개별 리드들 사이의 경계에 놓여 있는 수평으로 지향된 다이싱 레인(14)으로 정렬된 직사각 형상을 갖는다. 도 3d에 예시된 바와 같이, 스텐드오프 구조(206)는 "픽처 프레임 링 형상"으로서 기술될 수 있는 형태를 갖는다. 전술한 바와 같이, 스텐드오프 구조는 하나 이상의 무기 유전체 재료, 유기 유전체 재료, 반도체, 하나 이상의 금속과 같은 도체, 금속화합물, 또는 이러한 물질의 조합을 포함할 수 있다. 스텐드오프 구조는 예컨대 2004년 9월 24일자로 출원된 미국 특허 출원 번호 10/949,674 또는 미국 가출원 번호 60/761,171에 개시된 바와 같은 추가 공정(additive processing) 또는 제거 공정(subtractive processing)에 의해 제조될 수 있으며, 이를 특허는 그 개시 내용이 본 명세서에 원용되어 있다. 스텐드오프 구조는, 금속을 포함하는 경우, 금속 박층을 스퍼터링한 후에 제거 패터닝을 행하는 단계와, 그리고나서 잔류하는 구조를 최종 금속으로 전해도금하는 단계의 조합에 의해 제조될 수 있다. 이와 달리, 스텐드오프 구조는 무전해 도금(electroless plating)과 이에 후속되는 제거 패터닝 및 전해도금에 의해 형성될 수도 있다. 특정의 실시예에서, 스텐드오프 구조(206)는, 본 명세서에서 원용하고 있는 미국 가출원 번호 60/775,086에 기술된 바와 같은 방식으로, 이미 존재하고 있는 스퍼터링되거나 도금된 도전층 상에의 폴리머의 전기 영동 증착(electrophoretic deposition)에 의해 제조된다.

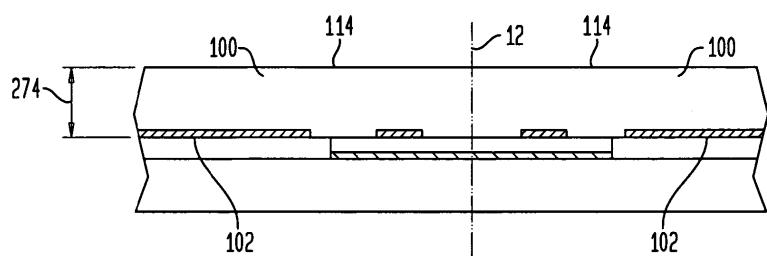

[0078] 도 3a에 예시된 바와 같이 소자 웨이퍼(101)를 리드 요소(111)에 결합한 후, 이 소자 웨이퍼의 두께는 배면(101A)으로부터 감소될 수 있다. 두께를 감소시키기 위해 배면으로부터의 그라인딩, 랩핑, 폴리싱 또는 이들의 조합이 이용될 수 있다. 두께를 감소시키기 위해 수행된 공정 동안, 반도체칩의 전면 상에 위치하는 리드 요소(104)는 반도체칩에 대한 구조적인 지지를 제공하여, 패키징된 반도체칩의 두께를 원하는 만큼 더 작은 두께로 감소시킬 수 있도록 강성을 증가시키는 것에 도움을 준다. 이 단계 동안, 예로서, 소자 웨이퍼의 두께는 약 700 nm에서 약 130 nm 이하로 감소될 수 있다.

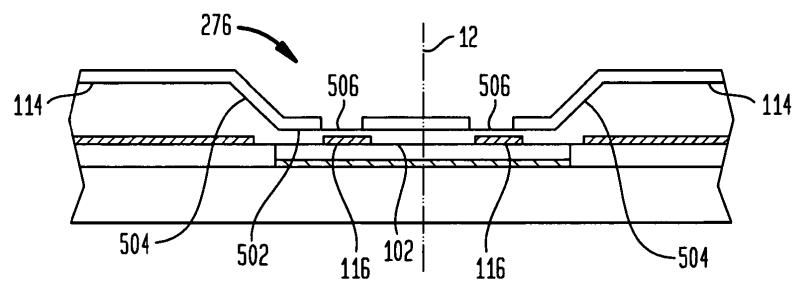

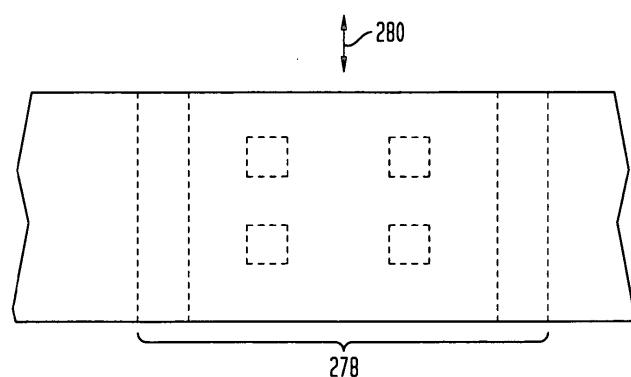

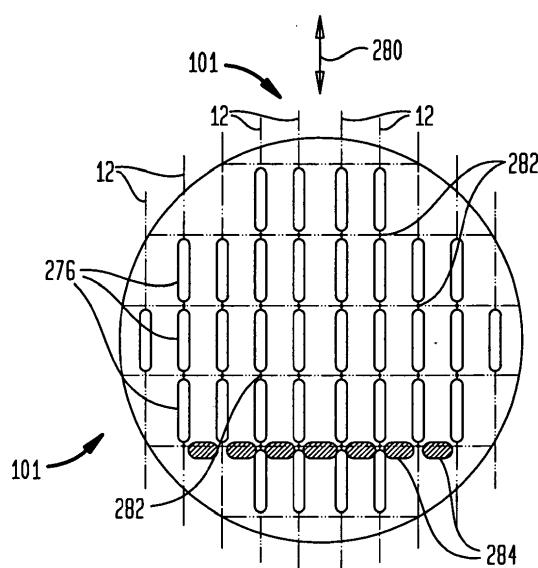

[0079] 그 후, 그 결과의 소자 웨이퍼는 도 4에 도시된 바와 같이 감소된 두께(274)를 가지며, 배면(114)이 두께(274) 만큼 각각의 반도체칩(100)의 전면(102)으로부터 분리된다. 다음에, 도 5a에 도시된 바와 같이, 배면(114)으로부터 소자 웨이퍼의 전면(102)을 향해 하방향으로 연장하는 리세스(276)가 소자 웨이퍼에 형성된다. 리세스는 예컨대 반도체칩의 배면(114)의 일부분을 잔류 상태로 보존하기 위해 요구되는 마스크층을 형성한 후에 소자 웨이퍼를 선택적으로 에칭함으로써 형성될 수 있다. 예컨대, 포토이미지어블층, 예컨대 포토레지스트층이 중착되고, 배면의 일부분만을 덮도록 패터닝될 수 있으며, 그 후에 시간이 정해진 에칭 공정(timed etch process)이 리세스(276)를 형성하기 위해 행해질 수 있다. 리세스는 다이싱 레인(12)과 정렬되어 소자 웨이퍼 위에 직선 방향(280)으로 연장하는 스트라이프(stripes)(278)로서 형성될 수 있다. 도 6a에 명확하게 도시되어 있는 바와

같이, 수직으로 연장하는 다이싱 레인과 정렬되어 소자 웨이퍼의 수직 레이아웃 방향(280)으로 연장하는 가늘고 긴 리세스(elongated recess)(276)들이 동시에 형성되는 것이 바람직하다. 수직으로 연장하는 리세스(276)는 각각의 반도체칩의 쌍의 다이싱 레인을 따라서만 연장하도록 형성될 수 있다. 이러한 경우, 리세스는 수직 다이싱 레인(12)과 소자 웨이퍼의 수평 레이아웃 방향으로 연장하는 수평 다이싱 레인(14)과의 사이의 교차부에 있는 반도체칩(100)의 모서리부 위에 위치하지 않을 수도 있다. 다른 예에서, 수평으로 연장하는 리세스(284)가 각각의 칩의 수평 다이싱 레인(14)에 인접한 접착 패드 상에 위치하도록 형성될 수 있다. 수직으로 연장하는 리세스(276) 및 수평으로 연장하는 리세스(284) 양자는 소자 웨이퍼 내에 형성될 수 있다. 특정의 예에서, 반도체칩의 경계를 정하는 다이싱 레인들 중의 하나의 다이싱 레인에만 인접한 접착 패드 상위 위치하는 리세스가 형성될 수 있다. 다른 예에서, 반도체칩의 2개의 다이싱 레인 상에만 위치하거나 또는 반도체칩의 경계를 정하는 3개 이상의 다이싱 레인 상에만 위치하는 리세스가 형성될 수 있다. 일례에서, 도 6a에 도시된 바와 같이, 리세스가 소자 웨이퍼(101)의 다이싱 레인(12)에 인접하여 놓여 있는 접착 패드의 행의 일부 접착 패드 상에만 위치하도록, 리세스가 더 작게 될 수 있다. 도 6b에 예시된 바와 같은 또 다른 예에서, 다이싱 레인(12)에 정렬된 리세스(286)는 소자 웨이퍼(101)의 각각의 예지(288, 290) 사이의 스트라이프로서 연장할 수 있다.

[0080] 도 5a에 구체적으로 도시된 바와 같이, 각각의 리세스(276)는, 평坦하고 전면(102)으로부터 동등한 거리에 있는 하위 표면(502)을 갖는다. 배면(114)으로부터 하위 표면을 향해 하방향으로 연장하는 리세스의 벽부(504)는 경사질 수도 있다. 즉, 이 벽부는 도 5a에 구체적으로 예시된 바와 같이 배면(114)에 대해 법선 각도(직각)가 아닌 각도로 연장할 수도 있다. 도 5a에 예시된 바와 같은 경사진 벽부(504)를 갖는 리세스를 형성하기 위해 예컨대 등방성 예칭 공정과 같은 습식 예칭 공정 및 다른 것 중에서도 테이퍼된 블레이드를 이용한 소잉(sawing)이 이용될 수 있다. 또한, 경사진 벽부를 갖는 리세스를 형성하기 위해 다른 것 중에서도 레이저 다이싱, 기계식 밀링이 이용될 수 있다. 이와 달리, 경사지게 하는 대신, 벽부가 배면(114)으로부터 배면(114)에 대해 직각으로 수직 하방향으로 연장할 수도 있다. 근본적으로 수직의 벽부를 갖는 리세스를 형성하기 위해, 다른 것 중에서도, 이방성 예칭 공정, 레이저 다이싱, 레이저 드릴링, 소잉 또는 밀링 등의 기계식 제거 공정, 초음파 가공이 이용될 수 있다. 소자 웨이퍼에 리세스를 형성한 후, 포토레지스트와 같은 포토이미지어블층이 소자 웨이퍼의 배면 상에 증착되어, 접착 패드(116)와 정합하여 하위 표면(502) 상에 위치하는 마스크 개구(506)를 형성하도록 패터닝된다.

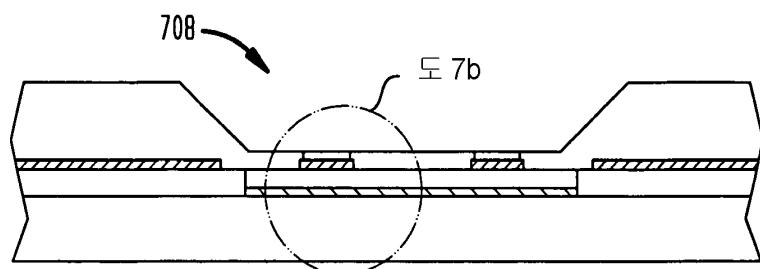

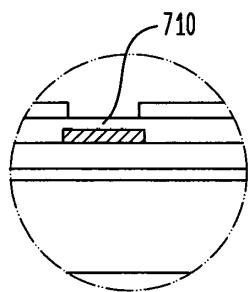

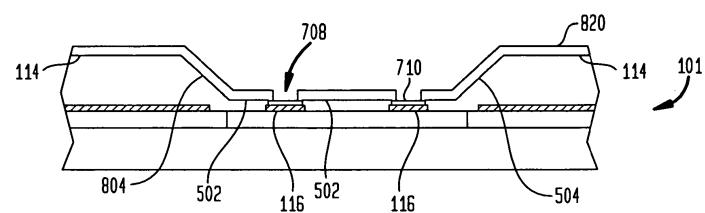

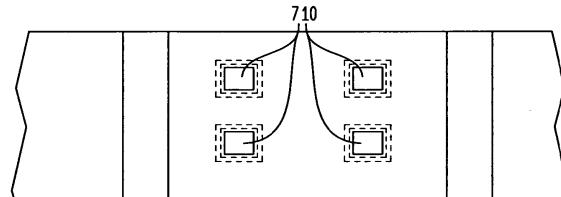

[0081] 그 후, 도 7a에 예시된 바와 같이, 마스크 개구 아래에 있는 반도체 재료를 제거하기 위해 마스크 개구 내에 노출되어 있는 하위 표면(502)의 부분에 예칭 공정이 가해진다. 그 결과, 하위 표면 사이에 연장하여 전면 컨택트(116)와 접촉하는 비아(708)가 형성된다. 예칭 공정은 예컨대 실리콘과 같은 반도체 재료를 선택적으로 예칭하지만 산화물 재료는 잔류시키는 방식으로 행해지는 것이 바람직하다. 통상적으로, 반도체칩의 접착 패드(116)와 같은 전면 컨택트가, 패시베이션(passivation)을 위해 층간 유전체층(interlevel dielectric layer) 또는 반도체칩의 절연 또는 고립을 제공하는 다른 용도로서 이용되는, 산화물 재료 또는 다른 유전체 재료로 이루어진 하나 이상의 산화물 재료의 층 상에 위치한다. 유전체를 잔류시키는 선택적 방식으로 반도체 재료를 예칭함으로써, 필요에 따라 과예칭(over-etching)을 수행하여, 소자 웨이퍼에 걸쳐 충분한 공정 간격(process window)을 유지하면서 소자 웨이퍼의 모든 위치에 있는 반도체 재료의 두께를 관통하여 예칭할 수 있다. 선택적 예칭 공정이 이용될 때, 도 7b의 확대 단면도로 나타낸 바와 같이, 비아(708)를 형성한 후의 위치에 유전체 층(710), 예컨대 산화물층이 잔류한다. 이와 달리, 비아(708)를 형성하기 위해 레이저 드릴링 또는 기계식 밀링이 이용될 수 있으며, 그 경우에는 비아 내에서 전면 접촉 패드의 표면이 노출될 수 있다.

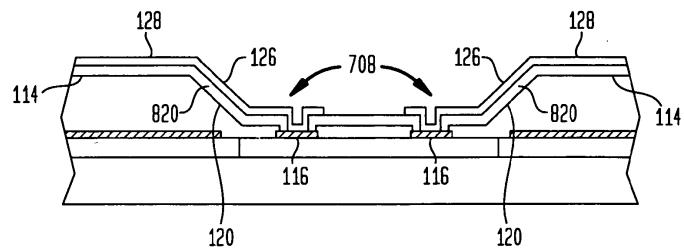

[0082] 그 후, 도 8a에 예시된 제조 단계에서, 비아의 벽부(806), 반도체칩의 벽부(504) 및 배면(114) 상에 유전체층(820)이 형성된다. 이러한 유전체층을 형성하기 위해 다양한 방법이 이용될 수 있다. 일례에서, 반도체칩(100)을 포함하고 있는 웨이퍼(101)의 배면(114)에 유동 가능한 유전체 재료가 가해지며, 이러한 유동 가능한 유전체 재료는 그 후 "스핀-코팅" 동작 동안 웨이퍼의 배면에 걸쳐 더욱 균일하게 분포되며, 그 후에 가열을 포함할 수도 있는 건조 기간이 후속된다. 다른 예에서, 유전체 재료의 열가소성막이 소자 웨이퍼(101)의 배면에 가해질 수 있으며, 그 후 웨이퍼 및 리드 요소를 포함하는 조립체가 가열되어, 열가소성막이 하위 표면(115) 상으로 및 비아(708) 내로 하방향으로 흐르게 된다. 다른 예에서, 유전체층을 형성하기 위해 증기 증착이 이용될 수 있다.

[0083] 다른 예에서, 리드 요소가 부착된 소자 웨이퍼를 포함하는 조립체가 등각 유전체 코팅 또는 등각 유전체층(820)을 형성하기 위해 유전체 증착 배쓰(dielectric deposition bath)에 침지된다. 등각 유전체 코팅이 조립체의 노출된 도전성 및 반도전성 표면 상에만 증착되도록, 등각 유전체 코팅을 형성하기 위해 전기 영동 증착 기술이 이용되는 것이 바람직하다. 증착 동안, 반도체 소자 웨이퍼는 요구된 전기 전위로 유지되고, 배쓰를 여러 요구

된 전위로 유지하기 위해 전극이 배쓰 내에 침지된다. 조립체는 그 후 충분한 시간 동안 적합한 조건 하에서 배쓰 내에 유지되어, 배면(114)과 함께 리세스의 벽부(504), 하위 표면(502) 및 비아(708)의 벽부(806)(이들로만 한정되지는 않음)를 포함하는 도전성이거나 또는 반도전성이 되는 소자 웨이퍼의 노출 표면 상에 전해도금된 등각 유전체 코팅(820)을 형성한다. 코팅될 표면과 배쓰 간에 충분히 강한 전계가 유지되는 한 전기 영동 증착이 발생한다. 전기 영동 방식으로 증착된 코팅은, 그 코팅이 이러한 증착의 파라미터, 예컨대 전압, 농도 등에 의해 좌우되는 특정 두께에 도달한 후에는, 증착이 정지된다는 점에서 자체 제한(self-limiting)적인 것이다. 전기 영동 증착은 조립체의 도전성 및/또는 반도전성 외측 표면 상에 연속적이고 균일한 두께의 등각 코팅을 형성한다. 또한, 전기 영동 방식으로 증착된 코팅은, 컨택트(116) 상에 위치하는 잔류 유전체층(710)의 유전(비도전성) 특성으로 인해 그 유전체층(710) 상에는 형성되지 않는다. 달리 말하면, 전기 영동 증착의 특성은, 도체 위에 위치하는 유전체 재료의 층이 충분한 두께를 가짐으로써 그 유전 특성을 제공하는 경우에는, 그 유전체 재료층 상에는 코팅이 형성되지 않는다는 점이다. 통상적으로, 전기 영동 증착은 약 10  $\mu\text{m}$  보다 크고 수십  $\mu\text{m}$ 까지의 두께를 갖는 유전체층 상에서는 발생하지 않을 것이다.

[0084]

등각 유전체층(820)은 음극성 에폭시 증착 선구체(cathodic epoxy deposition precursor)로 형성되는 것이 바람직하다. 이와 달리, 폴리우레탄 또는 아크릴 증착 선구체가 사용될 수 있다. 다양한 전기 영동 코팅 선구체 조성물 및 그 공급원이 아래의 표 1에 나열되어 있다.

[0085]

표 1

| 전기 영동 코팅 명칭             | POWERCRON 645 | POWERCRON 648    | CATHOGUARD 325 |

|-------------------------|---------------|------------------|----------------|

| 제조업체                    |               |                  |                |

| MFG                     | PPG           | PPG              | BASF           |

| 타입                      | 음극성           | 음극성              | 음극성            |

| 폴리머계                    | 에폭시           | 에폭시              | 에폭시            |

| 소재지                     | 피츠버그, PA      | 피츠버그, PA         | 사우스필드, MI      |

| 적용 데이터                  |               |                  |                |

| Pb/Pf-free              | Pb-free       | Pb or Pf-free    | Pb-free        |

| HAPs, g/L               |               | 60-84            | 컴플라이언트         |

| VOC, g/L (MINUS WATER)  |               | 60-84            | <95            |

| 경화                      | 20 min/175C   | 20 min/175C      |                |

| 막 특성                    |               |                  |                |

| 색상                      | 블랙            | 블랙               | 블랙             |

| 두께, $\mu\text{m}$       | 10-35         | 10-38            | 13-36          |

| 연필 경도(pencil hardness)  |               | 2H+              | 4H             |

| 배쓰 특성                   |               |                  |                |

| 고체, % wt                | 20 (18-22)    | 20 (19-21)       | 17.0-21.0      |

| pH (25C)                | 5.9 (5.8-6.2) | 5.8 (5.6-5.9)    | 5.4-6.0        |

| 도전율 (25C) $\mu\text{s}$ | 1000-1500     | 1200-1500        | 1000-1700      |

| P/B 비율                  | 0.12-0.14     | 0.12-0.16        | 0.15-0.20      |

| 동작 온도, C                | 30-34         | 34               | 29-35          |

| 시간, sec                 | 120-180       | 60-180           | 120+           |

| 양극                      | SS316         | SS316            | SS316          |

| 불트                      |               | 200-400          | >100           |

| 전기 영동 코팅 명칭             | ELECTROLAC    | LECTRASEAL DV494 | LECTROBASE 101 |

| 제조업체                    |               |                  |                |

| MFG                     | MACDERMID     | LVH COATINGS     | LVH COATINGS   |

| 타입                      | 음극성           | 양극성              | 음극성            |

| 폴리머계                    | 폴리우레탄         | 우레탄              | 우레탄            |

| 소재지                     | 워터베리, CT      | 영국 버밍햄           | 영국 버밍햄         |

| 적용 데이터                  |               |                  |                |

| Pb/Pf-free              |               | Pb-free          | Pb-free        |

| HAPs, g/L               |               |                  |                |

| VOC, g/L (MINUS WATER)  |               |                  |                |

| 경화                      | 20 min/149C   | 20 min/175C      | 20 min/175C    |

표 1 이어짐

[0086]

| 막 특성                    |               |         |         |

|-------------------------|---------------|---------|---------|

| 색상                      | 선명 (+착색)      | 블랙      | 블랙      |

| 두께, $\mu\text{m}$       |               | 10-35   | 10-35   |

| 연필 경도(pencil hardness)  | 4H            |         |         |

| 배쓰 특성                   |               |         |         |

| 고체, % wt                | 7.0 (6.5-8.0) | 10-12   | 9-11    |

| pH (25C)                | 5.5-5.9       | 7-9     | 4.3     |

| 도전율 (25C) $\mu\text{s}$ | 450-600       | 500-800 | 400-800 |

| P/B 비율                  |               |         |         |

| 동작 온도, C                | 27-32         | 23-28   | 23-28   |

| 시간, sec                 |               |         | 60-120  |

| 양극                      | SS316         | 316SS   | 316SS   |

| 볼트                      | 40, max       |         | 50-150  |

[0087]

도 8b는 접착 패드 위의 비아(710)가 전기 영동 증착 후에 개방 상태를 유지하고 있다는 것을 나타내고 있다. 등각 유전체 코팅을 전기 영동 방식으로 증착한 후, 반도체칩의 전면 접촉 패드를 폐키징된 반도체칩의 외부 컨택트에 접속시키는 도전성 트레이스를 형성하기 위한 처리가 개시된다.

[0088]

다음으로, 도 9a 및 도 9b를 참조하면, 도전성 트레이스(126) 및 랜드(1and)(128)를 형성하는 처리를 위해 기판이 준비된다. 이전의 처리가 유전체층(820)에 의해 반도체칩의 전면 접촉 패드(116)를 차단하는 결과를 초래한다면, 이 단계에서는 전면 접촉 패드에 인접한 비아의 저부를 개방시키기 위해 레이저 드릴링, 기계식 밀링 또는 다른 적합한 기술이 이용될 수 있다. 또한, 반도체칩의 기존의 유전체층(710)의 어떠한 부분이 컨택트(116)와 정렬되어 잔류한다면, 이러한 층이 이 단계에서 제거될 수 있다. 이러한 제거는 예컨대 레이저 드릴링, 기계식 밀링, 또는 다른 적합한 기술에 의해 달성될 수 있다. 다른 적합한 제거 기술은 본질적으로 등방성이거나 또는 이방성일 수 있는 다양한 선택적 에칭 기술을 포함한다. 이방성 에칭 공정은, 이온의 스트림이 에칭될 표면을 향해 지향되는 반응성 이온 에칭 공정을 포함한다. 반응성 이온 에칭 공정은 일반적으로 이방성 에칭 공정보다 덜 선택적이어서, 이온이 커다란 입사각으로 때리는 표면이 이온의 스트림으로 배향된 표면보다 더 큰 정도로 에칭되게 된다. 반응성 이온 에칭 공정이 사용될 때, 마스크층이 등각 유전체 코팅(820) 상에 위치하도록 증착되고, 비아(708)와 정렬되는 개구가 그 안에 형성되는 것이 바람직하다. 이로써, 에칭 공정은 비아(708) 내에 놓여있는 것 이외의 유전체 코팅(820) 부분을 제거하는 것을 방지한다.

[0089]

이어서, 등각 유전체 코팅(820) 상에 위치하도록 도전성 트레이스(126) 및 랜드(128)가 형성된다. 트레이스 및 랜드를 형성하는 일례의 방법은, 금속층을 등각 유전체 코팅(220) 상에 위치하도록 증착하는 단계를 포함한다. 이와 달리, 증착은 이들 표면의 일부분이 마스킹층에 의해 보호되면서 행해질 수 있다. 금속층은 조립체의 노출 표면 상으로 1차 금속층을 스퍼터링함으로써 또는 무전해 증착에 의해 증착된다. 이 단계는 예컨대 소자 웨이퍼의 배면, 벽부 및 하위 표면 상으로의 비선택적 증착(blanket deposition)에 의해 수행될 수 있다. 일실시 예에서, 1차 금속층은 알루미늄을 포함하거나 또는 본질적으로 알루미늄으로 이루어진다. 다른 특정의 실시예에서, 1차 금속층은 구리를 포함하거나 본질적으로 구리로 이루어진다. 또 다른 실시예에서, 1차 금속층은 티타늄을 포함하거나 본질적으로 티타늄으로 이루어진다. 1차 금속층을 형성하기 위한 공정에서는 하나 이상의 다른 예의 금속이 이용될 수 있다.

[0090]

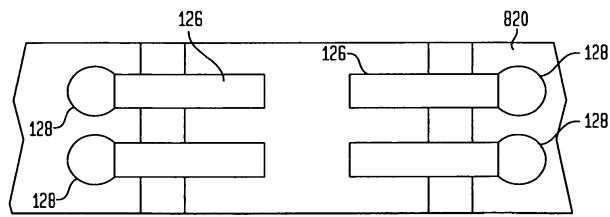

그 후, 1차 금속층 상에 위치하도록 포토이미지어블층이 증착되며, 1차 금속층을 패터닝하기 위해 "Badehi"에게 허여된 미국 특허 번호 5,716,759호에 개시된 공정과 같은 3차원 포토리소그래피 패터닝 공정이 이용되며, 상기 특허에 개시된 내용은 본 명세서에 원용되어 있다. 그 후, 포토이미지어블층의 나머지 부분이 제거된다. 그 결과, 그 위에 형성될 도전성 트레이스의 치수에 대응하는 개별 도전성 패턴이 형성된다. 개개의 라인으로의 1차 금속층의 패터닝에 후속하여, 포토이미지어블층이 소자 웨이퍼로부터 제거되고, 2차 금속층을 1차 금속층 상에 도금하여 전면 접촉 패드(116)로부터 벽부(120)를 따라 또한 반도체칩의 배면(114) 상으로 연장하는 개별 도전성 트레이스(126)를 형성하기 위해 전해 도금 공정이 이용된다. 2차 금속은 니켈 또는 다른 희금속을 포함할 수도 있다. 일실시 예에서, 1차 금속층 상의 전해 도금된 2차 금속은 도전성 트레이스를 완성한다. 이와 달리, 도전성 트레이스를 완성하기 위한 내부식성을 제공하기 위해 금, 백금, 또는 팔라듐과 같은 제3의 금속층이 2차 금속층 상에 도금될 수도 있다.

[0091]

후속하는 일례의 공정에서, 배면(114) 및 벽부(120)를 따라 연장하는 각각의 도전성 트레이스(226) 상에 위치하

도록 추가의 유전체층(230)이 증착된다. 추가의 유전체층(230)은 도 8a 및 도 8b를 참조하여 전술한 바와 같은 전기 영동 증착 공정에 의해 증착되는 것이 바람직하다. 포토레지스트, 산화물 마스크 등을 포함하는 패터닝된 마스크층이 컨택트(128) 상에 형성된다. 그 후, 전기 영동 증착 공정 동안, 그 결과의 유전체층(230)이 패터닝된 마스크층에 의해 컨택트(128) 상에 형성되는 것이 방지된다. 그 후, 패터닝된 마스크층이 제거되어, 유전체층(230)에 있는 개구 내의 컨택트(128)를 노출시킨다.

[0093] 이와 달리, 전기 영동 증착에 의해 유전체층(230)을 증착하는 대신, 봉지재(encapsulant) 또는 솔더 마스크 재료와 같은 포토이미지어블 유전체를 소자 웨이퍼의 배면(114) 및 벽부(120)를 향해 스판 코팅 또는 스프레이 코팅하여 상대적으로 균일하게 두꺼운 코팅을 형성함으로써 유전체층을 형성할 수 있다. 그 후, 포토리소그래피 공정에 의해 컨택트(128)와 정합하여 등각 유전체층(230)에 개구가 형성될 수 있다. 포토이미지어블 재료의 초기 증착 후에 유전체층(230)이 경화되도록 하기 위해 예컨대 가열 등의 하나 이상의 공정이 행해질 수도 있다.

[0094] 다음으로, 예컨대 "하부 범프 금속화" 또는 "UBM"과 같은 습윤 가능 금속층(132)이 유전체층(230)에 있는 개구 내에 형성되며, 습윤 가능 금속층은 각각의 컨택트(128)와 접촉된다. 일례의 공정에서, 예컨대 티타늄, 텅스텐, 탄탈 또는 다른 유사 금속을 포함하는 도전층과 같은 확산 장벽층이 컨택트(128)와 접촉하여 형성된다. 그 후, 제1 습윤 가능 금속을 포함하는 층이 장벽층 상에 위치하도록 증착될 수 있으며, 이러한 층은 니켈, 구리 또는 바람직하게는 화금속을 포함하는 다른 금속 등의 금속을 포함한다. 내부식성을 향상시키기 위해, 일반적으로 예컨대 0.1  $\mu\text{m}$ 의 매우 얇은 금으로 이루어진 층이 습윤 가능 금속의 최종적인 층으로서 증착될 수 있다. 습윤 가능 금속층을 형성한 후, 도전성 범프(134)가 각각의 컨택트 위에서 습윤 가능 금속층과 접촉하여 형성될 수 있다. 땜납, 주석 또는 공용 조성물 등의 융합 가능 금속을 포함하거나 또는 예컨대 땜납 충전 페이스트 또는 은 충전 페이스트 등의 도전성 페이스트를 포함하는 도전성 범프가 형성될 수 있다. 도전성 범프는 하나 이상의 도전성 재료를 포함할 수 있다. 특정의 예에서, 도전성 범프는 예컨대 구리, 니켈 등의 하나 이상의 화금속을 포함할 수 있다. 일례에서, 도전성 범프는, 땜납, 주석 또는 공용 금속 등의 융합 가능 금속을 포함하는 구체(sphere)를 습윤 가능 금속층(232) 상에 위치시키고, 그 후 도전성 범프를 가열하여 이들을 습윤 가능 금속층(232)에 융합되도록 함으로써 형성될 수 있다.

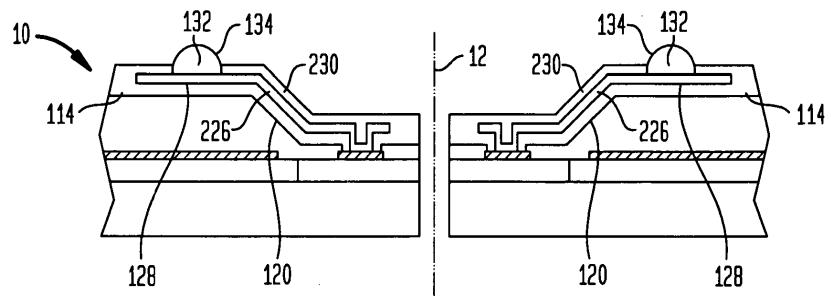

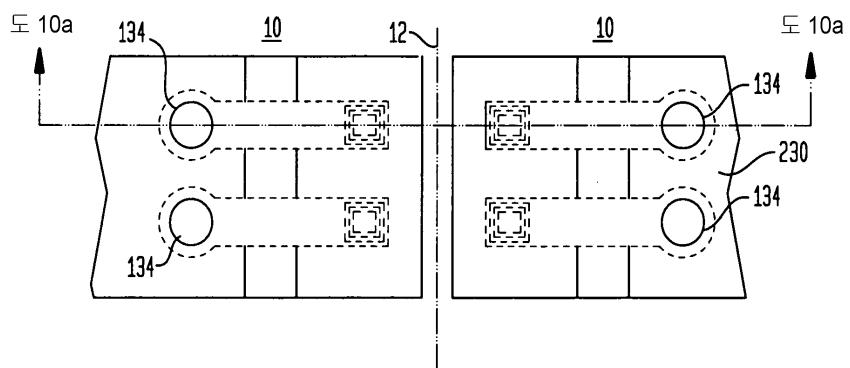

[0095] 최종적으로, 패키징된 반도체칩은 도 10a 및 도 10b에 예시된 바와 같이 개별 패키징된 반도체칩(10)을 형성하기 위해 소잉 또는 다른 다이싱 방법에 의해 다이싱 레인(12)을 따라 서로 절단된다. 패키징된 반도체칩을 개별 유닛으로 절단하기 위한 다양한 예의 공정이 본 명세서에 원용되어 있는 공동 소유의 미국 출원 번호 60/761,171 및 60/775,086에 개시되어 있으며, 이들 중의 어떠한 것도 패키징된 반도체칩을 절단하여 도 10a 및 도 10b에 도시된 바와 같이 개별 패키징된 반도체칩을 형성하는 데 이용될 수 있다.

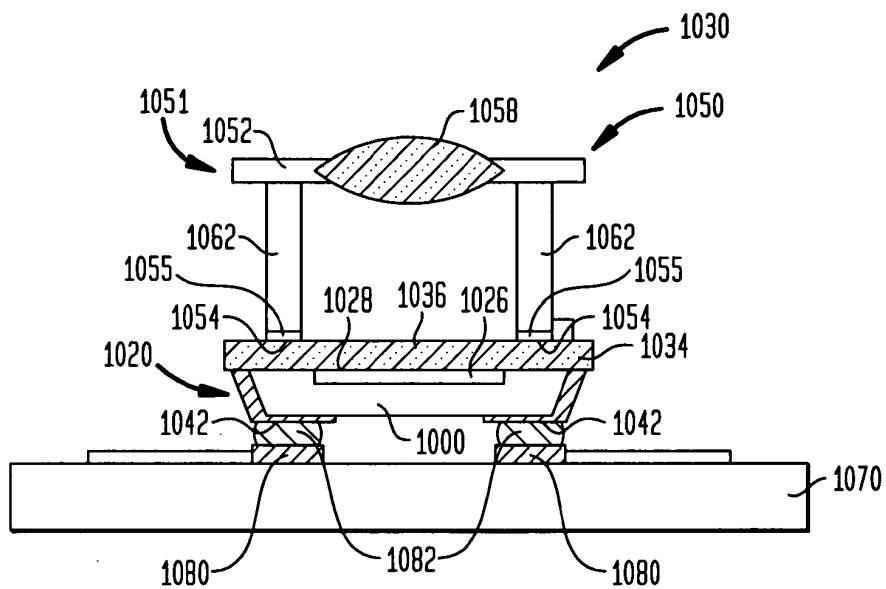

[0096] 본 발명의 실시예에 따른 카메라 모듈(1030)(도 11)은, 센서 유닛의 배면 상에, 즉 활상 영역(1026)을 보유하는 반도체칩(1000) 전면(1028)의 반대측의 표면 상에 증착된 컨택트(1042)를 갖는 센서 유닛(1020)을 포함한다. 센서 유닛은 도 1을 참조하여 도시 및 설명된 유닛일 수도 있다. 유사 센서 유닛 및 카메라 모듈이, 각각 대리인 문서 번호 TESSERA 3.0-381 CIP 및 3.0-464로 식별되어 있는, 공동 소유의 2005년 11월 2일자로 출원된 미국 특허 출원 번호 11/265,727 및 2005년 12월 30일자로 출원된 미국 특허 출원 번호 11/322,617에 개시되어 있으며, 상기 특허 출원은 그 개시 내용이 본 명세서에 원용되어 있다. 센서 유닛의 컨택트(1042)는 땜납과 같은 융합 가능 도전성 재료의 매쓰(1082)에 의해 회로 패널(1070)의 단자(1080)에 연결된다.

[0097] 이러한 구성의 광학 유닛(1050)은 하나 이상의 렌즈 또는 다른 광학 요소(1058)를 유지하도록 배치된 탑재부(1052)를 갖는 터렛(turret) 또는 지지 구조체(1051)를 포함한다. 지지 구조체(1051)는 또한 탑재부(1052)로부터 배면 방향으로 돌출하는 가늘고 긴 포스트(1062) 형태의 복수의 배면 요소(1062)를 포함한다. 이들 포스트는 센서 유닛에 대해 광학 유닛을 위치시키기 위해 센서 유닛 내의 기준 평면과 맞닿거나 또는 기계적인 방식으로 계합하는 배면(1054)을 갖는다. 도 11에 예시된 예에서, 배면(1054)은 활상 영역(1026) 상에 위치하는 투명 커버(1034)의 전면에 맞닿고 있다. 이와 달리, 터렛 또는 지지 구조체는, 반도체칩(1000)에 대하여 터렛의 기울어짐을 제한하면서 반도체칩(1000)에 대하여 광학 유닛(1050)의 높이를 기계적인 방식으로 설정하기 위해 예컨대 포스트, 핀, 리세스 등의 정합 특징부(registration feature)를 포함한다.

[0098] 포스트(1062)의 배면과 전면(1034) 간의 접속을 평평하고 두께가 균일하게 하는 것이 바람직하다. 이러한 목적을 달성하기 위한 다른 방식으로, 예컨대 확산 접착을 통해 포스트(1062)의 배면(1054)에 있는 금속성 특징부에 야금학적으로 접착되는 금속성의 부착 특징부 또는 패드(1055)가 커버(1034)의 외부면(1036)에 제공될 수 있다. 이와 달리, 포스트의 배면을 커버에 접착시키기 위해 다소 얇은 접착제가 사용될 수 있다.

[0099] 다른 실시예에서는, 포스트의 위치에서, 터렛 또는 지지 구조체(1051)가, 원통형 또는 다면체 형상을 갖는 체적

을 둘러싸거나 또는 실질적으로 둘러싸는 배면 요소를 포함한다. 원통형 벽부 또는 다면체 형상(예컨대, 상자 형상)의 벽부를 갖는 이러한 배면 요소가 제공될 수 있으며, 배면 요소의 후위 표면이 커버(1034)의 외측 표면(1036)에 제공된 바와 같은 센서 유닛의 기준 평면에 대해 맞닿게 된다.

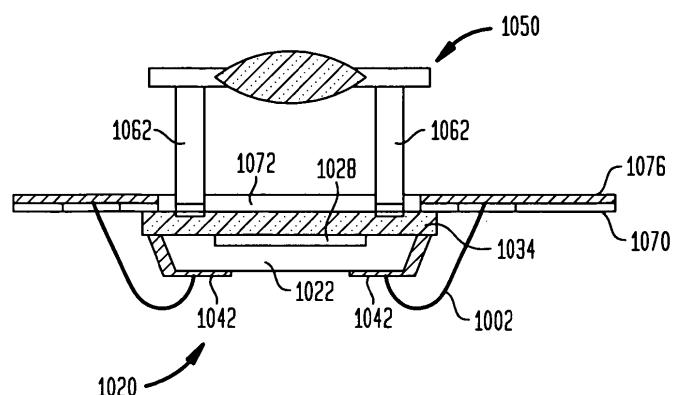

[0100] 도 12에 도시된 상기 실시예의 변형예에서, 센서 유닛(1020)은 센서 유닛의 앞에 탑재되며, 그에 따라 전방을 바라보는 활상 영역(1028)이 회로 패널(1070)의 배면 또는 저면을 향하게 된다. 센서 유닛의 컨택트(1042)는 적합한 리드선(lead) 또는 와이어 본드(1002)에 의해 회로 패널의 도전체(1076)에 접속된다. 본 실시예에서, 광학 유닛(1050)의 배면 요소(1062)는 활상 영역(1028)과 정렬된 회로 패널 내의 구명부(1072)를 통과하여 돌출 한다. 달리 말하면, 구명부(1072)는 광학 요소로부터 활상 영역까지의 광경로를 수용하고 또한 배면 요소(1062)를 수용하기에 충분할 정도로 크다. 전술한 바와 같이 전면 상에 컨택트를 갖는 센서 유닛을 포함하는 유사 구성이 이용될 수 있다.

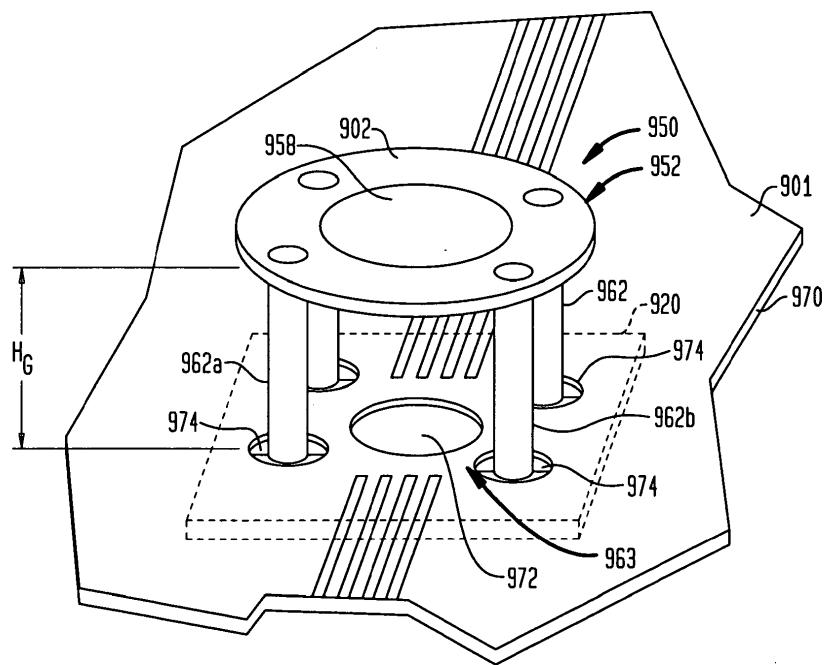

[0101] 본 발명의 다른 실시예에 따른 카메라 모듈(도 13)은 회로 패널(970)의 저면 또는 배면측 상에 위치된 점선으로 도시된 센서 유닛(920)을 포함한다. 여기에서도, 센서 유닛 내의 칩의 활상 영역은 회로 패널 내의 구명부(972)와 정렬된다. 이러한 구성에서의 광학 유닛(950)은 하나 이상의 렌즈 또는 다른 광학 요소(958)를 유지하도록 배치된 탑재부(902)를 갖는 터렛 또는 지지 구조체(952)를 포함한다. 지지 구조체(952)는 또한 탑재부(902)로부터 후방으로 돌출하는 가늘고 긴 포스트 형태의 복수의 배면 요소(962)를 포함한다. 이들 포스트는 회로 패널 내의 애피처(974)를 통해 연장하고, 전술한 바와 같이 센서 유닛에 관련하여 광학 유닛을 위치시키기 위해 센서 유닛과 기계적으로 계합한다. 여기에서도, 포스트는 예컨대 포스트 "962a"와 "962b" 사이의 갭(963a)과 같은 이들 사이의 갭을 형성한다. 여기에서도, 회로 패널(970)은 갭 내로 연장할 수도 있으며, 그에 따라 센서 유닛과 광학 유닛 사이에 연장할 수도 있어, 전술한 바와 같이 센서 유닛에 대한 접속의 구축을 용이하게 한다. 도 13의 실시예에서, 갭은 상당한 높이를 갖는다. 완성된 조립체에서의 갭의 높이  $H_c$ 는 회로 패널(970)의 전면(901) 위의 탑재부(902)의 높이와 동등하다. 높이  $H_c$ 는 대략 2  $\text{mm}$  이상 정도인 것이 바람직하며, 5  $\text{mm}$  이상인 것이 더욱 바람직하며, 1  $\text{cm}$  이상인 것이 가장 바람직하다. 각각의 갭의 폭(즉, 회로 패널에 평행한, 배면 요소(962a, 962b) 간의 수평 거리)은 대략 2  $\text{mm}$  이상 정도인 것이 바람직하며, 대략 5  $\text{mm}$  이상인 것이 더욱 바람직하며, 대략 1  $\text{cm}$  이상인 것이 가장 바람직하다. 아래에 추가로 설명되는 바와 같이, 이러한 갭의 설치에 의해, 완성된 조립체에 대한 조작을 수행하기 위해 광학 요소와 구명부(972) 사이의 영역에의 액세스가 가능하게 된다. 그러나, 조립체의 전체적인 높이를 증가시키지 않고서도 커다란 갭이 제공될 수 있다. 렌즈(958)와 같은 광학 요소와 센서 유닛 간의 거리는 예컨대 렌즈(958)의 초점 거리와 같은 시스템의 광학 특성에 의해 설정된다. 따라서, 렌즈는 어떠한 경우에도 회로 패널의 전방에 상당한 거리로 지지될 수 있을 것이다.

[0102] 도 13의 실시예에 따른 모듈 또는 조립체는 갭을 통해 및 바람직하게는 회로 패널 내의 구명부(972)를 통해서도 센서 유닛에 대한 조작을 수행함으로써 조립 후에 처리될 수 있다. 예컨대, 조립체는 세정 작업 시에 갭 중의 하나 이상의 갭 내로 및 구명부(972)를 통해 세정액, 세정 기구 또는 이들 모두가 삽입되어 센서 모듈의 표면을 청소할 수 있다. 예컨대, 센서 모듈이 회로 패널의 배면 또는 저면을 향해 전방으로 바라보는 커버를 통합하는 경우, 센서 칩의 활상 영역과 정렬된 영역을 포함하는 구명부에 정렬된 커버의 영역을 청소할 수 있다. 완성된 조립체에 대해 이러한 세정 작업을 수행할 수 있는 성능은 조립 공정 동안의 오염물의 영향을 상쇄한다. 그 결과, 이에 의해 더 높은 품질의 카메라 유닛을 제공할 수 있게 되고, 또한 조립 동안에 적용되는 조건을 어느 정도는 오염물을 제공하는 정도로 완화시킬 수 있게 된다. 예컨대, "클린 룸" 환경이 불필요하게 되거나, 또는 저렴한 낮은 품질의 클린 룸이 이용될 수도 있게 된다. 다른 예에서, 센서 유닛은 별도의 커버를 통합하지 않는 대신에, 활상 영역을 갖는 동시에 조립 공정 동안의 화학적 또는 기계적 손상으로부터 덮개 없는 칩(bare chip)의 요소를 보호하는 효과가 있는 얇은 코팅의 형태로 패시베이션층을 갖는 "덮개 없는" 반도체칩으로만 구성될 수도 있다. 이러한 덮개 없는 활상 칩은 통상적으로 하나 이상의 활상 요소 위에 면지가 침적하는 것을 방지하기 위해 취급 동안 매우 엄격한 주의를 필요로 한다. 커버를 통합하고 있는 센서 유닛에 대한 요구사항은 다소 덜 엄격하다. 그러나, 조립 후의 세정에 의하여, 커버를 포함하지 않는 센서 유닛의 조립체에는 덜 엄격한 요구사항이 적용될 것이다.

[0103] 본 발명의 다른 실시예에 따른 방법에서, 센서 유닛은 예컨대 커버를 포함하는 센서 유닛에서의 커버의 외부면 상에 위치하는 희생층, 또는 커버를 포함하지 않는 센서 유닛에서의 칩의 활상 영역 상에 위치하는 희생층과 같은, 센서 유닛의 전면 상에 위치하는 희생층을 포함할 수도 있다. 조립체는 정위치에 있는 희생층을 포함하여 제조된다. 완성된 조립체는 그 후 희생층 또는 센서 유닛의 활상 영역에 정렬된 희생층의 적어도 일부분을 구명부(972)를 통해 및 지지 구조체(952) 내의 하나 이상의 갭(963)을 통해 제거하는 작업에 놓이게 된다. 예컨대, 희생층은 용해에 의해 제거되거나, 또는 희생층을 기계적으로 계합하여 센서 유닛으로부터 박리시킴으로써

제거될 것이다. 희생층의 제거에 의해 그 희생층 상에 축적되어 있을 수도 있는 어떠한 오염물이 제거된다.

[0104] 캡을 통해 다른 조작 또한 수행될 수 있다. 예컨대, 회로 패널의 도전체를 계합하여 이들을 센서 유닛의 컨택트에 접착시키기 위한 공구가 캡 내에 삽입될 수도 있다. 이와 달리, 구멍부(972), 하나 이상의 추가의 애피처(974), 또는 이러한 용도로 회로 패널에 제공된 다른 애피처(도시하지 않음)를 통해, 도전체와 센서 유닛 사이에 연장하는 와이어 본드를 제공하기 위해 와이어-본딩 공구가 이용될 수도 있다.

[0105] 전술한 바와 같이 커다란 캡을 제공하기 위해 포스트 형상의 배면 요소를 설치하는 것은 반드시 필수적인 것은 아니다. 예컨대, 배면 요소는 플레이트 또는 리브의 형태가 될 수도 있다. 또한, 복수의 캡을 제공하지 않고, 여러 조작을 위해 단지 하나의 캡으로 충분할 수도 있다.

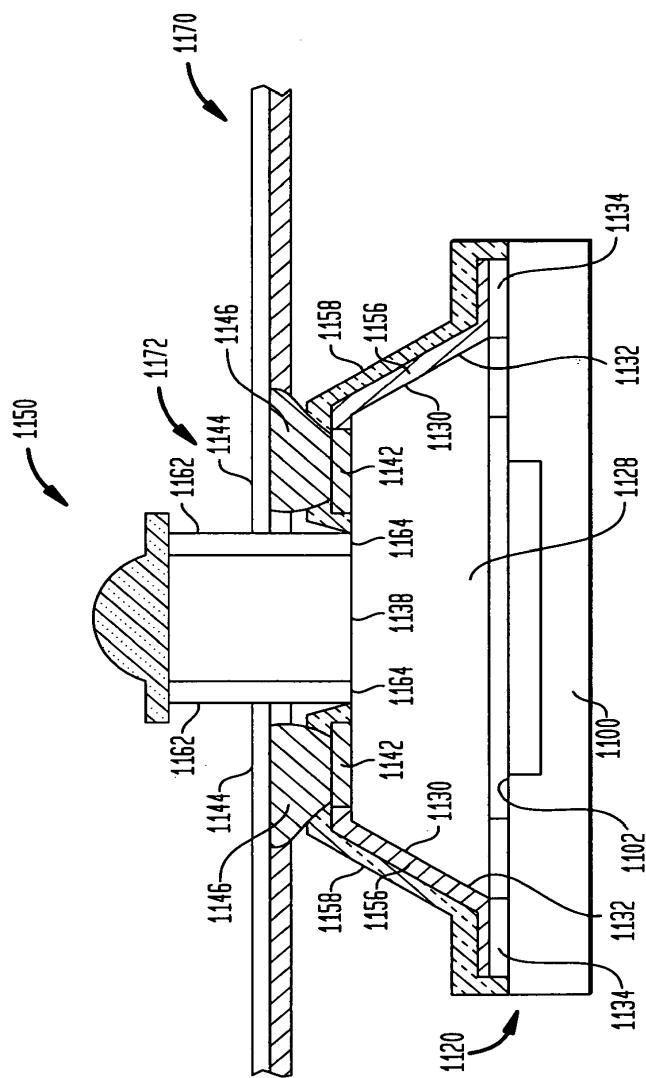

[0106] 도 14는 본 발명의 다른 실시예에 따른 광학 유닛 또는 카메라 모듈을 예시한다. 본 실시예에서, 센서 유닛(1120)은 예컨대 솔더 매쓰(1146)를 통해 커버(1128)의 외부면(1138) 상에 위치하는 회로 패널의 단자(1144)에 도전 가능하게 접속된 컨택트(1142)를 갖는다. 커버의 벽부(1130)는, 벽부의 에지(1132)에서의 편심거리(radius)가 경사가 완만하고, 바람직하게는 반도체칩의 전면(1102) 상에 제공된 제1 컨택트(1134)의 세트와 벽부(1130) 간의 원활한 전환을 제공하도록, 경사지는 것이 바람직하다. 도전성 트레이스(1156)의 세트가 제1 컨택트(1134)로부터 벽부(1130)를 따라 또한 커버(1128)의 외부면(1138) 상으로 연장하며, 이들은 컨택트(1128)에 도전 가능하게 접속된다. 바람직하게는 전기 영동 증착을 통해 증착된 에폭시 또는 다른 종합성 재료와 같은 유전체 코팅(1158)이 도전성 트레이스(1156) 상에 위치하고, 예컨대 컨택트(1142) 상에 노출된 개구를 갖는 솔더 마스크와 같은 패시베이션층으로서 이용된다.

[0107] 도 12를 참조하여 도시 및 설명된 예에서와 같이, 광학 유닛(1150)은 예컨대 렌즈 또는 다른 것 중에서 굴절성 또는 회절성 요소, 필터, 반사기 및 산란기로부터 선택된 다른 광학 소자와 같은 광학 요소(1158)를 지지하는 구조로부터 후방으로 연장하는 배면 요소(1162)의 세트를 갖는다. 여기에서도, 배면 요소의 배면(1164)은 회로 패널 내의 구멍부(1172)를 통해 연장하도록 구성되어, 커버(1128)의 외부면(1138) 또는 센서 유닛(1120)의 다른 기준 평면과 맞닿거나 계합한다.

[0108] 전술한 실시예에서, 회로 패널은 센서 유닛의 활상 영역과 정렬하여 회로 패널을 관통하여 연장하는 구멍부를 갖는다. 이러한 구멍부는 회로 패널 내의 투명 영역을 형성한다. 다른 실시예에서, 회로 패널은 센서 유닛의 활상 영역과 정렬하여 강성이지만 투명한 영역을 포함한다. 예컨대, 회로 패널은 투명 유전체 재료로부터 형성될 수 있으며, 그 경우 회로 패널의 투명 영역은 단순히 회로 패널의 도전체가 투명 영역을 교차하지 않도록 도전체를 배정함으로써 제공될 수 있다.

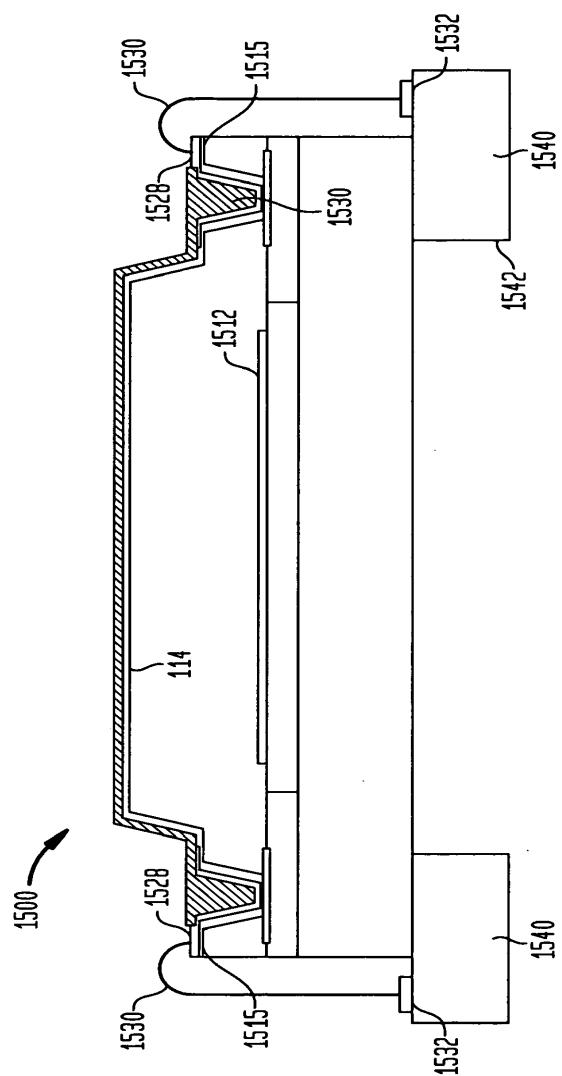

[0109] 도 15는 패키징된 반도체칩(10)(도 1)의 변형예에 따른 패키징된 반도체칩(1500)을 예시하는 단면도이다. 도 15에 도시된 바와 같이, 패키징된 반도체칩의 외부 컨택트(1528)는 패키징된 반도체칩의 하위 표면에 의해 형성된 패키징된 반도체칩의 레그(1515)에서 노출되어 있으며, 외부 컨택트(1528)는 반도체칩의 에지(1502)에 인접하여 배치되어 있다. 회로 패널과 같은 외부 요소에 대한 상호접속은 제1 단부에 있는 외부 컨택트(1528) 및 제2 단부에 있는 회로 패널(1540)의 단자(1532)에 접속된 본드 와이어(1530)를 형성함으로써 이루어질 수 있으며, 회로 패널은 패키징된 반도체칩의 광전 요소(1512), 예컨대 이미지 센서와 정합하여 개구(1542)를 갖는다. 이와 달리, 와이어 본드 대신에, 컨택트(1528)를 패키징된 반도체칩의 배면(114) 상에 노출된 외부 요소에 상호 접속시키기 위해 예컨대 솔더 매쓰 등과 같은 도전성 매쓰가 사용될 수 있다.

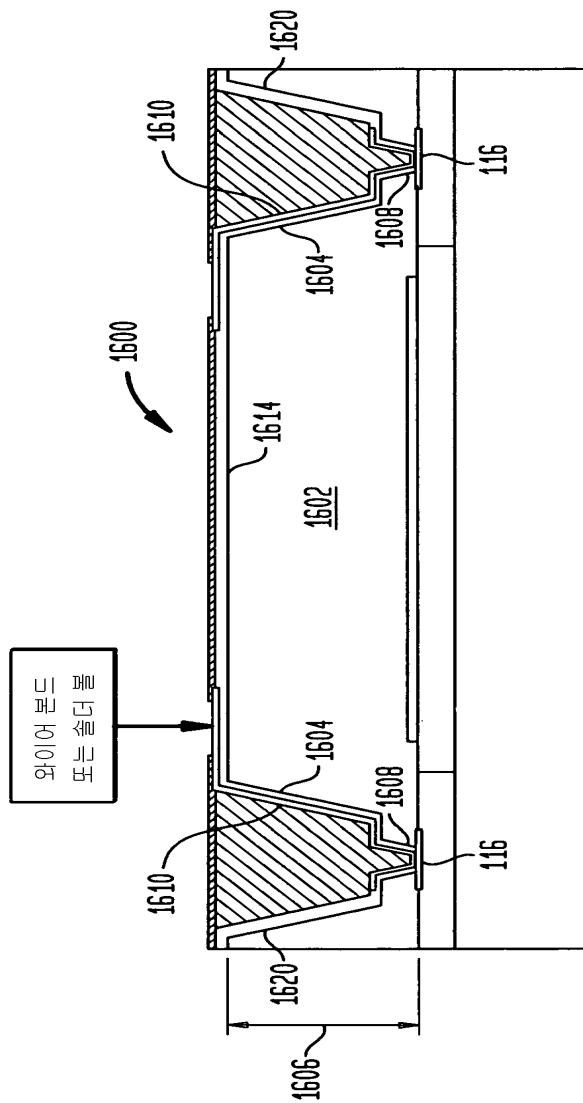

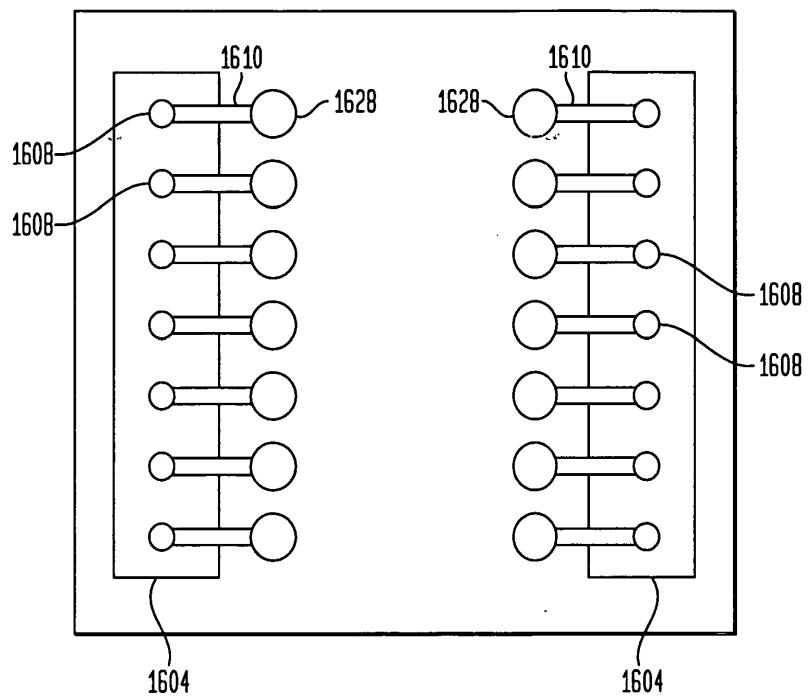

[0110] 도 16a는 패키징된 반도체칩(10)(도 1)의 변형예에 따른 패키징된 반도체칩(1600)을 예시하는 단면도이다. 본 실시예에서, 반도체칩(1602)에서의 커다란 개구(1604)가 반도체칩의 두께(1606)의 대부분을 통해 연장하며, 비아(1608)가 커다란 개구 내에서 전면 도전성 컨택트(116)까지 연장한다. 커다란 개구(1604)는 비아(1608) 중의 개별 비아 상에 위치하는 구멍부 형태로 제공될 수 있거나, 이와 달리 도 6a에 도시된 바와 같은 각각의 개별 칩의 접착 패드의 행(row)의 형태로 제공되거나, 또는 칩을 포함하는 웨이퍼의 길이를 연장하는 채널의 형태로 제공될 수 있다(도 6b). 웨이퍼 형태로 있는 동안의 칩의 두께(1606)는 도 16a에 도시된 패키징된 반도체칩을 형성하기 위한 단계들을 수행하기 전에 원래의 두께로부터 감소된다. 예컨대, 칩을 포함하고 있는 소자 웨이퍼는 소자 웨이퍼를 대응하는 리드 요소에 접착시키기 전에 약 200  $\mu\text{m}$ 의 두께를 갖도록 배면으로부터 그라인딩 또는 랩핑에 의해 얇게 될 수 있다. 웨이퍼를 리드 요소에 접착한 후에 그라인딩이 수행되면, 두께는 예컨대 50  $\mu\text{m}$  까지 더욱 감소될 수 있다.

[0111] 도 16a에 도시된 예에서, 도전성 트레이스(1610)는 비아(1608) 및 개구(1604)의 벽부를 따라 칩의 접착 패드(116)로부터 상방향으로 연장한다. 이와 달리, 비아(1608)는 도전성 재료로 채워질 수 있다. 이러한 경우에,

트레이스(1610)는 몇몇 비아에 의해 공유된 개구(1604)의 벽부를 따라 상방향으로 비아 중의 개별 비아로부터 연장할 수 있다(배면을 향해 바라본 평면도(도 16b)를 참조). 트레이스(1610)는 반도체칩(1602)의 배면(1614) 상의 위치에서 외부 컨택트(1628)에 연결된다. 도 1 및 도 15~24b는 채워진 작은 비아(1908)(예컨대, 도 19a) 또는 비아(예컨대 1608)를 따라 연장하는 트레이스를 갖는 실시예를 도시하고 있지만, 각각의 경우에서 도전성 비아의 다른 구조가 상호 변경 가능하다.

[0112] 이와 달리, 각각의 커다란 개구(1604)가 그 안에 하나의 비아만을 갖고 있을 때, 비아(1608) 및 커다란 개구(1604)는 비아(1608) 및 개구(1604)의 벽부 상에 배치된 유전체층(1620) 상에 위치하는 도전성 재료로 채워질 수 있다.

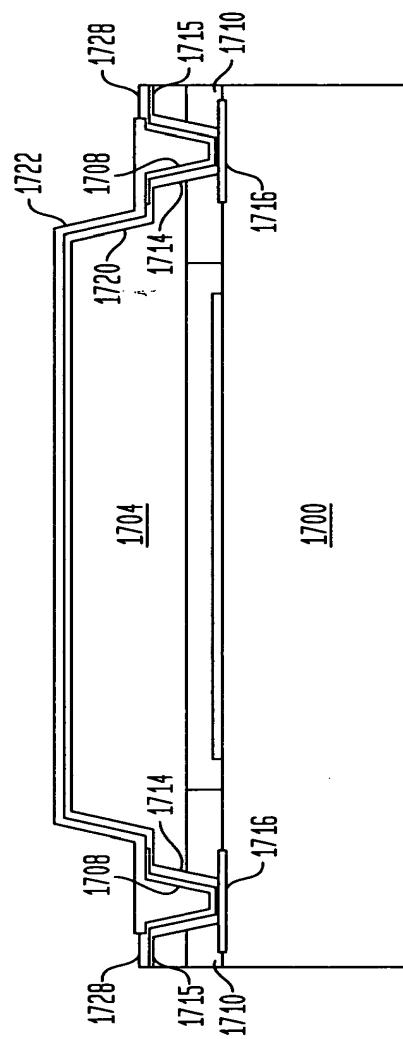

[0113] 도 17은 도 15를 참조하여 도시 및 설명된 실시예의 변형예에 따른 패키징된 반도체칩을 예시하고 있다. 이 예는 칩보다는 광학적으로 투광성의 리드가 그 에지에 인접한 하위 표면에 의해 정해진 레그(1715) 및 레그 상에 배치된 컨택트(1728)를 갖는다. 도 17은 예컨대 스판 코팅된 유전체, 솔더 마스크 등과 같은 하나 이상의 유전체층(1720, 1722)이 리드의 상면 상에 연장할 수도 있는 실시예를 예시하고 있다. 그러나, 리드(1704)가 통상적으로 유전체 특성을 갖는다면, 이러한 유전체층은 반드시 필요하지는 않을 것이며, 일반적으로 생략될 수 있다. 또한, 도 17에 도시된 바와 같이, 리드의 내부면(1706)은 지지 구조체(1710)에 의해 반도체칩의 전면(1702)으로부터 이격된다. 비아는, 리드를 포함하고 있는 리드 웨이퍼가 칩(1700)을 포함하고 있는 소자 웨이퍼에 소자 웨이퍼와 리드 웨이퍼 사이의 지지 구조체(1710)를 두고 결합된 후에, 형성되는 것이 바람직하다. 리드 및 지지 구조체(1710) 내에 구멍부(1714)를 형성하여 컨택트(1716)를 노출시킨 후에, 비아를 금속화하고, 컨택트(1728), 트레이스 등을 형성하기 위해, 전술한 바와 같은 각종 에칭, 밀링, 레이저 드릴링 또는 기계식 드릴링 공정이 이용될 수 있다.

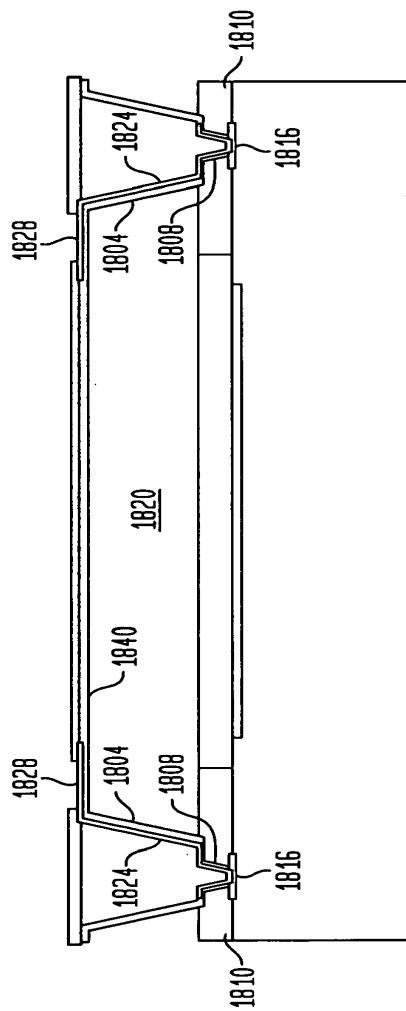

[0114] 도 18은 도 17에 도시된 실시예의 변형예에 따른 패키징된 반도체칩을 예시하고 있으며, 이 변형예는 도 16a 및 도 16b에 도시된 실시예와 유사성을 갖는다. 본 실시예에서, 리드 내의 커다란 개구(1804)의 벽부를 따라 연장하는 트레이스(1824)는 제1 단부에서는 금속화된 비아(1808)에 접속되고, 제2 단부에서는 리드(1820)의 상면(1844) 상에 위치하는 외부 컨택트(1828)에 접속된다. 비아는 지지 구조체(1810)를 통해 반도체칩의 도전성 컨택트(1816)까지 연장한다. 외부 요소에 대한 전기적인 상호접속은, 외부 컨택트(1828)에 부착된 본드 와이어를 통해 또는 예컨대 솔더 볼, 범프 등과 같은 솔더 매쓰를 통해 제공될 수 있다.

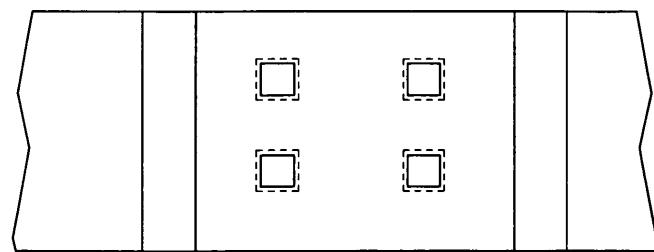

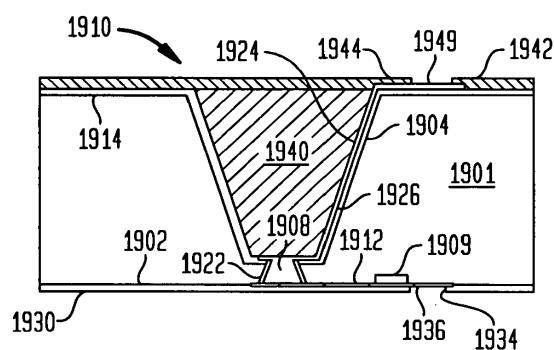

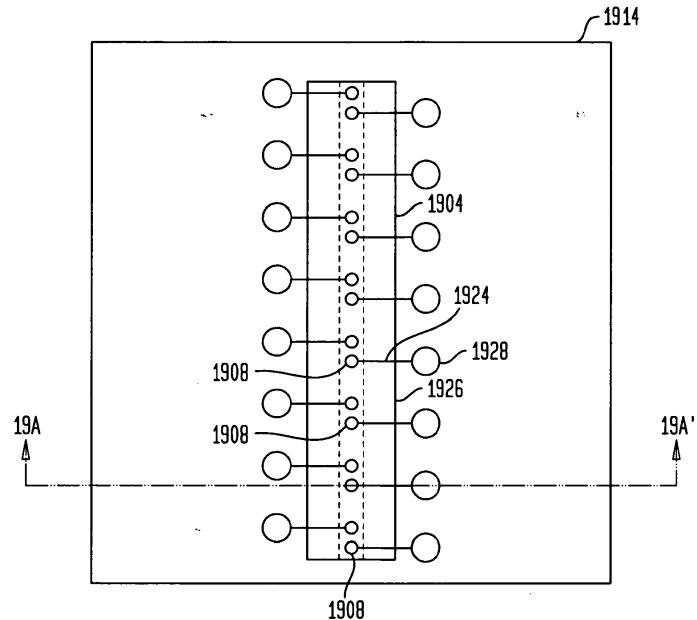

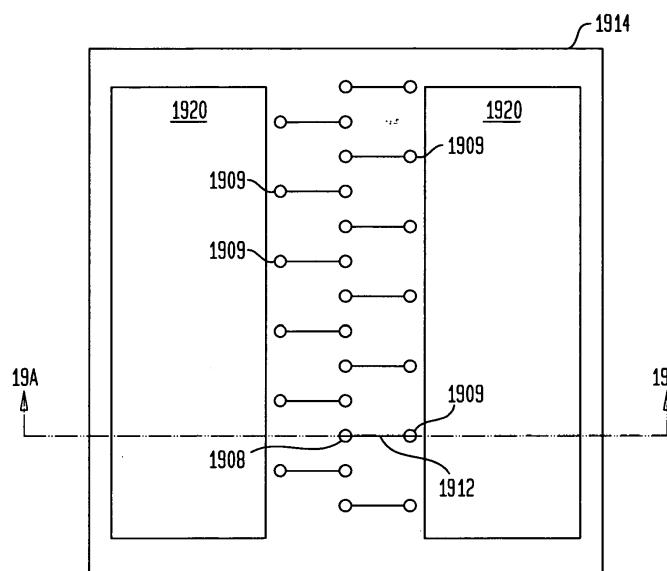

[0115] 도 19a는 본 발명의 다른 실시예에 따른 적층 가능한 칩-스케일 패키징된 반도체칩(1910)을 예시하는 단면도이다. 패키징된 반도체칩은 동적 랜덤 액세스 메모리("DRAM")와 같은 특정 유형의 미소전자 소자를 포함할 수 있다. 반도체칩(1901)의 전면(1902)으로부터 내측으로 연장하는 도전성 비아(1908)가 반도체칩의 배면(1914) 내의 커다란 개구의 벽부를 따라 연장하는 트레이스(1924)에 접속한다는 점에서, 패키징된 반도체칩(1910)은 패키징된 반도체칩(1600)(도 16a)과 유사한 특성을 갖는다. 그러나, 패키징된 반도체칩(1910)은 전면 상에 위치하지 않는 리드를 포함하지 않으며, 도전성 비아(1908)가 반도체칩(1901)의 전면을 따라 연장하는 재분배 트레이스(redistribution trace)(1912)를 통해 접착 패드(1909)에 접속된다. 도 19b는 패키징된 반도체칩의 배면(1914a)을 향해 바라본 대응 평면도이다. 도 19a의 도면은 도 19b의 라인 19A-19A'을 따라 절취된 것이다. 도 19b에 예시된 바와 같이, 트레이스(1924)는 비아(1908)로부터 커다란 개구(1904)의 벽부(1926)를 따라 또한 배면(1914) 상으로 상방향으로 연장한다. 트레이스(1924)는 반도체칩의 배면(1914) 상에 위치하는 외부 컨택트(1928)에 접속한다. 도 19c를 참조하면, 반도체칩(1901)의 전면을 향해 바라본 평면도가 도시되어 있으며, 이 반도체칩은 예컨대 DRAM을 포함하고 있다. DRAM에서는, 통상적으로 접착 패드(1909)가 메모리 회로(1920) 사이에 행으로 제공된다. 도 19a는 도 19c의 라인 19A-19A'을 따라 절취된 것이다. 전면(1902) 상의 재분배 트레이스(1912)는 접착 패드(1909)를 도전성 비아(1908)에 접속시킨다. 일부 트레이스가 도전성 비아로부터 떨어진 제1 방향으로 연장하고, 다른 트레이스가 비아로부터 떨어진 제2 방향으로 연장하도록, 트레이스가 도 19b 및 도 19c에 도시된 바와 같이 배치될 수 있으며, 여기서 제2 방향과 제1 방향은 서로 반대 방향이다. 이로써, 도전성 비아의 좌측편에 대한 접착 패드는 일부 도전성 비아에 접속되며, 도전성 비아의 우측편에 대한 접착 패드는 다른 도전성 비아에 접속된다.

[0116] 다시 도 19a를 참조하면, 도전성 비아(1908)는 이들이 전면(1902)으로부터 반도체칩의 배면(1914)을 향하는 방향으로 작아지게 되도록 테이퍼된다. 도전성 비아는 유전체층(1922)에 의해 반도체칩의 반도체 재료로부터 절연된다. 패시베이션층(1924)은 도전성 비아(1908)를 포함하는 반도체칩의 전면(1902) 상에 위치한다. 유전체층 내의 구멍부(1934)는 반도체칩의 전면에 있는 컨택트(1936)를 노출시킨다. 전면 컨택트(1936)는 접착 패드(1909)와 정합될 수 있지만 정합되지 않는 것이 바람직하다.

- [0117] 유전체 충전 재료(1940)가 패키징된 칩(1901)에 대한 기계적 지지뿐만 아니라 트레이스 간의 전기적 고립을 제공하기 위해 커다란 개구(1904) 내의 트레이스(1924) 상에 위치하는 것이 바람직하다. 예컨대 솔더 마스크와 같은 유전체층(1942)이 트레이스(1924) 상에 위치하는 것이 바람직하다. 유전체층 내의 개구(1944)는 칩의 배면 컨택트(1946)를 노출시킨다.

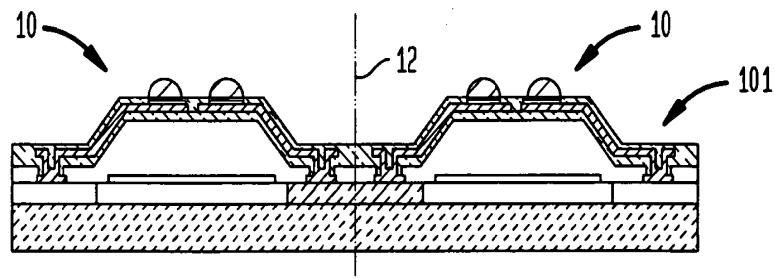

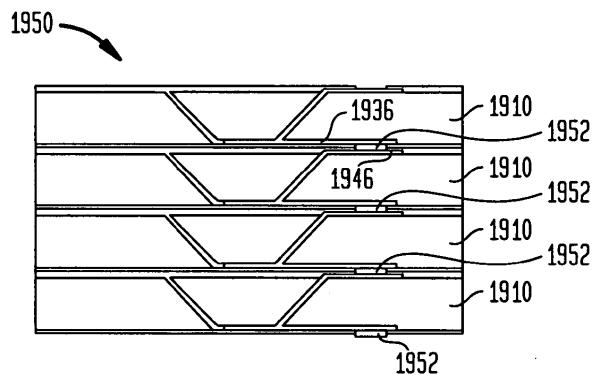

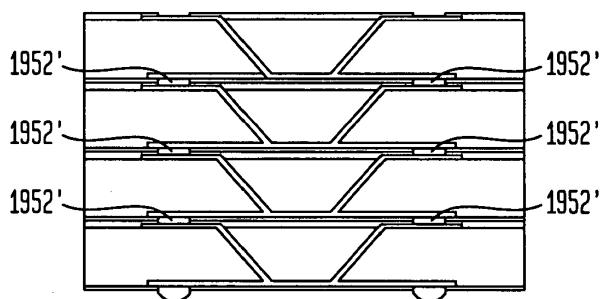

- [0118] 전면 컨택트(1936) 및 배면 컨택트(1946) 모두를 제공함으로써, 여러 개의 패키징된 칩이 하나 위에 다른 하나가 적층되어, 패키징된 칩의 적층 조립체(1950)를 형성할 수 있다(도 19d). 이러한 구성에서, 전면 컨택트는 배면 컨택트와 정렬된다. 적층 조립체에서의 패키징된 칩의 각각의 인접 패키징된 칩 간의 연결은 도전성 매쓰를 통해 이루어진다. 전면 상의 유전체층(1930) 및 배면 상의 유전체층(1942)은 상호접속이 제공된 곳을 제외하고는 조립체 내의 인접 패키징된 칩(1910) 간의 전기적 고립을 제공한다.

- [0119] 적층된 조립체(1950)의 이점은, 전면 컨택트 및 배면 컨택트가 패키징된 칩 내의 커다란 개구(1904)로부터 오프셋된다는 점이다. 따라서, 패키징된 칩을 상호접속할 때의 적층된 조립체에 가해지는 압력은 커다란 개구로부터 떨어진 지점에 있는 이들 컨택트에서 주로 느껴지게 된다. 이러한 구성은 반도체칩이 커다란 개구를 형성하기 위한 반도체 재료의 제거에 의해 약화될 가능성이 있는 곳에서 커다란 개구에 있는 패키징된 칩에 압력을 가하는 것을 방지하는데 도움을 준다.

- [0120] 오프셋 컨택트를 채용함에 따른 한 가지 가능한 이점은, 칩의 실제 접착 패드와 전면 및 배면 컨택트 간에 재분배 트레이스를 제공할 수 있다는 것이다. 예컨대 DRAM과 같은 특정 유형의 메모리의 칩 선택 특징은, 칩의 어떠한 접착 패드가 이들 칩 위에 위치하는 다른 칩의 접착 패드에 연결되지 않는 것을 요구할 수도 있다.

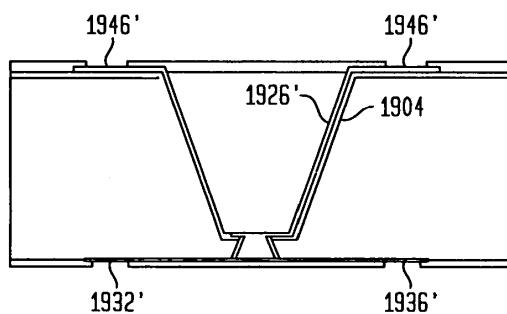

- [0121] 도 19e는 도 19a 내지 도 19c에 예시된 실시예의 변형예를 예시하는 단면도이다. 이 경우, 배면 컨택트(1946')는 커다란 개구(1904)의 좌측편과 우측편 양측에서 배면에 노출된다. 마찬가지로, 전면 컨택트(1936')는 개구(1904)의 좌측편과 우측편 양측에서 전면에 노출된다. 트레이스(1926')는 2개의 배면 컨택트(1946')를 동일한 도전성 비아(1908)에 접속시킨다. 도 10f는 도전성 매스(1952')가 커다란 개구의 각각의 좌측편과 우측편 상의 전면 컨택트를 커다란 개구의 각각의 좌측편과 우측편 상의 전면 컨택트에 결합시키고 있는 대응하는 적층 조립체를 예시하는 단면도이다. 도 19e 및 도 19f에 도시된 구성의 또 다른 가능한 이점은, 인접한 칩들 간에 흐르는 전류가 이제는 각각의 신호마다에 대해 좌측 컨택트와 우측 컨택트의 세트를 통해 흐르기 때문에 패키징된 칩 간의 인덕턴스가 감소된다는 점이다.

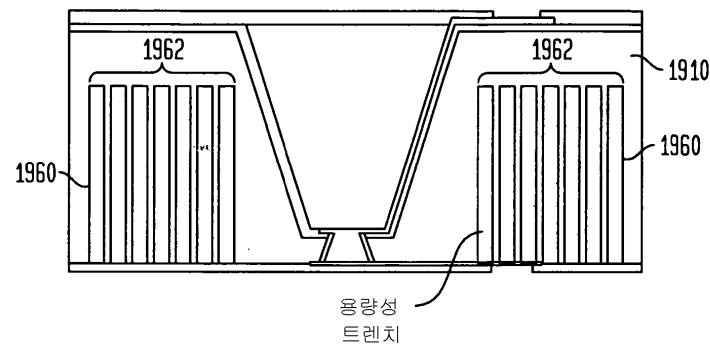

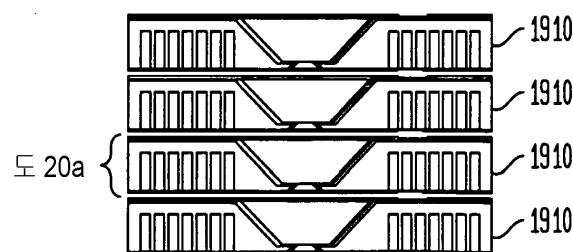

- [0122] 도 20a는 칩이 DRAM을 포함할 때의 적층 가능한 패키징된 칩(1910)의 장점을 예시하는 단면도이다. DRAM을 포함한 특정 유형의 반도체칩은 칩의 전면으로부터 하방향으로 연장하는 높은 종횡비의 트렌치(1960)에 형성된 커패시터를 포함한다. 간혹, 칩의 접착 패드가 이러한 트렌치 커패시터의 어레이(1962)에 근접하게 배치되는 경우가 있다. 패키징된 칩(1910)에서, 전면 컨택트와 배면 컨택트 간의 상호접속은 트렌치 커패시터 어레이(1962)로부터 약간의 거리에 있는 커다란 개구를 통해 이루어진다. 도 20b를 참조하면, 적층체 내의 인접한 칩(1910)들 간의 상호접속은 트렌치 커패시터 어레이의 배치 또는 기능과 간접하지 않는 칩을 통해 연장하는 상호접속을 이용하여 제공될 수 있다.

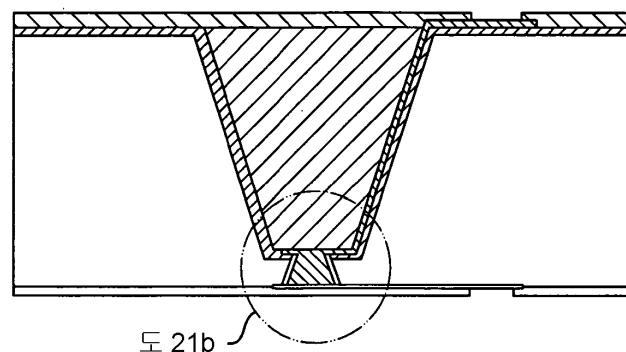

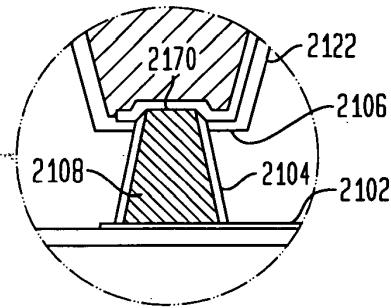

- [0123] 커다란 개구 내의 트레이스와 도전성 비아 간의 상호접속은, 상이한 방식으로 달성될 수 있다. 도 21a는 상호접속의 일례를 나타낸다. 도 21b에 확대도로 도시된 바와 같이, 칩의 전면(2102)으로부터 하방향으로 연장하도록 형성된 도전성 비아(2108)는 금속으로 채워진다. 예컨대, 전면으로부터 구멍부를 예칭한 후, 비교적 얇은 금속층이 구멍부의 벽부 및 저부를 덮도록 스퍼터링될 수 있다. 그 후, 금속 충전을 형성하기 위해 전해 도금이 이용될 수 있다. 도 21b에 예시된 바와 같이, 커다란 개구(2104)는, 예컨대 도전성 비아를 형성하고 있는 금속을 유지하면서 반도체 재료를 선택적으로 예칭하는 화학적 예칭에 의해 형성된다. 개구(2104)의 과예칭은 도전성 비아의 상면(2170)을 완전히 노출시키는 결과로 나타난다. 그 후, 유전체층(2122)이 형성되고, 개구가 예컨대 레이저를 사용하여 비아(2108) 상에 위치하는 유전체층 내에 형성된다. 레이저는 비아가 커다란 개구의 저부(2106) 상에 위치하는 유전체층과는 상이한 초점 평면에 있기 때문에 비아의 상면 위에서부터 유전체층을 선택적으로 제거할 수 있다. 후속하여, 도전성 트레이스(2124)가 형성될 때, 트레이스는 비아(2108)의 전체 상면(2170)과 접촉한다.

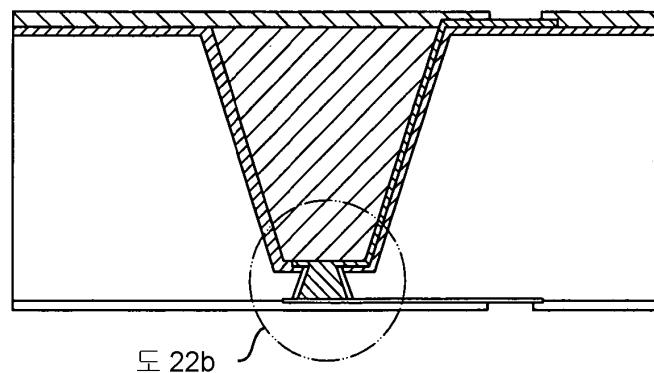

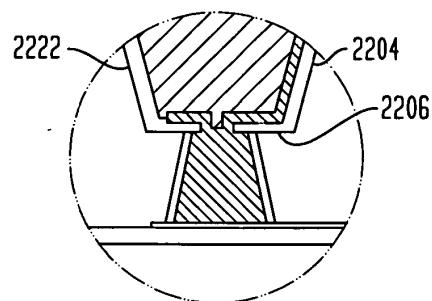

- [0124] 도 22a는 다른 예의 상호접속을 예시하고 있다. 도 22b에 확대도로 예시된 바와 같이, 커다란 개구(2204)는 도전성 비아를 형성한 후에 소잉함으로써 형성된다. 그리고나서, 유전체층(2222)을 형성한 후, 예컨대 레이저를 이용하여 유전체층 내에 개구를 형성한다. 이 예에서, 레이저 개구는 유전체층이 개구(2206)의 저부에 있는 반도체 재료를 접촉하는 개구를 형성하는 것을 방지하기 위해 크기가 축소된다.

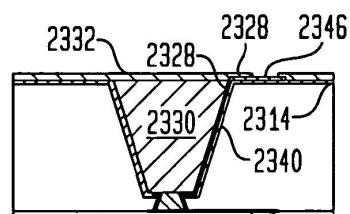

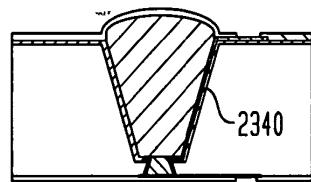

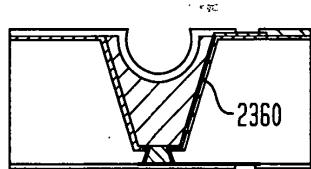

- [0125] 도 23a 내지 도 23f는 칩의 커다란 개구에 도전성 트레이스를 형성한 후에 그 개구를 채우기 위한 다양한 대안을 예시하는 단면도이다. 도 23a에 예시된 바와 같이, 도전성 트레이스를 형성한 후, 유동 가능한 유전체 충전재료(2330)가 커다란 개구 내에 또는 칩의 배면 상에 증착되거나 분배된다. 유동 가능한 유전체 재료는, 충전재료가 개구(2304)를 충전하고 또한 배면(2314)과 대략 동일한 높이의 표면을 제공하도록, 예컨대 스핀 코팅 또는 열처리에 의해 개구 내로 분배되도록 된다. 그리고나서, 충전 재료(2330) 및 트레이스(2328) 상에 위치하도록 솔더 마스크(2332)가 증착되며, 솔더 마스크 내의 개구는 배면 컨택트(2346)를 노출시킨다. 도 23b는 충전재료(2340)가 커다란 개구보다 큰 체적을 가져 배면(2304) 위로 튀어나오도록 하는 대안을 예시하고 있다. 이와 달리, 충전 재료(2340)가 균일하게 분포되지 않을 때, 충전 재료는 배면(2314) 위로 튀어나올 수도 있다. 도 23c는 충전 재료(2350)의 체적이 개구(2304)의 체적보다 작을 때 또는 충전 재료(2350)가 균일하게 분포되지 않을 때의 다른 예를 도시하고 있다.

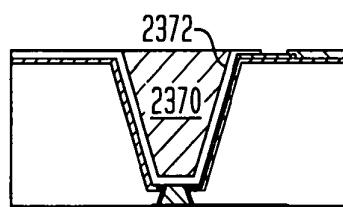

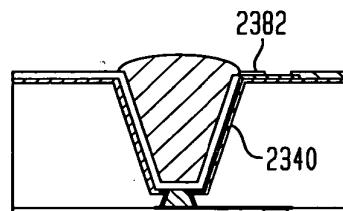

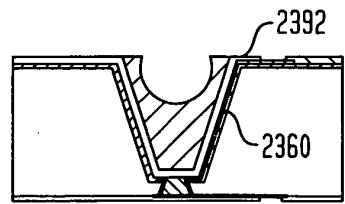

- [0126] 도 23d는 도 23a에 도시된 것과 유사하지만, 충전 재료(2370)를 증착하기 전에 솔더 마스크층(2372)이 증착되는 다른 대안을 예시하고 있다. 도 23e는 도 23b에 도시된 것과 유사하지만, 충전 재료(2380)를 증착하기 전에 솔더 마스크층(2382)이 증착되는 다른 예를 도시하고 있다. 마지막으로, 도 23f는 도 23c에 도시된 것과 유사하지만, 충전 재료(2390)를 증착하기 전에 솔더 마스크층(2392)이 증착되는 다른 예를 도시하고 있다.

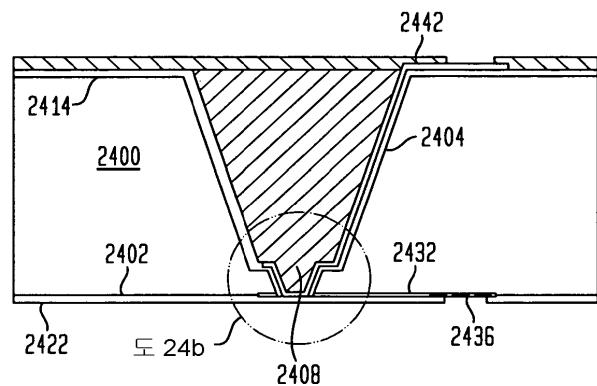

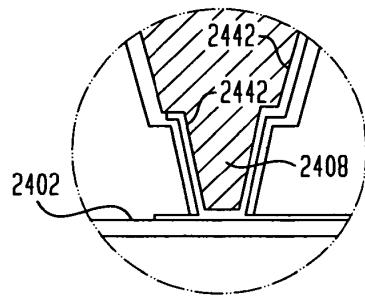

- [0127] 도 24a는 도 19a 내지 도 19c에 예시된 패키징된 칩의 변형예를 예시하는 단면도이다. 도 24b는 패키징된 칩의 도전성 비아(2408)를 나타내는 확대도이다. 본 변형예에서, 도전성 비아(2408)는 칩의 전면(2402)을 향하는 방향으로 커다란 개구를 통해 가해지는 압력으로부터 형성된다. 이 경우, 그 공정은 도 16a 및 도 16b를 참조하여 설명한 것과 유사하다. 제조하는 동안, 칩(2400)을 포함하는 소자 웨이퍼는 전면 상에 전면 컨택트(2436), 트레이스(2432) 및 유전체층(2422)을 형성한 후에 캐리어 웨이퍼(도시하지 않음) 상에 전면을 아래로 하여 일시적으로 탑재될 수 있다. 커다란 개구를 형성한 후, 구멍부는 레이저 드릴링, 에칭, 기계적 밀링 등에 의해 커다란 개구 내에서부터 비아용으로 형성될 수 있다. 구멍부가 형성된 후, 캐리어 웨이퍼는 도전성 트레이스(2402)를 구멍부의 저부에 있는 정위치에 유지하는데 도움을 주기 위해 도전성 트레이스(2402에 대한 기계적 지지를 제공할 수 있다. 후속하여, 비아 및 커다란 개구는, 비아 및 커다란 개구 내에 및 배면(2414) 상으로 연장하는 도전성 트레이스(2442)를 형성하기 위한 동시 가공에 의해 금속화될 수 있다.

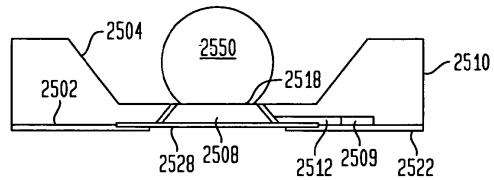

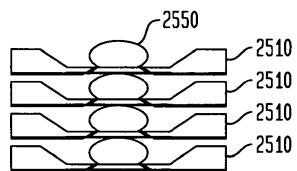

- [0128] 도 19a 내지 도 19c를 참조하여 전술된 패키징된 칩(1910)의 다른 변형에서, 도 25a는 솔더 볼(2550) 형태의 노출된 칩간(chip-to-chip) 상호접속부를 갖는 칩(2510)을 예시하고 있다. 본 실시예에서, 솔더 볼(2550)은 커다란 개구(2504) 내의 도전성 비아(2508)의 상면에 결합된다. 도전성 비아는 예컨대 도전성 트레이스를 통해 칩(2510)의 전면(2502) 상의 접착 패드(2509) 또는 다른 컨택트에 도전 가능하게 접속될 수 있다. 도전성 비아(2508)에 정합하는 개구를 갖는 패시베이션층(2522)이 도전성 트레이스(2512) 및 접착 패드(2509) 상에 위치한다. 도 25b는, 도 25a에 예시된 칩(2510)의 복수 개를 포함하고, 이 칩의 각각이 다음의 인접 칩과의 사이에 있는 솔더 볼(2550)을 통해 상호접속되는 적층 조립체를 예시하고 있다.

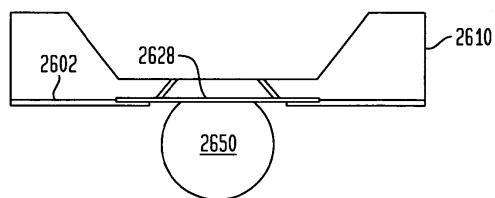

- [0129] 도 26a는 도 25a에 도시된 실시예의 변형예로, 솔더 볼(2650)이 칩의 전면(2602) 아래에서 하방향으로 돌출하도록 도전성 비아(2608)의 저면(2628)에 결합되는 예를 예시하고 있다. 도 26b는 인접 칩(2610) 간의 솔더 볼(2650)을 통해 서로 도전 가능하게 결합되어 있는 복수의 칩(2610)을 포함하는 적층 조립체를 예시하고 있다.

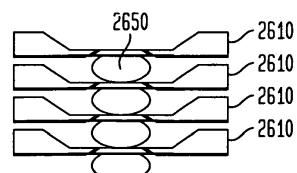

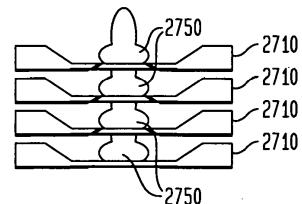

- [0130] 도 27a는 도 25a에 도시된 실시예의 변형예로, 금 또는 기타 금속으로 구성되는 스터드 범프(2750)가 도전성 비아(2708)의 상면(2718)에 결합되는 예를 예시하고 있다. 도 27b는 스터드 범프(2750)가 인접 칩을 도전 가능하게 상호접속시키는 대응하는 적층 조립체를 예시하고 있다.

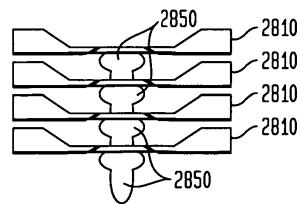

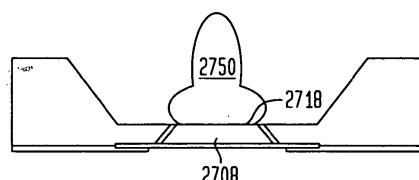

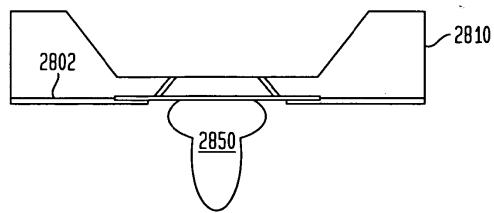

- [0131] 도 28a는 도 26a에 도시된 변형예와 유사한 다른 변형예로, 스터드 범프가 칩의 전면(2802)으로부터 하방향으로 돌출하도록 도전성 비아의 저면에 결합되는 예를 예시하고 있다. 도 28b는 도 28a에 도시된 것과 같은 칩(2810)이 스터드 범프(2850)에 의해 도전 가능하게 상호접속되는 대응하는 적층 조립체를 예시하고 있다.

- [0132] 본 발명을 특정의 실시예를 참조하여 설명하였지만, 이들 실시예는 단지 본 발명의 원리 및 응용에 대한 예시를 위한 것이다. 따라서, 이러한 예시 실시예에 대해 다수의 수정이 이루어질 수도 있으며, 칩부된 청구범위에 의해 한정된 바와 같은 본 발명의 사상 및 범위로부터 일탈함이 없이 다른 구성이 고려될 수도 있다.

- [0133] 예컨대, 본 발명의 특정 실시예에서, 도전성 트레이스는 반도체칩의 전면에 있는 도전성 특징부로부터 리드의 에지를 따라 또는 반도체칩을 덮고 있는 리드에 형성된 개구의 벽부를 따라 커버 요소의 외부면 상으로 연장한다.

## 도면의 간단한 설명

- [0019] 도 1은 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

- [0020] 도 2는 본 발명의 실시예에 따른 복수의 패키징된 반도체칩의 동시 제조 방법에서의 단계를 예시하는 단면도이다.

- [0021] 도 3a 및 도 3b는 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도와 그에 대응하는 하향(top-down) 평면도이다.

- [0022] 도 3c 및 도 3d는 본 발명의 실시예에 따른 제조 단계에서의 리드 부재의 설치를 예시하는 단면도와 그에 대응하는 평면도이다.

- [0023] 도 4는 본 발명의 실시예에 따른 제조 방법에서의 단계를 예시하는 단면도이다.

- [0024] 도 5a 및 도 5b는 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도 및 그에 대응하는 하향 평면도이다.

- [0025] 도 6a는 본 발명의 실시예에 따른 제조 단계를 예시하는 평면도이다.

- [0026] 도 6b는 본 발명의 다른 실시예에 따른 제조 단계를 예시하는 평면도이다.

- [0027] 도 7a, 도 7b 및 도 7c는 각각 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도, 그에 대응하는 하향 평면도, 및 확대도이다.

- [0028] 도 8a 및 도 8b는 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도 및 그에 대응하는 하향 평면도이다.

- [0029] 도 9a 및 도 9b는 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도 및 하향 평면도이다.

- [0030] 도 10a 및 도 10b는 본 발명의 실시예에 따른 제조 단계를 예시하는 단면도 및 하향 평면도이다.

- [0031] 도 11은 본 발명의 실시예에 따른 카메라 모듈 등의 광전자 소자 모듈을 예시하는 단면도이다.

- [0032] 도 12 및 도 13은 본 발명의 실시예에 따른 카메라 모듈 등의 다른 광전 소자 모듈을 예시하는 단면도 및 그에 대응하는 사시도이다.

- [0033] 도 14는 본 발명의 실시예에 따른 카메라 모듈 등의 또 다른 광전 소자 모듈을 예시하는 단면도이다.

- [0034] 도 15는 본 발명의 실시예에 따른 패키징된 반도체칩을 포함하는 조립체를 예시하는 단면도이다.

- [0035] 도 16a는 본 발명의 다른 실시예에 따른 패키징된 반도체칩을 포함하는 단면도이다.

- [0036] 도 16b는 도 16a에 도시된 패키징된 반도체칩을 예시하는 평면도이다.

- [0037] 도 17은 본 발명의 다른 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

- [0038] 도 18은 본 발명의 또 다른 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

- [0039] 도 19a는 본 발명의 또 다른 실시예에 따른 패키징된 반도체칩을 예시하는 부분 단면도이다.

- [0040] 도 19b는 도 19a에 도시된 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 평면도이다.

- [0041] 도 19c는 도 19a에 도시된 본 발명의 실시예의 변형예에 따른 패키징된 반도체칩을 예시하는 평면도이다.

- [0042] 도 19d는 도 19a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

- [0043] 도 19e는 도 19a에 도시된 본 발명의 실시예의 변형예에 따른 패키징된 반도체칩을 예시하는 부분 단면도이다.

- [0044] 도 19f는 도 19a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 부분 단면도이다.

- [0045] 도 20a는 도 19a에 도시된 본 발명의 실시예의 변형예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

- [0046] 도 20b는 도 20a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

- [0047] 도 21a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

- [0048] 도 21b는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 상세 확대도이다.

[0049] 도 22a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0050] 도 22b는 도 22a에 도시된 패키징된 반도체칩을 예시하는 상세 확대도이다.

[0051] 도 23a, 도 23b 및 도 23c는 본 발명의 실시예에 따른 변형예를 예시하는 패키징된 반도체칩을 도시하는 단면도이다.

[0052] 도 23d, 도 23e 및 도 23f는 본 발명의 실시예에 따른 변형예를 예시하는 패키징된 반도체칩을 도시하는 단면도이다.

[0053] 도 24a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0054] 도 24b는 도 24a에 도시된 패키징된 반도체칩을 예시하는 상세 확대도이다.

[0055] 도 25a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0056] 도 25b는 도 25a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

[0057] 도 26a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0058] 도 26b는 도 26a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

[0059] 도 27a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0060] 도 27b는 도 27a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

[0061] 도 28a는 본 발명의 실시예에 따른 패키징된 반도체칩을 예시하는 단면도이다.

[0062] 도 28b는 도 28a에 도시된 바와 같은 복수의 패키징된 반도체칩을 포함하는 적층 조립체를 예시하는 단면도이다.

## 도면

## 도면1

도면2

도면3a

도면3b

도면3c

도면3d

도면4

도면5a

도면5b

도면6a

도면6b

도면7a

도면7b

도면7c

도면8a

도면8b

도면9a

도면9b

도면10a

도면10b

도면11

도면12

도면13

도면14

도면15

도면16a

도면16b

도면17

도면18

도면19a

### 도면19b

### 도면19c

도면19d

도면19e

도면19f

도면20a

도면20b

도면21a

도면21b

도면22a

도면22b

도면23a

도면23b

도면23c

도면23d

도면23e

도면23f

도면24a

도면24b

도면25a

도면25b

도면26a

도면26b

도면27a

도면27b

도면28a

도면28b