(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6235093号

(P6235093)

(45) 発行日 平成29年11月22日(2017.11.22)

(24) 登録日 平成29年11月2日(2017.11.2)

(51) Int.Cl.

F 1

|        |         |           |        |        |     |

|--------|---------|-----------|--------|--------|-----|

| G 11 C | 5/02    | (2006.01) | G 11 C | 5/02   | 100 |

| G 11 C | 8/12    | (2006.01) | G 11 C | 8/12   |     |

| G 11 C | 11/408  | (2006.01) | G 11 C | 11/408 | 120 |

| G 11 C | 11/418  | (2006.01) | G 11 C | 11/418 | 120 |

| HO 1 L | 21/8242 | (2006.01) | HO 1 L | 27/108 | 321 |

請求項の数 2 (全 38 頁) 最終頁に続く

(21) 出願番号 特願2016-195544 (P2016-195544)

(22) 出願日 平成28年10月3日 (2016.10.3)

(62) 分割の表示 特願2012-111813 (P2012-111813)

原出願日 平成24年5月15日 (2012.5.15)

(65) 公開番号 特開2017-16728 (P2017-16728A)

(43) 公開日 平成29年1月19日 (2017.1.19)

審査請求日 平成28年11月1日 (2016.11.1)

(31) 優先権主張番号 特願2011-113011 (P2011-113011)

(32) 優先日 平成23年5月20日 (2011.5.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 長塚 修平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 松崎 隆徳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 井上 広樹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

複数のビット線と、ワード線と、サブワード線と、トランジスタと、複数のメモリセルと、を有し、

前記複数のメモリセルのそれぞれは、データ保持部と、選択トランジスタと、を有し、前記トランジスタは、前記選択トランジスタの一つと積層されており、

前記選択トランジスタは、ソース又はドレインの一方が前記複数のビット線の一つと電気的に接続され、ソース又はドレインの他方が前記データ保持部と電気的に接続され、ゲートが前記サブワード線と電気的に接続され、

前記トランジスタは、ソース又はドレインの一方が前記ワード線と電気的に接続され、ソース又はドレインの他方が前記サブワード線と電気的に接続されていることを特徴とする半導体装置。

## 【請求項2】

複数のビット線と、ワード線と、サブワード線と、トランジスタと、複数のメモリセルと、を有し、

前記複数のメモリセルのそれぞれは、選択トランジスタと、容量素子と、を有し、

前記トランジスタは、前記選択トランジスタの一つ及び前記容量素子の一つと積層されており、

前記選択トランジスタは、ソース又はドレインの一方が前記複数のビット線の一つと電気的に接続され、ソース又はドレインの他方が前記容量素子と電気的に接続され、ゲート

10

20

が前記サブワード線と電気的に接続され、

前記トランジスタは、ソース又はドレインの一方が前記ワード線と電気的に接続され、ソース又はドレインの他方が前記サブワード線と電気的に接続されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体素子が適用された記憶装置に関する。特に選択トランジスタを用いて書き込み、読み出しを行う記憶装置に関する。

【背景技術】

10

【0002】

半導体素子を利用した記憶装置において、各メモリセルに設けられた選択トランジスタを用いてデータの書き込みや読み出しを行う方法が知られている。選択トランジスタを用いる記憶装置の代表的な例としては、DRAM (Dynamic Random Access Memory) やSRAM (Static Random Access Memory) などが挙げられる。

【0003】

複数のメモリセルを有する記憶装置の場合、各メモリセルに設けられた選択トランジスタにはワード線とビット線が接続され、ワード線に入力された信号により当該メモリセルを選択状態、又は非選択状態に制御することができる。

20

【0004】

ここで、一つのワード線を選択すると、当該ワード線に接続された複数のメモリセルは全て選択状態に遷移するため、これら全てのメモリセルに接続されたビット線に対して処理を行う必要がある。そのためメモリセルの数（ビット数ともいう）が増大すると、ランダムアクセスに要するサイクルタイムが、ビット数の増大に応じて増大してしまう。このような問題を解決するため、論理回路を用いて一つのワード線を分割する方法が考案されている（特許文献1）。また、トランジスタを用いて一つのワード線を分割する方法も考案されている（特許文献2）

【先行技術文献】

【特許文献】

30

【0005】

【特許文献1】特開2004-171744号公報

【特許文献2】特開2004-234713号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に示す従来のワード線の分割方法では、各ワード線に接続される分割ワードライン（以降、サブワード線ともいう）のそれぞれに、CMOS技術が適用された論理回路を接続する必要があった。例えば、それぞれのサブワード線に対してAND回路を接続する構成とした場合、4～6個ものトランジスタで構成された回路をサブワード線ごとに設ける必要がある。

40

【0007】

特に近年のDRAMなどに代表されるように、セルサイズの縮小によるメモリセルの集積化が顕著になると、それぞれのサブワード線に接続する回路のサイズが大きい場合、集積化の妨げの要因となってしまう。

【0008】

また、特許文献2に示すワード線の分割方法では、安定した動作が行えない恐れがある。すなわち、ワード線（特許文献2の主ワード線に相当）とサブワード線（特許文献2の副ワード線に相当）に接続されるトランジスタのリーク電流により、徐々にサブワード線の電位が変動してしまい、サブワード線に接続されるメモリセルが選択状態となってしま

50

う。特にDRAMではメモリセルが意図せずに選択状態になると、保持されていたデータが消失してしまう。

#### 【0009】

本発明はこのような技術的背景のもとでなされたものである。したがって本発明は、回路構成が簡略化され、安定して動作可能なワード線分割回路を提供することを課題の一つとする。また、回路構成が簡略化され、安定して動作可能な記憶装置を提供することを課題の一つとする。

#### 【0010】

本発明の一態様は、上記課題の少なくとも一を解決するものである。

#### 【課題を解決するための手段】

10

#### 【0011】

本発明の一態様のワード線分割回路は、ワード線と、複数のサブワード線と、複数のトランジスタと、を有する。また上記トランジスタは、それぞれソース又はドレインの一方がワード線と電気的に接続され、ソース又はドレインの他方がサブワード線の一つと電気的に接続され、且つ、オフ状態におけるリーク電流がチャネル幅 $1\text{ }\mu\text{m}$ あたり $1\times 10^{-17}\text{ A}$ 以下である。

#### 【0012】

上記本発明の一態様のワード線分割回路は、ワード線とサブワード線との間に極めてリーク電流の低減されたトランジスタが電気的に接続される。したがって、当該トランジスタがオン状態の時には、ワード線に入力される信号がサブワード線に入力される。一方、当該トランジスタがオフ状態の時には、ワード線に入力される信号によらず、サブワード線は非選択状態が保持される。

20

#### 【0013】

ここで例えば、チャネルが形成される半導体層としてシリコンを用いたトランジスタを上記トランジスタに適用した場合、トランジスタがオフ状態に保持されていても、そのリーク電流によって徐々にサブワード線の電位が変動してしまう。そのため結果としてサブワード線に接続されるメモリセルが選択状態となってしまう恐れがあるため、上記のような簡略化され、安定して動作可能なワード線分割回路を実現することができない。ここで、リーク電流の極めて低減されたトランジスタを用いることにより、上記のような極めて回路構成が簡略化され、安定して動作可能なワード線分割回路を実現することができる。

30

#### 【0014】

また、本発明の一態様は、上記ワード線分割回路において、上記トランジスタは、チャネルが形成される半導体層に酸化物半導体が適用されていることを特徴とする。

#### 【0015】

特に、上記トランジスタとして、シリコンよりもバンドギャップの広い酸化物半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタを適用することが好ましい。このようなトランジスタは、オフ状態におけるリーク電流が小さい特徴を有する。

#### 【0016】

また、上記トランジスタを構成する半導体は、真性キャリア密度が極めて低い酸化物半導体を用いることが好ましい。チャネルが形成される半導体層の真性キャリア密度が極めて低いため、トランジスタのオフ状態におけるリーク電流は極めて小さいものとなる。このような特徴は、他の半導体（例えばシリコン）にはない酸化物半導体に特有の特徴である。

40

#### 【0017】

また、本発明の一態様の記憶装置は、ビット線と、ワード線と、複数のサブワード線と、複数のトランジスタと、複数のメモリセルと、を有する。また、上記メモリセルのそれぞれは、データ保持部と、選択トランジスタと、を有し、上記選択トランジスタは、ソース又はドレインの一方がビット線に電気的に接続され、ソース又はドレインの他方がデータ保持部に電気的に接続され、ゲートがサブワード線の一つと電気的に接続される。また、トランジスタは、それぞれソース又はドレインの一方がワード線と電気的に接続され、

50

ソース又はドレインの他方がサブワード線の一つと電気的に接続され、且つ、オフ状態におけるリーク電流がチャネル幅  $1 \mu m$ あたり  $1 \times 10^{-17} A$ 以下である、記憶装置である。

【0018】

このように、本発明の一態様の構成が簡略化され、安定して動作可能なワード線分割回路が適用された記憶装置は、回路構成を簡略化することができるため、回路面積が小さく、高集積化に適した記憶装置とすることができます。

【0019】

また、本発明の一態様の上記記憶装置は、メモリセルとしてDRAMの構成を適用することもできるし、またSRAMの構成を適用することもできる。

10

【0020】

したがって、従来のDRAMやSRAMに比べて回路面積の増加を抑制しつつ、安定してワード線を分割して用いることができる。

【0021】

また、本発明の一態様の上記記憶装置の選択トランジスタとして、オフ状態におけるリーク電流がチャネル幅  $1 \mu m$ あたり  $1 \times 10^{-17} A$ 以下であるトランジスタを適用できる。

【0022】

選択トランジスタにこのようなリーク電流が極めて低減されたトランジスタを適用することにより、データ保持部に保持されたデータが選択トランジスタを介して消失してしまうことが抑制され、データ保持期間の極めて長い記憶装置、言い換えると実質的に不揮発性の記憶装置を実現できる。特に、DRAMの選択トランジスタに、上記リーク電流の極めて低いトランジスタを適用することにより、リフレッシュの頻度が極めて低減された、若しくはリフレッシュが不要な記憶装置として用いることができる。

20

【0023】

また、本発明の一態様は、上記記憶装置において、上記トランジスタは、チャネルが形成される半導体層に酸化物半導体が適用されていることを特徴とする。

【0024】

このように、本発明の一態様のワード線分割回路が適用された記憶装置は、回路構成を簡略化することができるため、回路面積が小さく、高集積化に適した記憶装置とすることができます。また、ワード線分割回路を構成するトランジスタとして、チャネルが形成される半導体層に酸化物半導体が適用されたトランジスタを適用することが好ましい。

30

【0025】

なお、本明細書等において、ワード線とは、接続されるセルの選択トランジスタのゲートに電気的に接続され、当該ワード線に接続されるセルを選択するための選択信号線の一つである。記憶装置においては、上記セルはデータ保持部を有するメモリセルとなる。

【0026】

また、本明細書等において、ビット線とは、接続されるセルへの入力信号、またはセルからの出力信号が与えられる信号線のひとつである。記憶装置においては、上記セルは、データ保持部を有するメモリセルであり、ビット線にはメモリセルからのデータの読み出し信号とメモリセルへの書き込み信号のいずれか、又は両方が与えられる。

40

【0027】

なお、本明細書等において、ワード線分割回路とは、ワード線に接続された複数のサブワード線の、各々の選択状態を制御可能な回路のことを言う。ここで、当該ワード線分割回路は、少なくとも一つのスイッチング素子（トランジスタを含む）を含んで構成されるものとする。また広義に、ワード線及び複数のサブワード線をワード線分割回路の構成要素として含むものとする。

【0028】

なお、本発明の一態様のワード線分割回路は、記憶装置に限られるものではなく、ワード線を用いた様々な回路に対して適用することができ、簡略化された構成により安定して

50

ワード線を分割して制御することができる。ワード線を用いる他の回路の例としては、液晶表示装置や、電界発光型の表示装置(有機EL(Electroluminescence)素子やLED(Light Emitting Diode)が適用された表示装置)、又はFED(Field Emission Display)などの表示装置が挙げられる。

【発明の効果】

【0029】

本発明の一態様によれば、回路構成が簡略化され、安定して動作可能なワード線分割回路を提供できる。また、回路構成が簡略化され、安定して動作可能な記憶装置を提供できる。

10

【図面の簡単な説明】

【0030】

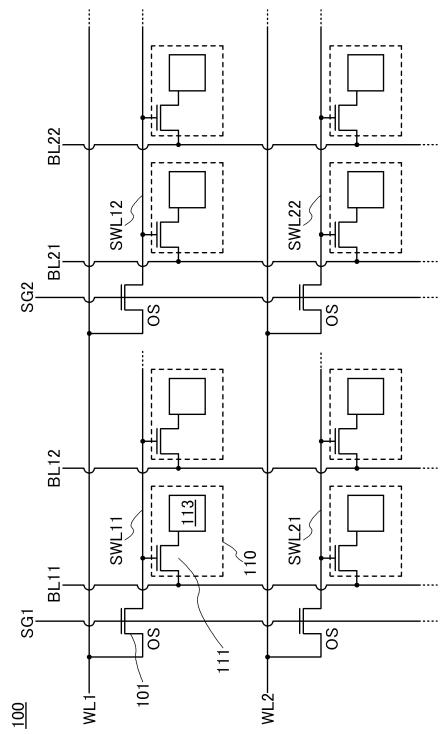

【図1】本発明の一態様の、記憶装置を説明する図。

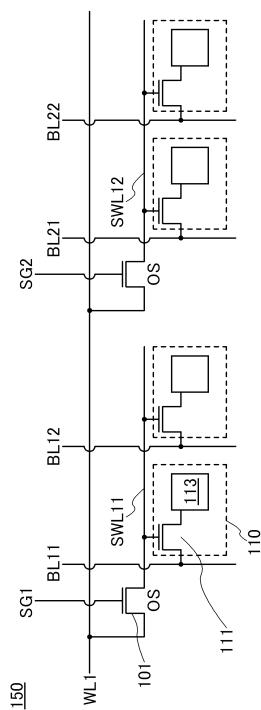

【図2】本発明の一態様の、記憶装置を説明する図。

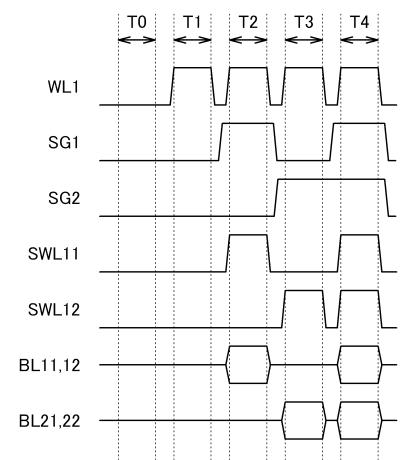

【図3】本発明の一態様の、記憶装置の動作を説明する図。

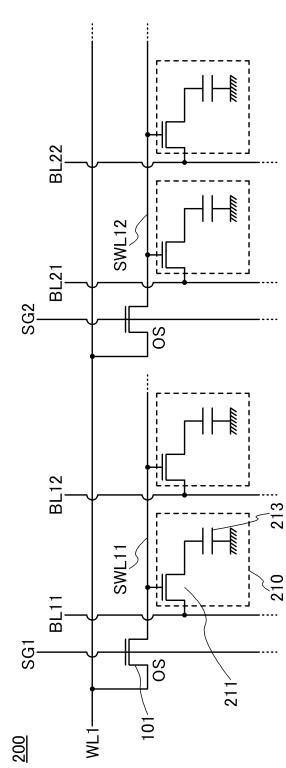

【図4】本発明の一態様の、記憶装置を説明する図。

【図5】本発明の一態様の、記憶装置を説明する図。

【図6】本発明の一態様の、記憶装置を説明する図。

【図7】本発明の一態様の、記憶装置を説明する図。

【図8】本発明の一態様の、記憶装置を説明する図。

20

【図9】本発明の一態様の、トランジスタの構成を説明する図。

【図10】本発明の一態様の、トランジスタの作製方法を説明する図。

【図11】本発明の一態様の、記憶装置の構成を説明する図。

【図12】本発明の一態様に係る酸化物材料の構造を説明する図。

【図13】本発明の一態様に係る酸化物材料の構造を説明する図。

【図14】本発明の一態様に係る酸化物材料の構造を説明する図。

【図15】本発明の一態様に係る酸化物材料の構造を説明する図。

【発明を実施するための形態】

【0031】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

30

【0032】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0033】

40

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET(Insulated Gate Field Effect Transistor)や薄膜トランジスタ(TFT:Thin Film Transistor)を含む。

【0034】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

50

**【 0 0 3 5 】**

また、本明細書等において、トランジスタのソース又はドレインのどちらか一方のことを「第1電極」と呼び、ソース又はドレインの他方を「第2電極」とも呼ぶことがある。なお、この際、ゲートについては「ゲート」又は「ゲート電極」とも呼ぶ。

**【 0 0 3 6 】**

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、コイル、容量素子、その他の各種機能を有する素子などが含まれる。10

**【 0 0 3 7 】**

なお、本明細書等においてノードとは、回路を構成する素子の電気的な接続を可能とする素子（例えば、配線など）のことをいう。したがって、”Aが接続されたノード”とは、Aと電気的に接続され、且つAと同電位と見なせる配線のことをいう。なお、配線の途中に電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど）が1個以上配置されていても、Aと同電位であれば、その配線はAが接続されたノードと見なせる。

**【 0 0 3 8 】**

なお、本明細書で説明する回路図においては、酸化物半導体などを用いたオフ電流が低減されたトランジスタであることを示すために、OSの符号を併せて付す場合がある。20

**【 0 0 3 9 】****(実施の形態 1 )**

本実施の形態では、本発明の一態様のワード線分割回路と、当該ワード線分割回路が適用された記憶装置の構成例について図1乃至図3を用いて説明する。

**【 0 0 4 0 】****<構成例>**

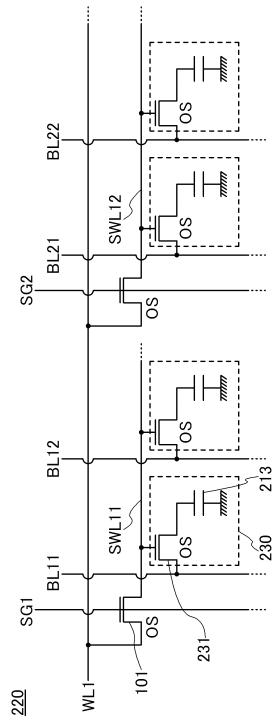

図1に示す記憶装置100は、m行×(n×1)列(m及び1は1以上の整数であり、nは2以上の整数である。)のマトリクス状に配置された複数のメモリセルを有する記憶装置である。なお、図1には明瞭化のため、m、n及び1がそれぞれ2までの構成を明示している。30

**【 0 0 4 1 】**

記憶装置100は、m本のワード線WLm、n本の選択信号線SGn、(n×1)本のビット線BLn1、及び(m×n)本のサブワード線SWLmnを有し、サブワード線SWLmnとビット線BLn1とそれぞれ接続する複数のメモリセル110を有する。

**【 0 0 4 2 】**

メモリセル110は、少なくとも一つの選択トランジスタ111と、データ保持部113を有する。選択トランジスタ111は、ゲートが一本のサブワード線SWLmnと接続し、第1電極が一本のビット線BLn1と接続し、第2電極がデータ保持部113と接続する。40

**【 0 0 4 3 】**

データ保持部113は、選択トランジスタ111を介して入力されたデータを保持する機能を有する。また、データ保持部113は選択トランジスタ111を介してデータを出力することもできる。データ保持部113やメモリセル110の具体的な構成例については後の実施の形態で例示する。

**【 0 0 4 4 】**

サブワード線SWLmnは、トランジスタ101を介してワード線WLmに接続されている。トランジスタ101は、第1電極がワード線WLmと接続し、第2電極がサブワード線SWLmnと接続し、ゲートが選択信号線SGnと接続する。

**【 0 0 4 5 】**

10

20

30

40

50

ここで、本実施の形態では、トランジスタ 101 及び選択トランジスタ 111 は共に n チャネル型のトランジスタとする。

#### 【0046】

ここで、トランジスタ 101 にはオフ状態におけるリーク電流（オフ電流とも呼ぶ）が低減されたトランジスタが適用される。トランジスタ 101 のオフ電流は、接続されるサブワード線と、これに接続される複数のメモリセルとの間の寄生容量の値や、当該サブワード線の選択時間などに応じて要求される値が異なるが、オフ電流が低いほど非選択状態におけるサブワード線の電位の変動を小さいものとすることができますため好ましい。例えばトランジスタ 101 のオフ電流の値としては、チャネル幅 1 μmあたり 10 aA ( $1 \times 10^{-17} A$ ) 以下とすればよい。なお一般的には、チャネルが形成される半導体層としてシリコンを用いた場合には、オフ電流はチャネル幅 1 μmあたり数 pA ( $1 \times 10^{-12} A$ ) ~ 数 nA ( $1 \times 10^{-9} A$ ) 程度である。10

#### 【0047】

このような低いオフ電流を実現するトランジスタとしては、例えば、チャネルが形成される半導体層にシリコンよりもバンドギャップの広い半導体を用いたトランジスタを適用することができる。例えば 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3.0 eV 以上のバンドギャップを有する半導体を用いることができる。このような半導体として酸化物半導体を用いることが好ましい。

#### 【0048】

さらに、上記酸化物半導体を含むトランジスタは、オフ状態におけるリーク電流が低く、チャネル幅 1 μmあたり 10 aA ( $1 \times 10^{-17} A$ ) 以下、好ましくはチャネル幅 1 μmあたり 1 aA ( $1 \times 10^{-18} A$ ) 以下、より好ましくはチャネル幅 1 μmあたり 10 zA ( $1 \times 10^{-20} A$ ) 以下、さらに好ましくはチャネル幅 1 μmあたり 1 zA ( $1 \times 10^{-21} A$ ) 以下、さらに好ましくはチャネル幅 1 μmあたり 100 yA ( $1 \times 10^{-22} A$ ) 以下である。20

#### 【0049】

一つのトランジスタ 101 に接続されるサブワード線は、当該トランジスタ 101 のオン、オフによってワード線との導通、非導通が制御される。トランジスタ 101 がオン状態のとき、ワード線とサブワード線とは導通し、一方オフ状態のとき、これらは非導通となる。またトランジスタ 101 のリーク電流が極めて小さいため、当該トランジスタ 101 がオフ状態、すなわちサブワード線が非導通状態ではワード線に入力される電位によるサブワード線の電位の変動が極めて小さいものとなる。30

#### 【0050】

このように、極めてリーク電流の小さいトランジスタを用いることにより、構成が極めて簡略化され、安定して動作可能なワード線分割回路を実現することが出来る。本実施の形態においては、ワード線 WLm と、ワード線 WLn に接続される複数のサブワード線 SWLmn と、これらに直列に接続される複数のトランジスタとを含む構成がワード線分割回路に相当する。

#### 【0051】

<回路動作例>40

続いて、上記記憶装置の動作例について説明する。ここでは簡単のため、図 2 に示すように 1 行 × 4 列に配置された 4 つのメモリセルを有する記憶装置 150 の動作について説明する。記憶装置 150 は、上記記憶装置 100 において、m を 1、n を 2、また l を 2 とした記憶装置である。

#### 【0052】

図 3 は、記憶装置 150 の動作におけるタイミングチャートの一例である。図 3 には上から順に、図 2 に示すワード線 WL1、選択信号線 SG1、選択信号線 SG2、サブワード線 SWL11、サブワード線 SWL12、ビット線 BL11 及び BL12、ビット線 BL21 及び BL22 における電位の時間推移を模式的に示している。

#### 【0053】

50

なお、ワード線WL1、選択信号線SG1、選択信号線SG2に入力される電位がハイレベル電位のときこれらは選択状態であり、ローレベル電位のときこれらは非選択状態であるとする。また、トランジスタ101及び選択トランジスタ111は、それぞれのゲートに入力される電位がハイレベル電位のときにオン状態となり、一方ローレベル電位のときにオフ状態となるものとする。

#### 【0054】

以下では、各メモリセル内のデータ保持部113へデータを書き込む場合を想定して説明する。

#### 【0055】

期間T0では、ワード線WL1が非選択状態となっている。またこのとき、選択信号線SG1及びSG2も非選択状態である。10

#### 【0056】

期間T1では、ワード線WL1が選択状態、また選択信号線SG1及びSG2が非選択状態である。このとき、選択信号線SG1及び選択信号線SG2に接続されるトランジスタ101のオフ電流は極めて小さいため、サブワード線SWL11及びSWL12の電位は変化しない。

#### 【0057】

期間T2では、ワード線WL1及び選択信号線SG1が選択状態である。したがって、サブワード線SWL11にはワード線WL1の電位が入力され、サブワード線SWL11に接続される複数のメモリセル110は選択状態となる。一方、選択信号線SG2は非選択状態であり、且つ当該選択信号線SG2に接続されるトランジスタ101のオフ電流は極めて小さいため、サブワード線SWL12の電位はローレベル電位のまま保持される。20

#### 【0058】

ここで、ビット線BL11及びBL12にはそれぞれに接続されるメモリセル110への書き込みデータが入力される。すなわち、ビット線BL11及びBL12には、ハイレベル電位、又はローレベル電位のいずれかが入力される。このとき、ビット線BL11及びBL12に接続されるそれぞれのメモリセル110内の選択トランジスタ111はオン状態であるため、ビット線BL11又はBL12の電位が選択トランジスタ111を介してデータ保持部113に入力される。このようにして、サブワード線SWL11に接続されるメモリセル110にデータを書き込むことができる。30

#### 【0059】

期間T3では、ワード線WL1及び選択信号線SG2が選択状態である。したがって、サブワード線SWL12にはワード線WL1の電位が入力され、サブワード線SWL12に接続される複数のメモリセル110は選択状態となる。一方、選択信号線SG1は非選択状態であり、且つ当該選択信号線SG1に接続されるトランジスタ101のオフ電流は極めて小さいため、サブワード線SWL11の電位はローレベル電位のまま保持される。

#### 【0060】

ここで、ビット線BL21及びBL22にはそれぞれに接続されるメモリセル110への書き込みデータが入力される。すなわち、ビット線BL21及びBL22には、ハイレベル電位、又はローレベル電位のいずれかが入力される。このとき、ビット線BL21及びBL22に接続されるそれぞれのメモリセル110内の選択トランジスタ111はオン状態であるため、ビット線BL21又はBL22の電位が選択トランジスタ111を介してデータ保持部113に入力される。このようにして、サブワード線SWL12に接続されるメモリセル110にデータを書き込むことができる。40

#### 【0061】

期間T4では、ワード線WL1並びに選択信号線SG1及びSG2が選択状態である。したがって、サブワード線SWL11及びSWL12には同時にワード線WL1の電位が入力され、サブワード線SWL11及びSWL12に接続される複数のメモリセル110は選択状態となる。

#### 【0062】

50

20

30

40

50

さらに、上記と同様にビット線 B L 1 1 乃至 B L 2 2 にはそれぞれに接続されるメモリセル 1 1 0 への書き込みデータが入力され、それぞれのメモリセル 1 1 0 内のデータ保持部 1 1 3 に選択トランジスタ 1 1 1 を介してデータが書き込まれる。

#### 【 0 0 6 3 】

なお、上記ではメモリセル 1 1 0 へのデータの書き込みを想定した動作について説明したが、読み出しに関しても同様の動作で行うことができる。読み出し動作の場合は、ビット線 B L 1 1 乃至 B L 2 2 には、メモリセル 1 1 0 内のデータ保持部 1 1 3 に保持されたデータに応じた電位が出力される。したがって、読み出し動作の場合は、図 3 に示すタイミングチャートのうち、ビット線 B L 1 1 乃至 B L 2 2 の波形を出力電位に置き換えることができる。

10

#### 【 0 0 6 4 】

なお、ここではデータ保持部 1 1 3 に書き込まれるデータをハイレベル電位又はローレベル電位の 2 種類の電位として説明したが、データ保持部 1 1 3 の構成によっては、3 種類以上の複数のレベルの電位を保持することもできる。例えば 4 種類の電位を保持することができれば、一つのメモリセルに 2 ビット分のデータを保持することができる。

#### 【 0 0 6 5 】

以上が記憶装置 1 5 0 の動作に関する説明である。

#### 【 0 0 6 6 】

このように、本発明の一態様のワード線分割回路は、極めてリーク電流が低減されたトランジスタを適用することにより、ただ一つのトランジスタを用いることで安定してワード線を分割して用いることができる。このような簡略化されたワード線分割回路は、その集積化を阻害するがないため、当該ワード線分割回路を記憶装置に適用することにより、高度に集積化された記憶装置を実現できる。

20

#### 【 0 0 6 7 】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【 0 0 6 8 】

##### ( 実施の形態 2 )

本実施の形態では、実施の形態 1 で示した記憶装置について、より具体的な構成例について図 4 乃至図 7 を用いて説明する。

30

#### 【 0 0 6 9 】

なお、実施の形態 1 で説明した内容と重複する部分については、説明を省略する、若しくは簡略化して説明する。

#### 【 0 0 7 0 】

##### < 構成例 1 >

図 4 は、実施の形態 1 で例示した記憶装置 1 0 0 内のメモリセル 1 1 0 に、DRAM のメモリセルを適用した例である。

#### 【 0 0 7 1 】

図 4 に示す記憶装置 2 0 0 は、複数のメモリセル 2 1 0 を有する。なお、記憶装置 2 0 0 の構成は、メモリセル以外は記憶装置 1 0 0 と同様の構成である。

40

#### 【 0 0 7 2 】

メモリセル 2 1 0 は、選択トランジスタ 2 1 1 と、容量素子 2 1 3 を有する。選択トランジスタ 2 1 1 の第 2 電極は容量素子 2 1 3 の一方の電極に接続され、容量素子 2 1 3 の他方の電極は共通電位が与えられる。本構成例では、選択トランジスタ 2 1 1 は n チャネル型のトランジスタである。ここで、共通電位に代えて、基準電位や接地電位を用いても良い。また、基準電位としてビット線に入力される 2 種類の電位の中間の電位を用いると、容量素子 2 1 3 にかかる電圧を低減でき、容量素子 2 1 3 の絶縁破壊を抑制できるため好ましい。

#### 【 0 0 7 3 】

メモリセル 2 1 0 へのデータの書き込みは、選択トランジスタ 2 1 1 をオン状態とし、

50

当該選択トランジスタ 211 が接続されるビット線に書き込みデータを入力する。このとき、選択トランジスタ 211 を介して容量素子 213 に電荷が蓄積され、書き込みを行うことができる。

**【0074】**

また、データの読み出しへは、選択トランジスタ 211 をオン状態とすることにより、容量素子 213 に保持されていた電荷に応じて、当該選択トランジスタ 211 が接続されるビット線の電位が変動する。この電位の変動を検知することにより、メモリセル 210 に保持されていたデータの読み出しを行うことができる。なお、読み出しを行うと、メモリセル 210 に保持されていたデータは消失する。

**【0075】**

ここで、後の実施の形態で例示するように、トランジスタ 101 は選択トランジスタ 211 及び容量素子 213 に積層して形成することができる。したがって、メモリセル 210 が高度に集積化されたとしても、面積の増大を招くことなくトランジスタ 101 を備えるワード線分割回路を記憶装置に接続することができる。

**【0076】**

このように、ただ一つのトランジスタを用いて構成される本発明の一態様のワード線分割回路は、D R A M に適用することができる。さらに、このような簡略化されたワード線分割回路は、その集積化を阻害することができないため、当該ワード線分割回路を D R A M に適用することにより、高度に集積化された D R A M を実現できる。

**【0077】**

<変形例>

ここで、構成例 1 で例示した記憶装置 200 において、メモリセル 210 内の選択トランジスタ 211 に、上記で例示したリーク電流の極めて低減されたトランジスタを適用することができる。

**【0078】**

図 5 に示す記憶装置 220 は、上記構成例 1 で例示した記憶装置 200 内のメモリセル 210 を、リーク電流の極めて低減された選択トランジスタ 231 を有するメモリセル 230 に置き換えたものである。

**【0079】**

選択トランジスタ 231 は、リーク電流が極めて低減されているため、容量素子 213 に保持された電荷、すなわちメモリセル 230 に書き込まれたデータを極めて長期間保持することができる。したがって、データの再書き込み動作（リフレッシュ動作）を行わない、またはその頻度を極めて低減することができるため、従来の D R A M に比べて消費電力が極めて低減された記憶装置とすることができます。

**【0080】**

また、選択トランジスタ 231 のリーク電流が極めて低いことから、電荷を保持するための容量素子 213 のサイズを小さくすることができる。または、容量素子 213 を設けず、配線間の寄生容量などを保持容量として利用することもできる。そのため、メモリセルサイズを小さくできる。

**【0081】**

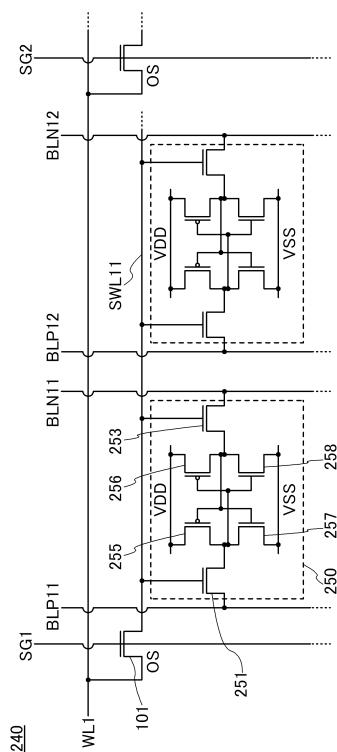

<構成例 2>

図 6 は、実施の形態 1 で例示した記憶装置 100 内のメモリセル 110 に、S R A M のメモリセルを適用した例である。

**【0082】**

図 6 に示す記憶装置 240 は、メモリセルの構成が異なる点、及び各メモリセルに 2 本のビット線が接続される点以外は、実施の形態 1 で例示した記憶装置 100 と同じ構成である。

**【0083】**

メモリセル 250 には、サブワード線 S W L m n と、第 1 ビット線 B L P n 1 と第 2 ビット線 B L N n 1 が接続される。ここで、第 1 ビット線 B L P n 1 と第 2 ビット線 B L N

10

20

30

40

50

$n_1$  にはそれぞれ反転した信号が入力又は出力される。

【0084】

メモリセル 250 は、選択トランジスタ 251、選択トランジスタ 253、並びにトランジスタ 255 乃至 258 の 6 個のトランジスタから構成される。ここで、トランジスタ 255 及び 256 は p チャネル型のトランジスタであり、トランジスタ 257 及び 258 は n チャネル型のトランジスタである。

【0085】

ここで、トランジスタ 255 及び 256 のそれぞれの第 1 電極には電源電位 VDD が、またトランジスタ 257 及びトランジスタ 258 のそれぞれの第 2 電極には基準電位 VSS が入力されている。トランジスタ 255 とトランジスタ 257、及びトランジスタ 256 とトランジスタ 258 がそれぞれインバータ回路を構成し、さらにこの 2 つのインバータ回路が組み合わされてフリップフロップ回路が構成されている。10

【0086】

選択トランジスタ 251 は第 1 電極が第 1 ビット線に接続され、第 2 電極がフリップフロップ回路の一方の入出力部に接続されている。また選択トランジスタ 253 は第 1 電極がフリップフロップ回路の他方の入出力部に接続され、第 2 電極が第 2 ビット線に接続されている。選択トランジスタ 251 及び 253 のそれぞれのゲートは共に、サブワード線に接続されている。

【0087】

メモリセル 250 へのデータの書き込みは、サブワード線を選択状態とすることにより選択トランジスタ 251 及び選択トランジスタ 253 を共にオン状態とし、第 1 ビット線及び第 2 ビット線にそれぞれ反転した書き込みデータを入力する。このとき、選択トランジスタ 251 と、選択トランジスタ 253 を介して、メモリセル 250 内のフリップフロップ回路にデータが保持される。20

【0088】

また、データの読み出しも同様に、サブワード線を選択状態とすることにより選択トランジスタ 251 及び選択トランジスタ 253 を共にオン状態とする。このとき、第 1 ビット線及び第 2 ビット線にそれぞれ反転したデータが出力され、これらの電位が変動する。この電位の変動を検知することにより、メモリセル 250 に保持されているデータの読み出しを行うことができる。30

【0089】

このように、ただ一つのトランジスタを用いて構成される本発明の一態様のワード線分割回路は、SRAM に適用することができる。さらに、このような簡略化されたワード線分割回路を有する SRAM は、回路面積の小さな SRAM とすることができます。

【0090】

<構成例 3>

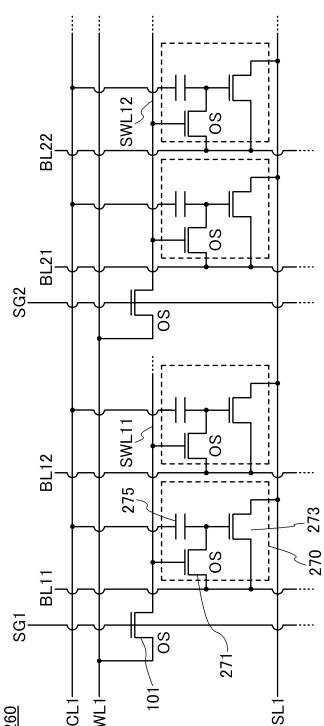

本構成例では、上記構成例とは異なる形態の記憶装置について説明する。

【0091】

図 7 に示す記憶装置 260 は、メモリセルの構成が異なる点、また m 本の容量線 CLm 及び m 本のソース線 SLm を有する点以外は実施の形態 1 で例示した記憶装置 100 と同様の構成である。40

【0092】

メモリセル 270 は、リーク電流が極めて低減された選択トランジスタ 271 と、トランジスタ 273 と容量素子 275 を有する。本構成例では選択トランジスタ 271 及びトランジスタ 273 はそれぞれ n チャネル型のトランジスタである。

【0093】

選択トランジスタ 271 は、ゲートがサブワード線に接続され、第 1 電極がビット線に接続され、第 2 電極がトランジスタ 273 のゲート、及び容量素子 275 の一方の電極に接続される。トランジスタ 273 は、第 1 電極がビット線に接続され、第 2 電極がソース線に接続される。容量素子 275 の他方の電極は容量線に接続される。ここで、選択トラ50

ンジスタ 271 の第 2 電極、容量素子 275 の一方の電極、及びトランジスタ 273 のゲートに接続されるノード（以下、保持ノードともいう）に電位が保持されることによりデータを記憶することができる。

#### 【 0094 】

メモリセル 270 へのデータの書き込みは、サブワード線を選択状態とすることにより選択トランジスタ 271 をオン状態とし、ビット線に書き込みデータを入力する。このとき、選択トランジスタ 271 を介して容量素子 275 に電荷が蓄積され、書き込みを行うことができる。

#### 【 0095 】

また、データの読み出しへは、一本の容量線に接続される全てのメモリセルについて行われる。全てのサブワード線を非選択状態とし、読み出しを行うメモリセル 270 が接続されたソース線にハイレベル電位を与える。ここで、容量線に与える負の電位は、保持ノードに保持されている電位によらず、容量素子 275 を介して容量結合によりトランジスタ 273 のゲートに入力され、当該トランジスタ 273 をオフ状態とする電位である。したがって、読み出しを行わないメモリセル 270 内のトランジスタ 273 は全てオフ状態となる。

#### 【 0096 】

このとき、読み出しを行うメモリセル 270 の保持ノードにハイレベル電位が保持されていると、トランジスタ 273 はオン状態となるため、ビット線にはトランジスタ 273 を介してソース線に与えられるハイレベル電位が出力される。一方、当該保持ノードにローレベル電位が保持されていると、トランジスタ 273 はオフ状態を維持するため、ビット線の電位は変動しない。したがって、このビット線の電位の変動の有無を検知することにより、メモリセル 270 に保持されたデータを読み出すことができる。

#### 【 0097 】

ここで、選択トランジスタ 271 として、リーク電流が極めて低減されたトランジスタを適用する。したがって、保持ノードに保持された電荷が、選択トランジスタ 271 を介して抜けてしまうことが極めて抑制されるため、データの保持期間を極めて長くすることができる。このようなリーク電流が極めて低減された選択トランジスタが適用された記憶装置 260 は、実質的に不揮発性の記憶装置として用いることができる。

#### 【 0098 】

なお、本構成例ではトランジスタ 273 に n チャネル型のトランジスタを適用したが、 p チャネル型のトランジスタとしてもよい。その場合、負の電位を用いない記憶装置の構成とすることができます、装置が簡略化できるため好ましい。

#### 【 0099 】

また、本構成例では、ソース線を一行につき一つ配置する構成としたいが、ソース線は複数の行に共通して用いてもよい。また、ソース線は列方向に配置してもよく、複数の列に共通して用いても良い。

#### 【 0100 】

このように、ただ一つのトランジスタを用いて構成される本発明の一態様のワード線分割回路は、選択トランジスタを有する不揮発性の記憶装置に適用することができる。さらに、このような簡略化され、安定して動作可能なワード線分割回路が適用されることにより、安定して動作可能で回路面積の小さな記憶装置を実現できる。

#### 【 0101 】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【 0102 】

##### ( 実施の形態 3 )

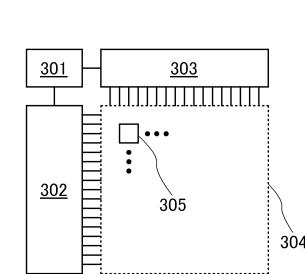

本実施の形態では、本発明の一態様のワード線分割回路が適用された記憶装置の構成例について、図 8 を用いて説明する。

10

20

30

40

50

**【0103】**

図8は、本実施の形態で例示する記憶装置300の構成例を示すプロック図である。

**【0104】**

記憶装置300は、制御回路301、駆動回路302、駆動回路303、及びメモリセルアレイ304を有する。

**【0105】**

制御回路301には、書き込み制御信号、読み出し制御信号、及びアドレス信号が入力される。制御回路301は、入力される各信号に応じて、複数の制御信号を生成して出力する機能を有する。例えば、制御回路301は、入力されるアドレス信号に応じて行アドレス信号及び列アドレス信号を出力する機能を有する。

10

**【0106】**

駆動回路302には、行アドレス信号が入力される。駆動回路302は、入力された行アドレス信号に従って行方向に設けられた配線（例えば上記実施の形態におけるワード線、容量線、ソース線など）を選択し、選択した配線の電圧を設定する機能を有する。駆動回路302は、例えば第1のデコーダを備える。第1のデコーダは、入力された行アドレス信号に従って行方向に設けられた配線を選択する機能を有する。

**【0107】**

駆動回路303には、データ信号及び列アドレス信号が入力される。駆動回路303は、列方向に設けられた配線（例えば上記実施の形態におけるビット線、選択信号線など）を選択し、選択した配線の電圧を設定する機能を有する。駆動回路303は、例えば第2のデコーダ及び複数のアナログスイッチを備える。第2のデコーダは、列方向に設けられた配線を選択する機能を有し、複数のアナログスイッチは、第2のデコーダから入力される信号に応じてデータ信号を出力するか否かを制御する機能を有する。なお、駆動回路303に読み出し回路を設けても良い。読み出し回路は、選択した配線に接続されたメモリセル305に記憶されたデータを読み出す機能を有する。

20

**【0108】**

メモリセルアレイ304は、マトリクス状に配置された複数のメモリセル305から構成される。メモリセル305の構成としては、上記実施の形態で例示したメモリセルを適用できる。メモリセル305は、駆動回路302及び駆動回路303により選択され、選択されたメモリセル305では、データの書き込み又は読み出しが行われる。

30

**【0109】**

図8に示す記憶装置300は、制御回路に入力される信号に従って駆動回路によりメモリセルを選択し、書き込み動作又は読み出し動作を行う。

**【0110】**

本実施の形態で例示した記憶装置300には、本発明の一態様のワード線分割回路が適用されている。従って、回路構成が簡略化され、且つランダムアクセス時のサイクルタイムが低減された記憶装置とすることができます。

**【0111】**

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

40

**【0112】****(実施の形態4)**

本実施の形態では、上記実施の形態に示す記憶装置に適用可能な酸化物半導体層を含むトランジスタの例について説明する。

**【0113】**

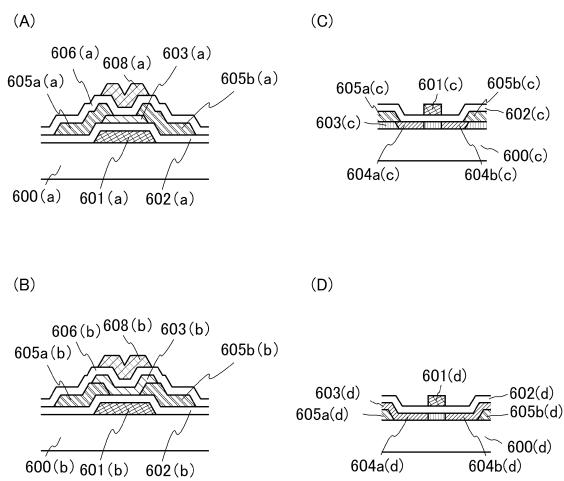

上記酸化物半導体層を含むトランジスタの構造例について、図9を用いて説明する。図9は、本実施の形態におけるトランジスタの構造例を示す断面模式図である。

**【0114】**

図9(A)に示すトランジスタは、導電層601(a)と、絶縁層602(a)と、半導体層603(a)と、導電層605a(a)と、導電層605b(a)と、絶縁層60

50

6 ( a ) と、導電層 6 0 8 ( a ) と、を含む。

【 0 1 1 5 】

導電層 6 0 1 ( a ) は、被素子形成層 6 0 0 ( a ) の上に設けられる。

【 0 1 1 6 】

絶縁層 6 0 2 ( a ) は、導電層 6 0 1 ( a ) の上に設けられる。

【 0 1 1 7 】

半導体層 6 0 3 ( a ) は、絶縁層 6 0 2 ( a ) を介して導電層 6 0 1 ( a ) に重畠する。

【 0 1 1 8 】

導電層 6 0 5 a ( a ) 及び導電層 6 0 5 b ( a ) のそれぞれは、半導体層 6 0 3 ( a ) 10 の上に設けられ、半導体層 6 0 3 ( a ) に電気的に接続される。

【 0 1 1 9 】

絶縁層 6 0 6 ( a ) は、半導体層 6 0 3 ( a ) 、導電層 6 0 5 a ( a ) 、及び導電層 6 0 5 b ( a ) の上に設けられる。

【 0 1 2 0 】

導電層 6 0 8 ( a ) は、絶縁層 6 0 6 ( a ) を介して半導体層 6 0 3 ( a ) に重畠する。

【 0 1 2 1 】

なお、必ずしも導電層 6 0 1 ( a ) 及び導電層 6 0 8 ( a ) の一方を設けなくてもよい。また、導電層 6 0 8 ( a ) を設けない場合には、絶縁層 6 0 6 ( a ) を設けなくてもよい。 20

【 0 1 2 2 】

図 9 ( B ) に示すトランジスタは、導電層 6 0 1 ( b ) と、絶縁層 6 0 2 ( b ) と、半導体層 6 0 3 ( b ) と、導電層 6 0 5 a ( b ) と、導電層 6 0 5 b ( b ) と、絶縁層 6 0 6 ( b ) と、導電層 6 0 8 ( b ) と、を含む。

【 0 1 2 3 】

導電層 6 0 1 ( b ) は、被素子形成層 6 0 0 ( b ) の上に設けられる。

【 0 1 2 4 】

絶縁層 6 0 2 ( b ) は、導電層 6 0 1 ( b ) の上に設けられる。

【 0 1 2 5 】

導電層 6 0 5 a ( b ) 及び導電層 6 0 5 b ( b ) のそれぞれは、絶縁層 6 0 2 ( b ) の一部の上に設けられる。 30

【 0 1 2 6 】

半導体層 6 0 3 ( b ) は、導電層 6 0 5 a ( b ) 及び導電層 6 0 5 b ( b ) の上に設けられ、導電層 6 0 5 a ( b ) 及び導電層 6 0 5 b ( b ) に電気的に接続される。また、半導体層 6 0 3 ( b ) は、絶縁層 6 0 2 ( b ) を介して導電層 6 0 1 ( b ) に重畠する。

【 0 1 2 7 】

絶縁層 6 0 6 ( b ) は、半導体層 6 0 3 ( b ) 、導電層 6 0 5 a ( b ) 、及び導電層 6 0 5 b ( b ) の上に設けられる。

【 0 1 2 8 】

導電層 6 0 8 ( b ) は、絶縁層 6 0 6 ( b ) を介して半導体層 6 0 3 ( b ) に重畠する。

【 0 1 2 9 】

なお、必ずしも導電層 6 0 1 ( b ) 及び導電層 6 0 8 ( b ) の一方を設けなくてもよい。導電層 6 0 8 ( b ) を設けない場合には、絶縁層 6 0 6 ( b ) を設けなくてもよい。

【 0 1 3 0 】

図 9 ( C ) に示すトランジスタは、導電層 6 0 1 ( c ) と、絶縁層 6 0 2 ( c ) と、半導体層 6 0 3 ( c ) と、導電層 6 0 5 a ( c ) と、導電層 6 0 5 b ( c ) と、を含む。

【 0 1 3 1 】

半導体層 6 0 3 ( c ) は、領域 6 0 4 a ( c ) 及び領域 6 0 4 b ( c ) を含む。領域 6

50

04a(c)及び領域604b(c)は、互いに離間し、それぞれドーパントが添加された領域である。なお、領域604a(c)及び領域604b(c)の間の領域がチャネル形成領域になる。半導体層603(c)は、被素子形成層600(c)の上に設けられる。なお、必ずしも領域604a(c)及び領域604b(c)を設けなくてもよい。

#### 【0132】

導電層605a(c)及び導電層605b(c)は、半導体層603(c)の上に設けられ、半導体層603(c)に電気的に接続される。また、導電層605a(c)及び導電層605b(c)は、テーパ状である。

#### 【0133】

また、導電層605a(c)は、領域604a(c)の一部に重畳するが、必ずしもこれに限定されない。導電層605a(c)を領域604a(c)の一部に重畳させることにより、導電層605a(c)及び領域604a(c)の間の抵抗値を小さくすることができる。また、導電層605a(c)に重畳する半導体層603(c)の領域の全てが領域604a(c)でもよい。10

#### 【0134】

また、導電層605b(c)は、領域604b(c)の一部に重畳するが、必ずしもこれに限定されない。導電層605b(c)を領域604b(c)の一部に重畳させることにより、導電層605b(c)及び領域604b(c)の間の抵抗を小さくすることができる。また、導電層605b(c)に重畳する半導体層603(c)の領域の全てが領域604b(c)でもよい。20

#### 【0135】

絶縁層602(c)は、半導体層603(c)、導電層605a(c)、及び導電層605b(c)の上に設けられる。

#### 【0136】

導電層601(c)は、絶縁層602(c)を介して半導体層603(c)に重畳する。絶縁層602(c)を介して導電層601(c)と重畳する半導体層603(c)の領域がチャネル形成領域になる。

#### 【0137】

また、図9(D)に示すトランジスタは、導電層601(d)と、絶縁層602(d)と、半導体層603(d)と、導電層605a(d)と、導電層605b(d)と、を含む。30

#### 【0138】

導電層605a(d)及び導電層605b(d)は、被素子形成層600(d)の上に設けられる。また、導電層605a(d)及び導電層605b(d)は、テーパ状である。

#### 【0139】

半導体層603(d)は、領域604a(d)及び領域604b(d)と、を含む。領域604a(d)及び領域604b(d)は、互いに離間し、それぞれドーパントが添加された領域である。また、領域604a(d)及び領域604b(d)の間の領域がチャネル形成領域になる。半導体層603(d)は、例えば導電層605a(d)、導電層605b(d)、及び被素子形成層600(d)の上に設けられ、導電層605a(d)及び導電層605b(d)に電気的に接続される。なお、必ずしも領域604a(d)及び領域604b(d)を設けなくてもよい。40

#### 【0140】

領域604a(d)は、導電層605a(d)に電気的に接続される。

#### 【0141】

領域604b(d)は、導電層605b(d)に電気的に接続される。

#### 【0142】

絶縁層602(d)は、半導体層603(d)の上に設けられる。

#### 【0143】

10

20

30

40

50

導電層 601 (d) は、絶縁層 602 (d) を介して半導体層 603 (d) に重畠する。絶縁層 602 (d) を介して導電層 601 (d) と重畠する半導体層 603 (d) の領域がチャネル形成領域になる。

#### 【0144】

以下では、図 9 (A) 乃至図 9 (D) に示す各構成要素について説明する。

#### 【0145】

被素子形成層 600 (a) 乃至被素子形成層 600 (d) としては、例えば絶縁層、又は絶縁表面を有する基板などを用いることができる。また、予め素子が形成された層を被素子形成層 600 (a) 乃至被素子形成層 600 (d) として用いることもできる。

#### 【0146】

導電層 601 (a) 乃至導電層 601 (d) のそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタのゲートとしての機能を有する層をゲート電極又はゲート配線ともいう。

#### 【0147】

導電層 601 (a) 乃至導電層 601 (d) としては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層 601 (a) 乃至導電層 601 (d) の形成に適用可能な材料の層の積層により、導電層 601 (a) 乃至導電層 601 (d) を構成することもできる。

#### 【0148】

絶縁層 602 (a) 乃至絶縁層 602 (d) のそれぞれは、トランジスタのゲート絶縁層としての機能を有する。

#### 【0149】

絶縁層 602 (a) 乃至絶縁層 602 (d) としては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ハフニウム層、又は酸化ランタン層を用いることができる。

#### 【0150】

また、絶縁層 602 (a) 乃至絶縁層 602 (d) としては、例えば元素周期表における第 13 族元素及び酸素元素を含む材料の絶縁層を用いることができる。例えば、半導体層 603 (a) 乃至半導体層 603 (d) が第 13 族元素を含む場合に、半導体層 603 (a) 乃至半導体層 603 (d) に接する絶縁層として第 13 族元素を含む絶縁層を用いることにより、該絶縁層と半導体層との界面の状態を良好にすることができる。

#### 【0151】

第 13 族元素及び酸素元素を含む材料としては、例えば酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどが挙げられる。なお、酸化アルミニウムガリウムとは、ガリウムの含有量（原子%）よりアルミニウムの含有量（原子%）が多い物質のことをいい、酸化ガリウムアルミニウムとは、ガリウムの含有量（原子%）がアルミニウムの含有量（原子%）以上の物質のことをいう。例えば、 $A_{1-x}O_x$  ( $x = 3 +$  、  $x$  は 0 より大きく 1 より小さい値)、 $Ga_{2-x}O_x$  ( $x = 3 +$  、  $x$  は 0 より大きく 1 より小さい値)、又は  $Ga_xAl_{2-x}O_{3+x}$  ( $x$  は 0 より大きく 2 より小さい値、  $x$  は 0 より大きく 1 より小さい値) で表記される材料を用いることができる。

#### 【0152】

また、絶縁層 602 (a) 乃至絶縁層 602 (d) に適用可能な材料の層の積層により絶縁層 602 (a) 乃至絶縁層 602 (d) を構成することもできる。例えば、複数の  $Ga_2O_x$  で表記される酸化ガリウムを含む層の積層により絶縁層 602 (a) 乃至絶縁層 602 (d) を構成してもよい。また、 $Ga_2O_x$  で表記される酸化ガリウムを含む絶縁層及び  $Al_2O_x$  で表記される酸化アルミニウムを含む絶縁層の積層により絶縁層 602 (a) 乃至絶縁層 602 (d) を構成してもよい。

#### 【0153】

10

20

30

40

50

半導体層 603 (a) 乃至半導体層 603 (d) のそれぞれは、トランジスタのチャネルが形成される層としての機能を有する。半導体層 603 (a) 乃至半導体層 603 (d) に適用可能な酸化物半導体としては、例えば四元系金属の酸化物、三元系金属の酸化物、又は二元系金属の酸化物などを含む金属酸化物を用いることができる。

#### 【0154】

用いる酸化物半導体としては、少なくともインジウム (In) あるいは亜鉛 (Zn) を含むことが好ましい。特に In と Zn を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム (Ga) を有することが好ましい。また、スタビライザーとしてスズ (Sn) を有することが好ましい。また、スタビライザーとしてハフニウム (Hf) を有することが好ましい。また、スタビライザーとしてアルミニウム (Al) を有することが好ましい。10

#### 【0155】

また、他のスタビライザーとして、ランタノイドである、ラントン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) のいずれか一種あるいは複数種を有してもよい。

#### 【0156】

四元系金属の酸化物としては、例えば In - Sn - Ga - Zn - O 系金属酸化物、In - Sn - Al - Zn - O 系金属酸化物、In - Sn - Hf - Zn - O 系金属酸化物、または In - Hf - Al - Zn - O 系金属酸化物などを用いることができる。20

#### 【0157】

三元系金属の酸化物としては、例えば In - Ga - Zn - O 系金属酸化物、In - Sn - Zn - O 系金属酸化物、In - Al - Zn - O 系金属酸化物、Sn - Ga - Zn - O 系金属酸化物、Al - Ga - Zn - O 系金属酸化物、Sn - Al - Zn - O 系金属酸化物、In - Hf - Zn - O 系金属酸化物、In - La - Zn - O 系金属酸化物、In - Ce - Zn - O 系金属酸化物、In - Pr - Zn - O 系金属酸化物、In - Nd - Zn - O 系金属酸化物、In - Pm - Zn - O 系金属酸化物、In - Sm - Zn - O 系金属酸化物、In - Eu - Zn - O 系金属酸化物、In - Gd - Zn - O 系金属酸化物、In - Tb - Zn - O 系金属酸化物、In - Dy - Zn - O 系金属酸化物、In - Ho - Zn - O 系金属酸化物、In - Er - Zn - O 系金属酸化物、In - Tm - Zn - O 系金属酸化物、In - Yb - Zn - O 系金属酸化物、又はIn - Lu - Zn - O 系金属酸化物などを用いることができる。30

#### 【0158】

二元系金属の酸化物としては、例えば In - Zn - O 系金属酸化物、Sn - Zn - O 系金属酸化物、Al - Zn - O 系金属酸化物、Zn - Mg - O 系金属酸化物、Sn - Mg - O 系金属酸化物、In - Mg - O 系金属酸化物、In - Sn - O 系金属酸化物、又は In - Ga - O 系金属酸化物などを用いることができる。

#### 【0159】

また、酸化物半導体としては、例えば In - O 系金属酸化物、Sn - O 系金属酸化物、又は Zn - O 系金属酸化物などを用いることもできる。また、上記酸化物半導体として適用可能な金属酸化物は、酸化シリコンを含んでいてもよい。

#### 【0160】

半導体層には、例えば、In : Ga : Zn = 1 : 1 : 1 あるいは In : Ga : Zn = 2 : 2 : 1 の原子比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In : Sn : Zn = 1 : 1 : 1、In : Sn : Zn = 2 : 1 : 3 あるいは In : Sn : Zn = 2 : 1 : 5 の原子比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0161】

50

20

30

40

50

しかし、これらに限らず、必要とする半導体特性（移動度、しきい値、ばらつき等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

#### 【0162】

また、酸化物半導体としては、 $InLO_3 (ZnO)_m$  ( $m$ は0より大きく、且つ整数でない。)で表記される材料を用いることもできる。 $InLO_3 (ZnO)_m$ のLは、Ga、Al、Mn、及びCoから選ばれた一つ又は複数の金属元素を示す。

#### 【0163】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

#### 【0164】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるので、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

#### 【0165】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができます。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することができる。具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

#### 【0166】

また、半導体層603(a)乃至半導体層603(d)の少なくともチャネルが形成される領域は、結晶性を有し、非単結晶であって、ab面に垂直な方向から見て、三角形、六角形、正三角形、又は正六角形の原子配列を有し、且つ、c軸方向に金属原子が層状に配列した相、又はc軸方向に金属原子と酸素原子が層状に配列した相を有してもよい。上記相を有する材料をCAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)ともいう。

#### 【0167】

また、結晶性を有する酸化物半導体を用いたトランジスタは、トランジスタのストレス劣化(ゲートバイアスストレスなどによる劣化)や、可視光や紫外光の照射によるトランジスタの電気的特性変化が抑制され、信頼性の高いトランジスタとすることができます。

#### 【0168】

また、トランジスタのチャネル長を30nmとしたとき、半導体層603(a)乃至半導体層603(d)の厚さを例えば5nm程度にしてもよい。このとき、半導体層603(a)乃至半導体層603(d)がCAAC-OSである酸化物半導体層であれば、トランジスタにおける短チャネル効果を抑制することができる。

#### 【0169】

なお、CAAC-OSについては、実施の形態6で詳細に説明する。

#### 【0170】

領域604a(c)、領域604b(c)、領域604a(d)、及び領域604b(d)は、n型又はp型の導電性を付与するドーパントが添加され、トランジスタのソース又はドレインとしての機能を有する。ドーパントとしては、例えば元素周期表における13族の元素(例えば硼素など)、又は、元素周期表における15族の元素(例えば窒素、リン、又は砒素など)などを用いることができる。なお、トランジスタのソースとしての機能を有する領域をソース領域ともいい、トランジスタのドレインとしての機能を有する領域をドレイン領域ともいう。領域604a(c)、領域604b(c)、領域604a(d)、及び領域604b(d)にドーパントを添加することにより導電層との接触抵抗を小さくすることができるため、トランジスタを微細化することができる。

10

20

30

40

50

## 【0171】

導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) のそれぞれは、トランジスタのソース又はドレインとしての機能を有する。なお、トランジスタのソースとしての機能を有する層をソース電極又はソース配線ともいい、トランジスタのドレインとしての機能を有する層をドレイン電極又はドレイン配線ともいう。

## 【0172】

導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) としては、例えばアルミニウム、マグネシウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタンゲステンなどの金属材料、又はこれらの金属材料を主成分とする合金材料の層を用いることができる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層により、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) を構成することができる。また、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) に適用可能な材料の層の積層により、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) を構成することもできる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層と銅を含む層の積層により、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) を構成することができる。

## 【0173】

また、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) としては、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例えば酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、又は酸化インジウム酸化亜鉛を用いることができる。なお、導電層 605a (a) 乃至導電層 605a (d)、及び導電層 605b (a) 乃至導電層 605b (d) に適用可能な導電性の金属酸化物は、酸化シリコンを含んでいてもよい。

## 【0174】

絶縁層 606 (a) 及び絶縁層 606 (b) としては、絶縁層 602 (a) 乃至絶縁層 602 (d) に適用可能な材料の層を用いることができる。また、絶縁層 606 (a) 及び絶縁層 606 (b) に適用可能な材料の積層により、絶縁層 606 (a) 及び絶縁層 606 (b) を構成してもよい。例えば、酸化シリコン層、酸化アルミニウム層などにより絶縁層 606 (a) 及び絶縁層 606 (b) を構成してもよい。例えば、酸化アルミニウム層を用いることにより、半導体層 603 (a) 及び半導体層 603 (b) への不純物の侵入抑制効果をより高めることができ、また、半導体層 603 (a) 及び半導体層 603 (b) 中の酸素の脱離抑制効果を高めることができる。

## 【0175】

導電層 608 (a) 及び導電層 608 (b) のそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタが導電層 601 (a) 及び導電層 608 (a) の両方、又は導電層 601 (b) 及び導電層 608 (b) の両方を含む構造である場合、導電層 601 (a) 及び導電層 608 (a) の一方、又は導電層 601 (b) 及び導電層 608 (b) の一方を、バックゲート、バックゲート電極、又はバックゲート配線ともいう。ゲートとしての機能を有する導電層を、チャネル形成層を介して複数設けることにより、トランジスタの閾値電圧を制御しやすくすることができる。

## 【0176】

導電層 608 (a) 及び導電層 608 (b) としては、例えば導電層 601 (a) 乃至導電層 601 (d) に適用可能な材料の層を用いることができる。また、導電層 608 (a) 及び導電層 608 (b) に適用可能な材料の層の積層により導電層 608 (a) 及び導電層 608 (b) を構成してもよい。

## 【0177】

なお、本実施の形態のトランジスタを、チャネル形成層としての機能を有する半導体層

10

20

30

40

50

の一部の上に絶縁層を含み、該絶縁層を介して半導体層に重畠するように、ソース又はドレインとしての機能を有する導電層を含む構造としてもよい。上記構造である場合、絶縁層は、トランジスタのチャネル形成層を保護する層（チャネル保護層ともいう）としての機能を有する。チャネル保護層としての機能を有する絶縁層としては、例えば絶縁層 602(a)乃至絶縁層 602(d)に適用可能な材料の層を用いることができる。また、絶縁層 602(a)乃至絶縁層 602(d)に適用可能な材料の積層によりチャネル保護層としての機能を有する絶縁層を構成してもよい。

#### 【0178】

また、被素子形成層 600(a)乃至被素子形成層 600(d)の上に下地層を形成し、該下地層の上にトランジスタを形成してもよい。このとき、下地層としては、例えば絶縁層 602(a)乃至絶縁層 602(d)に適用可能な材料の層を用いることができる。また、絶縁層 602(a)乃至絶縁層 602(d)に適用可能な材料の積層により下地層を構成してもよい。例えば、酸化アルミニウム層及び酸化シリコン層の積層により下地層を構成することにより、下地層に含まれる酸素が半導体層 603(a)乃至半導体層 603(d)を介して脱離するのを抑制することができる。

#### 【0179】

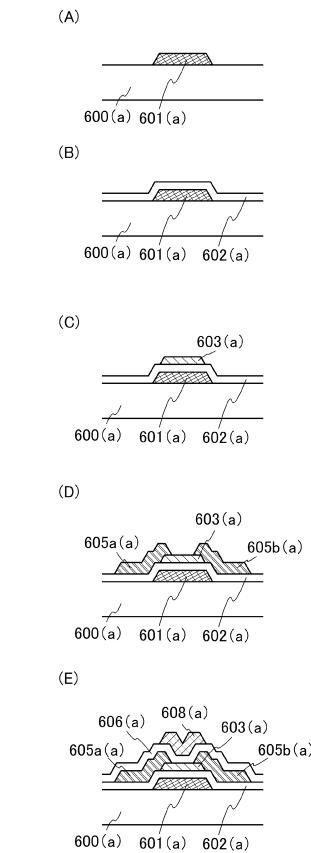

続いて、以下では本実施の形態におけるトランジスタの作製方法例として、図 9(A)に示すトランジスタの作製方法例について、図 10 を用いて説明する。図 10 は、図 9(A)に示すトランジスタの作製方法例を説明するための断面模式図である。

#### 【0180】

まず、図 10(A)に示すように、被素子形成層 600(a)を準備し、被素子形成層 600(a)の上に第 1 の導電膜を形成し、第 1 の導電膜の一部をエッティングすることにより導電層 601(a)を形成する。

#### 【0181】

例えば、スパッタリング法を用いて導電層 601(a)に適用可能な材料の膜を形成することにより第 1 の導電膜を形成することができる。また、導電層 601(a)に適用可能な材料の膜を積層させ、第 1 の導電膜を形成することもできる。

#### 【0182】

なお、スパッタリングガスとして、例えば水素、水、水酸基、又は水素化物などの不純物が除去された高純度ガスを用いることにより、形成される膜の上記不純物濃度を低減することができる。

#### 【0183】

なお、スパッタリング法を用いて膜を形成する前に、スパッタリング装置の予備加熱室において予備加熱処理を行ってもよい。上記予備加熱処理を行うことにより、水素、水分などの不純物を脱離することができる。

#### 【0184】

また、スパッタリング法を用いて膜を形成する前に、例えばアルゴン、窒素、ヘリウム、又は酸素雰囲気下で、ターゲット側に電圧を印加せずに、基板側に R F 電源を用いて電圧を印加し、プラズマを形成して被形成面を改質する処理（逆スパッタともいう）を行ってもよい。逆スパッタを行うことにより、被形成面に付着している粉状物質（パーティクル、ごみともいう）を除去することができる。

#### 【0185】

また、スパッタリング法を用いて膜を形成する場合、吸着型の真空ポンプなどを用いて、膜を形成する成膜室内の残留水分を除去することができる。吸着型の真空ポンプとしては、例えばクライオポンプ、イオンポンプ、又はチタンサブリメーションポンプなどを用いることができる。また、コールドトラップを設けたターボ分子ポンプを用いて成膜室内の残留水分を除去することもできる。上記真空ポンプを用いることにより、不純物を含む排気の逆流を低減することができる。

#### 【0186】

また、上記導電層 601(a)の形成方法のように、本実施の形態におけるトランジス

10

20

30

40

50

タの作製方法例において、膜の一部をエッティングして層を形成する場合、例えば、フォトリソグラフィ工程により膜の一部の上にレジストマスクを形成し、レジストマスクを用いて膜をエッティングすることにより、層を形成することができる。なお、この場合、層の形成後にレジストマスクを除去する。

#### 【0187】

また、インクジェット法を用いてレジストマスクを形成してもよい。インクジェット法を用いることにより、フォトマスクが不要になるため、製造コストを低減することができる。また、透過率の異なる複数の領域を有する露光マスク（多階調マスクともいう）を用いてレジストマスクを形成してもよい。多階調マスクを用いることにより、異なる厚さの領域を有するレジストマスクを形成することができ、トランジスタの作製に使用するレジストマスクの数を低減することができる。10

#### 【0188】

次に、図10(B)に示すように、導電層601(a)の上に第1の絶縁膜を形成することにより絶縁層602(a)を形成する。

#### 【0189】

例えば、スパッタリング法やプラズマCVD法などを用いて絶縁層602(a)に適用可能な材料の膜を形成することにより第1の絶縁膜を形成することができる。また、絶縁層602(a)に適用可能な材料の膜を積層させることにより第1の絶縁膜を形成することもできる。また、高密度プラズマCVD法（例えばμ波（例えば、周波数2.45GHzのμ波）を用いた高密度プラズマCVD法）を用いて絶縁層602(a)に適用可能な材料の膜を形成することにより、絶縁層602(a)を緻密にすることができ、絶縁層602(a)の絶縁耐圧を向上させることができる。20

#### 【0190】

次に、図10(C)に示すように、絶縁層602(a)の上に酸化物半導体膜を形成し、その後酸化物半導体膜の一部をエッティングすることにより半導体層603(a)を形成する。

#### 【0191】

例えば、スパッタリング法を用いて半導体層603(a)に適用可能な酸化物半導体材料の膜を形成することにより酸化物半導体膜を形成することができる。なお、希ガス雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で酸化物半導体膜を形成してもよい。また、半導体層603(a)としてCAC-O<sub>S</sub>である酸化物半導体層を形成する場合、スパッタリング法を用い、酸化物半導体膜が形成される被素子形成層の温度を100以上500以下、好ましくは200以上350以下にして酸化物半導体膜を形成する。このとき、スパッタリング装置内の水素又は水などの不純物の濃度が極めて低いことが好ましい。例えば、酸化物半導体膜の形成前に熱処理を行うことにより、スパッタリング装置内の水素又は水などの不純物の濃度を低くすることができる。また、このとき、絶縁層602(a)は平坦であることが好ましい。例えば、絶縁層602(a)の平均面粗さは、0.5nm未満、さらには0.1nm以下であることが好ましい。30

#### 【0192】

また、スパッタリングターゲットとして、例えば、In : Zn = 50 : 1乃至In : Zn = 1 : 2（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 25 : 1乃至In<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 4）、好ましくはIn : Zn = 20 : 1乃至In : Zn = 1 : 1（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 10 : 1乃至In<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 2）、さらに好ましくはIn : Zn = 15 : 1乃至In : Zn = 1.5 : 1（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 15 : 2乃至In<sub>2</sub>O<sub>3</sub> : ZnO = 3 : 4）の組成比である酸化物ターゲットを用いて酸化物半導体膜を形成することができる。例えば、In-Zn-O系酸化物半導体の形成に用いるターゲットは、原子数比がIn : Zn : O = S : U : Rのとき、R > 1.5S + Uとする。Inの量を多くすることにより、トランジスタの移動度を向上させることができるとする。40

#### 【0193】

50

また、In - Sn - Zn - O系金属酸化物の材料膜をスパッタリング法によって形成する場合に用いる酸化物半導体のターゲットの組成比は、In : Sn : Znが原子数比で、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、或いは20 : 45 : 35などを用いることができる。

#### 【0194】

また、In - Ga - Zn - O系金属酸化物の材料膜をスパッタリング法によって形成する場合に用いる酸化物半導体のターゲットの組成比は、In : Ga : Znが原子数比で、1 : 1 : 0.5、1 : 1 : 1、或いは1 : 1 : 2などを用いることができる。

#### 【0195】

また、スパッタリング法を用いる場合、例えば、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で半導体層603(a)を形成する。このとき、希ガスと酸素の混合雰囲気下で半導体層603(a)を形成する場合には、希ガスの量に対して酸素の量が多い方が好ましい。10

#### 【0196】

次に、図10(D)に示すように、絶縁層602(a)及び半導体層603(a)の上に第2の導電膜を形成し、第2の導電膜の一部をエッチングすることにより導電層605a(a)及び導電層605b(a)を形成する。

#### 【0197】

例えば、スパッタリング法などを用いて導電層605a(a)及び導電層605b(a)に適用可能な材料の膜を形成することにより第2の導電膜を形成することができる。また、導電層605a(a)及び導電層605b(a)に適用可能な材料の膜を積層させることにより第2の導電膜を形成することもできる。20

#### 【0198】

次に、図10(E)に示すように、半導体層603(a)に接するように絶縁層606(a)を形成する。

#### 【0199】

例えば、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で、スパッタリング法を用いて絶縁層606(a)に適用可能な膜を形成することにより、絶縁層606(a)を形成することができる。スパッタリング法を用いて絶縁層606(a)を形成することにより、トランジスタのバックチャネルとしての機能を有する半導体層603(a)の部分における抵抗の低下を抑制することができる。また、絶縁層606(a)を形成する際の基板温度は、室温以上300以下であることが好ましい。30

#### 【0200】

また、絶縁層606(a)を形成する前にN<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行い、露出している半導体層603(a)の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、その後、大気に触れることなく、絶縁層606(a)を形成することが好ましい。

#### 【0201】

さらに、図9(A)に示すトランジスタの作製方法の一例では、例えば600以上750以下、又は600以上基板の歪み点未満の温度で加熱処理を行う。例えば、酸化物半導体膜を形成した後、酸化物半導体膜の一部をエッチングした後、第2の導電膜を形成した後、第2の導電膜の一部をエッチングした後、又は絶縁層606(a)を形成した後に上記加熱処理を行う。40

#### 【0202】

なお、上記加熱処理を行う加熱処理装置としては、電気炉、又は抵抗発熱体などの発熱体からの熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えばGRTA(Gas Rapid Thermal Annealing)装置又はLRTA(Lamp Rapid Thermal Annealing)装置などのRTA(Rapid Thermal Annealing)装置を用いることができる。LRTA50

装置は、例えばハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、又は高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。また、G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスとしては、例えば希ガス、又は加熱処理によって被処理物と反応しない不活性気体(例えば窒素)を用いることができる。

#### 【0203】

また、上記加熱処理を行った後、該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-60以下、好ましくは-60以下の雰囲気)を導入してもよい。このとき、酸素ガス又はN<sub>2</sub>Oガスは、水、水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又はN<sub>2</sub>Oガスの純度を、6N以上、好ましくは7N以上、すなわち、酸素ガス又はN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、半導体層603(a)に酸素が供給され、半導体層603(a)中の酸素欠陥に起因する欠陥を低減することができる。なお、上記高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エアの導入は、上記加熱処理時に行ってもよい。

10

#### 【0204】

また、絶縁層602(a)形成後、酸化物半導体膜形成後、ソース電極又はドレイン電極となる導電層形成後、ソース電極又はドレイン電極となる導電層の上の絶縁層形成後、又は加熱処理後に酸素プラズマによる酸素ドーピング処理を行ってもよい。例えば2.45GHzの高密度プラズマにより酸素ドーピング処理を行ってもよい。また、イオン注入法を用いて酸素ドーピング処理を行ってもよい。酸素ドーピング処理を行うことにより、作製されるトランジスタの電気特性のばらつきを低減することができる。例えば、酸素ドーピング処理を行い、絶縁層602(a)及び絶縁層606(a)の一方又は両方を、化学量論的組成比より酸素が多い状態にする。

20

#### 【0205】

半導体層603(a)に接する絶縁層中の酸素を過剰にすることにより、半導体層603(a)に供給されやすくなる。よって、半導体層603(a)中、又は絶縁層602(a)及び絶縁層606(a)の一方又は両方と、半導体層603(a)との界面における酸素欠陥を低減することができるため、半導体層603(a)のキャリア濃度をより低減することができる。また、これに限定されず、製造過程により半導体層603(a)に含まれる酸素を過剰にした場合であっても、半導体層603(a)に接する上記絶縁層により、半導体層603(a)からの酸素の脱離を抑制することができる。

30

#### 【0206】

例えば、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化ガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムの組成をGa<sub>2</sub>O<sub>x</sub>にすることができる。

#### 【0207】

また、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化アルミニウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化アルミニウムの組成をAl<sub>2</sub>O<sub>x</sub>にすることができる。

40

#### 【0208】

また、絶縁層602(a)及び絶縁層606(a)の一方又は両方として、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムの組成をGa<sub>x</sub>Al<sub>2-x</sub>O<sub>3+</sub>とすることができます。

#### 【0209】

以上の工程により、半導体層603(a)から、水素、水、水酸基、又は水素化物(水素化合物ともいう)などの不純物を排除し、且つ半導体層603(a)に酸素を供給することにより、半導体層603(a)を高純度化させることができます。

#### 【0210】

50

さらに、上記加熱処理とは別に、絶縁層 606 (a) を形成した後に、不活性ガス雰囲気下、又は酸素ガス雰囲気下で加熱処理（好ましくは 200 以上 600 以下、例えば 250 以上 350 以下）を行ってもよい。

#### 【0211】

さらに、図 10 (E) に示すように、絶縁層 606 (a) の上に第 3 の導電膜を形成し、第 3 の導電膜の一部をエッチングすることにより導電層 608 (a) を形成する。

#### 【0212】

例えば、スパッタリング法を用いて導電層 608 (a) に適用可能な材料の膜を形成することにより第 3 の導電膜を形成することができる。また、第 3 の導電膜に適用可能な材料の膜を積層させ、第 3 の導電膜を形成することもできる。

10

#### 【0213】

なお、図 9 (A) に示すトランジスタの作製方法例を示したが、これに限定されず、例えば図 9 (B) 乃至図 9 (D) に示す各構成要素において、名称が図 9 (A) に示す各構成要素と同じであり且つ機能の少なくとも一部が図 9 (A) に示す各構成要素と同じであれば、図 10 (A) に示すトランジスタの作製方法例の説明を適宜援用することができる。

#### 【0214】

また、図 9 (C) 及び図 9 (D) に示すように、領域 604a (c) 及び領域 604a (d)、並びに領域 604b (c) 及び領域 604b (d) を形成する場合には、ゲートとしての機能を有する導電層が形成される側から半導体層にドーパントを添加することにより、ゲート絶縁層としての機能を有する絶縁層を介して自己整合で領域 604a (c) 及び領域 604a (d)、並びに領域 604b (c) 及び領域 604b (d) を形成する。

20

#### 【0215】

例えば、イオンドーピング装置又はイオン注入装置を用いてドーパントを添加することができる。

#### 【0216】

図 9 及び図 10 を用いて説明したように、本実施の形態におけるトランジスタの一例は、ゲートとしての機能を有する導電層と、ゲート絶縁層としての機能を有する絶縁層と、ゲート絶縁層としての機能を有する絶縁層を介してゲートとしての機能を有する導電層に重畠し、チャネルが形成される酸化物半導体層と、酸化物半導体層に電気的に接続され、ソース及びドレインの一方としての機能を有する導電層と、酸化物半導体層に電気的に接続され、ソース及びドレインの他方としての機能を有する導電層と、を含む構造である。

30

#### 【0217】

上記チャネルが形成される酸化物半導体層は、高純度化させることにより I 型又は実質的に I 型となった酸化物半導体層である。酸化物半導体層を高純度化させることにより、酸化物半導体層のキャリア濃度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満にすることができる。また、上記構造にすることにより、チャネル幅  $1 \mu\text{m}$ あたりのオフ電流を  $10 \text{ aA}$  ( $1 \times 10^{-11} \text{ A}$ ) 以下にすること、さらにはチャネル幅  $1 \mu\text{m}$ あたりのオフ電流を  $1 \text{ aA}$  ( $1 \times 10^{-10} \text{ A}$ ) 以下、さらにはチャネル幅  $1 \mu\text{m}$ あたりのオフ電流を  $10 \text{ zA}$  ( $1 \times 10^{-20} \text{ A}$ ) 以下、さらにはチャネル幅  $1 \mu\text{m}$ あたりのオフ電流を  $1 \text{ zA}$  ( $1 \times 10^{-21} \text{ A}$ ) 以下、さらにはチャネル幅  $1 \mu\text{m}$ あたりのオフ電流を  $100 \text{ yA}$  ( $1 \times 10^{-22} \text{ A}$ ) 以下にすることができる。トランジスタのオフ電流は、低ければ低いほどよいが、本実施の形態におけるトランジスタのオフ電流の下限値は、約  $10^{-30} \text{ A} / \mu\text{m}$  であると見積もられる。

40

#### 【0218】

本実施の形態の酸化物半導体層を含むトランジスタを、例えば上記実施の形態におけるワード線分割回路に適用するトランジスタとして用いることにより、極めて簡略化され、安定して動作可能なワード線分割回路を実現することができる。

50

**【0219】**

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

**【0220】****(実施の形態5)**

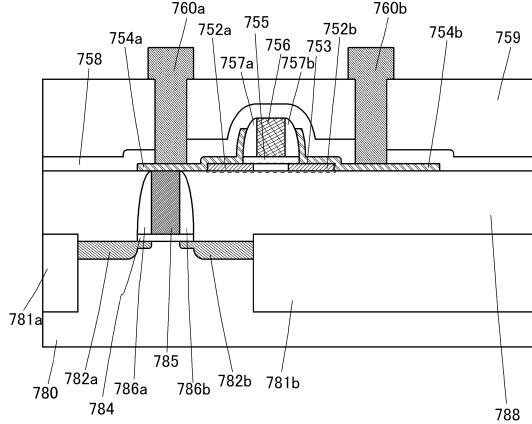

本実施の形態では、上記実施の形態における記憶装置の構造例について説明する。

**【0221】**

本実施の形態における記憶装置は、チャネルが形成され、元素周期表における第14族の半導体（シリコンなど）を含有する半導体層を含むトランジスタと、チャネルが形成される酸化物半導体層を含むトランジスタを用いて構成される。このとき、チャネルが形成される酸化物半導体層を含むトランジスタは、元素周期表における第14族の半導体（シリコンなど）を含有する半導体層を含むトランジスタの上に積層させることができる。元素周期表における第14族の半導体（シリコンなど）を含有する半導体層を含むトランジスタは、例えば図1における選択トランジスタ111や、図8における制御回路301、駆動回路302及び駆動回路303を構成するトランジスタに適用される。10

**【0222】**

元素周期表における第14族の半導体（シリコンなど）を含有する半導体層を含むトランジスタの上にチャネルが形成される酸化物半導体層を含むトランジスタを積層する例について、図11に示す。なお、図11では、実際の寸法と異なる構成要素を含む。20

**【0223】**

図11では、半導体層780と、絶縁層784と、導電層785と、絶縁層786aと、絶縁層786bと、絶縁層788と、半導体層753と、導電層754aと、導電層754bと、絶縁層755と、導電層756と、絶縁層757aと、絶縁層757bと、絶縁層758と、絶縁層759と、導電層760aと、導電層760bと、により元素周期表における第14族の半導体（シリコンなど）を含有する半導体層を含むnチャネル型トランジスタ（例えば図1における選択トランジスタ111に相当）とチャネルが形成される酸化物半導体層を含むトランジスタ（例えば図1に示すトランジスタ101に相当）が構成される。

**【0224】**

さらに、半導体層780は、領域782a、領域782bを有する。また、半導体層780には、絶縁領域781a及び絶縁領域781bが設けられ、隣接するトランジスタ（図示しない）が電気的に分離されている。30

**【0225】**

半導体層780としては、例えば半導体基板を用いることができる。また、別の基板の上に設けられた半導体層を半導体層780として用いることもできる。

**【0226】**

領域782a及び領域782bは、互いに離間して設けられ、n型の導電性を付与するドーパントが添加された領域である。領域782a及び領域782bは、上記nチャネル型トランジスタのソース領域又はドレイン領域としての機能を有する。例えば、領域782a及び領域782bのそれぞれは、別途設けられた導電層に電気的に接続されてもよい。40

**【0227】**

なお、領域782a及び領域782bに、p型の導電性を付与するドーパントを添加することにより、pチャネル型トランジスタのソース領域又はドレイン領域としての機能をもたせることもできる。

**【0228】**

なお、領域782a及び領域782bの一部に低濃度領域を設けてもよい。このとき低濃度領域の深さは、それ以外の領域782a及び領域782bの領域の深さよりも小さいが、これに限定されない。

**【0229】**

絶縁層 7 8 4 は、絶縁領域 7 8 1 a 及び絶縁領域 7 8 1 b に挟まれた半導体層 7 8 0 の領域の上に設けられる。絶縁層 7 8 4 は、上記 n チャネル型トランジスタのゲート絶縁層としての機能を有する。

#### 【 0 2 3 0 】

絶縁層 7 8 4 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、有機絶縁材料（例えばポリイミド又はアクリルなど）などの材料の層を用いることができる。また、絶縁層 7 8 4 に適用可能な材料の積層により絶縁層 7 8 4 を構成してもよい。

#### 【 0 2 3 1 】

導電層 7 8 5 は、絶縁層 7 8 4 を介して半導体層 7 8 0 に重畠する。導電層 7 8 5 に重畠する半導体層 7 8 0 の領域が上記 n チャネル型トランジスタのチャネル形成領域になる。導電層 7 8 5 は、上記 n チャネル型トランジスタのゲートとしての機能を有する。

#### 【 0 2 3 2 】

導電層 7 8 5 としては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層 7 8 5 に適用可能な材料の積層により、導電層 7 8 5 を構成することもできる。

#### 【 0 2 3 3 】

絶縁層 7 8 6 a は、絶縁層 7 8 4 の上に設けられ、導電層 7 8 5 における、互いに対向する一対の側面の一方に接する。

#### 【 0 2 3 4 】

絶縁層 7 8 6 b は、絶縁層 7 8 4 の上に設けられ、導電層 7 8 5 における、互いに対向する上記一対の側面の他方に接する。

#### 【 0 2 3 5 】

絶縁層 7 8 8 は、導電層 7 8 5 、絶縁層 7 8 6 a 、及び絶縁層 7 8 6 b の上に設けられる。

#### 【 0 2 3 6 】

絶縁層 7 8 6 a 、絶縁層 7 8 6 b 、及び絶縁層 7 8 8 としては、絶縁層 7 8 4 に適用可能な材料のうち、絶縁層 7 8 4 に適用した材料と同じ材料の層又は異なる材料の層を用いることができる。また、絶縁層 7 8 6 a 、絶縁層 7 8 6 b 、及び絶縁層 7 8 8 に適用可能な材料の積層により、絶縁層 7 8 6 a 、絶縁層 7 8 6 b 、及び絶縁層 7 8 8 を構成することもできる。

#### 【 0 2 3 7 】

半導体層 7 5 3 は、絶縁層 7 8 8 の上に設けられる。半導体層 7 5 3 は、領域 7 5 2 a 及び領域 7 5 2 b を含む。領域 7 5 2 a 及び領域 7 5 2 b はドーパントが添加された領域であり、ソース領域又はドレイン領域としての機能を有する。ドーパントとしては、上記実施の形態における酸化物半導体層を含むトランジスタに適用可能なドーパントを適宜用いることができる。なお、領域 7 5 2 a 及び領域 7 5 2 b は必ずしも設けなくともよい。

#### 【 0 2 3 8 】

半導体層 7 5 3 としては、例えば図 9 ( A ) に示す半導体層 6 0 3 ( a ) に適用可能な材料の層を用いることができる。

#### 【 0 2 3 9 】

絶縁層 7 5 5 は、半導体層 7 5 3 の上に設けられる。また絶縁層 7 5 5 は、トランジスタのゲート絶縁層としての機能を有する。

#### 【 0 2 4 0 】

絶縁層 7 5 5 としては、例えば図 9 ( A ) に示す絶縁層 6 0 2 ( a ) に適用可能な材料の層を用いることができる。また、絶縁層 7 5 5 に適用可能な材料の積層により絶縁層 7 5 5 を構成してもよい。

#### 【 0 2 4 1 】

10

20

30

40

50

導電層 756 は、絶縁層 755 を介して半導体層 753 に重畠する。導電層 756 は、トランジスタのゲートとしての機能を有する。

#### 【0242】

導電層 756 としては、例えば図 9 (A) に示す導電層 601 (a) に適用可能な材料の層を用いることができる。また、導電層 756 に適用可能な材料の積層により導電層 756 を構成してもよい。

#### 【0243】

絶縁層 757a 及び絶縁層 757b は、導電層 756 の側面に接して絶縁層 755 の上に設けられる。なお、絶縁層 757a 及び絶縁層 757b は必ずしも設けなくてもよい。

#### 【0244】

導電層 754a は、半導体層 753 に接して電気的に接続される。また、導電層 754a は、導電層 785 に電気的に接続される。導電層 754a は、上記酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

#### 【0245】

導電層 754b は、半導体層 753 に接して電気的に接続される。導電層 754b は、上記酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

#### 【0246】

導電層 754a 及び導電層 754b としては、例えば図 9 (A) に示す導電層 605a (a) 及び導電層 605b (a) に適用可能な材料の層を用いることができる。また、導電層 754a 及び導電層 754b に適用可能な材料の積層により導電層 754a 及び導電層 754b を構成してもよい。

#### 【0247】

絶縁層 758 は、導電層 756、絶縁層 757a、絶縁層 757b、導電層 754a、及び導電層 754b の上に設けられる。

#### 【0248】

絶縁層 758 としては、例えば図 9 (A) に示す絶縁層 602 (a) に適用可能な材料の層を用いることができる。また、絶縁層 758 に適用可能な材料の積層により絶縁層 758 を構成してもよい。絶縁層 758 は、不純物の侵入を抑制する保護層としての機能を有する。

#### 【0249】

絶縁層 759 は、絶縁層 758 の上に設けられる。

#### 【0250】

絶縁層 759 としては、例えば図 9 (A) に示す絶縁層 602 (a) に適用可能な材料の層を用いることができる。また、絶縁層 759 に適用可能な材料の積層により絶縁層 759 を構成してもよい。

#### 【0251】

導電層 760a は、絶縁層 758 及び絶縁層 759 に設けられた開口部を介して導電層 754a に電気的に接続される。導電層 760a は、酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

#### 【0252】

導電層 760b は、絶縁層 758 及び絶縁層 759 に設けられた開口部を介して導電層 754b に電気的に接続される。導電層 760b は、酸化物半導体層を含むトランジスタのソース又はドレインとしての機能を有する。

#### 【0253】

導電層 760a 及び導電層 760b としては、例えば図 9 (A) に示す導電層 605a (a) 及び導電層 605b (a) に適用可能な材料の層を用いることができる。また、導電層 760a 及び導電層 760b に適用可能な材料の積層により導電層 760a 及び導電層 760b を構成してもよい。

#### 【0254】

以上が図 11 に示す記憶装置の構造例の説明である。

**【 0 2 5 5 】**

図11を用いて説明したように、本実施の形態における記憶装置の構造例では、異なる材料の半導体層を用いたトランジスタを積層させて記憶装置を構成することにより、回路面積を小さくすることができる。

**【 0 2 5 6 】**

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

**【 0 2 5 7 】**

## (実施の形態6)

酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。好ましくは、酸化物半導体膜は、CAAC-OS膜とする。10

**【 0 2 5 8 】**

本実施の形態では、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物(CAAC-OS)膜について説明する。

**【 0 2 5 9 】**

CAAC-OSは単結晶ではないが、非晶質のみから形成されているものでもない。CAAC-OS膜は、非晶質相に結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。20

**【 0 2 6 0 】**

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。30

**【 0 2 6 1 】**

CAAC-OSを構成する酸素の一部は窒素で置換されてもよい。また、CAAC-OSを構成する個々の結晶部分のc軸は一定の方向(例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向)に揃っていてもよい。または、CAAC-OSを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向)を向いていてもよい。40

**【 0 2 6 2 】**

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

**【 0 2 6 3 】**

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベク50

トルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

**【0264】**

C A A C - O S は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

**【0265】**

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

**【0266】**

このようなC A A C - O S の例として、膜状に形成され、膜表面または膜が形成される基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる酸化物を挙げることもできる。

**【0267】**

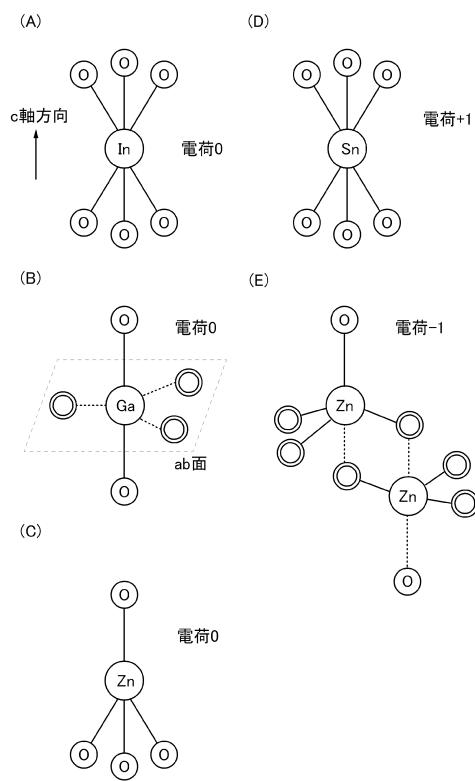

C A A C - O S について図12乃至図15を用いて詳細に説明する。なお、特に断りがない限り、図12乃至図14は上方向をc軸方向とし、c軸方向と直交する面をa b面とする。なお、単に上半分、下半分という場合、a b面を境にした場合の上半分、下半分をいう。また、図12において丸で囲まれたO原子は4配位のO原子を示し、二重丸は3配位のO原子を示す。

10

**【0268】**

図12(A)に、1個の6配位のIn原子と、In原子に近接の6個の4配位の酸素原子（以下4配位のO原子）と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図12(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図12(A)の上半分および下半分にはそれぞれ3個ずつ4配位のO原子がある。図12(A)に示す小グループは電荷が0である。

20

**【0269】**

図12(B)に、1個の5配位のGa原子と、Ga原子に近接の3個の3配位の酸素原子（以下3配位のO原子）と、Ga原子に近接の2個の4配位のO原子と、を有する構造を示す。3配位のO原子は、いずれもa b面に存在する。図12(B)の上半分および下半分にはそれぞれ1個ずつ4配位のO原子がある。また、In原子も5配位をとるため、図12(B)に示す構造をとりうる。図12(B)に示す小グループは電荷が0である。

30

**【0270】**

図12(C)に、1個の4配位のZn原子と、Zn原子に近接の4個の4配位のO原子と、を有する構造を示す。図12(C)の上半分には1個の4配位のO原子があり、下半分には3個の4配位のO原子がある。または、図12(C)の上半分に3個の4配位のO原子があり、下半分に1個の4配位のO原子があってもよい。図12(C)に示す小グループは電荷が0である。

**【0271】**

40

図12(D)に、1個の6配位のSn原子と、Sn原子に近接の6個の4配位のO原子と、を有する構造を示す。図12(D)の上半分には3個の4配位のO原子があり、下半分には3個の4配位のO原子がある。図12(D)に示す小グループは電荷が+1となる。

**【0272】**

図12(E)に、2個のZn原子を含む小グループを示す。図12(E)の上半分には1個の4配位のO原子があり、下半分には1個の4配位のO原子がある。図12(E)に示す小グループは電荷が-1となる。

**【0273】**

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体

50

を大グループ（ユニットセルともいう。）と呼ぶ。

#### 【0274】

ここで、これらの小グループ同士が結合する規則について説明する。図12(A)に示す6配位のIn原子の上半分の3個のO原子は、下方向にそれぞれ3個の近接In原子を有し、下半分の3個のO原子は、上方向にそれぞれ3個の近接In原子を有する。図12(B)に示す5配位のGa原子の上半分の1個のO原子は下方向に1個の近接Ga原子を有し、下半分の1個のO原子は上方向に1個の近接Ga原子を有する。図12(C)に示す4配位のZn原子の上半分の1個のO原子は、下方向に1個の近接Zn原子を有し、下半分の3個のO原子は、上方向にそれぞれ3個の近接Zn原子を有する。この様に、金属原子の上方向の4配位のO原子の数と、そのO原子の下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のO原子の数と、そのO原子の上方向にある近接金属原子の数は等しい。O原子は4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のO原子の数と、別の金属原子の下方向にある4配位のO原子の数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のO原子を介して結合する場合、4配位のO原子が3個であるため、5配位の金属原子(GaまたはIn)、4配位の金属原子(Zn)のいずれかと結合することになる。

#### 【0275】

これらの配位数を有する金属原子は、c軸方向において、4配位のO原子を介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

#### 【0276】

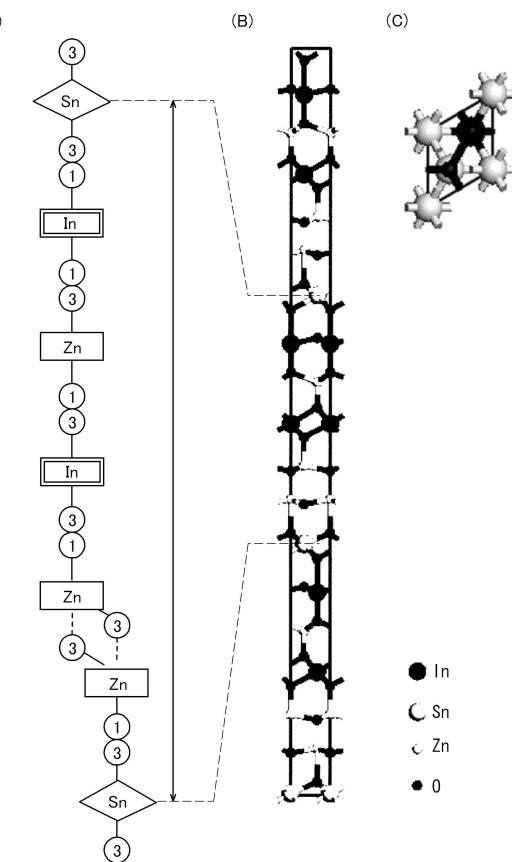

図13(A)に、In-Sn-Zn-O系の層構造を構成する中グループのモデル図を示す。図13(B)に、3つの中グループで構成される大グループを示す。なお、図13(C)は、図13(B)の層構造をc軸方向から観察した場合の原子配列を示す。

#### 【0277】

図13(A)においては、簡単のため、3配位のO原子は省略し、4配位のO原子は個数のみ示し、例えば、Sn原子の上半分および下半分にはそれぞれ3個ずつ4配位のO原子があることを丸枠の3として示している。同様に、図13(A)において、In原子の上半分および下半分にはそれぞれ1個ずつ4配位のO原子があり、丸枠の1として示している。また、同様に、図13(A)において、下半分には1個の4配位のO原子があり、上半分には3個の4配位のO原子があるZn原子と、上半分には1個の4配位のO原子があり、下半分には3個の4配位のO原子があるZn原子とを示している。

#### 【0278】

図13(A)において、In-Sn-Zn-O系の層構造を構成する中グループは、上から順に4配位のO原子が3個ずつ上半分および下半分にあるSn原子が、4配位のO原子が1個ずつ上半分および下半分にあるIn原子と結合し、そのIn原子が、上半分に3個の4配位のO原子があるZn原子と結合し、そのZn原子の下半分の1個の4配位のO原子を介して4配位のO原子が3個ずつ上半分および下半分にあるIn原子と結合し、そのIn原子が、上半分に1個の4配位のO原子があるZn原子2個からなる小グループと結合し、この小グループの下半分の1個の4配位のO原子を介して4配位のO原子が3個ずつ上半分および下半分にあるSn原子と結合している構成である。この中グループが複数結合して大グループを構成する。

#### 【0279】

ここで、3配位のO原子および4配位のO原子の場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)原子、Zn(4配位)原子、Sn(5配位または6配位)原子の電荷は、それぞれ+3、+2、+4である。従って、Sn原子を含む小グループは電荷が+1となる。そのため、Sn原子を含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。

電荷 - 1 をとる構造として、図 12 ( E ) に示すように、2 個の Zn 原子を含む小グループが挙げられる。例えば、Sn 原子を含む小グループが 1 個に対し、2 個の Zn 原子を含む小グループが 1 個あれば、電荷が打ち消されるため、層構造の合計の電荷を 0 とすることができる。

#### 【 0280 】

具体的には、図 13 ( B ) に示した大グループとすることで、In - Sn - Zn - O 系の結晶 ( $In_2SnZn_3O_8$ ) を得ることができる。なお、得られる In - Sn - Zn - O 系の層構造は、 $In_2SnZn_2O_7 (ZnO)_m$  ( $m$  は 0 または自然数。) とする組成式で表すことができる。

#### 【 0281 】

また、このほかにも、四元系金属の酸化物である In - Sn - Ga - Zn - O 系酸化物や、三元系金属の酸化物である In - Ga - Zn - O 系酸化物 (IGZO とも表記する。) 、 In - Al - Zn - O 系酸化物、 Sn - Ga - Zn - O 系酸化物、 Al - Ga - Zn - O 系酸化物、 Sn - Al - Zn - O 系酸化物や、 In - Hf - Zn - O 系酸化物、 In - La - Zn - O 系酸化物、 In - Ce - Zn - O 系酸化物、 In - Pr - Zn - O 系酸化物、 In - Nd - Zn - O 系酸化物、 In - Pm - Zn - O 系酸化物、 In - Sm - Zn - O 系酸化物、 In - Eu - Zn - O 系酸化物、 In - Gd - Zn - O 系酸化物、 In - Tb - Zn - O 系酸化物、 In - Dy - Zn - O 系酸化物、 In - Ho - Zn - O 系酸化物、 In - Er - Zn - O 系酸化物、 In - Tm - Zn - O 系酸化物、 In - Yb - Zn - O 系酸化物、 In - Lu - Zn - O 系酸化物や、二元系金属の酸化物である In - Zn - O 系酸化物、 Sn - Zn - O 系酸化物、 Al - Zn - O 系酸化物、 Zn - Mg - O 系酸化物、 Sn - Mg - O 系酸化物、 In - Mg - O 系酸化物や、 In - Ga - O 系酸化物などを用いた場合も同様である。

#### 【 0282 】

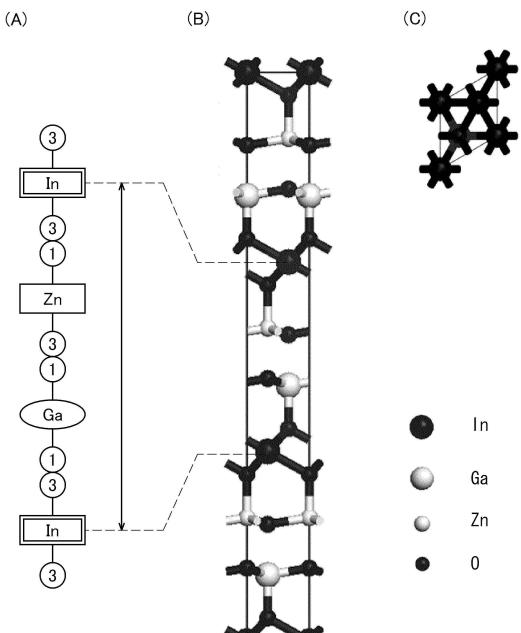

例えば、図 14 ( A ) に、In - Ga - Zn - O 系の層構造を構成する中グループのモデル図を示す。

#### 【 0283 】

図 14 ( A ) において、In - Ga - Zn - O 系の層構造を構成する中グループは、上から順に 4 配位の O 原子が 3 個ずつ上半分および下半分にある In 原子が、4 配位の O 原子が 1 個上半分にある Zn 原子と結合し、その Zn 原子の下半分の 3 個の 4 配位の O 原子を介して、4 配位の O 原子が 1 個ずつ上半分および下半分にある Ga 原子と結合し、その Ga 原子の下半分の 1 個の 4 配位の O 原子を介して、4 配位の O 原子が 3 個ずつ上半分および下半分にある In 原子と結合している構成である。この中グループが複数結合して大グループを構成する。

#### 【 0284 】

図 14 ( B ) に 3 つの中グループで構成される大グループを示す。なお、図 14 ( C ) は、図 14 ( B ) の層構造を c 軸方向から観察した場合の原子配列を示している。

#### 【 0285 】

ここで、In (6 配位または 5 配位) 原子、Zn (4 配位) 原子、Ga (5 配位) 原子の電荷は、それぞれ +3、+2、+3 であるため、In 原子、Zn 原子および Ga 原子のいずれかを含む小グループは、電荷が 0 となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に 0 となる。

#### 【 0286 】

また、In - Ga - Zn - O 系の層構造を構成する中グループは、図 14 ( A ) に示した中グループに限定されず、In 原子、Ga 原子、Zn 原子の配列が異なる中グループを組み合わせた大グループを取りうる。

#### 【 0287 】

具体的には、図 14 ( B ) に示した大グループとすることで、In - Ga - Zn - O 系の結晶を得ることができる。なお、得られる In - Ga - Zn - O 系の層構造は、 $InGaO_3 (ZnO)_n$  ( $n$  は自然数。) とする組成式で表すことができる。

10

20

30

40

50

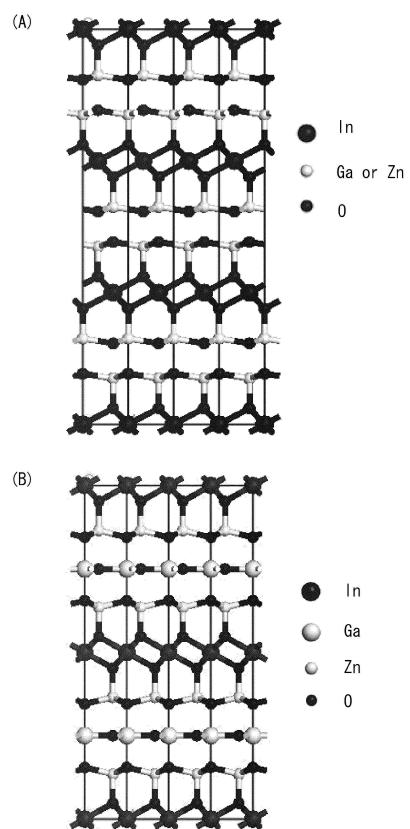

## 【0288】

$n = 1$  ( $\text{InGaZnO}_4$ ) の場合は、例えば、図15(A)に示す結晶構造を取りうる。なお、図15(A)に示す結晶構造において、図12(B)で説明したように、Ga原子及びIn原子は5配位をとるため、Ga原子がIn原子に置き換わった構造も取りうる。

## 【0289】

また、 $n = 2$  ( $\text{InGaZn}_2\text{O}_5$ ) の場合は、例えば、図15(B)に示す結晶構造を取りうる。なお、図15(B)に示す結晶構造において、図12(B)で説明したように、Ga原子及びIn原子は5配位をとるため、Ga原子がIn原子に置き換わった構造も取りうる。

10

## 【0290】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

## 【符号の説明】

## 【0291】

|     |          |    |

|-----|----------|----|

| 100 | 記憶装置     |    |

| 101 | トランジスタ   |    |

| 110 | メモリセル    |    |

| 111 | 選択トランジスタ |    |

| 113 | データ保持部   | 20 |

| 150 | 記憶装置     |    |

| 200 | 記憶装置     |    |

| 210 | メモリセル    |    |

| 211 | 選択トランジスタ |    |

| 213 | 容量素子     |    |

| 220 | 記憶装置     |    |

| 230 | メモリセル    |    |

| 231 | 選択トランジスタ |    |

| 240 | 記憶装置     |    |

| 250 | メモリセル    | 30 |

| 251 | 選択トランジスタ |    |

| 253 | 選択トランジスタ |    |

| 255 | トランジスタ   |    |

| 256 | トランジスタ   |    |

| 257 | トランジスタ   |    |

| 258 | トランジスタ   |    |

| 260 | 記憶装置     |    |

| 270 | メモリセル    |    |

| 271 | 選択トランジスタ |    |

| 273 | トランジスタ   | 40 |

| 275 | 容量素子     |    |

| 300 | 記憶装置     |    |

| 301 | 制御回路     |    |

| 302 | 駆動回路     |    |

| 303 | 駆動回路     |    |

| 304 | メモリセルアレイ |    |

| 305 | メモリセル    |    |

| 600 | 被素子形成層   |    |

| 601 | 導電層      |    |

| 602 | 絶縁層      | 50 |

|         |        |    |

|---------|--------|----|

| 6 0 3   | 半導体層   |    |

| 6 0 4 a | 領域     |    |

| 6 0 4 b | 領域     |    |

| 6 0 5 a | 導電層    |    |

| 6 0 5 b | 導電層    |    |

| 6 0 6   | 絶縁層    |    |

| 6 0 8   | 導電層    |    |

| 7 5 2 a | 領域     |    |

| 7 5 2 b | 領域     |    |

| 7 5 3   | 半導体層   | 10 |

| 7 5 4 a | 導電層    |    |

| 7 5 4 b | 導電層    |    |

| 7 5 5   | 絶縁層    |    |

| 7 5 6   | 導電層    |    |

| 7 5 7 a | 絶縁層    |    |

| 7 5 7 b | 絶縁層    |    |

| 7 5 8   | 絶縁層    |    |

| 7 5 9   | 絶縁層    |    |

| 7 6 0 a | 導電層    |    |

| 7 6 0 b | 導電層    | 20 |

| 7 8 0   | 半導体層   |    |

| 7 8 1 a | 絶縁領域   |    |

| 7 8 1 b | 絶縁領域   |    |

| 7 8 2 a | 領域     |    |

| 7 8 2 b | 領域     |    |

| 7 8 4   | 絶縁層    |    |

| 7 8 5   | 導電層    |    |

| 7 8 6 a | 絶縁層    |    |

| 7 8 6 b | 絶縁層    |    |

| 7 8 8   | 絶縁層    | 30 |

| W L     | ワード線   |    |

| S G     | 選択信号線  |    |

| B L     | ビット線   |    |

| S W L   | サブワード線 |    |

| C L     | 容量線    |    |

| S L     | ソース線   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

【図14】

【図15】

---

フロントページの続き

| (51)Int.Cl.              | F I                   |

|--------------------------|-----------------------|

| H 01 L 27/108 (2006.01)  | H 01 L 27/108 6 7 1 C |

| H 01 L 21/8244 (2006.01) | H 01 L 27/11          |

| H 01 L 27/11 (2006.01)   | H 01 L 29/78 6 1 3 B  |

| H 01 L 29/786 (2006.01)  |                       |

(56)参考文献 特開2004-234713 (JP, A)

特開平07-057456 (JP, A)

米国特許出願公開第2011/0089417 (US, A1)

特開2011-054936 (JP, A)

特開2009-135350 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| G 11 C | 5 / 02    |

| G 11 C | 8 / 12    |

| G 11 C | 11 / 408  |

| G 11 C | 11 / 418  |

| H 01 L | 21 / 8242 |

| H 01 L | 21 / 8244 |

| H 01 L | 27 / 108  |

| H 01 L | 27 / 11   |

| H 01 L | 29 / 786  |