(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

6 November 2008 (06.11.2008)

PCT

(10) International Publication Number

WO 2008/132894 A1

## (51) International Patent Classification:

*H01L 21/02* (2006.01)      *G09F 9/30* (2006.01)

*G02F 1/1368* (2006.01)      *H01L 27/12* (2006.01)

## (21) International Application Number:

PCT/JP2008/055172

## (22) International Filing Date:

14 March 2008 (14.03.2008)

## (25) Filing Language:

English

## (26) Publication Language:

English

## (30) Priority Data:

2007-106578      13 April 2007 (13.04.2007)      JP

(71) Applicant (for all designated States except US): SEMICONDUCTOR ENERGY LABORATORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

## (72) Inventor; and

(75) Inventor/Applicant (for US only): YAMAZAKI, Shunpei [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BI, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Published:

— with international search report

## (54) Title: DISPLAY DEVICE, METHOD FOR MANUFACTURING DISPLAY DEVICE, AND SOI SUBSTRATE

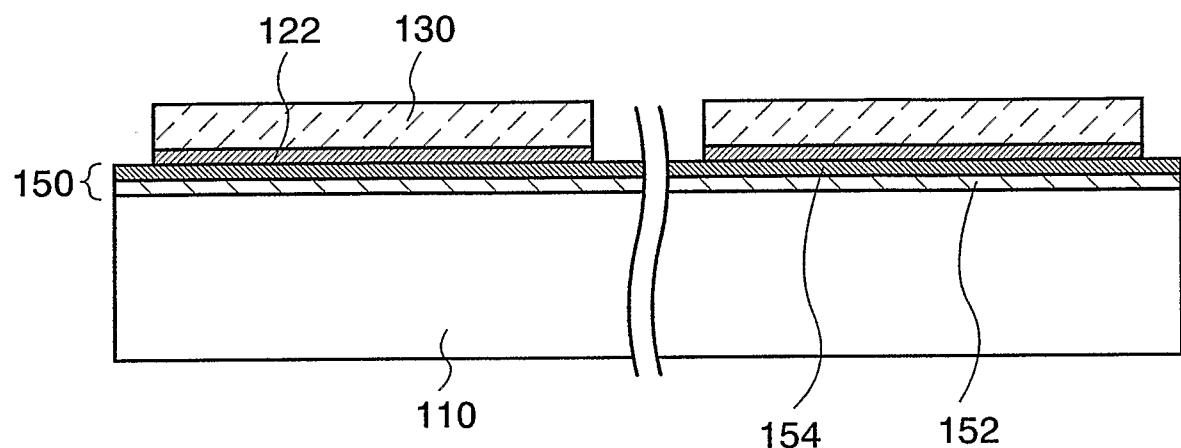

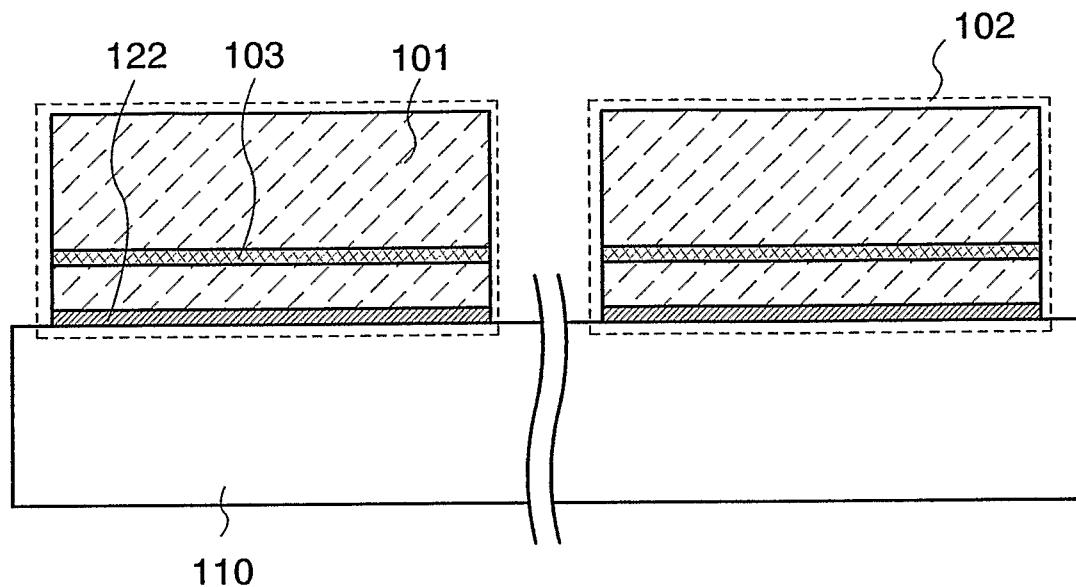

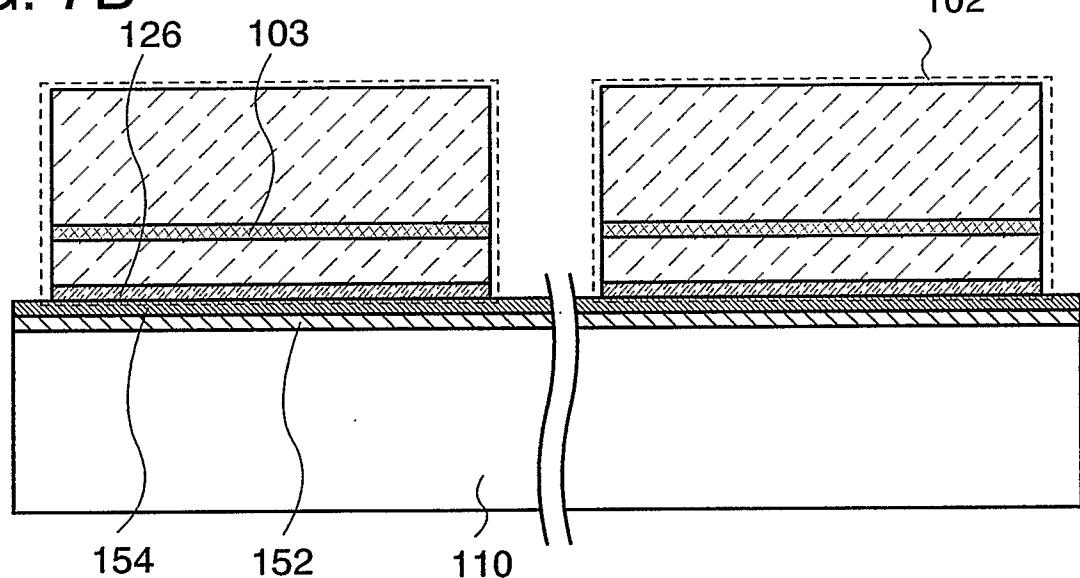

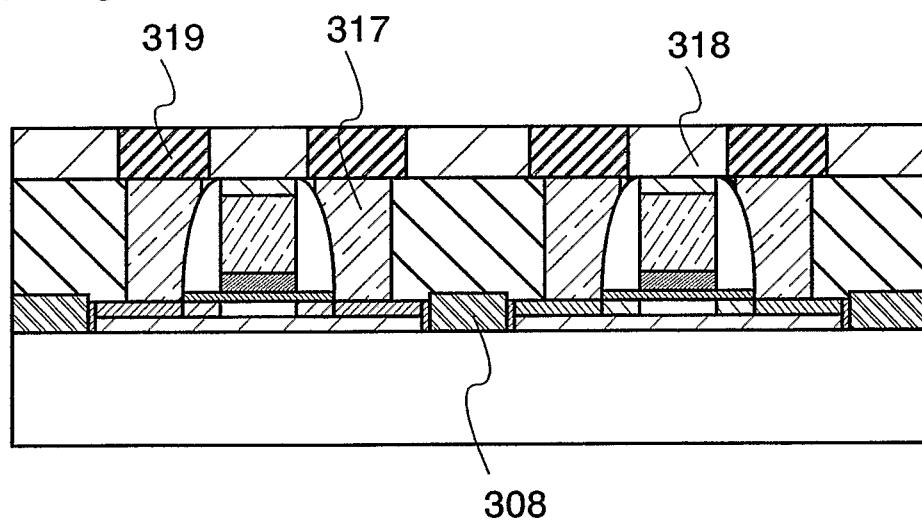

FIG. 6A

FIG. 6B

FIG. 6C

(57) Abstract: A manufacturing method is provided which achieves an SOI substrate with a large area and can improve productivity of manufacture of a display device using the SOI substrate. A plurality of single-crystalline semiconductor layers are bonded to a substrate having an insulating surface, and a circuit including a transistor is formed using the single-crystalline semiconductor layers, so that a display device is manufactured. Single-crystalline semiconductor layers separated from a single-crystalline semiconductor substrate are applied to the plurality of single-crystalline semiconductor layers. Each of the single-crystalline semiconductor layers has a size corresponding to one display panel (panel size).

## DESCRIPTION

**DISPLAY DEVICE, METHOD FOR MANUFACTURING DISPLAY DEVICE,

AND SOI SUBSTRATE**

5

**TECHNICAL FIELD**

[0001]

The present invention relates to an SOI (silicon on insulator) substrate and a display device that is manufactured using the SOI substrate. In particular, the present invention relates to a bonding SOI technology, an SOI substrate formed by bonding a single-crystalline or polycrystalline semiconductor layer to a substrate having an insulating surface (e.g. a glass), and a display device that is manufactured using the SOI substrate.

15 **BACKGROUND ART**

[0002]

With a quantum leap in VLSI technology in recent years, an SOI structure, which enables high-speed operation and low power consumption, has been attracting attention. In this technology, an active region (channel formation region) of a field-effect transistor (FET), which is conventionally formed with bulk single-crystalline silicon, is formed with a single-crystalline silicon thin film. It is known that use of the SOI structure enables manufacturing a MOS field-effect transistor with smaller parasitic capacitance than in the conventional case of using a bulk single-crystalline silicon substrate, and is advantageous to high speed operation.

25 [0003]

As a method for manufacturing a conventional SOI substrate, a hydrogen ion implanting separation method is known (for example, refer to Reference 1: PCT International Publication No. 00/24059). In the hydrogen ion implanting separation method, a microbubble layer is formed at a given depth from a surface by implanting hydrogen ions into a silicon wafer to make the microbubble layer a cleavage plane, so that a thin single-crystalline silicon layer (SOI layer) is bonded to another silicon wafer; in addition to performing heat treatment for separating the SOI layer, Reference 1

describes that a bonding strength needs to be enhanced by forming an oxide film on the SOI layer by heat treatment in an oxidation atmosphere, removing the oxide film, and performing heat treatment in a reduction atmosphere at 1000 to 1300 °C.

[0004]

5 As an example of a semiconductor device utilizing an SOI substrate, a semiconductor device by the present applicant is known (refer to Reference 2: Japanese Published Patent Application No. 2000-12864). Reference 2 also discloses that heat treatment at temperatures of 1050 to 1150 °C is necessary in order to remove a level or a defect due to a stress in the SOI layer.

10

## DISCLOSURE OF INVENTION

[0005]

A method for manufacturing a conventional SOI substrate needs heat treatment at high temperatures of 1000 °C or higher in order to ensure a high bonding strength of 15 the SOI layer. Therefore, it is difficult to form an SOI layer over a substrate with a heat-resistant temperature of about 600 °C (e.g. a glass substrate, which can be used for manufacturing a display device such as a liquid crystal panel). Even if an SOI layer is provided over a glass substrate by a hydrogen ion implanting separation method, heat treatment at a high temperature cannot be applied; therefore, there is a problem in that 20 the bonding strength of the SOI layer is low. Further, in a conventional SOI substrate utilizing a hydrogen ion implanting separation method, an SOI structure is obtained by bonding one sheet of silicon wafer to another sheet of silicon wafer and thinning one of the silicon wafers. Therefore, the conventional SOI substrate utilizing a hydrogen ion implanting separation method depends on the size of a silicon wafer, and it is difficult to 25 have a large area.

[0006]

In view of the above problems, an object of the present invention is to have a 30 large area in an SOI substrate and improve the productivity of manufacturing display devices utilizing the SOI substrate. Further, another object is high performance of the display devices.

## [0007]

A plurality of single-crystalline semiconductor layers are bonded to a substrate having an insulating surface, and circuits including transistors are formed using the single-crystalline semiconductor layers, so that display devices are manufactured.

## 5 [0008]

A single-crystalline semiconductor layer separated from a single-crystalline semiconductor substrate is applied to the single-crystalline semiconductor layers. A polycrystalline semiconductor substrate may be applied instead of the single-crystalline semiconductor substrate. The single-crystalline semiconductor layer is divided into 10 sections each having a size corresponding to one display panel (a panel size), specifically, sections each having an area including one panel, and the sections of the single-crystalline semiconductor layer are bonded to a substrate having an insulating surface.

## [0009]

15 In the case where a plurality of single-crystalline semiconductor layers are transferred from a single-crystalline semiconductor substrate, a plurality of single-crystalline semiconductor layers may belong to one alignment marker.

## [0010]

An aspect of the present invention is a method for manufacturing a display 20 device, including the steps of bonding a plurality of single-crystalline semiconductor layers obtained by dividing a semiconductor substrate into sections each having an area including one panel to a substrate having an insulating surface with an insulating layer interposed therebetween, and forming a circuit including a transistor using each of the single-crystalline semiconductor layers by exposing a block selected from the plurality 25 of single-crystalline semiconductor layers at a time and transferring and forming a circuit pattern.

## [0011]

Another aspect of the present invention is a method for manufacturing a display device, including the steps of bonding a plurality of single-crystalline 30 semiconductor layers obtained by dividing a semiconductor substrate into sections each having an area including one panel to a substrate having an insulating surface, with a silicon oxide layer interposed therebetween which is formed by a chemical vapor

deposition method using organic silane as a source gas; and forming a circuit including a transistor using each of the single-crystalline semiconductor layers by exposing a block selected from the plurality of single-crystalline semiconductor layers at a time and transferring and forming a circuit pattern.

5 [0012]

Another aspect of the present invention is that one block selected from the plurality of single-crystalline semiconductor layers may be a block in a range that can be exposed to light one time using a light exposure apparatus, i.e. a range that is exposed to light one time using the light exposure apparatus. Further, a plurality of 10 single-crystalline semiconductor layers may belong to one alignment marker in the one block.

[0013]

Another aspect of the present invention is a display device including a circuit including a transistor over a substrate having an insulating surface. The transistor 15 includes a channel formation region including a single-crystalline semiconductor. A silicon oxide layer formed by a chemical vapor deposition method using organic silane as a source gas is provided between the channel formation region of the transistor and the substrate having an insulating surface.

[0014]

20 Another aspect of the present invention is that tetraethoxysilane, trimethylsilane, tetramethylsilane, tetramethylcyclotetrasiloxane, octamethylcyclotetrasiloxane, hexamethyldisilazane, triethoxysilane, or trisdimethylaminosilane can be used as the organic silane.

[0015]

25 Another aspect of the present invention is that aluminosilicate glass, aluminoborosilicate glass, barium borosilicate glass, a quartz substrate, a sapphire substrate, or a ceramic substrate can be used as the substrate having an insulating surface.

[0016]

30 In this description, a display device designates a device in which a display element (e.g. a liquid crystal element, a light-emitting element, or an electrophoretic element) is used; i.e., an image display device. Further, examples of the display device

include all of the followings: a module in which an external input terminal such as a flexible printed circuit (FPC), tape automated bonding (TAB) tape, or tape carrier package (TCP) is attached to a display panel (e.g. a liquid crystal panel or a light-emitting panel); a module in which a printed wiring board is provided at an end of TAB tape or TCP; and a module in which an IC (integrated circuit) or a CPU (central processing unit) is mounted directly on a display panel by a COG (chip on glass) method.

5 [0017]

Application of the present invention enables achievement of an SOI substrate with a large area and improvement in the productivity of manufacturing display devices utilizing the SOI substrate. Further, high performance can be achieved in the display devices utilizing the SOI substrate.

#### BRIEF DESCRIPTION OF DRAWINGS

15 [0018]

In the accompanying drawings:

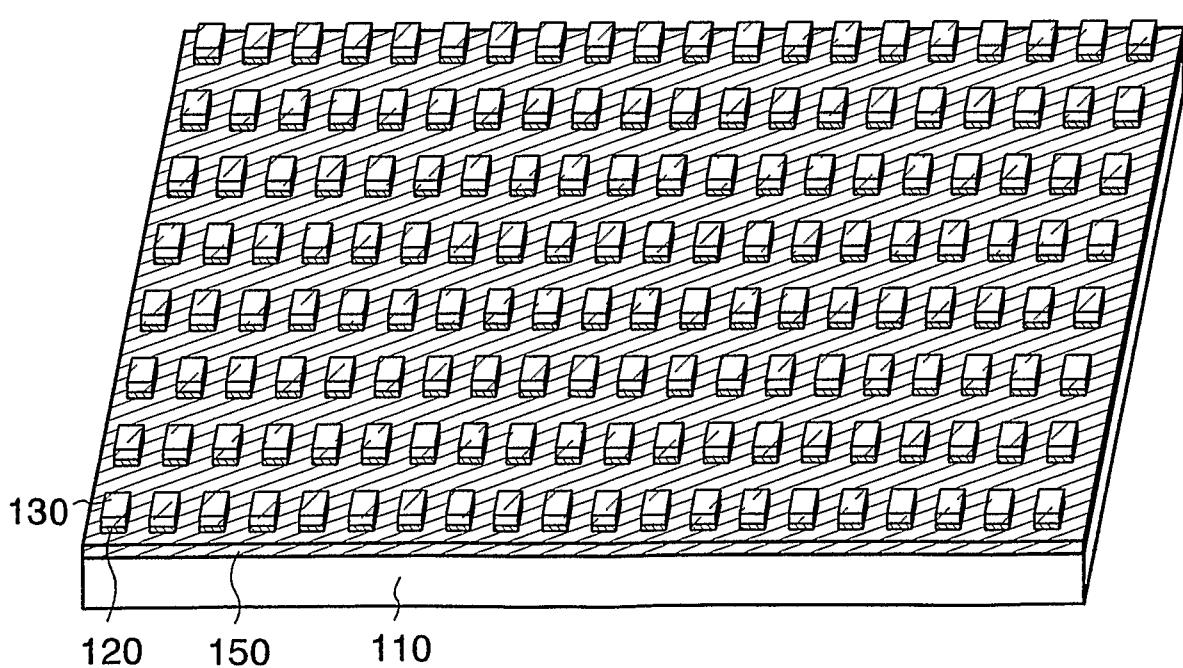

FIGS. 1A and 1B are perspective views showing examples of structures of an SOI substrate according to the present invention;

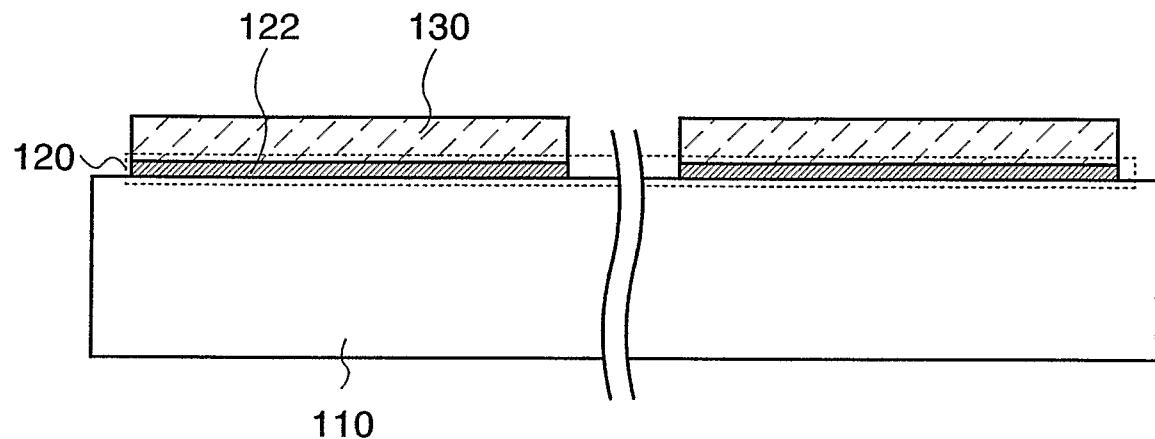

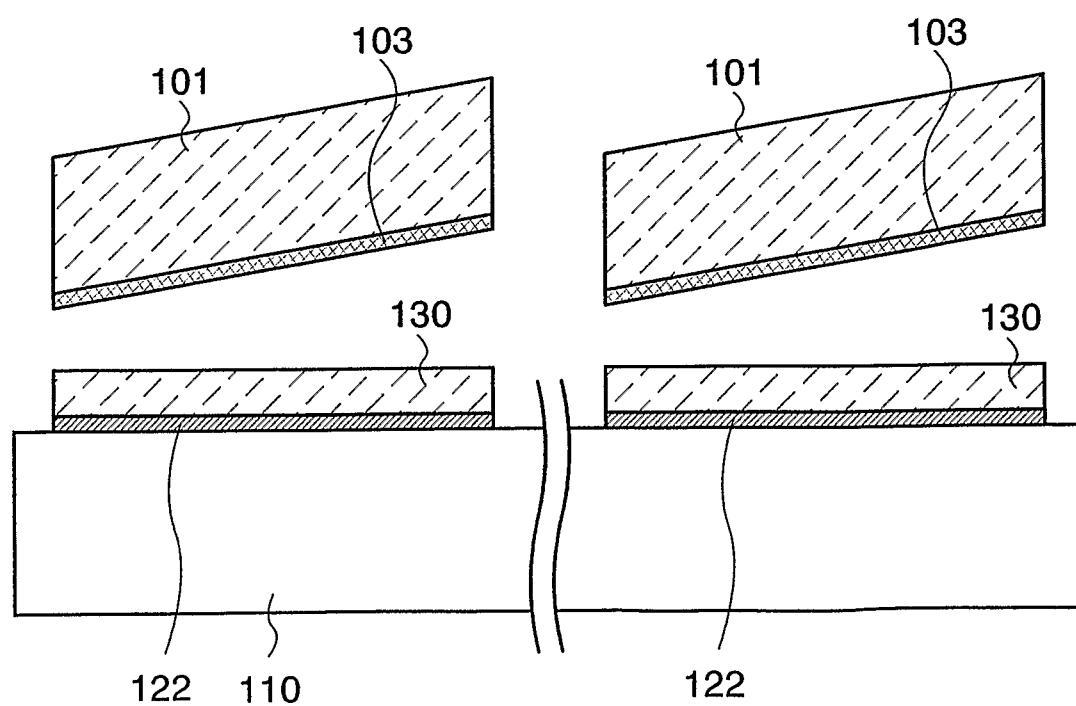

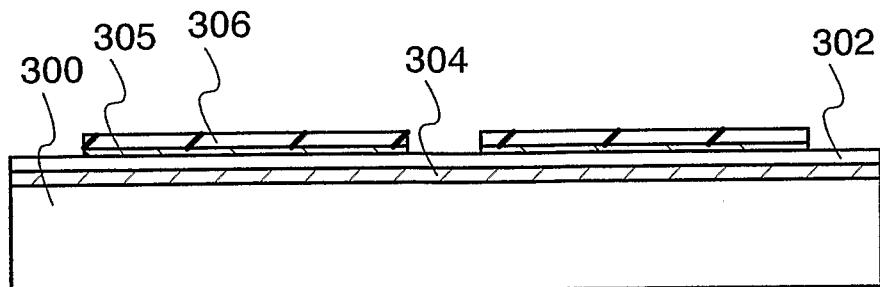

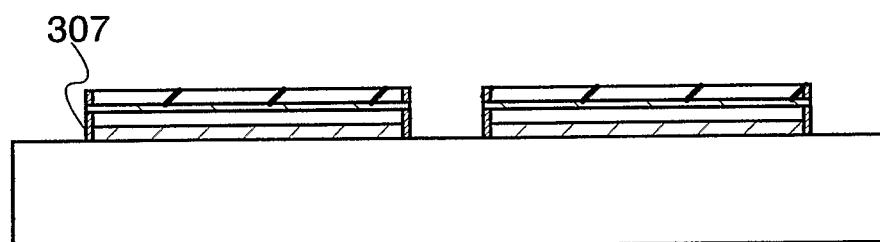

20 FIGS. 2A and 2B are cross-sectional views showing examples of structures of an SOI substrate according to the present invention;

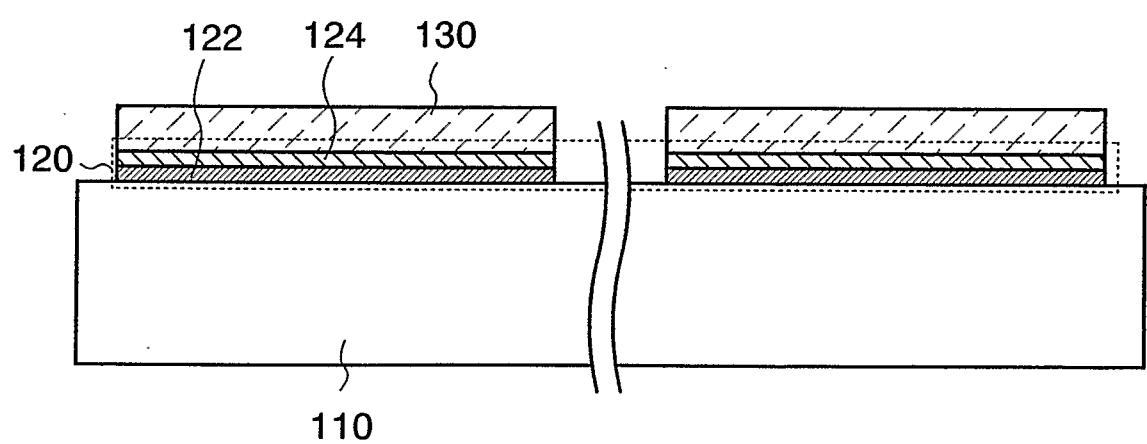

FIGS. 3A and 3B are cross-sectional views showing examples of structures of an SOI substrate according to the present invention;

FIGS. 4A to 4C are cross-sectional views showing an example of a method for manufacturing an SOI substrate according to the present invention;

25 FIGS. 5A and 5B are cross-sectional views showing an example of a method for manufacturing an SOI substrate according to the present invention;

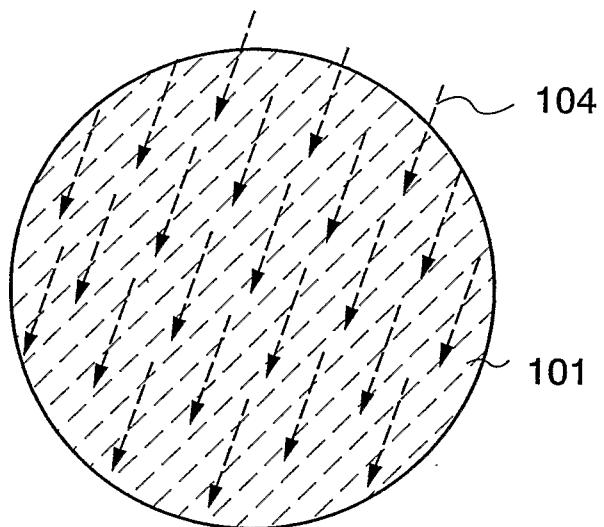

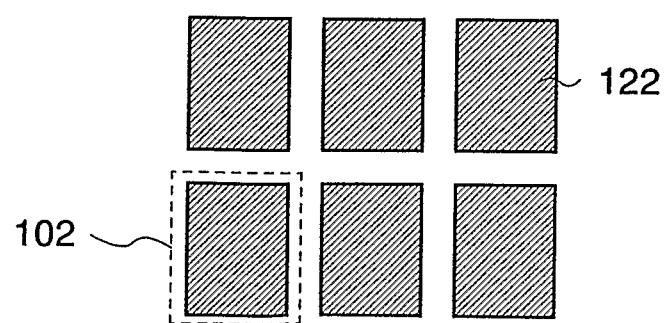

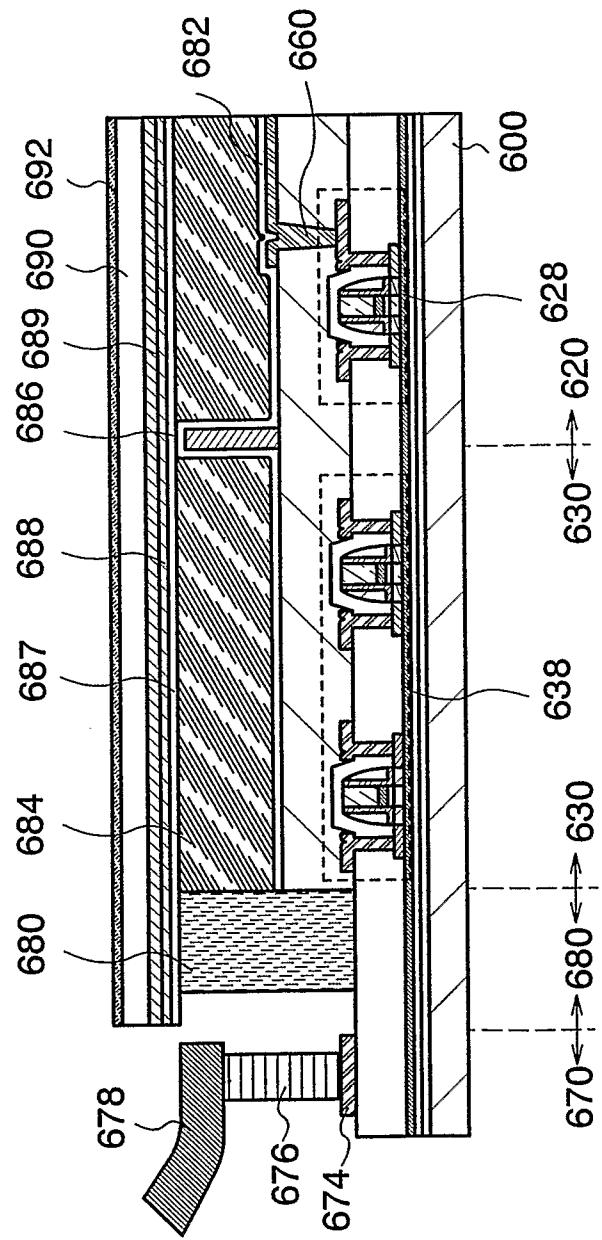

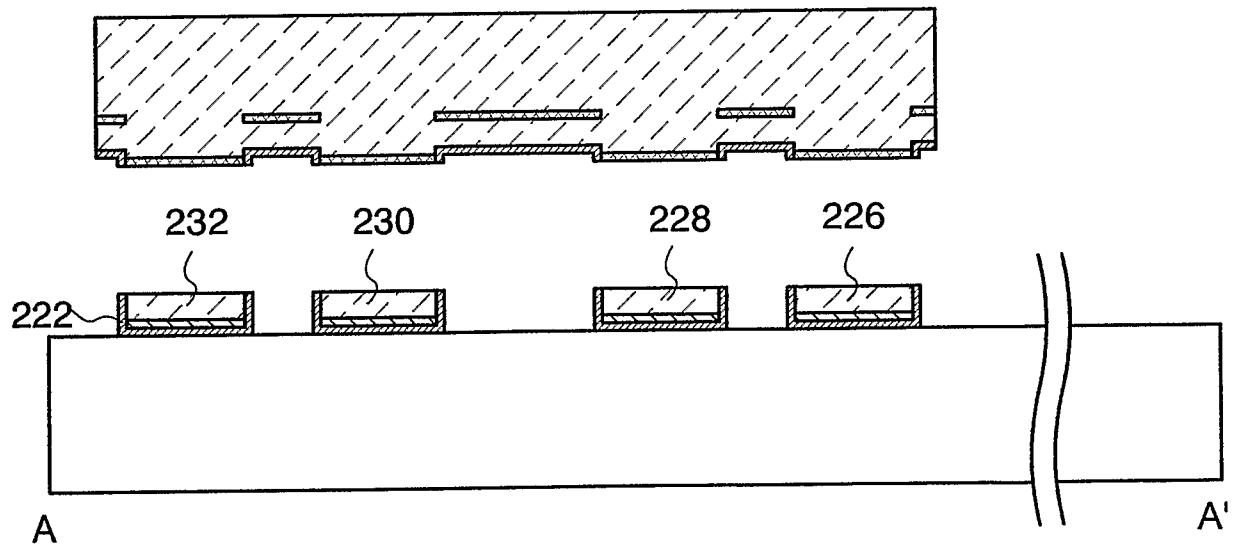

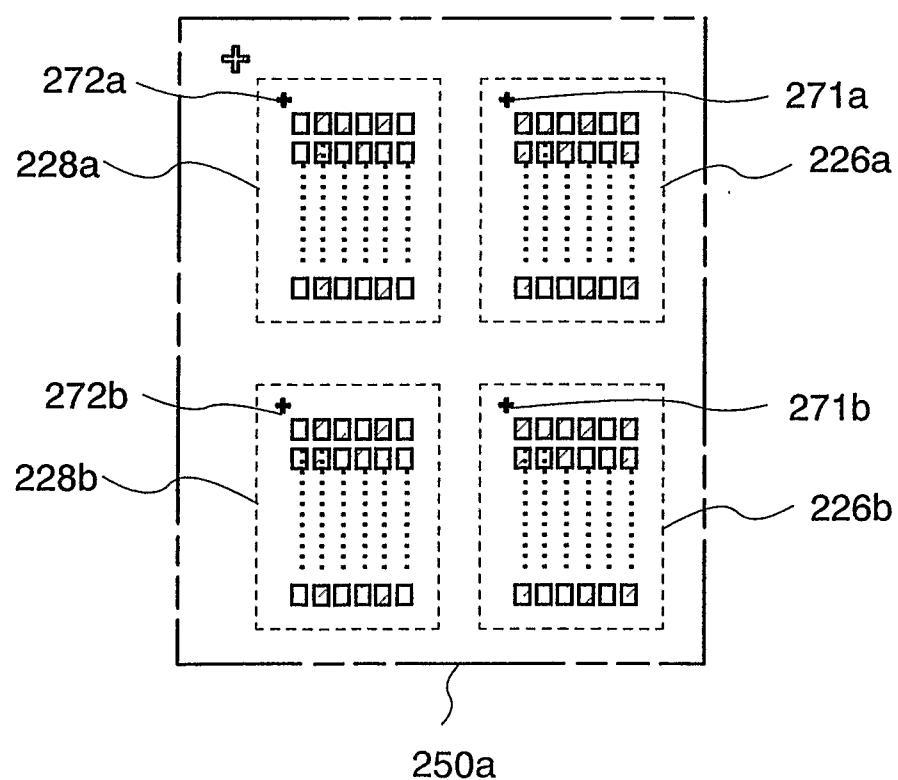

FIGS. 6A to 6C are top views showing an example of a method for manufacturing an SOI substrate according to the present invention;

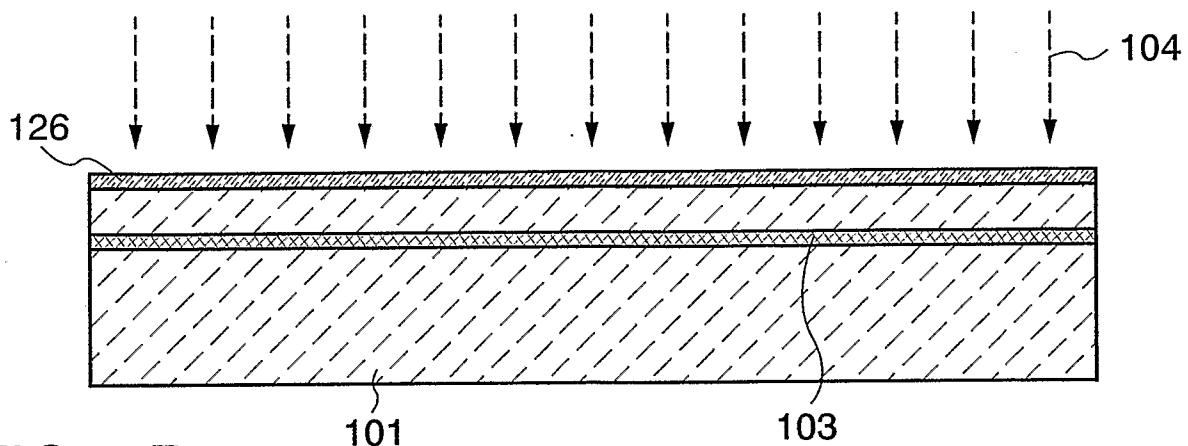

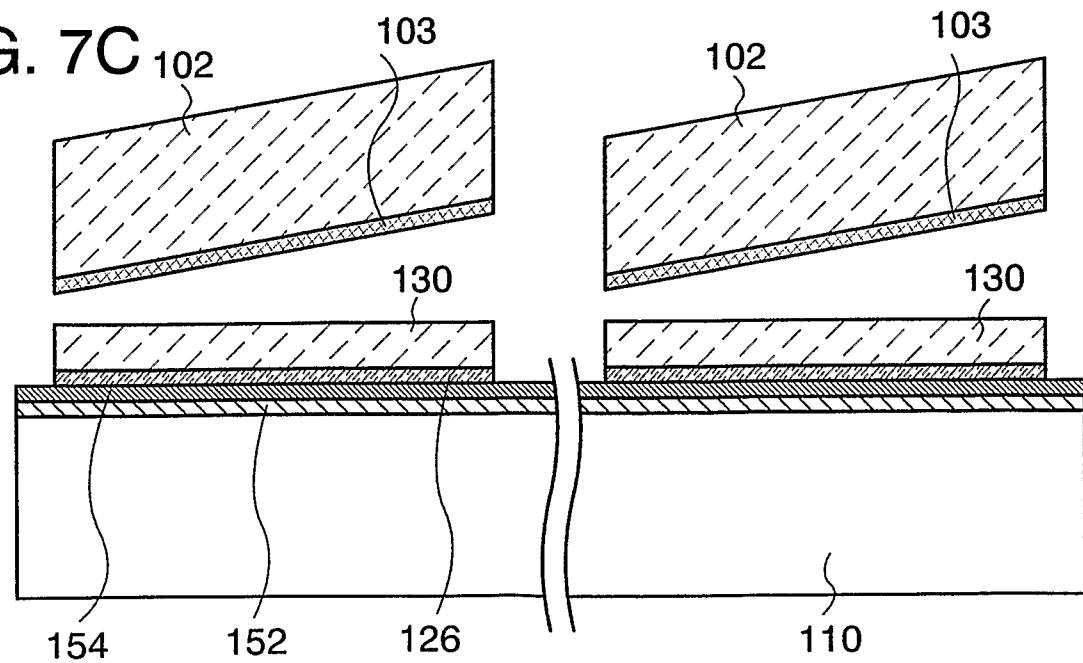

30 FIGS. 7A to 7C are cross-sectional views showing an example of a method for manufacturing an SOI substrate according to the present invention;

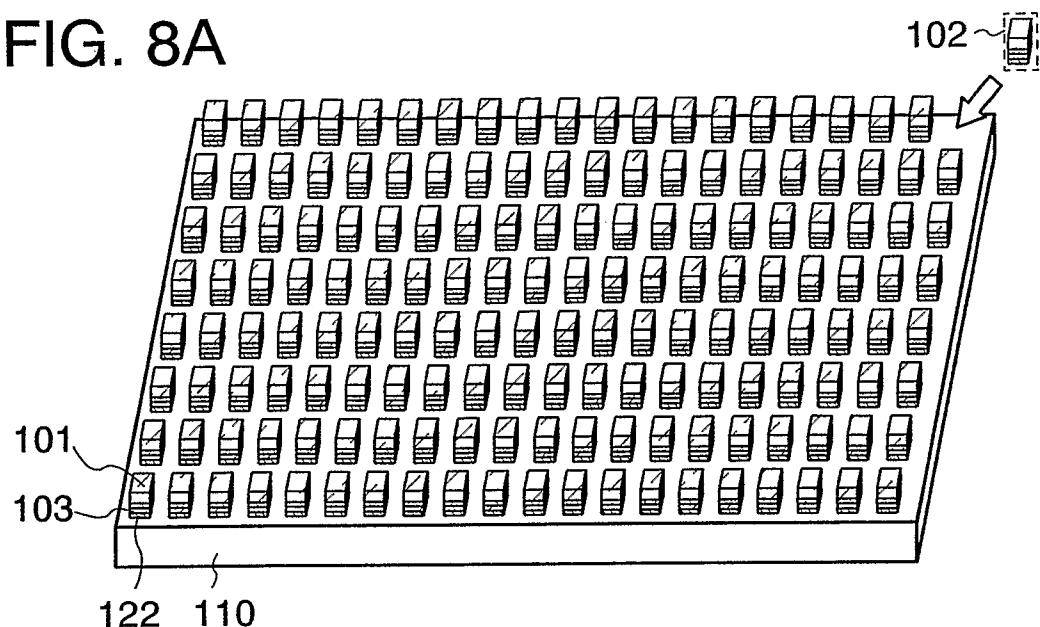

FIGS. 8A and 8B are perspective views showing an example of a method for manufacturing an SOI substrate according to the present invention;

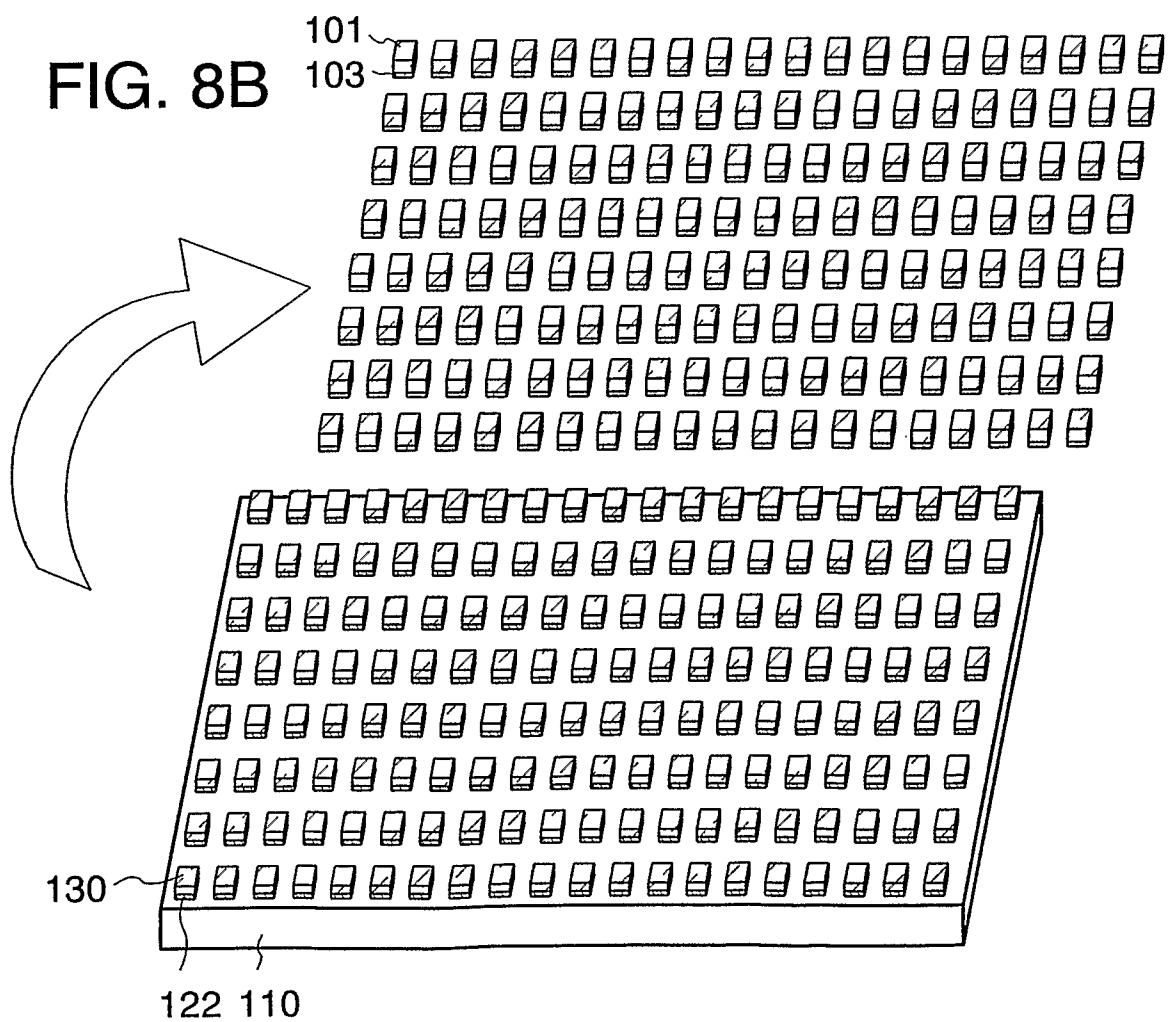

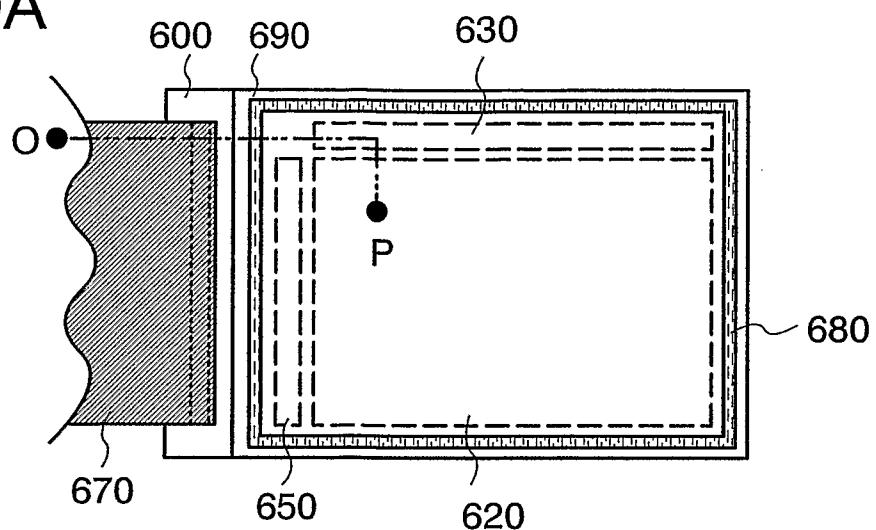

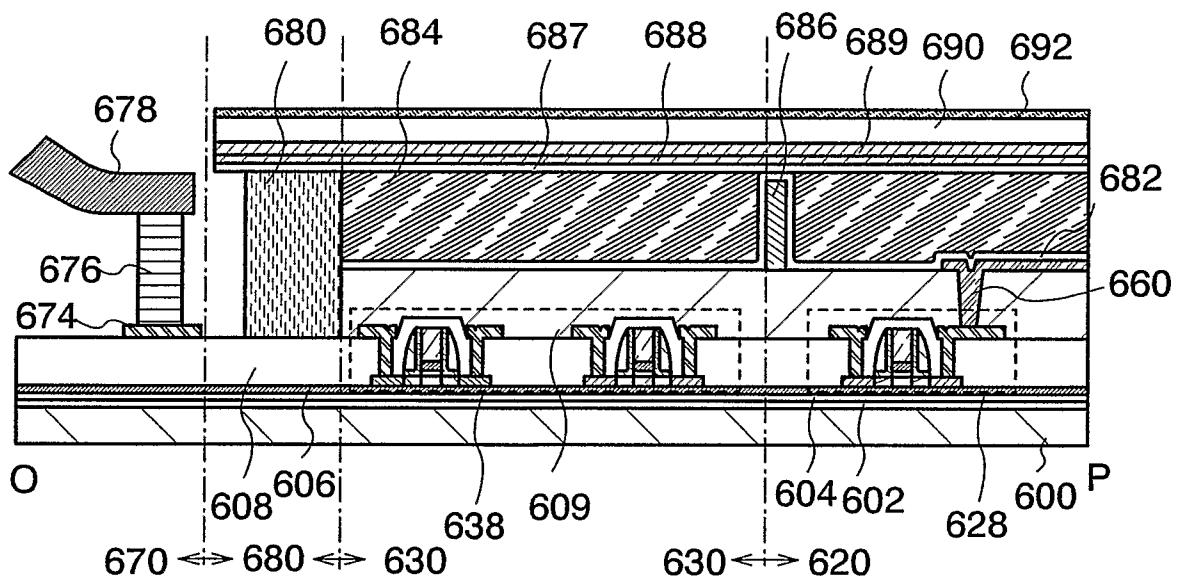

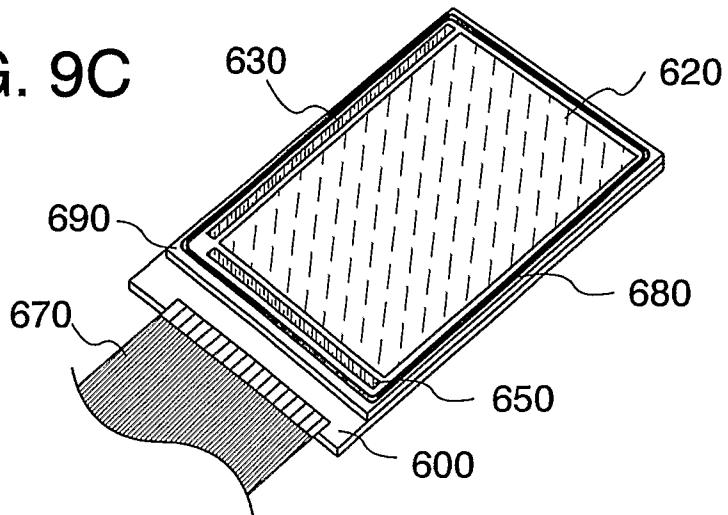

FIGS. 9A to 9C are a top view, a cross-sectional view, and a perspective view, respectively, showing an example of a display device according to the present invention;

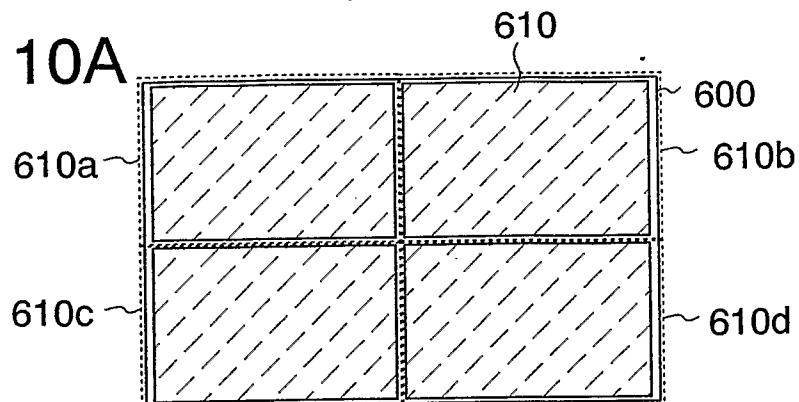

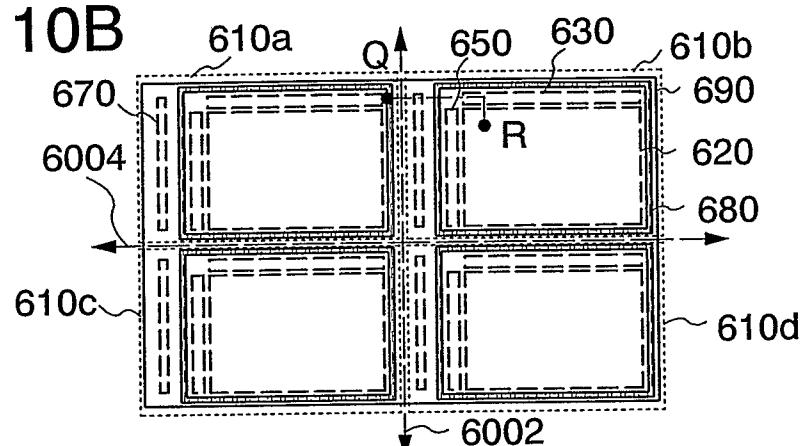

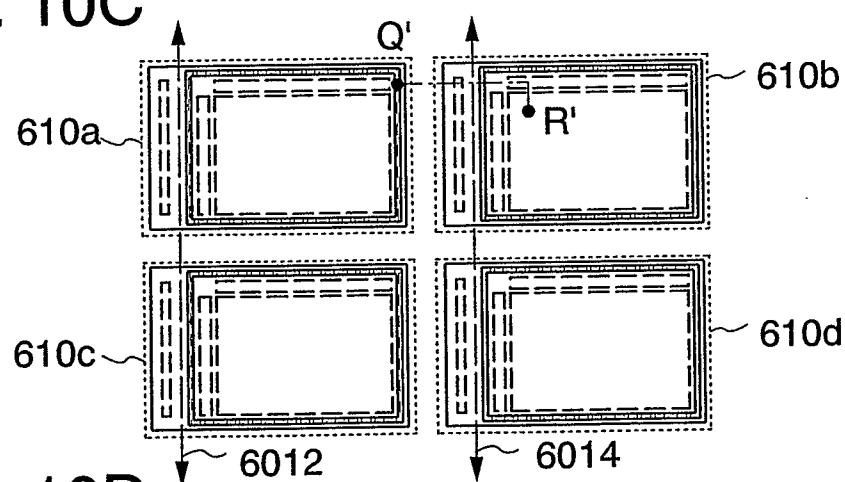

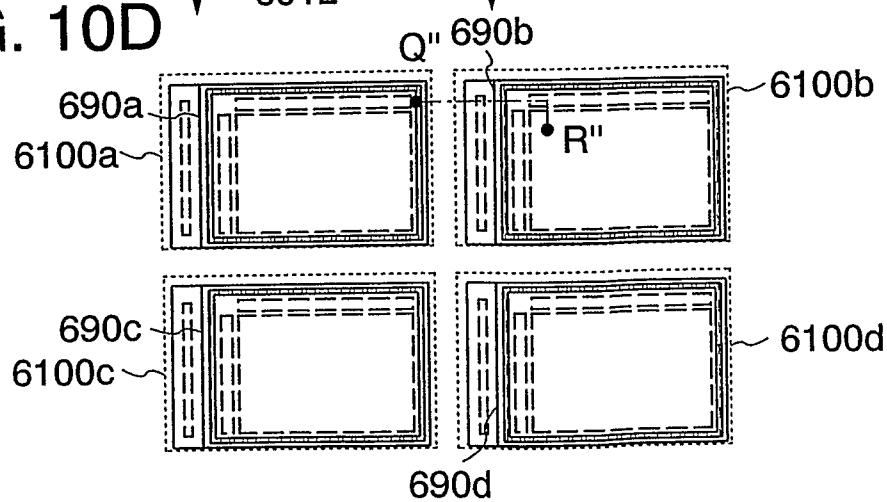

FIGS. 10A to 10D are top views showing an example of a method for manufacturing a display device according to the present invention;

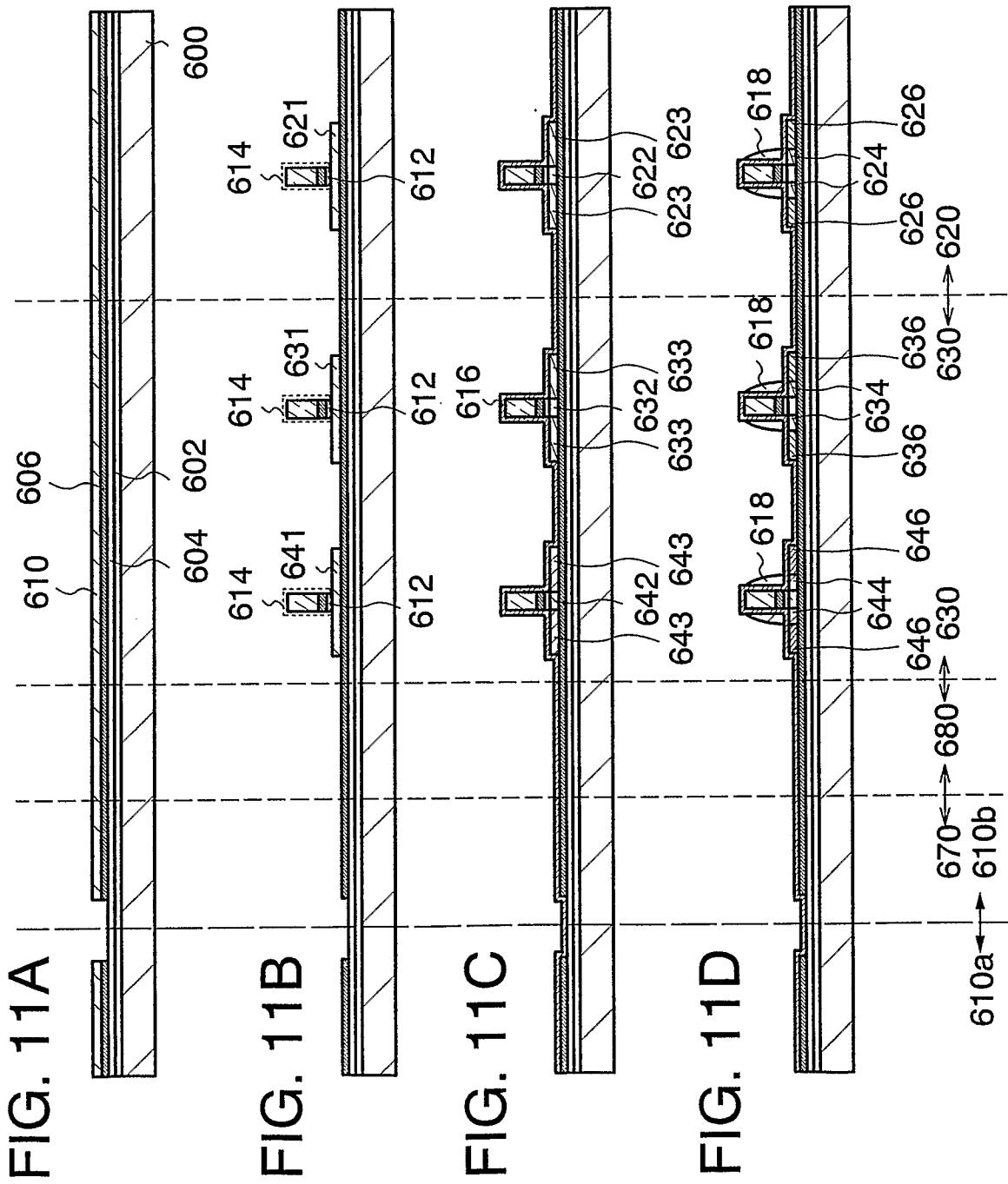

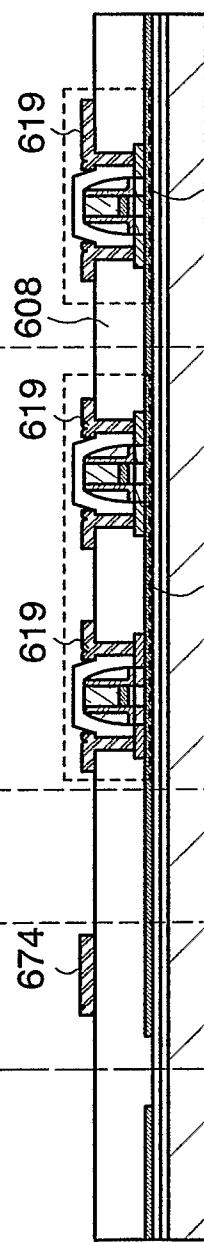

5 FIGS. 11A to 11D are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

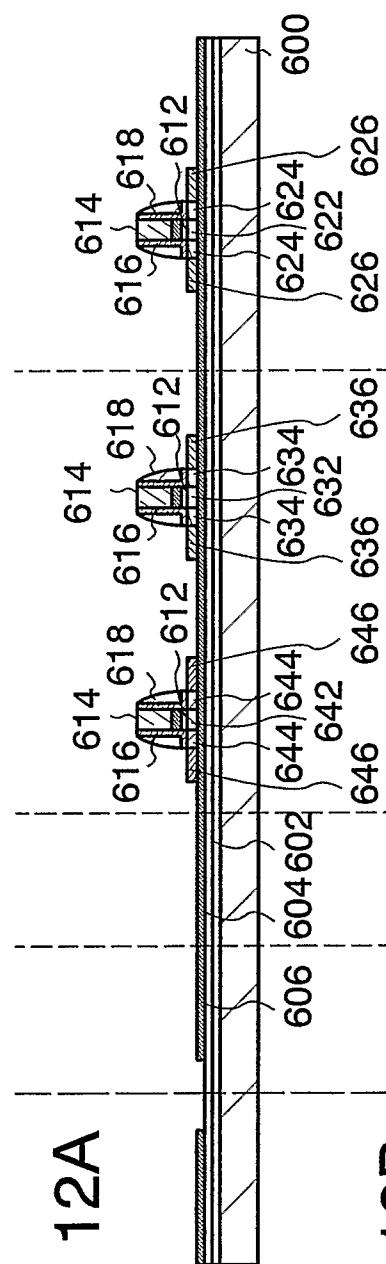

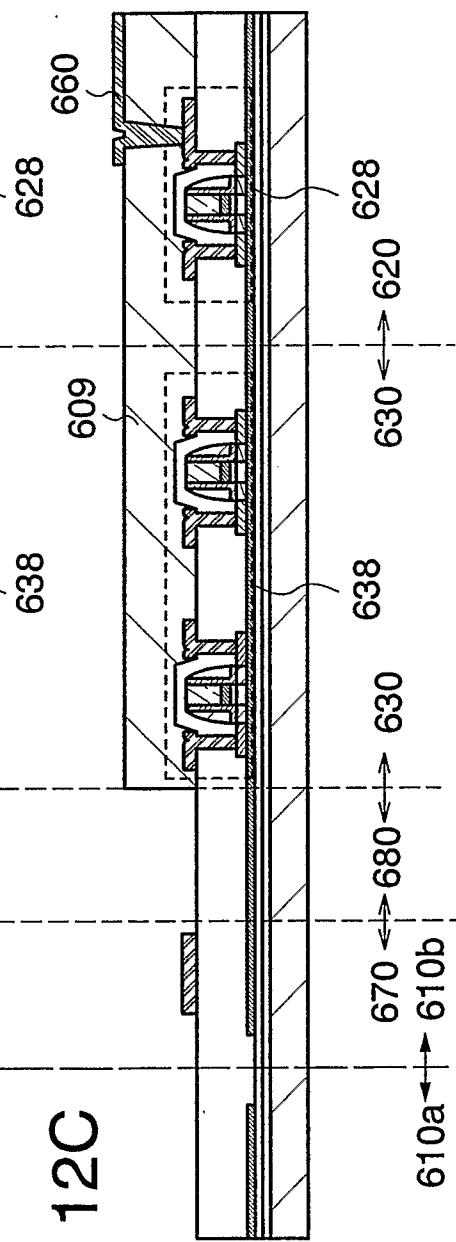

FIGS. 12A to 12C are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

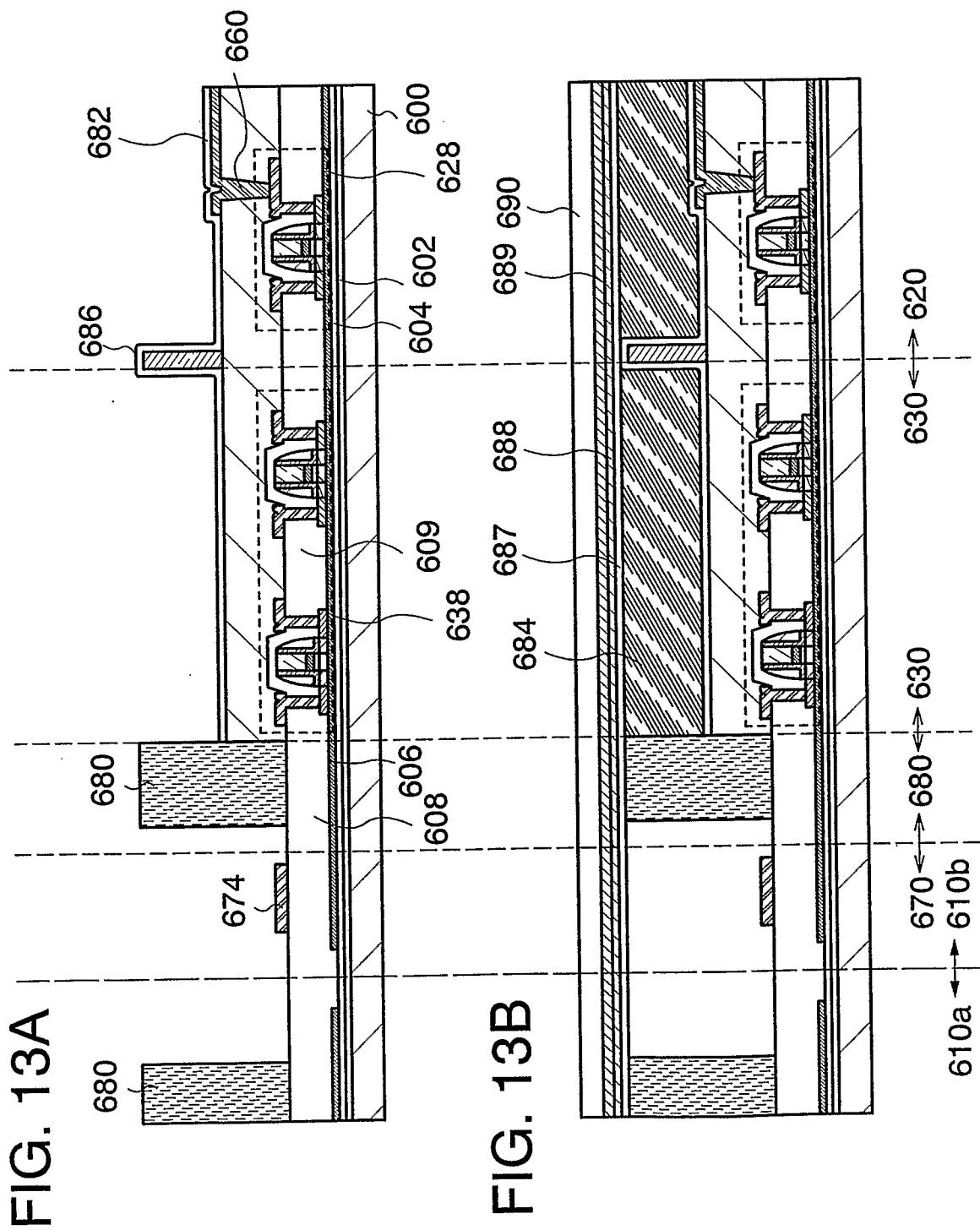

10 FIGS. 13A and 13B are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

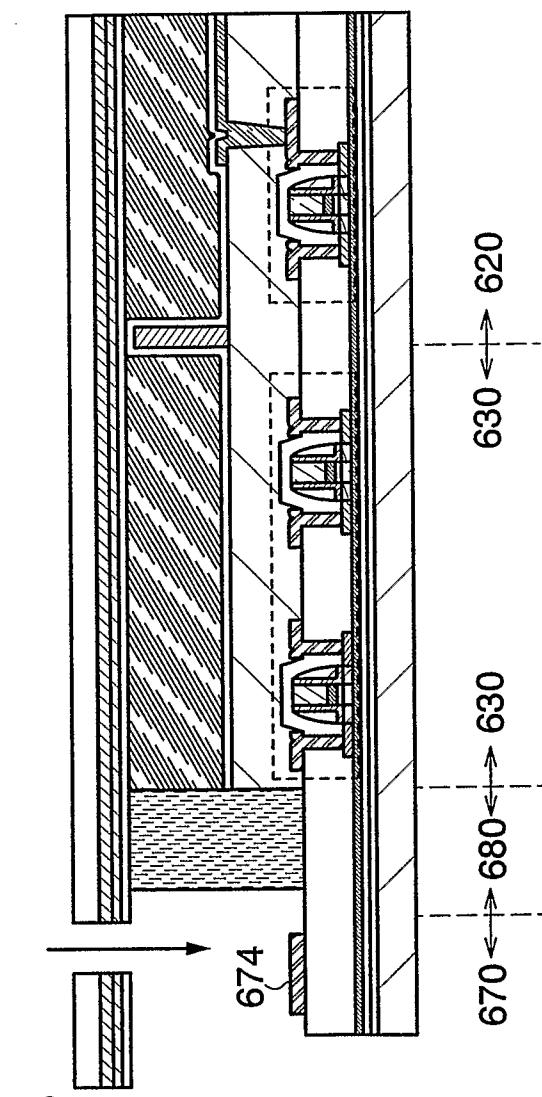

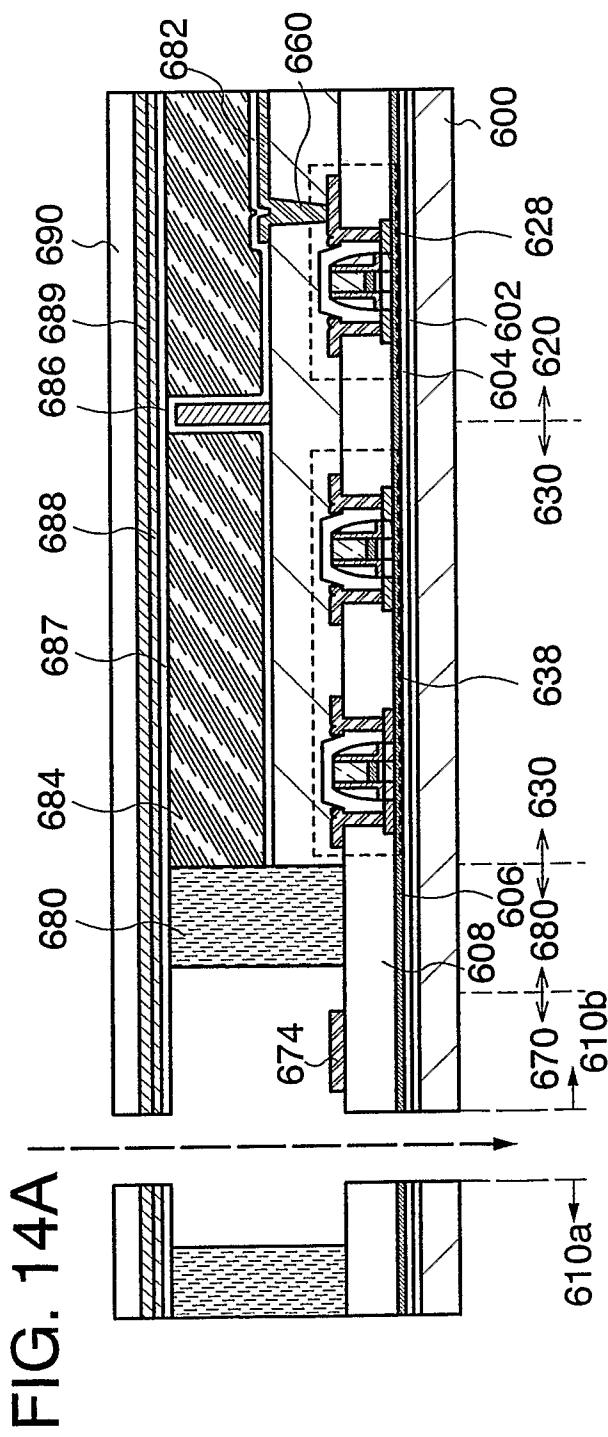

FIGS. 14A and 14B are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

FIG. 15 is a cross-sectional view showing an example of a method for manufacturing a display device according to the present invention;

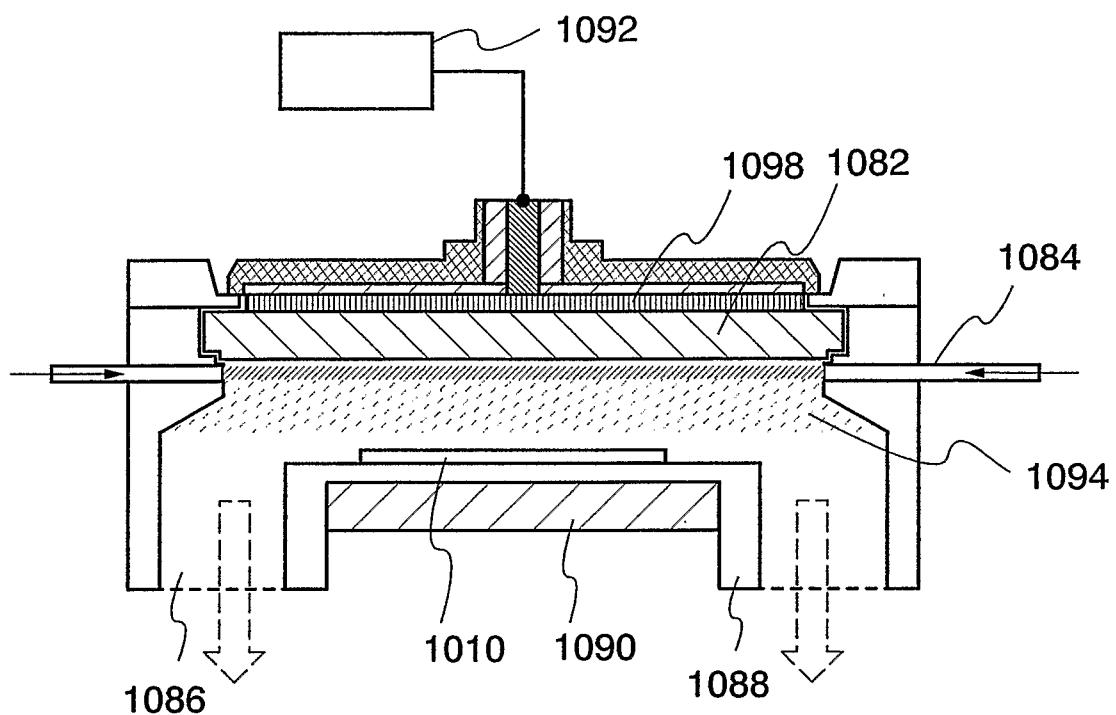

15 FIG. 16 is a diagram showing a structural example of a plasma process apparatus;

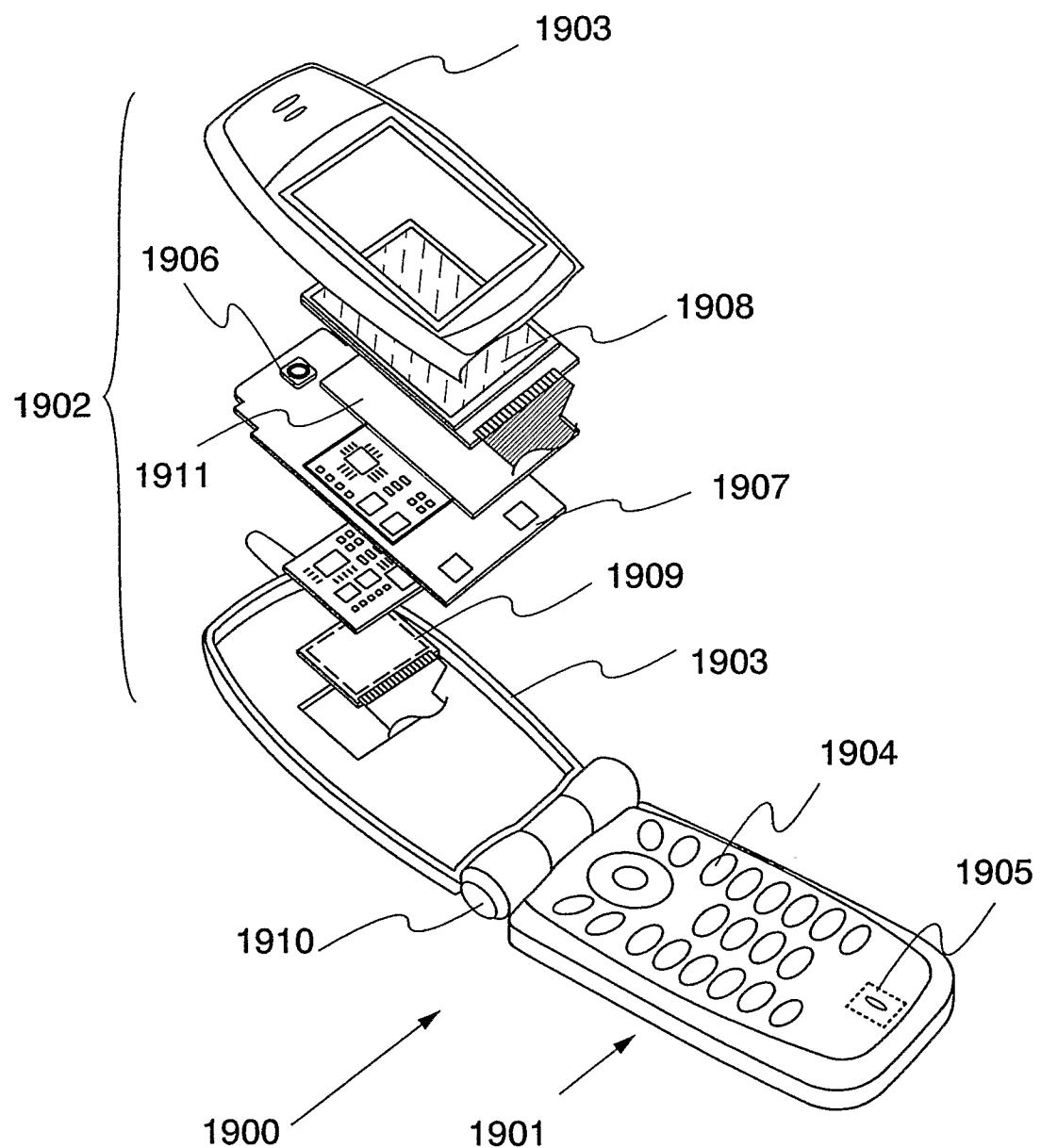

FIG. 17 is an exploded view showing an example of a display device according to the present invention;

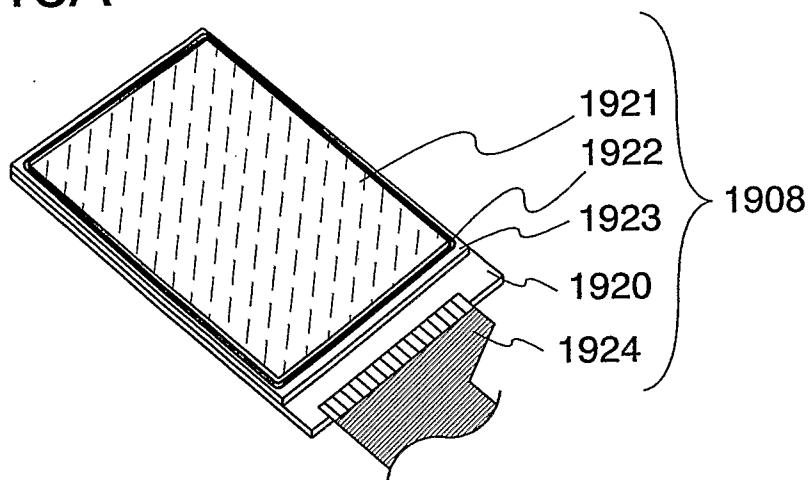

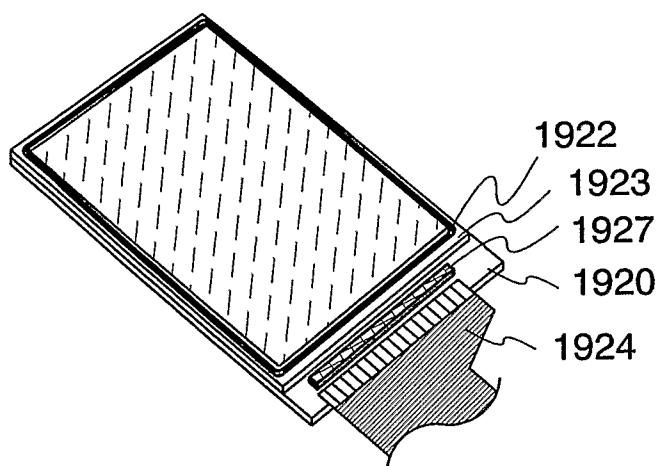

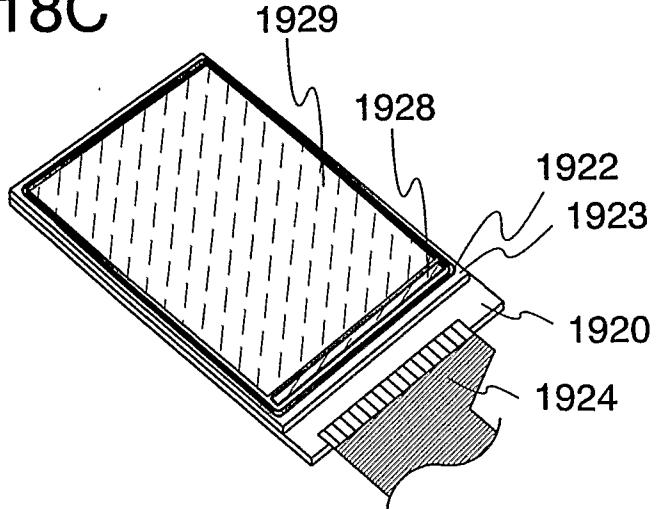

20 FIGS. 18A to 18C are perspective views showing an example of a display device according to the present invention;

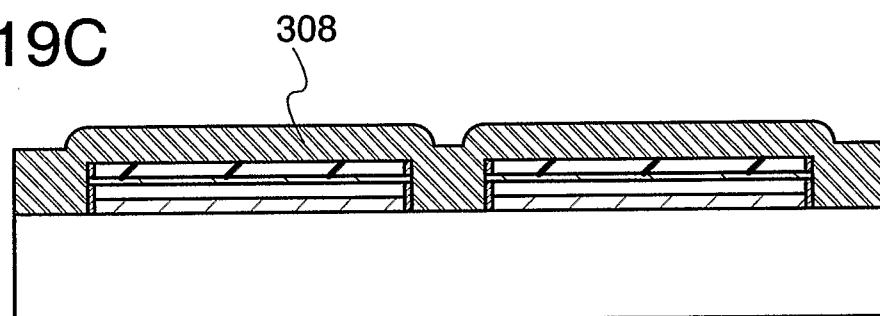

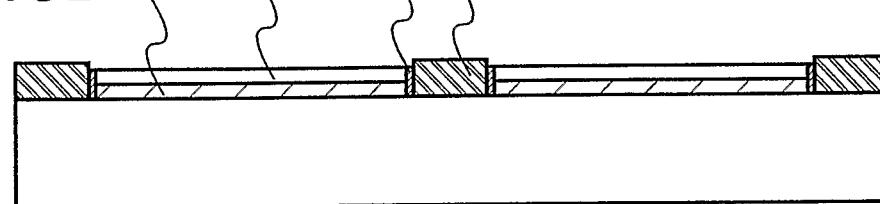

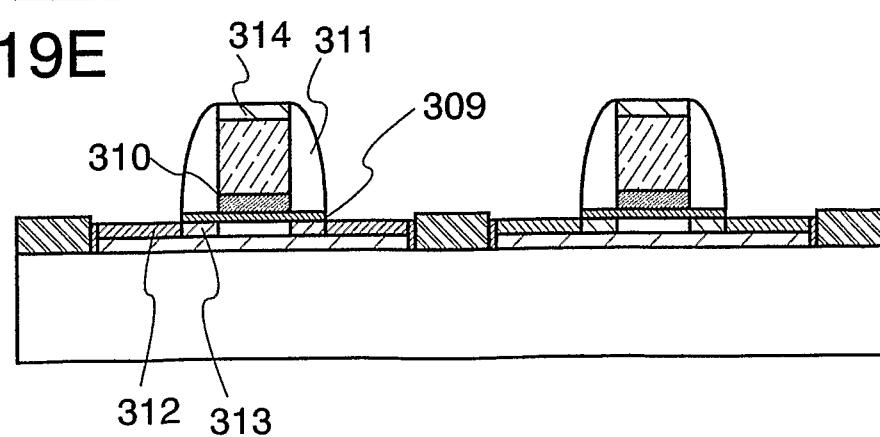

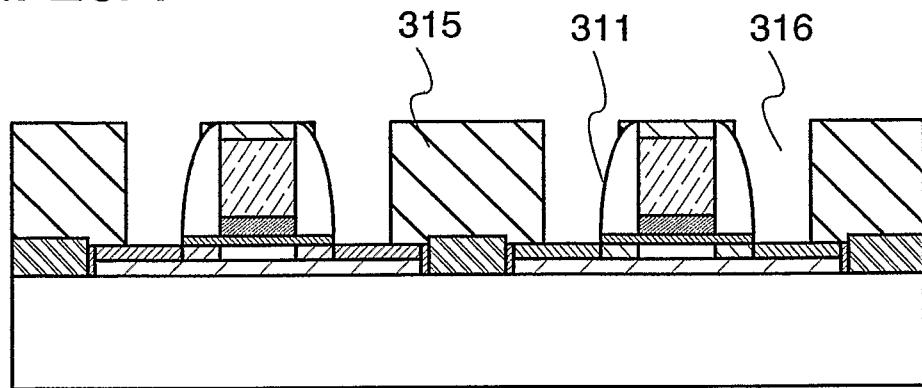

FIGS. 19A and 19E are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

FIGS. 20A and 20B are cross-sectional views showing an example of a method for manufacturing a display device according to the present invention;

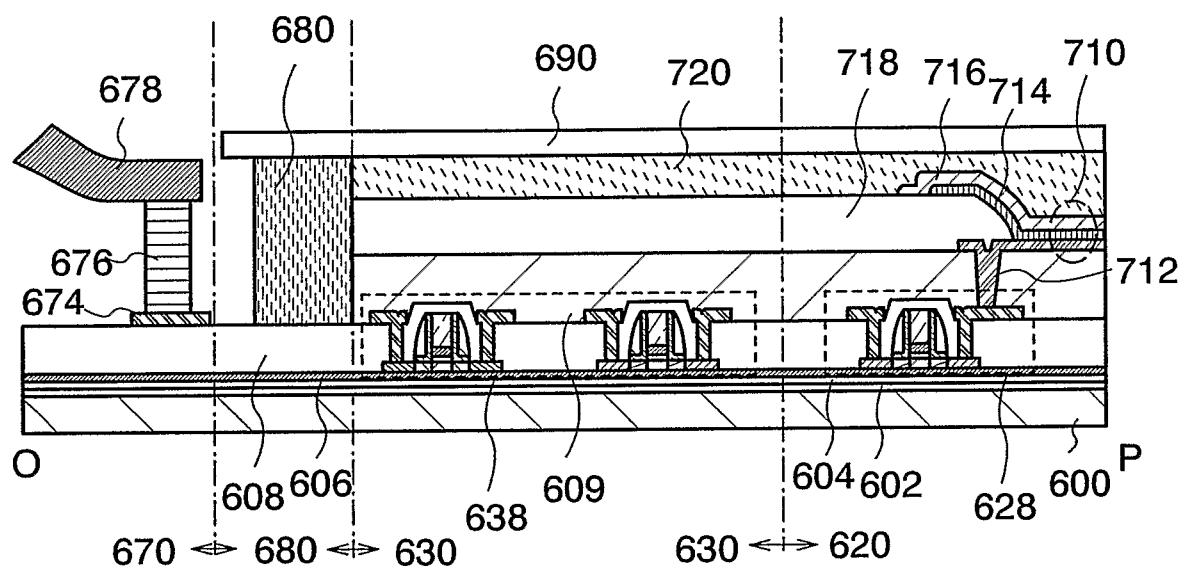

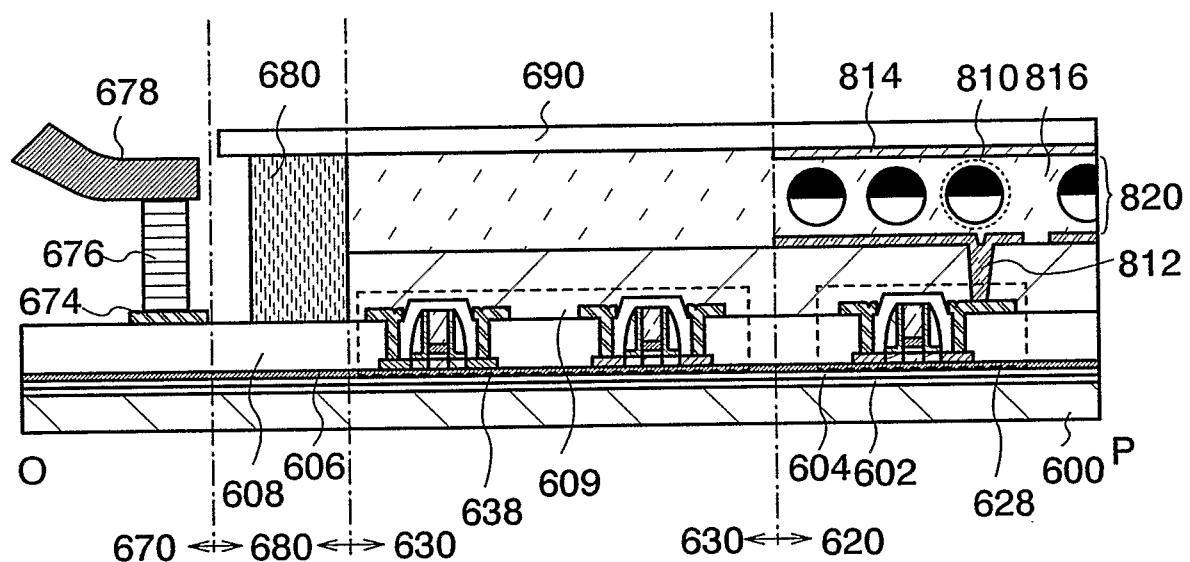

25 FIG. 21 is a cross-sectional view showing an example of a display device according to the present invention;

FIG. 22 is a cross-sectional view showing an example of a display device according to the present invention;

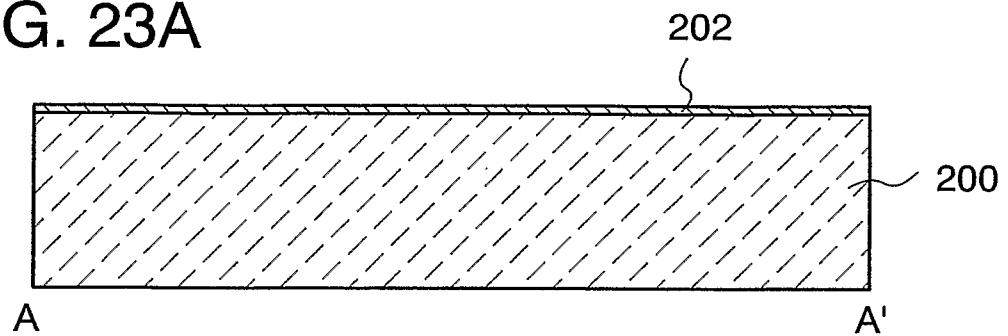

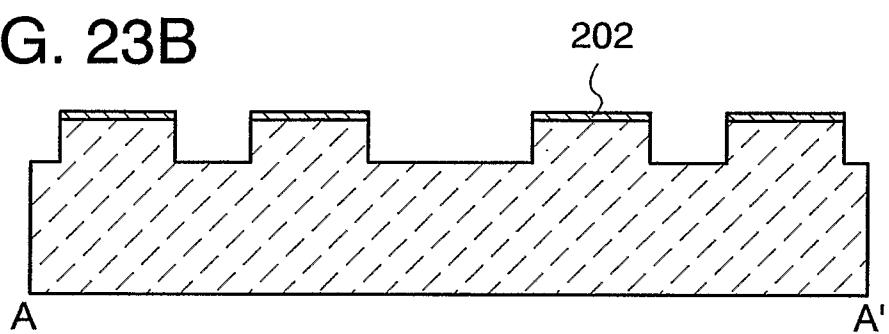

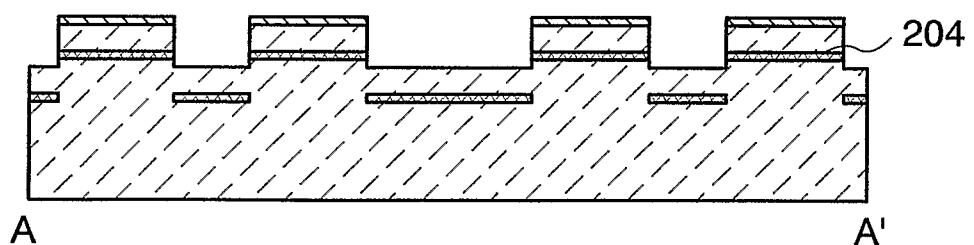

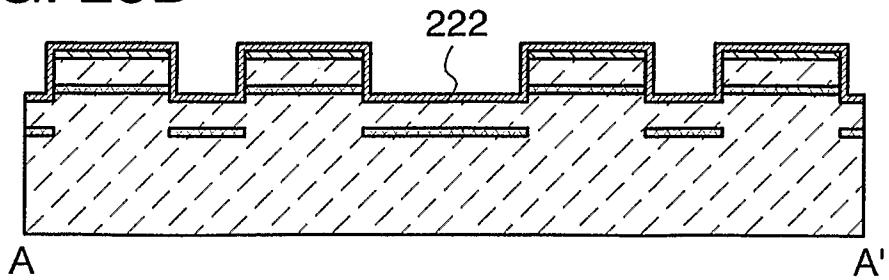

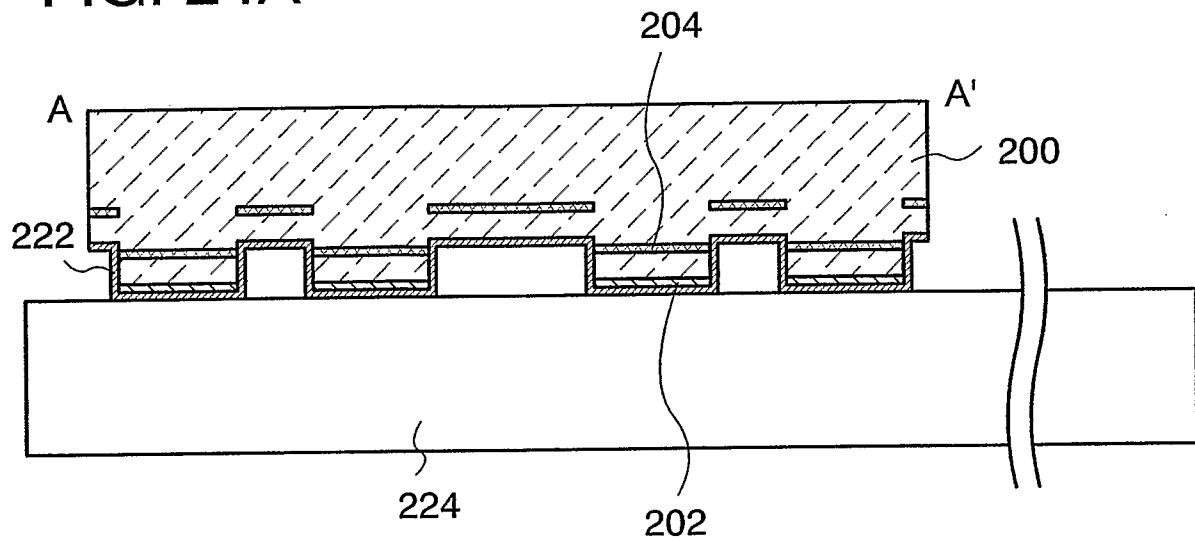

30 FIGS. 23A to 23D are cross-sectional views showing an example of a method for manufacturing an SOI substrate according to the present invention;

FIGS. 24A and 24B are cross-sectional views showing an example of a method for manufacturing an SOI substrate according to the present invention;

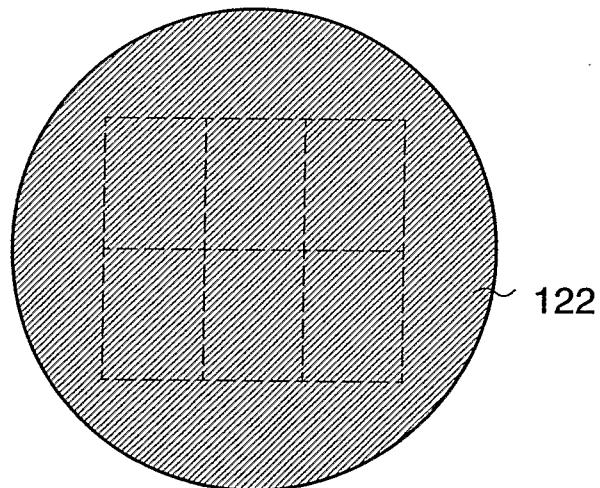

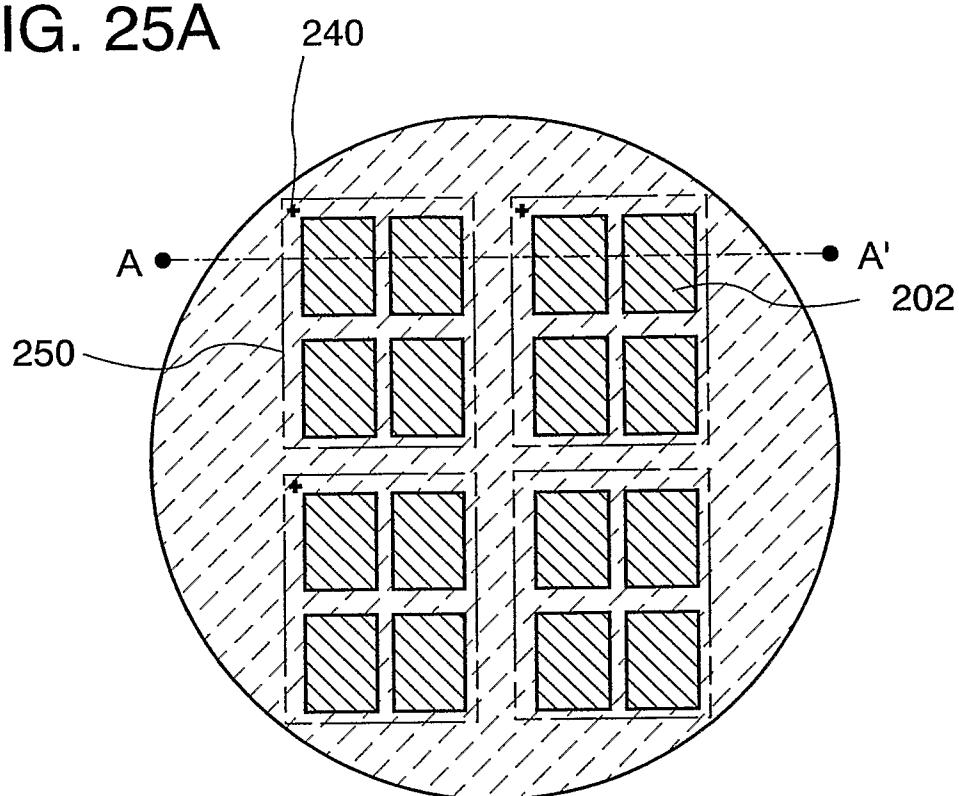

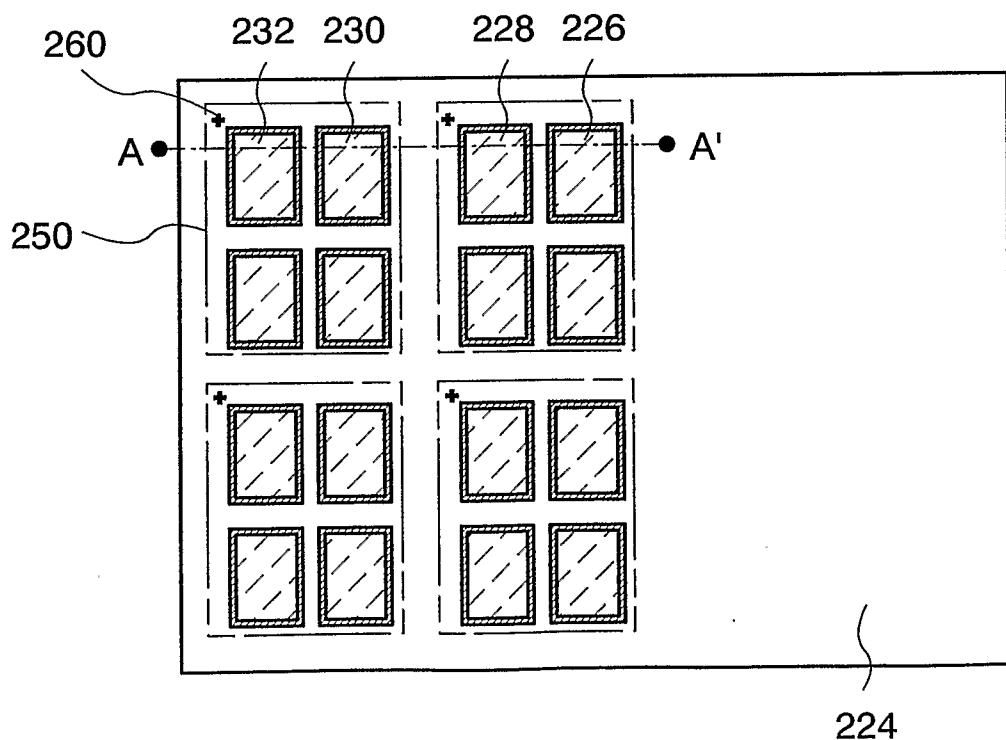

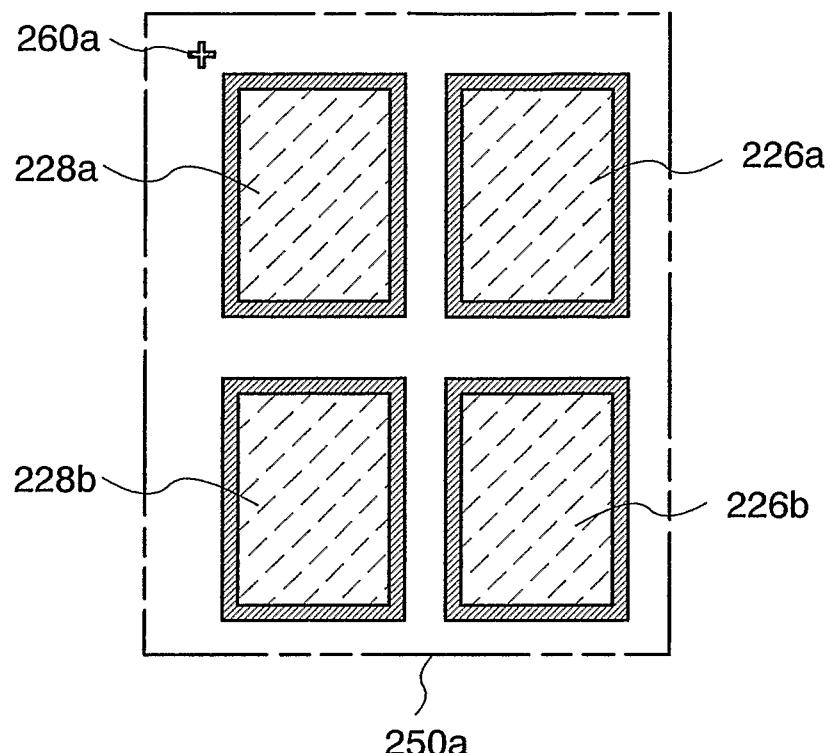

FIGS. 25A and 25B are top views showing an example of an SOI substrate according to the present invention; and

FIGS. 26A and 26B are top views showing an example of an SOI substrate according to the present invention.

5

## BEST MODE FOR CARRYING OUT THE INVENTION

### Embodiment Modes

[0019]

Hereinafter, embodiment modes of the present invention are described in detail with reference to the drawings. Note that the present invention is not limited to the following description, and it is easily understood by those skilled in the art that the modes and details disclosed herein can be modified in various ways without departing from the spirit and scope of the present invention. Therefore, the present invention should not be interpreted as being limited to the description of the embodiment modes to be given below. In the structures of the present invention to be described hereinafter, a reference numeral which designates the same parts is used in different drawings in some cases.

[0020]

(Embodiment Mode 1)

An SOI substrate according to this embodiment mode is formed by transferring single-crystalline semiconductor layers from a single-crystalline semiconductor substrate to a substrate of a different type (hereinafter, also referred to as a "base substrate"). Hereinafter, an SOI substrate according to this embodiment mode and an embodiment mode of a method for manufacturing the SOI substrate are described.

25 [0021]

FIGS. 1A and 1B show perspective views showing structural examples of an SOI substrate according to the present invention. Further, FIGS. 2A to 3B show cross-sectional views of examples of an SOI substrate according to the present invention.

30 [0022]

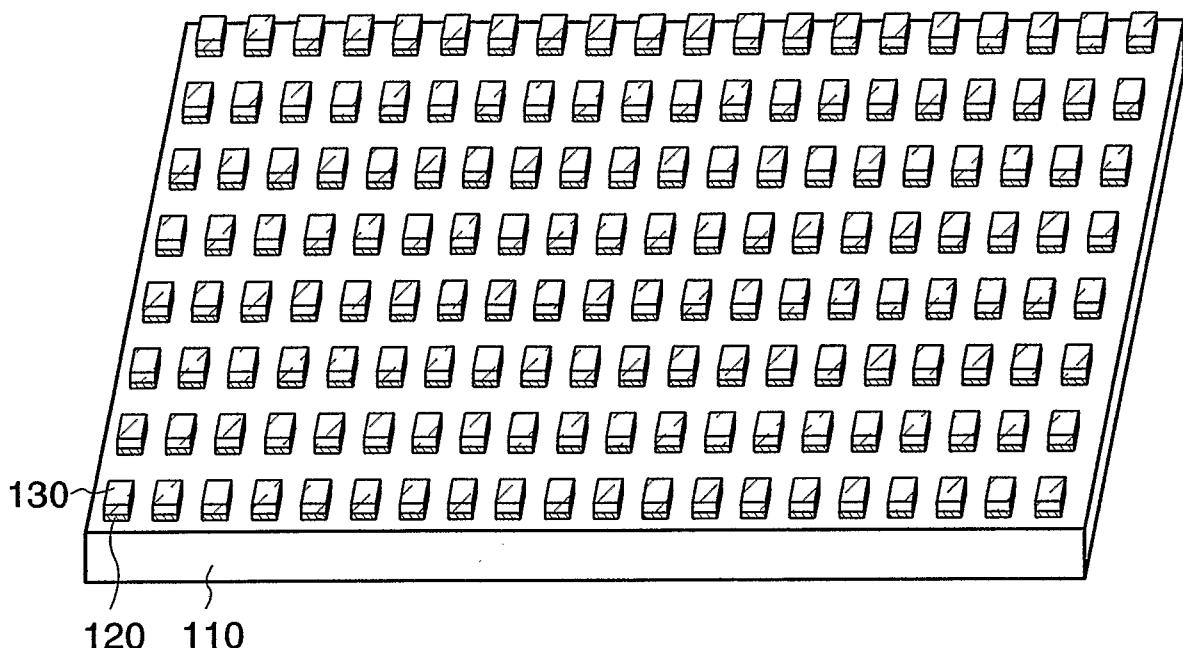

In FIGS. 1A, 2A, and 2B, an SOI substrate 100 has a structure in which a plurality of layered bodies in which an insulating layer 120 and a single-crystalline

semiconductor layer (hereinafter, also referred to as an SOI layer) 130 are stacked in this order are provided over a surface of a base substrate 110. The SOI layer 130 is provided over the base substrate 110 with the insulating layer 120 interposed therebetween, and constitutes what is called an "SOI structure". That is, a plurality of 5 SOI layers 130 are provided over one base substrate 110, and constitute one SOI substrate 100. FIGS. 2A and 2B show examples in which two SOI layers 130 are provided over one base substrate 110 for the sake of convenience.

[0023]

The SOI layer 130 is a single-crystalline semiconductor, and single-crystalline 10 silicon is typically applied thereto. Alternatively, a crystalline semiconductor layer of silicon, germanium, a compound semiconductor such as gallium arsenide or indium phosphide, or the like, which can be separated from a single-crystalline semiconductor substrate or a polycrystalline semiconductor substrate by a hydrogen ion implanting separation method, can also be applied.

15 [0024]

A feature of an SOI substrate according to the present invention is that a size of 20 the SOI layer 130 that constitutes the SOI substrate is a desired panel size. The SOI layer 130 is divided into sections each having an area including one panel, which is the desired panel size. In this specification, a "panel size" designates a size of a peripheral frame portion (non-display portion) of a display panel in addition to a display portion. Further, a "size" designates an area. In an SOI substrate according to the present 25 invention, the plurality of SOI layers 130 obtained by dividing a semiconductor substrate into sections each having an area including one panel, which is the desired panel size, are bonded to the base substrate 110 with the insulating layers 120 interposed therebetween.

[0025]

The panel size may be appropriately determined depending on the usage, and for example, a small to medium panel size of a diagonal line of 10 in. or less can be employed. With respect to a mobile phone, which has a small to medium panel, 30 known sizes (screen sizes) of a display portion are diagonal lines of 2.2 in. (56 mm), 2.4 in. (61 mm), and 2.6 in. (66 mm), for example; when a mobile phone has the above panel size, the panel size may be determined in consideration of a size of a frame

portion (screen frame size) around a display portion in addition to a screen size.

[0026]

Although the shape of the SOI layer 130 is not particularly limited, a rectangular shape (including a square), which enables easier processing and bonding of the SOI layer 130 to the base substrate 110 with a high integration degree, is preferable. When the SOI layer 130 is used for a panel of a display device, it is preferable that the SOI layer 130 have an aspect ratio of 4:3. By making the SOI layer 130 have a desired area including one panel, i.e., a size which is about equal to a desired panel size, it is possible to control a yield on a panel-to-panel basis in manufacturing a variety of display devices by incorporating a display panel manufactured using an SOI substrate completed. Further, damage to elements can be prevented in dividing a panel from each other. Therefore, a yield can be improved. By making the SOI layer 130 have a desired area including one panel, i.e., a size which is about equal to a desired panel size, the element of each panel can be formed using one SOI layer, and thus variation in characteristics can be suppressed.

[0027]

A substrate having an insulating surface or an insulating substrate is used for the base substrate 110. Concretely, a variety of glass substrates used for electronic industries (e.g. aluminosilicate glass, aluminoborosilicate glass, or barium borosilicate glass), a quartz substrate, a ceramic substrate, or a sapphire substrate can be given as an example. It is preferable to use a glass substrate for the base substrate 110: for example, a large-sized mother glass called “the sixth generation” (1500 mm × 1850 mm), “the seventh generation” (1870 mm × 2200 mm), or the “eighth generation” (2200 mm × 2400 mm) is used. By using a large-sized mother glass for the base substrate 110 and manufacturing an SOI substrate with application of the present invention, the SOI substrate can have a large area. In the SOI substrate formed by bonding a plurality of SOI layers obtained by dividing a semiconductor substrate into sections each having an area including one panel, specifically, a desired panel size, to a base substrate having an insulating surface, with an insulating layer interposed therebetween, each SOI layer has a desired panel size; thus, the number of display panels that can be manufactured using one base substrate can be increased. Therefore, productivity of

end products (display devices) manufactured with the display device incorporated therein can be improved.

[0028]

The insulating layer 120 is provided between the base substrate 110 and the 5 SOI layer 130. The insulating layer 120 may have a single-layer structure or a stacked-layer structure. A surface bonded to the base substrate 110 (hereinafter, also referred to as a “bonding surface”) is smooth and hydrophilic. In this description, hereinafter, a layer formed on a bonding surface is also referred to as a “bonding layer.” FIG. 2A shows an example in which a bonding layer 122 is formed as the insulating 10 layer 120. A silicon oxide layer is suitable for the bonding layer 122 that has a smooth surface and can form a hydrophilic surface. In particular, a silicon oxide layer which is made by a chemical vapor deposition method using organic silane as a source gas is preferable. As the organic silane, a compound containing silicon such as tetraethoxysilane (abbr.: TEOS; chemical formula:  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ), tetramethylsilane 15 (abbr.: TMS; chemical formula:  $\text{Si}(\text{CH}_3)_4$ ), trimethylsilane (chemical formula:  $(\text{CH}_3)_3\text{SiH}$ ), tetramethylcyclotetrasiloxane (abbr.: TMCTS), octamethylcyclotetrasiloxane (abbr.: OMCTS), hexamethyldisilazane (abbr.: HMDS), triethoxysilane (chemical formula:  $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ), or tridimethylaminosilane (chemical formula:  $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) can be used.

20 [0029]

It is preferable that the bonding layer 122 that has a smooth surface and forms a hydrophilic surface have a thickness of 5 to 500 nm inclusive. By making the bonding 25 layer 122 have a thickness within the above range, it is possible to smooth a rough film formation surface and ensure smoothness of a developing surface of the bonding layer 122. Further, a distortion between the bonding layer 122 and a substrate bonded thereto (in FIG. 2A, the base substrate 110) can be relieved. A silicon oxide layer similar to the bonding layer 122 may further be provided for the base substrate 110. With respect to the SOI substrate according to the present invention, in bonding the SOI 30 layer 130 to the base substrate 110, which is a substrate having an insulating surface or an insulating substrate, a bonding layer formed preferably of a silicon oxide layer formed using organic silane as a source gas is provided for either or both of the surfaces on which bonding is formed, whereby firm bonding can be formed.

## [0030]

FIG. 2B shows an example in which the insulating layer 120 has a stacked-layer structure: concretely, an example in which a stacked-layer structure including the bonding layer 122 and an insulating layer 124 containing nitrogen is formed as the insulating layer 120 is shown. The insulating layer 124 containing nitrogen is provided between the SOI layer 130 and the bonding layer 122 in order that the bonding layer 122 is formed on a bonding surface of the base substrate 110. The insulating layer 124 containing nitrogen is formed using a silicon nitride layer, a silicon nitride oxide layer, or a silicon oxynitride layer to have a single-layer structure or a stacked-layer structure. For example, the insulating layer 124 containing nitrogen can be formed by stacking a silicon oxynitride layer and then a silicon nitride oxide layer from the SOI layer 130 side. The bonding layer 122 is provided in order to form bonding with the base substrate 110. The insulating layer 124 containing nitrogen is preferably provided in order to prevent impurities such as movable ions or moisture from diffusing into the SOI layer 130 and thus contaminating the SOI layer 130.

## [0031]

Note that a silicon oxynitride layer means a film that contains more oxygen than nitrogen, and in the case where measurements are performed using Rutherford backscattering spectrometry (RBS) and hydrogen forward scattering (HFS), contains oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from 50 to 70 at.%, 0.5 to 15 at.%, 25 to 35 at.%, and 0.1 to 10 at.%, respectively. Further, a silicon nitride oxide layer means a film that contains more nitrogen than oxygen, and in the case where measurements are performed using RBS and HFS, contains oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from 5 to 30 at.%, 20 to 55 at.%, 25 to 35 at.%, and 10 to 30 at.%, respectively. Note that percentages of nitrogen, oxygen, silicon, and hydrogen fall within the ranges given above, where the total number of atoms contained in the silicon oxynitride layer or the silicon nitride oxide layer is defined as 100 at.%.

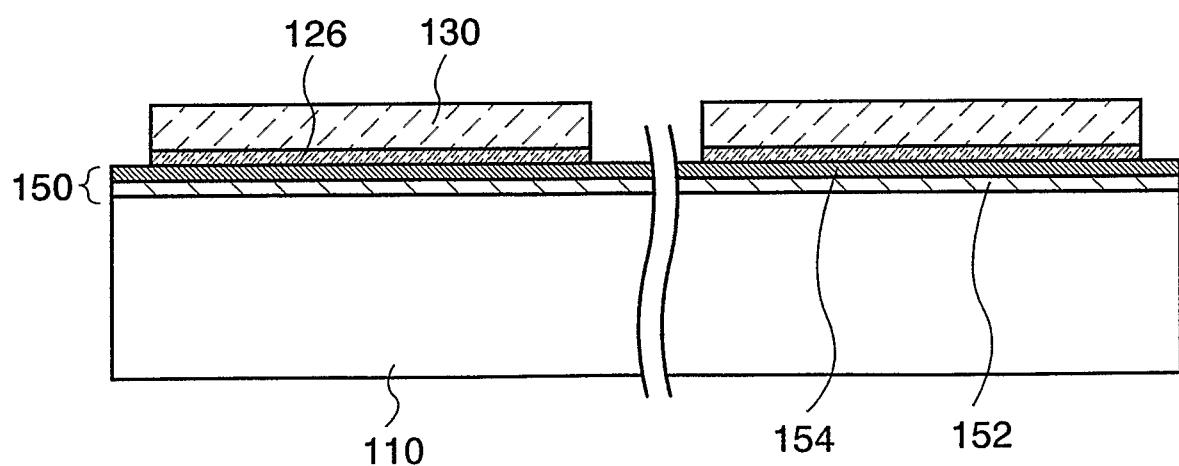

## [0032]

FIGS. 1B, 3A, and 3B show examples in which an insulating layer 150 including a bonding layer is provided for the base substrate 110. The insulating layer 150 may have a single-layer structure or a stacked-layer structure. A surface bonded to the SOI layer 130 is smooth and hydrophilic. It is preferable to provide a barrier layer

between the base substrate 110 and the bonding layer in order to prevent movable ions of an alkali metal, an alkaline earth metal, or the like from diffusing from the glass substrate used as the base substrate 110.

[0033]

5 FIG. 3A shows an example in which a stacked-layer structure including a barrier layer 152 and a bonding layer 154 is formed as the insulating layer 150. As the bonding layer 154, a silicon oxide layer similar to the bonding layer 122 may be provided. Further, a bonding layer may be provided for the SOI layer 130 as appropriate. FIG. 3A shows an example in which the bonding layer 122 is provided for 10 the SOI layer 130 as well. Such a structure can achieve firmer bonding because the bonding layers form the bonding in bonding the SOI layer 130 to the base substrate 110. The barrier layer 152 is formed using a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer, or a silicon nitride oxide layer to have a single-layer structure or 15 a stacked-layer structure. Preferably, the barrier layer 152 is formed using an insulating layer containing nitrogen.

[0034]

FIG. 3B shows an example in which a bonding layer is provided for the base substrate 110: concretely, an example in which a stacked-layer structure including the barrier layer 152 and the bonding layer 154 is provided as the insulating layer 150 on 20 the base substrate 110. Further, a silicon oxide layer 126 is provided for the SOI layer 130. In bonding the SOI layer 130 to the base substrate 110, the silicon oxide layer 126 forms bonding with the bonding layer 154. It is preferable to form the silicon oxide layer 126 by a thermal oxidation method. It is also possible to use a chemical oxide as the silicon oxide layer 126. A chemical oxide can be formed by, for example, 25 processing a surface of a semiconductor substrate with water containing ozone. A chemical oxide is preferable because it is formed reflecting planarity of a surface of a semiconductor substrate.

[0035]

Next, a method for manufacturing an SOI substrate according to the present 30 invention is described. Here, an example of a method for manufacturing the SOI substrate shown in FIG. 2A is described with reference to FIGS. 4A to 6C.

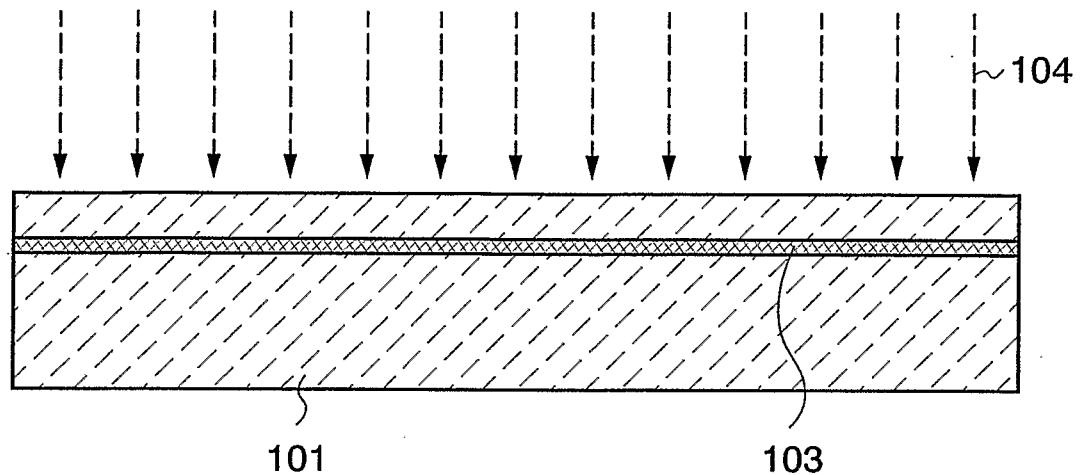

## [0036]

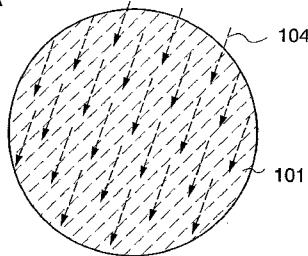

First, a semiconductor substrate 101 is prepared (see FIGS. 4A and 6A). As the semiconductor substrate 101, a commercial semiconductor substrate such as a single-crystalline semiconductor substrate or a polycrystalline semiconductor substrate 5 may be used: concretely, a semiconductor substrate (e.g. a silicon substrate or a germanium substrate) or a compound semiconductor (e.g. gallium arsenide or indium phosphide) substrate can be used. Typical sizes of the commercial silicon substrate are 5 in. (125 mm), 6 in. (150 mm), 8 in. (200 mm), and 12 in. (300 mm) in diameter, and most of the commercial silicon substrates are circular. Further, the film thickness can 10 be determined up to about 1.5 mm as appropriate.

## [0037]

Next, ions 104 accelerated by an electric field are implanted from a surface of the semiconductor substrate 101, so that an ion-doped layer 103 is formed in a region at a given depth (see FIGS. 4A and 6A). Note that in this description, ion implantation 15 means that a semiconductor substrate is irradiated with accelerated ions, so that an element that forms the ions for the irradiation is contained in a semiconductor substrate. Further, an ion-doped layer means a region that is weakened to have minute cavities by irradiating a semiconductor substrate with ions, and is referred to as a "separation layer," hereinafter. The semiconductor substrate is divided at the separation layer with 20 later heat treatment, so that an SOI layer can be formed over a base substrate. Irradiation with the ions 104 is performed in consideration of the thickness of an SOI layer that is transferred to a base substrate later. It is preferable that the SOI layer have a thickness of 5 to 500 nm inclusive, more preferably, 10 to 200 nm inclusive. The acceleration voltage and the dose of the ions in the ion irradiation are determined as 25 appropriate in consideration of the thickness of the SOI layer to be transferred. As the ions 104, ions of hydrogen, helium, or halogen such as fluorine can be used. As the ion 104, it is preferable to use an ion species including an atom or a plurality of the same atoms formed by exciting a source gas selected from hydrogen, helium, and a halogen element with plasma. In the case where hydrogen is implanted, it is preferable 30 that  $H^+$ ,  $H_2^+$ , and  $H_3^+$  ions be contained and the  $H_3^+$  ion be contained at a higher percentage. Thus, efficiency of the ion irradiation can be enhanced and time of the ion irradiation can be shortened. Further, such a structure enables easy separation.

## [0038]

In order to form the separation layer 103 at a given depth, irradiation with the ions 104 needs to be performed at a high dose rate in some cases. In this case, the surface of the semiconductor substrate 101 becomes rough depending on conditions.

5 Therefore, a silicon nitride layer, a silicon nitride oxide layer, or the like with a thickness of 50 to 200 nm inclusive may be provided as a protective layer for the surface of the semiconductor substrate, to which the ion is applied.

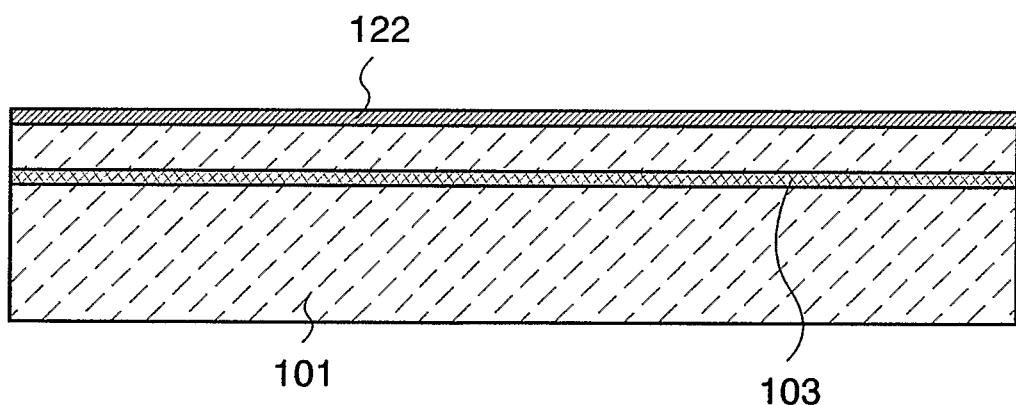

## [0039]

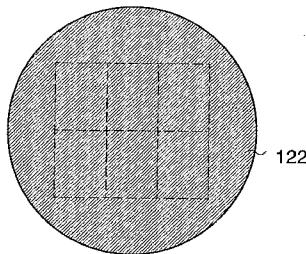

Next, the bonding layer 122 is formed on the semiconductor substrate 101 (see 10 FIGS. 4B and 6B). The bonding layer 122 is formed on the surface of the semiconductor substrate 101, which forms bonding with the base substrate. As the bonding layer 122 formed here, a silicon oxide layer formed by a chemical vapor deposition method using organic silane as a source gas as described above is preferable. It is also possible to use a silicon oxide layer formed by a chemical vapor deposition 15 method using silane as a source gas. Temperatures at which degasification from the separation layer 103 formed in the semiconductor substrate 101 does not occur are applied to forming a film by a chemical vapor deposition method. For example, a film formation temperature of 350 °C or lower is applied. A heat treatment temperature higher than the film formation temperature by a chemical vapor deposition method is 20 applied to heat treatment for separating the SOI layer from the semiconductor substrate such as a single-crystalline semiconductor substrate or a polycrystalline semiconductor substrate.

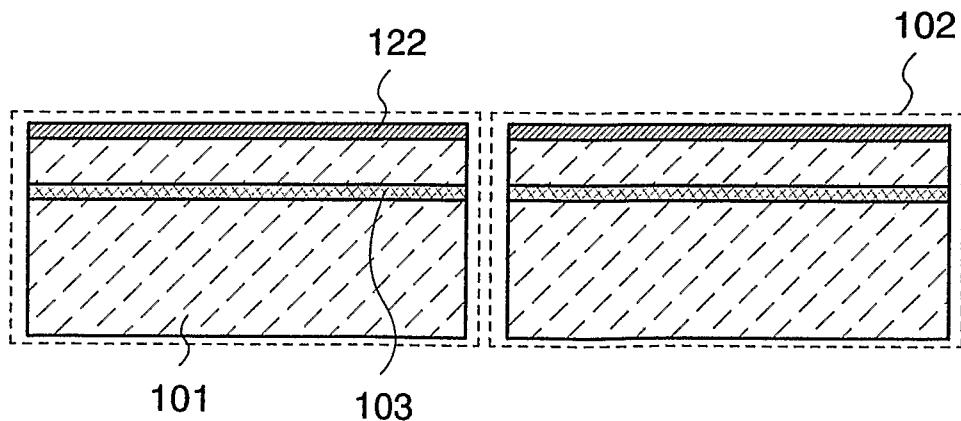

## [0040]

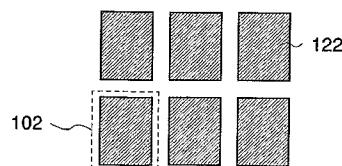

Next, the semiconductor substrate 101 is processed to have a desired size and 25 shape (see FIGS. 4C and 6C): concretely, the semiconductor substrate 101 is processed to have a desired panel size. FIG. 6C shows an example in which the semiconductor substrate 101 of a circular shape is divided into sections to form semiconductor substrates 102 of a rectangular shape. At this time, the bonding layer 122 and the separation layer 103 are also divided. That is, the semiconductor substrates 102 which 30 each have a desired panel size, include a separation layer 103 at a given depth, and have the bonding layer 122 formed on the surface (the surface to which the base substrate is bonded) are obtained.

## [0041]

It is preferable that the semiconductor substrate 102 have a panel size of a variety of display devices. The panel size may be determined as appropriate according to an end product into which the panel is incorporated, or the like: for example, the 5 panel size may be a diagonal line of less than 10 in., which is a panel size of a small to medium panel. For example, in the case where the semiconductor substrate 102 is applied to a mobile phone with a screen size of 2.4 in. in diagonal line, the panel size is determined in consideration of a screen frame size in addition to a screen size of 2.4 in. in diagonal line. The shape of the semiconductor substrate 102 may be determined as 10 appropriate according to the usage of an end product or the like. In the case where the semiconductor substrate 102 is applied to a display device, it is preferable that the semiconductor substrate 102 have a rectangular shape with an aspect ratio of about 3:4. Further, it is preferable that the semiconductor substrate 102 have a rectangular shape. Thus, processing in later manufacturing steps is easy and the semiconductor substrate 15 102 can be cut from the semiconductor substrate 101 efficiently. The semiconductor substrate 101 can be divided with a cutting apparatus such as a dicer or a wiresaw, a laser, plasma, an electronic beam, or any other cutting means.

## [0042]

An order of steps up to provision of the bonding layer on the surface of the 20 semiconductor substrate can be permuted as appropriate. FIGS. 4A to 4C and 6A to 6C show an example in which the separation layer is formed in the semiconductor substrate, the bonding layer is provided on the surface of the semiconductor substrate, and then the semiconductor substrate is processed to have a desired panel size each. However, the following method can also be taken, for example: after processing the 25 semiconductor substrate so as to have a desired panel size, the separation layer is formed in the semiconductor substrate having the desired panel size, and the bonding layer is provided for the surface of the semiconductor substrate having the desired panel size.

## [0043]

30 Next, the base substrate 110 and the semiconductor substrate 102 are bonded to each other. FIG. 5A shows an example in which the surface of the semiconductor substrate 102, for which the bonding layer 122 is provided is brought into close contact

with the base substrate 110, and the base substrate 110 and the bonding layer 122 are bonded to each other, so that the base substrate 110 and the semiconductor substrate 102 are bonded to each other. Note that it is preferable that the surface which forms bonding (bonding surface) be cleaned sufficiently. Close contact between the base 5 substrate 110 and the bonding layer 122 forms the bonding. Van der Waals force acts on this bonding, and the base substrate 110 and the semiconductor substrate 102 are bonded to each other by being pressed, so that the firm bonding due to a hydrogen bond can be formed.

[0044]

10 The bonding surface may be activated in order to form favorable bonding between the base substrate 110 and the bonding layer 122. For example, one or both of the surfaces on which the bonding is formed is irradiated with an atomic beam or an ion beam. In the case where an atomic beam or an ion beam is utilized, an inert gas (e.g. argon) neutral atom beam or an inert gas ion beam can be used. It is also possible 15 to activate the bonding surface by plasma irradiation or radical treatment. Such surface treatment facilitates forming bonding between different materials even at a temperature of 400 °C or lower.

[0045]

20 After bonding the semiconductor substrate 102 to the base substrate 110 with the bonding layer 122 interposed therebetween, it is preferable to perform heat treatment or pressure treatment. The heat treatment or the pressure treatment can improve a bonding strength. It is preferable that a process temperature of the heat treatment be lower than or equal to the heat-resistant temperature of the base substrate 110. The pressure treatment is performed so that pressure is applied to the bonding 25 surface in a perpendicular direction, in consideration of the pressure resistance of the base substrate 110 and the semiconductor substrate 102.

[0046]

30 Next, heat treatment is performed, so that part of the semiconductor substrate 102 is separated from the base substrate 110, the separation layer 103 functioning as a cleavage plane (see FIG. 5B). It is preferable that the process temperature of the heat treatment be higher than or equal to the film formation temperature of the bonding layer 122 and lower than or equal to the heat-resistant temperature of the base substrate 110.

For example, heat treatment is performed at process temperatures of 400 to 600 °C inclusive, whereby there occurs a change in volume of a minute cavity formed in the separation layer 103 and thus separation along the separation layer 103 is possible. The SOI layer 130, which has the same crystallinity as that of the semiconductor substrate 102, is left over the base substrate 110 because the bonding layer 122 is bonded to the base substrate 110. Note that in this description, “cleavage” means that part of a semiconductor substrate is separated at a separation layer which is weakened to have minute cavities by performing irradiation with ions of hydrogen, helium, or halogen such as fluorine, so that an SOI layer is formed over a base substrate. Further, the “cleavage plane” designates a separation plane (a plane opposite to the base substrate) of the SOI layer provided over the base substrate by the separation.

[0047]

In the above manner, the SOI structure in which the SOI layer 130 is provided over the base substrate 110 with the bonding layer 122 interposed therebetween is formed. Note that the SOI substrate according to the present invention has a feature that a plurality of SOI layers are provided over one base substrate with a bonding layer interposed therebetween. For example, a separation layer is formed, a bonding layer is formed at a surface, and the desired number of semiconductor substrates 102 formed by being processed into sections each having a desired panel size are prepared. Then, after bonding the desired number of semiconductor substrates 102 to the base substrate 110 as shown in FIG. 8A, separation is performed at one time by heat treatment as shown in FIG. 8B, so that an SOI substrate can be manufactured. Instead of performing the separation at one time by heat treatment, it is also possible to repeat the steps of bonding one or some semiconductor substrates 102 to the base substrate 110 and separating part of the semiconductor substrates 102 to manufacture an SOI substrate.

[0048]

It is preferable to arrange the semiconductor substrates 102 systematically over the base substrate 110 because such an arrangement makes later steps easy. For example, the use of a control system such as a CCD camera or a computer enables systematic arrangement and bonding of the semiconductor substrates 102. Alternatively, a marker or the like may be formed on the base substrate 110 or the

semiconductor substrates 102 to adjust the positions. Although FIGS. 8A and 8B show a structure in which adjacent SOI layers have some space therebetween, the SOI layers may be laid with as small space as possible.

[0049]

5 It is preferable that SOI layers obtained by separation be subjected to chemical mechanical polishing (CMP) in order to planarize the surfaces. Alternatively, the planarization may be performed by irradiating the surfaces of the SOI layers with a laser beam instead of using a physical polishing means such as CMP. The laser beam irradiation is preferably performed in a nitrogen atmosphere containing oxygen at a 10 concentration of 10 ppm or less. The reason is that the surfaces of the SOI layers can be rough when laser beam irradiation is performed in an oxygen atmosphere. Further, CMP or the like may be performed to thin SOI layers obtained.

[0050]

15 FIGS. 7A to 7C show a step of providing a bonding layer on a base substrate side and to form SOI layers. Here, an example of a method for manufacturing the SOI substrate shown in FIG. 3B is described.

[0051]

20 FIG. 7A shows a step of irradiating the semiconductor substrate 101 having the silicon oxide layer 126 with the ions 104 accelerated by an electric field to form the separation layer 103 at a given depth. The silicon oxide layer 126 can be formed by a CVD method or a sputtering method, preferably by a thermal oxidation method. As the silicon oxide layer 126, it is also possible to use a chemical oxide formed by treating the surface of the semiconductor substrate with water containing ozone or the like. A 25 semiconductor substrate similar to the semiconductor substrate 101 in FIG. 4A can be used for the semiconductor substrate 101 in FIG. 7A. Further, the irradiation with ions of hydrogen, helium, or halogen such as fluorine is performed in a similar manner to that shown in FIG. 4A. With formation of the silicon oxide layer 126 on the surface of the semiconductor substrate 101, loss of planarity due to damage to the surface of the semiconductor substrate in the ion irradiation can be prevented.

30 [0052]

FIG. 7B shows a step of bringing the surface of the semiconductor substrate 102, on which the silicon oxide layer 126, is formed into close contact with the base

substrate 110 on which the barrier layer 152 and the bonding layer 154 are formed, thereby forming bonding. The bonding is formed by bringing the silicon oxide layer 126 on the semiconductor substrate 102 into close contact with the bonding layer 154 over the base substrate 110. The semiconductor substrate 102 is obtained by 5 processing the semiconductor substrate 101, in which the separation layer 103 is formed and the silicon oxide layer 126 is formed at the surface, into sections each having a desired panel size. The barrier layer 152 may be formed by a CVD method or a sputtering method using a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer, or a silicon nitride oxide layer to have a single-layer structure or a stacked-layer 10 structure. As the bonding layer 154, a silicon oxide layer similar to the bonding layer 122 may be formed.

[0053]

Then, as shown in FIG. 7C, part of the semiconductor substrate 102 is separated. Heat treatment for the separation is performed in a similar manner to that shown in FIG. 15 5B: the part of the semiconductor substrate 102 is separated from the base substrate 110, the separation layer 103 functioning as a cleavage plane. After the separation, there remains the SOI layer 130 having the same crystallinity as that of the semiconductor substrate 102 over the base substrate 110, so that the SOI substrate as shown in FIG. 1B can be obtained. The SOI substrate shown in FIG. 7C has a structure in which the SOI 20 layer 130 is provided over the base substrate 110 with the barrier layer 152, the bonding layer 154, and the silicon oxide layer 126 interposed therebetween. After the separation, CMP, laser beam irradiation, or the like may be performed to planarize or thin the obtained SOI layer.

[0054]

25 With application of a manufacturing method of an SOI substrate according to the present invention, the SOI layer 130 having a bonding portion with a high bond strength can be obtained even if the base substrate 110 has a heat-resistant temperature of 600 °C or lower (e.g. a glass substrate). Further, a variety of glass substrates for electronic industry which are called “alkali-free glass” such as aluminosilicate glass, 30 aluminoborosilicate glass, or barium borosilicate glass can be used as the base substrate 110 because a process temperature of 600 °C or lower can be applied. Needless to say,

it is also possible to use a ceramic substrate, a sapphire substrate, a quartz substrate, or the like. That is, single-crystalline semiconductor layers can be formed over a substrate with a side more than 1 meter long. With the use of such a large-sized substrate, a display device (e.g. a liquid crystal display device) or a semiconductor integrated circuit can be manufactured.

5 [0055]

An SOI substrate according to the present invention has a structure in which panel-sized SOI layers are provided over a base substrate. Such a structure enables formation of desired display panels using one SOI layer, and can achieve improvement 10 in a yield. Further, desired display panels can be formed using one SOI layer, and thus variations in elements which form the display panels can be suppressed.

15 [0056]

Furthermore, the yield can be controlled on a panel-to-panel basis even if a defect occurs in a crystal of the SOI layer in transferring the SOI layers to the base 20 substrate. Still furthermore, even if different kinds of materials are bonded to each other, stress can be alleviated because the SOI layers each having a panel size are transferred to the base substrate; accordingly, improvement in the yield can be achieved.

15 [0057]

An SOI substrate according to the present invention can have a large area by 20 providing a plurality of SOI layers over a base substrate. Accordingly, a large number of display panels can be manufactured by only one series of manufacturing process, and thus productivity of end products manufactured by incorporating the display panel can be improved.

25 [0058]

A display device can be manufactured with the use of an SOI substrate manufactured in the above manner. FIGS. 9A to 9C show schematic diagrams of an example of a display device according to the present invention. An example of forming a liquid crystal display device is shown here. FIG. 9A is a schematic diagram of a top view of an example. FIG. 9B is a cross-sectional diagram taken along a line 30 OP of the example in FIG. 9A. FIG. 9C is a perspective view of the example of the display device.

## [0059]

The liquid crystal display device according to this embodiment mode includes a display portion 620, a first drive circuit portion 630, and a second drive circuit portion 650 over a first substrate 600. The display portion 620, the first drive circuit portion 630, and the second drive circuit portion 650 are sealed with a sealant 680 between the first substrate 600 and a second substrate 690. Further, a terminal region 670 where an external input terminal which transmits a signal or potential from the outside to the first drive circuit portion 630 and the second drive circuit portion 650 is connected is provided over the first substrate 600.

## 10 [0060]

As shown in FIG. 9B, a pixel circuit portion 628 including a transistor is provided in the display portion 620. A peripheral circuit portion 638 including a transistor is provided in the first drive circuit portion 630. An insulating layer 602, an insulating layer 604, and a bonding layer 606 that function as base insulating layers are stacked in this order between the first substrate 600, and the pixel circuit portion 628 and the peripheral circuit portion 638. An insulating layer 608 and an insulating layer 609 that function as interlayer insulating layers are provided in or over the pixel circuit portion 628 and the peripheral circuit portion 638. A source region or a drain region of the transistor in the pixel circuit portion 628 is electrically connected to a pixel electrode 660 through an opening formed in the insulating layer 609. Although circuits including transistors are integrated in the pixel circuit portion 628, FIG. 9B shows a cross-sectional view of one transistor for sake of convenience. Also in the peripheral circuit portion 638, although circuits including transistors are integrated, a cross-sectional view of two transistors is shown for sake of convenience.

## 25 [0061]

A liquid crystal layer 684 sandwiched between an orientation film 682 covering the pixel electrode 660, and an orientation film 687 is provided over the pixel circuit portion 628 and the peripheral circuit portion 638. In the liquid crystal layer 684, a distance (cell gap) is controlled with a spacer 686. The second substrate 690 is provided over the orientation film 687 with a counter electrode 688 and a color filter 689 interposed therebetween. The first substrate 600 and the second substrate 690 are bonded firmly with the sealant 680.

[0062]

A polarizing plate 692 is provided for the outside of the second substrate 690. An example in which the polarizing plate is provided for the second substrate 690 is shown because this embodiment mode shows a reflective liquid crystal display device.

5 In the case of a transmissive liquid crystal display device, for example, a polarizing plate may be provided for each of the first substrate 600 and the second substrate 690.

[0063]

A terminal electrode 674 is provided for the terminal region 670. The terminal electrode 674 is electrically connected to an external input terminal 678 through an anisotropic conductive layer 676.

[0064]

Next, an example of a manufacturing method of the liquid crystal display device shown in FIGS. 9A to 9C is described.

[0065]

15 First, an SOI substrate according to the present invention is provided (see FIG. 11A). An example in which the SOI substrate similar to that shown in FIG. 2A is used is shown here.

[0066]

20 A plurality of SOI layers 610 are provided over the substrate 600, which is a base substrate, with the insulating layers 602 and 604 and the bonding layer 606 interposed therebetween. The SOI layers 610 each have a desired panel size by being processed. Although an example in which a display device is manufactured using a panel formation region 610b including one SOI layer is described here for sake of convenience, it is possible to manufacture a display device also in an adjacent panel 25 formation region 610a at the same time.

[0067]

30 A substrate having an insulating surface or an insulating substrate is used for the substrate 600. For example, a variety of glass substrates for electronic industry which are called “alkali-free glass” such as aluminosilicate glass, alumino borosilicate glass, or barium borosilicate glass; a quartz substrate; a ceramic substrate; a sapphire substrate; or the like is used. In this example, a glass substrate is used.

[0068]

The insulating layers 602 and 604 are provided in order to prevent diffusion of movable ions of an alkali metal, an alkaline earth metal, or the like from the glass substrate. Concretely, insulating layers similar to the above barrier layer may be formed. It is preferable to form an insulating layer containing nitrogen (e.g. a silicon nitride layer or a silicon nitride oxide layer) for at least one of the insulating layers 602 and 604. As the bonding layer 606, a silicon oxide layer similar to the bonding layer 122 may be formed.

[0069]

This embodiment shows an example in which the insulating layers 602 and 604 are formed over the substrate 600, the bonding layer 606 is formed at a semiconductor substrate side from which an SOI layer is separated, the substrate 600 and the semiconductor substrate are bonded to each other, and then part of the semiconductor substrate is separated to form the SOI layer 610. Concretely, the bonding layer 606 formed over the semiconductor substrate is brought into close contact with the insulating layer 604 formed over the substrate 600 to bond the insulating layer 604 and the bonding layer 606 to each other, so that the substrate 600 and the semiconductor substrate are bonded to each other. In advance, a separation layer formed by irradiation with ions of hydrogen, helium, or halogen is formed in the semiconductor substrate at a given depth.

And then, heat treatment is performed to separate part of the semiconductor substrate, the separation layer in the semiconductor substrate functioning as a cleavage plane, so that the SOI layer 610 is obtained. In this example, the bonding layer 606 is formed on the semiconductor substrate side, so that the bonding layer 606 has almost the same size as that of the SOI layer 610. That is to say,

the bonding layer 606 is also split between the adjacent panel formation regions 610a and 610b in a similar manner to the SOI layer 610. Further, the insulating layers 602 and 604 form continuous layers across the panel formation regions 610a and 610b because the insulating layers 602 and 604 are formed over the substrate 600, which is a base substrate. The SOI substrate used may have any of the structures according to the present invention, and may have any of the structures shown in FIGS. 2A to 3B. For example, a bonding layer may be provided on a base substrate side, or an insulating layer such as a thermal oxidation film may be provided between the semiconductor

10

15

20

25

30

substrate and the bonding layer.

[0070]

The SOI layer 610 is selectively etched to form a first SOI layer 621 in the display portion 620, and a second SOI layer 631 and a third SOI layer 641 in the first drive circuit portion 630. And then gate electrodes 614 are formed over the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 with a gate insulating layer 612 interposed therebetween (see FIG. 11B).

[0071]

The first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 are obtained by etching the SOI layer 610 selectively to have a desired shape. In this embodiment mode, the SOI layer 610 is processed into a plurality of island shapes and separated. In the case where the thicknesses of the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 are desired to be smaller than that of the SOI layer of the prepared SOI substrate, the SOI layer may be etched to have smaller thicknesses. Alternatively, the SOI layer may be partially changed in its quality (quality change) and the changed portion may be selectively etched to have a smaller thickness. Quality change of the SOI layer indicates oxidation treatment, nitriding treatment, or the like. Further, the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 may be formed such that the end portion is either near-perpendicularly tapered or gently tapered by appropriate control of etching conditions or the like. For example, the end portion may be tapered at a taper angle of greater than or equal to 45° and less than 95°, preferably, greater than or equal to 60° and less than 95°, or may be gently tapered at a taper angle of less than 45°.

[0072]

In order to control a threshold voltage of a transistor to be completed, an impurity element imparting one conductivity type may be added to the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 at a low concentration. In this case, the impurity element is also added to a channel formation region of the transistor. The impurity element added at this time is added at a lower concentration than that of a high concentration impurity region serving as a source region or a drain region and that of a low concentration impurity region serving as a lightly-doped drain

(LDD) region.

[0073]

The gate electrodes 614 are formed by forming a conductive layer entirely over the substrate and then etching the conductive layer selectively to form a desired shape.

5 In this embodiment mode, as the gate electrodes 614, after stacked structures of conductive layers are formed, the conductive layers are selectively etched, so that the separated conductive layers cross the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641, respectively.

[0074]

10 The conductive layers forming the gate electrodes 614 can each be formed as follows: a conductive layer is formed entirely over the substrate by a CVD method or a sputtering method using a metal element such as tantalum (Ta), tungsten (W), titanium (Ti), molybdenum (Mo), chromium (Cr), aluminum (Al), copper (Cu), or niobium (Nb), or an alloy or compound material containing the above metal element, and then the 15 conductive layer is selectively etched. Further, a semiconductor material typified by polycrystalline silicon to which an impurity element imparting one conductivity type such as phosphorus has been added can also be used.

[0075]

20 Although this embodiment mode shows the example in which the gate electrodes 614 have a stacked structure of the two conductive layers, the gate electrodes may have a single-layer structure or a stacked-layer structure of three or more layers. In addition, the side face of the conductive layers may be tapered. In the case where the gate electrodes have a stacked-layer structure of conductive layers, the conductive layer in a lower portion may be wider than the conductive layer in an upper portion, or 25 the side faces of the conductive layers may have different taper angles from each other.

[0076]

30 The gate insulating layers 612 are formed between the first SOI layer 621 and the gate electrode 614, the second SOI layer 631 and the gate electrode 614, and the third SOI layer 641 and the gate electrode 614. The gate insulating layers 612 can be formed by a CVD method, a sputtering method, an ALD method, or the like using silicon oxide, silicon oxynitride, hafnium oxide, aluminum oxide, tantalum oxide, or the like. Further, the gate insulating layers 612 can also be formed by solid-phase

oxidizing or solid-phase nitriding the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 by plasma treatment. Furthermore, insulating layers may be formed by a CVD method or the like and the insulating layers may be solid-phase oxidized or solid-phase nitrided by plasma treatment.

5 [0077]

The solid-phase oxidation or the solid-phase nitridation is preferably performed using plasma excited by high frequency such as a microwave (typically, 2.45 GHz). Concretely, plasma which is excited by high-frequency waves and has an electron density of  $1 \times 10^{11}$  to  $1 \times 10^{13}$  cm<sup>-3</sup> inclusive and electron temperatures of 0.5 to 1.5 eV inclusive is preferably used for plasma treatment so that a dense insulating layer is formed and a practical reaction speed is achieved in the solid phase oxidation treatment or solid phase nitridation treatment at temperatures of lower than or equal to 500 °C.

10 [0078]

When the surfaces of the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 are oxidized by plasma treatment, the plasma treatment is performed in an atmosphere containing oxygen (e.g. an atmosphere containing oxygen, ozone, nitrous oxide, nitrogen monoxide, or nitrogen dioxide, and a rare gas (at least one of helium (He), neon (Ne), argon (Ar), krypton (Kr), and xenon (Xe)), or an atmosphere containing oxygen, ozone, nitrous oxide, nitrogen monoxide, or nitrogen dioxide, hydrogen, and a rare gas). When the surfaces of the insulating layers formed over the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 are nitrided by plasma treatment, the plasma treatment is performed in an atmosphere containing nitrogen (e.g. an atmosphere containing nitrogen and a rare gas (at least one of He, Ne, Ar, Kr, and Xe), an atmosphere containing nitrogen, hydrogen, and a rare gas, or an atmosphere containing NH<sub>3</sub> and a rare gas). As the rare gas, Ar is preferably used, for example. Further, a gas in which Ar and Kr are mixed may also be used.

20 [0079]

25 FIG. 16 shows a structural example of a plasma process apparatus 1080 for performing plasma treatment. The plasma process apparatus 1080 includes a support 1088, a gas supply portion 1084 for supplying a gas, an exhaust port 1086 that is connected to a vacuum pump to exhaust a gas, an antenna 1098, a dielectric plate 1082,

and a high-frequency wave supply portion 1092 for supplying high-frequency waves for plasma generation. An object to be processed 1010 is held by the support 1088. In addition, if a temperature controller 1090 is provided for the support 1088, the temperature of the object to be processed 1010 can be controlled. The object to be

5 processed 1010 is a body which is subjected to plasma treatment. In this embodiment mode, the object to be processed 1010 corresponds to a stacked body in which the insulating layer 602 and 604, the bonding layer 606, and the first SOI layer 621 are stacked; a stacked body in which the insulating layer 602 and 604, the bonding layer 606, and the second SOI layer 631 are stacked; and a stacked body in which the

10 insulating layer 602 and 604, the bonding layer 606, and the third SOI layer 641. Alternatively, the object to be processed 1010 corresponds to a stacked body in which an insulating layer is formed over the first SOI layer 621, a stacked body in which an insulating layer is formed over the second SOI layer 631, and a stacked body in which an insulating layer is formed over the third layer 641.

15 [0080]

Hereinafter, a specific example is described in which an insulating layer is formed on the surface of the semiconductor layer with the plasma process apparatus 1080 shown in FIG. 16. Examples of the plasma treatment include surface modification treatment, such as oxidation treatment, nitridation treatment,

20 oxynitridation treatment, or hydrogenation treatment, performed to a substrate, a semiconductor layer (an SOI layer), an insulating layer, or a conductive layer. For these treatments, a gas supplied from the gas supply portion 1084 may be determined in accordance with an intended purpose.

[0081]

25 First, a process chamber of the plasma process apparatus 1080 shown in FIG. 16 is evacuated of air and a gas containing a rare gas and oxygen or nitrogen is supplied from the gas supply portion 1084. The object to be processed 1010 is heated at room temperature or at temperatures of 100 to 550 °C inclusive, by the temperature controller 1090. The distance between the object to be processed 1010 and the dielectric plate

30 1082 (hereinafter, also referred to as an electrode interval) is about 20 to 200 mm inclusive (preferably, 20 to 60 mm inclusive).

[0082]

Next, high-frequency waves are supplied from the high-frequency wave supply portion 1092 to the antenna 1098. Here, microwaves (frequency: 2.45 GHz) are introduced as the high-frequency waves. Then, the microwaves are introduced from 5 the antenna 1098 into the process chamber through the dielectric plate 1082; thus, plasma 1094 is generated. With the plasma 1094, oxygen radicals (which may include an OH radical) or nitrogen radicals (which may include an NH radical) are generated. At this time, the plasma 1094 is generated using the gas supplied.

[0083]

10 When the plasma 1094 is generated by introducing high-frequency waves such as microwaves, plasma with the low electron temperature (less than or equal to 3 eV, preferably, less than or equal to 1.5 eV) and the high electron density (greater than or equal to  $1 \times 10^{11} \text{ cm}^{-3}$ ) can be generated. Concretely, plasma with electron temperatures of 0.5 to 1.5 eV inclusive, and an electron density of  $1 \times 10^{11}$  to  $1 \times 10^{13}$  15  $\text{cm}^{-3}$  inclusive, is preferably generated. In this description, plasma which has the low electron temperature and the high electron density and is generated by introducing microwaves is also called "high-density plasma". Further, plasma treatment utilizing high-density plasma is also called "high-density plasma treatment".

[0084]

20 With the oxygen radicals (which may include an OH radical) or nitrogen radicals (which may include an NH radical) generated by the plasma 1094, the surface of the SOI layer formed in the object to be processed 1010 is oxidized or nitrided, whereby an insulating layer is formed. Alternatively, the surface of the insulating layer formed over the SOI layer or the vicinity of the surface is oxidized or nitrided. 25 At this time, if the rare gas such as argon is mixed in the gas supplied, oxygen radicals or nitrogen radicals can be generated efficiently by excited species of the rare gas. In the case where the rare gas is used in the gas supplied, the rare gas may be contained in the insulating layer formed. In this method, oxidation or nitridation by a solid phase reaction can be performed at low temperatures of lower than or equal to 500 °C by 30 effective use of active radicals excited by plasma.

## [0085]

One preferable example of manufacturing the gate insulating layer 612 formed by plasma treatment in this embodiment mode is as follows: the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 are subjected to plasma treatment in an atmosphere containing oxygen to form silicon oxide layers, and the surfaces of the silicon oxide layers are treated with nitridation plasma in an atmosphere containing nitrogen to form nitrogen-plasma-treated layers. Concretely, first, the silicon oxide layers having thicknesses of 3 to 6 nm inclusive are formed on the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641 by plasma treatment in an atmosphere containing oxygen. Subsequently, the plasma treatment in an atmosphere containing nitrogen is performed, whereby the nitrogen-plasma-treated layers with high nitrogen concentration are provided for the surfaces of the silicon oxide layers or in the vicinity of the surfaces. The “the vicinity of the surface” refers to a region at a depth of about 0.25 to 1.5 nm inclusive from the surface of the silicon oxide layer. For example, by performing the plasma treatment in an atmosphere containing nitrogen after forming the silicon oxide layers, the nitrogen-plasma-treated layers in which nitrogen is contained at 20 to 50 at.% inclusive can be formed in the silicon oxide layers at depths of about 1 nm from the surfaces thereof in a perpendicular direction. The nitrogen-plasma-treated layers can be formed using silicon nitride or silicon nitride oxide depending on the conditions of the plasma treatment.

## [0086]

In any case, by the solid phase oxidation treatment or solid phase nitridation treatment with plasma treatment as described above, even if a glass substrate with a heat-resistant temperature of lower than or equal to 600 °C is used as the substrate 600, insulating layers that are equivalent to thermally-oxidized films formed at temperatures of 950 to 1050 °C inclusive can be obtained. That is, highly reliable insulating layers can be formed as the insulating layers that serve as gate insulating layers in semiconductor elements, in particular, thin film transistors or nonvolatile memory elements.

## 30 [0087]

FIG. 11B shows an example in which the end portions of the gate insulating

layer 612 and the gate electrode 614 are aligned; however, this is not a limiting example, and the gate insulating layer 612 may be left in etching the gate electrode 614.

[0088]

If a material with a high dielectric constant (also referred to as a high-k material) is used for the insulating layers 612, the gate electrodes 614 are formed using polycrystalline silicon, silicide, metal, or metal nitride. Preferably, the gate electrodes 614 are formed using metal or metal nitride. For example, in the gate electrodes 614, the conductive layers in contact with the gate insulating layers 612 are formed using a metal nitride material, and the conductive layers thereon are formed using a metal material. The combination like this can prevent a depletion layer from spreading in the gate electrodes even if the gate insulating layers are thinned, and further can prevent driving performance of transistors from being damaged even if miniaturization is done.

[0089]

Next, an insulating layer 616 is formed over the gate electrodes 614. Then, an impurity element imparting one type of conductivity is added using the gate electrodes 614 as masks (see FIG. 11C). This embodiment mode shows an example in which impurity elements imparting different types of conductivity are added to the second SOI layer 631 and the third SOI layer 641 in a first drive circuit portion 630. This embodiment mode further shows an example in which an impurity element imparting the same type of conductivity as that of the second SOI layer 631 is added to the first SOI layer 621 in a display portion 620.

[0090]

In the first SOI layer 621 formed in the display portion 620, a pair of impurity regions 623 and a channel formation region 622 located between the pair of impurity regions 623 are formed in a self-aligned manner using the gate electrode 614 as a mask.

[0091]

In the second SOI layer 631 formed in the first drive circuit portion 630, a pair of impurity regions 633 and a channel formation region 632 located between the pair of impurity regions 633 are formed in a self-aligned manner using the gate electrode 614 as a mask. In the third SOI layer 641, a pair of impurity regions 643 and a channel formation region 642 located between the pair of impurity regions 643 are formed in a self-aligned manner using the gate electrode 614 as a mask. Impurity elements

imparting different types of conductivity are added to the impurity regions 633 and 643.

[0092]

As the impurity element which imparts one type of conductivity, an element which imparts p-type conductivity such as boron (B), aluminum (Al), or gallium (Ga), or an element which imparts n-type conductivity such as phosphorus (P) or arsenic (As) can be used. In this embodiment mode, an element imparting n-type conductivity, e.g., phosphorus, is added to the first SOI layer 621 formed in the display portion 620 and the second SOI layer 631 formed in the first drive circuit portion 630. In addition, an element imparting p-type conductivity, e.g., boron, is added to the third SOI layer 641.

When the impurity element is added to the first SOI layer 621 and the second SOI layer 631, the third SOI layer 641 may be selectively covered with a resist mask or the like. Similarly, when the impurity element is added to the third SOI layer 641, the first SOI layer 621 and the second SOI layer 631 may be selectively covered with a resist mask or the like.

15 [0093]

The insulating layer 616 can be formed by a CVD method, a sputtering method, an ALD method, or the like using silicon oxide, silicon oxynitride, silicon nitride, silicon nitride oxide, or the like. With a structure in which the impurity element is added by passing through the insulating layer 616 in adding the impurity element that imparts one type of conductivity, damage to the SOI layers can be reduced.

[0094]

Next, sidewall insulating layers 618 are formed on the side surfaces of the gate electrodes 614. Then, the impurity element imparting one type of conductivity is added using the gate electrodes 614 and the sidewall insulating layers 618 as masks (see FIG. 11D). At this time, the impurity elements having the same conductivity types as those used in the previous step (the steps of forming the impurity regions 623, 633, and 643) are added to the first SOI layer 621, the second SOI layer 631, and the third SOI layer 641. The impurity elements added at this time are added at higher concentrations than those of the impurity elements used in the previous step.

30 [0095]

In the first SOI layer 621, a pair of high concentration impurity regions 626 and a pair of low concentration impurity regions 624 are formed in a self-aligned manner

using the gate electrode 614 and the sidewall insulating layers 618 as a mask. The high concentration impurity regions 626 formed at this time serve as a source region and a drain region, and the low concentration impurity regions 624 serve as LDD (lightly doped drain) regions.

5 [0096]

In the second SOI layer 631, a pair of high concentration impurity regions 636 and a pair of low concentration impurity regions 634 are formed in a self-aligned manner using the gate electrode 614 and the sidewall insulating layers 618 as a mask. The high concentration impurity regions 636 formed at this time serve as a source 10 region and a drain region, and the low concentration impurity regions 634 serve as LDD regions. In the third SOI layer 641, a pair of high concentration impurity regions 646 and a pair of low concentration impurity regions 644 are formed in a self-aligned manner using the gate electrode 614 and the sidewall insulating layers 618 as a mask. When the impurity element is added to the first SOI layer 621 and the second SOI layer 15 631, the third SOI layer 641 may be selectively covered with a resist mask or the like. Similarly, when the impurity element is added to the third SOI layer 641, the first SOI layer 621 and the second SOI layer 631 may be selectively covered with a resist mask or the like.

[0097]

20 The sidewall insulating layers 618 is provided for the side surfaces of the gate electrodes 614 with the insulating layer 616 therebetween. For example, the sidewall insulating layers 618 can be provided for the side surfaces of the gate electrodes 614 in a self-aligned manner by anisotropic etching, which proceeds mainly in the perpendicular direction, of an insulating layer formed to bury the gate electrodes 614. 25 The sidewall insulating layers 618 can be formed using silicon nitride, silicon nitride oxide, silicon oxide, silicon oxynitride, or the like. In the case where the insulating layer 616 is formed using silicon oxide or silicon oxynitride, the insulating layer 616 can function as an etching stopper if the sidewall insulating layers 618 is formed using silicon nitride or silicon nitride oxide. In the case where the insulating layer 616 is 30 formed using silicon nitride or silicon nitride oxide, the sidewall insulating layers 618 are preferably formed using silicon oxide or silicon oxynitride. When the insulating layer functioning as an etching stopper is provided in this manner, the SOI layers can be

prevented from being etched because of over-etching in forming the sidewall insulating layers.

[0098]

Next, exposed portions of the insulating layer 616 are etched (see FIG. 12A).

5 The insulating layer 616 is left between the sidewall insulating layers 618 and the gate electrode 614, between the sidewall insulating layers 618 and the first SOI layer 621, between the sidewall insulating layers 618 and the second SOI layer 631, and between the sidewall insulating layers 618 and the third SOI layer 641.

[0099]

10 A silicide layer may be formed in order to lower the resistance of the high concentration impurity region functioning as a source region and a drain region. For the silicide layer, cobalt silicide or nickel silicide is preferably applied. If the SOI layer has a small thickness, a silicide reaction may proceed to the bottom portion of the SOI layer in which the high concentration impurity region is formed, so that the SOI 15 layer in which the high concentration impurity region is formed may fully be silicided.

[0100]

Next, an insulating layer 608 is formed entirely over the substrate 600 and then is etched selectively, so that openings are formed to reach the high concentration impurity regions 626 formed in the first SOI layer 621 in the display portion 620. 20 Further, openings are formed to reach the high concentration impurity regions 636 formed in the second SOI layer 631 and the high concentration impurity regions 646 formed in the third SOI layer 641 in the first drive circuit portion 630. Then, conductive layers 619 are formed so as to fill the openings. Further, a terminal electrode 674 is formed in a terminal region 670 (see FIG. 12B).

25 [0101]

The insulating layer 608 is formed by a CVD method, a sputtering method, an ALD method, a coating method, or the like to have a single-layer structure or a stacked-layer structure. For example, the insulating layer 608 can be formed by a CVD method, a sputtering method, or an ALD method using an inorganic insulating 30 material containing oxygen and/or nitrogen, such as silicon oxide, silicon nitride, silicon oxynitride, or silicon nitride oxide, or an insulating material containing carbon, such as diamond like carbon (DLC); or can be formed by a coating method using an organic