OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 829 289**

⑮ Int. Cl.:

**B41J 2/045**

(2006.01)

⑫

## TRADUCCIÓN DE PATENTE EUROPEA

T3

⑥ Fecha de presentación y número de la solicitud internacional: **29.06.2017 PCT/GB2017/051911**

⑦ Fecha y número de publicación internacional: **04.01.2018 WO18002634**

⑨ Fecha de presentación y número de la solicitud europea: **29.06.2017 E 17736732 (3)**

⑩ Fecha y número de publicación de la concesión europea: **12.08.2020 EP 3478506**

---

④ Título: **Aparato de deposición de gotas y circuito de prueba para el mismo**

⑩ Prioridad:

**30.06.2016 GB 201611464**

④ Fecha de publicación y mención en BOPI de la traducción de la patente:

**31.05.2021**

⑦ Titular/es:

**XAAR TECHNOLOGY LIMITED (100.0%)

316 Science Park

Cambridge CB4 0XR, GB**

⑧ Inventor/es:

**BIRD, NEIL CHRISTOPHER y

ISLAM, MUJAHID-UL**

⑨ Agente/Representante:

**PONTI & PARTNERS, S.L.P.**

**ES 2 829 289 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Aparato de deposición de gotas y circuito de prueba para el mismo

- 5 La presente invención se refiere a un circuito de prueba. Un aparato que use elementos piezoeléctricos tales como actuadores, puede encontrar una aplicación particularmente beneficiosa en aparatos de deposición de gotas, sensores o recolectores de energía.

- 10 Se sabe que los aparatos de deposición de gotas, tales como impresoras de chorro de tinta, proporcionan una expulsión controlada de gotas desde un cabezal de deposición de gotas, y que proporcionan una colocación controlada de tales gotas para crear puntos en un medio receptor o de impresión.

- 15 Los cabezales de deposición de gotas, tales como los cabezales de impresión de chorro de tinta, generalmente comprenden mecanismos de expulsión proporcionados por elementos actuadores.

- 20 Es importante realizar pruebas de diagnóstico en los elementos actuadores y los circuitos de transmisión asociados, por ejemplo, para identificar una falla en un elemento(s) del actuador antes de ensamblarlo en un cabezal de impresión o después de haberlo ensamblado en un cabezal de impresión, para identificar cualquier falla que pueda generar defectos de impresión no deseados.

- 25 Existen varias técnicas de prueba de diagnóstico para probar los elementos actuadores.

- 30 Por ejemplo, cuando se prueban cortocircuitos a través de un elemento actuador, el elemento actuador toma una corriente a través de una sonda, y se mide una tensión correspondiente o se aplica una tensión y se mide una corriente resultante. Sin embargo, es difícil acceder a los elementos actuadores con una sonda cuando está ensamblada en el cabezal de impresión o la impresora. Esto se vuelve cada vez más difícil o inviable con la disminución del tamaño de la pieza del cabezal de impresión. Por lo tanto, la prueba de circuito abierto es difícil mediante el uso de este método.

- 35 Alternativamente, puede usarse una técnica óptica para probar circuitos abiertos a través de un elemento actuador, de manera que el elemento actuador es alimentado con una forma de onda y el calor resultante de cargar y descargar el elemento actuador es capturado por una cámara infrarroja (IR). Un punto de calor verifica la presencia o ausencia de un circuito abierto.

- 40 Sin embargo, el equipo necesario para capturar el punto de calor es complejo y costoso y, en particular, no es adecuado una vez que los elementos actuadores se ensamblan en el cabezal de impresión, ya que el hardware dentro del cabezal de impresión normalmente bloquea la línea de visión de la cámara IR.

- 45 Además, como un cortocircuito también da como resultado la generación de calor desde un elemento actuador cuando se acciona, la técnica óptica puede ser inexacta cuando se usa sola, y se requiere realizar una prueba adicional junto con la técnica óptica para descartar que haya un cortocircuito presente y, por lo tanto, dicha prueba puede ser lenta.

- 50 Por lo tanto, las técnicas de prueba existentes para probar los elementos actuadores son lentas, complejas, costosas y/o inexactas.

- 55 La técnica anterior se proporciona en el documento US 2012/007910 A1, que describe un aparato para inspeccionar un cabezal de inyección de tinta, el aparato incluye una unidad de exploración que está conectada al actuador piezoeléctrico de un cabezal de inyección de tinta para medir si se cambia la capacitancia del actuador piezoeléctrico; una unidad de entrada de pulsos que aplica pulsos de alta tensión a la unidad de exploración; una unidad de conmutación que conecta o desconecta la unidad de exploración hacia o desde el actuador piezoeléctrico y la unidad de entrada de pulsos; y un controlador que controla la unidad de conmutación para conectar la unidad de exploración al actuador piezoeléctrico y la unidad de entrada de pulso y recibe la información sobre si la capacitancia del actuador piezoeléctrico cambia de acuerdo con el pulso de alta tensión aplicado desde la unidad de escaneo para determinar si el actuador piezoeléctrico es anormal.

- 60 La presente invención proporciona un circuito de prueba como se define en la reivindicación 1 de las reivindicaciones adjuntas, para determinar la capacitancia de un elemento actuador en una serie de elementos actuadores. También se proporciona un circuito de cabezal de deposición de gotas como se define en la reivindicación 10, y un módulo de prueba como se define en la reivindicación 15.

- 65 De acuerdo con un aspecto, se proporciona un circuito de prueba para determinar la capacitancia de un elemento actuador ( $C_{ACT}$ ) en una serie de elementos actuadores, en donde el circuito de prueba comprende un controlador; una fuente para generar entradas de prueba; circuitos de medición para medir uno o más valores de prueba en una ruta

- de prueba entre el circuito de prueba y el elemento actuador; en donde el controlador se configura para, durante un período de prueba: controlar un primer interruptor asociado con el elemento actuador para conectar el elemento actuador a la ruta de prueba; controlar la fuente para generar una primera entrada de prueba; determinar una capacitancia total ( $C_{PAR} + C_{ACT}$ ) a partir de un primer valor de prueba generado en respuesta a la primera entrada de prueba; y determinar la capacitancia del elemento actuador ( $C_{ACT}$ ) a partir de la capacitancia total ( $C_{PAR} + C_{ACT}$ ).

- 5 Preferentemente, el controlador se configura además para, durante el primer período: controlar un segundo interruptor asociado con un elemento actuador adicional, para conectar el elemento actuador adicional a la ruta de prueba cuando hay un cortocircuito entre la ruta de prueba y el elemento actuador adicional.

- 10 Preferentemente, el controlador se configura además para: detectar una falla asociada con el elemento actuador en respuesta a uno o más de: los valores de prueba y la capacitancia determinada, en donde la falla comprende uno o más de: un circuito abierto, un cortocircuito a través del elemento actuador y el cortocircuito entre la ruta de prueba y el elemento actuador adicional.

- 15 Preferentemente, la falla comprende: la capacitancia determinada está por debajo de un umbral de capacitancia.

- 20 Preferentemente, el controlador se configura además para, durante un primer período de calibración: controlar el primer interruptor asociado con el elemento actuador para aislar el elemento actuador de la ruta de prueba; y controlar una segunda entrada de prueba en la ruta de prueba para cargar una capacitancia parásita asociada con el elemento actuador ( $C_{PAR}$ ); determinar la capacitancia parásita asociada ( $C_{PAR}$ ) a partir de un segundo valor de prueba generado en respuesta a la segunda entrada de prueba; y en donde la capacitancia parásita asociada para el elemento actuador ( $C_{PAR}$ ) se usa para determinar la capacitancia del elemento actuador ( $C_{ACT}$ ) de la capacitancia total ( $C_{PAR} + C_{ACT}$ ).

- 25 Preferentemente aún, el primer valor de prueba se genera además en respuesta a la primera entrada de prueba y una corriente parásita, en donde el controlador se configura además para, durante un primer período de calibración: controlar la fuente para desviar la corriente parásita lejos del elemento actuador; controlar el primer interruptor asociado con el elemento actuador para aislar eléctricamente el elemento actuador de la ruta de prueba; controlar la fuente para cargar una capacitancia parásita asociada con el elemento actuador con la corriente parásita; y generar un segundo valor de prueba en respuesta a cargar la capacitancia parásita asociada con la corriente parásita.

- 30 Preferentemente, el controlador se configura además para, durante un segundo período de calibración: controlar la fuente para desviar la corriente parásita lejos del elemento actuador; controlar el primer interruptor asociado con el elemento actuador para aislar eléctricamente el elemento actuador de la ruta de prueba; controlar la fuente para cargar la capacitancia parásita asociada con la corriente parásita y una segunda entrada de prueba; y generar un tercer valor de prueba en respuesta a cargar la capacitancia parásita asociada con la corriente parásita y la segunda entrada de prueba.

- 35 Preferentemente, los segundos valores de prueba y los terceros valores de prueba se usan para determinar la capacitancia del elemento actuador ( $C_{ACT}$ ) a partir de la capacitancia total ( $C_{PAR} + C_{ACT}$ ).

- 40 Preferentemente, el circuito de medición comprende uno o más comparadores, cada uno dispuesto para recibir uno o más valores de prueba en la ruta de prueba, en donde cada uno de los comparadores está dispuesto para recibir una entrada de nivel establecido y/o en donde la entrada de nivel establecido comprende uno de un nivel de tensión y un nivel de corriente.

- 45 Preferentemente, el circuito de medición comprende un temporizador dispuesto para recibir una salida de uno o más comparadores, en donde el temporizador se configura para medir uno o más de: el tiempo de transición del primer valor de prueba desde un primer nivel establecido a un segundo nivel establecido, el tiempo de transición del segundo valor de prueba desde un tercer nivel establecido a un cuarto nivel establecido y el tiempo de transición del tercer valor de prueba desde un quinto nivel establecido a un sexto nivel establecido.

- 50 Preferentemente, uno o más de los niveles de establecidos primero, tercero y quinto son sustancialmente iguales, y/o uno o más de los niveles de establecidos segundo, cuarto y sexto son sustancialmente iguales.

- 55 Preferentemente, el circuito de prueba comprende además un interruptor de prueba dispuesto para aislar eléctricamente el circuito de prueba de la ruta de prueba.

- 60 Preferentemente, el circuito de prueba comprende además: un circuito de precisión para proporcionar selectivamente una o más entradas de prueba a un circuito de medición adicional.

- 65 Preferentemente, el circuito de prueba comprende además un interruptor de descarga para descargar la ruta de prueba.

- 65 Preferentemente, la fuente comprende una fuente de corriente constante y la primera entrada de prueba comprende una corriente constante.

- 5 De acuerdo con un aspecto adicional, se proporciona un circuito de prueba para detectar una falla en una serie de elementos actuadores, en donde el circuito de prueba comprende: un controlador; una fuente para generar entradas de prueba; y circuitos de medición para medir uno o más valores de prueba en una ruta de prueba; en donde el controlador se configura para, durante un primer período: controlar un primer interruptor asociado con un primer elemento actuador de la serie para conectar el primer elemento actuador a la ruta de prueba; controlar la fuente para generar una primera entrada de prueba; y detectar la falla a partir de un primer valor de prueba generado en respuesta a la primera entrada de prueba.

- 10 Preferentemente, el controlador se configura además para: controlar un segundo interruptor asociado con un segundo elemento actuador en la serie para descargar el segundo elemento actuador.

- 15 Preferentemente, la falla comprende un cortocircuito a través del primer elemento actuador y/o la falla comprende un cortocircuito entre la ruta de prueba y el segundo elemento actuador.

- 20 15 De acuerdo con un aspecto adicional, se proporciona un circuito de cabezal de deposición de gotas que comprende: un ensamblaje de elemento actuador que comprende uno o más elementos actuadores; un circuito de conmutación que comprende una pluralidad de interruptores para conectar selectivamente un elemento actuador de uno o más elementos actuadores a una ruta de prueba o una ruta de accionamiento; y un circuito de prueba configurado para: determinar una capacitancia del elemento actuador cuando se conecta a la ruta de prueba y/o detectar una falla en el conjunto del actuador.

- 25 Preferentemente, el circuito de prueba comprende: un controlador; una fuente para generar entradas de prueba para la ruta de prueba; y circuitos de medición para medir uno o más valores de prueba en la ruta de prueba generadas en respuesta a las entradas de prueba.

- 30 Preferentemente, la ruta de prueba comprende un interruptor de descarga configurado para descargar una capacitancia en la ruta de prueba.

- 35 Preferentemente, la ruta de prueba comprende: un primer bus de prueba entre el circuito de prueba y uno o más elementos actuadores, en donde la ruta de accionamiento comprende el primer bus de prueba entre un circuito de accionamiento y uno o más elementos actuadores.

- 40 Preferentemente, la ruta de accionamiento comprende un segundo bus de prueba entre un circuito de accionamiento y uno o más elementos actuadores.

- 45 Preferentemente, la ruta de prueba comprende un interruptor de prueba para aislar eléctricamente el circuito de prueba de la ruta de accionamiento.

- 50 Preferentemente, un interruptor de la pluralidad de interruptores comprende los elementos interruptores primero y segundo dispuestos en serie.

- 55 Preferentemente, el interruptor comprende además un tercer elemento interruptor dispuesto en paralelo con el primer y segundo elementos interruptores, en donde la resistencia a ON del primer y segundo elementos interruptores es menor que la resistencia a ON del tercer elemento interruptor.

- 60 Preferentemente, el primer bus de prueba está acoplado entre el primer y el segundo elemento interruptor, y el primer elemento conmutador se configura para aislar eléctricamente el circuito de prueba de la ruta de accionamiento.

- 65 Preferentemente, el interruptor comprende además un tercer elemento interruptor dispuesto en paralelo con el primer elemento interruptor, en donde el primer bus de prueba está acoplado entre el segundo y tercer elementos interruptores, y en donde el interruptor de prueba se proporciona en el bus de prueba.

- 70 Preferentemente, el circuito del cabezal de deposición de gotas se configura además para iniciar una acción de falla cuando se detecta la falla.

- 75 Preferentemente, la falla comprende uno de: un circuito abierto, un cortocircuito y una capacitancia que alcanza un umbral.

- 80 60 De acuerdo con un aspecto adicional, se proporciona un método para determinar la capacitancia de un elemento actuador ( $C_{ACT}$ ) en un circuito de cabezal de impresión, el método comprende: acoplar el elemento actuador a una ruta de prueba; generar, en un circuito de prueba, una primera entrada para la ruta de prueba; medir, en el circuito de prueba, un primer valor de prueba en la ruta de prueba generado en respuesta a la entrada de prueba; determinando, en respuesta al primer valor de prueba, una capacitancia total ( $C_{PAR} + C_{ACT}$ ) a partir del primer valor de prueba; y determinar la capacitancia del elemento actuador ( $C_{ACT}$ ) a partir de la capacitancia total ( $C_{PAR} + C_{ACT}$ ).

Preferentemente, el método comprende además detectar una falla en respuesta al primer valor de prueba e iniciar una acción de falla en el circuito del cabezal de impresión cuando se detecta una falla.

Las modalidades se describirán ahora con referencia a las figuras adjuntas de las cuales:

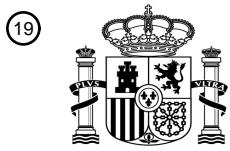

- 5 la Figura 1a muestra esquemáticamente una sección transversal a través de parte de un cabezal de deposición de gotas conocido;

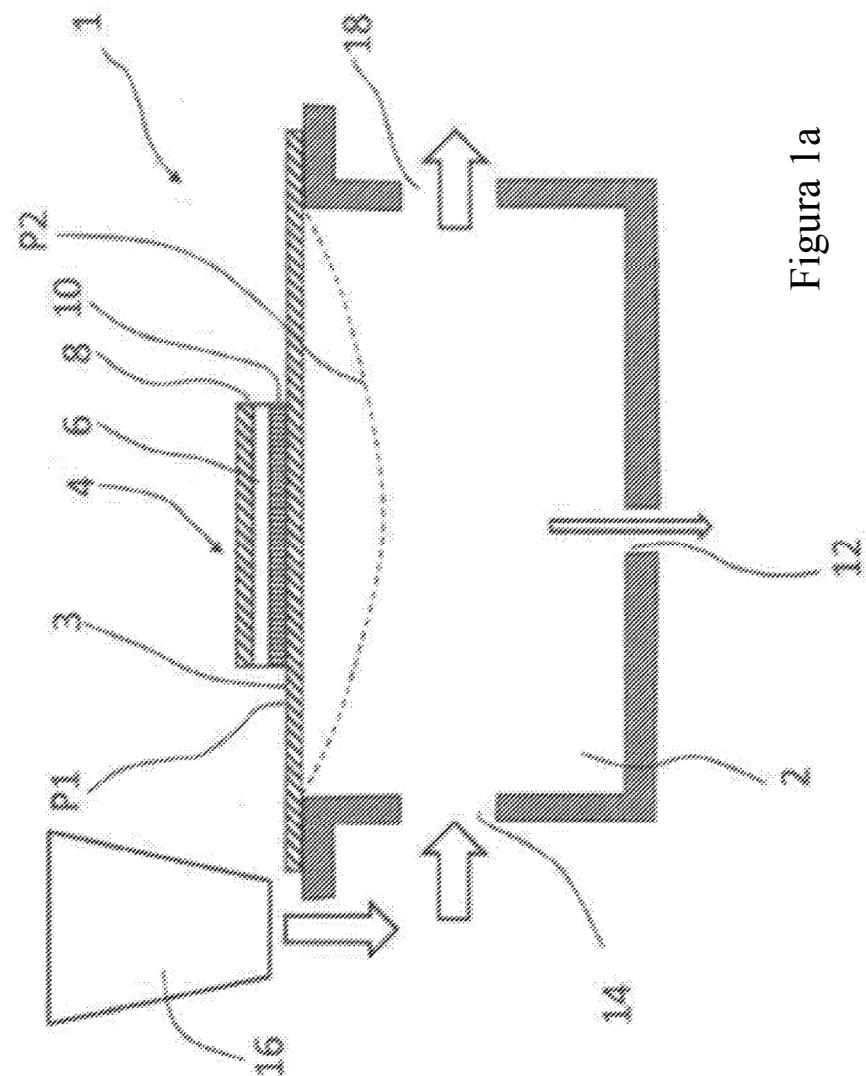

- la Figura 1b muestra esquemáticamente un ejemplo de un circuito conocido para accionar una pluralidad de elementos actuadores de la Figura 1 de acuerdo con una modalidad;

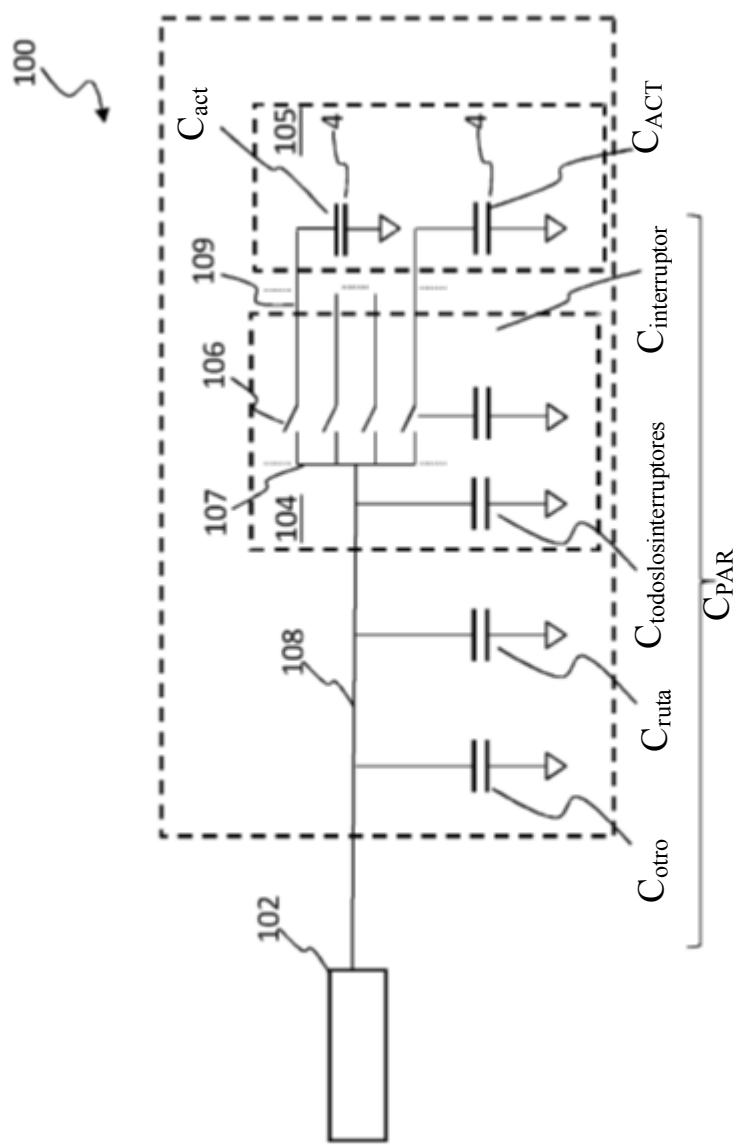

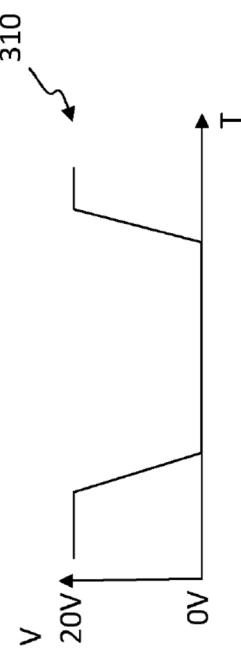

- 10 la Figura 2a muestra esquemáticamente un circuito de prueba para un elemento actuador de acuerdo con una modalidad;

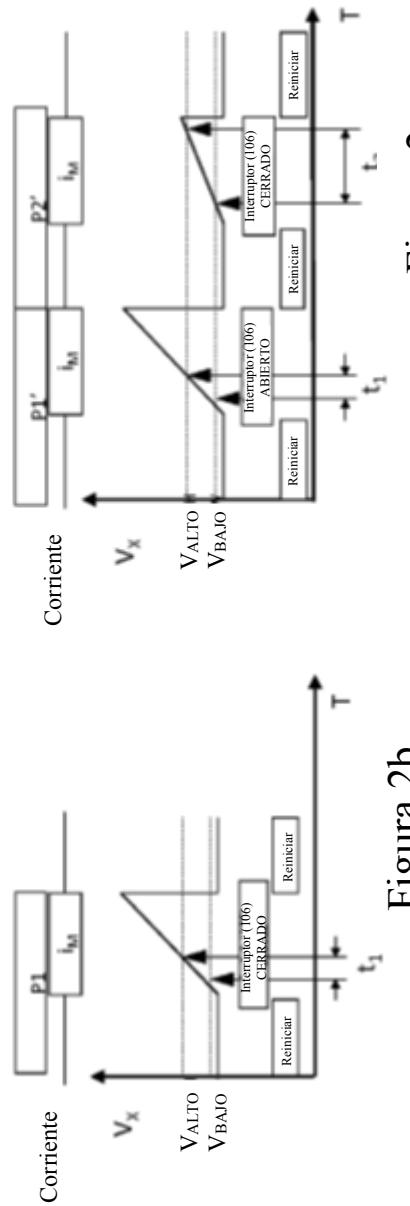

- la Figura 2b muestra gráficamente una medición obtenida mediante el uso del circuito de prueba de la Figura 2a;

- la Figura 2c muestra gráficamente una medición adicional obtenida mediante el uso del circuito de prueba de la Figura 2a;

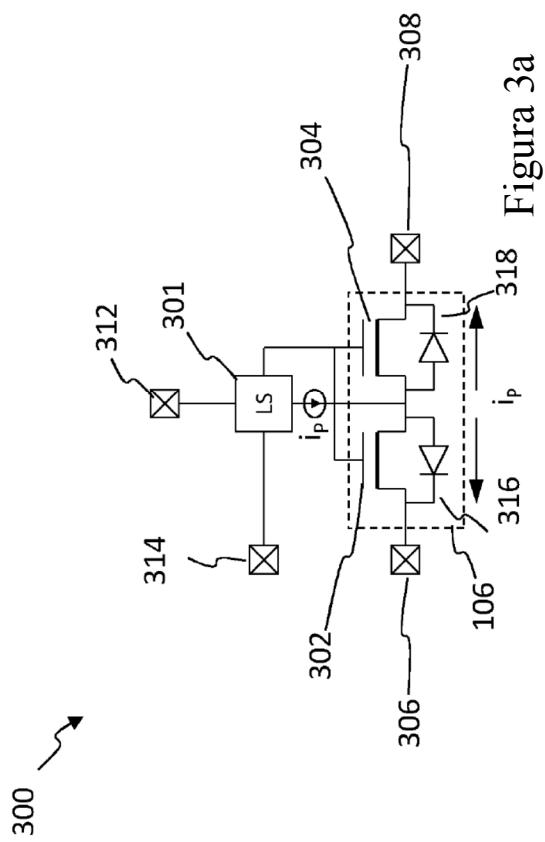

- 15 la Figura 3a muestra esquemáticamente un interruptor de ejemplo de acuerdo con una modalidad;

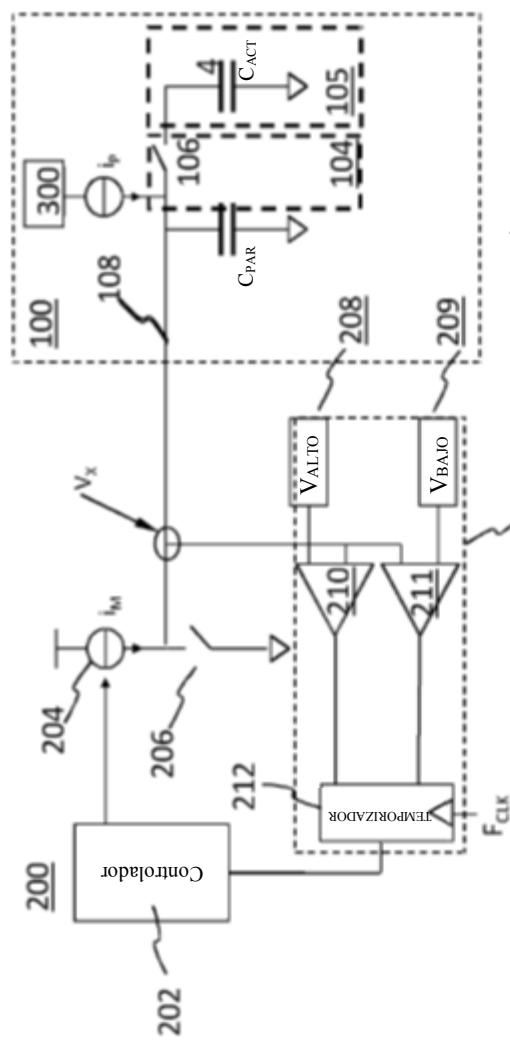

- la Figura 3b muestra esquemáticamente un ejemplo de forma de onda de accionamiento de acuerdo con una modalidad;

- la Figura 4a muestra esquemáticamente un ejemplo del circuito de prueba de la Figura 2a, en donde un elemento actuador es accionado por el interruptor de la Figura 3a de acuerdo con una modalidad;

- 20 la Figura 4b muestra gráficamente una medición obtenida mediante el uso del circuito de prueba de la Figura 4a;

- la Figura 5a muestra esquemáticamente un circuito que tiene un circuito de prueba de acuerdo con una modalidad;

- la Figura 5b muestra esquemáticamente un cortocircuito a través de un elemento actuador en el circuito de la Figura 5a;

- 25 la Figura 5c muestra esquemáticamente un cortocircuito entre elementos actuadores en el circuito de la Figura 5a;

- la Figura 6 muestra esquemáticamente un circuito que tiene un circuito de prueba de acuerdo con una modalidad;

- la Figura 7a muestra esquemáticamente un circuito que tiene un circuito de prueba de acuerdo con una modalidad adicional;

- 30 la Figura 7b muestra esquemáticamente un ejemplo de forma de onda de accionamiento de acuerdo con una modalidad;

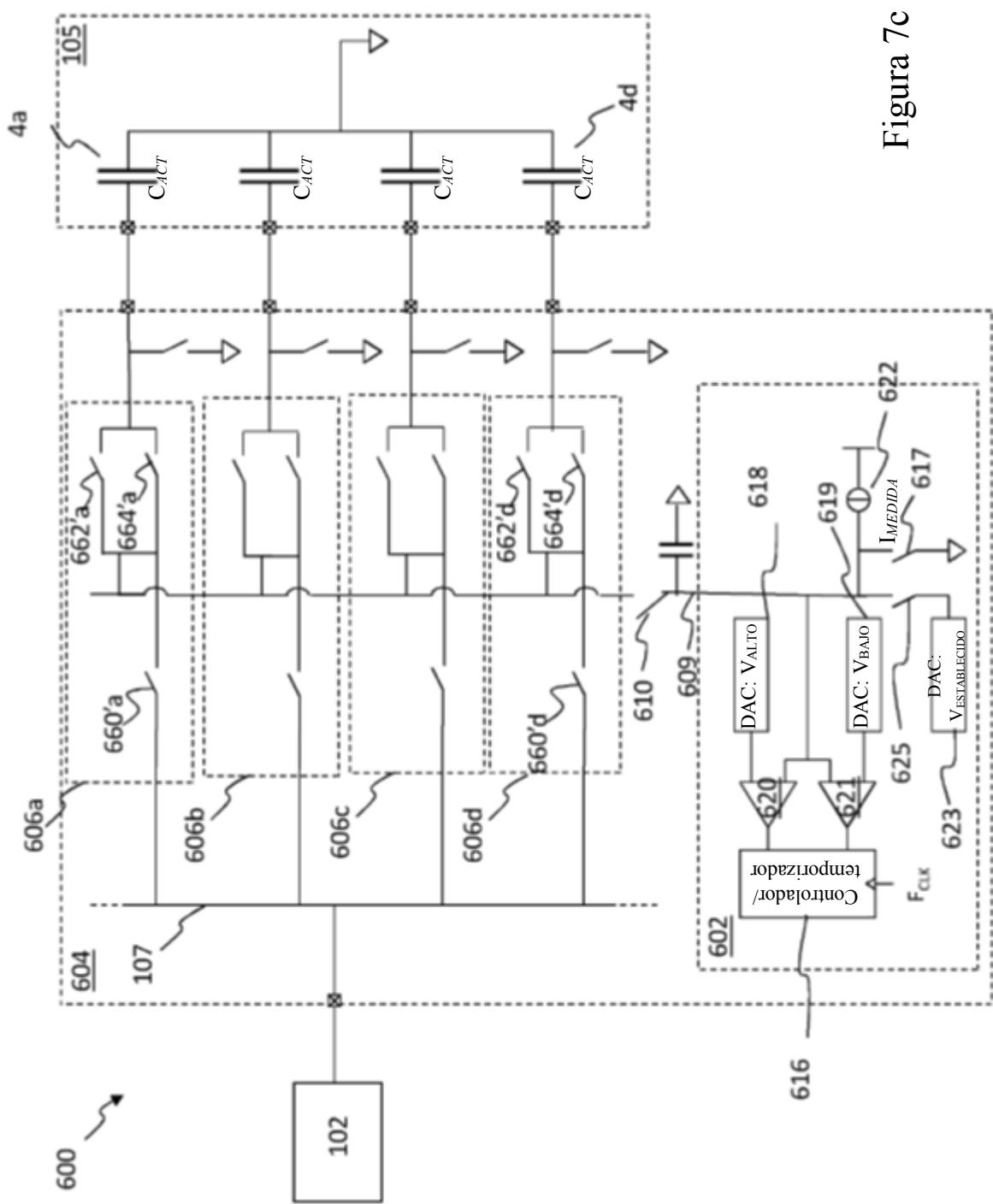

- la Figura 7c muestra esquemáticamente un circuito que tiene un circuito de prueba de acuerdo con una modalidad adicional;

- la Figura 7d muestra esquemáticamente otro ejemplo de forma de onda de accionamiento; y

- la Figura 8 muestra esquemáticamente un circuito de prueba implementado como un circuito dedicado.

- 35 La Figura 1a muestra esquemáticamente una sección transversal a través de parte de un cabezal de deposición de gotas conocido, en adelante "cabezal de impresión". El cabezal de impresión puede ser parte de un aparato de deposición de gotas conocido, en lo sucesivo "impresora".

En el presente ejemplo ilustrativo, el cabezal de impresión 1 comprende al menos una cámara de presión 2, teniendo la cámara de presión 2 una membrana 3 con un elemento actuador 4 que se proporciona en la misma para efectuar el movimiento de la membrana 3 entre una primera posición (representada como P1), aquí se muestra como una posición neutra, hacia adentro en la cámara de presión a una segunda posición (representada como P2). También se entenderá que el elemento actuador 4 también podría estar dispuesto para desviar la membrana en una dirección desde P1 opuesta a la de P2 (es decir, hacia fuera de la cámara de presión).

- 45 La cámara de presión 2 comprende un puerto de entrada fluídica 14 para recibir fluido desde un depósito 16 dispuesto en comunicación fluídica con la cámara de presión 2.

El depósito 16 se representa simplemente adyacente a la cámara de presión 2 con fines ilustrativos. Sin embargo, se puede proporcionar más arriba o alejado del cabezal de impresión mediante el uso de una serie de bombas/válvulas para regular el flujo de fluido desde el mismo/hacia el mismo según sea apropiado.

En los presentes ejemplos, el elemento actuador 4 se representa como un elemento actuador piezoelectrónico 4 de manera que se proporciona un material piezoelectrónico 6 entre un primer electrodo 8 y un segundo electrodo 10 de manera que la aplicación de un campo eléctrico a través del elemento actuador 4 provoca que el elemento actuador 4 para cargar, por lo que experimenta una fuerza y se deforma. Se debe entender que el elemento actuador no se limita a ser un elemento actuador piezoelectrónico, y cualquier elemento actuador 4 adecuado que demuestre una respuesta capacitiva puede usarse según sea apropiado.

60 En el ejemplo esquemático en la Figura 1, la cámara de presión 2 está dispuesta en lo que se denomina comúnmente configuración de "modo techo", de manera que la deflexión de la membrana 3 cambia el volumen y, por lo tanto, la presión, dentro de la cámara de presión 2. Aplicando una secuencia de deflexión adecuada a la membrana 3, se genera suficiente presión positiva dentro de la cámara de presión 2 para expulsar una o más gotas de la misma.

65 Tal expulsión de gotas desde la boquilla 12 se puede lograr aplicando uno o más pulsos de activación en forma de onda de tensión al elemento actuador asociado 4, por ejemplo al primer electrodo 8, mientras se mantiene el electrodo

inferior 10 a un potencial de referencia tal como potencial de tierra. Diseñando cuidadosamente la forma de onda de accionamiento, es posible lograr una expulsión de gotas predecible y uniforme desde la boquilla 12.

5 En modalidades, el cabezal de impresión 1 puede comprender una pluralidad de elementos actuadores y boquillas asociadas dispuestas en una o más series sobre el mismo.

10 En modalidades, una forma de onda de accionamiento común que comprende una secuencia de uno o más pulsos de accionamiento puede ser generada por un circuito de accionamiento y aplicada selectivamente a una pluralidad de elementos actuadores como una forma de onda de accionamiento para expulsar gotas de las boquillas asociadas con el mismo.

15 Alternativamente, se puede generar una forma de onda de accionamiento que comprende una secuencia de uno o más pulsos de excitación por elemento actuador. Tal forma de onda de accionamiento puede generarse, por ejemplo, mediante circuitos de accionamiento sobre, o en comunicación con, el cabezal de impresión.

20 Como entenderá un experto en la técnica, la expulsión de las gotas puede sincronizarse para que caigan con precisión en un medio receptor (junto con la regulación del movimiento de un medio receptor, cuando sea necesario) dentro de áreas predeterminadas definidas como píxeles.

25 Estos píxeles se basan en una rasterización de la imagen que se imprimirá derivada de los datos de impresión y se usan para determinar la posición conveniente del punto resultante en el medio receptor.

En una representación binaria simple, cada píxel se llenará con una gota o ninguna.

30 En una representación más compleja, se pueden agregar niveles de escala de grises imprimiendo dos o más gotas en cada píxel para alterar la densidad de color percibida del píxel resultante.

35 Si bien en la Figura 1a se representa solo una cámara de presión 2, se debe entender que se puede disponer cualquier número de cámaras de presión en una configuración o configuraciones adecuadas en el cabezal de impresión 1.

40 El cabezal de impresión 1 y las características asociadas del mismo (por ejemplo, boquilla(s), elemento(s) actuador(es), membrana(s), puerto(s) de fluido, etc.) se pueden fabricar mediante el uso de cualquier proceso o técnica de fabricación adecuada, como sistemas microelectromecánicos (MEMS) o procesos de fabricación a granel.

45 Se debe entender que las técnicas descritas en la presente descripción no se limitan a los cabezales de impresión que operan en configuraciones de modo de techo, y se aplican igualmente a los cabezales de impresión que tienen otras configuraciones, tales como configuraciones de pared compartida.

50 La Figura 1b muestra esquemáticamente un ejemplo de un circuito de cabezal de impresión 100 que comprende una serie de elementos actuadores 105 que tienen una pluralidad de elementos actuadores 4 como se describió anteriormente.

55 El circuito de cabezal de impresión 100 se proporciona en comunicación eléctrica con un circuito de accionamiento 102, de manera que el circuito de accionamiento 102 genera una forma de onda de accionamiento, por ejemplo, mediante el uso de un amplificador (no mostrado).

60 El circuito de accionamiento 102 está dispuesto en comunicación eléctrica con un circuito de conmutación 104, por lo que el circuito de conmutación 104 comprende una pluralidad de interruptores 106 para aplicar selectivamente la forma de onda de accionamiento a la pluralidad de elementos actuadores 4 de la serie de elementos actuadores 105.

65 En el presente ejemplo, los interruptores 106 están conectados al circuito de accionamiento 102 a través de una pista eléctrica 108 y el bus 107 que es común a todos los interruptores 106. En ejemplos alternativos, los interruptores 106 pueden estar conectados cada uno al circuito de accionamiento 102 a través de pistas eléctricas individuales. Cada interruptor 106 está conectado a un elemento actuador asociado 4 a través de una pista de actuador individual 109 entre ellos.

70 El circuito de conmutación 104 puede ser un circuito integrado y puede comprender, por ejemplo, un circuito integrado específico de aplicación (ASIC). El circuito de conmutación 104 es funcionalmente similar a un multiplexor en que se puede controlar un interruptor particular para que, por ejemplo, se encienda (por ejemplo, se cierre) para proporcionar un elemento actuador correspondiente en comunicación eléctrica con el circuito de accionamiento, por lo que una forma de onda de accionamiento puede ser aplicado al elemento actuador 4; o el interruptor particular puede controlarse para que, por ejemplo, se apague (por ejemplo, se abra) para aislar eléctricamente el elemento actuador del circuito de accionamiento 102. Para simplificar, la ruta eléctrica entre el circuito de accionamiento y un elemento actuador 4 se denominará "ruta de accionamiento".

- En el presente ejemplo ilustrativo, los elementos actuadores 4 son 10 elementos actuadores piezoelectrinos y, por lo tanto, el comportamiento eléctrico de cada elemento actuador 4 es similar a un capacitor, de manera que cada elemento actuador 4 tiene una capacitancia asociada  $C_{ACT}$ . Se debe entender que  $C_{ACT}$  también puede incluir la capacitancia de los circuitos (por ejemplo, componentes/lógica/funciones) asociados con el elemento actuador 4, tal como la capacitancia de su pista 109 del actuador o la capacitancia de una conexión física para conectar el elemento actuador a la pista 109 del actuador.

- Los diferentes circuitos/componentes del circuito del cabezal de impresión 100 también tendrán capacitancias asociadas. Para los fines de la presente solicitud, las capacitancias distintas de las asociadas con los elementos actuadores  $C_{ACT}$  se toman como "capacitancias parásitas".

- En la Figura 1b, todas las capacitancias parásitas en el circuito del cabezal de impresión 100 se representan como  $C_{PAR}$  e incluyen: la capacitancia parásita ( $C_{ruta}$ ) de la pista eléctrica 108; la capacitancia parásita combinada ( $C_{todoslosinterruptores}$ ) de todos los interruptores 106, la capacitancia parásita ( $C_{interruptor}$ ) de interruptores individuales 106; y otras capacitancias parásitas ( $C_{otro}$ ) tales como los asociados con, por ejemplo, el circuito de accionamiento 102 y las conexiones entre componentes en el circuito del cabezal de impresión 100. Tales componentes pueden incluir enlaces físicos entre el circuito de accionamiento 102 y la pista eléctrica 108, o entre el circuito de conmutación 104 y la pista eléctrica 108. Tales enlaces pueden incluir enlaces de película conductora anisotrópica.

- Como se detalla anteriormente, es útil realizar una o más pruebas de diagnóstico, por ejemplo, para determinar la capacitancia de un elemento actuador y/o para detectar un circuito abierto o cortocircuito en la serie de elementos actuadores 105 después de la fabricación y antes y después del ensamblaje en un cabezal de impresión. En algunos ejemplos, una capacitancia determinada puede ser indicativa de un circuito abierto o un cortocircuito. Por ejemplo, una capacitancia determinada por debajo de una capacitancia umbral predefinida puede ser indicativa de un circuito abierto.

- Sin embargo, tales pruebas son difíciles de realizar, por ejemplo, debido al posicionamiento de la serie de elementos actuadores en el cabezal de impresión o tales pruebas pueden ser inexactas debido, por ejemplo, a las capacitancias parásitas que afectan los resultados de las pruebas.

- La Figura 2a muestra esquemáticamente un ejemplo de un circuito de prueba 200 para realizar pruebas de diagnóstico en un elemento actuador 4 del circuito de cabezal de impresión 100 de acuerdo con una modalidad. La numeración similar se usará para describir características similares en todas partes.

- El circuito de prueba 200 está dispuesto en comunicación eléctrica con uno o más elementos actuadores 4 a través de la pista eléctrica 108 y el correspondiente interruptor 106 de la lógica de conmutación 104 (sólo se representa un elemento de accionamiento 4 en la Figura 2a).

- Para simplificar, la ruta eléctrica entre el circuito de prueba 200 y el conjunto de actuadores 105 se toma como una "ruta de prueba", de manera que los interruptores 106 pueden controlarse para conectar o aislar eléctricamente uno o más elementos actuadores a la ruta de prueba según sea apropiado.

- En la Figura 2a, el circuito de prueba 200 se representa en comunicación eléctrica con el circuito del cabezal de impresión 100, por ejemplo, a través de una interfaz en la impresora o cabezal de impresión. En otros ejemplos, el circuito de prueba 200 puede integrarse como parte del circuito de cabezal de impresión 100.

- El circuito de prueba 200 comprende el controlador 202, la fuente 204 y el circuito de medición 205.

- El controlador 202 puede comprender, por ejemplo, una serie de puertas programables en campo (FPGA), un microcontrolador u otro circuito adecuado (por ejemplo, componentes, lógica, funciones).

- El controlador 202 interactúa con varios circuitos y componentes dentro del circuito de prueba 200, como el circuito de cabezal de impresión 100, el circuito de accionamiento (no mostrado en la Figura 2a) y/u otros circuitos de la impresora (no mostrados). Por ejemplo, el controlador 202 controla los interruptores 106, de manera que uno o más elementos actuadores 4 pueden conectarse al circuito de prueba 200 para pruebas de diagnóstico en cualquier momento.

- En los siguientes ejemplos ilustrativos, la fuente 204 es una fuente de corriente para generar corriente constante ( $i_M$ ), cuyo nivel está definido por el controlador 202. Como resultará evidente, la fuente 204 de corriente tiene preferentemente una alta impedancia de salida para la carga lineal de los elementos actuadores para mejorar la precisión de la medición de capacitancia.

- El circuito de medición 205 está dispuesto para detectar o medir y procesar uno o más valores en una ruta de prueba durante la prueba de diagnóstico.

- En el presente ejemplo ilustrativo, el circuito de medición 205 comprende las fuentes 208, 209 y comparadores 210, 211 y temporizador 212.

Se proporciona un interruptor de reinicio 206 para descargar la ruta de prueba y puede ser cualquier elemento conmutador adecuado (por ejemplo, un transistor NMOS), que conecta la ruta de prueba a una tensión de referencia (por ejemplo, tierra). El interruptor de reinicio 206 es controlable por el controlador 202.

5 Las fuentes 208, 209, que, en los siguientes ejemplos, se representan como convertidores de digital a analógico (DAC), generan cada una un nivel de tensión definido (representado como  $V_{ALTO}$  de DAC 208 y  $V_{BAJO}$  de DAC 209). Los niveles de tensión generados por los DAC 208, 209 pueden definirse en respuesta a una señal (no mostrada) del controlador 202.

10 Cada uno de los comparadores 210, 211 usa uno de los niveles de tensión definidos por los DAC 208, 209 como primera entrada y tensión  $V_X$  desde la ruta de prueba como segunda entrada. En la Figura 2a, una primera entrada al comparador 210 es  $V_{ALTO}$  desde el DAC 208, mientras que una primera entrada al comparador 211 es  $V_{BAJO}$  desde el DAC 209.

15 El temporizador 212 recibe la salida de los comparadores 210, 211 y mide la transición de  $V_X$  de  $V_{BAJO}$  a  $V_{ALTO}$ . El temporizador 212 funciona a una frecuencia de reloj  $F_{CLK}$ , generado por cualquier fuente adecuada para funcionar a cualquier frecuencia adecuada (por ejemplo,  $\sim 10$  MHz). Se apreciará que la precisión de las mediciones a partir del mismo se puede mejorar aumentando la frecuencia del reloj. El temporizador 212 puede implementarse en una FPGA o el microcontrolador, o puede implementarse como un circuito integrado dedicado (IC). En ejemplos alternativos, el temporizador 212 puede estar integrado dentro del controlador 202.

20 El circuito de prueba 200 puede usarse para determinar la capacitancia  $C_{ACT}$  de un elemento actuador 4 de manera que la Figura 2b muestra gráficamente una medición obtenida mediante el uso del circuito de prueba 200 para determinar  $C_{ACT}$  de acuerdo con una modalidad.

25 Como ejemplo ilustrativo, para un primer período de prueba  $P_1$ , habiendo reiniciado el controlador 202 la capacitancia en la ruta de prueba cerrando el interruptor de reinicio 206 para descargar las capacitancias parásitas  $C_{PAR}$  (y en algunos ejemplos la capacitancia  $C_{ACT}$ ), cierra el interruptor 106 y abre el interruptor de reinicio 206 de manera que una entrada de prueba que comprende la corriente  $i_M$  carga las capacidades combinadas  $C_{PAR} + C_{ACT}$ , por lo que, como se muestra en la Figura 2b, la tensión  $V_X$  aumenta con el tiempo ( $T$ ) a una velocidad dada por la ecuación (1):

$$35 \quad (1) \left| \frac{dV}{dt} \right|_1 = \frac{(i_M)}{(C_{PAR} + C_{ACT})}$$

35  $V_X$  es una entrada para los comparadores 210, 211 y como  $V_X$  sube, el temporizador 212 mide el tiempo de transición ( $t_1$ ) entre la conmutación del comparador  $V_{BAJO}$  211 (es decir,  $V_X$  pasando  $V_{BAJO}$ ) y el cambio del comparador  $V_{ALTO}$  210 (es decir,  $V_X$  pasando  $V_{ALTO}$ ).

40 El tiempo de transición medido ( $t_1$ ) se obtiene de las ecuaciones (2) y (3):

$$45 \quad (2) \left| \frac{dV}{dt} \right|_1 = \frac{(V_{ALTO} - V_{BAJO})}{t_1}$$

$$(3) t_1 = \frac{(C_{PAR} + C_{ACT})(V_{ALTO} - V_{BAJO})}{i_M}$$

50 Por lo tanto, la capacitancia total se determina a partir de (4):

$$50 \quad (4) (C_{PAR} + C_{ACT}) = \frac{i_M t_1}{(V_{ALTO} - V_{BAJO})}$$

55 Por tanto,  $C_{ACT}$  se puede calcular a partir de (5):

$$60 \quad (5) C_{ACT} = \frac{i_M t_1}{(V_{ALTO} - V_{BAJO})} - C_{PAR}$$

65 Sin embargo, como  $C_{PAR}$  es desconocido,  $(C_{PAR} + C_{ACT})$  no proporciona una determinación precisa de  $C_{ACT}$ , y  $C_{ACT}$  por lo tanto, es posible que no indique de manera concluyente la presencia o ausencia de un circuito abierto.

65 Si bien se puede tomar un valor estimado para las capacitancias parásitas  $C_{PAR}$ , las variaciones de lote a lote para todos los circuitos pueden afectar las capacitancias parásitas y del actuador y, por lo tanto, pueden aumentar la dificultad para estimar con precisión las capacitancias parásitas.

Por lo tanto, para determinar con mayor precisión  $C_{ACT}$ , el circuito de prueba realiza dos mediciones durante dos períodos  $P_1'$  y  $P_2'$ , de manera que la Figura 2c muestra gráficamente las mediciones obtenidas mediante el uso del circuito de prueba 200 para determinar  $C_{ACT}$  de acuerdo con una modalidad adicional.

Para el primer período  $P_1'$ , que puede tomarse como un período de calibración, el controlador 202, habiendo reiniciado las capacitancias en la ruta de prueba, abre el interruptor 106 y abre el interruptor de reinicio 206 de manera que la corriente de entrada de prueba  $i_M$  carga la capacitancia parásita  $C_{PAR}$  durante  $P_1'$ , por lo que, como se muestra en la Figura 2c, la tensión  $V_X$  aumenta con el tiempo a una velocidad dada por (6):

$$(6) \left| \frac{dV}{dt} \right|_1 = \frac{(i_M)}{(C_{PAR})}$$

Como  $V_X$  sube, el temporizador 212 mide el tiempo de transición ( $t_1$ ) entre la conmutación del comparador  $V_{BAJO}$  211 y la conmutación del comparador  $V_{ALTO}$  210.

El tiempo de transición medido ( $t_1$ ) se obtiene de (7):

$$(7) t_1 = \frac{(C_{PAR})(V_{ALTO} - V_{BAJO})}{i_M}$$

Por lo tanto, la capacitancia parásita se determina a partir de (8):

$$(8) C_{PAR} = \frac{i_M t_1}{(V_{ALTO} - V_{BAJO})}$$

Por un segundo período  $P_2'$ , que puede tomarse como un período de prueba, el controlador 202 cierra el interruptor de reinicio 206 para reiniciar la capacitancia en la ruta de prueba, y luego cierra el interruptor 106 y abre el interruptor de reinicio 206 de manera que prueba la corriente de entrada  $i_M$  carga las capacidades combinadas  $C_{PAR} + C_{ACT}$ , por lo que, como se muestra en la Figura 2c, la tensión  $V_X$  aumenta con el tiempo a una velocidad dada por (9):

$$(9) \left| \frac{dV}{dt} \right|_2 = \frac{(i_M)}{(C_{PAR} + C_{ACT})}$$

Como  $V_X$  sube, el temporizador 212 mide el tiempo de transición  $t_2$  entre la conmutación del comparador  $V_{BAJO}$  211 y la conmutación del comparador  $V_{ALTO}$  210 viene dado por (10a).

$$(10a) t_2 = \frac{(C_{PAR} + C_{ACT})(V_{ALTO} - V_{BAJO})}{i_M}$$

Por lo tanto, la capacitancia total se puede determinar a partir de 10b, de manera que

$$(10b) (C_{PAR} + C_{ACT}) = \frac{i_M t_2}{(V_{ALTO} - V_{BAJO})}$$

y sustituyendo  $C_{PAR}$  de (8) es posible determinar  $C_{ACT}$ :

$$(11) C_{(ACT)} = \frac{i_M}{(V_{ALTO} - V_{BAJO})} \cdot (t_2 - t_1)$$

Por lo tanto, cuando se usa un período de calibración para determinar primero  $C_{PAR}$  es posible determinar con mayor precisión  $C_{ACT}$  en comparación con la estimación de  $C_{PAR}$ . También es posible, por lo tanto, detectar con mayor precisión la presencia o ausencia de un circuito abierto basado en, o en respuesta a,  $C_{ACT}$ .

La Figura 3a muestra esquemáticamente un ejemplo de un interruptor 106 y un circuito de control de conmutación 300 de acuerdo con una modalidad, y la Figura 3b muestra un ejemplo de una forma de onda de accionamiento 310 utilizada para accionar uno o más elementos actuadores.

En el presente ejemplo ilustrativo, el interruptor 106 comprende dos elementos interruptores, representados como transistores 302, 304 dispuestos en serie, por ejemplo, en una configuración de puerta de acceso. Tal disposición proporciona operaciones de alta tensión y alta corriente durante la impresión. Si bien los elementos de conmutación del interruptor 106 se representan como transistores, los elementos de conmutación no se limitan a ser transistores, ni el número de elementos de conmutación se limita a dos.

Es ventajoso minimizar la resistencia ON del interruptor 106 para minimizar la disipación de potencia en el circuito del cabezal de impresión (por ejemplo, reduciendo las pérdidas del conductor ( $I^2R$ )), y para optimizar la forma (por ejemplo, los bordes y velocidades de rotación) de la forma de onda de accionamiento 310 para obtener una velocidad de gota y un volumen de gota deseados.

En el presente ejemplo ilustrativo, los transistores 302, 304 comparten una fuente común. El drenaje del transistor 302 está dispuesto en comunicación eléctrica con el circuito de accionamiento/circuito de prueba (no mostrado) a través del terminal 306, y el drenaje del transistor 304 está dispuesto en comunicación eléctrica con un elemento actuador (no mostrado) a través del terminal 308. Cada transistor 302, 304 también tiene un diodo 316, 318 respectivo dispuesto entre su fuente y drenaje de manera que la corriente fluya desde la fuente al drenaje (como se indica mediante flechas). Cada uno de los diodos 316, 318 puede ser un diodo intrínseco en los transistores 302, 304.

Para encender el interruptor 106 (es decir, cerrar el interruptor), se aplica una diferencia de potencial de aproximadamente 5 V entre la fuente y la puerta de cada transistor 302, 304.

A medida que las formas de onda de accionamiento cambian entre diferentes tensiones, como la forma de onda de accionamiento 310 representada en la Figura 3b que cambia entre 0V y 20V, se requiere que la tensión en la fuente común responda a las diferentes tensiones para que los transistores 302, 304 permanezcan encendidos cuando sea necesario.

Tal control se proporciona por el circuito de control de conmutación 300 que comprende un cambiador de nivel 301 configurado para generar una tensión variable que se encuentra encima de la tensión de fuente común para proporcionar la diferencia de potencial necesaria a medida que la forma de onda de accionamiento 310 cambia entre las diferentes tensiones.

El cambiador de nivel 301 se alimenta a través del terminal 312, mientras que la tensión variable puede generarse en respuesta a las señales de nivel recibidas a través del terminal 314, por ejemplo, de un circuito de accionamiento.

Una corriente parásita  $i_p$  es generada por el cambiador de nivel 301, de manera que  $i_p$  fluye a través de la fuente común cuando el interruptor 106 está cerrado y también fluye a través de la fuente común cuando se abre el interruptor 106.

Una persona experta en la técnica entenderá que en otras modalidades una corriente parásita  $i_p$  puede ser generada por componentes/circuitos distintos del cambiador de nivel.

Cuando se abre el interruptor 106,  $i_p$  puede fluir al terminal 306, a través del diodo 316, donde será sumida (por ejemplo, por un amplificador en un circuito de accionamiento). Adicionalmente, o alternativamente, la corriente  $i_p$  puede fluir al terminal 308 a través del diodo 318, de manera que cargará el elemento actuador en comunicación eléctrica con él. Por lo tanto,  $i_p$  se verá que es una corriente parásita cuando se abre el interruptor 106.

Para controlar la dirección hacia donde fluye  $i_p$  cuando el interruptor 106 está apagado, las tensiones a cada lado del interruptor 106 (por ejemplo, en los terminales 306, 308) pueden ser establecidos por el circuito de prueba 200, por ejemplo, usando un DAC adicional (no mostrado en la Figura 3), para polarizar los terminales 306, 308 (o los circuitos en comunicación con ellos, tales como los elementos actuadores). Por lo tanto, el circuito de prueba 200 puede polarizar los terminales 306, 308 para asegurar que  $i_p$  no fluya a través del diodo 318 cuando se abre el interruptor 106.

La Figura 4a muestra esquemáticamente un ejemplo de un circuito de prueba 200 para realizar pruebas de diagnóstico en un elemento actuador 4 de un circuito de cabezal de impresión 100 de acuerdo con una modalidad, de manera que el elemento actuador 4 está conectado a un interruptor 106 que tiene un circuito de control de conmutación asociado 300, por lo que una corriente parásita  $i_p$  carga el elemento actuador 4 como se describió anteriormente.

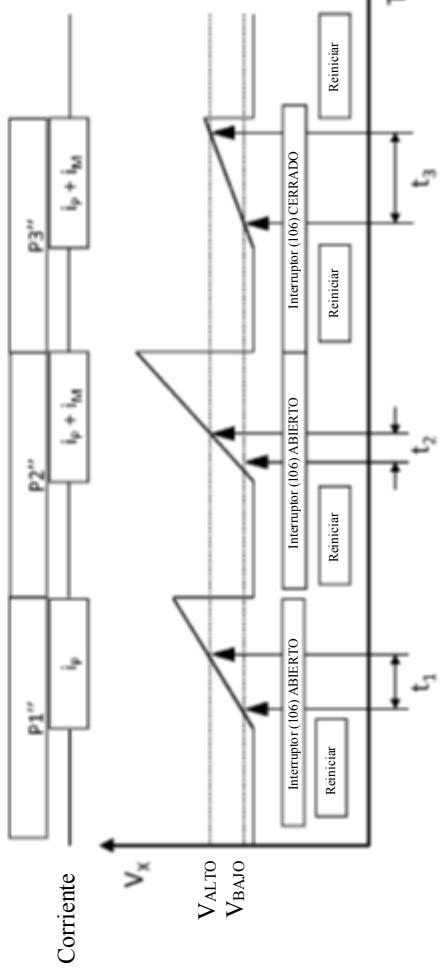

La Figura 4b muestra gráficamente las mediciones obtenidas mediante el uso del circuito de prueba 200 de la Figura 4a para determinar  $C_{ACT}$  de acuerdo con una modalidad adicional.

Como anteriormente, puede ser útil determinar la capacitancia  $C_{ACT}$  del elemento actuador 4. Sin embargo, existen múltiples incógnitas en el circuito que se muestra en la Figura 4a. Por ejemplo, la capacitancia del actuador ( $C_{ACT}$ ), la capacitancia parásita ( $C_{PAR}$ ) y la corriente parásita ( $i_p$ ) son desconocidas.

Por lo tanto, para determinar con mayor precisión  $C_{ACT}$ , el circuito de prueba 202 realiza tres mediciones durante tres períodos de tiempo  $P_1''$ ,  $P_2''$  y  $P_3''$ .

Para el primer período  $P_1''$ , que puede tomarse como un primer período de calibración, el controlador abre el interruptor de reinicio 206, cierra el interruptor 106 y controla la fuente de corriente 204 para generar  $i_M$  para polarizar los terminales del interruptor 106 y/o el elemento actuador 4 para controlar la dirección de  $i_p$  de manera que una entrada de prueba que comprenda  $i_p$  cargará la capacitancia parásita  $C_{PAR}$ .

Cuando el elemento actuador 4 está polarizado, el controlador 202 abre el interruptor 106 para aislar eléctricamente el elemento actuador 4 de la ruta de prueba, y cierra el interruptor de reinicio 206 y controla la fuente de corriente 204 para evitar que  $i_M$  fluya, de modo que  $C_{PAR}$  se descargue en la ruta de prueba.

El controlador 202 abre el interruptor de reinicio 206, abre el interruptor 106 y controla la fuente 204 de corriente para evitar que  $i_M$  fluya.

Como se representa en la Figura 4b, la tensión  $V_X$  aumenta con el tiempo durante  $P_1''$  en respuesta a  $i_p$  a una velocidad de respuesta  $SR_1$  dada por:

$$(12) SR_1 = \left| \frac{dV}{dt} \right|_1 = \frac{(i_p)}{(C_{PAR})}$$

Para un segundo período  $P_2''$ , que puede tomarse para representar un segundo período de calibración, el controlador 202 cierra el interruptor 106, abre el interruptor de reinicio 206 y controla la fuente de corriente 204 para generar  $i_M$  para polarizar los terminales del interruptor 106 y/o el elemento actuador 4 para controlar la dirección de  $i_p$  de manera que una entrada de prueba que comprenda  $i_p$  cargará la capacitancia parásita  $C_{PAR}$ .

El controlador 202 abre entonces el interruptor 106 para aislar eléctricamente el elemento actuador 4 de la ruta de prueba y cierra el interruptor de reinicio 206 y controla la fuente de corriente 204 para evitar que  $i_M$  fluya de manera que  $C_{PAR}$  se descargue en la ruta de prueba.

El controlador 202 abre el interruptor de reinicio 206, abre el interruptor 106 y controla la fuente 204 de corriente para generar  $i_M$  de manera que una entrada de prueba que comprenda  $(i_p + i_M)$  carga la capacitancia parásita  $C_{PAR}$  durante el segundo período de calibración  $P_2''$ .

Como se representa en la Figura 4b, la tensión  $V_X$  sube, durante  $P_2''$ , a una velocidad variable  $SR_2$  dada por:

$$(13) SR_2 = \left| \frac{dV}{dt} \right|_2 = \frac{(i_p + i_M)}{(C_{PAR})}$$

Por lo tanto, de (12) y (13):

$$(14) \frac{(SR_2)}{(SR_1)} = \frac{(i_p + i_M)}{(i_p)}$$

Para un tercer período  $P_3''$ , que puede tomarse para representar un período de prueba, el controlador 202 cierra el interruptor 106 para conectar eléctricamente el elemento actuador 4 a la ruta de prueba, cierra el interruptor de reinicio 206 y controla la fuente de corriente 204 para evitar que  $i_M$  fluya de manera que  $C_{PAR}$  se descargue en la ruta de prueba.

El controlador 202 abre el interruptor de reinicio 206, cierra el interruptor 106 y controla la fuente 204 de corriente para generar  $i_M$  tal que una entrada de prueba que comprenda  $(i_p + i_M)$  carga los capacitores parásitos y actuadores combinados a una capacitancia total ( $C_{PAR} + C_{ACT}$ ) durante  $P_3''$ .

Como se representa en la Figura 4b, la tensión  $V_X$  sube, durante  $P_3''$ , a una velocidad variable  $SR_3$  dada por:

$$(15) SR_3 = \left| \frac{dV}{dt} \right|_3 = \frac{(i_p + i_M)}{(C_{PAR} + C_{ACT})}$$

La velocidad de respuesta para un período de transición dado  $z$  viene dada por:

$$(16) SR_z = \frac{(V_{ALTO} - V_{BAJO})}{t_z}; \text{ o } t_z = \frac{(V_{ALTO} - V_{BAJO})}{SR_z}$$

Por lo tanto, reformular (14) proporciona:

$$5 \quad (17) \frac{(i_p + i_M)}{(i_p)} = \frac{\left( \frac{(V_{ALTO} - V_{BAJO})}{t_2} \right)}{\frac{(V_{ALTO} - V_{BAJO})}{t_1}} = \frac{(t_1)}{(t_2)}$$

10 Por lo tanto:

$$(18) \frac{(i_M)}{(i_p)} = \frac{(t_1)}{(t_2)} - 1$$

15 Además, reformulando (15) y sustituyendo para  $SR_3$  proporciona:

$$20 \quad (19) C_{ACT} = \frac{(i_M + i_p)t_3}{(V_{ALTO} - V_{BAJO})} - C_{PAR}$$

De (12) y (16):

$$25 \quad (20) i_p = C_{PAR} \frac{(V_{ALTO} - V_{BAJO})}{t_1}, \quad C_{PAR} = \frac{i_p t_1}{(V_{ALTO} - V_{BAJO})}$$

Sustituyendo por  $i_p$  y  $C_{PAR}$  de (20) a (19) da:

$$30 \quad (21) C_{ACT} = \frac{(i_M + i_p)t_3}{(V_{ALTO} - V_{BAJO})} - \frac{i_p t_1}{(V_{ALTO} - V_{BAJO})} = \frac{i_M t_3 + i_p(t_3 - t_1)}{(V_{ALTO} - V_{BAJO})} = \frac{i_M}{(V_{ALTO} - V_{BAJO})} \cdot \left[ t_3 + \frac{i_p}{i_M} (t_3 - t_1) \right]$$

35 La reformulación proporciona:

$$40 \quad (22) C_{ACT} = \frac{i_M}{(V_{ALTO} - V_{BAJO})} \cdot \left[ t_3 + \frac{(t_3 - t_1)}{\left( \frac{i_M}{i_p} \right)} \right]$$

La sustitución de (18) en (22) proporciona:

$$45 \quad (23) C_{ACT} = \frac{i_M}{(V_{ALTO} - V_{BAJO})} \cdot \left[ t_3 + \frac{(t_3 - t_1)}{\left( \frac{t_1}{t_2} - 1 \right)} \right]$$

50 La reformulación resulta en:

$$(24) C_{ACT} = \frac{i_M}{(V_{ALTO} - V_{BAJO})} \cdot \left[ t_3 + \frac{t_2(t_3 - t_1)}{(t_1 - t_2)} \right]$$

55 De (24),  $C_{ACT}$  se puede determinar a partir de los tres tiempos de transición medidos  $t_1$ ,  $t_2$  y  $t_3$  junto con la corriente controlada  $i_M$  y la diferencia establecida entre  $V_{ALTO}$  y  $V_{BAJO}$ .

60 En las modalidades descritas anteriormente, los valores de  $V_{ALTO}$  y  $V_{BAJO}$  son sustancialmente iguales para los diferentes períodos (por ejemplo, período de calibración/prueba). Sin embargo, en modalidades alternativas, los valores respectivos de  $V_{ALTO}$  y  $V_{BAJO}$  pueden modificarse durante un período determinado para aumentar la precisión de la determinación de  $C_{ACT}$ .

65 Si bien es posible controlar el cambiador de nivel de la Figura 3a para evitar que  $i_p$  fluya mientras el interruptor 106 está abierto,  $i_p$  fluiría cuando el interruptor 106 está cerrado independientemente del control del cambiador de nivel.

Sin embargo, a menos que  $i_p$  se mida mientras el interruptor está abierto, no sería determinable y, por lo tanto, disminuiría la precisión de la  $C_{ACT}$  determinada.

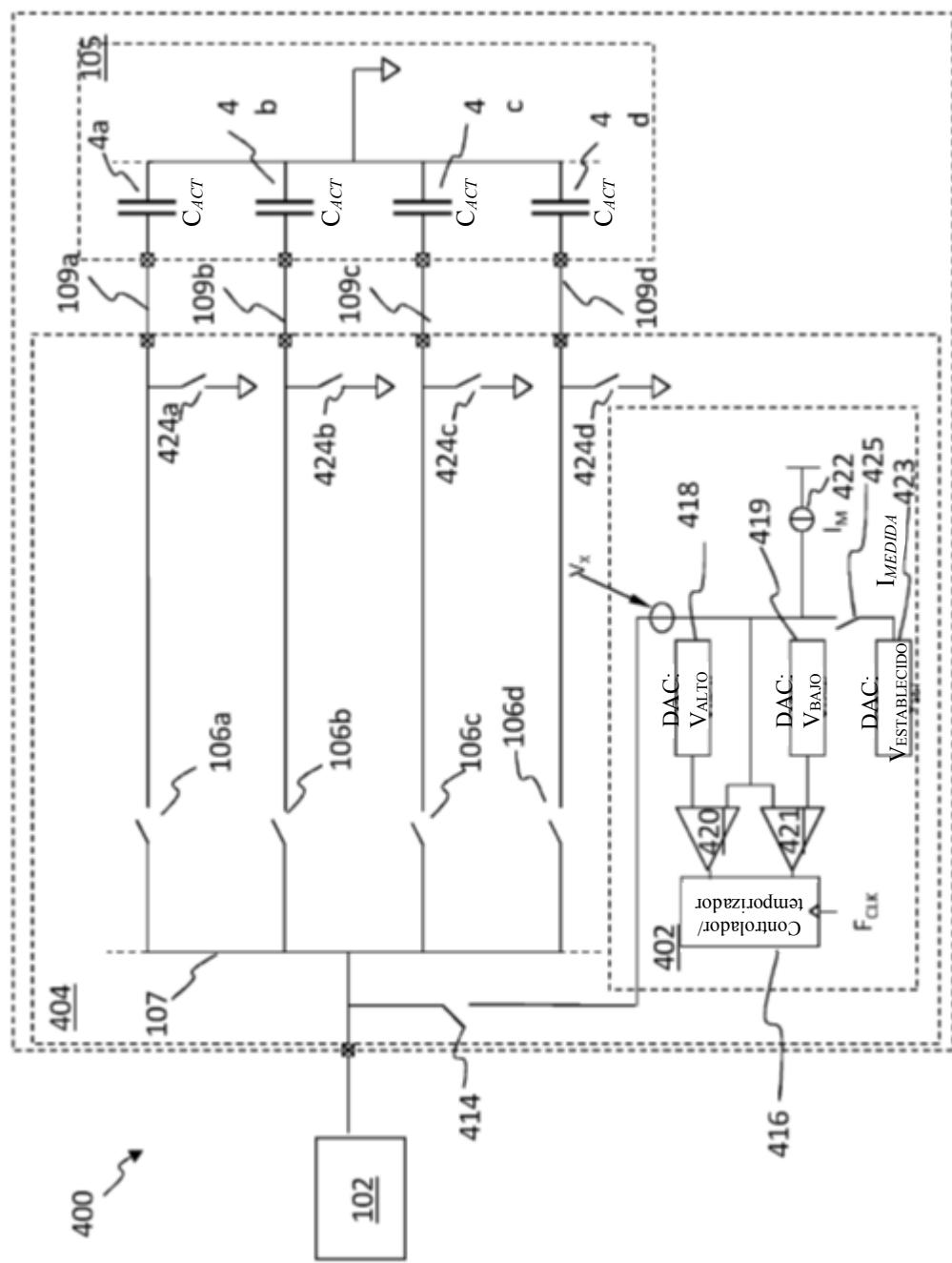

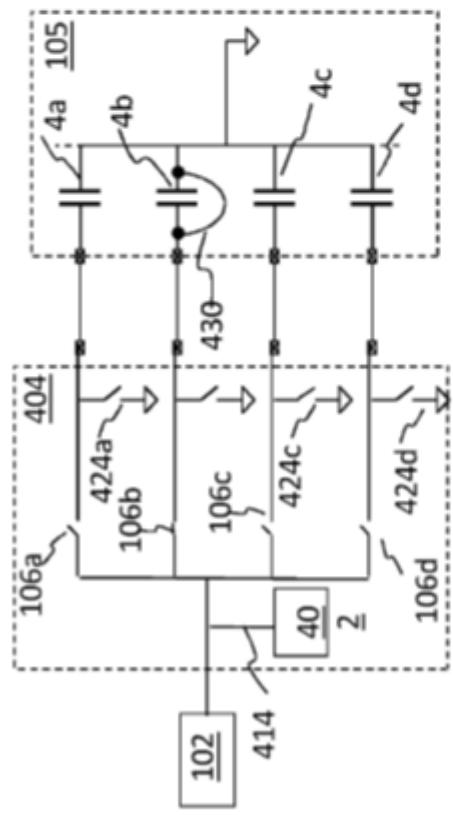

- 5 La Figura 5a muestra esquemáticamente un circuito de cabezal de impresión 400 de acuerdo con una modalidad adicional, de manera que el circuito de prueba 402 está incorporado dentro de un circuito de conmutación 404 del circuito de cabezal de impresión 400, de manera que el circuito de cabezal de impresión 400 también incluye la serie de elementos actuadores 105 como se describió anteriormente.

- 10 Como anteriormente, la serie de elementos actuadores 105 comprende una pluralidad de elementos actuadores 4a-4d dispuestos en comunicación eléctrica con un circuito de accionamiento 102 a través de un bus 107, de manera que un interruptor 106 conecta selectivamente un elemento actuador asociado a una ruta de accionamiento según sea necesario.

- 15 El circuito de prueba 402 está dispuesto en comunicación eléctrica con la pluralidad de elementos actuadores 4a-4d, de manera que un interruptor de prueba 414 conecta selectivamente el circuito de prueba 402 al bus 107. El interruptor de prueba 414 puede adoptar cualquier forma adecuada y, por ejemplo, puede comprender uno o más transistores.

- 20 Un elemento actuador 4 a probar también se conecta al bus 107 y al circuito de prueba (cuando el interruptor 414 está cerrado) encendiendo un interruptor asociado 106a-d.

- 25 Generalmente, el circuito de prueba 402 operará a tensiones de aproximadamente 5 V, mientras que el circuito de accionamiento 102 generará formas de onda de >5 V. Por lo tanto, el interruptor de prueba 414 puede aislar eléctricamente el circuito de prueba 402 de la ruta de accionamiento, por ejemplo, cuando el circuito de accionamiento 102 está accionando uno o más de los elementos actuadores, para evitar que el circuito de prueba 402 sea dañado por las corrientes/tensiones de accionamiento.

- 30 El controlador 416 puede usarse para controlar el interruptor de prueba 414 (por ejemplo, en respuesta a una señal del circuito de accionamiento u otro circuito).

- 35 El circuito de prueba 402 es similar a los circuitos de prueba descritos en las Figuras 2a y 4a, de manera que en el presente ejemplo, el circuito de prueba 402 comprende los DAC 418, 419 para generar  $V_{ALTO}$  y  $V_{BAJO}$ ; los comparadores 420, 421; y la fuente de corriente 422 para generar la corriente constante  $i_M$ . El temporizador se muestra integrado en el controlador 402.

- 40 El circuito de prueba 402 comprende además DAC 423 para generar  $V_{Establecido}$ , que cuando el interruptor de polarización 425 está cerrado puede polarizar los circuitos en la ruta de prueba para, por ejemplo, controlar la dirección del flujo de la corriente parásita  $i_p$ .

- 45 El circuito de prueba 402 puede usarse para determinar la capacitancia de uno o más de los elementos actuadores 4 y, por lo tanto, detectar un circuito abierto en uno o más de los elementos actuadores como se describió anteriormente. Un circuito abierto a través de un elemento actuador 4 también se considera que incluye un circuito abierto a través de una vía eléctrica asociada con el elemento actuador, tal como la vía eléctrica 109.

- 50 El circuito de prueba 402 también se puede usar para detectar otras fallas tales como cortocircuitos a través de un elemento actuador.

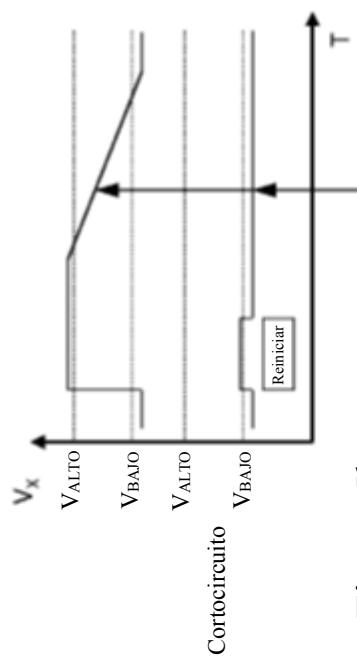

- 55 La Figura 5b ilustra esquemáticamente la detección de un cortocircuito 430 a través del elemento actuador 4b. Los interruptores 106b y 414 están cerrados de manera que el elemento actuador 4b está en comunicación eléctrica con el circuito de prueba 402 a través de una ruta de prueba.

- 60 La fuente de corriente 422 (como se muestra en la Figura 5a) se enciende y cuando hay un cortocircuito 430 a través del elemento actuador, el elemento actuador 4b no se cargará. Sin un cortocircuito a través de él, el elemento actuador 4b se cargará y la descarga posterior del elemento actuador se ingresará desde la ruta de prueba como  $V_x$  a los comparadores, de manera que, en el presente ejemplo,  $V_x \leq V_{BAJO}$  es indicativo de un cortocircuito en el elemento actuador 4b, mientras que  $V_{BAJO} \leq V_x \leq V_{ALTO}$  es indicativo de la ausencia de un cortocircuito.

- 65 Sin embargo, el circuito de prueba 402 no se limita a medir la descarga de un elemento actuador particular para detectar un cortocircuito (o ningún cortocircuito) a través de él, y en ejemplos alternativos se pueden tomar diferentes mediciones para indicar dicho cortocircuito. Como ejemplo ilustrativo, que  $V_x$  no alcance un nivel umbral dentro de un período de tiempo especificado puede ser indicativo de un cortocircuito en el elemento actuador.

- En la presente modalidad, cada elemento actuador 4 también está acoplado a un interruptor de descarga asociado 424 que puede usarse para descargar (por ejemplo, a tierra) su elemento actuador asociado 4 por ejemplo, cuando está cerrado y conectado a tierra.

Un interruptor de descarga 424 puede comprender un transistor y se puede proporcionar dentro de la lógica de interruptor 404 controlada por el controlador 416. Al controlar los interruptores de descarga de manera apropiada, el circuito de prueba 402 también se puede usar para detectar cortocircuitos entre elementos actuadores (por ejemplo, elementos actuadores vecinos) en la serie de elementos actuadores 105 (que también puede incluir cortocircuitos entre las pistas eléctricas 109 de los elementos actuadores).

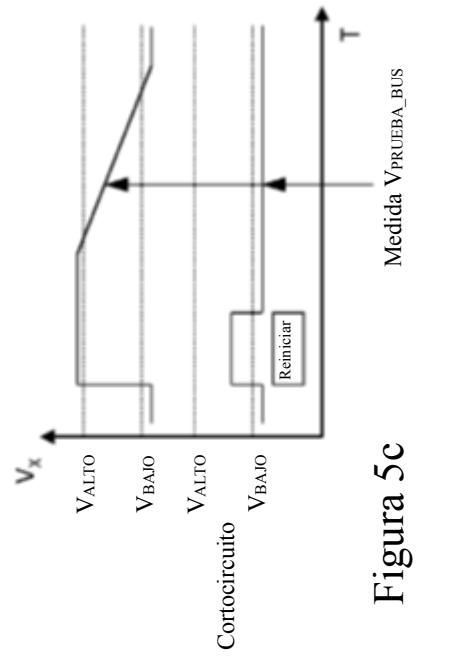

La Figura 5c ilustra esquemáticamente la detección de un cortocircuito entre los elementos actuadores 4b y 4c (representados como el cortocircuito 432), por lo que los interruptores 106b y 414 están cerrados de manera que el elemento actuador 4b está en comunicación eléctrica con el circuito de prueba 402 a través de una ruta de prueba. El interruptor de descarga 424c también está cerrado para proporcionar una ruta para descargar el elemento actuador 4c.

La fuente de corriente 422 (como se muestra en la Figura 5a) se enciende, y cuando hay un cortocircuito 432 presente entre los elementos actuadores adyacentes 4b y 4c, el interruptor de descarga 424c proporcionará una ruta de descarga y el elemento actuador 4b no se cargará. En ausencia de un cortocircuito, el elemento actuador 4b se cargará y la descarga posterior se ingresará desde la ruta de prueba como  $V_X$  a los comparadores, de manera que, para el presente ejemplo,  $V_X \leq V_{BAJO}$  es indicativo de un cortocircuito entre los elementos actuadores 4b y 4c, mientras que  $V_{BAJO} \leq V_X \leq V_{ALTO}$  es indicativo de la ausencia de un cortocircuito. Se debe entender que tal prueba no se limita a elementos actuadores adyacentes, sino que puede incluir la prueba entre cualquier número de elementos actuadores en la serie de elementos actuadores 105.

Sin embargo, el circuito de prueba 402 no se limita a medir la descarga de un elemento actuador en particular para detectar un cortocircuito (o la ausencia de un cortocircuito) entre los elementos actuadores, y en ejemplos alternativos se pueden tomar diferentes medidas para detectar dicho cortocircuito. Por ejemplo, que  $V_X$  no alcance un nivel umbral dentro de un período de tiempo especificado puede ser indicativo de un cortocircuito entre los elementos actuadores.

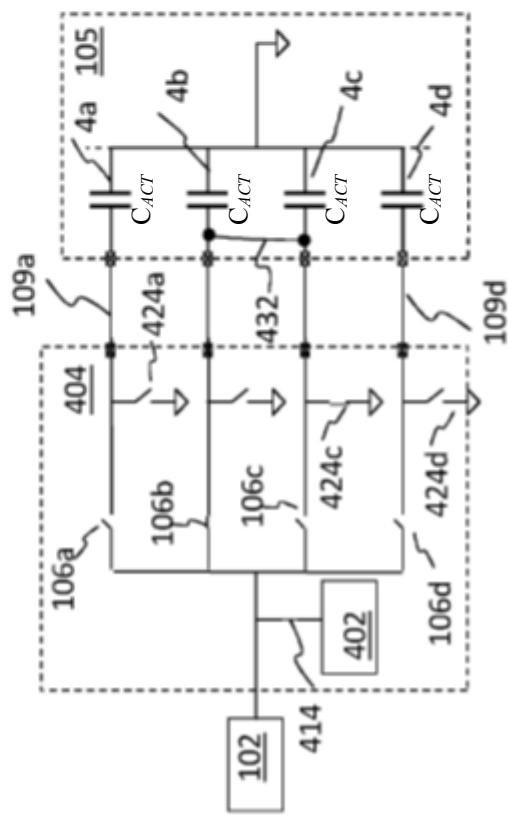

La Figura 6 muestra esquemáticamente un circuito de cabezal de impresión 500 de acuerdo con una modalidad adicional, de manera que el circuito de prueba 502 está incorporado dentro de un circuito de conmutación 504 del circuito de cabezal de impresión 500, y de manera que el circuito de cabezal de impresión 500 también incluye una serie de elementos actuadores 105 como se describió anteriormente.

Como anteriormente, la serie de elementos actuadores 105 comprende una pluralidad de elementos actuadores 4a-4d dispuestos en comunicación eléctrica con un circuito de accionamiento 102 a través de un bus 107, de manera que un interruptor 106 conecta selectivamente un elemento actuador asociado al bus 107.

El circuito de prueba 502 es similar al circuito de prueba descrito en la Figura 5a, de manera que en el presente ejemplo, el circuito de prueba 502 comprende los DAC 518, 519 para generar  $V_{ALTO}$  y  $V_{BAJO}$ ; los comparadores 520, 521; la fuente de corriente 522 para generar la corriente constante  $i_M$ ; el DAC 523 para generar  $V_{Establecido}$ ; y el interruptor de polarización 525.

Por lo tanto, se verá que el circuito de prueba 502 puede usarse para determinar la capacitancia de uno o más de los elementos actuadores 4, detectar un circuito abierto a través de un elemento actuador y/o detectar un circuito cerrado a través/entre los elementos actuadores.

En la presente modalidad, los elementos actuadores 4a-4d están dispuestos en comunicación eléctrica con el circuito de prueba 502 a través de un bus de prueba dedicado 509, de manera que un interruptor de prueba 511 conecta selectivamente un elemento actuador asociado al bus de prueba 509 según se requiera. Los interruptores de prueba 511 pueden adoptar cualquier forma adecuada y pueden comprender, por ejemplo, uno o más transistores. Los interruptores de prueba 511 son controlables por el controlador 516 y/o pueden ser controlados por otros circuitos.

Como se apreciará, el bus de prueba 509 tendrá una capacitancia 513 asociada, que se considerará una capacitancia parásita con el propósito de medir la capacitancia de un elemento actuador y detectar un circuito abierto.

En la presente modalidad, el circuito de prueba 502 incluye un interruptor de descarga 517 en comunicación eléctrica con el bus de prueba 509 para descargar la capacitancia 513 según sea necesario.

La disposición del bus de prueba 509 proporciona un mayor aislamiento eléctrico entre el bus de prueba 509 y el circuito de accionamiento 102, porque cuando el circuito de prueba 502 está realizando una prueba de diagnóstico en un elemento actuador, los interruptores 106 se pueden controlar (por ejemplo, mediante el controlador en el circuito de prueba, un controlador en el circuito de accionamiento u otro circuito de control adecuado) para asegurar que el circuito de accionamiento 102 esté eléctricamente aislado del circuito de prueba 502.

Además, como se describió anteriormente, puede ser ventajoso minimizar la resistencia ON de los interruptores 106. Sin embargo, minimizar la resistencia ON de un interruptor aumenta la capacitancia parásita del mismo.

Como los interruptores de prueba 511 se usan para conectar los elementos actuadores 4 al bus de prueba 509 y se controlan para que estén abiertos mientras el circuito de accionamiento 102 activa los elementos actuadores 4, los interruptores de prueba 511 no tienen sustancialmente ningún impacto en la forma de onda de accionamiento. Por lo tanto, la resistencia ON de los interruptores de prueba 511 puede ser mayor en comparación con los interruptores 106, y la capacitancia parásita de los interruptores de prueba 511 puede reducirse en comparación con los interruptores 106.

Por lo tanto, la capacitancia parásita de una ruta de prueba a través del bus de prueba 509 puede reducirse en comparación con la capacitancia parásita de una ruta de prueba a través del bus 107 descrita en la Figura 5a. Como resultado, la sensibilidad de las pruebas de diagnóstico y, en particular, la precisión en la determinación de  $C_{ACT}$  para un elemento actuador particular, puede mejorarse para una ruta de prueba a través de un bus de prueba dedicado 509.

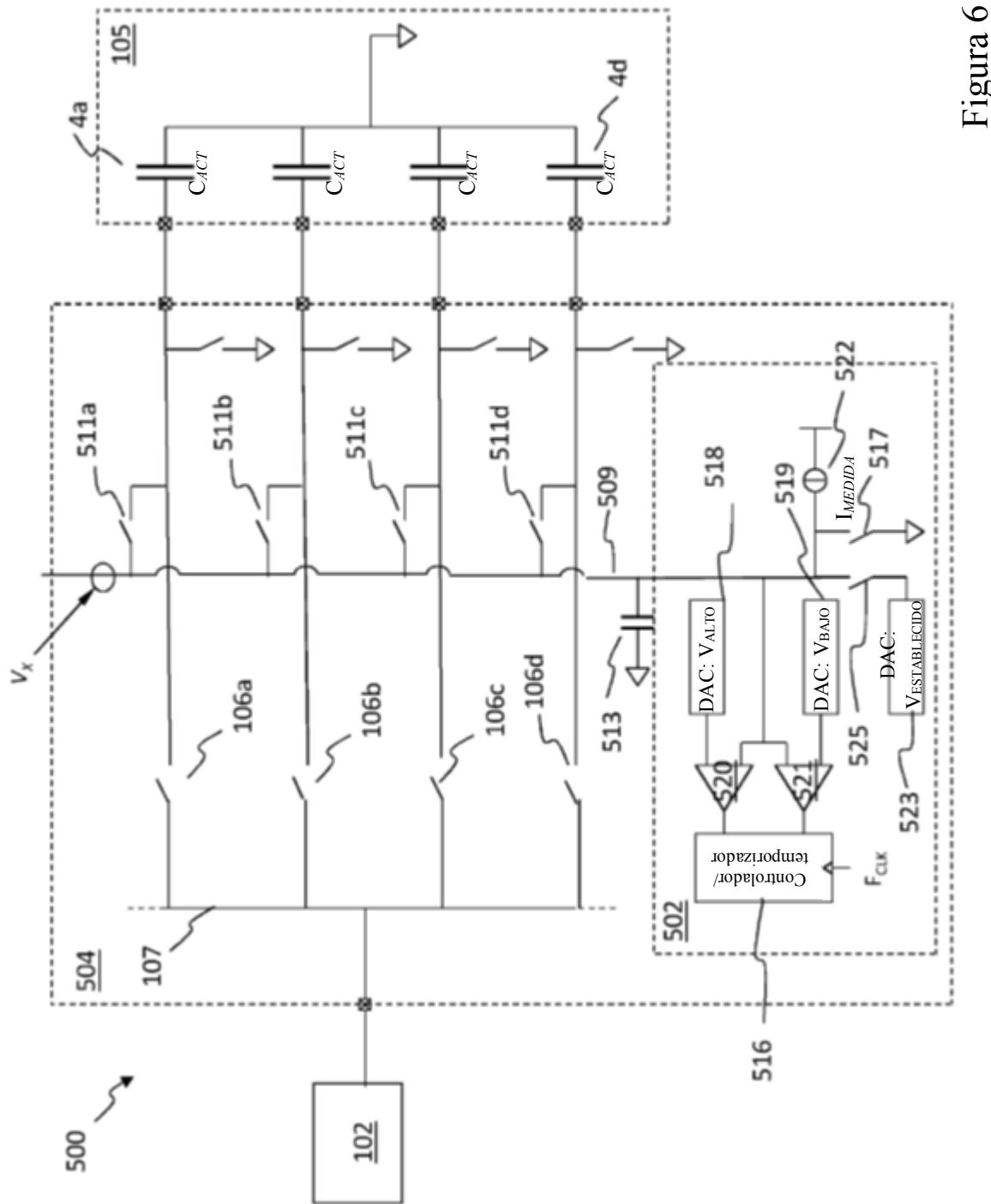

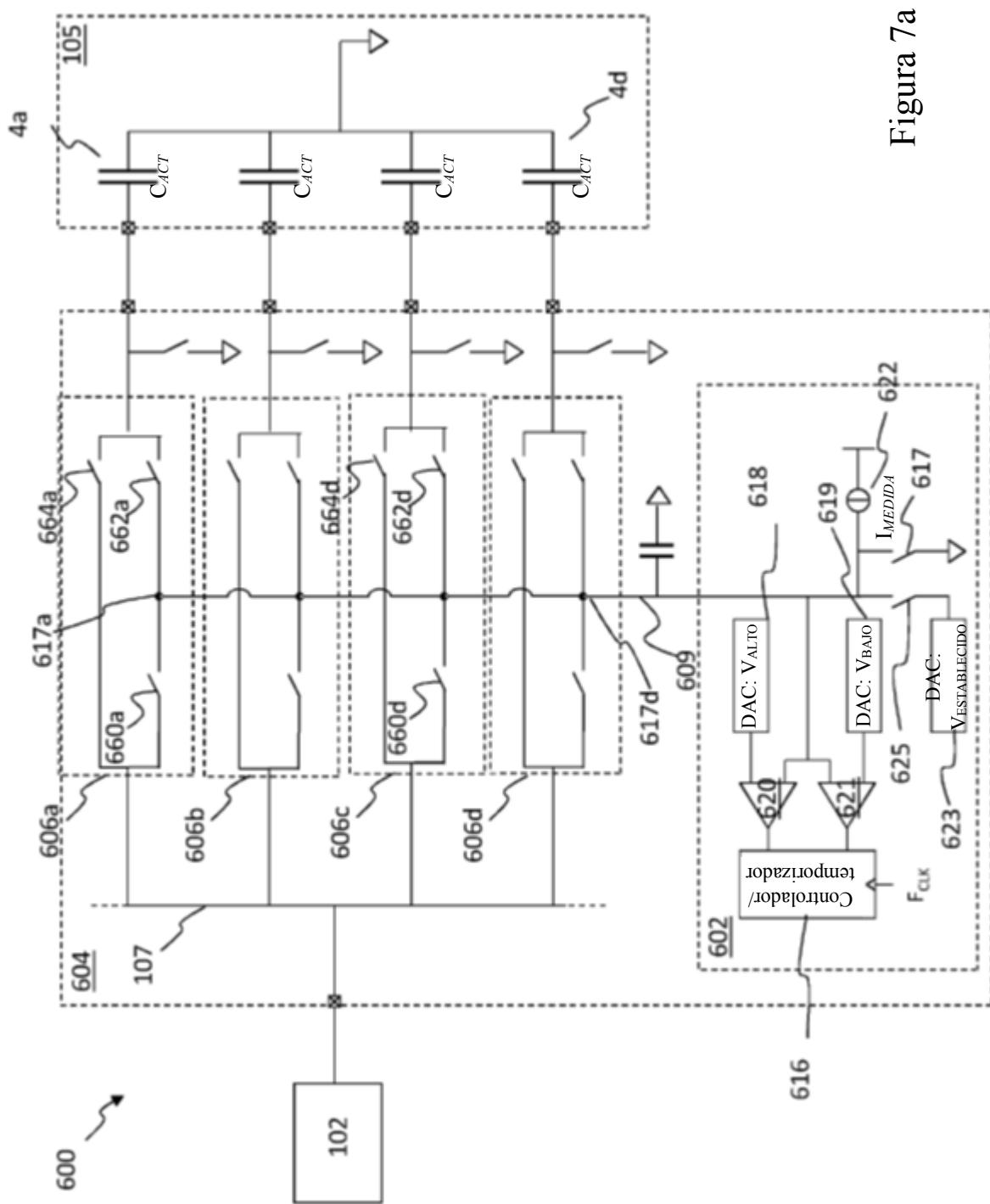

La Figura 7a muestra esquemáticamente un circuito de cabezal de impresión 600 de acuerdo con una modalidad adicional, de manera que el circuito 602 de prueba está incorporado dentro de un circuito de conmutación 604 del circuito de cabezal de impresión 600, de manera que el circuito de cabezal de impresión 600 también incluye la serie de elementos actuadores 105 como se describió anteriormente.

La Figura 7b muestra esquemáticamente un ejemplo de una forma de onda de accionamiento común 650 y una forma de onda recortada 652 obtenida mediante el uso del interruptor 606.

El circuito de prueba 602 es similar al circuito de prueba descrito en la Figura 6, de manera que en el presente ejemplo, el circuito de prueba 602 comprende los DAC 618, 619 para generar  $V_{ALTO}$  y  $V_{BAJO}$ ; los comparadores 620, 621; la fuente de corriente 622 para generar la corriente constante  $i_M$ ; el DAC 623 para generar  $V_{Establecido}$ ; y el interruptor de polarización 625.

Por lo tanto, se verá que el circuito de prueba 602 puede usarse para determinar la capacitancia de uno o más de los elementos actuadores 4, detectar un circuito abierto a través de un elemento actuador y/o detectar un circuito cerrado a través/entre los elementos actuadores.

En algunas modalidades, puede ser necesario modificar o 'recortar' la forma de la forma de onda de accionamiento para, por ejemplo, ajustar la velocidad de la gota y/o el volumen de la gota.

Para lograr tal recorte, el circuito de accionamiento 102 puede modificar una forma de onda de accionamiento común aplicada a todos los elementos actuadores. Sin embargo, algunas aplicaciones requieren que la forma de onda de la unidad se modifique en base a cada elemento del actuador.

En el ejemplo de la Figura 7a, los elementos de conmutación 660 y 662 están dispuestos en paralelo con el elemento de conmutación 664 en una configuración de compuerta, de manera que los elementos de conmutación 660 y 662 tienen una mayor resistencia ON en comparación con el elemento de conmutación 664.

Los elementos de conmutación 660, 662 y 664 pueden ser controlados por el controlador 616 en el circuito de prueba 602, un controlador en el circuito de accionamiento (no mostrado) u otro circuito de control adecuado.

Los elementos de conmutación 660, 662 & 664 están configurados para pasar selectivamente una forma de onda de accionamiento común 650 desde el circuito de accionamiento 102 a un elemento actuador 4 correspondiente. La resistencia ON del elemento de conmutación 664 puede minimizarse para obtener una forma de onda deseada (por ejemplo, teniendo bordes anteriores/posteriores y velocidades de respuesta definidos).

Durante el funcionamiento del cabezal de impresión, el elemento conmutador de baja resistencia ON 664 se cierra y los elementos de interruptor de alta resistencia ON 660, 662 están abiertos de manera que una forma de onda de accionamiento común pasa a través del elemento de conmutación 664 y se aplica a un elemento actuador asociado 4.

Para recortar la forma de onda de accionamiento común, se abre el elemento conmutador de baja resistencia ON 664 y los elementos de interruptor de alta resistencia ON 660, 662 se cierran mientras la forma de onda de accionamiento común pasa a través del elemento de conmutación.

Los elementos 660, 662 del interruptor de alta resistencia a la conexión modifican la forma de onda de accionamiento común 650 a medida que pasa a través de ellos (representada como la creación de un paso 654 en la Figura 7b). Cuando se completa el recorte deseado, el elemento conmutador 664 se cierra y los elementos de interruptor 660, 662 se abren, de manera que el resto de la forma de onda de accionamiento común 650 pasará a través del elemento de conmutación de baja resistencia ON 664 para aplicarse al elemento actuador a través del elemento interruptor 664.

En el presente ejemplo ilustrativo, el bus de prueba dedicado 609 está conectado a la conexión común 617 entre los elementos 660 y 662 del interruptor de alta resistencia en ON de cada interruptor 606.

Para conectar un elemento actuador 4 particular a la ruta de prueba, el elemento de conmutación 662 de alta resistencia ON de un interruptor 606 correspondiente se controla para que se cierre, mientras que los otros elementos de conmutación 660 y 664 del interruptor correspondiente se controlan para que estén abiertos.

- 5 Por lo tanto, se verá que el elemento de conmutación 662 de alta resistencia ON no es un elemento de conmutación de prueba dedicado o un elemento de conmutación de accionamiento dedicado sino que se usa para conectar el elemento actuador tanto a una ruta de accionamiento como a una ruta de prueba.

- 10 Como el circuito de prueba 602 está aislado eléctricamente del circuito de accionamiento 102, no será dañado por la tensión/corrientes de accionamiento mientras la forma de onda de accionamiento pasa por el elemento de conmutación 664 de baja resistencia ON.

- 15 En el presente ejemplo ilustrativo, ambos elementos de conmutación de alta resistencia ON 660 y 662 están cerrados cuando se recorta la forma de onda de accionamiento para un elemento actuador 4 asociado, de manera que la resistencia entre el circuito de accionamiento 102 y el elemento actuador 4 asociado es independiente del número de los elementos actuadores se recortan al mismo tiempo.

- 20 Si bien uno o más de los elementos de conmutación de alta resistencia ON 660a-660d pueden fusionarse para proporcionar un solo elemento de conmutación, se apreciará que en tal disposición la resistencia efectiva de dicho elemento de conmutación único será una función del número de los elementos de conmutación combinados 660 además del número de elementos de conmutación 662 de alta resistencia ON que están cerrados en cualquier momento (es decir, cuando se recortan las formas de onda de accionamiento de uno o más elementos actuadores).

- 25 La Figura 7c muestra esquemáticamente un circuito de cabezal de impresión 600 de acuerdo con una modalidad adicional, de manera que el circuito de prueba 602 está incorporado dentro de un circuito de conmutación 604 del circuito de cabezal de impresión 600, por lo que el circuito de cabezal de impresión 600 también incluye la serie de elementos actuadores 105 como se describió anteriormente.

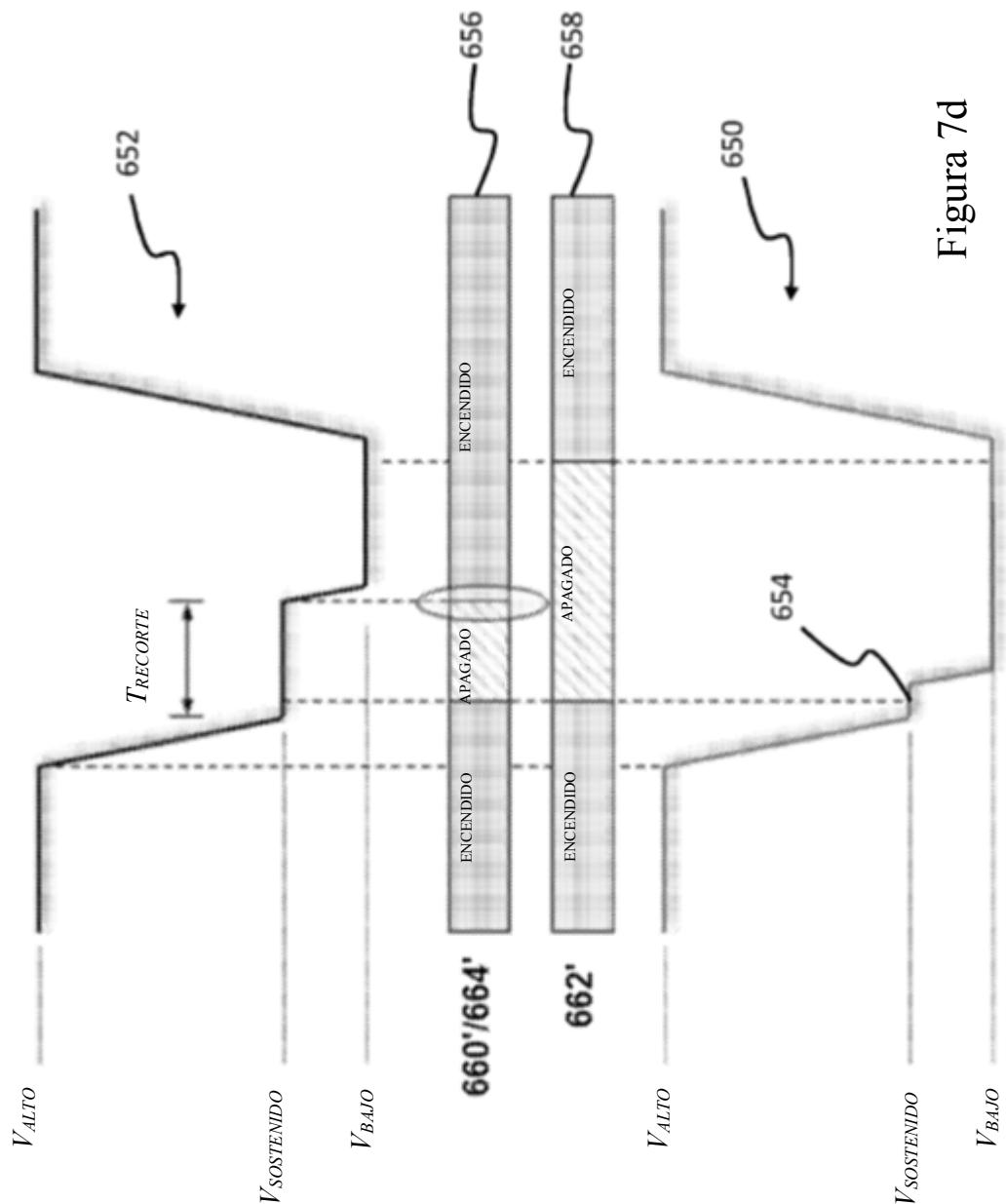

- 30 La Figura 7d muestra esquemáticamente un ejemplo de una forma de onda de accionamiento común 650 y una forma de onda recortada 652 obtenida mediante el uso del interruptor 606.

- 35 En el ejemplo ilustrativo de la Figura 7c, cada interruptor 606 comprende el elemento de conmutación 660', el elemento de conmutación 662' y el elemento de conmutación 664' dispuestos en una configuración de puerta de paso compuesta, de manera que el elemento de conmutación 662' está dispuesto en paralelo con el elemento de conmutación 664'.

- 40 En el presente ejemplo ilustrativo, los elementos de conmutación 660' y 662' tienen una resistencia ON más baja en comparación con el elemento de conmutación 664'. Como anteriormente, los elementos de conmutación 660', 662' y 664' pueden ser controlados por el controlador 616 en el circuito de prueba 602, un controlador en el circuito de accionamiento (no mostrado) u otro circuito de control adecuado.

- 45 El funcionamiento del interruptor 606 para activar un elemento actuador con la forma de onda de accionamiento 652 se describe en relación con la Figura 7d, que muestra un diagrama de tiempos para una implementación básica de un esquema de recorte basado en pasos controlado por desplazamiento de un CDW 650.

- 50 El CDW 650 comprende un pulso que puede tener cualquier forma. La forma de onda de accionamiento resultante 652 también tiene un pulso.

- 55 La temporización de los elementos de conmutación 660', 662', 664' para obtener la forma de onda de accionamiento 652 se indica en las dos barras horizontales 656, 658, mostrando la barra superior 656 el estado de los elementos de conmutación 660' y 664', y la barra inferior 658 que muestra el estado del elemento interruptor 662'.

- 60 Ambas barras horizontales 656 y 658 muestran que los elementos de conmutación 660', 662', 664' están cerrados para el borde delantero del pulso en el CDW 650. Esto significa que la resistencia ON de la puerta de paso está determinada por el elemento de conmutación 660' y el elemento interruptor 662'.

- 65 Los elementos de conmutación se abren después del inicio de la porción plana del paso 654 (mostrado en hash), durante el cual el elemento actuador 4 se desacopla de la ruta de accionamiento y, por lo tanto, el paso en el pulso de la forma de onda de accionamiento 652 se prolonga durante un tiempo duración controlada  $T_{RECORTE}$  y no sigue el final del paso 654 en el CDW 650.

El final del paso 650 en la forma de onda de accionamiento 652 se produce al volver a acoplar el elemento actuador 4 a la ruta de accionamiento después de una duración controlada  $T_{RECORTE}$ , y la tensión de la forma de onda de accionamiento 652 cae de  $V_{SOSTENIDO}$  hacia abajo para seguir la tensión  $V_{BAJO}$  de la parte inferior del pulso en el CDW 650. La transición  $V_{SOSTENIDO}$  a  $V_{BAJO}$  se habilita encendiendo sólo la mitad de la puerta de paso, específicamente, el elemento commutador 660' y el elemento commutador 664'.

Dado que el elemento interruptor 664' tiene una resistencia ON más alta en comparación con el elemento interruptor 660', la resistencia ON de la puerta de paso para esta transición aumentará. Esto permite ralentizar la transición  $V_{SOSTENIDO}$  a  $V_{BAJO}$  sin comprometer la transición  $V_{ALTO}$  a  $V_{SOSTENIDO}$ . El momento de la duración del paso  $T_{RECORTE}$ , y por lo tanto la cantidad de recorte, está determinada por el momento en que los elementos interruptores 660' y 664' se encienden (la transición resaltada por el círculo en la Figura 7d).

El bus de prueba dedicado 609 está acoplado a los elementos interruptores 662' y 664' de cada interruptor 606.

Para acoplar un elemento actuador 4 particular a una ruta de prueba, se controla que el elemento interruptor 660' del interruptor 606 correspondiente esté abierto, mientras que los elementos interruptores 662' y 664' se controlan para acoplar el elemento actuador 4 a la ruta de prueba dependiendo en un tiempo de subida/medición requerido. Además, en el presente ejemplo ilustrativo se dispone un interruptor de prueba 610 para conectar selectivamente el circuito de prueba 602 al bus de prueba 609. El interruptor de prueba 610 puede adoptar cualquier forma adecuada y, por ejemplo, puede comprender uno o más transistores.

Por ejemplo, debido a la respectiva  $R_{ON}$  resistencias del elemento de conmutación 662' y 664', abrir el elemento de conmutación 662' y cerrar el elemento de conmutación 664' proporcionará el mayor tiempo de subida/medición; cerrar el elemento de conmutación 662' y abrir el elemento de conmutación 664' proporcionará un tiempo de subida/medición más corto; mientras que cerrar ambos elementos de conmutación 662' y 664' proporciona el tiempo de subida/medición más corto.

Por tanto, se verá que los elementos de conmutación 662' y 664' no son elementos de conmutación de prueba dedicados ni elementos de conmutación de accionamiento dedicados, sino que se usan para conectar el elemento actuador 4 tanto a una ruta de accionamiento como a una ruta de prueba, mientras que controlar los elementos de conmutación 662' y 664' proporciona variaciones en el tiempo de subida/medición.

Se debe notar que para los ejemplos esquemáticos de las Figuras 7a y 7c, los elementos de conmutación 660', 662' y 664' se muestran como lógica de conmutación simple con fines ilustrativos únicamente y, en la práctica, estos pueden implementarse como dispositivos MOS o cualquier dispositivo adecuado.

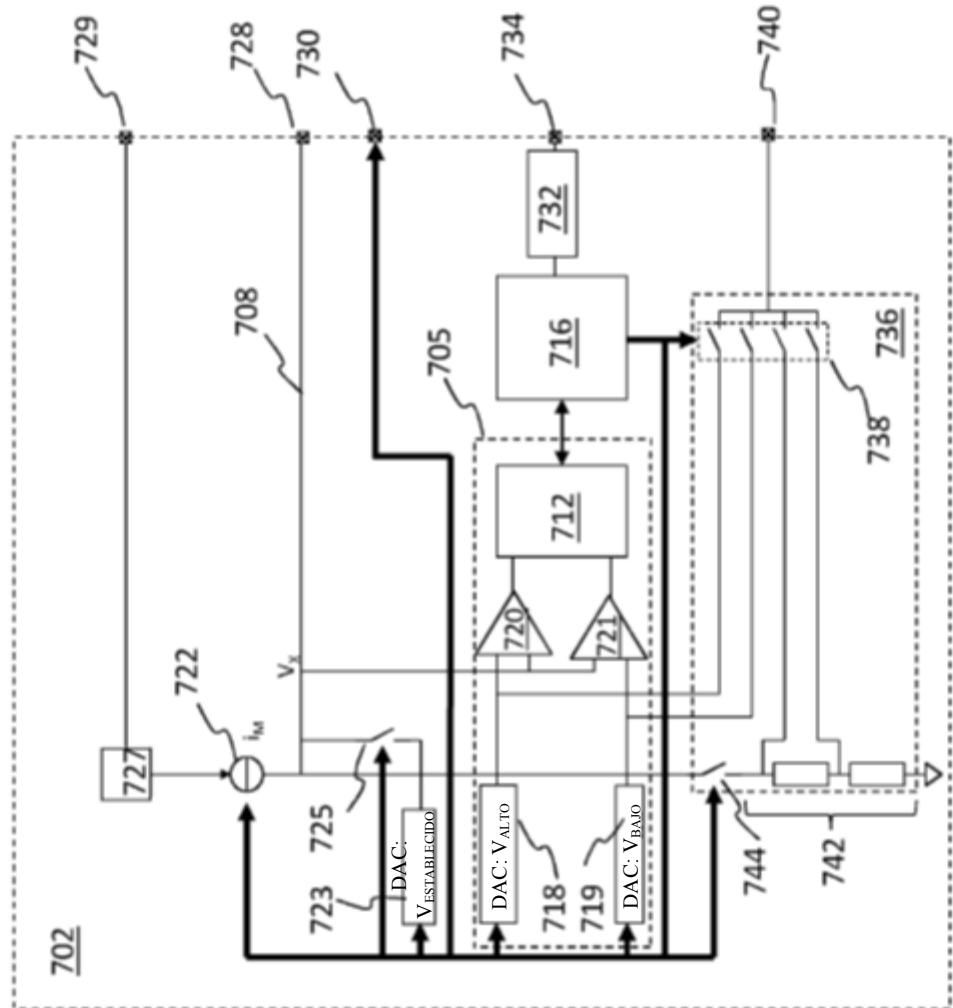

La Figura 8 muestra esquemáticamente un circuito de prueba 702 implementado como un circuito dedicado tal como en una placa de circuito impreso (PCB). La PCB puede insertarse en una impresora, cabezal de impresión o, por ejemplo, se puede usar como parte de un módulo de prueba discreto que se conecta a la impresora/cabezal de impresión.

El circuito de prueba 702 es similar en configuración y funcionalidad al circuito de prueba descrito en la Figura 7a, de manera que en el presente ejemplo ilustrativo, el circuito de prueba 702 comprende una pista eléctrica 708 que se puede proporcionar en comunicación eléctrica con elementos actuadores en un circuito de cabezal de impresión (no mostrado) a través del terminal 728.

El circuito de prueba 702 comprende un controlador 716 que, como anteriormente, controla los circuitos del circuito de prueba 702. El controlador 702 también genera señales que se usan para controlar uno o más circuitos externos o componentes de los mismos, como para controlar interruptores individuales en circuitos interruptores en un circuito de cabezal de impresión a través del terminal 730.

El circuito de prueba 702 comprende el circuito de medición 705 que incluye los DAC 718, 719 para generar  $V_{ALTO}$  y  $V_{BAJO}$  (según lo determinado por el controlador 716); los comparadores 720, 721 que comparan un valor medido  $V_x$  a las respectivas salidas DAC; y el temporizador 712 que mide la transición de  $V_x$  de  $V_{BAJO}$  a  $V_{ALTO}$  y proporciona el resultado al controlador 716. Como anteriormente, el temporizador 712 puede implementarse en un FPGA o puede ser un IC dedicado.

El circuito de prueba 702 comprende además una fuente de corriente programable 722 para generar la corriente constante  $i_M$  determinada, por ejemplo, por el controlador 716. Como anteriormente, en las modalidades, la fuente de corriente 722 tiene una alta impedancia de salida para la carga lineal de los elementos actuadores para mejorar la precisión de la medición de capacitancia.

El circuito de prueba 702 comprende además el DAC 723 para generar  $V_{Establecido}$  y el interruptor de polarización 725 como se describió anteriormente.

Una fuente de alimentación 727 suministra una tensión adecuada para la fuente de corriente 722. La fuente de alimentación 727 también puede suministrar tensiones a un circuito externo, tal como un circuito de cabezal de impresión, a través del terminal 729. Tales tensiones suministradas por la fuente de alimentación 727 pueden depender de una aplicación dada y pueden variar, por ejemplo, entre 1,8 V y 40 V.

- 5 El controlador 716 puede comunicarse con otros circuitos externos (por ejemplo, un terminal de ordenador) a través del circuito de comunicaciones 732 y el terminal 734. El circuito puede comprender una interfaz de comunicaciones que comprende un enlace en serie (por ejemplo, un bus serie universal (USB) a un enlace en serie). Como se apreciará, se pueden requerir circuitos/terminales adicionales no descritos en la presente descripción para enviar/recibir/generar señales según se requiera, por ejemplo, según pueda ser requerido por un protocolo de comunicaciones particular. Como ejemplo ilustrativo, un protocolo I<sup>2</sup>C puede requerir que el circuito de prueba 702 genere señales de reloj.

- 10 Se apreciará que el circuito de prueba 702 puede usarse para realizar pruebas de diagnóstico para determinar la capacitancia  $C_{ACT}$  de un elemento actuador y/o detectar una falla tal como un circuito abierto a través del elemento actuador o un circuito cerrado a través/entre elementos actuadores. El número de elementos actuadores en los ejemplos adjuntos no se limita a cuatro, pero puede aplicarse igualmente a cualquier número de elementos actuadores.

- 15 Se puede proporcionar un circuito de precisión 736 dentro del circuito de prueba 702, de manera que el circuito de precisión puede disponerse en comunicación eléctrica con un circuito o dispositivo de medición externo que podría medir las corrientes y tensiones generados dentro del circuito de prueba 702 con mayor precisión de lo que se lograría de cualquier otra manera, con la precisión intrínseca del circuito de prueba en sí.

- 20 Se apreciará que el circuito de precisión 736 comprende una serie de interruptores de precisión 738 que se usa para conectar selectivamente la fuente de corriente 722 y la salida de cada DAC 718, 719 al terminal 740, de manera que un circuito/dispositivo de medición externo, tal como un voltímetro digital (DVM) (por ejemplo, dentro del circuito del cabezal de impresión o alejado de la impresora), se puede conectar al terminal 740 para medir  $i_M$ ,  $V_{ALTO}$  y  $V_{BAJO}$  con mayor precisión de lo que se lograría de otro modo con la precisión intrínseca de la fuente de corriente 722 y los DAC 720, 721. El DVM puede entonces comunicarse con el controlador 716 para ajustar las salidas de la fuente de corriente 722, DAC 720 y/o DAC 721 en respuesta a los valores medidos.