(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2013-0128383

(43) 공개일자 2013년11월26일

- (51) 국제특허분류(Int. Cl.)

**G01K 7/22** (2006.01) **H01C 7/04** (2006.01)

**H05K 3/12** (2006.01) **H01C 7/02** (2006.01)

**H05K 1/16** (2006.01)

- (21) 출원번호 10-2013-7009246

- (22) 출원일자(국제) 2011년09월13일

심사청구일자 없음

- (85) 번역문제출일자 2013년04월11일

- (86) 국제출원번호 PCT/IB2011/054001

- (87) 국제공개번호 WO 2012/035494

국제공개일자 2012년03월22일

- (30) 우선권주장

2010/06532 2010년09월13일 남아프리카(ZA)

- (71) 출원인

피에스티 센서스 (피티와이) 리미티드

남아프리카 케이프타운 유니버시티 오브 케이프타운 어퍼 캠퍼스 룸 513 알더블유 제임스 빌딩 (우: 1100)

- (72) 발명자

브리튼, 테이비드, 토마스

남아프리카 8001 케이프 타운 브리 스트리트 120

데 우드 슈어 704

하팅, 마르깃

남아프리카 8001 케이프 타운 모우브레이 트워커

넘 로드 8

- (74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 27 항

(54) 발명의 명칭 **프린팅된 온도 센서**

### (57) 요 약

온도 감지 디바이스를 제작하는 방법이 제공된다. 방법은, 서미스터 구조물을 정의하는 적어도 하나의 실리콘 층 및 적어도 하나의 전극 또는 콘택을 형성하는 단계를 포함한다. 적어도 실리콘 층은 프린팅에 의하여 형성되고, 실리콘 층 및 전극들 또는 콘택들 중 적어도 하나는 그것의 프린팅 동안 기판에 의하여 지지된다. 바람직하게, 전극들 또는 콘택들은, 10 나노미터 내지 100 마이크로미터 범위의 사이즈를 갖는 실리콘 입자들을 포함하는 잉크와, 결합제 및 적절한 용매로 구성되는 액체 전색제를 사용하여, 프린팅에 의해 형성된다. 몇몇 실시예들에서, 기판은 온도가 측정될 대상물이다. 대신에, 기판은 템플레이트(template)일 수 있거나, 희생적일 수 있거나, 또는 플렉서블 또는 강성 물질일 수 있다. 다양한 디바이스 기하학적 구조들이 개시된다.

**대 표 도** - 도3

## 특허청구의 범위

### 청구항 1

온도 감지 디바이스를 제작하는 방법으로서,

서미스터(thermistor) 구조물을 정의하기 위하여 적어도 하나의 실리콘 층 및 적어도 하나의 전극 또는 콘택을 형성하는 단계를 포함하며,

적어도 상기 실리콘 층은 프린팅에 의하여 형성되고, 상기 실리콘 층 및 상기 적어도 하나의 전극 또는 콘택 중 적어도 하나는 그것의 프린팅 동안 기판에 의하여 지지되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 2

제1항에 있어서,

상기 적어도 하나의 전극 또는 콘택은 프린팅에 의하여 형성되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 3

제1항 또는 제2항에 있어서,

상기 적어도 하나의 실리콘 층 및 적어도 2개의 도전성 전극들 또는 콘택들은 온도가 측정될 대상물에 직접 적용되어, 상기 대상물 자체가 상기 서미스터 구조물에 대한 기판을 형성하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 4

제1항 또는 제2항에 있어서,

상기 기판이 전기 도전성 바디를 구성(comprise)하여, 상기 기판은 상기 서미스터 구조물의 전극 또는 콘택을 형성하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 5

제1항 내지 제4항 중 어느 한 항에 있어서,

상기 기판은 플렉서블 시트(flexible sheet)로 구성되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 6

제5항에 있어서,

상기 플렉서블 시트는 고체 필름, 섬유(fibrous) 물질 또는 직물(woven fabric)로 구성되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 7

제1항 내지 제4항 중 어느 한 항에 있어서,

상기 기판은 강성 시트(rigid sheet)로 구성되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 8

제7항에 있어서,

상기 강성 시트는, 고체 물질, 섬유 또는 미립자(particulate) 물질을 포함하는 복합물, 또는 직물을 포함하는 복합물로 구성되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 9

제1항 또는 제2항에 있어서,

상기 기판은 그것의 제작 동안에 상기 서미스터 구조물에 대한 일시적 지지물 또는 템플레이트(template)를 형성하는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 10

제9항에 있어서,

상기 기판은 희생적(sacrificial)이며, 상기 서미스터 구조물의 프린팅 이후에 화학적, 열적 또는 기계적 수단에 의하여 제거되는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 11

제9항에 있어서,

상기 기판은 재사용가능 템플레이트를 형성하는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 12

제1항 내지 제11항 중 어느 한 항에 있어서,

상기 실리콘 층은, 실리콘 입자들을 포함하는 잉크, 및 결합제(binder)와 적절한 용매로 구성된 액체 전색제(liquid vehicle)로부터 형성되며, 상기 실리콘 입자들은, 10 나노미터 내지 100 마이크로미터 범위의 사이즈, 및 입자들 사이의 전기 전하(electrical charge)의 전달을 허용하는 표면을 갖는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 13

제13항에 있어서,

효과적으로 상기 서미스터 구조물의 온도 의존적 저항과 병렬로 상대적으로 온도 독립적 내부 저항을 부가하기 위해, 실리콘 대 결합제 비율을 변경하는 것에 의한 잉크 조성의 변형에 의해, 또는 상기 잉크에 실리카 또는 다른 세라믹 나노입자들과 같은 절연 페이즈(phase) 또는 도전성 또는 반도전성(semiconducting) 페이즈 중 어느 하나의 부가에 의해, 상기 실리콘 입자 층으로의 적어도 하나의 부가적인 도전성 경로의 부가를 포함하는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 14

제13항에 있어서,

프린팅된 온도 센서의 공칭 저항을 감소시키기 위하여, 도전성 잉크를 사용하여 상기 서미스터 구조물의 상기 온도 의존적 저항과 병렬로 내부의 실질적인 온도 독립적 저항기를 프린팅하는 단계를 포함하는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 15

제13항에 있어서,

프린팅된 온도 센서의 공칭 저항을 증가시키기 위하여, 도전성 잉크를 사용하여 상기 서미스터 구조물의 상기 온도 의존적 저항과 직렬로 내부의 실질적인 온도 독립적 저항기를 프린팅하는 단계를 포함하는, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 16

제12항 내지 제15항 중 어느 한 항에 있어서,

상기 잉크의 실리콘 입자 프랙션(particle fraction)은 5% 내지 95% 범위인, 온도 감지 디바이스를 제작하는 방법.

#### 청구항 17

제16항에 있어서,

실리콘 입자들의 25 내지 60 부피 퍼센트 범위 내에서 상기 잉크의 실리콘 입자들의 프랙션을 변화시킴으로써, 프린팅된 온도 센서의 저항을 조정하는 단계를 포함하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 18

제16항에 있어서,

상기 잉크는 60% 초과의 그리고 바람직하게는 80% 초과의 실리콘 입자 프랙션을 갖는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 19

제1항 내지 제18항 중 어느 한 항에 있어서,

도전성 잉크를 사용하여, 프린팅에 의하여, 박막 증착 프로세스에 의하여, 또는 전기 도금 또는 무전해 도금에 의하여, 도전성 전극들 또는 콘택들 중 적어도 하나를 형성하는 단계를 포함하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 20

제19항에 있어서,

화학적 또는 전기화학적 에칭, 레이저 스크라이빙, 또는 원하는 형상을 형성하기 위한 다른 방식의 물질 제거에 의하여, 상기 적어도 하나의 콘택을 정확한 형태로 패터닝하는 단계를 포함하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 21

제1항 내지 제20항 중 어느 한 항에 있어서,

상기 콘택들이 원형 기하학적 구조를 가져, 상기 서미스터 구조물의 방사상 전기적 경로가, 측정된 저항이 프린팅 방향에 관한 모든 방향에 걸쳐 평균화되는 것을 보장하여, 프린팅 프로세스에서 임의의 측방(lateral) 이방성(anisotropy)의 효과가 제거되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 22

제1항 내지 제21항 중 어느 한 항에 있어서,

상기 서미스터 디바이스에 전류를 공급하는데 사용되는 임의의 2개의 콘택들 사이의 거리가 상기 콘택들 사이의 반도전성 경로의 폭에 비해 작도록, 상기 서미스터 디바이스의 종횡비는 낮고, 바람직하게는 1/30 미만, 그리고 더욱 바람직하게는 1/1000 미만인, 온도 감지 디바이스를 제작하는 방법.

### 청구항 23

제1항 내지 제20항 또는 제22항 중 어느 한 항에 있어서,

나란히 연장되는 2개의 신장된(elongated) 병렬 콘택들이 비교적 큰 영역을 커버하도록 나선형의(spiral) 또는 구불구불한(meandering) 경로를 정의하는 패턴으로 증착되고, 그에 의해 이와 대응하게 형상화된 기판 영역의 평균 온도가 모니터링되도록 허용되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 24

제1항 내지 제20항 또는 제22항 중 어느 한 항에 있어서,

2개의 서로 맞물린(interdigitated) 전기적 콘택들은 프린팅된 미립자 실리콘의 층에 의해 연결되거나 브릿징되며, 2개의 서로 맞물린 전기적 콘택들 각각은 병렬로 그리고 서로의 근처에서 연장되어 서펜타인(serpentine) 캡을 정의하는 다수의 신장 스트립(elongate strip)들 또는 팅거(finger)를 갖는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 25

제24항에 있어서,

상기 프린팅된 미립자 실리콘의 층은 상기 전극들 사이의 서펜타인(serpentine) 캡을 따라 구조화되는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 26

제24항에 있어서,

상기 프린팅된 미립자 실리콘의 층은 상기 전극들 사이의 서펜타인 캡 위에 연속층을 형성하는, 온도 감지 디바이스를 제작하는 방법.

### 청구항 27

제1항 내지 제22항 중 어느 한 항에 있어서,

더 높은 정확도를 달성하기 위하여 4개의 전기적 콘택들이 통상의 선형적 4-포인트 기하학적 구조 또는 흔히 사용되는 반 데어 파우브(van der Pauw) 기하학적 구조들 중 임의의 기하학적 구조 중 어느 하나로 증착되며, 상기 4개의 전기적 콘택들 중 2개의 전기적 콘택들은 상기 온도 감지 디바이스에 전류를 공급하는데 사용되고, 상기 4개의 전기적 콘택들 중 2개의 전기적 콘택들은 사용 중인 전압을 모니터링하는데 사용되는, 온도 감지 디바이스를 제작하는 방법.

## 명세서

### 기술 분야

[0001]

이 발명은 온도 감지 디바이스 및 그러한 디바이스들의 제작 방법에 관련된다. 특히, 발명은 부 온도 계수 서미스터(negative temperature coefficient thermistor)에 관련된다.

### 배경 기술

[0002]

기능성 잉크들의 프린팅은 전자 분야에서 오랜 전통을 갖는다. 예를 들어, 안료계 잉크들은 인쇄 회로 보드들 상에 상호접속부들 및 저항기들을 스크린-프린팅하는데 사용된다. 이들 애플리케이션들에서, 사용되는 후막 잉크들은 각각 은 및 탄소의 안료들 및 전색제(vehicle)로 구성되며, 여기서 안료 입자들은 나노미터 범위의 치수를 가질 수 있다.

[0003]

전통적으로 대부분의 기능성 물질들은 스크린 프린팅과 같은 종래의 프린팅 기법들에 의해 프린팅되었다. 더욱 최신의 개발들은 회로의 패시브(passive) 컴포넌트들 뿐 아니라 액티브 컴포넌트들 또한 프린팅하는 것을 목표로 한다. 예를 들어, 프린팅된 나노미립자(nanoparticulate) 실리콘 컴포넌트들은 국제 특허 출원 WO 2004/068536에 개시되며, 상기 국제 특허 출원은 태양 전지들 및 트랜지스터들 같은 액티브 디바이스들에서의 반도전(semiconducting) 층들의 프린팅을 개시한다. 그러나 반도전성 후막 페이스트들의 적용을 위해 흔히 알려진 예는, 서미스터로서 알려진 온도 의존적 저항기의 제조이다. 그러한 디바이스들은 일반적으로 패시브 전자 컴포넌트들인 것으로 간주된다. 본원과 특히 관련성이 있는 것은, 흔히 NTC 서미스터들로서 알려진, 저항부 온도 계수(negative temperature coefficient of resistance)(이는 전기 저항이 증가하는 온도에 따라 대략 지수적으로 감소하는 것을 의미함)를 갖는 서미스터들이다.

[0004]

이 일반적 타입의 현존하는 서미스터들은 글래스 프릿(glass frit)과 같은 결합제(binder) 물질 및 화합물 반도체 물질의 파우더로 이루어지는 페이스트들로 구성된다. 이 페이스트는 그린 바디(green body)를 형성하기 위하여 세라믹 기판 위에 스크린 프린팅되거나 또는 주조되고(cast), 이후 이것은 반도체 물질의 바디 또는 거대(massive) 층을 형성하도록 고온에서 소결된다. 언제나, 열적 처리 동안의 왜곡으로 인하여, 후막 서미스터들의 경우에, 정확한 저항을 획득하기 위한 물질의 추가적 트리밍(trimming)이 금속화 이전에 요구된다.

[0005]

사용되는 제조 프로세스들은, 페이퍼 및 중합체 막과 같은 다수의 경량의 플렉서블한 물질들의 사용을 배제하고, 사용될 수 있는 기판 물질들에 제한들을 둔다. 전통적으로, 서미스터들의 제조를 위해 사용되는 후막 잉크들은 황화납과 같은 중금속 황화물(heavy metal sulphide)들 및/또는 텔루르화물(telluride)들로 구성되고, ROHS(European Restriction on Hazardous Substances)와 같은 현대 제정지침에 부합하지 않는다. 최근에 도입된 대안적 물질들은 망간 산화물과 같은 희토류 및 전이 금속 산화물들의 혼합물들의 조성들을 포함한다. 실리콘 기반 서미스터들은 보통 고농도로 도핑된(heavy doped) 실리콘 웨이퍼들로부터 컷팅되고, 저항 정 온도

계수(positive temperature coefficient of resistance)를 갖는다.

[0006] 본 발명의 목적은 대안적인 온도 감지 디바이스 및 그러한 디바이스들을 제작하는 방법을 제공하는 것이다.

### 발명의 내용

[0007] 발명에 따라, 온도 감지 디바이스를 제작하는 방법이 제공되며, 이 방법은, 서미스터 구조물을 정의하기 위하여 적어도 하나의 실리콘 층 및 적어도 2개의 도전(conducting) 전극들 또는 콘택들을 형성하는 단계를 포함하고, 적어도 실리콘 층은 프린팅에 의하여 형성되고, 실리콘 층 및 도전성 전극들 또는 콘택들 중 적어도 하나는 그 것의 프린팅 동안 기판 물질에 의하여 지지된다.

[0008] 온도 감지 디바이스는 부 온도 계수(NTC: negative temperature coefficient) 서미스터일 수 있다.

[0009] 발명의 목적들을 위해, "프린팅"은 고체 기판 상에 액체 또는 콜로이달 혼합물을 증착하는 임의의 방법으로서 가장 넓은 의미로 해석되어야 하며, 따라서 드랍 캐스팅(drop casting), 슬릿 코팅(slit coating), 스핀 코팅(spin coating) 및 스프레이팅과 같은 코팅 방법들을 포함한다.

[0010] 스텐실(stencil)을 통한 코팅 또는 설계의 프린팅에 의한 직접 패터닝이 바람직하나, 기판 물질이 정확한 사이즈 및 형태를 갖는다면 이것은 필수적이지 않다.

[0011] 구체적으로, 프린팅의 정의는, 플렉소그래피(flexography) 및 레터프레스(letterpress)를 포함하는(그러나 이에 제한되는 것은 아님) 릴리프 프린팅(relief printing); 그라비아 프린팅(gravure printing)과 같은 인탈리오(intaglio) 프로세스들; 및 리소그래피, 제로그래피 및 서모그래피와 같은 평판 프린팅(planographic printing)의 모든 타입들을 포함해야 한다.

[0012] 예상된 평판 프린팅 방법들은 모든 오프셋 프린팅 프로세스들을 포함하며, 여기서 설계는 오프셋 리소그래피 및 오프셋 그라비아 프린팅과 같은 블랭킷 롤(blanket roll)로, 또는 패드 프린팅에서와 같이 탬폰(tampon)으로 먼저 전사된다.

[0013] 마지막으로, 프린팅이라는 용어는 대개 프린팅으로서 정의되는 전통적인 스텐실 방법들 및 스크린 프린팅 뿐만 아니라, 특히 잉크-젯 프린팅, 에어로졸 스프레이(aerosol spraying) 및 전기 수력학적 스프레이(electrohydrodynamic spraying)과 같은 비-접촉 프린팅 방법들을 포함해야 한다.

[0014] 적어도 실리콘 층 그리고 바람직하게 전극들 또는 콘택들은 상기 정의된 바와 같은 프린팅에 의하여 증착되어야 한다.

[0015] 상기 적어도 하나의 실리콘 층 및 적어도 2개의 도전성 전극들 또는 콘택들은 온도가 측정될 대상물에 직접 적용될 수 있어, 대상을 자체가 기판을 형성할 수 있다.

[0016] 대안적으로 기판이 서미스터에 대한 콘택들 중 하나를 형성하도록, 기판은 임의의 금속성, 또는 이와 다른 전기 도전성 바디일 수 있다.

[0017] 또 다르게는, 기판은 콘택들 및 실리콘 층이 그 상부에 증착될 수 있는 임의의 물질 또는 물질들의 조합일 수 있다.

[0018] 바람직한 일 실시예에서, 기판은, 예를 들어 금속 호일 또는 중합체 시트와 같은 고체 필름; 페이퍼 및 펠티드(felted) 물질들과 같은 섬유(fibrous) 물질; 또는 직물(woven fabric)로 구성될 수 있는 플렉서블 시트로 구성된다.

[0019] 디바이스에 대한 콘택들 중 하나의 콘택을 형성하지 않는 금속성 또는 도전성 기판의 경우에, 기판의 표면은 폐인트, 잉크, 바니시(varnish) 또는 라커의 형태로, 또는 산화, 침탄(carburization), 질화 또는 애노다이징(anodizing)과 같은 흔히 알려진 표면 처리 프로세스들을 통해, 중간 절연층의 적용에 의하여 비-도전성이 될 수 있다.

[0020] 다른 바람직한 실시예에서, 기판은 강성 시트로 구성되며, 강성 시트는 금속 시트, 글라스 또는 중합체 시트 또는 반도체 웨이퍼와 같은 고체 물질; 페이퍼 및 펠티드 물질들과 같은 섬유 또는 미립자(particulate) 물질을 포함하는 복합물(composite); 또는 직물을 포함하는 복합물로 구성될 수 있다.

[0021] 단지 예로서, 기판을 구성할 수 있는 가능한 물질들은, 구리, 알루미늄, 금, 은, 이들의 합금들, 실리콘, 계르마늄, 실리콘 탄화물, 플린트 글라스(flint glass), 크라운 글라스(crown glass), 보로실리케이트 글라스,

석영, 페이퍼 카드, 면, 유리 섬유, 폴리이미드, 폴리에스테르 및 그것의 유도체들, 다른 플라스틱들, 셀룰로즈 및 다수의 다른 물질들을 포함한다.

[0022] 온도가 측정될 바디가 기판을 형성하지 않는 경우, 기판은 서미스터 구조물에 대한 영구적 지지물(permanent support)을 형성할 수 있다.

[0023] 대안적으로 기판은 기판의 제작 동안 서미스터 구조물에 대한 일시적 지지물 또는 템플레이트(template)를 형성 할 수 있다.

[0024] 이 경우에, 기판은 회생적이며, 서미스터 구조물의 프린팅 이후에 화학적, 열적 또는 기계적 수단에 의하여 제거될 수 있거나, 또는 기판은 재사용가능 템플레이트를 형성할 수 있다.

[0025] 바람직한 실시예에서, 실리콘 층은 결합제 및 적절한 용매로 구성되는 액체 전색체(liquid vehicle) 및 실리콘 입자들을 포함하는 잉크로부터 형성된다. 몇몇 경우들에서, 프린팅 프로세스에 따라, 용매가 생략될 수 있거나 또는 시카티프(siccative)들 또는 안정제들과 같은 잉크들의 제제(formulation)에서 흔히 사용되는 부가적인 화합물들이 부가될 수 있다.

[0026] 실리콘 입자들은 10 나노미터 내지 100 마이크로미터 범위의 사이즈를 가져야 하며, 바람직하게는 50 나노미터 내지 250 나노미터의 특정적 사이즈를 갖는 나노입자들일 것이다.

[0027] 실리콘 나노입자들은 바람직하게 입자들 사이에 전기 전하의 전달을 허용하는 표면을 가져야 한다. 이것은 국제 특허 출원 WO 2007/004014에 설명된 바와 같은 산소, 하이드록실, 또는 수소 종에 의한 표면 맹글링 결합(dnagling bond)들의 적절한 종료를 통해 달성될 수 있다.

[0028] 프린팅된 실리콘 층 내에 형성되는 실리콘 나노입자 네트워크를 통한 전기 도전은 흡평 퍼컬레이션(hopping percolation) 프로세스에 의하여 발생하는 것으로 추정되고, 여기서 개별적 입자들 또는 입자들의 클러스터들 또는 반도체 물질과 도전성 전극 사이에서의 전하의 전달은 열적으로 활성화된 프로세스들에 의하여 제한된다. 따라서 저항 온도 계수는 대부분, 특히 그들의 표면들 및 계면들에서의 입자 특징들에 의해 결정된다. 다른 종, 특히 쉽게 이온화되는 작은 분자들의 흡착에 의하여 트랩핑된 상태들의 도입 또는 제거에 의한; 또는 다른 물질, 특히 큰 유기 분자들의 부분적 산화 또는 흡착에 의해 야기되는 계면 배리어의 두께의 변화에 의한 표면의 변형은 따라서 물질의 온도 반응(temperature response)을 변경하는데 또한 사용될 수 있다.

[0029] 저항의 온도 의존성에 기여하는 것으로 알려진 다른 메커니즘은 진성(intrinsic) 또는 저농도로 도핑된 lightly doped) 반도체들에서의 캐리어들의 열적 생성이다. 따라서 인습적으로 도핑된 n-타입 및 p-타입 물질로부터 반도체들을 제조하는 것 또는 국제 특허 출원 WO 2007/023362에 설명된 바와 같이 표면 위에 완전히 이온화된 이온 종을 흡착하는 것 중 어느 하나에 의하여, 실리콘 입자들의 적절한 도핑 레벨을 선택하는 것이 바람직하다.

[0030] 적절한 실리콘 나노입자들이, 별크 실리콘의 기계적 마모(attrition)에 의해 또는 모노실란 및 디실란 및 그들의 유도체들을 포함하는 임의의 실란 가스의 열분해와 같은 임의의 다른 방법에 의해 제작될 수 있으며, 여기서 국제 특허 출원 WO 2009/125370에 설명된 바와 같은 반화학량론적(sub-stoichiometric) 산화물들의 환원 또는 산소의 배제(exclusion)에 의하여 완전한(full) 산화가 방지된다.

[0031] 실리콘 층을 통한 전류의 전체 전달은 상호접속 입자들과 입자들의 클러스터들 사이에 퍼컬레이션 경로를 따른다. 따라서 공칭의, 즉 실온, 비저항은 주로 실리콘 층의 미세구조에 의하여 그리고 특히 입자 상호접속부들의 수에 의하여 좌우된다. 이것은 프린팅 프로세스 및 그것의 파라미터들의 선택에 의해서뿐 아니라, 실리카 또는 다른 세라믹과 같은 절연성 페이즈(phase) 나노입자들 또는 도전성의 금속성 나노입자들 중 어느 하나의 부가, 또는 실리콘 대 결합제 비율의 변경을 통한 잉크 조성의 변형에 의해서도 변형될 수 있다.

[0032] 방법은, 효율적으로 서미스터 구조물의 온도 의존적 저항과 병렬로 상대적으로 온도 독립적 내부 저항을 부가하기 위해, 실리콘 대 결합제 비율을 변형시키는 것에 의한 잉크 조성의 변형에 의해, 또는 잉크에 실리카 또는 다른 세라믹 나노입자들과 같은 절연 페이즈 또는 도전성 또는 반도전성 페이즈 중 어느 하나의 부가에 의한, 실리콘 입자 층으로의 적어도 하나의 부가적인 전도성 경로의 부가를 포함한다.

[0033] 실리콘 입자 층으로의 추가적인 도전성 경로들의 부가는 서미스터 구조물의 온도 의존적 저항과 병렬로 상대적으로 온도 독립적 내부 저항을 부가하는 효과를 갖는다. 이 조합은 디바이스의 온도 민감성을 변형하는데 또한 사용될 수 있다.

[0034] 이 아이디어의 연장으로, 부가적인 페이즈는 상이하게 도핑된 실리콘의 또는 다른 반도체 물질의 나노입자들을

포함할 수 있다.

- [0035] 대안적인 접근법에서, 프린팅된 온도 센서는 서미스터 구조물의 온도 의존적 저항과 병렬인, 도전성 잉크를 사용하여 프린팅된 온도 독립적 내부 저항과 함께 제조될 수 있다.

- [0036] 유사하게, 프린팅된 온도 센서의 공칭 저항은 서미스터 구조물의 온도 의존적 저항과 직렬로 온도 온도 독립적 내부 저항을 프린팅함으로써 증가될 수 있다.

- [0037] 사용되는 잉크들에서의 실리콘 파우더 대 결합제 비율은 실리콘 층의 구조적 무결성을 유지하도록 충분히 낮지만, 디바이스의 공칭 작동 범위에서 측정 가능한 전기 전도도를 허용하기에 충분해야 한다.

- [0038] 잉크의 나노입자 프랙션은 5% 내지 95% 범위일 수 있으나, 나노입자들의 농도가 약 25%의 실제적 제한을 갖는 더 낮은 퍼킬레이션 임계치들보다 상당히 더 큰 경우 최상의 성능이 더 잘(above) 달성된다.

- [0039] 하위 퍼킬레이션 임계치와 상위 퍼킬레이션 임계치 사이에서, 저항은 잉크의 실리콘 나노파우더의 프랙션의 변경에 의해 간단히 조정될 수 있다. 본원의 결과들은 이 영역이 잉크의 실리콘 나노파우더 입자들의 25 부피 퍼센트 내지 60 부피 퍼센트에 폭넓게 대응함을 보여준다.

- [0040] 물질 특성들이 잉크에서 실리콘의 프랙션과 함께 단지 약하게 변화하는 더 높은 퍼킬레이션 임계치를 초과하는 높은 입자 대 결합제 비율들에 대해 최상의 재현력(reproducibility)이 획득된다. 이것은 60%를 초과하는, 그리고 바람직하게는 80% 초과의 실리콘 프랙션으로 달성될 수 있다.

- [0041] 잉크 전색체는 유기 결합제 및 그것의 적절한 용매로 이루어진, 임의의 흔히 사용되는 잉크-베이스(ink-base)로 구성될 수 있다.

- [0042] 결합제는 폴리스티렌 또는 셀룰로즈 아세테이트 부티레이트와 같은 가용성 중합체, 또는 아크릴 에멀전과 같은 자동중합 단량체(autopolymerising monomer), 또는 WO 2007/072162에 설명된 바와 같은 아마씨 오일 또는 카렌들라 오일과 같은 천연 오일, 또는 지방산일 수 있다.

- [0043] 일 예에서 그리고 하기에 설명되는 예들에서, 사용되는 결합제는 수성 아크릴 에멀전을 포함하는 상업적 스크린 프린팅 잉크 베이스였으며, 용매는 프로필렌 글리콜이었다.

- [0044] 적절한 것으로 밝혀진 다른 결합제 및 용매 조합들은, 상업적 래커 씨너(lacquer thinner)들로 정제된 아마씨 오일, 아세톤, 또는 유사한 것들; 클로로폼을 갖는 폴리스티렌; 및 클로로폼을 갖는 셀룰로즈 아세테이트 부티레이트를 포함한다.

- [0045] 기판이 전기적 콘택틀 중 하나의 전기적 콘택을 형성하는 디바이스들을 제외하고, 전기적 콘택들이 프린팅에 의해 직접 패터닝되도록, 실리콘 층과 유사한 방식으로 전기적 콘택들을 제작하는 것이 바람직하다. 이러한 목적으로, 은, 금 또는 그래파이트 기반 스크린 프린팅 페이스트들 또는 금속성 나노입자들 기반 잉크들과 같은 임의의 흔히 이용가능한 도전성 잉크가 사용될 수 있다.

- [0046] 대안적으로, 콘택들은 스퍼터링, 증발, 또는 화학 기상 증착과 같은 다수의 구축된 박막 증착 프로세스들 중 하나의 프로세스에 의하여 형성될 수 있다. 동일하게, 전기 도금 또는 무전해 도금이 적용될 수 있다.

- [0047] 그러한 경우들에서, 콘택들은 원하는 형상을 형성하기 위하여 화학적 또는 전기화학적 에칭, 레이저 스크라이빙 또는 다른 방식의 물질 제거에 의해 정확한 형태로 패터닝될 수 있다.

- [0048] 바람직한 일 실시예에서, 콘택들은 원형 기하학적 구조를 가져, 서미스터 구조물의 방사상 전기 경로가 측정된 저항이 프린팅 방향에 관한 모든 방향들에 걸쳐 평균화되는 것을 보장하여, 프린팅 프로세스에서의 임의의 측방 이방성의 효과가 제거된다.

- [0049] 일반적으로, 프린팅된 실리콘 물질의 높은 비저항(resistivity)으로 인하여, 서미스터 디바이스의 종횡비는 낮아야 하며, 이로 인해 전류를 공급하는데 사용되는 임의의 2개의 콘택들 사이의 거리는 콘택들 사이의 반도전성 경로의 폭에 비해 작아야 한다.

- [0050] 바람직하게, 서미스터 디바이스의 종횡비는 1/30 미만, 그리고 더욱 바람직하게는 1/1000 미만이다.

- [0051] 일 실시예에서, 이것은 첨부 도면들의 도 1에 예시된 바와 같이, 도전성 물질의 2개 층들 사이에 프린팅된 실리콘 물질의 층을 포함하는 다중층 구조물에 의해 달성될 수 있다. 그러한 디바이스에서, 실리콘 층의 평면에 적각인 방향으로, 실리콘 층의 두께를 통해 저항이 측정된다. 그 결과, 그러한 온도 센서의 영역은 거의 무한정

으로(indefinitely) 연장될 수 있고, 어떠한 임의의 형상을 취할 수 있다.

[0052] 그러나 일반적으로, 제조 프로세스의 간략성으로 인하여 일련의 동일 평면 상의 전극들 또는 콘택들이 선호된다. 이 경우에 적어도 2개의 도전성 콘택들이 임의의 적절한 프로세스를 사용하여, 실리콘 층 위에 증착되거나, 또는 먼저 기판 위에 증착되고 후속하여 실리콘 층에 오버프린팅된다. 이들 2개 기하학적 구조들은 탑-콘택(top-contact) 또는 바텀-콘택(bottom-contact) 디바이스들로서 각각 지칭될 수 있다.

[0053] 동일 평면 상의 콘택들을 갖는 디바이스들에 대해, 하기의 도 2 내지 8에 표시된 특정 기하학적 구조들이 폭 대길이 비를 증가시키기 위하여 적용될 수 있다.

[0054] 일 실시예에서, 나란히 연장되는 2개의 신장된 병렬 콘택들은 나선형의(spiral) 또는 구불구불한(meandering) 경로를 정의하는 패턴으로 증착되어, 비교적 큰 영역을 커버하고, 그에 의해 기판의 대응하여 형상화된 영역의 평균 온도가 모니터링되게 허용한다.

[0055] 다른 실시예에서, 병렬로 그리고 서펜타인(serpentine) 캡을 정의하기 위해 서로의 근처에서 연장되는 다수의 신장 스트립들 또는 핑거(finger)들을 각각 갖는, 2개의 서로 맞물린(interdigitated) 전기적 콘택들은, 프린팅된 미립자 실리콘의 층에 의해 연결되거나 브릿징된다.

[0056] 프린팅된 미립자 실리콘의 층은 전극들 사이에서 서펜타인 캡을 따르도록 구조화될 수 있거나, 또는 전극들 사이에서 서펜타인 캡 위에 연속층을 형성할 수 있다.

[0057] 다른 실시예에서, 4개의 전기적 콘택들은 더 높은 정확도를 달성하기 위하여 흔히 사용되는 반 데어 파우브(van der Pauw) 기하학적 구조들 중 임의의 것 또는 종래의 선형적 4-포인트 기하학적 구조 중 어느 하나로 증착되며, 상기 4개의 전기적 콘택들 중 2개는 온도 감지 디바이스에 전류를 공급하는데 사용되고, 상기 4개의 전기적 콘택들 중 2개는 사용 중인 전압을 모니터링하는데 사용된다.

[0058] 발명은 상기 정의된 방법들에 의하여 제작되는 온도 감지 디바이스로 확장된다.

### 도면의 간단한 설명

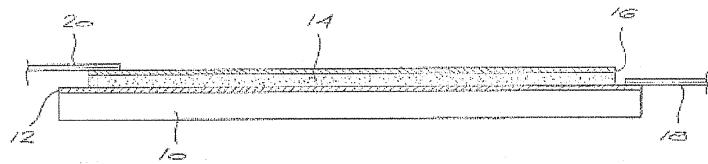

[0059] 도 1은 본 발명에 따른 다중-층 온도 감지 디바이스의 개략적인 측면도이다.

도 2는 나선형 구성을 갖는, 발명에 따른 프린팅된 서미스터의 제1 실시예의 어레인지먼트(arrangement)를 보여주는 개략도이다.

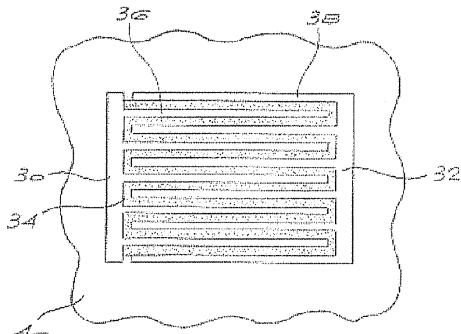

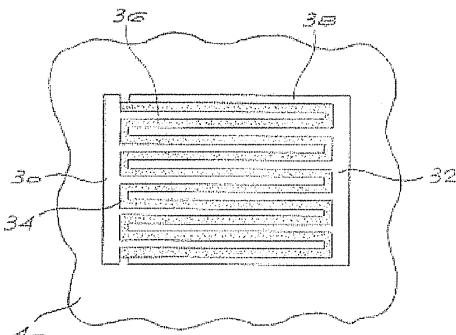

도 3은 서로 맞물린 구성을 갖는, 발명에 따른 프린팅된 서미스터의 제2 실시예의 어레인지먼트를 보여주는 개략도이다.

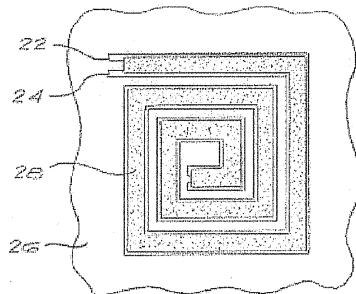

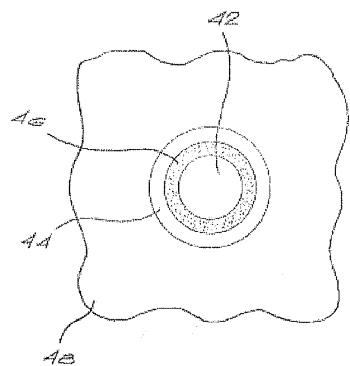

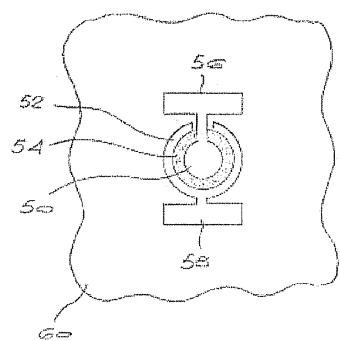

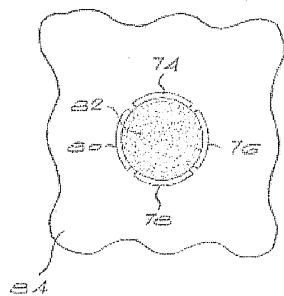

도 4 및 5는 동심으로(concentrically) 배열된 콘택들을 갖는, 발명에 따른 프린팅된 서미스터의 제3 실시예 및 제4 실시예의 어레인지먼트를 보여주는 개략도들이다.

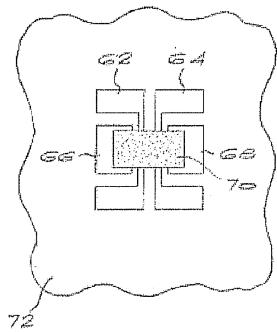

도 6은 4개 전극 구성을 갖는, 발명에 따른 프린팅된 서미스터의 제5 실시예의 어레인지먼트를 보여주는 개략도이다.

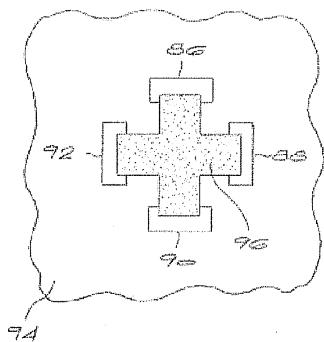

도 7은 전기 저항을 결정하기 위하여 반 데어 파우브 방법이 사용될 수 있는 프린팅된 미립자 실리콘의 층에 의해 연결되는 4개의 전기적 콘택들을 갖는, 발명에 따른 프린팅된 서미스터의 제6 실시예의 어레인지먼트를 보여주는 개략도이다.

도 8은 도 7의 실시예와 유사하지만 확장된 콘택 아암(contact arm)들을 갖는, 발명에 따른 프린팅된 서미스터의 제6 실시예의 어레인지먼트를 보여주는 개략도이다.

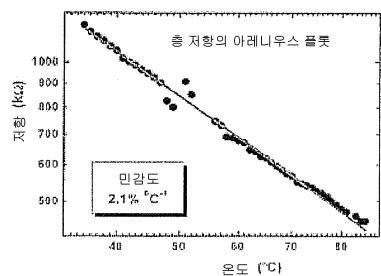

도 9는 도 6에 도시된 설계의 서미스터의 일 예에 대한 아레니우스 곡선(Arrhenius curve)을 보여주는 그래프이다.

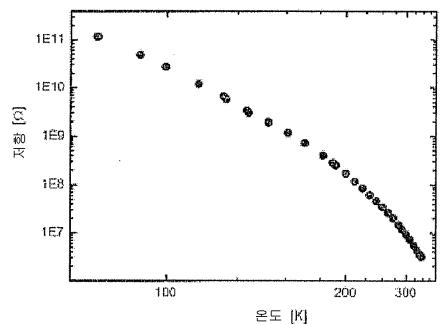

도 10은 도 5에 도시된 설계의 바텀-콘택 서미스터의 예에 대한 아레니우스 곡선을 보여주는 그래프이다.

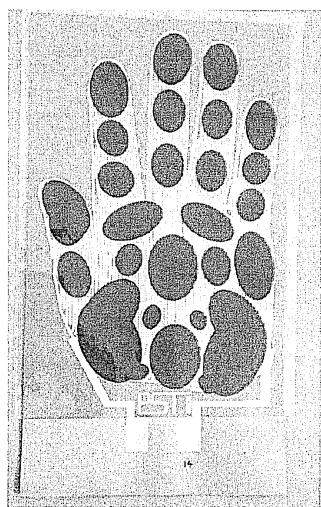

도 11은 발명의 방법에 따라 형성되는 부 온도 계수 서미스터의 일 실시예의 사진이다.

도 12는 도 11에 도시된 서로 맞물린 서미스터의 변형의 사진이다.

### 발명을 실시하기 위한 구체적인 내용

[0060] 도 1은 본 발명의 예시적 실시예에 따른 기본적 다중-층 서비스터 구조물의 개략적인 측단면도를 도시한다.

[0061] 서비스터 구조물은 기판(10) 상에 형성되며, 제1 금속성 층(12), 제1 금속성 층(12) 상에 프린팅된 미립자 실리콘의 층(14), 및 미립자 실리콘의 층(14) 위에 증착된 제2 금속성 층(16)을 포함한다. 상기 표시된 바와 같이, 기판(10)은 다수의 형태들을 취할 수 있으나, 통상적으로, 예를 들어, 금속 호일 또는 중합체 시트와 같은 고체 필름; 페이퍼 및 펠터드 물질들과 같은 섬유 물질; 또는 직물로 구성될 수 있는, 플렉서블 시트로 구성될 것이다. 이들 예들은 단지 예시를 목적으로 제공되며, 제한하도록 의도되지 않는다. 금속성 층들 및 미립자 실리콘 층은 상기 정의된 바와 같은 프린팅에 의해 바람직하게 증착된다.

[0062] 도 1의 실시예에서, 기판(10)은 비-도전성이거나, 또는 도전성이며, 도전성이라면 서비스터 구조물에 대한 전기적 콘택의 역할을 하지 않는다. 이 실시예에서, 제1 및 제2 금속성 층들(12 및 16)은 도전성 전극들 또는 콘택들의 역할을 하며, 여기에는 개별적인 와이어들 또는 다른 컨덕터들(18 및 20)이 연결될 수 있다.

[0063] 발명의 방법들에 의해 제작되는 서비스터들의 수 개의 예시적 실시예들이 도 2 내지 8을 참고로 하기에 설명된다.

[0064] 도 2에 도시된 바와 같이, 제1 실시예는 바텀-콘택 2-단자 서비스터이다. 이 실시예는 기판(26) 상에 형성된 2개의 신장형 도전성 콘택들(22 및 24)을 포함하며, 이 신장형 도전성 콘택들은 나란히 연장되고 나선형과 같은 패턴으로 배열되어, 비교적 큰 영역을 커버할 수 있다. 콘택들은 신장형 나선 형상을 갖고 부분적으로 개별 콘택들 위에 놓이는 프린팅된 미립자 실리콘의 층(28)에 의하여 연결되거나 브릿징되고, 전체 구조물은 기판에 의해 지지된다. 필요에 따라 콘택들(22 및 24)에 전기 접속부들이 만들어질 수 있다.

[0065] 예시되는 준비된(squared-off) 나선 형상 대신에, 미립자 실리콘의 브릿징 층 및 콘택들은 다른 평행한 구불구불한 또는 곡선형의 나선형 경로를 따를 수 있다. 서비스터 구조물은 기판(26)(또는 기판(26)이 부착되는 대상물)의 크고 아마도 불규칙적으로 형상화되는 영역의 평균 온도가 모니터링되도록 허용하기 위하여, 비교적 큰 영역을 커버할 수 있다.

[0066] 유사한 탑 콘택 디바이스는 증착 시퀀스를 단순히 반전시킴으로서 제조될 수 있으며, 미립자 실리콘의 층이 먼저 프린팅되고 콘택들이 그 위에 증착된다. 대안적 접근법에서, 실리콘 스트립은 콘택 스트립들 상에 또는 그 아래에 증착되는 연속적 층을 형성할 수 있다.

[0067] 도 3은 2개의 서로 맞물린 전기적 콘택들(30 및 32)로 구성되는 서로 맞물린 2개의 단자 서비스터의 예시이며, 이 전기적 콘택들(30 및 32)은 프린팅된 미립자 실리콘의 층(34)에 의하여 연결되거나 브릿징된다. 콘택들(30 및 32) 각각은, 서펜타인 캡을 정의하기 위하여, 별별로 그리고 서로의 근처에서 연장되는 다수의 신장 스트립들 또는 평거들(36 및 38)을 가지며, 이 서펜타인 캡 상에는 실리콘 잉크의 층이 프린팅되어 층(34)을 형성하고 그 세트의 전극들을 연결한다. 콘택들 또는 전극들 그리고 그들의 평거들의 수 및 길이는 임의의 원하는 영역을 커버하기 위하여 변경될 수 있다. 서비스터가 기판(40) 상에 프린팅된다.

[0068] 이 실리콘 층(34)은 도시된 바와 같이 전극들 사이에 캡들을 따르도록 구조화될 수 있거나, 또는 연속적 층을 형성할 수 있다. 디바이스는 상기 설명된 바와 같이 물질들의 증착 순서에 따라, 바텀-콘택 또는 탑-콘택 디바이스 중 어느 하나일 수 있다.

[0069] 도 4는, 서비스터의 전기 경로가 내부 전기적 콘택(42) 및 동심 링-형상 외부 콘택 또는 전극(44)을 갖는 원형 구조물의 방사상 방향인 일 실시예를 도시한다. 콘택들은 프린팅된 미립자 실리콘의 환형 층(46)에 의하여 연결된다. 서비스터가 기판(48) 상에 프린팅된다.

[0070] 도 5는 2개 콘택들이 동축 기하학적 구조로 증착된 솔리드 내부 원(50) 및 동심 외부 링(52)을 포함하는, 도 4의 실시예와 유사한 실시예를 도시한다. 프린팅된 미립자 실리콘 층(54)은 2개 콘택들을 브릿징하는 제2 동심 링을 형성한다. 그러나 도 5의 디바이스에서, 내부 전극 콘택(50)은 외부 콘택(52)의 캡을 통해 제1 전기적 콘택 패드로 방사상으로 바깥쪽으로 연장된다. 외부 콘택은 제2 전기적 콘택 패드(58)로 바깥쪽으로 또한 연장된다. 구조물이 기판(60) 상에 프린팅된다. 2개 콘택들 사이의 환형 캡을 브릿징하는, 프린팅된 실리콘 층(54)에 의하여 정의되는 동심 링은 완성형 또는 (예시된 바와 같이) 파상형(broken)일 수 있다.

[0071] 탑-콘택 또는 바텀-콘택 디바이스들 중 어느 하나로서 제작될 수 있는, 도 4 및 5의 예시적 실시예들은 특히 프린팅 프로세스들에 적응된다. 이들 서비스터 구조물들의 방사상 전기적 경로는, 측정된 저항이 프린팅 방향에 관한 모든 방향들에 걸쳐 평균화되도록 보장하고, 따라서 증착 프로세스에서 임의의 측방 이방성의 효과를 제거한다.

- [0072] 더 높은 정확성을 위해, 잘 알려진 4 포인트 저항 측정 기법에서의 사용을 위해 적응되는 서미스터 디바이스들이 바람직할 수 있다. 이것은 도 6에 도시된 바와 같은 4개의 동일 평면 상의 전극들을 갖는 디바이스에 의하여 달성될 수 있다. 이 디바이스는, 정밀하게 구조화된 2개의 내부 전극들(62 및 64)(이 2개의 내부 전극들(62 및 64) 간의 전위차가 결정됨) 및 2개의 부가적인 전극들(66 및 68)(이 2개의 부가적인 전극들(66 및 68)을 통해 전류가 공급됨)을 갖는다. 모든 4개 전극들은 프린팅된 미립자 실리콘의 오버-프린팅된 층(70)에 의하여 연결된다. 디바이스는 기판(72) 상에 형성된다. 내부 전극들(62 및 64) 각각은 내부 전극들의 각각의 단부에서 확대된 콘택 패드를 갖는다.

- [0073] 2개의 내부 전극들(62 및 64)은 미립자 실리콘 층의 전위차를 측정하는데 사용되고, 매우 정밀하게 프린팅될 수 있다. 외부 전극들(66 및 68)은 여자 전류(excitation current)를 공급하는데 사용되며, 내부 전극들에 비해 상대적으로 클 수 있다. 예시된 바와 같이, 이 기하학적 구조의 가장 단순한 변형에서, 실리콘 층(70)은 디바이스의 중앙 영역에서 4개 전극들을 브릿징하는 두꺼운 스트립으로서 간단히 프린팅된다.

- [0074] 4 포인트 저항 방법에 대한 대안은 도 7에 도시된 원형 설계 또는 도 8에 도시된 "그릭 크로스(greek cross)" 기하학적 구조와 같은, 잘 알려진 반 데어 파우브 기하학적 구조들 중 임의의 기하학적 구조를 사용하는 것이다.

- [0075] 도 7의 프린팅된 서미스터 디바이스에서, 중실형(solid) 원형 형상을 갖는 프린팅된 미립자 실리콘의 층(82)에 의하여 연결된, 4개의 등거리로 이격된 웨지형 전기적 콘택들(74, 76, 78 및 80)이 제공된다. 디바이스가 기판(84) 상에 프린팅된다. 4개 콘택들은 패턴의 중앙에, 프린팅된 실리콘의 층에 의해 충진되는 공간을 갖는 원형 패턴으로 대칭적으로 배열된다. 가장 높은 정확성을 획득하기 위하여, 이 프린팅된 실리콘 층은 원형 형태를 갖고, 중앙에 위치되어야 한다. 그러나 이것은 필수적이지 않고, 적합한 디바이스들이 전극들 상에 또는 전극들 아래에 실리콘의 연속 층을 프린팅함으로써 제작될 수 있다.

- [0076] 도 8의 디바이스에서, 4개 전극들(86, 88, 90 및 92)은 기판(94) 상에 대칭적으로 증착된다. 미립자 실리콘의 층(96)은 콘택들 사이에서 디바이스의 중앙 영역에 증착된다. 층(96)은 그릭 크로스 기하학적 구조를 가지며, 크로스의 아암들의 팁들은 부분적으로 개별 전극들 위에 놓이며, 전극들 사이의 2개의 직각 실리콘 경로들을 정의한다.

- [0077] 발명의 서미스터들에 의하여 정의될 수 있는 반 데어 파우브 기하학적 구조의 추가적인 잘 알려진 변형들은 클로버 잎 또는 몰타 십자가(Maltese cross)와 같은 이들 2개의 기본적 형태들의 기하학적 조합하는 구조들을 포함한다.

- [0078] 디바이스를 제조하기 위한 프린팅의 사용에 의해 가능해진, 온도 의존적 저항을 결정하는 신규한 방법은, 탑 콘택 및 바텀 콘택을 형성하는 동일한 대칭적 전극 구조물을 가짐으로써 반 데어 파우브 기법의 원리들을 확장시키는 것이다. 상기 제시된 2-콘택 설계들 중 임의의 설계는 표준 4-포인트 반 데어 파우브 기법과 유사한 방법에서 벌크(bulk) 실리콘 층을 통해 저항을 결정하는데 사용될 수 있다. 유사하게, 탑 콘택 및 바텀 콘택 양자 모두로서 적용되는 4-전극 구성들은 저항 측정의 훨씬 더 높은 정확성 및 안정성을 제공할 것이다.

- [0079] 더욱이, 상기 설계들 중 임의의 설계, 또는 전극들의 유사한 어레이인자먼트들은 주어진 영역에 걸친 온도 분포가 맵핑되도록 허용할 픽셀처리된(pixellated) 센서를 형성하기 위하여, 기판 상의 넓은 영역에 걸쳐 어레이로 배열될 수 있다.

- [0080] 예 1

- [0081] 제1 예에서, 도 6에 도시된 설계에 따라 부 온도 계수 서미스터가 제작되었다. 4개 은 전극들 또는 콘택들이 Du Pont 5000 은 컨덕터를 사용하여 스크린-프린팅에 의하여  $80 \text{ g/m}^2$  백상지(wood-free paper) 시트 기판 상에 증착되었다. 임의의 2개의 인접한 전극들 사이의 간극(separation)은 2 mm였다. 대기 조건들 하에서 대략 하루 동안 은 잉크가 건조되도록 허용한 이후, 실리콘 잉크는 디바이스의 모든 4개 전극들 사이에 접속부를 형성하기 위하여 드랍-캐스트(drop-cast)되었다. 잉크에서 사용되는 실리콘 나노입자들은 WO 2009/125370에 개시된 방법에 따라, 봉소 도핑된 p-타입 실리콘 웨이퍼로부터 밀링되었다. 이들 입자들은 95 중량 퍼센트의 실리콘의 비율로 상업적으로 이용가능한 아크릴 스크린-프린팅 베이스와 혼합되었으며, 잉크의 농도(consistency)는 프로필렌 글리콜로 씨닝(thinning)함으로써 조정되었다.

- [0082] 완성된 디바이스는 대략 15 mm × 10 mm 사이즈의 작은 플렉서블 디바이스를 형성하기 위하여 더 큰 페이퍼 시트로부터 컷 아웃되었다. 예비 테스트들에서, 실온 전류/전압 특징들은 4-포인트 기법 및 2-포인트 기법 양자

모두에 의하여 결정되었다. 이것의 온도 반응을 테스트하기 위하여, 이 디바이스는, 프린팅된 서미스터 디바이스와 글라스 사이에 페이퍼 기판이 있도록, 그리고 디바이스의 축에 글라스의 원주(circumference)가 따르도록, 65 mm 직경의 글라스 비이커의 외부에 접착 테이프로 고정되었다.

[0083] 저항의 온도 의존성을 교정하기 위하여, 비이커는 얼음 물로 채워지고, 전기 핫플레이트로 가열되면서, 물의 온도가 디지털 온도계로 측정되었다. 편의를 위해, 저항은 디지털 멀티미터로 간단히 측정되었다. 도 9는 서미스터의 저항 온도 반응을 아레니우스 스케일로 보여준다. 표시된 온도 범위에서, 디바이스는 흔히  $2210 \pm 30K$ 의 베타 값을으로서 지칭되는, 대수 온도 계수를 나타낸다.

## 예 2

[0085] 제2 예에서, 또한 도 5에 도시된 설계에 따라, 부 온도 계수 서미스터가 제작되었다. 은 콘택들이 Du Pont 5000 은 컨덕터를 사용하여 스크린-프린팅에 의하여  $80 g/m^2$  백상지의 시트를 포함하는 기판 상에 증착되었다. 내부 전극의 직경이 5 mm였고, 2개 전극들 사이의 간극은 0.5 mm였다. 은 잉크가 대기 조건들 하에서 대략 하루 동안 건조되도록 허용한 이후, 실리콘 층은 WO 2009/125370에 개시된 방법에 따라 2503 금속금(grade metallurgical) 실리콘으로부터 밀링된 실리콘 나노입자들을 사용하여, 전극들 사이의 캡 위에 스크린 프린팅되었다. 이들 나노입자들은 88 중량 퍼센트의 실리콘의 비율로 상업적으로 이용가능한 아크릴 스크린-프린팅 베이스와 혼합되었으며, 잉크의 농도는 프로필렌 글리콜로 씨닝(thinning)함으로써 조정되었다.

[0086] 완성된 디바이스는 대략  $20 mm \times 15 mm$  사이즈의 작은 플렉서블 디바이스를 형성하기 위하여 더 큰 페이퍼 시트로부터 컷 아웃되었다. 은 와이어들은 안전한 영구적 접속부들을 형성하기 위하여 콘택 패드들에 납땜되었다. 제로(zero) 자계 조건들 하에서, Lake Shore 7700 Hall 측정 시스템 및 연관된 저온 유지 장치(cryostat)를 사용하여 50K 내지 350K의 온도 범위에서 디바이스에 대해 전류/전압 특징들이 측정되었다. 도 10의 예로서 도시된 저항/온도 특징들은 낮은 여자 전류에서 전압/전류 특징들의 기울기로부터 결정되었다. 확장된 온도 범위에 걸쳐, 통상적으로 액체 질소 온도들에서 1000K 그리고 상온 근처에서 2000K의 적어도 2개의 아레니우스 계수들이 존재한다. 유사한 디바이스들에 대한 추가적 연구들은 350K 초과의 온도들에서 명백한 대략 10000K의 제3 베타 값을 표시한다. 상이한 범위들의 이들 상이한 베타 값들의 조합은 프린팅된 실리콘 서미스터들이 광범위한 온도들에 걸쳐 적용되도록 허용한다.

## 예 3

[0088] 도 11은 도 3에 도시된 설계에 따른 부 온도 계수 서미스터의 사진이다. 이 경우에, 실리콘은 서로 맞물린 은 콘택들 위에 중실형 블록으로서 프린팅되지만, 콘택들 사이에 증착된 실리콘의 영역만이 온도 의존적 저항에 기여한다. 낮은 저항에 대해, 실리콘 반도체의 길이 대 폭 종횡비는 이상적으로는, 1/1000 미만으로 낮아야 한다. 이 예에서, 은 콘택들은 인접한 전극들 사이의 24개의 캡들과 함께 25개의 개별적 전극으로 구성되며, 각각의 캡은 16 mm의 길이를 갖고, 각각의 캡의 폭(인접한 전극들 사이의 간극)은 0.25mm이다.

[0089] 높은 저항 디바이스이며 (도 5의 컨덕터들 사이의 캡을 정의하는 원의 원주에 대한 컨덕터들 사이의 가로(transverse) 캡의 비율에 의해 주어지는) 대략 1/30의 길이 대 폭 종횡비를 갖는 예 2의 디바이스와 대조적으로, 본 예의 설계는 1/1600의 종횡비 및 동일한 실리콘 층 두께에 대한 대응하는 더 낮은 저항을 갖는다.

[0090] 은 콘택들은 Du Pont 5000 은 컨덕터를 사용하여 160 gsm 페이퍼 보드 기판들 상에 스크린 프린팅에 의하여 증착되었다. 대기 조건들 하에서 대략 하루 동안 은 잉크가 건조되도록 허용한 이후, 실리콘 층은 WO 2009/125370에 개시된 방법에 따라 2503 금속금 실리콘으로부터 밀링된 실리콘 나노입자들을 사용하여, 전극들 사이의 캡 위에 스크린-프린팅되었다. 이들 나노입자들은 80 중량 퍼센트의 실리콘의 비율로 상업적으로 이용가능한 아크릴 스크린-프린팅 베이스와 혼합되었으며, 잉크의 농도는 프로필렌 글리콜로 씨닝함으로써 조정되었다.

[0091] 최종적 서미스터는 그 후 남아프리카 공화국 가특허 명세서 2010/06533에 개시된 방법에 따라 이산 컴포넌트로서 패키징되었으며, 은 콘택들은 플라스틱 라미네이션으로부터 돌출되도록 허용된다. 다수의 그러한 디바이스들의 테스트들이 20 °C 내지 60 °C 온도 범위에 걸쳐 박스 오븐에서 수행되었으며,  $\pm 100 K$ 의 통계적 변이성(statistical variation)으로 2000 K의 일관된 베타 값을 산출했다. 실리콘 층의 두께에 따라 통상적 저항들은 100 kΩ이다. 15 K 내지 350 K의 확장된 온도 범위에 걸친, Lake Shore 7700 시스템을 사용한 저온 측정들로부터의 전도도의 상세한 분석은 대략 20 K, 650 K 및 1900 K의 3개의 특징적 베타 값을 보였다.

## 예 4

[0093]

도 12는 도 3의 기본적 설계에 따른, 예 3에 설명된 서로 맞물린 서미스터의 변형의 사진이며, 이는 더 큰 영역에 걸쳐 확장되고 그것의 형태를 그래픽 설계로서 취한다. 일 예로서, 풀 사이즈 휴먼 핸드프린트(full size human handprint)가 설계로서 선택되었으나, 제한 없이 임의의 다른 추상적인 또는 그림을 이용한 설계가 선택될 수 있다.

[0094]

다수의 은 트랙들(이들의 공통 접속부들은 손의 경계선을 형성함)은 서로 맞물린 전극들을 형성하기 위하여 DuPont 5000 은 컨덕터를 사용하여 180 gsm 페이퍼 보드의 다양한 컬러들로 스크린 프린팅된다. 전극들 사이의 캡들은 설계의 형상에 맞도록 조정되고, 0.5 mm 내지 1 mm 범위이다. WO 2009/125370에 개시된 방법에 따른 2503 금속급 실리콘으로부터 밀링된 나노입자들의 80 중량 퍼센트를 포함하는 실리콘 잉크는, 병렬로 연결된 서미스터들의 세트 및 그래픽 설계 양자 모두를 형성하기 위하여 상이한 위치들에서 프린팅된다. 동일하게 손의 전체 영역은 실리콘에서 프린팅될 수 있으나, 이것은 서미스터의 동작 및 구성의 원리들의 예시를 허용하기 위하여 수행되지는 않았다. 프린팅 이후에, 서미스터는 남아프리카 공화국 가특허 명세서 2010/06533에 개시된 방법에 따라 이산 컴포넌트로서 패키징되었으며, 은 콘택들은 플라스틱 라미네이션으로부터 돌출되도록 허용된다. 실리콘 층의 두께에 따라 이 설계를 위한 통상적인 저항들은  $20 \text{ k}\Omega$  내지  $40 \text{ k}\Omega$ 이며, 베타 값은  $2000 \pm 100$  K에 일치한다.

## 도면

### 도면1

### 도면2

### 도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12