(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-34976

(P2010-34976A)

(43) 公開日 平成22年2月12日(2010.2.12)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H04L 1/00</b> (2006.01)  | H04L 1/00  | B 5J065     |

| <b>H03M 13/15</b> (2006.01) | H03M 13/15 | E 5K014     |

|                             | H04L 1/00  |             |

審査請求 未請求 請求項の数 9 O L (全 14 頁)

|           |                              |            |                                            |

|-----------|------------------------------|------------|--------------------------------------------|

| (21) 出願番号 | 特願2008-196438 (P2008-196438) | (71) 出願人   | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (22) 出願日  | 平成20年7月30日 (2008.7.30)       | (74) 代理人   | 100123434<br>弁理士 田澤 英昭                     |

|           |                              | (74) 代理人   | 100101133<br>弁理士 濱田 初音                     |

|           |                              | (72) 発明者   | 宮田 好邦<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

|           |                              | (72) 発明者   | 吉田 英夫<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

|           |                              | F ターム (参考) | 5J065 AD08 AD11<br>5K014 BA08 EA02 FA13    |

(54) 【発明の名称】誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法

## (57) 【要約】

【課題】短縮フレームの情報ビットの長さに応じてRS符号のパリティビットの長さを変動させることにより符号化率を向上させた符号化、復号を実現できる誤り訂正符号化装置、誤り訂正復号装置、伝送システム及び誤り訂正符号化方法を提供する。

【解決手段】入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成し、サブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するフレーム生成手段と、

前記フレーム生成手段で生成されたサブフレームごとにロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化する符号化手段とを備えた誤り訂正符号化装置。

**【請求項 2】**

符号化手段は、所定の情報長を有するサブフレームとの間で、復号後のビット誤り率が均一になるように、前記所定の情報長に満たないサブフレームに付与する検査ビット長を設定することを特徴とする請求項 1 記載の誤り訂正符号化装置。 10

**【請求項 3】**

符号化手段は、所定の情報長に満たないサブフレームの情報長と所定の閾値を比較し、この比較結果に応じて前記サブフレームに付与する検査ビット長を設定することを特徴とする請求項 1 記載の誤り訂正符号化装置。

**【請求項 4】**

符号化手段は、所定の情報長に満たないサブフレームの情報長が所定の閾値よりも短い場合、前記サブフレームに付与する検査ビット長を、フレーム生成手段で生成された他のサブフレームの検査ビット長より短くすることを特徴とする請求項 3 記載の誤り訂正符号化装置。 20

**【請求項 5】**

符号化手段は、フレーム生成手段で生成されたサブフレームごとにロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たない短縮されたサブフレームに対し、当該サブフレームの情報長に応じて検査ビットの一部を棄却して誤り訂正符号化することを特徴とする請求項 1 記載の誤り訂正符号化装置

**【請求項 6】**

符号化手段は、ロック符号としてリード - ソロモン符号を用いることを特徴とする請求項 1 から請求項 5 のうちのいずれか 1 項記載の誤り訂正符号化装置。

**【請求項 7】**

請求項 1 から請求項 6 のうちのいずれか 1 項記載の誤り訂正符号化装置で生成された誤り訂正符号化データを受信し、当該誤り訂正符号化データを構成する各サブフレームに同期するためのフレーム同期信号を生成するフレーム同期手段と、 30

前記フレーム同期手段で生成されたフレーム同期信号に基づいて、前記誤り訂正符号化データを、前記サブフレームごとに誤り訂正を行って復号するとともに、所定の情報長に満たないサブフレームに当該情報長に応じた長さの検査ビットを付与した符号化データを復号する復号手段とを備えた誤り訂正復号装置。

**【請求項 8】**

符号化手段は、請求項 5 記載の誤り訂正符号化装置で棄却された検査ビットの一部を消失ビットとみなして復号することを特徴とする請求項 7 記載の誤り訂正復号装置。 40

**【請求項 9】**

入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するステップと、

前記ステップで生成されたサブフレームごとにロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化するステップとを備えた誤り訂正符号化方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

10

20

30

40

50

この発明は、光伝送システム等のデジタル通信装置に用いる誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法に関するものである。

【背景技術】

【0002】

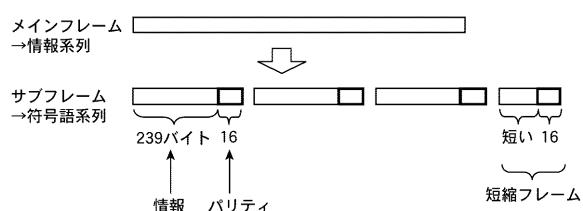

I E E E 8 0 2 . 3 a h にて規格化された G E - P O N ( Gigabit Ethernet-Passive Optical Network (Ethernetは登録商標) ) では、誤り訂正符号化方式 ( FEC ; Forward Error Correction ) として R S ( Reed-Solomon ) 符号を採用している。非特許文献 1 に記載される従来の技術では、図 8 に示すフレームフォーマットのように、メインフレームであるイーサネット ( 登録商標 ) フレームを情報系列として、 R S 符号による符号化処理 ( R S 符号化 ) が行われる。

10

【0003】

具体的には、メインフレームを、情報ビットの長さが 239 バイト、パリティビットの長さが 16 バイトに固定された複数のサブフレームに分割し、これらサブフレーム毎に R S 符号化して符号語系列を生成する。このとき、最後に余ったサブフレーム ( 符号語 ) のみ、パリティ長は 16 バイト固定としつつ、情報長を短縮して符号化する。この最後のサブフレームを短縮フレーム ( Shortened frame ) と呼ぶ。なお、図 8 において、制御用のオーバーヘッド ( O H ) 等は記載を省略している。

【0004】

【非特許文献 1】 I E E E S t d - 8 0 2 . 3 a h - 2 0 0 4 ( 6 5 . 2 . 3 . 1 節 )

20

【発明の開示】

【発明が解決しようとする課題】

【0005】

上述したように、従来では、短縮フレームに対して、それ以外のサブフレームと同一長のパリティシンボルを付加するような符号化が行われるため、符号化率が低減するという課題があった。

【0006】

この発明は、上記のような課題を解決するためになされたもので、短縮フレームの情報ビットの長さに応じて R S 符号のパリティビットの長さを変動させることにより符号化率を向上させた符号化、復号を実現できる誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法を得ることを目的とする。

30

【課題を解決するための手段】

【0007】

この発明に係る誤り訂正符号化装置は、入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するフレーム生成手段と、フレーム生成手段で生成されたサブフレームごとにロック符号による誤り訂正符号化を行うとともに、情報ビットが所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化する符号化手段とを備えるものである。

【発明の効果】

【0008】

この発明によれば、入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成し、サブフレームごとにロック符号による誤り訂正符号化を行うとともに、情報ビットが所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化するので、符号化率を向上することができるという効果がある。

40

【発明を実施するための最良の形態】

【0009】

実施の形態 1 。

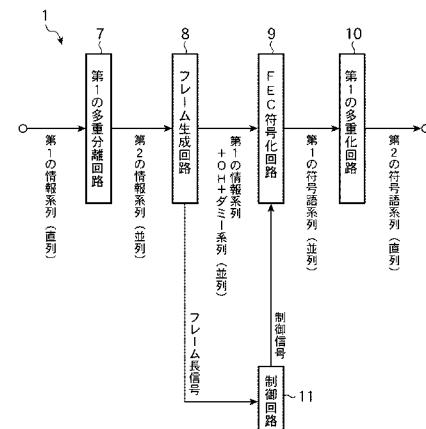

図 1 は、この発明の実施の形態 1 による誤り訂正符号化装置を用いたデジタル伝送システム ( 以下、単に伝送システムと呼ぶ ) の構成を示すブロック図である。図 1 において、実施の形態 1 によるデジタル伝送システム A は、誤り訂正符号化装置 1 、変調器 2 、通信

50

路 3 、復調器 4 、アナログ / デジタル (A / D) 変換器 5 、及び誤り訂正復号装置 6 を備える。

【 0 0 1 0 】

誤り訂正符号化装置 1 は、情報源から情報系列を入力し、実施の形態 1 による誤り訂正符号化方法による符号化を施して符号語系列を生成する。変調器 2 は、誤り訂正符号化装置 1 により生成された符号語系列を変調してデジタル信号を生成し、送信信号として通信路 3 に出力する。

【 0 0 1 1 】

復調器 4 は、上記変調器 2 からの送信信号を通信路 3 を介して受信してアナログ受信系列に復調する。A / D 変換器 5 は、復調器 4 により復調されたアナログ受信系列をデジタル変換して量子化受信系列を生成する。誤り訂正復号装置 6 は、量子化受信系列に対し、上記誤り訂正符号化方法に対応した誤り訂正復号処理を施して推定情報系列を生成し受信者側へ出力する。なお、通信路 3 は、有線、無線を問わない。

10

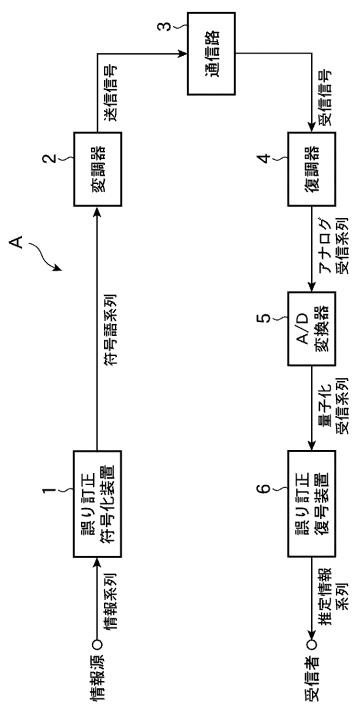

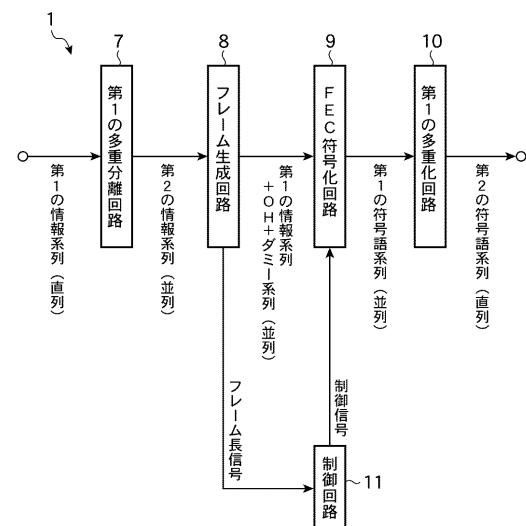

【 0 0 1 2 】

( 1 ) 誤り訂正符号化装置の構成

図 2 は、図 1 中の誤り訂正符号化装置の構成を概略的に示すブロック図である。図 2 において、誤り訂正符号化装置 1 は、第 1 の多重分離回路 7 、フレーム生成回路 8 、FEC 符号化回路 9 、第 1 の多重化回路 10 及び制御回路 11 を備える。情報源に接続する第 1 の多重分離回路 7 からフレーム生成回路 8 、FEC 符号化回路 9 、第 1 の多重化回路 10 の順で接続しており、第 1 の多重分離回路 7 から後段へ処理データが順次入力されて符号化処理が行われる。

20

【 0 0 1 3 】

第 1 の多重分離回路 7 は、情報源に接続する最上段に配置され、情報源から入力された第 1 の情報系列 ( 直列 ) に基づいて、第 2 の情報系列 ( 並列 ) を生成する。以降、説明の簡単のため、図 2 においては、第 1 の多重分離回路 7 が、情報源から直列の順序で入力された第 1 の情報系列 ( 直列 ) を、  $q$  並列の順序に多重分離を施して第 2 の情報系列 ( 並列 ) へ変換する。

20

【 0 0 1 4 】

フレーム生成回路 ( フレーム生成手段 ) 8 は、第 2 の情報系列に基づいて、サブフレームとなる、第 1 の情報系列 + OH ( オーバーヘッド ) + ダミー系列 ( 並列 ) を生成する。また、制御回路 11 の制御用のフレーム長信号を生成する。FEC 符号化回路 ( 符号化手段 ) 9 は、制御回路 11 からの制御信号に従って、第 1 の情報系列 + OH + ダミー系列に基づき、第 1 の符号語系列 ( 並列 ) を生成する。

30

【 0 0 1 5 】

第 1 の多重化回路 10 は、誤り訂正符号化装置 1 内の最下段側に配置され、第 1 の符号語系列に基づいて、第 2 の符号語系列 ( 直列 ) を生成する。制御回路 11 は、フレーム生成回路 8 から入力した制御用のフレーム長信号に基づいて、FEC 符号化回路 9 の動作を制御するための制御信号を生成する。

【 0 0 1 6 】

( 2 ) 誤り訂正符号化装置の動作

40

次に、誤り訂正符号化装置 1 の動作について説明する。

第 1 の多重分離回路 7 は、情報源から入力した第 1 の情報系列を多重分離して、第 2 の情報系列に変換する。この変換方法は、情報源から入力された情報系列の態様に応じて異なる。つまり、入力した情報系列の並列数 ( 直列若しくは所定の並列 ) 及び動作周波数等の違いによって異なる。なお、情報系列の態様は、入力側の処理と出力側の処理とで整合していればよい。また、情報系列の態様の違い自体は、この発明の特徴となるものではない。

【 0 0 1 7 】

以降、説明の簡単のため、第 1 の多重分離回路 7 は、情報源から直列の順序で入力した第 1 の情報系列 ( 直列 ) を、  $q$  並列の順序に多重分離を施して第 2 の情報系列 ( 並列 ) へ

50

変換する。また、第1の多重分離回路7の出力側における処理として、q並列信号、1クロック分のデータにあたるqビットを、1シンボルとして扱うものとする。

【0018】

フレーム生成回路8は、第1の多重分離回路7から入力したq並列の第1の情報系列に加え、同期用制御信号等を含むオーバーヘッド（以下、適宜OHと記載する）を付加する領域、及び誤り訂正符号のパリティ系列を付加する領域を確保し、そこにダミー系列を付加する。これら冗長領域を付加した分だけ伝送速度を上昇させ、FEC符号化回路9及び図3を用いて後述するFEC復号回路14の処理単位となるサブフレームを生成する。

【0019】

具体的に説明すると、フレーム生成回路8は、q並列の第1の情報系列を、予め定めたシンボル長（ここでは、kとする）毎に分割し、分割した各情報系列に対して所定のOH及び所定のシンボル長（ここでは、mとする）のダミー系列を付加する。これらを合わせてサブフレームとする。このようにして生成した複数個のサブフレームを連続してq並列で出力する。

【0020】

なお、サブフレーム生成の際に問題となるのは、第1の情報系列をkシンボル毎に分割して最後に余る情報ビットの長さがk'（k' < k）のサブフレームの処理である。この最後に余る短縮フレーム（Shortened frame）に対して、後述する符号化率の変動処理により、割り当てるべきパリティ長m'シンボルを定め、情報長k'でパリティ長m'のサブフレームを生成する。この短縮フレームの生成が、この発明に特有な処理である。

【0021】

また、フレーム生成回路8は、生成したサブフレームのフレーム長に関する制御信号を制御回路11に通知する。制御回路11は、FEC符号化回路9の動作を制御するための制御信号を出力する。なお、この実施の形態1では、フレーム長に関する制御信号を別に出力する形式にしているが、例えばOHにその信号を埋め込むことが可能であれば、この信号をあえて別に出力する必要はない。

【0022】

FEC符号化回路9では、フレーム生成回路8から入力したサブフレーム毎の情報系列に対して、RS（Reed-Solomon）符号等に代表される、ガロア体GF（ $2^q$ ）上の要素を1シンボルとする（つまり、qビットを1シンボルとして利用する）ブロック符号による符号化を行う。なお、この発明では、BCH符号等に代表される、ガロア体GF（2）上のビットを1シンボルとして（つまり、「0」及び「1」の2値を利用する）符号化する場合でも、その他のブロック符号により符号化する場合でも、効果がある。以降、説明の簡単のため、この発明の実施の形態として最も効果的である、RS符号による符号化を例に挙げて説明する。

【0023】

RS符号による符号化の場合、FEC符号化回路9は、フレーム生成回路8が生成したサブフレームの系列、及び制御回路11からの制御信号を利用して、情報長k、パリティ長mのブロック符号による符号化を実施し、符号長n = k + mの符号語系列を生成する。また、短縮フレームに対しては、情報長k'、パリティ長m'のブロック符号による符号化を実施し、符号長n' = k' + m'の符号語系列を生成する。FEC符号化回路9は、生成したサブフレーム毎の符号語系列をまとめて、q並列の第1の符号語系列として出力する。

【0024】

上述のように、この発明では、通常のサブフレームの他、短縮フレームのパリティ長を変動させるため、FEC符号化回路9には、通常のサブフレームに対するFEC符号化処理部と、短縮フレームに対するFEC符号化処理部と、の2種類のFEC符号化処理部の実装が必要となる。但し、ブロック符号としてRS符号を適用する場合、FEC符号化回路としてLFSR（Linear Feedback Shift Register）を実装し、レジスタの遅延段数及び生成多項式の係数を切り替える機能を追加することで、1種類のFEC符号化処理部の

10

20

30

40

50

実装で、通常のサブフレームと短縮フレームの双方に対応可能に構成することができる。

【0025】

第1の多重化回路10は、FEC符号化回路9で生成されたq並列の第1の符号語系列を、直列の第2の符号語系列に変換して、図1に示す変調器2に入力する。この変換方法は、変調器2への入力態様に応じて異なるが、この態様は第1の多重分離回路7と同様に入力側の処理と出力側の処理とで整合していればよい。また、その態様の違い自体は、本発明の特徴となるものではない。以降、説明の簡単のため、第1の多重化回路10が、q並列の順序で入力された第1の情報系列を、直列の順序に多重化処理を行うものとする。

【0026】

なお、誤り訂正符号化装置1の各回路7～10間で伝達される情報（データ）が、各回路7～10間を接続するバスを経由する構成にしてもよく、隣接する前後の回路から参照可能な作業用記憶領域を介して受け渡されるように構成してもよい。以降では、理解を容易にするために、バスを経由するパイプライン方式で受け渡されるものとして説明する。

【0027】

(3) 誤り訂正復号装置の構成

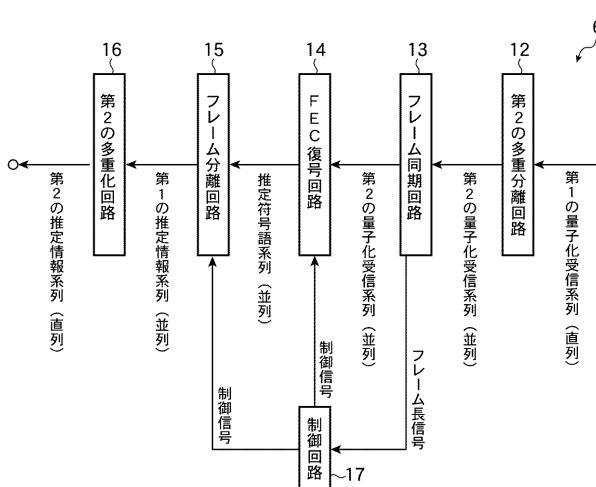

図3は、図1中の誤り訂正復号装置の構成を概略的に示すブロック図である。図3において、誤り訂正復号装置6は、誤り訂正符号化装置1が符号化した誤り訂正符号を復号する機能を有し、第2の多重分離回路12、フレーム同期回路13、FEC復号回路14、フレーム分離回路15、第2の多重化回路16、及び制御回路17を備える。図1中のA/D変換器5に接続する第2の多重分離回路12からフレーム同期回路13、FEC復号回路14、フレーム分離回路15、第2の多重化回路16の順で接続しており、第2の多重分離回路12から後段へ処理データが順次入力されて復号処理が行われる。

【0028】

第2の多重分離回路12は、図1中のA/D変換器5に接続する最上段に配置され、A/D変換器5から入力された第1の量子化受信系列（直列）に基づいて、第2の量子化受信系列（並列）を生成する。フレーム同期回路（フレーム同期手段）13は、第2の量子化受信系列に基づいて、第2の量子化受信系列（並列）を生成する。また、第2の量子化受信系列を構成する各サブフレームにフレーム同期するための制御用のフレーム同期信号を生成する。FEC復号回路（復号手段）14は、第2の量子化受信系列に基づいて、推定符号語系列（並列）を生成する。

【0029】

フレーム分離回路15は、推定符号語系列に基づいて、第1の推定情報系列（並列）を生成する。第2の多重化回路16は、誤り訂正復号装置6内の最下段側に配置され、第1の推定情報系列に基づいて、第2の推定情報系列（直列）を生成する。制御回路17は、制御用のフレーム同期信号に基づいて、FEC復号回路14及びフレーム分離回路15の動作を制御するための制御信号を生成する。

【0030】

なお、誤り訂正復号装置6（受信側）において、復調器4及びA/D変換器5は、通信路3を通じて雑音の混入した直列の順序の受信系列を、復調しA/D変換して量子化受信系列を生成する。

【0031】

また、受信信号の1シンボルあたりpビットに量子化することを想定し、p=1の場合を「硬判定」、p>1の場合を「軟判定」と称する。この発明では、軟判定の適用も可能であり、量子化pビットを誤り訂正復号装置6での1ビットと同様に扱って、FEC復号回路14で軟判定復号することはできる。ここでは、説明の簡単のため、硬判定を想定する。

【0032】

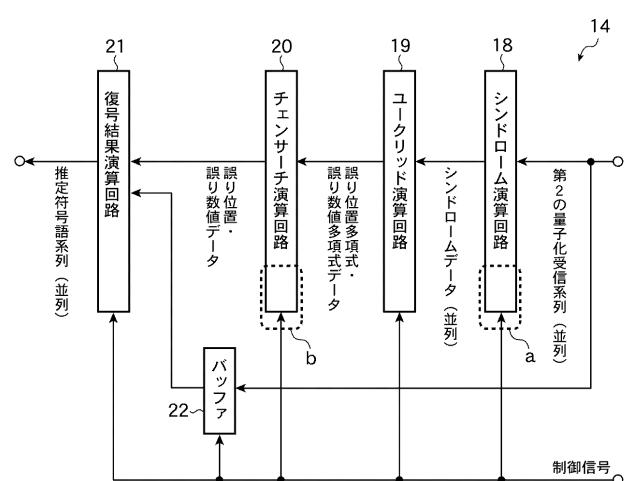

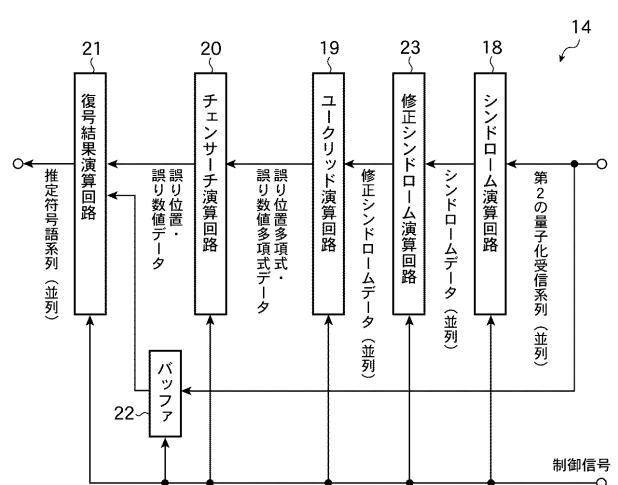

(4) FEC復号回路の構成

図4は、図3中のFEC復号回路の構成を概略的に示すブロック図であり、RS符号による符号化に対応した回路構成を示している。図4において、FEC復号回路14は、シ

10

20

30

40

50

ンドローム演算回路 18、ユークリッド演算回路 19、チェンサーチ演算回路 20、復号結果演算回路 21、及び遅延バッファ 22 を備える。

【0033】

ここで、RS 符号のパラメータとしては、様々なものを選択することが可能であるが、説明を簡単にするため、以下の定義に基づくものとする。

定義：1 の原始  $2^q - 1$  乗根 の連続する  $m$  個のベキ  $\gamma^i$ ,  $i = 0, \dots, m-1$  を根に持つガロア体  $GF(2^q)$  上の多項式を生成多項式とする符号 ( $m$  は偶数)。

【0034】

シンドローム演算回路 18 は、フレーム同期回路 13 から  $q$  並列で入力した第 2 の量子化受信系列に基づいて、 $q$  並列のシンドロームデータを生成する。ユークリッド演算回路 19 は、シンドロームデータを利用してユークリッド演算を実施し、誤り位置多項式データを出力する。

【0035】

チェンサーチ演算回路 20 は、上記誤り位置多項式データを用いてチェンサーチ演算を行い、誤り位置データを算出する。また、復号結果演算回路 21 は、誤り位置データ及び遅延バッファ 22 に保持されていた第 2 の量子化受信系列を用いて推定符号語系列を算出する。遅延バッファ 22 は、演算回路 18 ~ 20 による演算遅延を吸収すため、フレーム同期回路 13 からの第 2 の量子化受信系列を保持する。

【0036】

上述した一連の RS 復号処理において、シンドローム演算回路 18 は、第 2 の量子化受信系列を入力すると、下記式 (1) に基づいて、シンドロームデータ  $S_i$  ( $i = 1, 2, \dots, m$ ) を算出する。但し、 $\gamma$  はガロア体  $GF(2^q)$  の原始元、 $Y(x)$  は受信系列を多項式形式で表現した受信多項式である。なお、シンドローム演算回路 18 の実装としては、 $m$  個のシンドロームデータ  $S_i$  ( $i = 1, 2, \dots, m$ ) に対して、シフトレジスタを  $m$  並列に並べて演算するものとする。

$$S_i = Y(\gamma^i) \quad (i = 1, 2, \dots, m) \quad \dots \quad (1)$$

【0037】

ユークリッド演算回路 19 は、シンドローム演算回路 18 により算出されたシンドロームデータに対して、ユークリッドアルゴリズムに基づいて、下記式 (2) 及び (3) で定義される誤り位置多項式  $(z)$  及び誤り数値多項式  $(z)$  を算出する。但し、 $(z)$  は、誤り位置  $j^1, j^2, \dots, j^l$  に対して、 $\gamma^{-j^1}, \gamma^{-j^2}, \dots, \gamma^{-j^l}$  を根にもつ多項式である。また、 $e_i$ ,  $i = 1, 2, \dots, l$  は、誤り位置  $j^1, j^2, \dots, j^l$  に対する誤り数値である。誤り数 1 の最大値は、 $m/2$  であるため、 $(z)$  の最大次数は、 $m/2$  となり、 $(z)$  の最大次数は、 $(m/2) - 1$  となる。なお、ユークリッドアルゴリズムの詳細は、本願出願時に公知技術として開示されているものを用いてよく、その詳細な説明は省略する。

【数 1】

$$\sigma(z) = (1 - \alpha^{j_1} z)(1 - \alpha^{j_2} z) \dots (1 - \alpha^{j_l} z) \quad (2)$$

$$\omega(z) = \sum_{i=1}^l e_i \alpha^{j_i} \prod_{\substack{k=1 \\ k \neq i}}^l (1 - \alpha^{j_k} z) \quad (3)$$

【0038】

チェンサーチ演算回路 20 は、誤り位置多項式及び誤り数値多項式データを入力して、チェンサーチ演算に基づき、誤り位置  $j^1, j^2, \dots, j^l$  及び誤り数値  $e_i$  ( $i = 1, 2, \dots, l$ ) を算出する。チェンサーチ演算回路 20 の実装としては、 $(z)$  の最大次数分のシフトレジスタを  $m$  並列に並べて、 $(z)$  の根及び誤り数値を逐次的に演算するものとする。

【0039】

10

20

30

40

50

復号結果演算回路 21 は、チェンサーチ演算回路 20 から誤り位置・誤り数値データを入力し、遅延バッファ 22 から第 2 の量子化受信系列を入力して、推定符号語系列を算出する。

【0040】

図 4 で示した FEC 復号回路 14 では、通常のサブフレーム（情報長  $k$  シンボル及びパリティ長  $m$  シンボルの RS 符号による符号化データ）の復号処理機能のみを実装することで、短縮フレーム、すなわち情報長  $k' < k$  及びパリティ長  $m' < m$  の RS 符号による符号化データの復号処理機能を共存することができる。

【0041】

シンドローム演算回路 18 は、短縮フレームの処理において、 $m$  並列のシフトレジスタのうち、図 4 中に点線枠 a に示す  $m - m'$  個のシフトレジスタを停止して、入力タイミングを調整する。また、チェンサーチ演算回路 20 も同様に、短縮フレームの処理において、 $m$  並列のシフトレジスタのうち、図 4 中の点線枠 b に示す  $m - m'$  個のシフトレジスタを停止して、入力タイミングを調整する。なお、ユークリッド演算回路 19 は、 $(z)$  の最大次数  $m/2$  のものを実装しておけば、 $(z)$  の次数  $m'/2 < m/2$  のものを演算することができる。

【0042】

（5）誤り訂正復号装置の動作

次に、誤り訂正復号装置 6 の動作について説明する。

誤り訂正復号装置 6 に直列の順序で入力された第 1 の量子化受信系列は、第 2 の多重分離回路 12 により  $q$  並列の順序に変換され、第 2 の量子化受信系列が生成される。なお、第 2 の多重分離回路 12 で実施される多重分離処理は、第 1 の多重化回路 10 の逆変換に対応するものとなる。

【0043】

続いて、フレーム同期回路 13 は、 $q$  並列の第 2 の量子化受信系列に付加されている OH 情報（オーバーヘッド情報）を検出し各サブフレームの先頭位置を特定する。そして、フレーム同期信号を出力する。

【0044】

次に、FEC 復号回路 14 は、フレーム同期回路 13 から出力された系列に対し、サブフレーム毎に、FEC 符号化回路 9 で符号化されたブロック符号に対応する復号処理を行う。なお、この発明では、FEC 符号化回路 9 で符号化されたブロック符号に対応するものであれば、様々な種類のブロック符号に対する復号処理であっても、適用可能である。しかし、以下の説明を簡単にするため、この発明の実施の形態として最も効果的である、RS 符号により符号化されたデータの復号処理を説明する。また、前述のように硬判定復号の場合を説明する。

【0045】

FEC 復号回路 14 は、フレーム同期回路 13 から入力した第 2 の量子化受信系列を用い、制御回路 17 から入力した制御信号に従って、誤り訂正符号化装置 1 で符号化されたサブフレームに対応する、情報長  $k$  及びパリティ長  $m$  の量子化受信系列に対する復号処理を実施し、符号長  $n = k + m$  の推定符号語系列を生成する。また、短縮フレームに対して、情報長  $k'$ 、パリティ長  $m'$  の量子化受信系列に対する復号処理を実施し、符号長  $n' = k' + m'$  の推定符号語系列を生成する。FEC 復号回路 14 は、生成したサブフレーム毎の推定符号語系列をまとめて、 $q$  並列の第 1 の推定符号語系列として出力する。

【0046】

上述のように、この発明では、通常のサブフレームの他、短縮フレームのパリティ長を変動させるため、FEC 復号回路 14 には、通常のサブフレームに対する FEC 復号処理部と、短縮フレームに対する FEC 復号処理部と、の 2 種類の FEC 復号処理部の実装が必要となる。但し、ブロック符号として RS 符号を適用する場合、FEC 復号回路として 1 種類の FEC 復号処理部の実装で、通常のサブフレームと短縮フレームの双方に対応可能に構成することができる。

10

20

30

40

50

## 【0047】

フレーム分離回路15は、送信側のフレーム生成回路8に対応するものであり、推定符号語系列からOHに対応するビットを除去するとともに、送信側のフレーム生成回路8で実行した速度変換に基づいて、確保されたパリティ系列領域に対応するビットを分離及び除去し、q並列の系列の逆速度変換を行い、q並列の第1の推定情報系列を出力する。

## 【0048】

第2の多重化回路16では、フレーム分離回路15から入力したq並列の第1の推定情報系列を、直列の第2の推定情報系列に変換する。なお、第2の多重化回路16で実施される多重分離処理は、第1の多重分離回路7の逆変換に対応するものとなる。

## 【0049】

なお、誤り訂正復号装置6を構成する各回路12～16間で伝達される情報（データ）が、誤り訂正符号化装置1と同様に、各回路12～16間を接続するバスを経由するパイプライン方式で受け渡される構成にしてもよく、隣接する前後の回路から参照可能な作業用記憶領域を介して受け渡されるように構成してもよい。以降では、理解を容易にするために、バスを経由するパイプライン方式で受け渡されるものとして説明する。

10

## 【0050】

## (6) 符号化率を変動させた符号化処理

誤り訂正符号化装置1のFEC符号化回路9は、図5に示すように、通常のサブフレームの情報長をkシンボルとし、パリティ長をmシンボルと定めたとき、入力された情報系列の最後に対応する短縮フレームに対し、予め設定された条件でパリティ長m'を変動させる。また、短縮フレームの情報長k'は、入力された情報系列であるイーサネット（登録商標）フレームの長さ及び通常のサブフレームの情報長kに基づいて、一意に定まる。なお、FEC符号化回路9による、情報長k'に対するパリティ長m'は、下記の算出基準1,2に基づいて設定する。

20

## 【0051】

## (A) 算出基準1

算出基準1として、復号後ビット誤り率を基準として、これが均一になるような条件を定める。具体的には、下記式(4)に基づいて算出する。但し、通常のサブフレームの符号語 $c_{k,m}$ の復号後ビット誤り率をBER( $c_{k,m}, s$ )とし、短縮フレームの符号語 $c_{k',m'}$ の復号後ビット誤り率をBER( $c_{k',m'}, s$ )と定義する。また、sは、通信路3の信号対雑音比、関数BERは通信路モデルにより規定されるものである。

30

## 【数2】

$$m' = \arg \min_{m'} \{ \text{BER}(c_{k',m'}, s) \leq \text{BER}(c_{k,m}, s) \} \quad (4)$$

## 【0052】

算出基準1の原理について述べる。

RS符号の復号後ビット誤り率は、パリティ長固定で情報長を短くすると、同一信号対雑音比に対して向上することが知られている。逆に言うと、従来の短縮フレームは、通常の符号語に比べて訂正能力が向上する一方、符号化率が劣る。このため、短縮フレームについてのみ、通常の符号語と同程度の復号後ビット誤り率BERになるように、パリティ長さm'を短縮するように切り替える。これにより、従来より符号化率が向上する。

40

## 【0053】

## (B) 算出基準2

算出基準2として、各サブフレームの分割された入力情報系列の情報長を基準として、予め設定する閾値の条件を定める。具体的には下記式(5)に基づいて算出する。但し、 $k_1, k_2, \dots$ は予め設定する閾値であり、伝送条件等により適宜定めるものである。この算出基準2では、短縮フレームのパリティ長m'の算出基準を、短縮フレームの情報長k'のみで規定する。このように算出基準2では、短縮フレームの情報長の場合分けに

50

よってパリティ長  $m'$  を決定できるので、上記式(4)に基づく算出処理より演算を簡易化できる。

【数3】

$$m' = \begin{cases} m, & \text{if } k_1 < k' \leq k \\ m-2, & \text{if } k_2 < k' \leq k_1 \\ \vdots & \end{cases} \quad (5)$$

【0054】

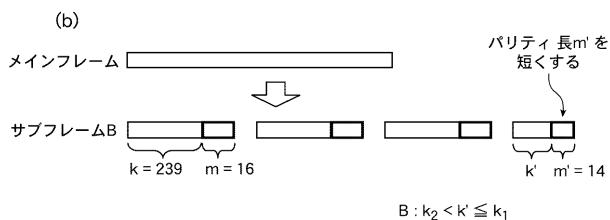

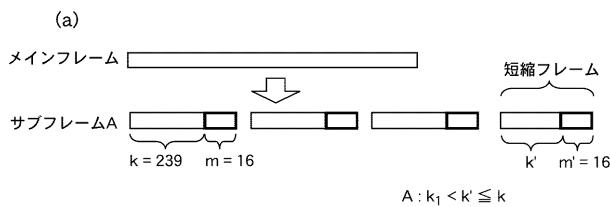

図5の例は、算出基準2に基づいて短縮フレームのパリティ長  $m'$  を変動させる場合を説明するための図である。なお、図5において、制御用のオーバーヘッド(OH)等は記載を省略している。図5(a)に示すサブフレームAは、短縮フレームの情報長  $k'$  が、通常のサブフレームの情報長  $k$  以下であり、かつ閾値  $k_1$  よりも長いため、短縮フレームのパリティ長を  $m' = m$  (16バイト) に設定し、通常のサブフレームと同一長とした場合を示している。

【0055】

一方、図5(b)に示すサブフレームBは、短縮フレームの情報長  $k'$  が閾値  $k_1$  以下であるため、短縮フレームのパリティ長を  $m' = m - 2$  (図5(b)では14バイト) に設定し、通常のサブフレームよりも短くしている。このように、短縮フレームの情報長に応じてパリティ長を変動させることで、通常の符号語と同程度の復号後ビット誤り率BERにことができる。

【0056】

以上のように、この実施の形態1によれば、入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するフレーム生成回路8と、フレーム生成回路8で生成されたサブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが所定の情報長に満たない短縮フレームに対し、当該短縮フレームの情報長に応じてパリティ長を変動させて誤り訂正符号化するFEC符号化回路9とを備える。このように、短縮フレームの情報長に応じてブロック符号のパリティ長を変動させることで、符号化率を向上させることができる。

【0057】

なお、この発明は、上記実施の形態1で示したパラメータに限定されるものではなく、誤り訂正符号化の方法、フレームフォーマットの長さ、入出力並列数、伝送速度などを、うまく当てはめられる組み合わせであれば、他の例として実現され得ることは言うまでもない。

【0058】

また、上記実施の形態1では、光伝送システムに適用する例を示したが、この発明は、これに限定されるものではない。例えば、加入者系有線通信、モバイル無線通信、衛星通信など、様々な種類の伝送システムに適用可能である。

【0059】

実施の形態2.

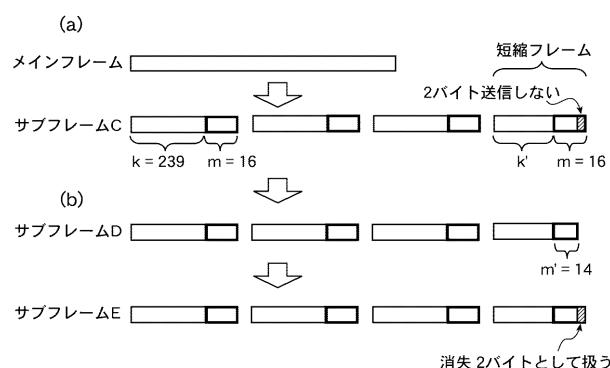

上記実施の形態1は、誤り訂正符号化装置1において、パリティ長  $m' < m$  の短縮フレームについて、情報長  $k'$  及びパリティ長  $m'$  のブロック符号として符号化する場合を示した。これに対し、この実施の形態2では、短縮フレームを情報長  $k'$  及びパリティ長  $m$  のブロック符号として符号化し、差分  $m - m'$  については送信せずに棄却する処理を説明する。

【0060】

この実施の形態2による誤り訂正符号化装置は、上記実施の形態1の図2と基本的な構成は同一であるが、FEC符号化回路9による符号化処理において、短縮フレームを情報長  $k'$  及びパリティ長  $m$  のブロック符号として符号化し、差分  $m - m'$  については送信せ

10

20

30

40

50

ずに棄却する点で異なる。そこで、実施の形態2においても、図2を用いて誤り訂正符号化装置を説明する。

【0061】

また、この実施の形態2による誤り訂正復号装置は、入力した量子化受信系列に含まれる長さ $m'$ のパリティに加えて、送信側で棄却された差分 $m - m'$ について、消失シンボルとみなし、情報長 $k'$ 及びパリティ長 $m$ （うち $m - m'$ は消失シンボル）のブロック符号として復号処理する。

【0062】

図6は、この発明の実施の形態2によるFEC復号回路の構成を概略的に示すブロック図である。図6において、修正シンドローム演算回路23は、シンドローム演算回路18で算出された送信側でパリティの一部が棄却されたシンドロームデータ及びその一部を消失シンボルとした場合のシンボル位置（消失位置）を入力し、上記消失シンボルに相当するパリティ長を考慮した修正シンドロームデータを算出する。なお、図6における他の構成要素は、図4に示したものと同様であるので説明を省略する。このように、フレーム同期回路13によりオーバヘッド(OH)に記載の情報から消失位置を把握し、それを制御信号によって伝達する。消失位置を予め定義していれば、数ビットの制御信号でそれを特定することができる。

10

【0063】

次に動作について説明する。

20

図7は、実施の形態2による訂正符号化を説明するための図であり、この図に沿って説明する。実施の形態2による誤り訂正符号化装置1のFEC符号化回路9は、図7(a)中のサブフレームCに示すように、短縮フレームを情報長 $k'$ 及びパリティ長 $m$ のブロック符号として符号化処理する。また、差分 $m - m'$ （図7(a)の例では、2バイト分）については送信せずに棄却する。これにより、実施の形態2による誤り訂正符号化装置1から通信路3へは、図7(b)中のサブフレームDに示すような系列（短縮フレームのパリティ長が $m' = 14$ バイト）が送信される。

20

【0064】

一方、受信側の誤り訂正復号装置6は、図7(b)中のサブフレームEに示すように、量子化受信系列に含まれる長さ $m'$ のパリティに加え、送信側で棄却された差分 $m - m'$ について消失シンボルとみなし、情報長 $k'$ 及びパリティ長 $m$ （うち $m - m'$ は消失シンボル）のブロック符号として復号処理する。

30

【0065】

具体的には、FEC復号回路14内の修正シンドローム演算回路23が、シンドローム演算回路18で算出された送信側でパリティの一部が棄却されたシンドロームデータ $S_i$ （ $i = 1, 2, \dots, m$ ）、及び、その一部を消失シンボルとした場合の消失位置 $j^{1'}, j^{2'}, \dots, j^{h'}$ を入力し、下記式(6)に示すような、上記消失シンボルに相当するパリティ長を付加した修正シンドロームデータ $S'_i$ （ $i = 1, 2, \dots, m$ ）を出力する。ここで、 $(z)$ は消失位置 $j^{1'}, j^{2'}, \dots, j^{h'}$ に対して、 $-j^{1'}, -j^{2'}, \dots, -j^{h'}$ を根にもつ下記式(7)に示す多項式である。

$$S'_i = Y(-j^{1'}) \cdot \dots \cdot (-j^{h'}) (i = 1, 2, \dots, m) \quad \dots \quad (6)$$

$$(z) = (1 - -j^{1'}z) (1 - -j^{2'}z) \dots (1 - -j^{h'}z) \dots \quad (7)$$

40

【0066】

ユークリッド演算回路19は、修正シンドローム演算回路23で算出された修正シンドロームデータを入力し、誤り位置多項式 $(z)$ と、修正誤り数値多項式 $(z)$ とを算出する。ここで、 $(z)$ は下記式(8)で定義される $(1 + h - 1)$ 次以下の多項式である。また、 $e'_{-i}$ ,  $i = 1, 2, \dots, h$ は、消失位置 $j^{1'}, j^{2'}, \dots, j^{h'}$ に対する誤り数値である。なお、消失を含むユークリッドアルゴリズムの詳細は、本願出願時に公知技術として開示されているものを用いてもよく、その詳細な説明は省略する。

## 【数4】

$$\psi(z) = \omega(z)\lambda(z) + \sigma(z) \sum_{i=1}^h e'_i \alpha^{j'_i} \prod_{\substack{k=1 \\ k \neq i}}^h (1 - \alpha^{j'_k} z) \quad (8)$$

## 【0067】

チェンサーチ演算回路20は、ユークリッド演算回路19で算出された誤り位置多項式<sup>10</sup> ( $z$ ) 及び修正誤り数値多項式 ( $z$ ) を入力して、誤り位置・誤り数値データとともに、消失数値データを算出する。復号結果演算回路21は、チェンサーチ演算回路20から誤り位置・誤り数値データを入力し、遅延バッファ22から第2の量子化受信系列を入力して、推定符号語系列を算出する。

## 【0068】

なお、この実施の形態2では、短縮フレームを通常のサブフレームと同様に扱うことから、上記実施の形態1の図4で示したような、短縮フレームに対する制御を切り替えて、シンドローム演算回路18が点線枠aに示す $m - m'$ 個のシフトレジスタを停止したり、チェンサーチ演算回路20が点線枠bに示す $m - m'$ 個のシフトレジスタを停止する処理を行う必要がない。

## 【0069】

以上のように、この実施の形態2によれば、誤り訂正符号化装置1のFEC符号化回路9が、短縮フレームの情報長に応じてパリティビットの一部を棄却して誤り訂正符号化し、誤り訂正復号装置6のFEC復号回路14が、誤り訂正符号化装置1で棄却されたパリティビットの一部を消失ビットとみなして復号する。このようにすることで、通常のサブフレームと短縮フレームとの制御切り替えを意識することなく、符号化率及び伝送効率を向上させることができる。

## 【図面の簡単な説明】

## 【0070】

【図1】この発明の実施の形態1による誤り訂正符号化装置を用いたデジタル伝送システムの構成を示すブロック図である。

【図2】図1中の誤り訂正符号化装置の構成を概略的に示すブロック図である。

【図3】図1中の誤り訂正復号装置の構成を概略的に示すブロック図である。

【図4】図3中のFEC復号回路の構成を概略的に示すブロック図である。

【図5】短縮フレームのパリティ長の変動処理を説明するための図である。

【図6】この発明の実施の形態2によるFEC復号回路の構成を概略的に示すブロック図である。

【図7】実施の形態2による訂正符号化を説明するための図である。

【図8】従来の訂正符号化を説明するための図である。

## 【符号の説明】

## 【0071】

1 誤り訂正符号化装置、2 変調器、3 通信路、4 復調器、5 アナログ／デジタル(A/D)変換器、6 誤り訂正復号装置、7 第1の多重分離回路、8 フレーム生成回路(フレーム生成手段)、9 FEC符号化回路(符号化手段)、10 第1の多重化回路、11, 17 制御回路、12 第2の多重分離回路、13 フレーム同期回路(フレーム同期手段)、14 FEC復号回路(復号手段)、15 フレーム分離回路、16 第2の多重化回路、18 シンドローム演算回路、19 ユークリッド演算回路、20 チェンサーチ演算回路、21 復号結果演算回路、22 遅延バッファ、23 修正シンドローム演算回路、A デジタル伝送システム。

【 図 1 】

【図2】

(図3)

〔 図 4 〕

【図5】

【図6】

【図7】

【図8】