(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4800007号

(P4800007)

(45) 発行日 平成23年10月26日(2011.10.26)

(24) 登録日 平成23年8月12日(2011.8.12)

(51) Int.Cl.

F 1

HO 1 L 21/66 (2006.01)

GO 1 R 1/073 (2006.01)

GO 1 R 31/26 (2006.01)HO 1 L 21/66

GO 1 R 1/073

GO 1 R 31/26B

E

J

請求項の数 16 (全 40 頁)

(21) 出願番号 特願2005-327183 (P2005-327183)

(22) 出願日 平成17年11月11日 (2005.11.11)

(65) 公開番号 特開2007-134554 (P2007-134554A)

(43) 公開日 平成19年5月31日 (2007.5.31)

審査請求日 平成20年10月21日 (2008.10.21)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 本山 康博

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 堀米 好巳

東京都新宿区西新宿六丁目5番1号 株式会社ルネサス東日本セミコンダクタ内

(72) 発明者 中村 清吾

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置の製造方法およびプローブカード

## (57) 【特許請求の範囲】

## 【請求項 1】

以下の工程を含む半導体集積回路装置の製造方法：

(a) 複数のチップ領域に区画され、前記複数のチップ領域の各々には半導体集積回路が形成され、主面上において前記半導体集積回路と電気的に接続する複数の第1電極が形成された半導体ウエハを用意する工程、

(b) 第1配線が形成された第1配線基板と、前記複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有する第1カードを用意する工程、

(c) 前記複数の接触端子の前記先端を前記複数の第1電極に接触させて前記半導体集積回路の電気的検査を行う工程、

ここで、前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成し、

前記複数層の配線層の各々において、前記複数の第2配線および前記複数の第3配線を含む複数の配線の配置密度が均一化されている。

## 【請求項 2】

請求項 1 記載の半導体集積回路装置の製造方法において、

前記複数の接触端子の各々の上部に相当する位置に前記第 2 配線もしくは前記第 3 配線が配置されている。

【請求項 3】

請求項 2 記載の半導体集積回路装置の製造方法において、

前記複数層の配線層の各々において、前記複数の第 2 配線および前記複数の第 3 配線を含む前記複数の配線の幅および間隔が揃えられている。

【請求項 4】

請求項 1 記載の半導体集積回路装置の製造方法において、

前記 (c) 工程は、前記半導体ウエハ内において並列して隣接する複数の前記チップ領域に対して一括して行う。 10

【請求項 5】

以下の工程を含む半導体集積回路装置の製造方法：

(a) 複数のチップ領域に区画され、前記複数のチップ領域の各々には半導体集積回路が形成され、主面上において前記半導体集積回路と電気的に接続する複数の第 1 電極が形成された半導体ウエハを用意する工程、

(b) 第 1 配線が形成された第 1 配線基板と、前記複数の第 1 電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第 2 配線および前記複数の接触端子とは電気的に接続しない複数の第 3 配線が形成され、前記複数の第 2 配線が前記複数の第 1 配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第 1 配線基板に保持された第 1 シートと、前記第 1 シートのうち前記複数の接触端子が形成された第 1 領域を裏面側より押圧する押圧機構とを有する第 1 カードを用意する工程、 20

(c) 前記複数の接触端子の前記先端を前記複数の第 1 電極に接触させて前記半導体集積回路の電気的検査を行う工程、

ここで、前記複数の第 2 配線および前記複数の第 3 配線は、前記第 1 シート中に複数層の配線層から形成し、

前記第 1 シート中において、前記複数の接触端子の各々の上部に相当する位置には、前記複数層の配線層のうちの最下層の第 1 配線層に含まれる前記第 2 配線のみが配置され、

前記複数の接触端子の各々の上部に相当する位置以外の領域では、前記複数層の配線層の各々において、前記複数の第 2 配線および前記複数の第 3 配線を含む複数の配線の配置密度が均一化されている。 30

【請求項 6】

請求項 5 記載の半導体集積回路装置の製造方法において、

前記複数の接触端子の各々の上部に相当する位置の周囲では、前記第 1 配線層に配置される前記第 2 配線と、前記第 1 配線層の上層の第 2 配線層に形成される前記第 2 配線もしくは前記第 3 配線が、重なるように配置されている。

【請求項 7】

請求項 6 記載の半導体集積回路装置の製造方法において、

前記複数層の配線層の各々において、前記複数の第 2 配線および前記複数の第 3 配線を含む前記複数の配線の幅および間隔が揃えられている。 40

【請求項 8】

請求項 5 記載の半導体集積回路装置の製造方法において、

前記 (c) 工程は、前記半導体ウエハ内において互いに対角的に隣接する複数の前記チップ領域に対して一括して行う。

【請求項 9】

第 1 配線が形成された第 1 配線基板と、

半導体ウエハの主面に形成された複数の第 1 電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第 2 配線および前記複数の接触端子とは電気的に接続しない複数の第 3 配線が形成され、前記複数の第 2 配線が前記複数の第 1 配線 50

と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、

前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有し、

前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成され、

前記複数層の配線層の各々において、前記複数の第2配線および前記複数の第3配線を含む複数の配線の配置密度が均一化されたプローブカード。

【請求項10】

請求項9記載のプローブカードにおいて、

10

前記複数の接触端子の各々の上部に相当する位置に前記第2配線もしくは前記第3配線が配置されている。

【請求項11】

請求項10記載のプローブカードにおいて、

前記複数層の配線層の各々では、前記複数の第2配線および前記複数の第3配線を含む前記複数の配線の幅および間隔が揃えられている。

【請求項12】

請求項9記載のプローブカードにおいて、

前記複数の接触端子が1度に接触する前記複数の第1電極は、前記半導体ウエハ内にて選択された複数のチップ領域内に形成され、

20

前記2つのチップ領域は、並列して隣接している。

【請求項13】

第1配線が形成された第1配線基板と、

半導体ウエハの主面に形成された複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、

前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有し、

30

前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成され、

前記第1シート中において、前記複数の接触端子の各々の上部に相当する位置には、前記複数層の配線層のうちの最下層の第1配線層に含まれる前記第2配線のみが配置され、

前記複数の接触端子の各々の上部に相当する位置以外の領域では、前記複数層の配線層の各々において、前記複数の第2配線および前記複数の第3配線を含む複数の配線の配置密度が均一化されたプローブカード。

【請求項14】

請求項13記載のプローブカードにおいて、

前記複数の接触端子の各々の上部に相当する位置の周囲では、前記第1配線層に配置される前記第2配線と、前記第1配線層の上層の第2配線層に形成される前記第2配線もしくは前記第3配線が、重なるように配置されている。

40

【請求項15】

請求項14記載のプローブカードにおいて、

前記複数層の配線層の各々では、前記複数の第2配線および前記複数の第3配線を含む前記複数の配線の幅および間隔が揃えられている。

【請求項16】

請求項13記載のプローブカードにおいて、

前記複数の接触端子が1度に接触する前記複数の第1電極は、前記半導体ウエハ内にて選択された複数のチップ領域内に形成され、

50

前記複数のチップ領域は、互いに対角的に隣接している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置の製造技術およびプローブカードに関し、特に、半導体集積回路装置の電極パッドにプローブカードの探針を押し当てて行う半導体集積回路の電気的検査に適用して有効な技術に関するものである。

【背景技術】

10

【0002】

日本特開平7-283280号公報（特許文献1）、日本特開平8-50146号公報（特許文献2（対応PCT国際公開WO95-34000））、日本特開平8-201427号公報（特許文献3）、日本特開平10-308423号公報（特許文献4）、日本特開平11-23615号公報（特許文献5（対応米国特許公報USP6,305,230））、日本特開平11-97471号公報（特許文献6（対応欧州特許公報EP1022775））、日本特開2000-150594号公報（特許文献7（対応欧州特許公報EP0999451））、日本特開2001-159643号公報（特許文献8）、日本特開2004-144742号公報（特許文献9）、日本特開2004-132699号公報（特許文献10）、日本特開2004-288672号公報（特許文献11）、日本特開2005-24377号公報（特許文献12）、日本特開2005-136302号公報（特許文献13）、および日本特開2005-136246号公報（特許文献14）には、半導体集積回路装置の製造技術を用いて形成された探針（接触端子）、絶縁フィルムおよび引き出し用配線を有するプローバの構造と、その製造方法と、テストパッドが狭ピッチ化したチップに対してもそのプローバを用いることによってプローブ検査の実施を可能とする技術とが開示されている。

20

【特許文献1】特開平7-283280号公報

【特許文献2】特開平8-50146号公報

【特許文献3】特開平8-201427号公報

【特許文献4】特開平10-308423号公報

30

【特許文献5】特開平11-23615号公報

【特許文献6】特開平11-97471号公報

【特許文献7】特開2000-150594号公報

【特許文献8】特開2001-159643号公報

【特許文献9】特開2004-144742号公報

【特許文献10】特開2004-132699号公報

【特許文献11】特開2004-288672号公報

【特許文献12】特開2005-24377号公報

【特許文献13】特開2005-136302号公報

【特許文献14】特開2005-136246号公報

40

【発明の開示】

【発明が解決しようとする課題】

【0003】

半導体集積回路装置の検査技術としてプローブ検査がある。このプローブ検査は、所定の機能どおりに動作するか否かを確認する機能テストや、DC動作特性およびAC動作特性のテストを行って良品／不良品を判別するテスト等を含む。プローブ検査においては、ウエハ出荷対応（品質の差別化）、KGD（Known Good Die）対応（MCP（Multi-Chip Package）の歩留り向上）、およびトータルコスト低減などの要求から、ウエハ状態でプローブ検査を行う技術が用いられている。

【0004】

50

近年、半導体集積回路装置の多機能化が進行し、1個の半導体チップ（以下、単にチップと記す）に複数の回路を作りこむことが進められている。また、半導体集積回路装置の製造コストを低減するために、半導体素子および配線を微細化して、半導体チップ（以下、単にチップと記す）の面積を小さくし、半導体ウエハ（以下、単にウエハと記す）1枚当たりの取得チップ数を増加することが進められている。そのため、テストパッド（ボンディングパッド）数が増加するだけでなく、テストパッドの配置が狭ピッチ化し、テストパッドの面積も縮小されてきている。このようなテストパッドの狭ピッチ化に伴って、上記プローブ検査にカンチレバー状の探針を有するプローバを用いようとした場合には、探針をテストパッドの配置位置に合わせて設置することが困難になってしまい課題が存在する。

10

#### 【0005】

また、半導体集積回路装置の一種であるメモリ製品の大容量化や、同じく半導体集積回路装置の一種であるメモリ内蔵ロジック製品の増加に伴い、ウエハ状態でのプローブ検査に要する時間が増大している。そのため、ウエハ状態でのプローブ検査のスループットを向上させることが求められている。このスループットを向上させるためには、ウエハ1枚当たりの検査に要する時間を短縮することが求められる。ウエハ1枚当たりの検査に要する時間T0は、たとえば、検査装置の1回の検査に要する時間をT1、プローバのインデックスに要する時間をT2、プローバが有する探針（プローブ針）とウエハとを接触させる回数（以下、タッチダウン回数と記す）をN、およびウエハの交換に要する時間をT3とすると、 $T_0 = (T_1 + T_2) \times N + T_3$ と表される。この式より、ウエハ状態でのプローブ検査のスループットを向上させるためには、タッチダウン回数を少なくすることが課題となる。なお、高温では熱ベント終息時間分待ち時間が増える。

20

#### 【0006】

本発明者らは、半導体集積回路装置の製造技術を用いて形成された探針を有するプローバを用いることにより、テストパッドが狭ピッチ化したチップに対してもプローブ検査が実現できる技術について検討しており、特に、複数のチップに対して一括してプローブ検査を実施できるプローバについて検討している。その中で、本発明者らは、以下のようないくつかの課題を見出した。

#### 【0007】

すなわち、上記探針は、半導体集積回路装置の製造技術を用いて金属膜およびポリイミド膜の堆積や、それらのパターニング等を実施することにより形成された薄膜プローブの一部であり、検査対象であるチップと対向する薄膜プローブの正面側に設けられている。プローブ検査時には、たとえば42アロイなどからなり押圧面が平坦な押圧具によって、探針が形成された領域の薄膜プローブを前記正面とは反対側の裏面から押圧する。この時、すべての探針の先端の高さおよび対応するテストパッドの高さに差が生じていると、接触できない探針と対応するテストパッドとが生じてしまう不具合が懸念される。そのため、プローブ検査時には、すべての探針と対応するテストパッドとを確実に接触させることが課題となっている。

30

#### 【0008】

また、複数のチップに対して一括してプローブ検査を実施可能な薄膜プローブを形成するには、探針と電気的に接続する配線を薄膜プローブ中に多数引き回すことになる。そのため、薄膜プローブ中で配線密度がばらつき、薄膜プローブの平坦性が低下してしまうことが懸念される。薄膜プローブの平坦性が低下すると、プローブ検査時に押圧具が薄膜プローブを押圧した際に探針の先端の高さにばらつきが生じ、先端の高さが低くなった探針はテストパッドと接触できなくなってしまう課題が生じる。

40

#### 【0009】

本願に開示された一つの代表的な発明の一つの目的は、半導体集積回路装置の製造技術によって形成された探針を有するプローバを用い、複数のチップに対して一括してプローブ検査を実施する際に、探針とテストパッドとを確実に接触させることができる技術を提供することにある。

50

## 【課題を解決するための手段】

## 【0010】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

## 【0011】

1. 本発明による半導体集積回路装置の製造方法は、以下の工程を含む：

(a) 複数のチップ領域に区画され、前記複数のチップ領域の各々には半導体集積回路が形成され、主面上において前記半導体集積回路と電気的に接続する複数の第1電極が形成された半導体ウエハを用意する工程、

(b) 第1配線が形成された第1配線基板と、前記複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有する第1カードを用意する工程、

(c) 前記複数の接触端子の前記先端を前記複数の第1電極に接触させて前記半導体集積回路の電気的検査を行う工程。

## 【0012】

ここで、前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成し、

前記複数層の配線層の各々において、前記複数の接触端子の各々の上部に相当する位置に前記第2配線もしくは前記第3配線を配置する。

## 【0013】

2. また、本発明による半導体集積回路装置の製造方法は、以下の工程を含む：

(a) 複数のチップ領域に区画され、前記複数のチップ領域の各々には半導体集積回路が形成され、主面上において前記半導体集積回路と電気的に接続する複数の第1電極が形成された半導体ウエハを用意する工程、

(b) 第1配線が形成された第1配線基板と、前記複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有する第1カードを用意する工程、

(c) 前記複数の接触端子の前記先端を前記複数の第1電極に接触させて前記半導体集積回路の電気的検査を行う工程。

## 【0014】

ここで、前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成し、

前記第1シート中にて前記複数の接触端子の各々の上部に相当する位置には、前記複数層の配線層のうちの最下層の第1配線層に含まれる前記第2配線のみを配置する。

## 【0015】

3. また、本発明による半導体集積回路装置の製造方法は、以下の工程を含む：

(a) 複数のチップ領域に区画され、前記複数のチップ領域の各々には半導体集積回路が形成され、主面上において前記半導体集積回路と電気的に接続する複数の第1電極が形成された半導体ウエハを用意する工程、

(b) 第1配線が形成された第1配線基板と、前記複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記

10

20

30

40

50

複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有する第1カードを用意する工程、

(c) 前記複数の接触端子の前記先端を前記複数の第1電極に接触させて前記半導体集積回路の電気的検査を行う工程。

【0016】

ここで、前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて1層の配線層から形成し、

前記(c)工程は、前記半導体ウエハ内において互いに1つ以上の前記チップ領域分を離間して並列する2つ以上の前記チップ領域に対して一括して行う。 10

【0017】

4. また、本発明によるプローブカードは、

第1配線が形成された第1配線基板と、

半導体ウエハの主面に形成された複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、

前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有し、 20

前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成され、

前記複数層の配線層の各々において、前記複数の接触端子の各々の上部に相当する位置に前記第2配線もしくは前記第3配線が配置されている。

【0018】

5. また、本発明によるプローブカードは、

第1配線が形成された第1配線基板と、

半導体ウエハの主面に形成された複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、 30

前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有し、

前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて複数層の配線層から形成され、

前記第1シート中において、前記複数の接触端子の各々の上部に相当する位置には、前記複数層の配線層のうちの最下層の第1配線層に含まれる前記第2配線のみが配置されている。 40

【0019】

6. また、本発明によるプローブカードは、

第1配線が形成された第1配線基板と、

半導体ウエハの主面に形成された複数の第1電極に接触させるための複数の接触端子、前記複数の接触端子と電気的に接続する複数の第2配線および前記複数の接触端子とは電気的に接続しない複数の第3配線が形成され、前記複数の第2配線が前記複数の第1配線と電気的に接続し前記複数の接触端子の先端が前記半導体ウエハの前記主面に対向して前記第1配線基板に保持された第1シートと、

前記第1シートのうち前記複数の接触端子が形成された第1領域を裏面側より押圧する押圧機構とを有し、 50

前記複数の第2配線および前記複数の第3配線は、前記第1シート中にて1層の配線層から形成され、

前記複数の接触端子が1度に接触する前記複数の第1電極は、前記半導体ウエハ内にて選択され互いに1つ以上のチップ領域分を離間して並列する複数の前記チップ領域内に形成されている。

【発明の効果】

【0020】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

(1)シリコンウエハを半導体集積回路の製造に用いるのと同様なパターニング手法によって、配線層およびそれに電気的に接続された先端部を一体的に形成した複数の接触端子またはプローブを有し、複数の配線層を有する薄膜プローブにおいて、上下の配線層にて平面で配線が重なるように各配線の平面パターンを形成するので、各々の接触端子またはプローブの上部において薄膜プローブの厚さを均一にすることができる。それにより、各々の接触端子またはプローブと検査対象の複数のチップに設けられたテストパッドとを確実に接触させることができる。

(2)シリコンウエハを半導体集積回路の製造に用いるのと同様なパターニング手法によって配線層およびそれに電気的に接続された先端部を一体的に形成した複数の接触端子またはプローブを有し複数の配線層を有する薄膜プローブにおいて、各配線層にて配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成するので、各々の接触端子またはプローブの上部において薄膜プローブの厚さおよび剛性を均一にすることができる。それにより、各々の接触端子またはプローブの近傍では薄膜プローブに皺および撓みが発生することを防ぐことができるので、各々の接触端子またはプローブと検査対象の複数のチップに設けられたテストパッドとのコンタクト性を向上することができる。

【発明を実施するための最良の形態】

【0021】

本願発明を詳細に説明する前に、本願における用語の意味を説明すると次の通りである。

【0022】

ウエハとは、集積回路の製造に用いる単結晶シリコン基板（一般にほぼ平面円形状）、S O I (Silicon On Insulator) 基板、エピタキシャル基板、サファイア基板、ガラス基板、その他の絶縁、反絶縁または半導体基板等並びにそれらの複合的基板をいう。また、本願において半導体集積回路装置というときは、シリコンウエハやサファイア基板等の半導体または絶縁体基板上に作られるものだけでなく、特に、そうでない旨明示された場合を除き、T F T (Thin Film Transistor) およびS T N (Super-Twisted-Nematic) 液晶等のようなガラス等の他の絶縁基板上に作られるもの等も含むものとする。

【0023】

デバイス面とは、ウエハの主面であって、その面にリソグラフィにより、複数のチップ領域に対応するデバイスパターンが形成される面をいう。

【0024】

接触端子またはプローブとは、シリコンウエハを半導体集積回路の製造に用いるのと同様な、ウエハプロセス、すなわちフォトリソグラフィ技術、C V D (Chemical Vapor Deposition) 技術、スパッタリング技術およびエッチング技術などを組み合わせたパターニング手法によって、配線層およびそれに電気的に接続された先端部を一体的に形成したものとす。

【0025】

接触端子またはプローブとは、各チップ領域上に設けられた電極パッドに接触させて電気的特性の検査を行うための針、プローブ、突起等をいう。

【0026】

薄膜プローブ (membrane probe) 、薄膜プローブカード、または突起針配線シート複合

10

20

30

40

50

体とは、上記のような検査対象と接触する前記接触端子（突起針）とそこから引き回された配線とが設けられ、その配線に外部接触用の電極が形成された薄膜をいい、たとえば厚さ 10 μm ~ 100 μm 程度のものをいい、シリコンウエハを半導体集積回路の製造に用いるのと同様な、ウエハプロセス、すなわちフォトリソグラフィ技術、CVD (Chemical Vapor Deposition) 技術、スパッタリング技術およびエッチング技術などを組み合わせたパターニング手法によって、配線層およびそれに電気的に接続された先端部（接触端子）を一体的に形成されたもの等を言う。もちろん、プロセスは複雑になるが、一部を別に形成して、後に合体させることも可能である。

#### 【 0 0 2 7 】

プロープカードとは、検査対象となるウエハと接触する接触端子および多層配線基板などを有する構造体をいい、プローバもしくは半導体検査装置とは、フロッギング、プロープカードおよび検査対象となるウエハを載せるウエハステージを含む試料支持系を有する検査装置をいう。

#### 【 0 0 2 8 】

プロープ検査とは、ウエハ工程が完了したウエハに対してプローバを用いて行われる電気的試験であって、チップ領域の主面上に形成された電極に上記接触端子の先端を当てて半導体集積回路の電気的検査を行うことをいい、所定の機能通りに動作するか否かを確認する機能テストや DC 動作特性および AC 動作特性のテストを行って良品 / 不良品を判別するものである。各チップに分割してから（またはパッケージング完了後）行われる選別テスト（最終テスト）とは区別される。

#### 【 0 0 2 9 】

ポゴピン (POGO pin) またはスプリングプロープとは、接触ピン（プランジャ（接触針））をばね（コイルスプリング）の弾性力で電極（端子）に押し当てる構造を有し、必要に応じてその電極への電気的接続を行うようにした接触針をいい、たとえば金属製の管（保持部材）内に配置されたばねが金属ボールを介して接触ピンへ弾性力を伝える構成となっている。

#### 【 0 0 3 0 】

テスタ (Test System) とは、半導体集積回路を電気的に検査するものであり、所定の電圧および基準となるタイミング等の信号を発生するものをいう。

#### 【 0 0 3 1 】

テスタヘッドとは、テスタと電気的に接続し、テスタより送信された電圧および信号を受け、電圧および詳細なタイミング等の信号を半導体集積回路に対して発生し、ポゴピンなどを介してプロープカードへ信号を送るものをいう。

#### 【 0 0 3 2 】

フロッギングとは、ポゴピンなどを介してテスタヘッドおよびプロープカードと電気的に接続し、テスタヘッドより送られてきた信号を後述するプロープカードへ送るものを行う。

#### 【 0 0 3 3 】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

#### 【 0 0 3 4 】

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

#### 【 0 0 3 5 】

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

#### 【 0 0 3 6 】

10

20

30

40

50

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0037】

また、材料等について言及するときは、特にそうでない旨明記したとき、または、原理的または状況的にそうでないときを除き、特定した材料は主要な材料であって、副次的要素、添加物、付加要素等を排除するものではない。たとえば、シリコン部材は特に明示した場合等を除き、純粋なシリコンの場合だけでなく、添加不純物、シリコンを主要な要素とする2元、3元等の合金（たとえばSiGe）等を含むものとする。

10

【0038】

また、本実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。

【0039】

また、本実施の形態を説明するための全図においては、各部材の構成をわかりやすくするために、平面図であってもハッチングを付す場合がある。

【0040】

また、本願で使用する半導体リソグラフィ技術による薄膜プローブの各詳細については、本発明者および関連する発明者等による以下の特許出願に開示されているので、特に必要な時以外はそれらの内容は繰り返さない。前記特許出願、すなわち、日本特願平6-22885号、日本特開平7-283280号公報、日本特開平8-50146号公報、日本特開平8-201427号公報、日本特願平9-119107号、日本特開平11-23615号公報、日本特開2002-139554号公報、日本特開平10-308423号公報、日本特願平9-189660号、日本特開平11-97471号公報、日本特開2000-150594号公報、日本特開2001-159643号公報、日本特許出願第2002-289377号（対応米国出願番号第10/676,609号；米国出願日2003.10.2）、日本特開2004-132699号公報、日本特開2005-24377号公報、日本特開2004-288672号公報（対応米国出願番号第10/765,917号；米国出願日2004.1.29）、日本特開2004-144742号公報（対応米国公開番号第2004/070,413号）、日本特開2004-157127号公報、日本特開2005-136246号公報（対応米国出願番号第10/968,215号；米国出願日2004.10.20）、日本特開2005-136302号公報（対応米国出願番号第10/968,431号；米国出願日2004.10.20）、日本特許出願第2004-208213号、PCT出願番号PCT/JP2004/17160号、PCT出願番号PCT/JP2005/4344号、日本特許出願第2004-378504号、日本特許出願第2005-109350号、日本特許出願第2005-168112号、日本特許出願第2005-181085号、日本特許出願第2005-194561号、日本特許出願第2005-291886号、および日本特許出願第2005-315115号である。

20

30

40

【0041】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0042】

（実施の形態1）

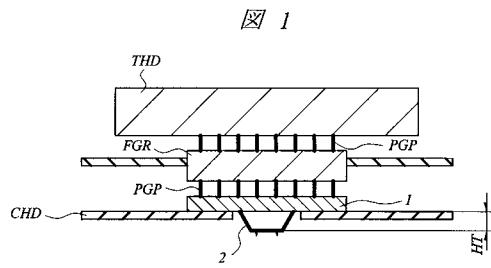

図1は、本実施の形態1のプローブカード（第1カード）の要部断面図である。図1に示すように、本実施の形態1のプローブカードは、多層配線基板（第1配線基板）1、薄膜シート（第1シート）2、テスタヘッドTHD、フロッギングFGRおよびカードホールダCHDなどから形成されている。テスタヘッドTHDとフロッギングFGRとの間、およびフロッギングFGRと多層配線基板1との間は、それぞれ複数本のポゴピンP

50

G Pを介して電気的に接続され、それによりテスタヘッドT H Dと多層配線基板1との間が電気的に接続されている。カードホルダC H Dは、多層配線基板1をプローバに機械的に接続するもので、かつポゴピンP G Pからの圧力によって多層配線基板1に反りが生じてしまうことを防ぐ機械的強度を持つ。

【0043】

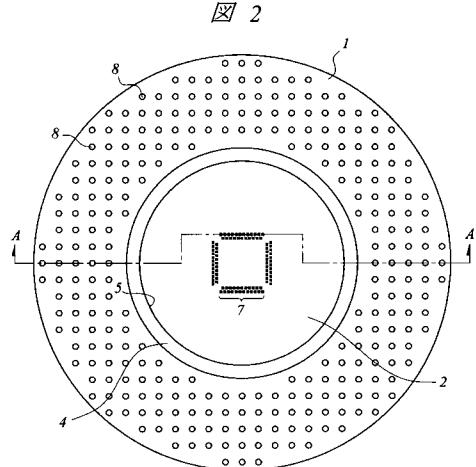

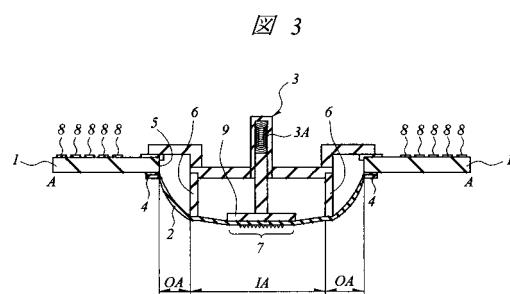

図2は、本実施の形態1のプローブカードの下面の要部平面図であり、図3は図2中のA-A線に沿った断面図である。

【0044】

図2および図3に示すように、本実施の形態のプローブカードは、図1で示した部材の他に、たとえばプランジャ3などを含んでいる。薄膜シート2は押さえリング4によって多層配線基板1の下面に固定され、プランジャ3は多層配線基板1の上面に取り付けられている。多層配線基板1の中央部には開口部5が設けられ、この開口部5内において、薄膜シート2とプランジャ3とは接着リング6を介して接着されている。

10

【0045】

薄膜シート2の下面には、たとえば4角錐型または4角錐台形型の複数のプローブ(接触端子)7が形成されている。薄膜シート2内には、プローブ7の各々と電気的に接続し、各々のプローブ7から薄膜シート2の探部まで延在する複数の配線(第2配線)が形成されている。多層配線基板1の下面または上面には、この複数の配線の端部とそれぞれ電気的に接觸する複数の受け部(図示は省略)が形成されており、この複数の受け部は、多層配線基板1内に形成された配線(第1配線)を通じて多層配線基板1の上面に設けられた複数のポゴ(POGO)座8と電気的に接続している。このポゴ座8は、テスタからの信号をプローブカードへ導入するピンを受ける機能を有する。

20

【0046】

本実施の形態1において、薄膜シート2は、たとえばポリイミドを主成分とする薄膜から形成されている。このような薄膜シート2は柔軟性を有することから、本実施の形態1では、チップ(半導体集積回路装置)のパッドにすべてのプローブ7を接觸させるために、プローブ7が形成された領域(第1領域)の薄膜シート2を上面(裏面)から押圧具(押圧機構)9を介してプランジャ3が押圧する構造となっている。すなわち、プランジャ3内に配置されたばね3 Aの弾性力によって一定の圧力を押圧具9に加えるものである。本実施の形態において、押圧具9の材質としては、42アロイを例示することができる。

30

【0047】

ここで、検査対象のチップ表面に形成されたテストパッド(ボンディングパッド)数が増加すると、それに伴って各テストパッドのそれぞれに信号を送るためのポゴピンP G Pの本数が増加することになる。また、ポゴピンP G Pの本数が増加することによって、多層配線基板1に加わるポゴピンP G Pからの圧力も増加することになるので、多層配線基板1の反りを防ぐためにカードホルダC H Dを厚くする必要が生じる。さらに、薄膜シート2に形成された各プローブ7を対応するテストパッドに確実に接觸させるために、薄膜シート2の中心領域IA(図3参照)および接着リングを境に外周側となり中心領域IAを取り囲む外周領域OA(図3参照)のそれぞれに張力を加える構造とした場合には、多層配線基板1の表面から薄膜シート2のプローブ面までの高さHT(図1参照)に限界が生じる。その高さHTの限界値よりカードホルダC H Dの厚さのほうが大きくなつた場合には、薄膜シート2がカードホルダC H D内に埋もれてしまうことになり、プローブ7をテストパッドに確実に接觸させることができなくなる不具合が懸念される。

40

【0048】

そこで、本実施の形態1では、上記薄膜シート2の中心領域IAのみに張力を加えた状態で薄膜シート2と接着リング6とを接着し、外周領域OAには張力を加えない構造とする。この時、接着リング6の材質としては、Si(シリコン)と同程度の熱膨張率の金属(たとえば、42アロイ)を選択し、薄膜シート2と接着リング6とを接着する接着剤としては、エポキシ系接着剤を用いることを例示できる。それにより、上記薄膜シート2のプローブ面までの高さHTを規定する接着リング6の高さを高くすることができるので、

50

その高さHTも高くなり、薄膜シート2がカードホルダCHD内に埋もれてしまう不具合を避けることができる。すなわち、カードホルダCHDが厚くなつた場合でも、プローブ7をテストパッドに確実に接触させることが可能となる。

#### 【0049】

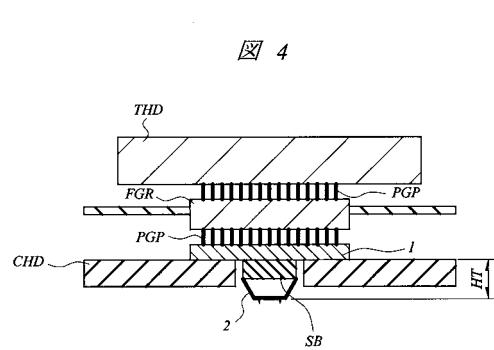

上記のような手段を用いる代わりに、図4に示すように、多層配線基板1の中央部に補助基板SBを取り付け、その補助基板SBに薄膜シート2を取り付ける構造として、多層配線基板1の表面から薄膜シート2のプローブ面までの高さHTを向上させてもよい。多層配線基板1と同様に、補助基板SB内には複数の配線が形成され、さらにこれら配線の端部とそれぞれ電気的に接觸する複数の受け部(図示は省略)が形成されている。多層配線基板1に設けられた受け部と補助基板SBに設けられた受け部とは、たとえばそれぞれ対応するもの同士がはんだによって電気的に接続されている。はんだを用いる代わりに、異方性導電ゴムを介して多層配線基板1と補助基板SBとを圧着する手段、もしくは多層配線基板1および補助基板SBのそれぞれの表面に上記受け部と電気的に接続するCu(銅)めっき製の突起部を形成し、対応する突起部同士を圧着する手段を用いてもよい。

10

#### 【0050】

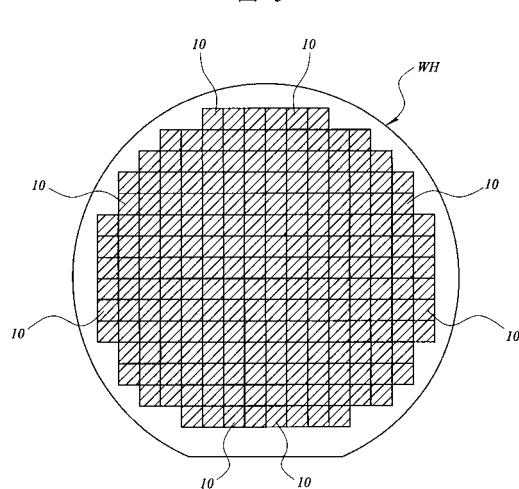

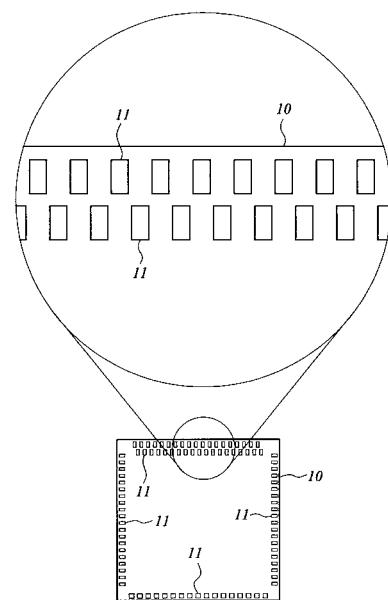

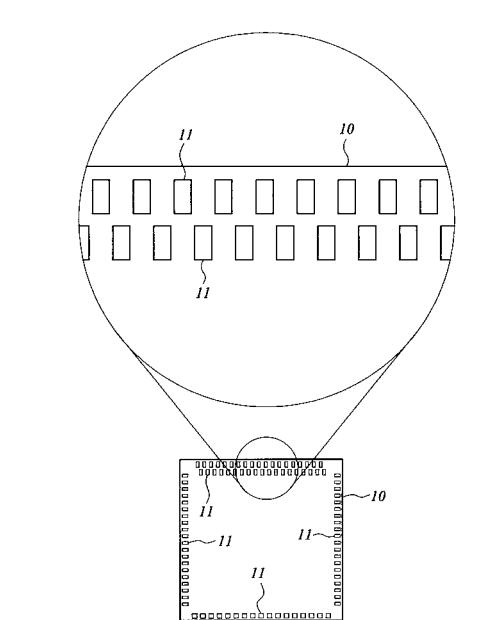

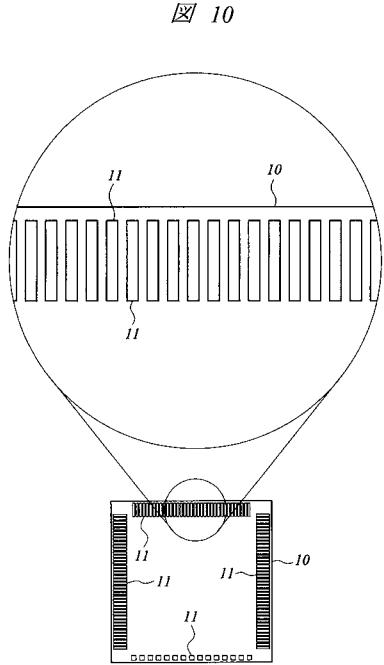

本実施の形態1において、上記プローブカードを用いてプローブ検査(電気的検査)を行う対象としては、複数の機能の半導体集積回路が形成されたSoC(System on Chip)構造のチップを例示することができる。図5は、それら複数のチップ(チップ領域)10が区画されたウエハWHの平面図である。なお、本実施の形態のプローブカードを用いたプローブ検査は、これら複数のチップ10が区画されたウエハWHに対して行うものである。また、図6は、そのチップ10の平面と、その一部を拡大したものを図示している。このチップ10は、たとえば単結晶シリコン基板からなり、その主面にはLCDドライバ回路が形成されている。また、チップ10の主面の周辺部には、チップ10内に形成されている半導体集積回路と電気的に接続する多数のパッド(テストパッド(第1電極))11が配置されている。パッド11のうちチップ10の外周に沿って2列で配列されたものは、隣り合ったパッド11の間隔をできる限り広げるために、そのチップ10の外周に沿って互いの列のパッド11が互い違いに配列されている。

20

#### 【0051】

また、上記チップ10は、ウエハの主面に区画された多数のチップ領域に半導体製造技術を使って種々の半導体集積回路や入出力端子(ボンディングパッド)を形成し、次いで入出力端子上に上記の方法でパッド11を形成した後、ウエハをダイシングしてチップ領域を個片化することにより製造することができる。また、本実施の形態1において、上記プローブ検査は、ウエハをダイシングする前に各チップ領域に対して実施するものである。なお、以後プローブ検査(パッド11とプローブ7とが接觸する工程)を説明する際に、特に明記しない場合には、チップ10はウエハをダイシングする前の各チップ領域を示すものとする。

30

#### 【0052】

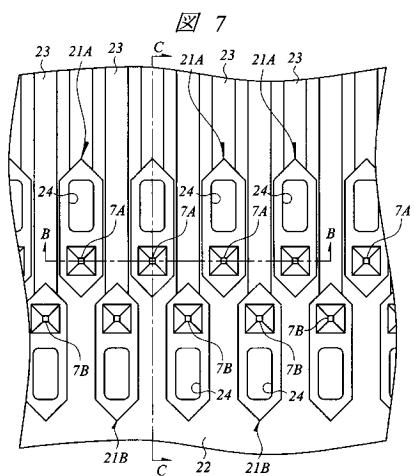

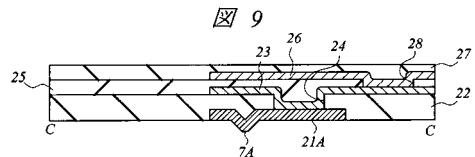

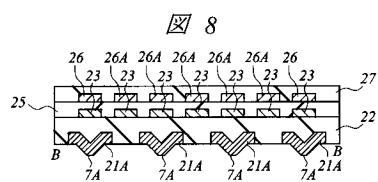

図7は上記薄膜シート2の下面のプローブ7が形成された領域の一部を拡大して示した要部平面図であり、図8は図7中のB-B線に沿った要部断面図であり、図9は図7中のC-C線に沿った要部断面図である。

40

#### 【0053】

上記プローブ7は、薄膜シート2中にて平面六角形状にパターニングされた金属膜21A、21Bの一部であり、金属膜21A、21Bのうちの薄膜シート2の下面に4角錐型または4角錐台形型に飛び出した部分である。プローブ7は、薄膜シート2の主面において上記チップ10に形成されたパッド11の位置に合わせて配置されている。これらプローブ7のうち、プローブ7Aは、2列で配列されたパッド11のうちの相対的にチップ10の外周に近い配列(以降、第1列と記す)のパッド11に対応し、プローブ7Bは、2列で配列されたパッド11のうちの相対的にチップ10の外周から遠い配列(以降、第2列と記す)のパッド11に対応している。

#### 【0054】

50

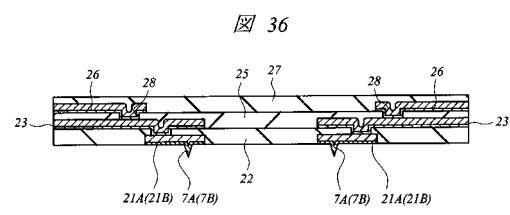

金属膜 21A、21B は、たとえば下層からロジウム膜およびニッケル膜が順次積層して形成されている。金属膜 21A、21B 上にはポリイミド膜 22 が成膜され、ポリイミド膜 22 上には各金属膜 21 と電気的に接続する配線（第 2 配線）23 が形成されている。配線 23 は、ポリイミド膜 22 に形成されたスルーホール 24 の底部で金属膜 21A、21B と接触している。また、ポリイミド膜 22 および配線 23 上には、ポリイミド膜 25 が成膜され、ポリイミド膜 22 上には配線 26、26A が形成されている。ポリイミド膜 25 および配線 26、26A 上には、ポリイミド膜 27 が成膜されている。金属膜 21A 上に延在する配線（第 2 配線）26 は、ポリイミド膜 25 に形成されたスルーホール 28 の底部で配線 23 と接触し、金属膜 21A と電気的に接続されている。

## 【0055】

10

上記したように、金属膜 21A、21B の一部は 4 角錐型または 4 角錐台形型に形成されたプローブ 7A、7B となり、ポリイミド膜 22 には金属膜 21A、21B に達するスルーホール 24 が形成される。そのため、プローブ 7A が形成された金属膜 21A およびスルーホール 24 の平面パターンと、プローブ 7B が形成された金属膜 21B およびスルーホール 24 の平面パターンとが同じ方向で配置されるようにすると、隣り合う金属膜 21A と金属膜 21B とが接触してしまい、プローブ 7A、7B からそれぞれ独立した入出力を得られなくなってしまう不具合が懸念される。そこで、本実施の形態 1 では、図 7 に示すように、プローブ 7B が形成された金属膜 21B およびスルーホール 24 の平面パターンは、プローブ 7A が形成された金属膜 21A およびスルーホール 24 の平面パターンを 180° 回転したパターンとしている。それにより、平面でプローブ 7A およびスルーホール 24 が配置された金属膜 21A の幅広の領域と、平面でプローブ 7B およびスルーホール 24 が配置された金属膜 21B の幅広の領域とが、紙面の左右方向の直線上に配置されないようになり、金属膜 21A および金属膜 21B の平面順テーパー状の領域が紙面の左右方向の直線上に配置されるようになる。その結果、隣り合う金属膜 21A と金属膜 21B とが接触してしまって不具合を防ぐことができる。また、狭ピッチでパッド 11（図 6 参照）が配置されても、それに対応した位置にプローブ 7A、7B を配置することができる。

20

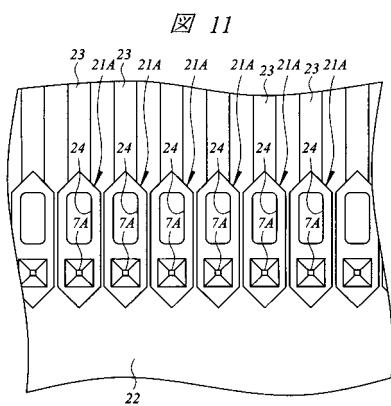

## 【0056】

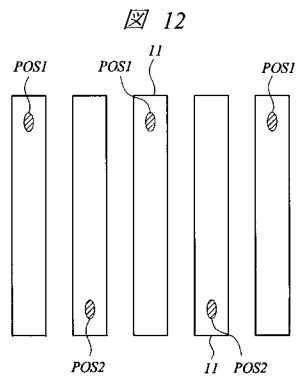

本実施の形態では、図 6 を用いてパッド 11 が 2 列で配列されている場合について説明したが、図 10 に示すように、1 列で配列されているチップも存在する。そのようなチップに対しては、図 11 に示すように、上記金属膜 21A の幅広の領域が紙面の左右方向の直線上に配置された薄膜シート 2 を用いることで対応することができる。また、このようにパッド 11 が 1 列で配列され、図 11 に示したパターンの金属膜 21A を有する薄膜シート 2 では対応できないほどにパッド 11 が小さく、かつパッド 11 が配置されているピッチが狭い場合には、次のようにして対応することができる。すなわち、図 7～図 9 に示したパターンの金属膜 21A を有する薄膜シート 2 を用いることにより、チップ 10 の外周に沿った方向でのパッド 11 の中心位置を図 6 に示したパッド 11 の中心位置と揃えることができる。図 12 に示す位置 POS1、POS2 でプローブ 7A、7B のそれをパッド 11 に接触させることができることになる。

30

## 【0057】

40

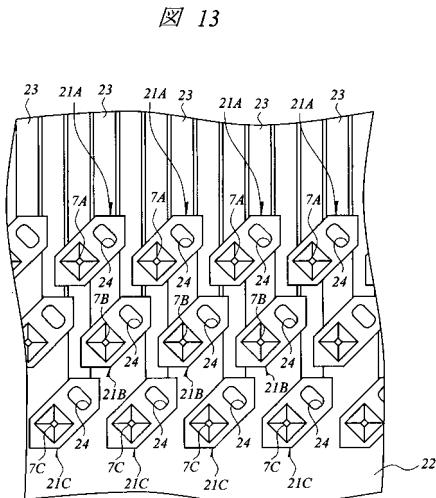

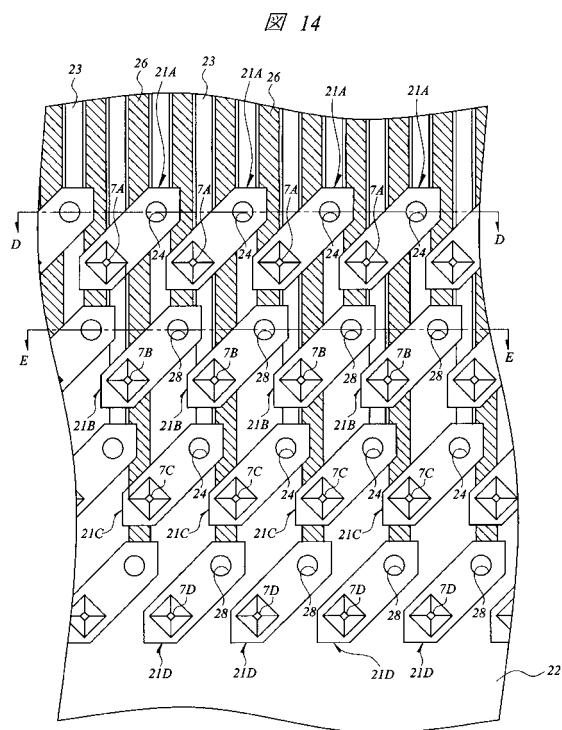

また、パッド 11 の数がさらに多い場合には、3 列以上で配列されている場合もある。図 13 は 3 列で配列されたパッド 11 に対応した薄膜シート 2 の要部平面図であり、図 14 は 4 列で配列されたパッド 11 に対応した薄膜シート 2 の要部平面図である。チップ 10 のサイズが同じであれば、パッド 11 の配列数が増えるに従って、隣接する金属膜 21A、21B の間隔がさらに狭くなるので、上記金属膜 21A、21B を含む金属膜が接触してしまうことがさらに懸念される。そこで、図 13 および図 14 に示すように、金属膜 21A、21B、21C、21D を、たとえば図 7 に示した金属膜 21A の平面パターンを 45° 回転させたものとすることで、金属膜 21A、21B、21C、21D が互いに接触してしまう不具合を防ぐことが可能となる。また、ここでは図 7 に示した金属膜 21A の平面パターンを 45° 回転させた例について説明したが、45° に限定するものでは

50

なく、金属膜 21A、21B、21C、21Dの互いの接触を防ぐことができるのであれば他の回転角でもよい。なお、金属膜 21Cには、プローブ 7B が対応するパッド 11 よりさらにチップ 10 内の内側に配置されたパッド 11 に対応するプローブ 7C が形成され、金属膜 21D には、プローブ 7C が対応するパッド 11 よりさらにチップ 10 内の内側に配置されたパッド 11 に対応するプローブ 7D が形成されている。

#### 【0058】

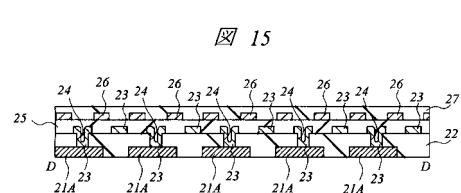

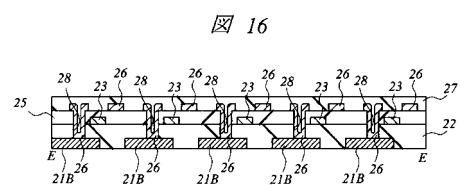

ここで、図 15 は図 14 中の D - D 線に沿った要部断面図であり、図 16 は図 14 中の E - E 線に沿った要部断面図である。図 14 に示したように、4 列のパッド 11 に対応するプローブ 7A ~ 7D を有する金属膜 21A ~ 21D を配置した場合には、金属膜 21A ~ 21D のそれぞれに上層から電気的に接続する配線のすべてを同一の配線層で形成することが困難になる。これは、隣接する金属膜 21A ~ 21D の間隔が狭くなることによって、金属膜 21A ~ 21D のそれぞれ同士が接触する虞が生じるのと共に、金属膜 21A ~ 21D に電気的に接続する配線同士も接触する虞が生じるからである。そこで、本実施の形態 1 においては、図 15 および図 16 に示すように、それら配線を 2 層の配線層（配線 23、26）から形成することを例示することができる。なお、配線 26 およびポリイミド膜 25 上には、ポリイミド膜 27 が形成されている。相対的に下層の配線 23 はポリイミド膜 22 に形成されたスルーホール 24 の底部で金属膜 21A、21C と接触し、相対的に上層の配線 26 はポリイミド膜 22、25 に形成されたスルーホール 28 の底部で金属膜 21B、21D と接触している。それにより、同一の配線層においては、隣り合う配線 23 または配線 26 の間隔を大きく確保することができる。また、パッド 11 が 5 列以上となり、それに対応するプローブ数が増加して隣接する金属膜 21A ~ 21D 等の間隔が狭くなる場合には、さらに多層に配線層を形成することによって、配線間隔を広げてもよい。

#### 【0059】

次に、上記の本実施の形態 1 の薄膜シート 2 の構造について、その製造工程と併せて図 17 ~ 図 29 を用いて説明する。図 17 ~ 図 29 は、図 7 ~ 図 9 を用いて説明した 2 列のパッド 11（図 6 参照）に対応したプローブ 7A、7B を有する薄膜シート 2 の製造工程中の要部断面図もしくは要部平面図である。なお、薄膜シートの構造および薄膜シートの製造工程と、上記プローブ 7（プローブ 7A ~ 7D）と同様のプローブの構造および製造工程については、日本特開 2004-288672 号公報、日本特開 2005-136246 号公報、日本特開 2005-136302 号公報、日本特許出願第 2004-115048 号、PCT 出願番号 PCT/JP2004/17160 号、PCT 出願番号 PCT/JP2005/4344 号、日本特許出願第 2005-109350 号、日本特許出願第 2005-168112 号、日本特許出願第 2005-181085 号、日本特許出願第 2005-194561 号、日本特許出願第 2005-291886 号および日本特許出願第 2005-315115 号にも記載がある。

#### 【0060】

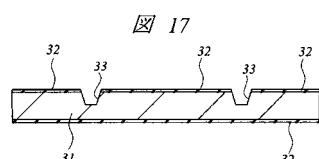

まず、図 17 に示すように、厚さ 0.2 mm ~ 0.6 mm 程度のシリコンからなるウエハ 31 を用意し、熱酸化法によってこのウエハ 31 の両面に膜厚 0.5 μm 程度の酸化シリコン膜 32 を形成する。続いて、フォトレジスト膜をマスクとしてウエハ 31 の正面側の酸化シリコン膜 32 をエッチングし、ウエハ 31 の正面側の酸化シリコン膜 32 にウエハ 31 に達する開口部を形成する。次いで、残った酸化シリコン膜 32 をマスクとし、強アルカリ水溶液（たとえば水酸化カリウム水溶液）を用いてウエハ 31 を異方的にエッチングすることによって、ウエハ 31 の正面に（111）面に囲まれた 4 角錐型または 4 角錐台形型の穴 33 を形成する。

#### 【0061】

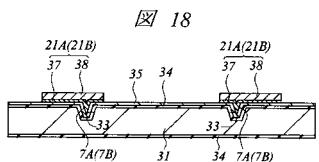

次に、図 18 に示すように、上記穴 33 の形成時にマスクとして用いた酸化シリコン膜 32 をフッ酸およびフッ化アンモニウムの混合液によるウェットエッチングにより除去する。続いて、ウエハ 31 に熱酸化処理を施すことにより、穴 33 の内部を含むウエハ 31

の全面に膜厚0.5μm程度の酸化シリコン膜34を形成する。次いで、穴33の内部を含むウエハ31の正面に導電性膜35を成膜する。この導電性膜35は、たとえば膜厚0.1μm程度のクロム膜および膜厚1μm程度の銅膜を順次スパッタリング法または蒸着法によって堆積することによって成膜することができる。次いで、導電性膜35上にフォトレジスト膜を成膜し、フォトリソグラフィ技術によって後の工程で金属膜21A、21B(図9～図11参照)が形成される領域のフォトレジスト膜を除去し、開口部を形成する。

#### 【0062】

次に、導電性膜35を電極とした電解めっき法により、上記フォトレジスト膜の開口部の底部に現れた導電性膜35上に硬度の高い導電性膜37および導電性膜38を順次堆積する。本実施の形態1においては、導電性膜37をロジウム膜とし、導電性膜38をニッケル膜とすることを例示できる。ここまで工程により、導電性膜37、38から前述の金属膜21A、21Bを形成することができる。また、穴33内の導電性膜37、38が前述のプローブ7A、7Bとなる。なお、導電性膜35は、後の工程で除去されるが、その工程については後述する。

#### 【0063】

金属膜21A、21Bにおいては、後の工程で前述のプローブ7A、7Bが形成された時に、ロジウム膜から形成された導電性膜37が表面となり、導電性膜37がパッド11に直接接触することになる。そのため、導電性膜37としては、硬度が高く耐磨耗性に優れた材質を選択することが好ましい。また、導電性膜37はパッド11に直接接触するため、プローブ7A、7Bによって削り取られたパッド11の屑が導電性膜37に付着すると、その屑を除去するクリーニング工程が必要となり、プローブ検査工程が延びてしまうことが懸念される。そのため、導電性膜37としては、パッド11を形成する材料が付着し難い材質を選択することが好ましい。そこで、本実施の形態1においては、導電性膜37として、これらの条件を満たすロジウム膜を選択している。それにより、そのクリーニング工程を省略することができる。

#### 【0064】

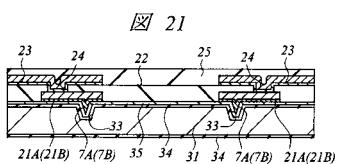

次に、上記金属膜21A、21B(導電性膜37、38)の成膜に用いたフォトレジスト膜を除去した後、図21に示すように、金属膜21A、21Bおよび導電性膜35を覆うようにポリイミド膜22(図8および図9も参照)を成膜する。続いて、そのポリイミド膜22に金属膜21A、21Bに達する前述のスルーホール24を形成する。このスルーホール24は、レーザーを用いた穴あけ加工またはアルミニウム膜をマスクとしたドライエッチングによって形成することができる。

#### 【0065】

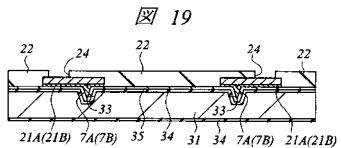

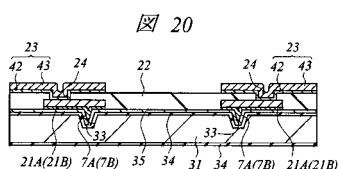

次に、図20に示すように、スルーホール24の内部を含むポリイミド膜22上に導電性膜42を成膜する。この導電性膜42は、たとえば膜厚0.1μm程度のクロム膜および膜厚1μm程度の銅膜を順次スパッタリング法または蒸着法によって堆積することによって成膜することができる。続いて、その導電性膜42上にフォトレジスト膜を形成した後に、そのフォトレジスト膜をフォトリソグラフィ技術によってパターニングし、フォトレジスト膜に導電性膜42に達する開口部を形成する。次いで、めっき法により、その開口部内の導電性膜42上に導電性膜43を成膜する。本実施の形態1においては、導電性膜43として銅膜、または銅膜およびニッケル膜を下層から順次堆積した積層膜を例示することができる。

#### 【0066】

次に、上記フォトレジスト膜を除去した後、導電性膜43をマスクとして導電性膜42をエッチングすることにより、導電性膜42、43からなる配線23を形成する。配線23は、スルーホール24の底部にて金属膜21A、21Bと電気的に接続することができる。

#### 【0067】

また、上記配線23を形成する工程時には、配線23と同じ配線層にて金属膜21A、

10

20

30

40

50

2 1 B とは電気的に接続しない配線も形成される。この配線も配線 2 3 と同様に導電性膜 4 2、4 3 から形成することができる。

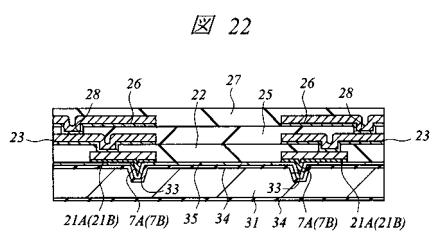

【 0 0 6 8 】

次に、図 2 1 に示すように、ウエハ 3 1 の主面に前述のポリイミド膜 2 5 を成膜する。続いて、図 2 2 に示すように、上記スルーホール 2 4、配線 2 3 およびポリイミド膜 2 5 を形成した工程と同様の工程を繰り返すことによって、スルーホール 2 8、配線 2 6 およびポリイミド膜 2 7 を形成する。配線 2 6 は、スルーホール 2 8 の底部にて配線 2 3 と電気的に接続することができる。また、配線 2 6 を形成する際には、配線 2 6 と同じ配線層で前述の配線 2 6 A (図 8 参照) も形成される。

【 0 0 6 9 】

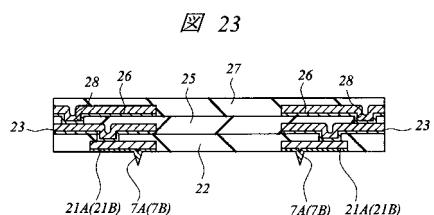

次に、図 2 3 に示すように、たとえばフッ酸とフッ化アンモニウムの混合液を用いたエッチングによって、ウエハ 3 1 の裏面の酸化シリコン膜 3 4 を除去する。続いて、強アルカリ水溶液 (たとえば水酸化カリウム水溶液) を用いたエッチングにより、薄膜シート 2 を形成するための型材であるウエハ 3 1 を除去する。次いで、酸化シリコン膜 3 4 および導電性膜 3 5 を順次エッチングにより除去し、本実施の形態 1 の薄膜シート 2 を製造する。この時、酸化シリコン膜 3 4 はフッ酸およびフッ化アンモニウムの混合液を用いてエッチングし、導電性膜 3 5 に含まれるクロム膜は過マンガン酸カリウム水溶液を用いてエッチングし、導電性膜 3 5 に含まれる銅膜はアルカリ性銅エッチング液を用いてエッチングする。ここまで工程により、プローブ 7 A、7 B を形成する導電性膜 3 7 (図 1 8 参照) であるロジウム膜がプローブ 7 A、7 B の表面に現れる。前述したように、ロジウム膜が表面に形成されたプローブ 7 A、7 B においては、プローブ 7 A、7 B が接触するパッド 1 1 の材料である Au などが付着し難く、Ni より硬度が高く、かつ酸化され難く接触抵抗を安定させることができる。

【 0 0 7 0 】

必要に応じて、上記スルーホール 2 4、配線 2 3 およびポリイミド膜 2 5 を形成する工程を繰り返すことによって、さらに配線を多層に形成してもよい。

【 0 0 7 1 】

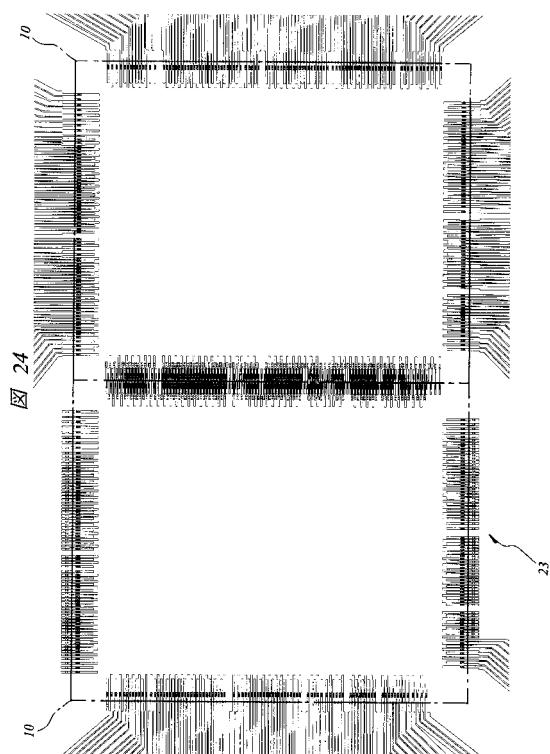

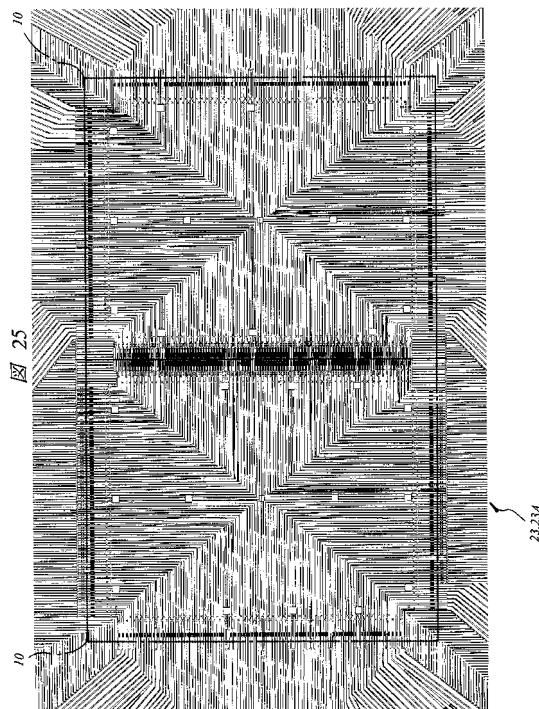

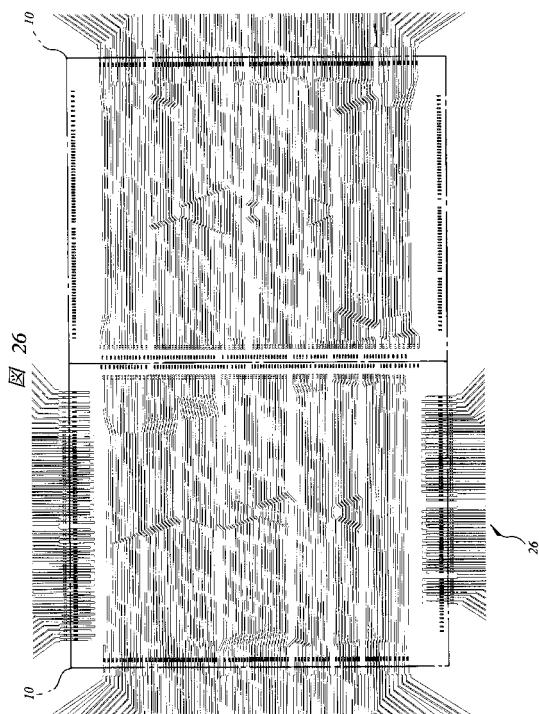

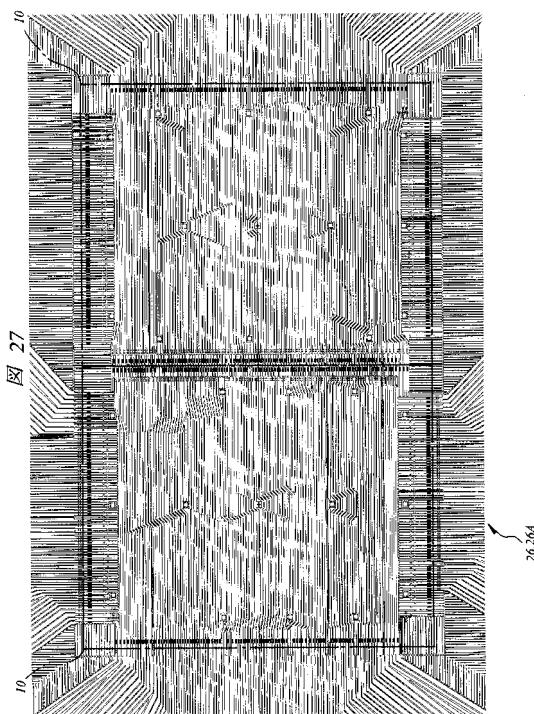

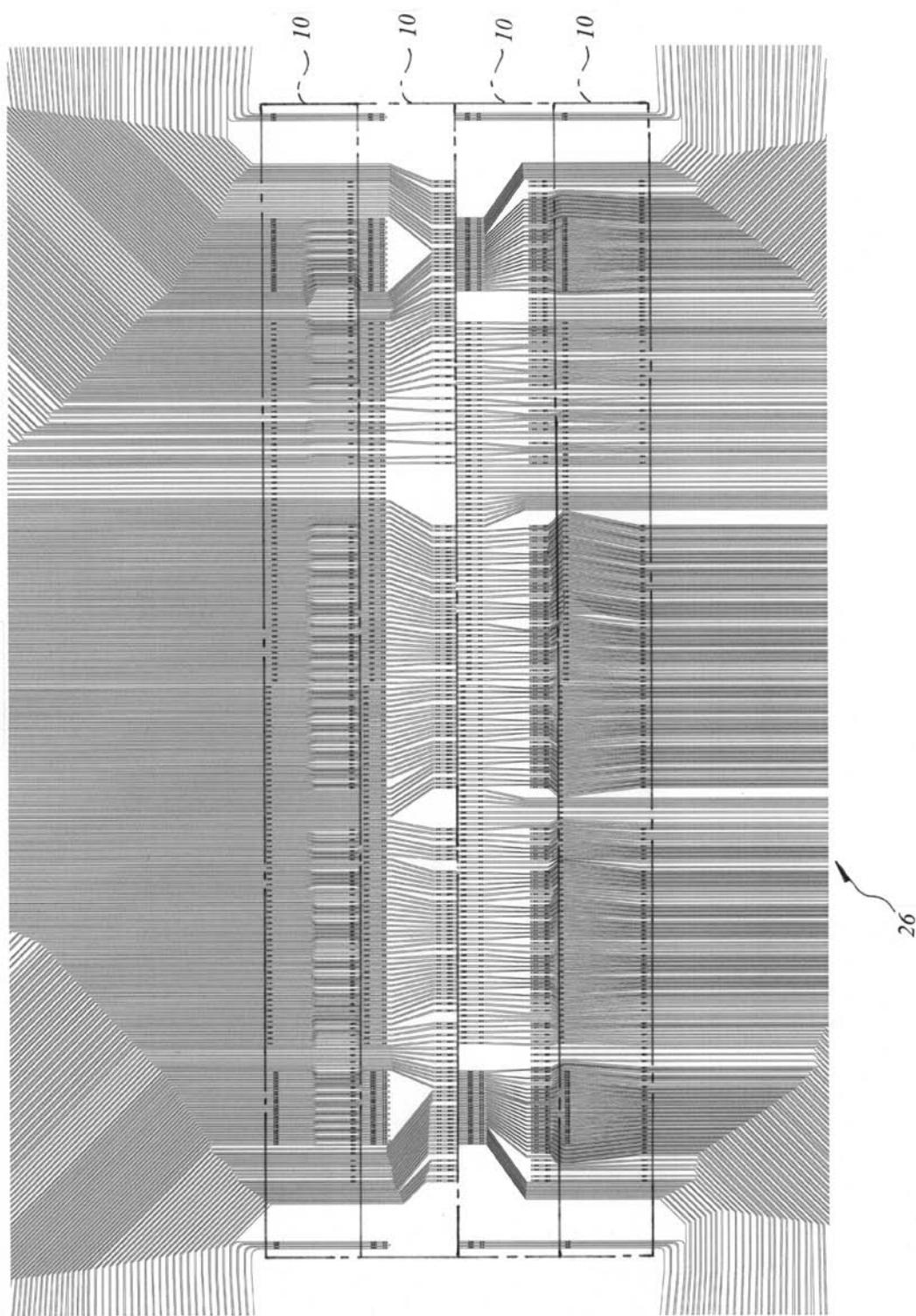

本実施の形態 1 では、一边で対向して隣接する 2 個のチップ 1 0 に対して一度にプローブ検査を実施する。ここで、図 2 4 ~ 図 2 7 は、薄膜シート 2 のうち、検査対象の 2 個のチップ 1 0 に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ 1 0 の外形に相当する。また、図 2 4 ~ 図 2 7 は、それぞれ、1 層目の配線層に形成された配線 2 3 の平面パターン、図 2 4 の平面パターンに配線 2 3 と同じ配線層で形成された配線 2 3 A を加えた平面パターン、2 層目の配線層に形成された配線 2 6 の平面パターン、および図 2 6 の平面パターンに配線 2 6 と同じ配線層で形成された配線 (第 3 配線) 2 6 A を加えた平面パターンを図示したものである。配線 (第 3 配線) 2 3 A は、図 2 1 を用いて前述した金属膜 2 1 A、2 1 B とは電気的に接続しない配線である。

【 0 0 7 2 】

図 2 4 ~ 図 2 7 に示した平面パターンは、本実施の形態 1 のプローブカードにおけるチャネル割り付けに制約があり、各々の配線 2 3、2 6 が所定のチャネルと電気的に接続するためには、所定のポゴ座 8 (図 2 参照) と電気的に接続しなければならない場合のものである。

【 0 0 7 3 】

金属膜 2 1 A、2 1 B と電気的に接続された配線 2 3 の一部は、薄膜シート 2 の外周に向かって引き回され、多層配線基板 1 (図 1 および図 2 参照) に設けられた複数の受け部のうちの対応するものと電気的に接続される。また、他の配線 2 3 には配線 2 6 が接続され、各々の配線 2 6 は薄膜シート 2 の外周に向かって引き回され、多層配線基板 1 に設けられた複数の受け部のうちの対応するものと電気的に接続される。

【 0 0 7 4 】

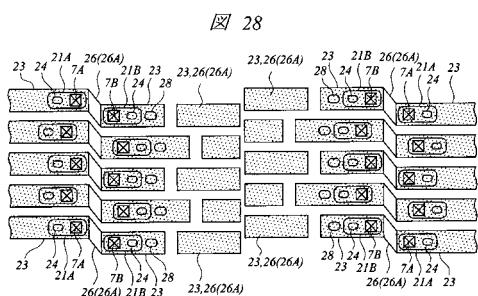

図 2 8 に示すように、本実施の形態 1 では、平面でプローブ 7 A、7 B の近傍となる領

10

20

30

40

50

域においては、配線 2 3 と、配線 2 3 と電気的に接続する配線 2 6 もしくは配線 2 3 とは電気的に接続しない配線 2 6 A とが重なるように各配線の平面パターンを形成する。なお、図 2 8 中において、梨地模様のハッチングを付した個所は、配線 2 3 と配線 2 6 もしくは配線 2 6 A とが重なっている個所を示しており、かつ配線 2 3 が配置されている個所を示している。また、プローブ 7 A、7 B の上部には、配線 2 3 および配線 2 6 (もしくは配線 2 6 A) の両方が配置される平面パターンとする。このような平面パターンとすることにより、プローブ 7 A、7 B の各々の上部において薄膜シート 2 の厚さを均一にすることができる。それにより、プローブ検査時においては、押圧具 9 (図 3 参照) から加わる荷重が均等に各々のプローブ 7 A、7 B に加わるようにすることができる。その結果、プローブ 7 A、7 B の各々と対応するパッド 1 1 (図 6 および図 10 参照) とのコンタクト性を向上することが可能となる。 10

#### 【 0 0 7 5 】

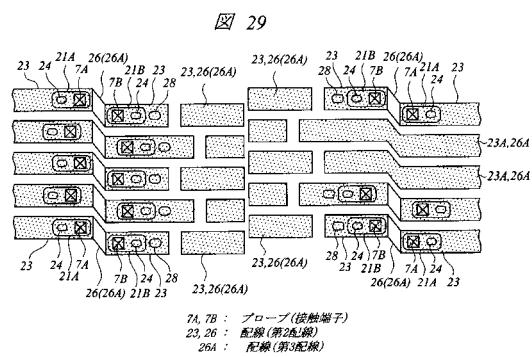

また、本実施の形態 1 では、薄膜シート 2 中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成する。たとえば、図 2 9 に示すように、配線 2 3 が形成されている配線層において、配線 2 3 の配置間隔が開き過ぎている個所には、金属膜 2 1 A、2 1 B とは電気的に接続しない配線 2 3 A を配置することによって、この配線層における配線の配置間隔および配線の配置密度を均一にすることができる。この配線 2 3 A は、配線 2 3 を形成した工程で同時に形成することができる。また、前述した配線 2 6 A は、配線 2 6 が形成されている配線層において配線 2 6 の配置間隔が開き過ぎている個所に配置されたものであり、この配線 2 6 A を配置することによって、この配線層における配線の配置間隔および配線の配置密度を均一にすることができる。このように、薄膜シート 2 中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成することにより、薄膜シート 2 のうち特にプローブ 7 A、7 B の近傍では剛性および厚さを均一にすることができる。それにより、プローブ 7 A、7 B の近傍では、薄膜シート 2 に皺および撓みが発生することを防ぐことができるので、プローブ 7 A、7 B の各々と対応するパッド 1 1 とのコンタクト性を向上することが可能となる。 20

#### 【 0 0 7 6 】

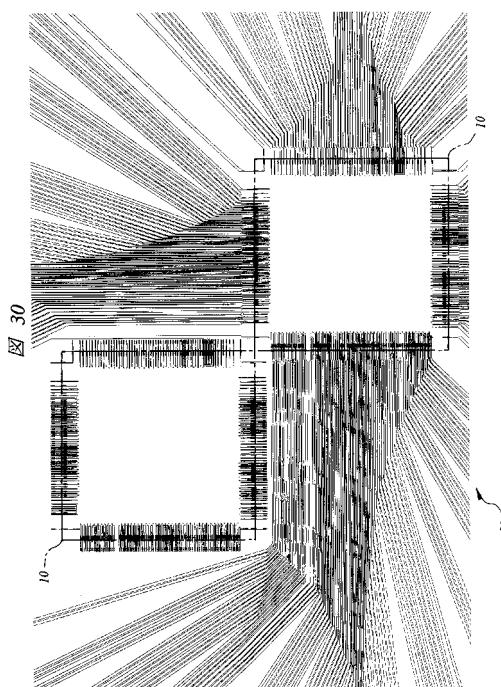

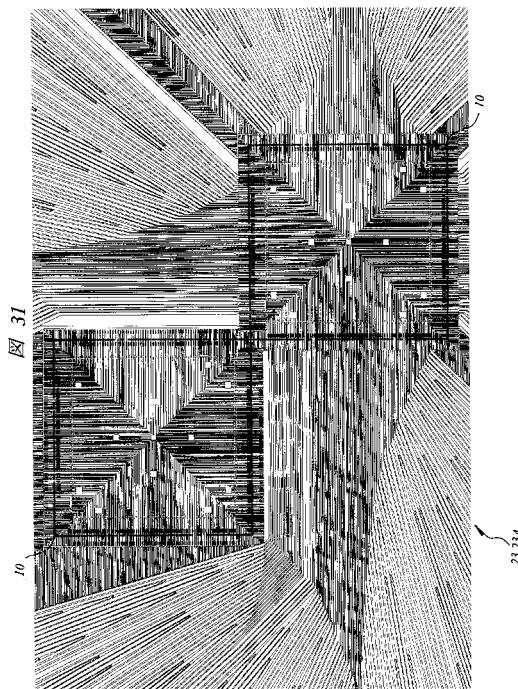

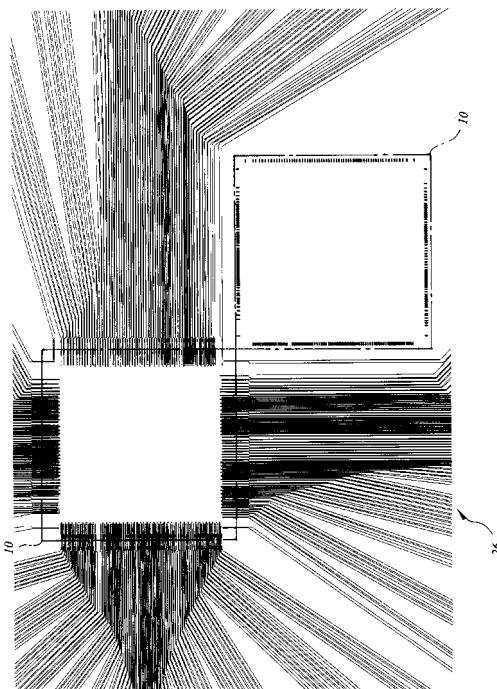

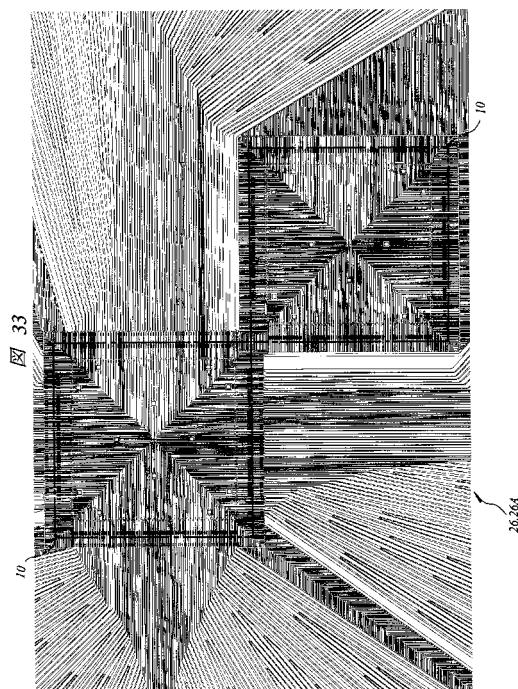

図 2 4 ~ 図 2 7 では、一辺で対向して隣接する 2 個のチップ 1 0 に対して一度にプローブ検査を実施する場合の薄膜シート 2 中の配線の平面パターンを示したが、対角線方向で (対角的に) 隣接する 2 個のチップ 1 0 に対して一度にプローブ検査を実施できるように、薄膜シート 2 中の各配線層の配線の平面パターンを形成してもよい。ここで、図 3 0 ~ 図 3 3 は、薄膜シート 2 のうち、検査対象の 2 個のチップ 1 0 に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ 1 0 の外形に相当する。また、図 3 0 ~ 図 3 3 は、それぞれ、1 層目の配線層に形成された配線 2 3 の平面パターン、図 3 0 の平面パターンに配線 2 3 と同じ配線層で形成された配線 2 3 A を加えた平面パターン、2 層目の配線層に形成された配線 2 6 の平面パターン、および図 3 2 の平面パターンに配線 2 6 と同じ配線層で形成された配線 2 6 A を加えた平面パターンを図示したものである。 30

#### 【 0 0 7 7 】

上記のように対角線方向で (対角的に) 隣接する 2 個のチップ 1 0 に対して一度にプローブ検査を実施できるように薄膜シート 2 中の各配線層の配線の平面パターンを形成した場合でも、平面でプローブ 7 A、7 B の近傍となる領域においては、配線 2 3 と、配線 2 3 と電気的に接続する配線 2 6 もしくは配線 2 3 とは電気的に接続しない配線 2 6 A とが重なるように各配線の平面パターンを形成する。また、プローブ 7 A、7 B の上部には、配線 2 3 および配線 2 6 (もしくは配線 2 6 A) の両方が配置される平面パターンとする。それにより、プローブ 7 A、7 B の各々の上部において薄膜シート 2 の厚さを均一にすることができるので、プローブ検査時においては、押圧具 9 (図 3 参照) から加わる荷重が均等に各々のプローブ 7 A、7 B に加わるようにすることができる。その結果、プローブ 7 A、7 B の各々と対応するパッド 1 1 とのコンタクト性を向上することが可能となる。 40 50

。また、一辺で対向して隣接する2個のチップ10に対して一度にプローブ検査を実施する場合の薄膜シート2と同様に、薄膜シート2中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線23A、26Aを配置する。それにより、薄膜シート2のうち特にプローブ7A、7Bの近傍では剛性および厚さを均一にすることができるので、プローブ7A、7Bの近傍では、薄膜シート2に皺および撓みが発生することを防ぐことができる。すなわち、プローブ7A、7Bの各々と対応するパッド11とのコンタクト性を向上することが可能となる。

#### 【0078】

##### (実施の形態2)

前記実施の形態1では、前記実施の形態1のプローブカードにおけるチャネル割り付けに制約がある場合の薄膜シート2中の各配線層の配線の平面パターンについて説明したが、本実施の形態2では、プローブカードにおけるチャネル割り付けに制約がない場合の例について説明する。

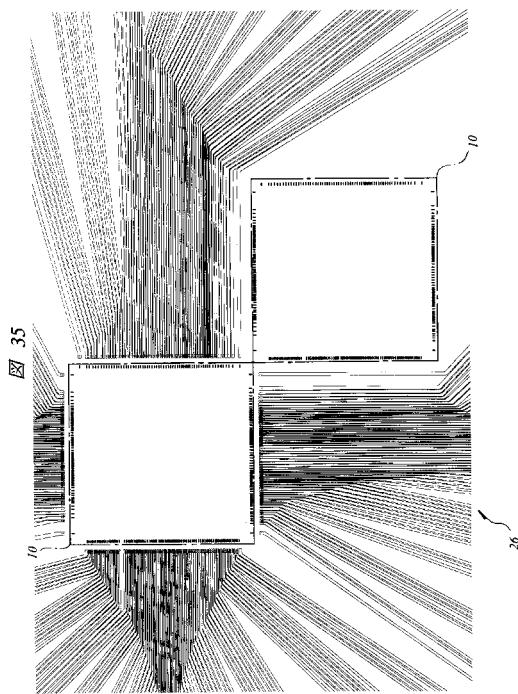

#### 【0079】

本実施の形態2では、対角線方向で(対角的に)隣接する2個のチップ10に対して一度にプローブ検査を実施する。ここで、図34および図35は、薄膜シート2のうち、検査対象の2個のチップ10に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ10の外形に相当する。また、図34および図35は、それぞれ、1層目の配線層に形成された配線23の平面パターン、および2層目の配線層に形成された配線26の平面パターンを図示したものである。このように対角線方向で隣接する2個のチップ10に対応する仕様とすることにより、1つのチップ10に対応する位置で配線23もしくは配線26を平面で全方向に狭ピッチで引き出すことが可能となる。

#### 【0080】

本実施の形態2においても、前記実施の形態1と同様に、金属膜21A、21B(図7～図9参照)と電気的に接続された配線23の一部は、薄膜シート2の外周に向かって引き回され、多層配線基板1(図1および図2参照)に設けられた複数の受け部のうちの対応するものと電気的に接続される。また、他の配線23には配線26が接続され、各々の配線26は薄膜シート2の外周に向かって引き回され、多層配線基板1に設けられた複数の受け部のうちの対応するものと電気的に接続される。

#### 【0081】

また、本実施の形態2においても、前記実施の形態1と同様に、平面でプローブ7A、7Bの近傍となる領域においては、配線23と、配線23と電気的に接続する配線26もしくは配線23とは電気的に接続しない配線26Aとが重なるように各配線の平面パターンを形成するが、プローブ7A、7B(金属膜21A、21B)の上部においては、配線26よりも相対的に下層(第1配線層)の配線23のみが配置され、配線26(もしくは配線26A)が配置されないパターンとする(図36参照)。このような配線23、26のパターンとすることにより、プローブ7A、7Bの各々の上部において薄膜シート2の厚さを均一にことができる。それにより、プローブ検査時においては、押圧具9(図3参照)から加わる荷重が均等に各々のプローブ7A、7Bに加わるようにすることができる。その結果、プローブ7A、7Bの各々と対応するパッド11(図6および図10参照)とのコンタクト性を向上することが可能となる。また、薄膜シート2のうち、プローブ7A、7B(金属膜21A、21B)の近傍では配線26が配置されていないことによって他の部分より剛性を低くすることができるので、プローブ7A、7Bの各々と対応するパッド11とのコンタクト性を前記実施の形態1より向上することが可能となる。

#### 【0082】

また、本実施の形態2においても、前記実施の形態1と同様に、薄膜シート2中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線23、23A、26、26Aのパターンを形成する。このように、薄膜シート2中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成する

10

20

30

40

50

ことにより、薄膜シート2のうち特にプローブ7A、7Bの近傍では剛性および厚さを均一にすることができる。それにより、プローブ7A、7Bの近傍では、薄膜シート2に皺および撓みが発生することを防ぐことができるので、プローブ7A、7Bの各々と対応するパッド11とのコンタクト性を向上することが可能となる。

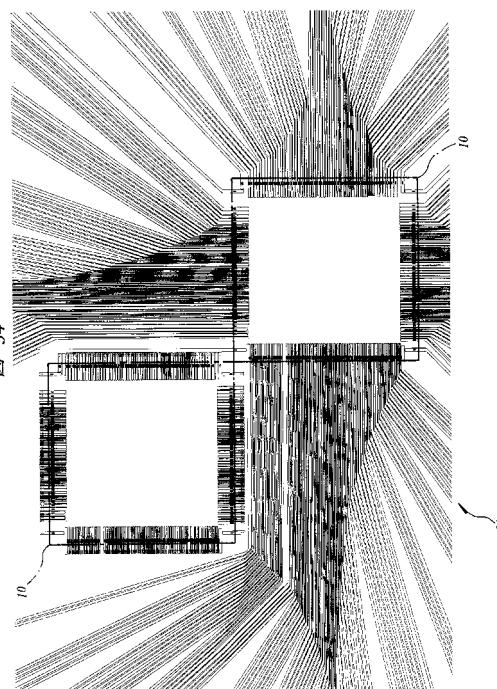

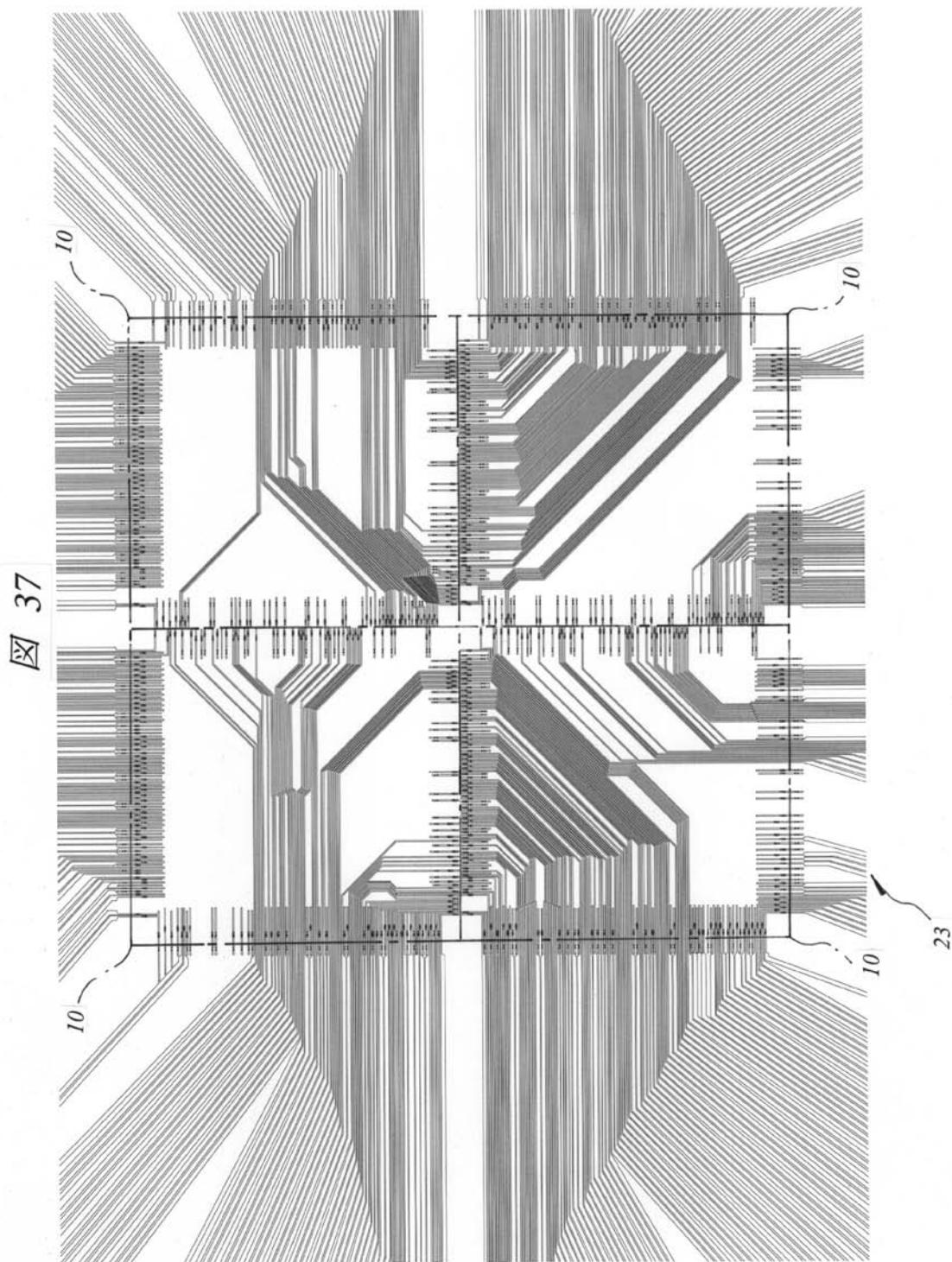

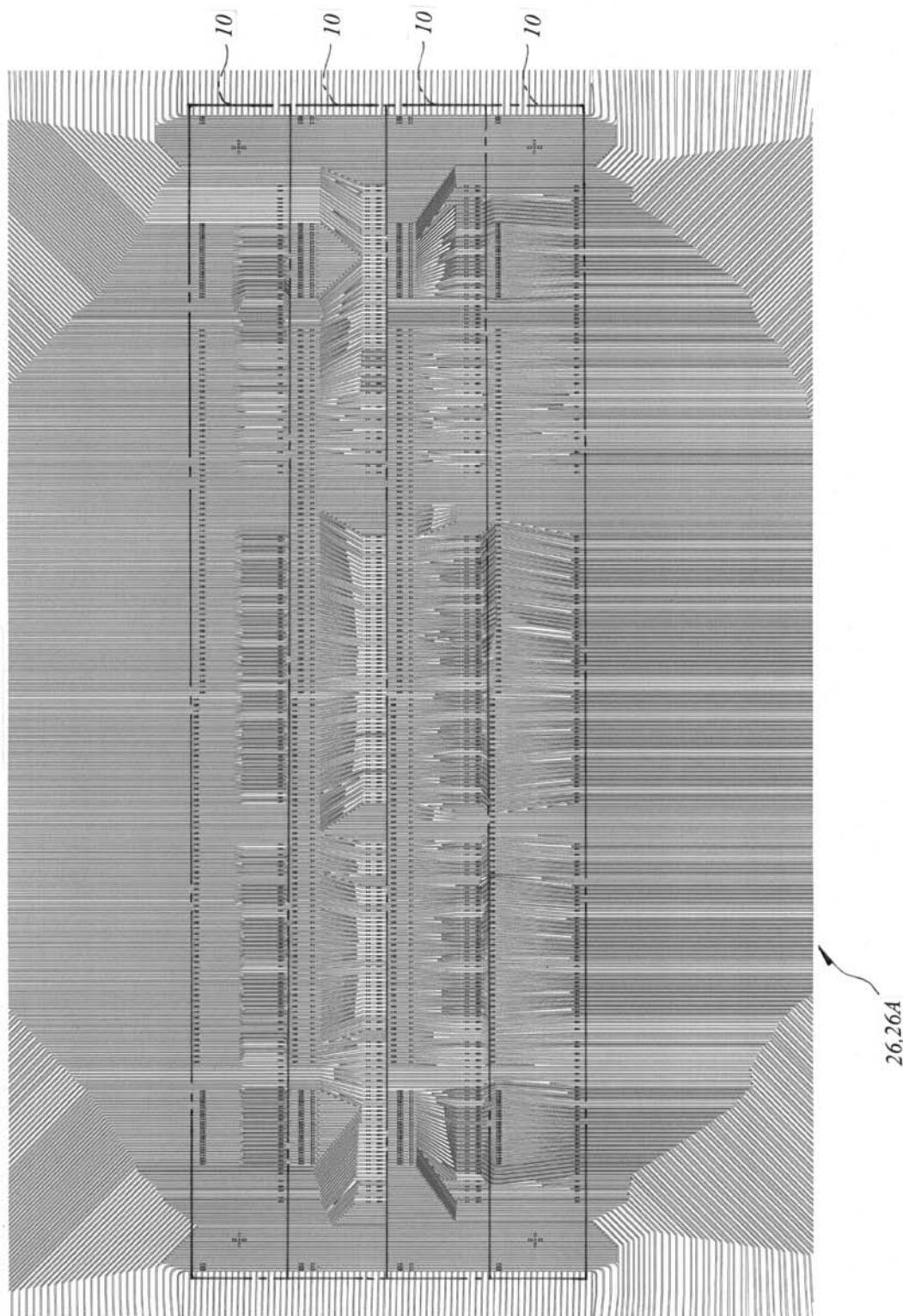

#### 【0083】

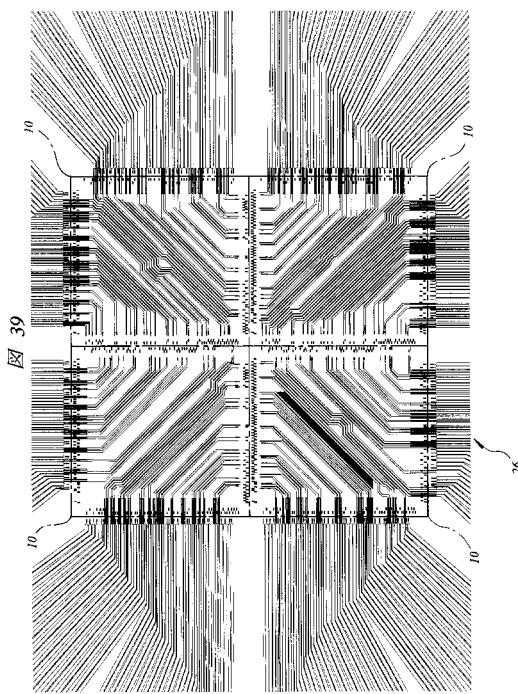

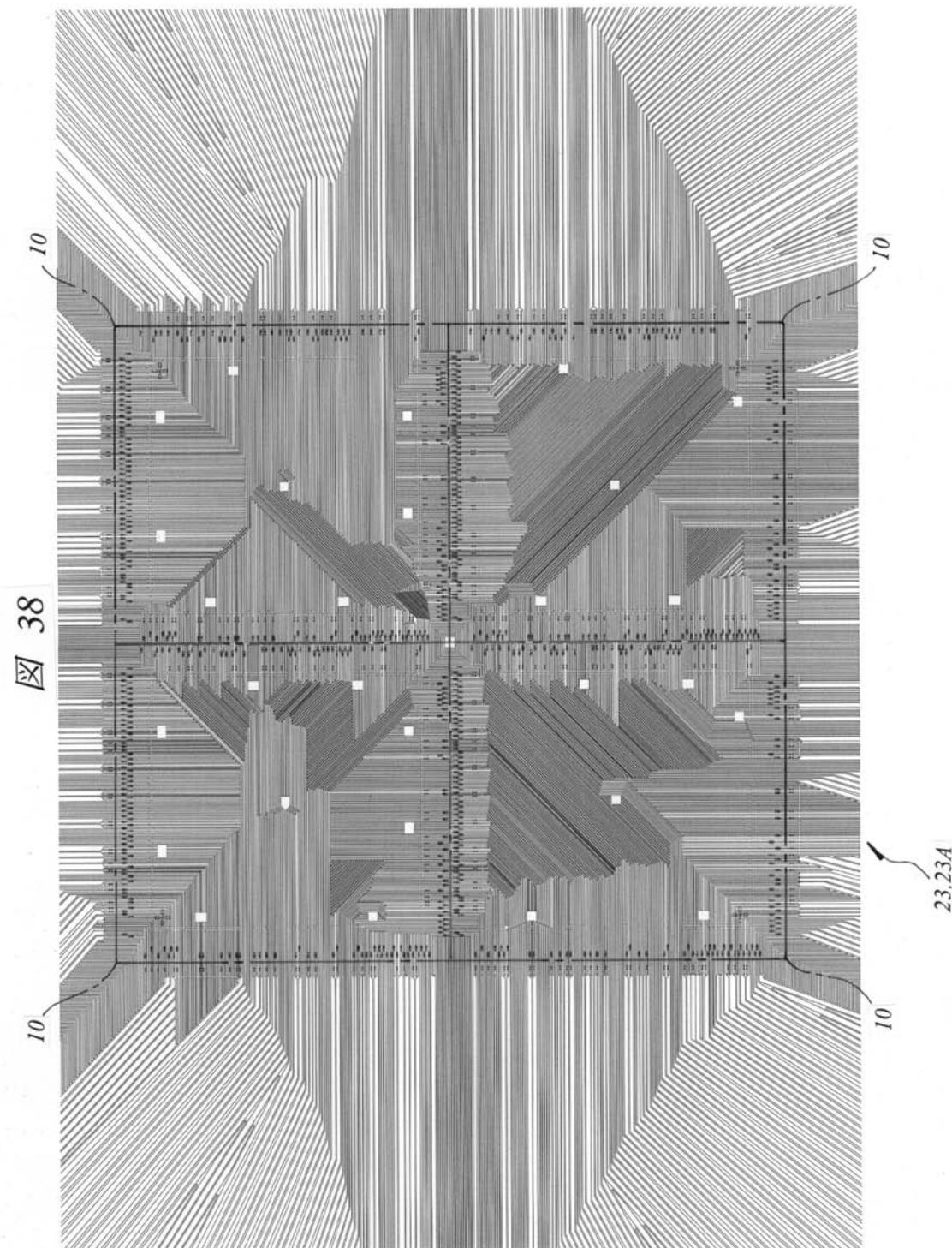

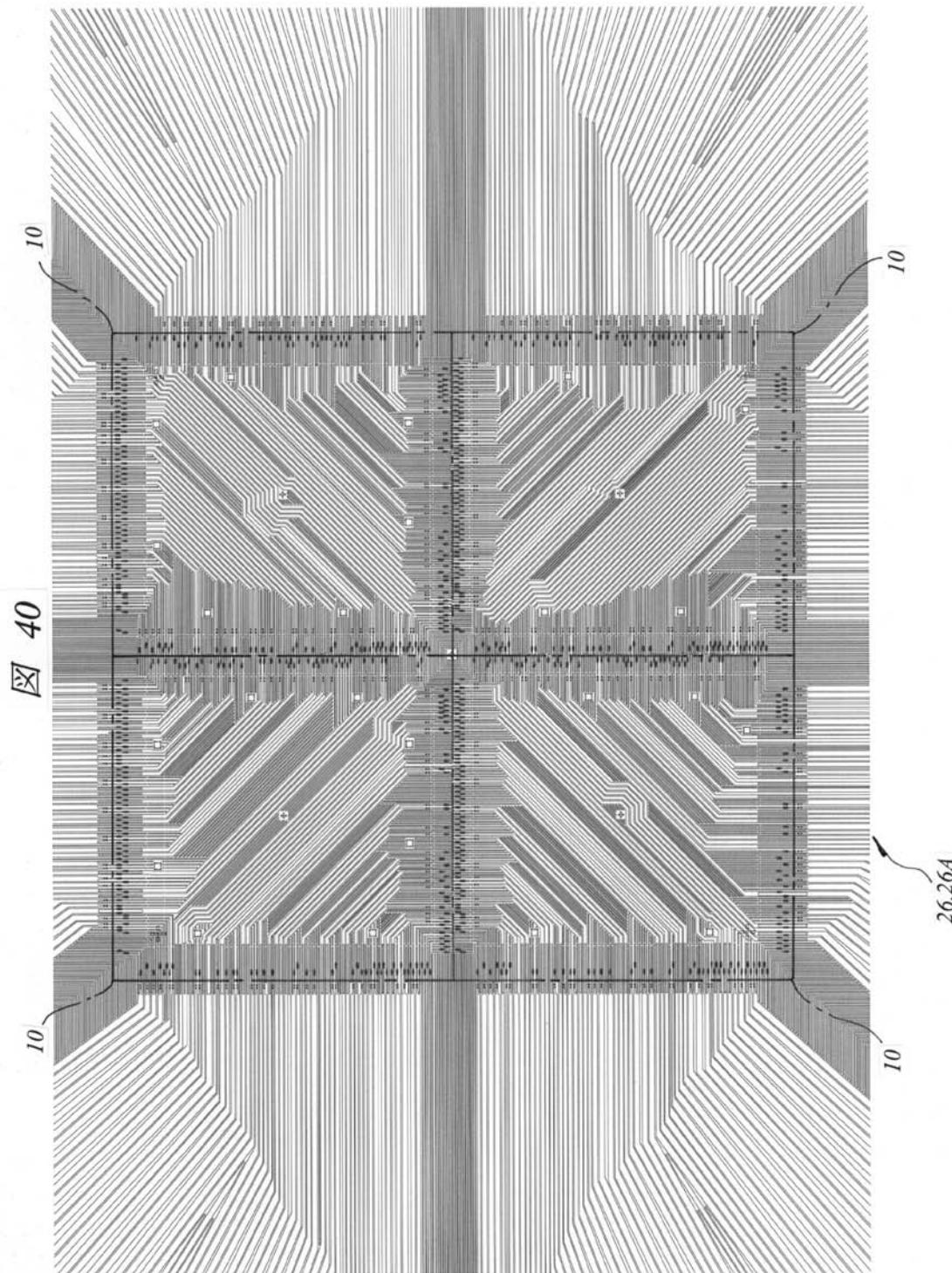

図34および図35では、対角線方向で(対角的に)隣接する2個のチップ10に対して一度にプローブ検査を実施する場合の薄膜シート2中の配線の平面パターンを示したが、その2個のチップ10と一緒に対向して隣接する2個のチップ10も含めて合計4個のチップ10に対して一度にプローブ検査を実施できるように、薄膜シート2中の各配線層の配線の平面パターンを形成してもよい。ここで、図37～図40は、薄膜シート2のうち、検査対象の4個のチップ10に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ10の外形に相当する。また、図37～図40は、それぞれ、1層目の配線層に形成された配線23の平面パターン、図37の平面パターンに配線23と同じ配線層で形成された配線23Aを加えた平面パターン、2層目の配線層に形成された配線26の平面パターン、および図39の平面パターンに配線26と同じ配線層で形成された配線26Aを加えた平面パターンを図示したものである。

#### 【0084】

上記のように4個のチップ10に対して一度にプローブ検査を実施できるように薄膜シート2中の各配線層の配線の平面パターンを形成した場合でも、平面でプローブ7A、7Bの近傍となる領域においては、配線23と、配線23と電気的に接続する配線26もしくは配線23とは電気的に接続しない配線26Aとが重なるように各配線の平面パターンを形成するが、プローブ7A、7B(金属膜21A、21B)の上部においては、配線26よりも相対的に下層の配線23のみが配置され、配線26(もしくは配線26A)が配置されないパターンとする(図36参照)。このような配線23、26のパターンとすることにより、プローブ7A、7Bの各々の上部において薄膜シート2の厚さを均一にすることができる。それにより、プローブ検査時においては、押圧具9(図3参照)から加わる荷重が均等に各々のプローブ7A、7Bに加わるようにすることができる。その結果、プローブ7A、7Bの各々と対応するパッド11(図6および図10参照)とのコンタクト性を向上することが可能となる。また、薄膜シート2のうち、プローブ7A、7B(金属膜21A、21B)の近傍では配線26が配置されていないことによって他の部分より剛性を低くすることができるので、プローブ7A、7Bの各々と対応するパッド11とのコンタクト性を前記実施の形態1より向上することが可能となる。

#### 【0085】

上記の本実施の形態2では、2個または4個のチップ10に対して一度にプローブ検査を実施できるように薄膜シート2中の各配線層の配線の平面パターンを形成した場合について説明したが、選択するチップ10は2個または4個に限定するものなく、前述したようなパターンで配線23、23A、26、26Aの引き回しが可能であれば何個であってもよい。

#### 【0086】

上記のような本実施の形態2によっても前記実施の形態1と同様の効果を得ることができる。

#### 【0087】

##### (実施の形態3)

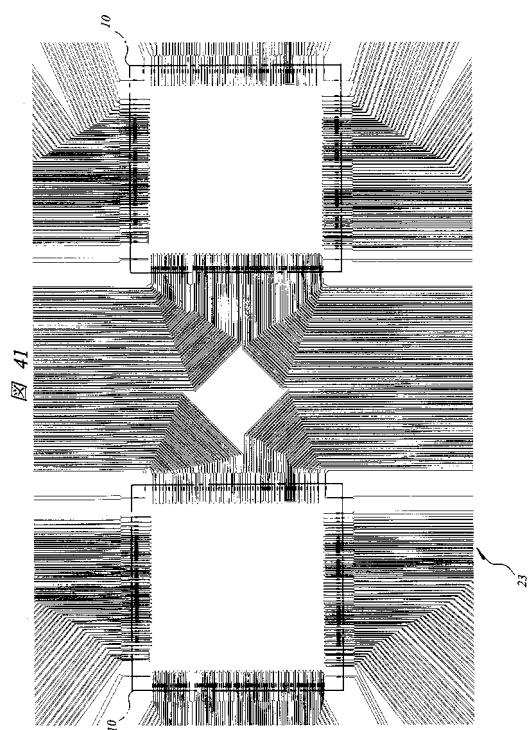

本実施の形態3では、ウエハWH(図5参照)内において1個以上のチップ10に相当する間隔を離間して並ぶ2個のチップ10に対して一度にプローブ検査を実施する場合の薄膜シート2中の配線の平面パターンについて説明する。

#### 【0088】

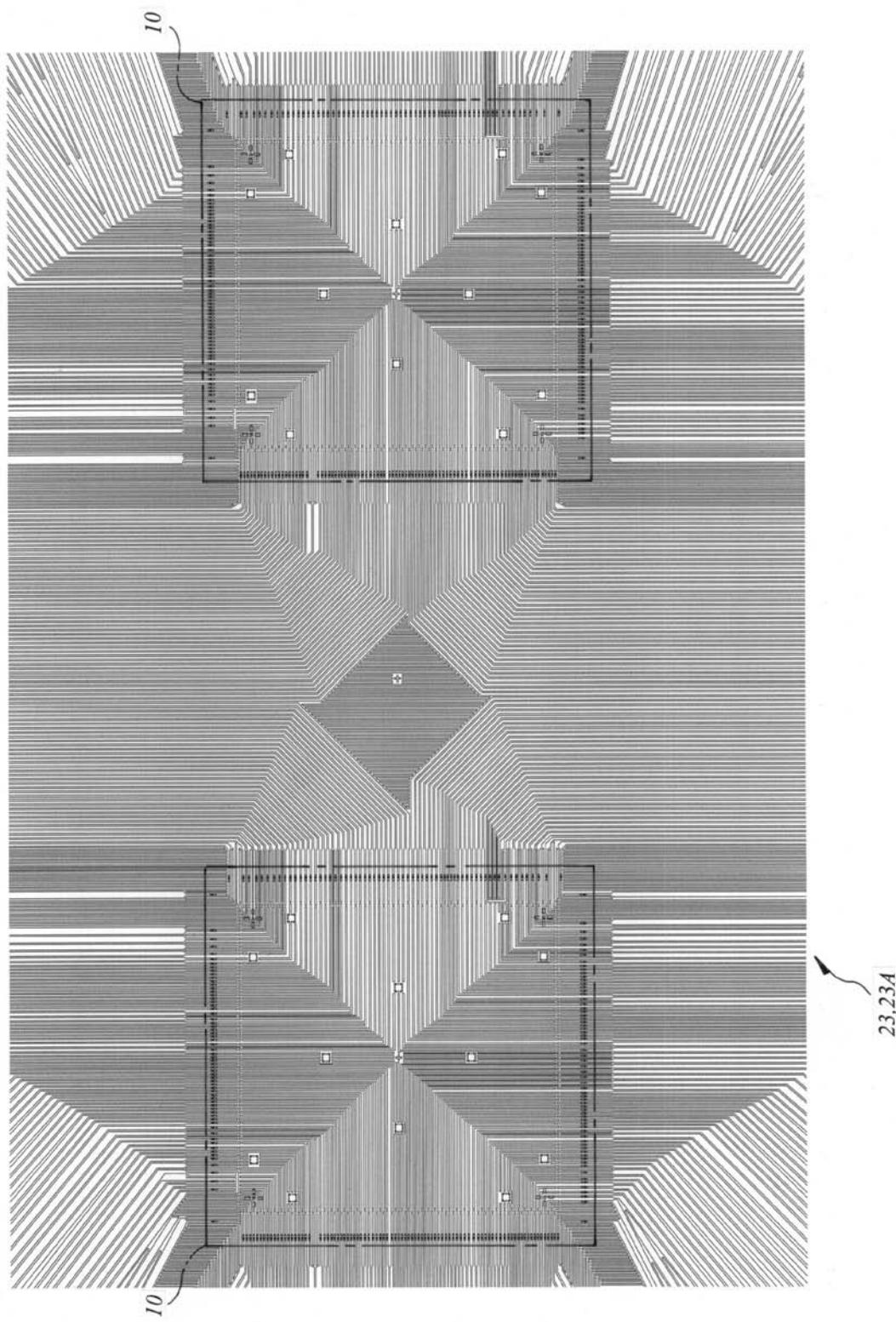

図41および図42は、薄膜シート2のうち、検査対象の2個のチップ10に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ10の外形に相当する。また、図41および図42は、それぞれ、1層目の配線層に形成され

10

20

30

40

50

た配線 2 3 の平面パターン、および図 4 1 の平面パターンに配線 2 3 と同じ配線層で形成された配線 2 3 A を加えた平面パターンを図示したものである。

【 0 0 8 9 】

本実施の形態 3 においても、前記実施の形態 1 と同様に、金属膜 2 1 A、2 1 B（図 7～図 9 参照）と電気的に接続された配線 2 3 の一部は、薄膜シート 2 の外周に向かって引き回され、多層配線基板 1（図 1 および図 2 参照）に設けられた複数の受け部のうちの対応するものと電気的に接続される。また、本実施の形態 3 では、薄膜シート 2 中の配線は配線 2 3、2 3 A を含む 1 層の配線層で形成される。

【 0 0 9 0 】

また、本実施の形態 3 においても、前記実施の形態 1 と同様に、薄膜シート 2 中の配線層において、配線の配置間隔および配線の配置密度が均一になるように配線 2 3、2 3 A のパターンを形成する。このように、薄膜シート 2 中の配線層において、配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成することにより、薄膜シート 2 のうち特にプローブ 7 A、7 B の近傍では剛性および厚さを均一にすることができる。それにより、プローブ 7 A、7 B の近傍では、薄膜シート 2 に皺および撓みが発生することを防ぐことができるので、プローブ 7 A、7 B の各々と対応するパッド 1 1 とのコンタクト性を向上することが可能となる。

【 0 0 9 1 】

上記のような配線 2 3、2 3 A のパターンを有する本実施の形態 3 の薄膜シート 2 によれば、間を離間させて 2 個のチップ 1 0 を選択するように薄膜シート 2 の構造を形成している。それにより、薄膜シート 2 中においては、配線層を 1 層のみとして配線 2 3、2 3 A を狭ピッチで引き出すことが可能となる。その結果、薄膜シート 2 全体で剛性を低くすることができるので、プローブ 7 A、7 B の各々と対応するパッド 1 1 とのコンタクト性を前記実施の形態 1 より向上することが可能となる。

【 0 0 9 2 】

上記のような本実施の形態 3 によっても前記実施の形態 1 と同様の効果を得ることができる。

【 0 0 9 3 】

（実施の形態 4 ）

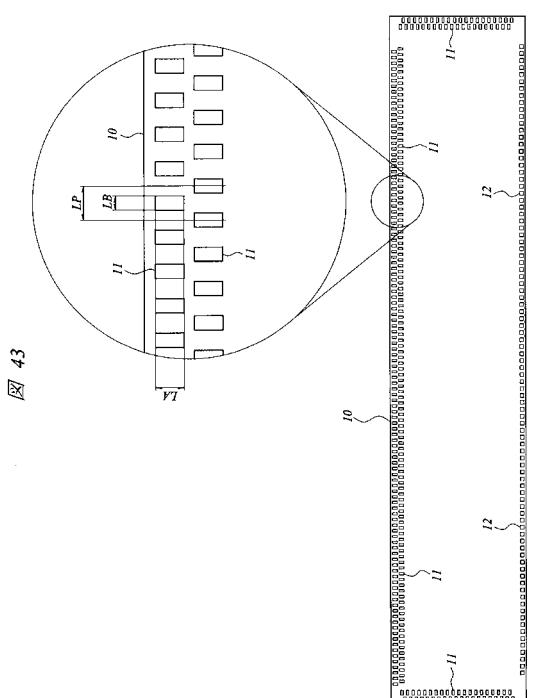

前記実施の形態 1 では、プローブ検査（電気的検査）を行う対象として複数の機能の半導体集積回路が形成された S o C 構造のチップを例示したが、本実施の形態 4 では、L C D（Liquid Crystal Display）ドライバが形成されたチップを例示する。

【 0 0 9 4 】

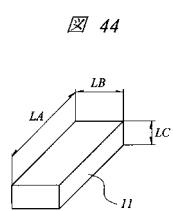

図 4 3 は、そのチップ 1 0 の平面と、その一部を拡大したものを図示している。このチップ 1 0 は、たとえば単結晶シリコン基板からなり、その正面には L C D ドライバ回路が形成されている。また、チップ 1 0 の正面の周辺部には、L C D ドライバ回路と電気的に接続する多数のパッド（テストパッド（第 1 電極））1 1、1 2 が配置されており、図 4 3 中におけるチップ 1 0 の上側の長辺および両短辺に沿って配列されたパッド 1 1 は出力端子となり、チップ 1 0 の下側の長辺に沿って配列されたパッド 1 2 は入力端子となっている。L C D ドライバの出力端子数は入力端子数より多いことから、隣り合ったパッド 1 1 の間隔をできる限り広げるために、パッド 1 1 はチップ 1 0 の上側の長辺および両短辺に沿って 2 列で配列され、チップ 1 0 の上側の長辺および両短辺に沿って互いの列のパッド 1 1 が互い違いに配列されている。本実施の形態 1 において、隣り合うパッド 1 1 が配置されているピッチ L P は、たとえば約 6 8  $\mu\text{m}$  である。また、本実施の形態 1 において、パッド 1 1 は平面矩形であり、チップ 1 0 の外周と交差（直交）する方向に延在する長辺の長さ L A は約 6 3  $\mu\text{m}$  であり、チップ 1 0 の外周に沿って延在する短辺の長さ L B は約 3 4  $\mu\text{m}$  である。また、隣り合うパッド 1 1 が配置されているピッチ L P が約 6 8  $\mu\text{m}$  であり、パッド 1 1 の短辺の長さ L B が約 3 4  $\mu\text{m}$  であることから、隣り合うパッド 1 1 の間隔は約 3 4  $\mu\text{m}$  となる。

【 0 0 9 5 】

10

20

30

40

50

パッド11、12は、たとえばAu(金)から形成されたバンプ電極(突起電極)であり、チップ10の入出力端子(ボンディングパッド)上に、電解めっき、無電解めっき、蒸着あるいはスパッタリングなどの方法によって形成されたものである。図44は、パッド11の斜視図である。パッド11の高さLCは約15μmであり、パッド12も同程度の高さを有する。

【0096】

また、上記チップ10は、ウエハの正面に区画された多数のチップ領域に半導体製造技術を使ってLCDドライバ回路(半導体集積回路)や入出力端子(ボンディングパッド)を形成し、次いで入出力端子上に上記の方法でパッド11を形成した後、ウエハをダイシングしてチップ領域を個片化することにより製造することができる。また、本実施の形態4において、上記プローブ検査は、ウエハをダイシングする前に各チップ領域に対して実施するものである。なお、以後プローブ検査(パッド11、12とプローブ7とが接触する工程)を説明する際に、特に明記しない場合には、チップ10はウエハをダイシングする前の各チップ領域を示すものとする。

10

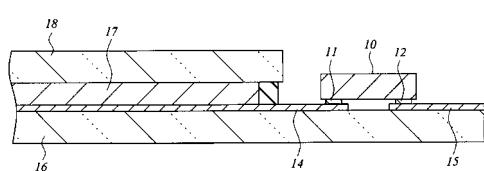

【0097】

図45は、上記チップ10の液晶パネルへの接続方法を示す要部断面図である。図45に示すように、液晶パネルは、たとえば正面に画素電極14、15が形成されたガラス基板16、液晶層17、および液晶層17を介してガラス基板16と対向するように配置されたガラス基板18などから形成されている。本実施の形態4においては、このような液晶パネルのガラス基板16の画素電極14、15に、それぞれパッド11、12が接続するようにチップ10をフェイスダウンボンディングすることによって、チップ10を液晶パネルへ接続することを例示できる。

20

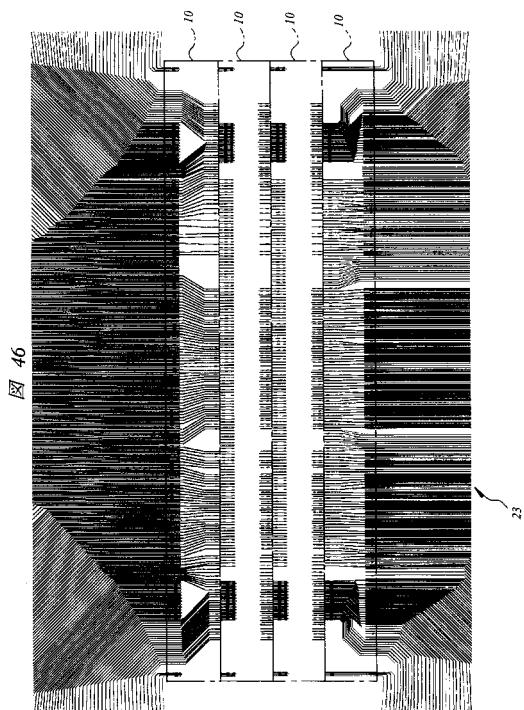

【0098】

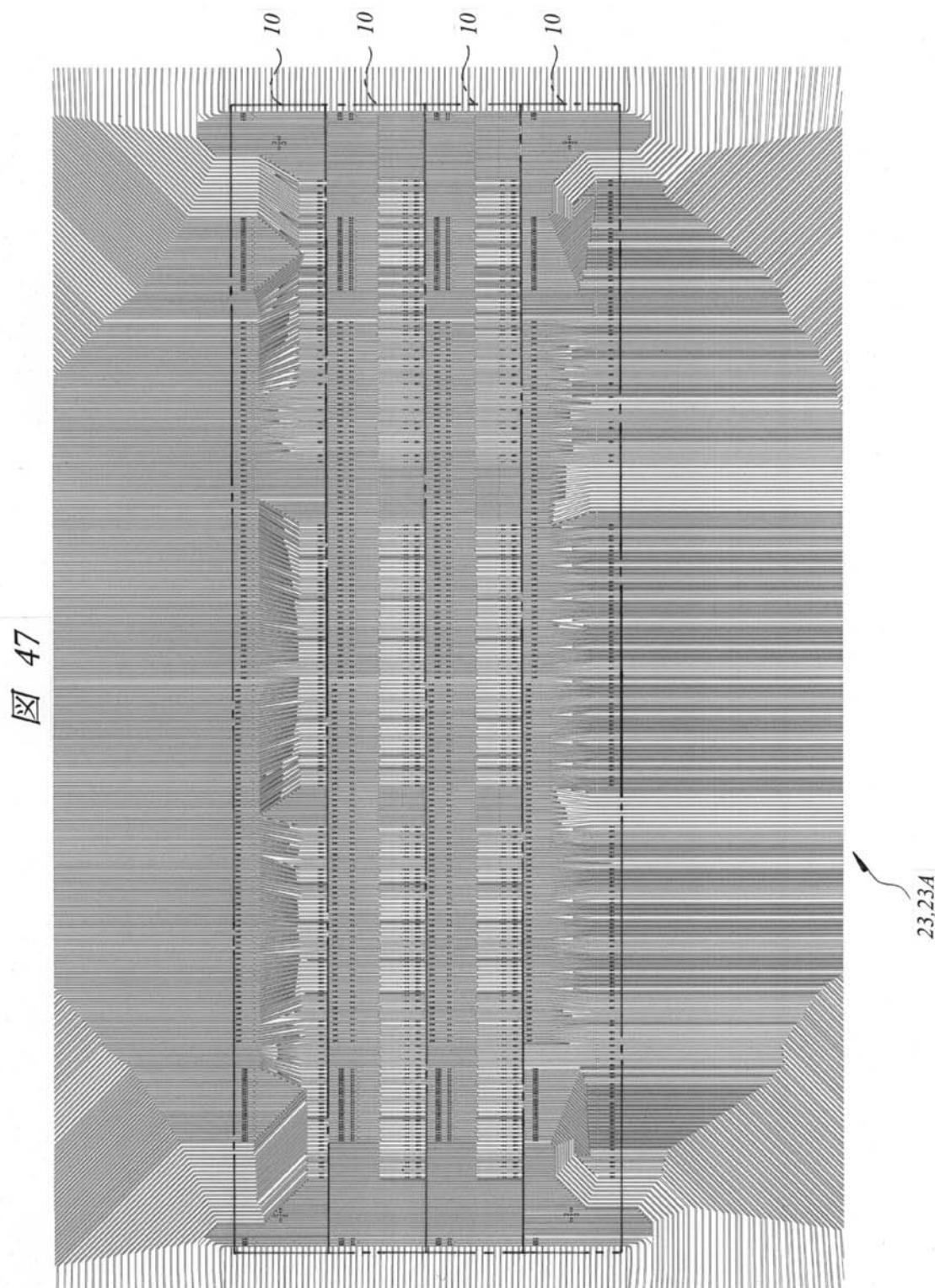

本実施の形態4では、長辺で対向して隣接し、連続する4個のチップ10に対して一度にプローブ検査を実施する。ここで、図46～図49は、薄膜シート2のうち、検査対象の4個のチップ10に対応する領域を示した要部平面図であり、図中において一点鎖線で囲まれている領域がチップ10の外形に相当する。また、図46～図49は、それぞれ、1層目の配線層に形成された配線23の平面パターン、図46の平面パターンに配線23と同じ配線層で形成された配線23Aを加えた平面パターン、2層目の配線層に形成された配線26の平面パターン、および図48の平面パターンに配線26と同じ配線層で形成された配線26Aを加えた平面パターンを図示したものである。

30

【0099】

本実施の形態4においても、前記実施の形態1と同様に、金属膜21A、21B(図7～図9参照)と電気的に接続された配線23の一部は、薄膜シート2の外周に向かって引き回され、多層配線基板1(図1および図2参照)に設けられた複数の受け部のうちの対応するものと電気的に接続される。また、他の配線23には配線26が接続され、各々の配線26は薄膜シート2の外周に向かって引き回され、多層配線基板1に設けられた複数の受け部のうちの対応するものと電気的に接続される。

【0100】

また、本実施の形態4においても、前記実施の形態1と同様に、平面でプローブ7A、7Bの近傍となる領域においては、配線23と、配線23と電気的に接続する配線26もしくは配線23とは電気的に接続しない配線26Aとが重なるように各配線の平面パターンを形成し、プローブ7A、7Bの上部には、配線23および配線26(もしくは配線26A)の両方が配置される平面パターンとする(図28および図29参照)。このような平面パターンとすることにより、本実施の形態4においてもプローブ7A、7Bの各々の上部にて薄膜シート2の厚さを均一にすることができる。それにより、プローブ検査時においては、押圧具9(図3参照)から加わる荷重が均等に各々のプローブ7A、7Bに加わるようにすることができる。その結果、プローブ7A、7Bの各々と対応するパッド11(図6および図10参照)とのコンタクト性を向上することが可能となる。

40

【0101】

50

また、本実施の形態 4 においても、前記実施の形態 1 と同様に、薄膜シート 2 中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線 23、23A、26、26A のパターンを形成する。このように、薄膜シート 2 中の各配線層において、配線の配置間隔および配線の配置密度が均一になるように配線のパターンを形成することにより、薄膜シート 2 のうち特にプローブ 7A、7B の近傍では剛性および厚さを均一にすることができます。それにより、プローブ 7A、7B の近傍では、薄膜シート 2 に皺および撓みが発生することを防ぐことができるので、プローブ 7A、7B の各々と対応するパッド 11 とのコンタクト性を向上することが可能となる。

#### 【0102】

上記のような本実施の形態 4 によっても前記実施の形態 1 と同様の効果を得ることができます。 10

#### 【0103】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【0104】

本発明の半導体集積回路装置の製造方法およびプローブカードは、半導体集積回路装置の製造工程におけるプローブ検査工程に広く適用することができる。 20

#### 【図面の簡単な説明】

#### 【0105】

【図 1】本発明の実施の形態 1 であるプローブカードの要部断面図である。

【図 2】本発明の実施の形態 1 であるプローブカードの下面の要部平面図である。

【図 3】図 2 中の A - A 線に沿った断面図である。

【図 4】本発明の実施の形態 1 であるプローブカードの要部断面図である。

【図 5】本発明の実施の形態 1 であるプローブカードを用いてプローブ検査を行う対象の半導体チップ領域が形成された半導体ウエハの平面図である。 30

【図 6】本発明の実施の形態 1 であるプローブカードを用いてプローブ検査を行う対象の半導体チップの平面図である。

【図 7】本発明の実施の形態 1 であるプローブカードを形成する薄膜シートの要部平面図である。 30

【図 8】図 7 中の B - B 線に沿った断面図である。

【図 9】図 7 中の C - C 線に沿った断面図である。

【図 10】本発明の実施の形態 1 であるプローブカードを用いてプローブ検査を行う対象の半導体チップの平面図である。 40

【図 11】本発明の実施の形態 1 であるプローブカードを形成する薄膜シートの要部平面図である。

【図 12】本発明の実施の形態 1 であるプローブカードを用いてプローブ検査を行う対象の半導体チップに設けられたパッド上にてプローブが接触する位置を示した要部平面図である。 40

【図 13】本発明の実施の形態 1 であるプローブカードを形成する薄膜シートの要部平面図である。

【図 14】本発明の実施の形態 1 であるプローブカードを形成する薄膜シートの要部平面図である。

【図 15】図 14 中の D - D 線に沿った断面図である。

【図 16】図 14 中の E - E 線に沿った断面図である。

【図 17】本発明の実施の形態 1 であるプローブカードを形成する薄膜シートの製造工程を説明する要部断面図である。

【図 18】図 17 に続く薄膜シートの製造工程中の要部断面図である。

【図 19】図 18 に続く薄膜シートの製造工程中の要部断面図である。 50

【図20】図19に続く薄膜シートの製造工程中の要部断面図である。

【図21】図20に続く薄膜シートの製造工程中の要部断面図である。

【図22】図21に続く薄膜シートの製造工程中の要部断面図である。

【図23】図22に続く薄膜シートの製造工程中の要部断面図である。

【図24】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図25】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図26】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

10

【図27】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図28】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図29】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図30】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図31】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

20

【図32】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図33】本発明の実施の形態1であるプローブカードを形成する薄膜シートの要部平面図である。

【図34】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図35】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図36】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部断面図である。

30

【図37】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図38】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図39】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図40】本発明の実施の形態2であるプローブカードを形成する薄膜シートの要部平面図である。

【図41】本発明の実施の形態3であるプローブカードを形成する薄膜シートの要部平面図である。

40

【図42】本発明の実施の形態3であるプローブカードを形成する薄膜シートの要部平面図である。

【図43】本発明の実施の形態4であるプローブカードを用いてプローブ検査を行う対象の半導体チップの平面図である。

【図44】図43に示した半導体チップに形成されたパッドの斜視図である。

【図45】図43に示した半導体チップの液晶パネルへの接続方法を示す要部断面図である。

【図46】本発明の実施の形態4であるプローブカードを形成する薄膜シートの要部平面図である。

【図47】本発明の実施の形態4であるプローブカードを形成する薄膜シートの要部平面

50

図である。

【図48】本発明の実施の形態4であるプローブカードを形成する薄膜シートの要部平面図である。

【図49】本発明の実施の形態4であるプローブカードを形成する薄膜シートの要部平面図である。

【符号の説明】

【0106】

- |                     |                   |    |  |

|---------------------|-------------------|----|--|

| 1                   | 多層配線基板（第1配線基板）    |    |  |

| 2                   | 薄膜シート（第1シート）      |    |  |

| 3                   | プランジャ             | 10 |  |

| 3 A                 | ばね                |    |  |

| 4                   | 押さえリング            |    |  |

| 5                   | 開口部               |    |  |

| 6                   | 接着リング             |    |  |

| 7、7 A、7 B、7 C、7 D   | プローブ（接触端子）        |    |  |

| 8                   | ポゴ座               |    |  |

| 9                   | 押圧具（押圧機構）         |    |  |

| 10                  | チップ（チップ領域）        |    |  |

| 11、12               | パッド（テストパッド（第1電極）） |    |  |

| 14、15               | 画素電極              | 20 |  |

| 16、18               | ガラス基板             |    |  |

| 17                  | 液晶層               |    |  |

| 21 A、21 B、21 C、21 D | 金属膜               |    |  |

| 22、25、27            | ポリイミド膜            |    |  |

| 23                  | 配線（第2配線）          |    |  |

| 23 A                | 配線（第3配線）          |    |  |

| 24、28               | スルーホール            |    |  |

| 26                  | 配線（第2配線）          |    |  |

| 26 A                | 配線（第3配線）          |    |  |

| 31                  | ウエハ               | 30 |  |

| 32                  | 酸化シリコン膜           |    |  |

| 33                  | 穴                 |    |  |

| 34                  | 酸化シリコン膜           |    |  |

| 35                  | 導電性膜              |    |  |

| 37、38、42、43         | 導電性膜              |    |  |

| C H D               | カードホルダ            |    |  |

| F G R               | フロッギング            |    |  |

| I A                 | 中心領域              |    |  |

| O A                 | 外周領域              |    |  |

| P G P               | ポゴピン              | 40 |  |

| S B                 | 補助基板              |    |  |

| T H D               | テスタヘッド            |    |  |

| W H                 | ウエハ               |    |  |

【図1】

【図2】

図1

【図3】

【図4】

図3

図1

【図5】

図2

【図6】

図4

図4

【図7】

【図9】

【図8】

【図10】

【図11】

## 【図12】

図 12

【図13】

☒ 13

【図14】

☒ 14

【図15】

15

【図16】

图 16

【図17】

图 17

【図18】

【図19】

【図20】

【図21】

【図24】

【図22】

【図23】

【図25】

### 【図26】

### 【図27】

### 【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図39】

【図41】

【図43】

図43

【図44】

図44

【図45】

図45

【図46】

図46

【図 37】

【図 3 8】

【図 4 0】

【図 4 2】

図 42

【図 47】

【図 4 8】

図 48

【図 49】

図 49

---

フロントページの続き

(72)発明者 名取 巍

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 滝谷 亮一

(56)参考文献 特開2005-302917 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/66

G 01 R 1/073

G 01 R 31/26