(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4815572号

(P4815572)

(45) 発行日 平成23年11月16日(2011.11.16)

(24) 登録日 平成23年9月9日(2011.9.9)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO3L 7/093   | (2006.01) |

| HO3L 7/08    | (2006.01) |

| HO3L 7/10    | (2006.01) |

|              | HO3L 7/08 |

|              | HO3L 7/10 |

|              | HO3L 7/10 |

請求項の数 5 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-530809 (P2007-530809)  |

| (86) (22) 出願日 | 平成17年8月30日 (2005.8.30)        |

| (65) 公表番号     | 特表2008-512920 (P2008-512920A) |

| (43) 公表日      | 平成20年4月24日 (2008.4.24)        |

| (86) 国際出願番号   | PCT/IB2005/052840             |

| (87) 国際公開番号   | W02006/030335                 |

| (87) 国際公開日    | 平成18年3月23日 (2006.3.23)        |

| 審査請求日         | 平成20年8月27日 (2008.8.27)        |

| (31) 優先権主張番号  | 04104413.2                    |

| (32) 優先日      | 平成16年9月13日 (2004.9.13)        |

| (33) 優先権主張国   | 欧洲特許庁 (EP)                    |

|           |                                                          |

|-----------|----------------------------------------------------------|

| (73) 特許権者 | 510000633<br>エスティー・エリクソン、ソシエテ、アノニム                       |

|           | スイス国プラン-レ-ズアト、シュマン、デュ、シャン-デ-フィュ、39                       |

| (74) 代理人  | 100117787<br>弁理士 勝沼 宏仁                                   |

| (72) 発明者  | ビンフリット、ビルト<br>オランダ国5656、アーアー、アインドーフェン、ケアオブ、プロフ、ホルストラーン、6 |

| 審査官       | 上田 智志                                                    |

最終頁に続く

(54) 【発明の名称】補償されたフェーズロックループ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

フェーズロックループ回路であって、

a) ループフィルタ手段と、

b) 前記ループフィルタ手段に結合された電圧制御発振器手段と、

c) 前記ループフィルタ手段に結合されて、前記フェーズロックループ回路の閉ループ動作中に所定のオフセット電圧を前記ループフィルタ手段に供給する電圧発生器手段と、

d) 前記電圧制御発振器手段の特性に従って前記オフセット電圧を設定する設定手段と、

e) 補償電流を発生し、かつ前記補償電流を前記ループフィルタ手段の入力に供給して前記フェーズロックループ回路の位相検出器手段の位相誤差を補償するための補償手段であって、入力変調周波数を前記補償電流に変換するための第1の変換手段を備える補償手段と、

を備えるフェーズロックループ回路。

## 【請求項 2】

前記電圧発生器手段と前記ループフィルタ手段の入力抵抗器との間に直列に結合された抵抗器手段をさらに備え、前記補償手段が、前記抵抗器手段に並列に接続された電流源を備える、請求項1に記載のフェーズロックループ回路。

## 【請求項 3】

前記入力変調周波数を入力位相信号に変換するための第2の変換手段をさらに備える、

10

20

請求項 1 または 2 に記載の フェーズロックループ回路。

【請求項 4】

前記入力変調周波数を、前記フェーズロックループ回路に設けられた分数分割器の分割係数に変換するための第 3 の変換手段をさらに備える、請求項 1 ないし 3 のいずれか一項に記載の フェーズロックループ回路。

【請求項 5】

前記第 3 の変換手段の入力に接続された事前補償手段をさらに備える、請求項 4 に記載の フェーズロックループ回路。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、フェーズロックループ (PLL) 回路およびそのような PLL 回路を補償する方法に関し、特に一次の PLL ループの整定時間を減少させる。ここで使用される用語「一次の PLL」は、ループフィルタに積分機能 (レギュレーターム) を有しない PLL を指す。

【背景技術】

【0002】

フェーズロックループ回路の出力する信号は、入力信号と同期している。基本的に、フェーズロックループ回路の生成する出力信号は、周波数の点では入力信号を追跡し、かつ入力信号に対して一定の位相関係を示す。通常、PLL 回路が備えるものは、位相 / 周波数検出器、ループフィルタ例えば低域通過フィルタ、電圧制御発振器 (VCO)、および、必要であれば、周波数分割器である。位相検出器に入力されるクロック周波数と VCO の出力周波数が等しければ、周波数分割器は必要でない。

20

【0003】

移動体通信用グローバルシステム (GSM) 標準では、送信用 VCO のロックする能力は、100 MHz ステップを 90 Hz よりも良い精度に 200 マイクロ秒未満でロックできなければならない。この理由は、使用中でないとき送信サブシステムをオフにして電流消費 (ドレイン) を最小限にし、かつオンにするとき素早く再起動する必要があるからである。その上、重要なことは、この仕様が満たされる範囲が相当な温度範囲および部品ばらつきにわたることである。従来のループフィルタ構成が不十分であることがあるのは、積分レギュレータが遅いからである。望ましい PLL 帯域幅が積分レギュレータの可能な速度を制限する理由は、ループで十分な安定余裕度が必要であるからである。PLL の帯域幅を制限しているのは、PLL で行われるフィルタリングの要求条件である。

30

【0004】

従来の PLL 回路は、電荷ポンプ位相検出器を備え、この電荷ポンプが充放電するのは、低域通過フィルタ中のコンデンサであり、この充放電は進みまたは遅れ位相信号に依存している。そして、低域通過フィルタが除去するのは、出力電圧信号の高周波成分および雑音であり、これらは位相差に対応している。低域通過フィルタは位相差信号を平滑化して、これを制御電圧に変換する。この制御電圧は、VCO に供給されて発振周波数を制御する。VCO は、PLL 回路の最もクリティカルな部品である。出力周波数の制御電圧依存性を決定するのは、VCO の変換利得  $V_{vco}$  である。PLL 回路は負帰還ループであることにより、PLL 回路は機能して、位相検出器に供給された発振信号と周波数入力信号の位相差を最小限にする。PLL 回路がロックイン点すなわち定常状態に達したとき、これら 2 つの信号の位相は互いに一致している。すなわち、VCO 出力信号の発振位相および周波数は、周波数入力信号の位相および周波数と同じになる。

40

【0005】

理想的な場合に、周波数入力信号の入力位相  $i$ 、位相検出器の出力の誤差位相  $e$  および VCO の出力位相  $o$  がゼロであるのは、整定モードまたは状態であり、これは、また、ロックモードまたは状態、または定常モードまたは状態とも呼ばれることがある。

【0006】

50

「フェーズロック技術」、F. M. Gardener, Wiley and Sons、New York、1979年、第2版、48頁で、PLL回路は「2次ループ」と名前がつけられている。この名前が関係しているのは、開ループのラプラス伝達関数の積分項  $1/s$  の数である。特に、開ループ伝達関数は、次のように表すことができる。

【数1】

$$G(s) = K_p Z_{LF} K_0 / s \quad (1)$$

ここで、 $Z_{LF} = (R + 1/sC) F_r(s)$  であるので、式(1)は次のように改める

10

ことができる。

$$G(s) = K_p R K_0 F_r(s) (1/s + 1/(s^2 R C)) \quad (2)$$

ここで、 $F_r(s)$  は、リップルフィルタの伝達関数を示し、このフィルタはループフィルタに含まれてもよい。 $Z_{LF}$  は、ループフィルタのインピーダンスを示し、 $R$  が示す抵抗器の抵抗および  $C$  が示すコンデンサのキャパシタンスはループフィルタの  $R C$  積分回路のものであり、 $K_p$  は、位相検出器の伝達係数を示し、 $K_0$  は、VCOの伝達係数を示し、また、 $s$  はラプラス演算子 ( $s = j\omega = j2\pi f$ ) に対応する。一次ループが積分コンデンサ  $C$  を含まないことにより、第2の項  $1/(s^2 R C)$  は、一次ループでは省略される。リップルフィルタの伝達関数を無視して、したがって  $F_r = 1$  と設定して、一次ループの開ループ伝達関数は、次式に変えることができる。

20

【数3】

$$G(s) = K_p R K_0 / s \quad (3)$$

この関数は、漸近線を表し、この漸近線は、0 dB軸と角周波数  $\omega_A = K_p R K_0$  で交差する。

【0007】

しかし、一次ループはどんな積分挙動も示さないために、非常に大きな定常状態位相誤差が得られる。積分挙動を有する二次ループは、そのような定常状態位相誤差を無くすることができるが、整定速度減少を犠牲にして無くすることができる。

30

【0008】

文献米国特許第6,157,271号が開示するPLL回路についている高速調整機能は、広い周波数範囲にわたっている。コントローラが発生させるデジタル開ループ周波数制御信号はデジタル・アナログ変換器(DAC)に供給され、このDACが可変DC基準電位を生成する。この基準電位が開ループ調整電圧として使用され位相検出器の出力に加えられて、PLL回路の捕捉時間(acquisition time)を減少させる。

【発明の開示】

【発明が解決しようとする課題】

【0009】

したがって、本発明の目的は、改善されたPLL回路および補償方法を提供することであり、これらによって、定常状態位相誤差および整定時間を減少させることができる。

40

【課題を解決するための手段】

【0010】

この目的の達成は、請求項1で請求されるようなPLL回路および請求項12で請求されるような補償方法によって行われる。

【0011】

したがって、オフセットすなわち補償電圧のループフィルタ手段への供給は、閉ループ動作の特定の時間位相で行われる。このオフセット電圧の電圧値は、電圧制御発振器手段の特性に従って設定される。適切に選ばれたオフセット電圧によって、このオフセット電

50

圧の機能は二次ループの積分素子の電圧に似ており、可能なことは、一次ループの整定を、非常に大きな定常状態位相誤差のない状態で行うことである。一次ループに応用されたとき、提案された解決策がもたらすループ整定は、二次ループよりもはるかに高速である。このことは、多くの用途で非常に有用である。

【0012】

さらに、補償手段を設けて、補償電流を発生し、かつこの補償電流をループフィルタ手段の入力に供給して、PLL回路の位相検出器手段の位相誤差を補償することができる。それによって、残存する定常状態位相誤差の不利をさらに減少させることができる。補償手段が備えることができる抵抗器手段は、電圧発生器手段とループフィルタ手段の入力抵抗器との間に直列に結合されている。電流源は、この抵抗器手段に並列に接続されてもよい。それによって、増加した電流を供給することができるので、電流源からの漏れ電流はいっそう危険でなくなる。

10

【0013】

設定手段の構成は、オフセット電圧の設定を電圧制御発振器の入力に要求される値にして、所望の出力周波数を発生させるように構成されてもよい。したがって、定常状態で、オフセット電圧の設定は、所望の周波数のためにVCO曲線に従って要求される値に大体合っているので、定常状態位相誤差を相当に減少させることができる。

【0014】

さらに、設定手段の構成は、電圧制御発振器の特性曲線の事前選択を電圧制御発振器の所望の出力周波数に基づいて行うように構成されてもよい。それによって、電圧制御発振器の変換特性は、所望の周波数に適合されて、定常状態位相誤差を最小限にすることができる。

20

【0015】

特に、設定手段の構成は、電圧制御発振器を制御してVCO特性をシフトさせるように構成されてもよい。VCO特性をシフトさせることができると有利な点は、電圧制御発振器の調整すなわち制御電圧の変化を妨げることができることである。VCO特性をシフトさせることは、VCOの前のループフィルタのDC設定値と同等とみなされる代替えである。

【0016】

送信機の周波数変調または位相変調は、様々なやり方でPLLシステムに投入され、上記の補償手段と組み合わせることができる。そのような組合せは、高度な補償手段となり、この高度な補償手段は、第1の変換手段を備えて入力変調周波数を補償電流に変換することができる。さらに、第2の変換手段を設けて、変調周波数を入力位相信号に変換することができる。これによって保証されることは、変調周波数が変化するとき誤差位相が変化しないことである。

30

【0017】

本発明の他の態様に従った代替えとして、第3の変換手段を設けて、入力変調周波数をPLL回路に設けられた分数分割器(fractional divider)の分割係数(divider factor)に変換することができる。この場合、第1および第2の変換手段が、追加して使用されてもよく、また変調周波数は、直接、位相検出手段に供給されてもよい。

40

【0018】

これから、本発明の説明は、好ましい実施形態に基づき、添付の図面を参照して行われる。

【発明を実施するための最良の形態】

【0019】

これから好ましい実施形態の説明はPLL回路に関連して行われ、このPLL回路はループフィルタ中に積分レギュレータを有しないが、補償手段を有し、減少した整定時間および減少した定常状態位相誤差を得る。

【0020】

50

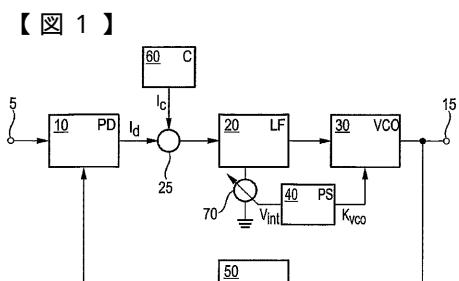

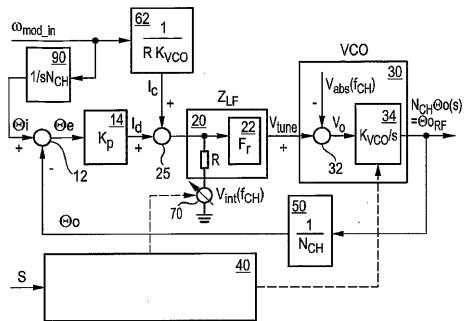

図1が示す模式的なブロック図のPLL回路は、好ましい実施形態に従っている。このPLL回路が備えるものは、位相検出器10、ループフィルタ20（低域通過フィルタであってもよい）、VCO30、および周波数分割器50である。さらに、補償回路60が設けられ、この補償回路60は、補償電流 $I_c$ を加算ノード25に供給する。この加算ノード25で、補償電流 $I_c$ は検出電流 $I_d$ に加えられる。この検出電流 $I_d$ は、位相検出器10で検出される位相差に対応している。

#### 【0021】

これに加えて、事前選択回路40が設けられ、事前選択するものは、望ましい周波数 $f_{c_H}$ のためのVCO曲線すなわち特性と、周波数分割器50の分割比 $N_{c_H}$ と、VCO30の変換利得 $K_{vco}$ と、またはこれらのパラメータの少なくとも一つの値である。さらに、事前選択回路40は電圧源70を制御し、この電圧源70は、ループフィルタ20と基準電位、例えば接地電位との間に接続されて、オフセット電圧 $V_{int}$ をループフィルタ20に導入する。

#### 【0022】

位相検出器10は位相差を検出するデバイスであり、この位相差は、入力端子5に供給された入力信号と、出力端子15に供給され周波数分割器50を経由して帰還されたVCO30の出力信号との間の位相差である。2つの入力信号の間の差に基づいて、位相検出器10は、位相差の量に比例した検出電流 $I_d$ を生成する。PLL回路で、入力端子5で受け取られる入力信号は、周波数基準信号に対応し、出力端子15の出力信号は、帰還または出力周波数信号に対応している。ループフィルタ20は、高周波成分および雑音を除去し、さらに、位相差信号を平滑化してこれを誤差すなわち制御電圧に変換する。この制御電圧は、VCO30に供給されて発振周波数を制御する。VCO30の利得 $K_{vco}$ は、電圧-周波数変換に関連している。制御電圧の周波数依存性は、VCO30のこの変換利得 $K_{vco}$ によって決定される。

#### 【0023】

事前選択回路40の構成は、電圧源70の電圧 $V_{int}$ をある値に設定するように構成されており、このある値は、VCO30の特性曲線が所望の周波数を発生させるために必要とする値である。または、代わりに、事前選択回路40は、VCO曲線をシフトさせる。PLL回路が整定されたとき、すなわち、制御ループの平衡状態が達成されたとき、小さな電圧誤差が依然としてループフィルタ20の中に残っている。この誤差のために、定常状態位相誤差が位相検出器10の出力に生じる。追加の補償電流 $I_c$ が供給されて、この誤差を補償する。

#### 【0024】

図2が示す模式的な回路図は、選択肢として、補償電流 $I_c$ をループフィルタ20の入力に加えるためのものである。したがって、図2の回路を使用して、図1の補償ブロック60と、加算ノード25と、ループフィルタブロック20との組合せの代わりをさせることができる。特に、図2に従って、ループフィルタ20は、インピーダンス $Z_{LF}$ を有し、伝達関数 $F_r$ を有するリップルフィルタ22を備える。このリップルフィルタ22は制御すなわち調整電圧 $V_{tune}$ を出力し、この電圧 $V_{tune}$ はVCO30に供給される。さらに、ループフィルタ20が備えるものは、直列接続の抵抗値（ $R - R_{div}$ ）の入力抵抗器と分割抵抗器 $R_{div}$ である。電圧源70は、入力抵抗器と分割抵抗器の直列接続と基準電位との間に直列に接続されている。さらに、電流源80が、分割抵抗器 $R_{div}$ に並列に接続されて、増加した補償電流 $I_c$ を供給し、この増加した補償電流 $I_c$ は、補償電流 $I_c$ に、直列接続の全抵抗 $R$ と分割抵抗器 $R_{div}$ の抵抗値との比を掛けることによって得られる。これによって、 $V_{int_0} = I_c \cdot R + V_{int}$ なるトータル電圧をループフィルタ20の入力にもたらすことができ、この入力には増加した電流 $I_c = I_c \cdot R / R_{div}$ が流れている。通常は補償電流 $I_c$ が小さな電流であることを考慮して、より適切なのは、増加した電流 $I_c$ および図2に示すような回路を使用することである。それにより、電流源80からの漏れ電流の危険性が減少する。

#### 【0025】

10

20

30

40

50

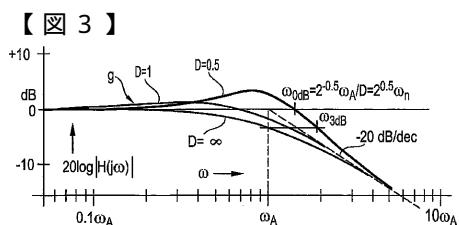

図3が示す模式的な周波数図は、様々なPLL回路の閉ループ挙動で、リップルフィルタが無視された状態( $F_r = 1$ )のものである。図3において、パラメータDは、2次の項のダンピングすなわち減衰係数を示す。パラメータ $\omega_n$ は、固有周波数に対応し、パラメータ $\omega_A$ はクリティカル周波数に対応し、クリティカル周波数は、 $-20\text{dB/dec}$ の傾斜の曲り角を定義する。D=0の曲線は、一次ループに対応し、この場合二次の項はゼロであり、したがって、また、好ましい実施形態に従ったPLL回路に対応する。

#### 【0026】

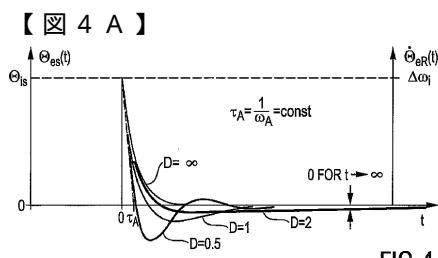

図4Aおよび4Bが示す模式的な信号すなわち波形図が表すのは、位相検出器10の出力の誤差位相の時間挙動で、それぞれ、入力位相 $i$ の位相ステップの場合および入力角周波数 $i$ の周波数ステップの場合のものである。図4Aから分かるように、位相ステップ応答 $\theta_e(s)(t)$ はダンピング係数Dに依存し、D=0の場合に速い整定を実現する。

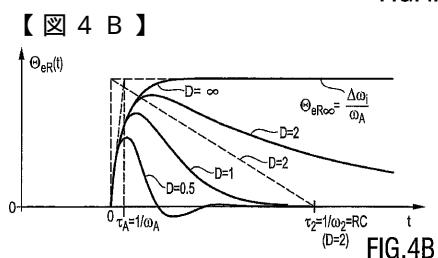

D=0は一次ループに対応している。図4Bによると、周波数ステップに対する位相応答 $\theta_e(t)$ は、ランプ(ramp)から始まってゼロに戻り、速度はダンピング係数Dに依存している。無限大のダンピング係数D=0の場合、誤差位相はゼロに戻らず、定常状態位相誤差 $\theta_e = \omega_i / \omega_A$ にとどまる。定常状態位相誤差 $\theta_e$ は、周波数ステップとクリティカル周波数の比に対応している。

#### 【0027】

好ましい実施形態によると、事前選択回路40および補償回路60の導入は、図4Aおよび4Bに示された位相誤差を補償するのに役立つ。

#### 【0028】

図5が示す模式的な機能ブロック図のPLL回路は、第1の好ましい実施形態に従ったものである。ここで、位相検出器の機能的な挙動は、減算ノード12と、変換関数すなわちパラメータ $K_p$ を有する変換ユニット14によって示され、パラメータ $K_p$ は、検出された位相誤差 $\theta_e$ から検出電流 $I_d$ への変換を表す。さらに、補償電流 $I_c$ は、変換ユニット62によって補償ユニット60中で発生され、この変換ユニットの関数は $1/RK_{vc_0}$ で表すことができる。 $1/RK_{vc_0}$ は、入力変調周波数 $m_{mod\_in}$ に基づいた補償電流 $I_c$ の発生を表している。ここで、Rはループフィルタ20の入力抵抗器の抵抗値に対応し、 $K_{vc_0}$ はVCO30の変換利得に対応している。また、入力位相 $i$ は、別の変換ユニット90を使用して入力変調周波数 $m_{mod\_in}$ から発生される。この変換ユニット90は、関数 $1/sN_{ch}$ に基づいた変換を行う。ここで、sはラプラス演算子を示す。補償電流 $I_c$ と検出電流 $I_d$ の和が、加算ノード25で得られ、ループフィルタ20に供給される。このループフィルタ20に制御可能電圧源70が接続されている。制御可能電圧源70は、オフセット電圧 $V_{int}(f_{ch})$ を、受け取られた送信チャネルのチャネル周波数 $f_{ch}$ の関数として発生する。

#### 【0029】

ループフィルタ20は、加算された電流を調整すなわち制御電圧 $V_{tune}$ に変換し、この電圧 $V_{tune}$ は、VCO30の減算ノード32に供給される。減算ノード32で、電圧 $V_{abs}(f_{ch})$ が引かれることで、制御電圧 $V_{tune}$ を増大し、したがって制御電圧 $V_{tune}$ の現実的な電圧範囲を与えることができるようになる。電圧差 $V_0$ はVCO30の変換ユニット34に供給され、変換ユニット34で電圧差 $V_0$ は出力信号 $N_{ch_0}(s)$ に変換される。この出力信号 $N_{ch_0}(s)$ は、RF信号の位相 $\theta_{RF}$ である。VCO出力信号は、周波数分割器50に供給され、ここで、VCO出力信号が $N_{ch}$ で割られて、帰還位相 $\theta_0$ が得られ、この帰還位相 $\theta_0$ が位相検出器で入力位相 $i$ と比較される。変調の $\theta_e$ に及ぼす影響は、 $F_r = 1$ 、かつ $K_{vc_0\_62} = K_{vc_0\_34}$ の場合には、無視できるほどである。

#### 【0030】

事前設定ユニットすなわち機能40で、VCO曲線のデジタル事前選択が、所望のチャネル周波数 $f_{ch}$ および値 $N_{ch}$ 、 $K_{vc_0}$ 、 $V_{abs}$ 、および $V_{int}(f_{ch})$ のために、開始信号Sに応答して行われる。したがって、オフセット電圧 $V_{int}$ およびVCO30の特性の調整が、所望の周波数 $f_{ch}$ に基づいて行われ、それによって、変調周

10

20

30

40

50

波数  $m o d\_i n$  の変化に応じて制御ループの整定速度が高められる。

【0031】

リップルフィルタ関数  $F_r(s)$  は、接地へのオーム接続のない R C フィルタであってもよい。ループフィルタ 20 の入力源および出力負荷は、高いオーム抵抗値を有する。したがって、図 4 B に示す残存定常状態位相誤差の不利点を最小限にすることは、オフセット電圧  $V_{i n t}$  および DC 補償電流  $I_c$  を導入することによって可能である。さらなる減少の達成は、補償電流  $I_c$  を追加して適用することによって行うことができる。図 5 に示す回路を使用して、例えば、移動端末またはそのようなもので周波数変調を行うことができる。位相誤差は、 $F_r(s) = 1$  という特殊な場合に、完全に補償することができる。変調周波数  $m o d\_i n$  が変化するとき、位相誤差  $\epsilon$  は変化しない。

10

【0032】

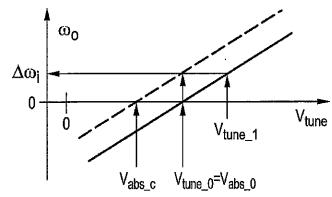

図 6 は、VCO 30 の変換機能の特性図であり、(この図において、) VCO 曲線が動いて、追加の電圧  $V_{a b s}$  を、 $I_c \cdot R$  なる値だけ、または  $V_{a b s} = V_{a b s}(f_{c H}) - m o d\_i n / K_{v c o}$  なる値だけ、シフトする。このシフトにより、周波数変化  $i$  は、初期制御電圧  $V_{t u n e\_0}$  で、シフトした曲線について満たされる。したがって、 $V_{t u n e\_0}$  から  $V_{t u n e\_1}$  の制御電圧の変化は、曲線の変化により必要でなくなる。これによって、定常状態誤差を防ぐことができる。VCO 曲線のシフトを達成することは、VCO 30 のような VCO に通常設けられるバラクタダイオード (varactor diode) の電圧を減少させることによって可能である。

20

【0033】

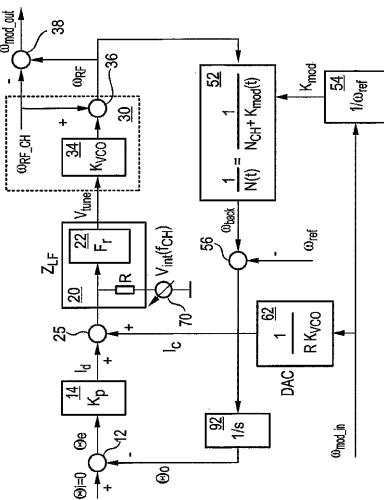

図 7 は、他の第 2 の好ましい実施形態の模式的な機能ブロック図を示す。この場合、変調周波数  $m o d\_i n$  は、図 5 の変換ブロック 90 を介して位相検出器の位相入力端子に供給されるのではなく、修正された分数分割器 52 に供給されている。新しい分数分割器 52 は、分割係数  $N = N_{c H} + K_{m o d}(t)$  を有する。ここで  $K_{m o d} = m o d\_i n / r e f$  である。係数  $K_{m o d}(t)$  は、時間変化係数であり分数  $N$  送信変調に使用される。分割器 52 での変調は、 $\epsilon$  の変調を補償するのに役立つ。したがって、ブロック 62 および 20 を介した VCO の変調は、PLL システムの動的挙動によって乱されない。分割器の変調は、図 5 のブロック 90 と同じことを行う。

【0034】

微小ステップサイズ用途では、分数  $N$  シンセサイザ、すなわち周波数発生器は、従来の整数  $N$  分割器の代わりに図 7 の分数  $N$  分割器 52 を使用することによって、整数  $N$  設計を改善する。この分数  $N$  分割器 52 は、VCO 30 の周波数を非整数  $N$  で実効的に割る。非整数  $N$  は、分数であってもよく、例えば  $N / (N + 1 - 3)$  のように大きくてもよい。結果として、周波数発生器は、例えば基準周波数  $r e f$  の  $N / (N + 3)$  のステップだけ進むことができるようになる。この改善が得られるのは、分数  $N$  分割器 52 で生じるスパurius 応答 (spurious response) の導入という犠牲を払ってである。分数  $N$  分割器 52 のアキュムレータの遅延誤差および周期的挙動によって、これらのスプール (spur) が起こる。しかし、ループフィルタ 20 は、これらのスプールを減衰させ、ループ帯域幅を制限してこれらのスプールを許容可能なレベルに減少させる。図 5 の整数  $N$  分割器と比較した結果は、図 5 のブロック 90 を省略することができるが、不要なスプールを導入するという犠牲を払うことになるということである。

30

【0035】

この第 2 の好ましい実施形態では、変調周波数  $m o d\_i n$  は、ベースバンドでガウス最小シフトキーイング (GMSK) 変調信号であってもよく、かつデジタル的に用意され、比決定ユニット 54 に供給される。比決定ユニット 54 で、変調周波数  $m o d\_i n$  と基準周波数  $r e f$  の比が計算されて、 $K_{m o d}$  が得られ、この  $K_{m o d}$  は分数  $N$  分割器 52 に供給される。さらに、図 5 の第 1 の好ましい実施形態と同様に、入力変調周波数  $m o d\_i n$  は変換ユニット 62 に供給され、変換ユニット 62 は DAC 機能を有して補償電流  $I_c$  を発生させることができる。この補償電流は加算ノード 25 に供給される。今、入力位相  $i = 0$  が、位相検出器 10 の減算ノード 12 に供給される。分数  $N$  分

40

50

割器 5 2 の出力に、帰還周波数  $b_{a c k}$  が得られ、第 2 の減算ノード 5 6 (これは、図 1 のブロック 1 0 に含まれてもよい) に供給される。第 2 の減算ノード 5 6 で、基準周波数  $r_{e f f}$  が引かれ、その差が変換ユニット 9 2 に供給される (数学的に見て位相は周波数にわたる積分であるので。また、 $1/s$  は積分を表す)。変換ユニット 9 2 で周波数差が位相差  $\theta$  に変換され、位相差  $\theta$  が第 1 の減算ノード 1 2 に供給される。

#### 【 0 0 3 6 】

VCO 3 0 で、制御電圧  $V_{t u n e}$  は変換ユニット 3 4 に直接供給される。今、変換ユニット 3 4 の構成は、制御電圧  $V_{t u n e}$  を周波数信号に変換するように構成されており、この周波数信号に、無線チャネル周波数  $R_F_{-C_H}$  が第 2 の加算ノード 3 6 で加えられて、無線周波数  $R_F$  が得られ、これが分数 N 分割器 5 2 に供給される。そして、無線チャネル周波数  $R_F_{-C_H}$  と無線周波数  $R_F$  の差を第 3 の減算ノード 3 8 で発生させることによって、PLL 回路の変調出力周波数が、VCO 3 0 で得られる。

10

#### 【 0 0 3 7 】

したがって、第 2 の好ましい実施形態に従った PLL 回路またはシステムは、分数 N シンセサイザおよび分数 N 送信変調器を備える。変調誤差の補償は、補償電流  $I_c$  で行うことができる。

#### 【 0 0 3 8 】

上の第 1 および第 2 の好ましい実施形態では、異なる種類の二点変調が使用され、さらにループフィルタの積分レギュレータの代わりに、所定の設定がループフィルタまたは電圧制御発信器に導入される。それによって、PLL 回路の動的整定時間を改善して、他の回路部品のための時間を得ることができ、この他の回路部分は、変調に要求される精度を保証することができる。補償電流  $I_c$  の実現は、図 2 に示す回路で行うことができる。さらに、図 6 に示す VCO 曲線の移動の実行は、設定すなわち事前選択回路 4 0 で行うことができる。この事前選択回路 4 0 は、図 7 に明示的に示されていないが、第 2 の好ましい実施形態に組み込んでもよい。

20

#### 【 0 0 3 9 】

代替えとして、第 3 の好ましい実施形態によると、分数 N 变調の使用は、事前補償を用い、かつ二点变調を用いずに行うことができる。この場合、図 7 の DAC 6 2 はもはや必要でなく、追加の事前補償ユニットが、比決定ユニット 5 4 の前に追加されなければならない。レギュレータを有する従来の高次の PLL 回路において、そのような追加の事前補償ユニットは、PLL 回路の特有のパラメータについて正確な知識を必要とする。しかし、例えば、上記の第 1 および第 2 の実施形態の事前選択ユニット 4 0 を使用することによって、レギュレータを不要にすることができるならば、この問題を大いに軽減することができる。したがって、事前選択回路 4 0 と事前補償付き分数 N 变調との組合せは、改善された回路拳動をもたらし、どんな二点变調も必要としない。

30

#### 【 0 0 4 0 】

$V_{i n t}$  の値および / または VCO 特性を得るための、事前選択ユニット 4 0 の設定値は、PLL 回路の製造中に格納またはプログラムされてもよい。代替えとして、制御関数の機能の実現は、デジタル機能またはソフトウェアルーチンとして行われ、これは整定が完了するまで可変にされてもよく、そして整定のとき固定される。同様に、VCO 特性曲線は、段階的な方法で、整定プロセス中に切り替えられてもよく、また PLL 回路が整定した後で固定されてもよい。

40

#### 【 0 0 4 1 】

留意されたいことであるが、本発明は、上の好ましい実施形態の特定の特徴に限定されない。オフセット電圧  $V_{i n t}$  の接続は、どんな種類のループフィルタに行われてもよく、そのループフィルタで定常状態誤差信号が発生される。さらに、どんな種類の電流発生および電流結合技術を使用して、補償電流  $I_c$  を、位相検出回路 1 0 の出力またはループフィルタ 2 0 の入力に加えてよい。したがって、好ましい実施形態は、添付の特許請求の範囲内で変化することができる。

#### 【 0 0 4 2 】

50

さらに、描かれた図面の図は、単に説明するものであり、制限するものでない。図面において、要素のいくつかの大きさが誇張され、また比例で描かれていないことは、説明の目的のためである。用語「備える」は、この説明および特許請求の範囲で使用される場合、他の要素またはステップを排除しない。単数名詞を参照する際（例えば「ひとつの」または「その」）、不定または定冠詞が使用されるが、何か他のことが特に述べられていない限り、これはその名詞の複数を含む。説明および特許請求の範囲での、第1、第2、第3などの用語は、類似した要素を区別するために使用されており、必ずしも連続した順序または年代順を述べるために使用されているわけではない。理解すべきことであるが、本明細書で説明した本発明の実施形態は、本明細書で説明または図示したもの以外の他の順序で動作することができる。さらに、好ましい実施形態、特定の構造および構成を本明細書で議論したが、様々な変更または修正を形または細部に加えることが、添付の特許請求の範囲を逸脱しないで、可能である。

10

【図面の簡単な説明】

【0043】

【図1】好ましい実施形態に従ったPLL回路を示す模式的なブロック図である。

【図2】好ましい実施形態に従ったループフィルタのオフセット電圧の補償電流の導入を示す模式的な回路図である。

【図3】PLL回路の閉ループ挙動を示す模式的な周波数図である。

【図4A】様々なPLLループの誤差位相挙動を示す模式的な波形図である。

20

【図4B】様々なPLLループの誤差位相挙動を示す模式的な波形図である。

【図5】第1の好ましい実施形態に従ったPLL回路を示す模式的な機能ブロック図である。

【図6】VCO曲線のシフトを示す模式的な図である。

【図7】第2の好ましい実施形態に従ったPLL回路を示す模式的な機能ブロック図である。

【符号の説明】

【0044】

5 入力端子

10 位相検出器

15 出力端子

30

20 ループフィルタ

25 加算ノード

30 電圧制御発振器(VCO)

40 事前選択回路

50 周波数分割器

60 補償回路

70 電圧源

22 リップルフィルタ

80 電流源

40

12 減算ノード

14 変換ユニット

32 減算ノード

34 変換ユニット

62 変換ユニット

90 変換ユニット

36 加算ノード

38 減算ノード

50

- 5 2 分数分割器

5 4 比決定ユニット

5 6 減算ノード

9 2 変換ユニット

FIG.1

FIG.2

FIG.3

FIG.4A

FIG.4B

【図5】

FIG.5

【図6】

FIG.6

【図7】

FIG.7

---

フロントページの続き

(56)参考文献 特開2000-165459(JP, A)

特開平02-067822(JP, A)

特開2001-028541(JP, A)

特開平04-196716(JP, A)

特開2004-080624(JP, A)

特開2001-339301(JP, A)

特開平07-202638(JP, A)

特開平04-252621(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/06-7/23,

H04L 7/033