### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5890656号 (P5890656)

最終頁に続く

(45) 発行日 平成28年3月22日(2016.3.22)

(24) 登録日 平成28年2月26日 (2016.2.26)

| (51) Int.Cl.                           |                                  | FI                  |                     |                     |          |        |  |

|----------------------------------------|----------------------------------|---------------------|---------------------|---------------------|----------|--------|--|

| GO9G 3/30                              | (2006.01)                        | GO9G                | 3/30                | J                   |          |        |  |

| GO9G 3/20                              | (2006.01)                        | GO9G                | 3/20                | 624B                |          |        |  |

| HO1L 51/50                             | (2006.01)                        | GO9G                | 3/20                | 611H                |          |        |  |

|                                        |                                  | GO9G                | 3/20                | 621F                |          |        |  |

|                                        |                                  | GO9G                | 3/20                | 622C                |          |        |  |

|                                        |                                  |                     |                     | 請求項の数 13            | (全 20 頁) | 最終頁に続く |  |

| (21) 出願番号 特願2011-245724 (P2011-245724) |                                  | (73) 特許権者 512187343 |                     |                     |          |        |  |

| (22) 出願日                               | 出願日 平成23年11月9日(2011.11.9)        |                     |                     | 三星ディスプレイ株式會社        |          |        |  |

| (65) 公開番号                              | 香号 特開2013-101265 (P2013-101265A) |                     |                     | Samsung Display Co. |          |        |  |

| (43) 公開日                               | 平成25年5月23日 (2013.5.23)           |                     |                     | , L t d.            |          |        |  |

| 審査請求日                                  | 平成26年9月29日                       | (2014.9.29)         | 大韓民国京畿道龍仁市器興区三星路1   |                     |          |        |  |

|                                        |                                  |                     | (74) 代理人 110000408  |                     |          |        |  |

|                                        |                                  |                     | 特許業務法人高橋・林アンドパートナーズ |                     |          |        |  |

|                                        |                                  |                     | (72) 発明者            | 石井 良                |          |        |  |

|                                        |                                  |                     | 神奈川県横浜市鶴見区菅沢町2-7 株式 |                     |          |        |  |

|                                        |                                  |                     | 会社サムスン横浜研究所内        |                     |          |        |  |

|                                        |                                  |                     | (72)発明者             | 発明者 勝瀬 浩文           |          |        |  |

|                                        |                                  |                     | 神奈川県横浜市鶴見区菅沢町2-7 株式 |                     |          |        |  |

|                                        |                                  |                     | 会社サムスン横浜研究所内        |                     |          |        |  |

|                                        |                                  |                     |                     |                     |          |        |  |

# (54) 【発明の名称】電気光学装置の駆動方法および電気光学装置

# (57)【特許請求の範囲】

# 【請求項1】

第1電源と、第2電源と、複数のデータ線と、複数の走査線と、複数の信号線と、複数 の制御線と、前記データ線と前記走査線とが交わる領域に設けられる複数の画素回路と、 を備え、

前記画素回路は、

前記第1電源から前記第2電源へ電流が流れることにより発光する発光素子と、

第1端子が前記第1電源側に、ゲートが第2ノードに、第2端子が前記第2電源側にそ れぞれ接続されている第1トランジスタと、

第1端子が前記第2ノードに、ゲートが前記信号線に、第2端子が前記第1トランジス タの前記第2端子にそれぞれ接続されている第2トランジスタと、

第1端子がデータ線に、ゲートが走査線に、第2端子が第1ノードにそれぞれ接続され ている第3トランジスタと、

第1端子が前記第1トランジスタの前記第2端子に、ゲートが前記制御線に、第2端子 が前記発光素子のアノードにそれぞれ接続されている第4トランジスタと、

一の端子が前記第1ノードに、他の端子が前記第2ノードに接続されているキャパシタ と、

### を備え、

前記発光素子が全ての前記画素回路において1フレーム中の所定の期間に一斉に発光す る電気光学装置において、

20

<u>前記第4トランジスタをオフすることによって</u>前記発光素子を非発光状態にして、前記信号線に印加するパルスの変化により前記第2トランジスタをオンする第1ステップと、

前記第 2 トランジスタ<u>のオンが維持された状態で</u>、前記<u>複数の</u>走査線を順次排他的に選択し、選択された前記走査線にゲートが接続されている前記第 3 トランジスタをオンして、対応するデータ電圧を前記データ線から前記第 3 トランジスタを介して前記第 1 ノードに書き込む第 2 ステップと、

を備えることを特徴とする、電気光学装置の駆動方法。

## 【請求項2】

前記第2ステップの後に、全ての前記走査線を同時に選択して前記第3トランジスタをオンすることにより所定の基準電圧を前記データ線から前記第3トランジスタを介して前記第1ノードに書き込む第3ステップをさらに備えることを特徴とする、請求項1に記載の電気光学装置の駆動方法。

### 【請求項3】

前記第3ステップの後に、前記第1電源から前記第2電源へ電流を流して、前記第2ノードの電圧値に対応する明るさで前記発光素子を発光させる第4ステップをさらに備えることを特徴とする、請求項2に記載の電気光学装置の駆動方法。

#### 【請求項4】

前記第4ステップにおいて、前記制御線に印加するパルスの変化により前記第4トランジスタをオンさせることで前記第1電源から前記第2電源に電流を流すことを特徴とする、請求項3に記載の電気光学装置の駆動方法。

### 【請求項5】

前記第4ステップにおいて、前記第2電源の電位を前記第1電源の電位より低くすることで前記第1電源から前記第2電源に電流を流すことを特徴とする、請求項3に記載の電気光学装置の駆動方法。

#### 【請求項6】

前記第3ステップにおいて、前記第2トランジスタを全ての画素回路において一斉にオフさせることを特徴とする、請求項2に記載の電気光学装置の駆動方法。

#### 【請求項7】

前記第2ステップにおいて、前記第2トランジスタを前記走査線毎に順次オフさせることを特徴とする、請求項2に記載の電気光学装置の駆動方法。

### 【請求項8】

前記電気光学装置は、複数のリセット線と、リセット電源と、をさらに備え、

前記画素回路は、第1端子が前記第2ノードに、ゲートが前記リセット線に、第2端子が前記リセット電源にそれぞれ接続されている第5トランジスタをさらに備え、

前記第4ステップの後に、前記リセット線に印加するパルスの変化により前記第5トランジスタをオンさせることで前記第2ノードを前記リセット電源に接続して所定のリセット電位に設定することを特徴とする、請求項3に記載の電気光学装置の駆動方法。

### 【請求項9】

前記電気光学装置は、複数のリセット線をさらに備え、

前記画素回路は、第1端子が前記第2ノードに、ゲートが前記リセット線に、第2端子が前記データ線にそれぞれ接続されている第6トランジスタをさらに備え、

前記第4ステップの後に、前記データ線の電位を所定のリセット電位に設定し、前記リセット線に印加するパルスの変化により前記第6トランジスタをオンさせることで前記第2ノードを前記データ線に接続して前記所定のリセット電位に設定することを特徴とする、請求項3に記載の電気光学装置の駆動方法。

# 【請求項10】

第1電源と、第2電源と、複数のデータ線と、複数の走査線と、複数の信号線と、<u>複数</u>の制御線と、前記データ線と前記走査線とが交わる領域に設けられる複数の画素回路と、 を備え、

前記画素回路は、

10

20

30

40

前記第1電源から前記第2電源へ電流が流れることにより発光する発光素子と、

第1端子が前記第1電源側に、ゲートが第2ノードに、第2端子が第2トランジスタの ドレインおよび前記第2電源側にそれぞれ接続されている第1トランジスタと、

第1端子が前記第2ノードに、ゲートが前記信号線に、第2端子が前記第1トランジス タの前記第2端子にそれぞれ接続されている第2トランジスタと、

第1端子がデータ線に、ゲートが走査線に、第2端子が第1ノードにそれぞれ接続され ている第3トランジスタと、

第1端子が前記第1トランジスタの前記第2端子に、ゲートが前記制御線に、第2端子 が前記発光素子のアノードにそれぞれ接続されている第4トランジスタと、

一の端子が前記第1ノードに、他の端子が前記第2ノードに接続されているキャパシタ と、

を備え、

前記発光素子が全ての前記画素回路において1フレーム中の所定の期間に一斉に発光し

前記第4トランジスタをオフすることによって前記発光素子を非発光状態にして、前記 信号線に印加するパルスの変化により前記第2トランジスタがオンし、

前記第2トランジスタのオンが維持された状態で、前記複数の走査線を順次排他的に選 択し、選択された前記走査線にゲートが接続されている前記第3トランジスタをオンして 、対応するデータ電圧を前記データ線から前記第3トランジスタを介して前記第1ノード に書き込む

ことを特徴とする、電気光学装置。

#### 【請求項11】

複数のリセット線と、リセット電源と、をさらに備え、

前記画素回路は、第1端子が前記第2ノードに、ゲートが前記リセット線に、第2端子 が前記リセット電源にそれぞれ接続されている第5トランジスタをさらに備えることを特 徴とする、請求項10に記載の電気光学装置。

# 【請求項12】

複数のリセット線をさらに備え、

前記画素回路は、第1端子が前記第2ノードに、ゲートが前記リセット線に、第2端子 が前記データ線にそれぞれ接続されている第6トランジスタをさらに備えることを特徴と する、請求項10に記載の電気光学装置。

【請求項13】

前記第1トランジスタ、前記第2トランジスタ、および前記第3トランジスタは、いず れもPチャネル型のMOSFET (Metal - Oxide - Semiconducto r Field-Effect Transistor)であることを特徴とする、請求 項10に記載の電気光学装置。

【発明の詳細な説明】

# 【技術分野】

[0001]

本発明は、電気光学装置の駆動方法および電気光学装置に関する。

#### 【背景技術】

[0002]

テレビ受像機の表示部には、透過型あるいは半透過反射型の液晶パネルを備えた液晶表 示装置や、有機EL素子が構成された有機EL表示パネルを備えた有機EL表示装置が広 く用いられている。このような電気光学装置は、近年では高解像度化や三次元画像の表示 に伴って、画素回路の駆動の高速化が求められている。

# [0003]

駆動の高速化に伴い、画素回路中の駆動トランジスタのスレッショルド電圧補償時間お

20

10

30

40

よびデータ書き込み時間を十分に取ることができず、表示品位の劣化が大きな問題となっている。これらの問題を解決するためには、画素回路のトランジスタ数、キャパシタ数の増加が避けられなかったが、画素回路の素子数を削減した技術として、例えば特許文献 1 , 2 等がある。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2010-113230号公報

【特許文献2】特開2005-099773号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

しかし、これらの技術では、駆動トランジスタのスレッショルド電圧補償と画素回路のデータ書き込みと基準電位書き込みとを各走査線選択期間中に行う必要があるので、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に取ることができず、表示品位の劣化が避けられないという問題があった。この問題は、特に三次元画像表示のために面順次駆動を行う場合、走査線選択期間がさらに短くなるため、顕著となる。

[0006]

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能な、新規かつ改良された電気光学装置の駆動方法および電気光学装置を提供することにある。

【課題を解決するための手段】

[0007]

上記課題を解決するために、本発明のある観点によれば、第1電源と、第2電源と、複数のデータ線と、複数の走査線と、複数の信号線と、データ線と走査線とが交わる領域に設けられる複数の画素回路と、を備え、画素回路は、第1電源から第2電源へ電流が流れることにより発光する発光素子と、第1端子が前記第1電源側に、ゲートが第2ノードに、第2端子が前記第1トランジスタと、第1端子が前記第2カードに、ゲートが前記信号線に、第2端子が前記第1トランジスタと、第1端子が前記第2ノードに、ゲートが前記信号線に、第2端子がデータ線に、ゲートが記第2ノードにそれぞれ接続されている第3トランジスタと、ゲーーの端子にで前記第1ノードに接続されているキャパシタと、を備えるにの前記第1ノードに、他の端子が前記第2ノードに接続されているキャパシタと、を備えるとを特徴とする、電気光学装置の駆動方法が提供される

[00008]

かかる方法によれば、発光素子を非発光状態にして、信号線に印加するパルスの変化により第2トランジスタをオンした後に、走査線を順次排他的に選択し、選択された走査線にゲートが接続されている第3トランジスタをオンして、選択された画素に対応するデータ電圧をデータ線から第3トランジスタを介して第1ノードに書き込む。その結果、本発明のある観点による電気光学装置の駆動方法は、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能となる。

[0009]

10

20

30

10

20

30

40

50

第2ステップの後に全ての走査線を同時に選択して第3トランジスタをオンすることにより所定の基準電圧をデータ線から第3トランジスタを介して第1ノードに書き込む第3ステップをさらに備えていてもよい。

#### [ 0 0 1 0 ]

第3ステップの後に、第1電源から第2電源へ電流を流して、第2ノードの電圧値に対応する明るさで発光素子を発光させる第4ステップをさらに備えていてもよい。

#### [0011]

電気光学装置は、複数の制御線をさらに備え、画素回路は、第1端子が前記第1トランジスタの前記第2端子に、ゲートが前記制御線に、第2端子が前記発光素子のアノードにそれぞれ接続されている第4トランジスタをさらに備え、第4ステップにおいて、制御線に印加するパルスの変化により第4トランジスタをオンさせることで第1電源から第2電源に電流を流すようにしてもよい。

## [0012]

第4ステップにおいて、第2電源の電位を第1電源の電位より低くすることで第1電源から第2電源に電流を流すようにしてもよい。

#### [0013]

第 3 ステップにおいて、第 2 トランジスタを全てのラインで一斉にオフさせるようにしてもよい。

### [0014]

第 3 ステップにおいて、第 2 トランジスタをライン毎に順次オフさせるようにしてもよい。

#### [0015]

電気光学装置は、複数のリセット線と、リセット電源と、をさらに備え、画素回路は、第 1 端子が第 2 ノードに、ゲートがリセット線に、第 2 端子がリセット電源にそれぞれ接続されている第 5 トランジスタをさらに備え、第 4 ステップの後に、リセット線に印加するパルスの変化により第 5 トランジスタをオンさせることで第 2 ノードをリセット電源に接続して所定のリセット電位に設定するようにしてもよい。

#### [0016]

電気光学装置は、複数のリセット線をさらに備え、画素回路は、第1端子が第2ノードに、ゲートがリセット線に、第2端子がデータ線にそれぞれ接続されている第6トランジスタをさらに備え、第4ステップの後に、データ線の電位を所定のリセット電位に設定し、リセット線に印加するパルスの変化により第6トランジスタをオンさせることで第2ノードをデータ線に接続して所定のリセット電位に設定するようにしてもよい。

### [0017]

また、上記課題を解決するために、本発明の別の観点によれば、第1電源と、第2電源と、複数のデータ線と、複数の走査線と、複数の信号線と、データ線と走査線とが交わる領域に設けられる複数の画素回路と、を備え、画素回路は、第1電源から第2電源へ電流が流れることにより発光する発光素子と、第1端子が前記第1電源側に、ゲートが第2ノードに、第2端子が第2トランジスタのドレインおよび前記前記第2電源側にそれぞれ接続されている第1トランジスタの前記第2ノードに、ゲートが前記信号線に、第2端子が前記第1トランジスタの前記第2ノードに、ゲートが前記信号線に、第2端子が前記第1トランジスタと、第1端子が第1ノードにそれぞれ接続されている第3トランジスタと、一の端子が第1ノードに、他の端子が第2ノードに接続されている第3トランジスタと、を備え、発光素子が全ての画素回路において1フレームに接続されているキャパシタと、を備え、発光素子が全ての画素回路において1フレームでの所定の期間に一斉に発光し、第1トランジスタのスレッショルド電圧を補償している間に、走査線の走査により選択された画素に対応するデータ電圧を、データ線から第3トランジスタを介して第1ノードに書き込むことを特徴とする、電気光学装置が提供される。

# [0018]

上記電気光学装置は、複数の制御線をさらに備え、画素回路は、第 1 端子が第 1 トランジスタの第 2 端子に、ゲートが制御線に、第 2 端子が発光素子のアノードにそれぞれ接続

されている第4トランジスタをさらに備えていてもよい。

#### [0019]

上記電気光学装置は、複数のリセット線と、リセット電源と、をさらに備え、画素回路 は、第1端子が第2ノードに、ゲートがリセット線に、第2端子がリセット電源にそれぞ れ接続されている第5トランジスタをさらに備えていてもよい。

#### [0020]

上記電気光学装置は、複数のリセット線をさらに備え、画素回路は、第1端子が第2ノ ードに、ゲートがリセット線に、第2端子がデータ線にそれぞれ接続されている第6トラ ンジスタをさらに備えていてもよい。

#### [0021]

第1トランジスタ、第2トランジスタ、および第3トランジスタは、いずれもPチャネ ル型のMOSFET (Metal-Oxide-Semiconductor Fiel d-Effect Transistor)であってもよい。

# 【発明の効果】

### [0022]

以上説明したように本発明によれば、画素回路の素子数を削減しつつ、駆動トランジス タのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示 品位の劣化を避けることが可能な、新規かつ改良された電気光学装置の駆動方法および電 気光学装置を提供することができる。

# 【図面の簡単な説明】

[0023]

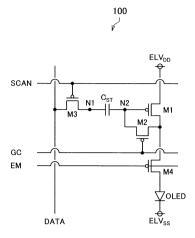

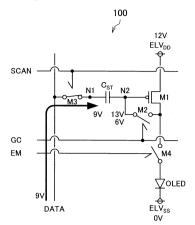

- 【図1】本発明の第1の実施形態にかかる電気光学装置の画素回路100の構成を示す説 明図である。

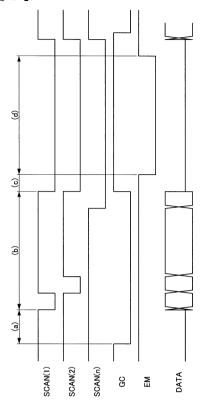

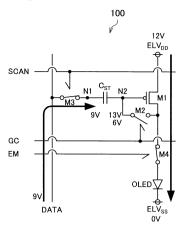

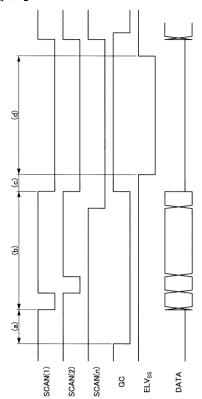

- 【図2】本発明の第1の実施形態に係る電気光学装置の画素回路100を駆動させるため の各信号のタイミングチャートを示す説明図である。

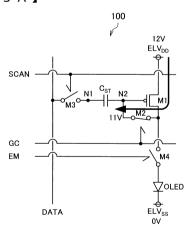

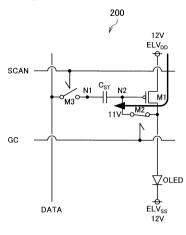

- 【図3A】本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動状態を示 す説明図である。

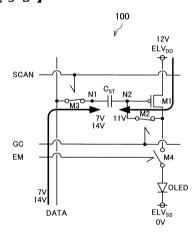

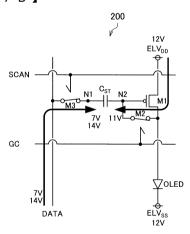

- 【図3B】本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動状態を示 す説明図である。

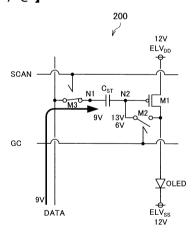

- 【図3C】本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動状態を示 す説明図である。

- 【図3D】本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動状態を示 す説明図である。

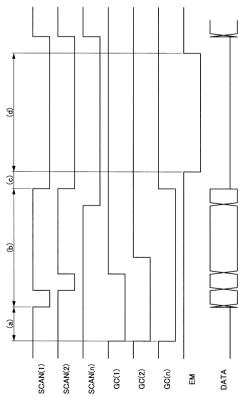

- 【図4】本発明の第1の実施形態に係る電気光学装置の画素回路100を駆動させるため の各信号のタイミングチャートの変形例を示す説明図である。

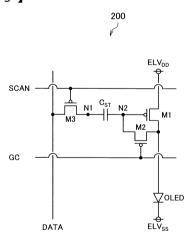

- 【図5】本発明の第2の実施形態にかかる電気光学装置の画素回路200の構成を示す説 明図である。

- 【図6】本発明の第2の実施形態に係る電気光学装置の画素回路200を駆動させるため の各信号のタイミングチャートを示す説明図である。

- 【図7A】本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動状態を示 す説明図である。

- 【図7B】本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動状態を示 す説明図である

- 【図7C】本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動状態を示 す説明図である

- 【図7D】本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動状態を示 す説明図である

- 【図8】本発明の第3の実施形態にかかる電気光学装置の画素回路300の構成を示す説 明図である。

- 【図9】本発明の第4の実施形態にかかる電気光学装置の画素回路400の構成を示す説

10

20

30

40

明図である。

【図10】本発明の第3の実施形態にかかる電気光学装置の画素回路300および本発明の第4の実施形態にかかる電気光学装置の画素回路400を駆動させるための各信号のタイミングチャートを示す説明図である。

【発明を実施するための形態】

[0024]

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。 なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については 、同一の符号を付することにより重複説明を省略する。

[0025]

10

20

< 1 . 第 1 の実施形態 >

「電気光学装置の画素回路の構成 ]

まず、本発明の第1の実施形態に係る電気光学装置の画素回路の構成について説明する。図1は、本発明の第1の実施形態にかかる電気光学装置の画素回路100の構成を示す説明図である。本発明の第1の実施形態にかかる電気光学装置は、図1に示した画素回路100が、n行の走査線とm列のデータ線との交点にマトリクス状に配置された構造を有するものである。以下、図1を用いて本発明の第1の実施形態に係る電気光学装置の画素回路の構成について説明する。

[0026]

図 1 に示したように、本発明の第 1 の実施形態にかかる電気光学装置の画素回路 1 0 0 は、第 1 トランジスタ M 1 と、第 2 トランジスタ M 2 と、第 3 トランジスタ M 3 と、第 4 トランジスタ M 4 と、キャパシタ C <sub>S T</sub> と、発光素子 O L E D と、を含んで構成される。

[0027]

[0028]

第2トランジスタM2は、第1端子が第2ノードN2に、ゲートが信号線GCに、第2端子が第1トランジスタM1の上記第2端子および第4トランジスタM4の第1端子に、それぞれ接続されている。

30

[0029]

第 3 トランジスタ M 3 は、第 1 端子がデータ線 D A T A に、ゲートが走査線 S C A N に、第 2 端子が第 1 ノード N 1 に、それぞれ接続されている。

[0030]

第4トランジスタM4は、ゲートが制御線EMに、第2端子が発光素子OLEDのエミッタに、それぞれ接続されている。

[0031]

画素回路  $1\ 0\ 0$  における第  $1\ h$  ランジスタ  $M\ 1$  、第  $2\ h$  ランジスタ  $M\ 2$  、第  $3\ h$  ランジスタ  $M\ 3$  および  $3\ h$  も  $1\ h$  も

40

50

[0032]

キャパシタ  $C_{ST}$  は、一の端子が第 1 ノード N 1 に、他の端子が第 2 ノード N 2 に、それぞれ接続されている。

[0033]

走査線SCANは、第3トランジスタM3をオン・オフするための制御パルスを供給するものである。走査線SCANに供給される制御パルスによって第3トランジスタM3はオン・オフされる。

[0034]

データ線DATAは、画素回路100にデータ信号を供給するものである。走査線SC

10

20

30

40

50

ANに供給される制御パルスによって第3トランジスタM3がオンになると、その画素回路100に対応するデータ電圧が、第3トランジスタM3を介して第1ノードN1に書き込まれる。

### [0035]

信号線GCは、第2トランジスタM2をオン・オフするための制御パルスを供給するものである。信号線GCに供給される制御パルスによって第2トランジスタM2はオン・オフされる。

### [0036]

制御線 E M は、第4トランジスタ M 4をオン・オフするための制御パルスを供給するものである。制御線 E M に供給される制御パルスによって第4トランジスタ M 4 はオン・オフされ、第4トランジスタ M 4 がオンになっている期間で、画素回路 1 0 0 の第2 ノード N 2 に保持されている電位に応じた電流を発光素子 O L E D に流す。

#### [0037]

発光素子OLEDは、例えば有機EL素子で構成され、アノードとカソードとの間を流れる電流量に応じて自発光する素子である。本実施形態では、上述したように、制御線EMに供給される制御パルスによって第4トランジスタM4がオンになっている期間に、画素回路100の第2ノードN2に保持されている電位に応じた電流が発光素子OLEDに流れ、この電流によって発光素子OLEDは自発光する。

### [0038]

本発明の第1の実施形態に係る電気光学装置では、全ての画素回路100について、第4トランジスタEMを一斉にオンにするための制御パルスが制御線EMにより供給される。これにより、本発明の第1の実施形態に係る電気光学装置は面順次駆動される。

# [0039]

以上、図1を用いて本発明の第1の実施形態に係る電気光学装置の画素回路100の構成について説明した。次に、本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動方法について説明する。

# [0040]

「電気光学装置の画素回路の駆動方法 ]

図2は、本発明の第1の実施形態に係る電気光学装置の画素回路100を駆動させるための各信号のタイミングチャートを示す説明図であり、図3A~図3Dは、本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動状態を示す説明図である。以下、図2および図3A~図3Dを用いて、本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動方法について説明する。

### [0041]

図2に示したタイミングチャートには、1行目の走査線SCAN(1)、2行目の走査線SCAN(2)、n行目の走査線SCAN(n)にそれぞれ供給される制御パルス、信号線GCに供給される制御パルス、制御線EMに供給される制御パルス、データ線DATAに供給されるデータ信号の状態が図示されている。

#### [0042]

図 2 の期間 (a) および図 3 A において、制御線 E M をハイにすることにより、第 4 トランジスタ M 4 をオフした状態とし、信号線 G C をローにすることで、第 2 トランジスタ M 2 をオンする。この結果、発光素子 O L E D は非発光状態となり、第 1 トランジスタ M 1 はダイオード接続状態となる。第 2 トランジスタ M 2 がオンされ第 1 トランジスタ M 1 がダイオード接続状態となることで、ノード N 2 の電圧が、 E L V D D - V t h ( V t h は第 1 トランジスタ M 1 のスレッショルド電圧)に向かって変動し始める。図 3 A では、E L V D D = 1 2 V 、 V t h = 1 V としている。これにより、第 2 ノード N 2 の電位は 1 1 V となる。もちろん、本発明では E L V D D および V t h の値はかかる例に限定されるものではない。

### [0043]

続いて、図2の期間(b)および図3Bにおいて、各走査線SCAN(1)、SCAN

10

20

40

50

(2)、・・・、SCAN(n)が順次排他的に選択され、選択された走査線上の第3トランジスタM3がオンする。選択された走査線上の第3トランジスタM3がオンすると、その選択された画素に対応するデータ電圧  $V_{DATA}$ が、データ線 DATAから、第3トランジスタM3を介して第1ノードN1に書き込まれる。

### [0044]

図 2 の期間(b)において、データ線 D A T A から供給されるデータ電圧  $V_{DATA}$ (図 3 B では 7  $V \sim 1$  4 V の範囲を有する)は、階調レベルと、後述する基準電位  $V_{Das}$  とによって適宜設定される。図 2 の期間(b)においても、第 1 トランジスタ M 1 はダイオード接続状態を維持しているので、第 2 ノード N 2 は E L  $V_{DD}$  -  $V_{th}$  になるまで変動し続けることになり、キャパシタ  $C_{ST}$  に充電される電圧は、第 1 ノード N 1 を基準とすると、E L  $V_{DD}$  -  $V_{th}$  -  $V_{DATA}$  となる。

[0045]

続いて、図2の期間(c)および図3Cにおいて、信号線GCをハイにすることで、第2トランジスタM2をオフするとともに、全走査線SCAN(1)、SCAN(2)、・・、SCAN(n)を同時選択することにより、全ての画素回路100の第3トランジスタM3をオンする。

[0046]

図 2 の期間( c )において、データ電圧  $V_{DATA}$  を基準電位  $V_{bas}$ (図 3 C では 9 V)とすることにより、第 3 トランジスタM 3 を介して全ての画素回路 1 0 0 の第 1 ノードN 1 に電位  $V_{bas}$  が書き込まれる。第 1 ノードN 1 に電位  $V_{bas}$  が書き込まれることに伴い、第 2 ノードN 2 の電位は、キャパシタ  $C_{ST}$  の容量結合により、EL  $V_{DD}$  -  $V_{th}$  -  $V_{DATA}$  +  $V_{bas}$  となる。従って、データ電圧  $V_{DATA}$  が 7 V ~ 1 4 V の範囲を有する場合は、第 2 ノードN 2 の電位は 6 V ~ 1 3 V の範囲を有することになる。

[0047]

続いて、図2の期間(d)および図3Dにおいて、全ての画素回路100について、制御線EMをローにすることで、全ての画素回路100において同時に第4トランジスタM4をオンする。第4トランジスタM4がオンになることで、各画素回路100の第2ノードN2が保持する電位に応じた発光素子OLEDの発光が行われる。

[0048]

また、図 2 の期間( c )から引き続いて第 3 トランジスタ M 3 がオンしたままなので、第 1 ノード N 1 は基準電位 V  $_{\rm b~a~s}$  に維持される。第 1 ノード N 1 が基準電位 V  $_{\rm b~a~s}$  に維持されることよって、第 2 ノード N 2 の電位( E L V  $_{\rm D~D}$  - V  $_{\rm t~h}$  - V  $_{\rm D~A~T~A}$  + V  $_{\rm b~a~s}$  )が、期間( d )の間保持される。

[0049]

以上、本発明の第1の実施形態に係る電気光学装置の画素回路100の駆動方法について説明した。本発明の第1の実施形態に係る電気光学装置の画素回路100をこのように駆動させることで、画素回路100のレイアウト上大きな面積を占めるキャパシタを、キャパシタC <sub>5 T</sub> の1個に収めることができる。

[0050]

また本発明の第1の実施形態に係る電気光学装置の画素回路100は、面順次駆動において、第1トランジスタM1のスレッショルド電圧の補償時間の拡大と、データ書き込み時間の拡大を実現できる。これにより、本発明の第1の実施形態に係る電気光学装置は、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能となる。

[0051]

そして本発明の第 1 の実施形態に係る電気光学装置の画素回路 1 0 0 は、データ保持期間中は第 1 ノード N 1 が基準電位 V  $_{\rm b}$   $_{\rm a}$   $_{\rm s}$  に維持されているので、第 2 ノード N 2 のデータ保持電圧レベルを一定に保つことができる。

[0052]

また、本発明の第1の実施形態に係る電気光学装置を、三次元画像の表示に用いる場合

には、画像を表示する表示期間と画像データの書き込みを行なう非表示期間とを繰り返すことになるが、図2の期間(a)から期間(c)の、発光素子OLEDの非発光期間は全画面が黒表示となり、図2の期間(d)で全画面が同時に表示状態となる。従って、ユーザが三次元画像として視認するためのシャッタ眼鏡のシャッタ制御タイミングを、発光期間と非発光期間とで同期させることにより、片方の眼用の画像にもう片方の眼用の画像が漏れ込む、いわゆるクロストークのない高品位表示が得られる。

### [0053]

なお、本発明においては、電気光学装置の画素回路 1 0 0 の駆動方法はかかる例に限定されない。次に、本発明の第 1 の実施形態に係る電気光学装置の画素回路 1 0 0 の駆動方法の変形例について説明する。

# [0054]

図4は、本発明の第1の実施形態に係る電気光学装置の画素回路100を駆動させるための各信号のタイミングチャートの変形例を示す説明図である。図4に示したタイミングチャートは、図2に示したものと異なり、信号線GCに供給される制御パルスが各行で異なっている。従って図4には、1行目の信号線GC(1)に供給される制御パルス、2行目の信号線GC(2)に供給される制御パルス、・・・、n行目の信号線GC(n)に供給される制御パルスを図示している。

### [0055]

1 行目の信号線 G C ( 1 ) に供給される制御パルスは、図 4 の期間 ( b ) において 1 行目の走査線 S C A N ( 1 ) が選択された後、1 行目の走査線 S C A N ( 1 ) に供給される制御パルスがローからハイに切り替わるタイミングで、ローからハイに切り替わる。1 行目の走査線 S C A N ( 1 ) に供給される制御パルスがローからハイに切り替わるタイミングで 1 行目の信号線 G C ( 1 ) に供給される制御パルスをローからハイに切り替えることで、その行の画素回路 1 0 0 の第 2 トランジスタ M 2 をオフする。

#### [0056]

走査線SCANの選択が完了した時点で第2トランジスタM2をオフすることで、第2 ノードN2の電位を安定化させることができ、その後の期間(c)においてデータ線から 基準電位を印加することで、より所望の電位を第2ノードN2に保持することが可能となる。

# [0057]

以上説明したように本発明の第1の実施形態に係る電気光学装置の画素回路100は、第1トランジスタM1のスレッショルド電圧を補償している間に、選択された画素に対応するデータ電圧V<sub>DATA</sub>が、データ線DATAから第3トランジスタM3を介して第1ノードN1に書き込まれる。

### [0058]

これにより、本発明の第1の実施形態に係る電気光学装置の画素回路100は、画素回路100のレイアウト上大きな面積を占めるキャパシタを、キャパシタC $_{ST}$ の1個に収めつつ、かつ、面順次駆動において、第1トランジスタM1のスレッショルド電圧の補償時間の拡大と、データ書き込み時間の拡大を実現できる。これにより、本発明の第1の実施形態に係る電気光学装置は、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能となる。

## [0059]

本発明の第1の実施形態に係る電気光学装置の画素回路100は、全ての信号線GCの制御タイミングを同一にしてもよく、行毎に変えても良い。信号線GCの制御タイミングを行毎に変える場合は、走査線SCANの選択が完了した時点で第2トランジスタM2をオフすることで、第2ノードN2の電位を安定化させることができ、その後の期間(c)においてデータ線から基準電位を印加することで、より所望の電位を第2ノードN2に保持することが可能となる。

## [0060]

40

30

10

20

#### < 2 . 第 2 の実施形態 >

# 「電気光学装置の画素回路の構成]

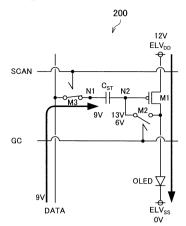

次に、本発明の第2の実施形態に係る電気光学装置の画素回路の構成について説明する。図5は、本発明の第2の実施形態にかかる電気光学装置の画素回路200の構成を示す説明図である。本発明の第2の実施形態にかかる電気光学装置は、図5に示した画素回路200が、n行の走査線とm列のデータ線との交点にマトリクス状に配置された構造を有するものである。以下、図5を用いて本発明の第2の実施形態に係る電気光学装置の画素回路の構成について説明する。

# [0061]

図 5 に示したように、本発明の第 2 の実施形態にかかる電気光学装置の画素回路 2 0 0 は、第 1 トランジスタ M 1 と、第 2 トランジスタ M 2 と、第 3 トランジスタ M 3 と、キャパシタ C  $_{S-T}$  と、発光素子 O L E D と、を含んで構成される。図 5 に示した画素回路 2 0 0 は、図 1 に示した画素回路 1 0 0 から第 4 トランジスタ M 4 が削除された構成を有している。

## [0062]

第 1 トランジスタ M 1 は、第 1 端子が第 1 電源 E L V  $_{\rm D}$  D に、ゲートが第 2 ノード N 2 に、第 2 端子が第 2 トランジスタ M 2 の第 2 端子および発光素子 O L E D の アノード に、それぞれ接続されている。

#### [0063]

第2トランジスタM2は、第1端子が第2ノードN2に、ゲートが信号線GCに、第2端子が第1トランジスタM1のドレインおよび発光素子OLEDのアノードに、それぞれ接続されている。

### [0064]

第 3 トランジスタM 3 は、第 1 端子がデータ線DATAに、ゲートが走査線SCANに、第 2 端子が第 1 ノードN 1 に、それぞれ接続されている。

### [0065]

画素回路 2 0 0 における第 1 トランジスタ M 1 、第 2 トランジスタ M 2 および第 3 トランジスタ M 3 は、いずれも P チャネル型の M O S F E T である。

## [0066]

キャパシタ  $C_{S,T}$  は、一の端子が第 1 ノード N 1 に、他の端子が第 2 ノード N 2 に、そ M れぞれ接続されている。

# [0067]

走査線SCANは、第3トランジスタM3をオン・オフするための制御パルスを供給するものである。走査線SCANに供給される制御パルスによって第3トランジスタM3はオン・オフされる。

# [0068]

データ線 DATAは、画素回路 2 0 0 にデータ信号を供給するものである。走査線 S C A N に供給される制御パルスによって第 3 トランジスタ M 3 がオンになると、その画素回路 2 0 0 に対応するデータ電圧が、第 3 トランジスタ M 3 を介して第 1 ノード N 1 に書き込まれる。

# [0069]

信号線GCは、第2トランジスタM2をオン・オフするための制御パルスを供給するものである。信号線GCに供給される制御パルスによって第2トランジスタM2はオン・オフされる。

### [0070]

発光素子OLEDは、例えば有機EL素子で構成され、アノードとカソードとの間を流れる電流量に応じて自発光する素子である。本実施形態では、第2電源ELV $_S$  $_S$ の電位が第1電源ELV $_D$ Dの電位より低くなると、画素回路200の第2ノードN2に保持されている電位に応じた電流が発光素子OLEDに流れ、この電流によって発光素子OLEDは自発光する。

10

20

40

#### [0071]

本発明の第2の実施形態に係る電気光学装置では、全ての画素回路200について、第2電源 $ELV_{SS}$ の電位が第1電源 $ELV_{DD}$ の電位より低くなる制御が行われる。これにより、本発明の第2の実施形態に係る電気光学装置は面順次駆動される。

# [0072]

以上、図5を用いて本発明の第2の実施形態に係る電気光学装置の画素回路200の構成について説明した。次に、本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動方法について説明する。

# [0073]

# 「電気光学装置の画素回路の駆動方法]

図6は、本発明の第2の実施形態に係る電気光学装置の画素回路200を駆動させるための各信号のタイミングチャートを示す説明図であり、図7A~図7Dは、本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動状態を示す説明図である。以下、図6および図7A~図7Dを用いて、本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動方法について説明する。

#### [0074]

図6に示したタイミングチャートには、1行目の走査線SCAN(1)、2行目の走査線SCAN(2)、n行目の走査線SCAN(n)にそれぞれ供給される制御パルス、信号線GCに供給される制御パルス、およびデータ線DATAに供給されるデータ信号の状態が図示されている。図2に示したタイミングチャートからは制御線EMに供給される制御パルスの状態が削除された替わりに第2電源ELV<sub>SS</sub>の電圧レベルの状態が図示されており、その他の点は図2に示したタイミングチャートと同一である。

# [0075]

図 6 の期間(a)および図 7 Aにおいて、第 2 電源 E L V  $_{SS}$ をハイにした状態で、信号線 G C をローにすることで、第 2 トランジスタ M 2 をオンする。この結果、発光素子 O L E D は非発光状態となり、第 1 トランジスタ M 1 はダイオード接続状態となる。第 2 トランジスタ M 2 がオンされ第 1 トランジスタ M 1 はダイオード接続状態となることで、ノード N 2 の電圧が、E L V  $_{DD}$  - V  $_{th}$  ( V  $_{th}$  は第 1 トランジスタ M 1 のスレッショルド電圧)に向かって変動し始める。図 7 A では、E L V  $_{DD}$  = 1 2 V 、V  $_{th}$  = 1 V としている。もちろん、本発明では E L V  $_{DD}$  および V  $_{th}$  の値はかかる例に限定されるものではない。

# [0076]

続いて、図6の期間(b)および図7Bにおいて、各走査線SCAN(1)、SCAN(2)、・・・、SCAN(n)が順次排他的に選択され、選択された走査線上の第3トランジスタM3がオンすると、その選択された画素に対応するデータ電圧V<sub>DATA</sub>が、データ線DATAから、第3トランジスタM3を介して第1ノードN1に書き込まれる。

### [0077]

図 6 の期間(b)において、データ線 D A T A から供給されるデータ電圧  $V_{DATA}$ (図 7 B では 7  $V_{\sim}$  1 4  $V_{O}$  の範囲を有する)は、階調レベルと、後述する基準電位  $V_{Das}$  とによって適宜設定される。図 6 の期間(b)においても、第 1 トランジスタ M 1 はダイオード接続状態を維持しているので、第 2 ノード N 2 は E L  $V_{DD}$  -  $V_{th}$  になるまで変動し続けることになり、キャパシタ  $V_{CS}$  - に充電される電圧は、第 1 ノード N 1 を基準とすると、E L  $V_{DD}$  -  $V_{th}$  -  $V_{DATA}$  となる。

#### [0078]

続いて、図6の期間(c)および図7Cにおいて、信号線GCをハイにすることで、第2トランジスタM2をオフするとともに、全走査線SCAN(1)、SCAN(2)、・・、SCAN(n)を同時選択することにより、全ての画素回路200の第3トランジスタM3をオンする。

# [0079]

50

10

20

30

図 6 の期間( c )において、データ電圧  $V_{DATA}$  を基準電位  $V_{bas}$ (図 7 C では 9 V)とすることにより、第 3 トランジスタM 3 を介して全ての画素回路 2 0 0 の第 1 ノード N 1 に電位  $V_{bas}$  が書き込まれる。第 1 ノード N 1 に電位  $V_{bas}$  が書き込まれることに伴い、第 2 ノード N 2 の電位は、キャパシタ C  $_{ST}$  の容量結合により、 E L  $V_{DD}$  -  $V_{th}$  -  $V_{DATA}$  +  $V_{bas}$  となる。従って、データ電圧  $V_{DATA}$  が 7 V ~ 1 4 V の範囲を有することになる。

続いて、図 6 の期間(d)および図 7 Dにおいて、全ての画素回路 2 0 0 について、第 2 電源 E L V  $_{SS}$ をローにすることで、全ての画素回路 2 0 0 において同時に発光素子 O L E D に電流を流す。第 2 電源 E L V  $_{SS}$ をローにすることで、各画素回路 2 0 0 の第 2 ノード N 2 が保持する電位に応じた発光素子 O L E D の発光が行われる。

[0081]

また、図 6 の期間( c )から引き続いて第 3 トランジスタ M 3 がオンしたままなので、第 1 ノード N 1 は基準電位 V  $_{\rm b~a~s}$  に維持される。第 1 ノード N 1 が基準電位 V  $_{\rm b~a~s}$  に維持されることよって、第 2 ノード N 2 の電位( E L V  $_{\rm D~D}$  - V  $_{\rm t~h}$  - V  $_{\rm D~A~T~A}$  + V  $_{\rm b~a~s}$  )が、期間( d )の間保持される。

[0082]

以上、本発明の第2の実施形態に係る電気光学装置の画素回路200の駆動方法について説明した。本発明の第2の実施形態に係る電気光学装置の画素回路200をこのように駆動させることで、画素回路200のレイアウト上大きな面積を占めるキャパシタを、キャパシタC<sub>ST</sub>の1個に収めることができる。

[0083]

また本発明の第2の実施形態に係る電気光学装置の画素回路200は、面順次駆動において、第1トランジスタM1のスレッショルド電圧の補償時間の拡大と、データ書き込み時間の拡大を実現できる。これにより、本発明の第2の実施形態に係る電気光学装置は、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能となる。

[0084]

そして本発明の第2の実施形態に係る電気光学装置の画素回路200は、データ保持期間中は第1ノードN1が基準電位V<sub>bas</sub>に維持されているので、第2ノードN2のデータ保持電圧レベルを一定に保つことができる。

[0085]

< 3 . 第 3 の実施形態 >

[電気光学装置の画素回路の構成]

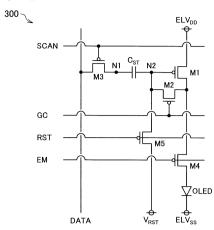

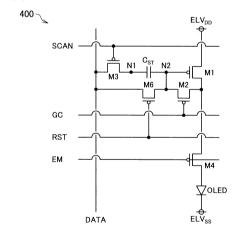

次に、本発明の第3の実施形態に係る電気光学装置の画素回路の構成について説明する。図8は、本発明の第3の実施形態にかかる電気光学装置の画素回路300の構成を示す説明図である。本発明の第3の実施形態にかかる電気光学装置は、図8に示した画素回路300が、n行の走査線とm列のデータ線との交点にマトリクス状に配置された構造を有するものである。以下、図8を用いて本発明の第3の実施形態に係る電気光学装置の画素回路の構成について説明する。

[0086]

図8に示したように、本発明の第3の実施形態にかかる電気光学装置の画素回路300は、第1トランジスタM1と、第2トランジスタM2と、第3トランジスタM3と、第4トランジスタM4と、第5トランジスタM5と、キャパシタC<sub>ST</sub>と、発光素子OLEDと、を含んで構成される。図8に示した画素回路300は、図1に示した画素回路100に第5トランジスタM5が追加された構成を有している。

[0087]

第 5 トランジスタ M 5 は、第 1 端子が第 2 ノード N 2 に、ゲートがリセット線 R S T に、第 2 端子がリセット電源 V <sub>R S T</sub> に、それぞれ接続されている。第 5 トランジスタ M 5 は、発光素子 O L E D に電流を流して発光素子 O L E D を発光させた後に、第 2 ノード N

10

20

30

40

2 をリセット電源 V <sub>R S T</sub> に接続して所定のリセット電位 V <sub>R S T</sub> に設定するものである

#### [0088]

より具体的には、図2における期間(d)の発光期間終了後、期間(a)の第1トランジスタM1のダイオード接続が開始される前までの間に、第1トランジスタM1を十分オンさせるだけの所定のリセット電位V。、下を第2ノードN2に書き込む。

#### [0089]

発光素子OLEDを発光させた後に、第2ノードN2をリセット電源V $_{RST}$ に接続して所定のリセット電位V $_{RST}$ に設定することで、特に前フレームの表示が暗階調であった場合の、第1トランジスタM1のスレッショルド補償完了までの時間を短縮させることができる。

### [0090]

< 4 . 第 4 の実施形態 >

[電気光学装置の画素回路の構成]

次に、本発明の第4の実施形態に係る電気光学装置の画素回路の構成について説明する。図9は、本発明の第4の実施形態にかかる電気光学装置の画素回路400の構成を示す説明図である。本発明の第4の実施形態にかかる電気光学装置は、図9に示した画素回路400が、n行の走査線とm列のデータ線との交点にマトリクス状に配置された構造を有するものである。以下、図9を用いて本発明の第4の実施形態に係る電気光学装置の画素回路の構成について説明する。

### [0091]

図9に示したように、本発明の第4の実施形態にかかる電気光学装置の画素回路400は、第1トランジスタM1と、第2トランジスタM2と、第3トランジスタM3と、第4トランジスタM4と、第6トランジスタM6と、キャパシタC<sub>ST</sub>と、発光素子OLEDと、を含んで構成される。図9に示した画素回路300は、図8に示した画素回路300から第5トランジスタM5が削除され、第6トランジスタM6が追加された構成を有している。

#### [0092]

第6トランジスタM6は、第1端子が第2ノードN2に、ゲートがリセット線RSTに、第2端子がデータ線DATAに、それぞれ接続されている。第6トランジスタM6は、図8に示した画素回路300の第5トランジスタM5と同様に、発光素子OLEDに電流を流して発光素子OLEDを発光させた後に、第2ノードN2を所定のリセット電位V<sub>RST</sub>に設定するものである。

# [0093]

本発明の第4の実施形態にかかる電気光学装置の画素回路400は、第6トランジスタ M6の第2端子をデータ線DATAへ接続し、上述のリセットタイミングにおいてデータ 線DATAからリセット電位  $V_{RST}$  を供給することにより、本発明の第3の実施形態にかかる電気光学装置の画素回路300と同様の効果を得ることができる。そして本発明の第4の実施形態にかかる電気光学装置の画素回路400は、本発明の第3の実施形態にかかる電気光学装置の画素回路300において設けられていたリセット電位  $V_{RST}$  用の電源線が不要となるので、さらなる高解像度化への対応も可能となる。

#### **r** n n a 1 **1**

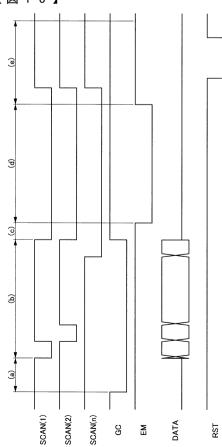

図10は、本発明の第3の実施形態にかかる電気光学装置の画素回路300および本発明の第4の実施形態にかかる電気光学装置の画素回路400を駆動させるための各信号のタイミングチャートを示す説明図である。図10に示したタイミングチャートは、図2に示したタイミングチャートに、リセット線RSTに印加される制御パルスの状態が図示されている。

# [0095]

リセット線RSTに印加される制御パルスは、図10に示したように、期間(d)の後で次フレームの期間(a)が始まるまでの期間(e)においてローにするものである。期

20

10

30

40

間(e)において、リセット線RSTに印加される制御パルスをローにすることで、第5トランジスタM5または第6トランジスタM6がオンされ、第2ノードN2が所定のリセット電位  $V_{RST}$ に設定される。第2ノードN2を所定のリセット電位  $V_{RST}$ に設定することで、特に前フレームの表示が暗階調であった場合の、第1トランジスタM1のスレッショルド補償完了までの時間を短縮させることができる。

# [0096]

< 5 . まとめ>

以上説明したように本発明の各実施形態によれば、第1トランジスタM1のスレッショルド電圧を補償している間に、選択された画素に対応するデータ電圧V<sub>DATA</sub>を、データ線DATAから第3トランジスタM3を介して第1ノードN1に書き込む。これにより、画素回路のレイアウト上大きな面積を占めるキャパシタを1個に収めつつ、かつ、面順次駆動において、第1トランジスタM1のスレッショルド電圧の補償時間の拡大と、データ書き込み時間の拡大を実現できる。そして、本発明の各実施形態に係る電気光学装置は、画素回路の素子数を削減しつつ、駆動トランジスタのスレッショルド電圧補償時間およびデータ書き込み時間を十分に確保することで表示品位の劣化を避けることが可能となる。また、本発明の各実施形態に係る電気光学装置の画素回路は、データ保持期間中は第1ノードN1が基準電位V<sub>bas</sub>に維持されているので、第2ノードN2のデータ保持電圧レベルを一定に保つことができる。

### [0097]

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

#### 【符号の説明】

### [0098]

100、200、300、400 画素回路 M1、M2、M3、M4、M5、M6 トランジスタ

OLED 発光素子

С<sub>ѕ т</sub> キャパシタ

SCAN 走査線

DATA データ線

G C 信号線

EM 制御線

RST リセット線

ELV<sub>DD</sub> 第1電源

ELV<sub>SS</sub> 第2電源

V<sub>RST</sub> リセット電源

10

20

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図8】

【図9】

【図10】

# フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 2 2 D G 0 9 G 3/20 6 2 3 C G 0 9 G 3/20 6 2 3 D G 0 9 G 3/20 6 2 4 Z H 0 5 B 33/14 A

(72)発明者 奥野 武志

神奈川県横浜市鶴見区菅沢町2-7 株式会社サムスン横浜研究所内

(72)発明者 古宮 直明

神奈川県横浜市鶴見区菅沢町2-7 株式会社サムスン横浜研究所内

審査官 西島 篤宏

(56)参考文献 特開2011-034039(JP,A)

国際公開第2010/016316(WO,A1)

特開2008-040444(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 3 0 G 0 9 G 3 / 2 0 H 0 1 L 5 1 / 5 0