OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 269 213**

(51) Int. Cl.:

**G11C 7/24** (2006.01)

**G11C 16/22** (2006.01)

**G11C 16/10** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Número de solicitud europea: **00986483 .6**

(86) Fecha de presentación : **14.12.2000**

(87) Número de publicación de la solicitud: **1238393**

(87) Fecha de publicación de la solicitud: **11.09.2002**

(54) Título: **Dispositivo de comunicación móvil que presenta una memoria flash y una memoria SRAM incorporadas e integradas.**

(30) Prioridad: **17.12.1999 US 465665**

(73) Titular/es: **QUALCOMM INCORPORATED

5775 Morehouse Drive

San Diego, California 92121-1714, US**

(45) Fecha de publicación de la mención BOPI:

**01.04.2007**

(72) Inventor/es: **Jha, Sanjay;

Simmonds, Stephen;

Elhusseini, Jalal;

Yu, Nicholas, K. y

Khan, Safi**

(45) Fecha de la publicación del folleto de la patente:

**01.04.2007**

(74) Agente: **Curell Suñol, Marcelino**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Dispositivo de comunicación móvil que presenta una memoria flash y una memoria SRAM incorporadas e integradas.

### I. Campo de la invención

La presente invención se refiere en general a los dispositivos de comunicación móvil, tales como los teléfonos celulares, y en particular, a una memoria flash y una memoria estática de acceso aleatorio (SRAM) para ser utilizadas en éstos.

### II. Descripción de la técnica relacionada

Una memoria flash es un tipo de memoria no volátil que conserva la información almacenada incluso después de una desconexión de la alimentación. Esto contrasta con los dispositivos de memoria volátil, tales como los dispositivos de SRAM o RAM dinámica (DRAM), que pierden los datos almacenados cuando se desconecta la alimentación. Además de ser no volátil, la memoria flash puede borrarse y reprogramarse eléctricamente dentro del sistema en el cual está incorporada. Por el contrario, en otros dispositivos de memoria no volátil, tales como los dispositivos de memoria de sólo lectura, programable y borrbable (EPROM), se requieren unas tensiones especiales para la reprogramación y, por consiguiente, la memoria sólo suele ser reprogramable por el fabricante o el personal de servicio especializado.

En consecuencia, la memoria flash se emplea ventajosamente en los dispositivos que requieren memoria no volátil que pueda ser borrada y reprogramada selectivamente. En particular, la memoria flash es muy adecuada para ser utilizada en los ordenadores personales de sobremesa, los ordenadores portátiles, los cartuchos de videojuegos, las grabadoras digitales de voz, los asistentes personales digitales (PDA) y los teléfonos celulares (u otras estaciones móviles de los sistemas de comunicación inalámbrica). Habitualmente, dentro de dichos sistemas, la memoria flash está configurada como una única macro flash, que puede ser leída o escrita, pero no ambas cosas, en un momento determinado. Para la mayoría de los dispositivos esto resulta suficiente. Por ejemplo, en la mayoría de los dispositivos que contienen una memoria flash, los datos que van a almacenarse en la memoria flash se almacenan en memoria volátil hasta que el dispositivo se desconecta y, a continuación, la memoria flash se reprograma con los datos durante una operación de apagado. Así pues, es improbable que el dispositivo necesite leer y escribir alguna vez en la memoria flash al mismo tiempo. En un ejemplo, un PC o un ordenador portátil puede almacenar los cambios para un sistema básico de entrada-salida (BIOS) en una memoria DRAM hasta que el ordenador deba desconectarse, siendo transferidos, entonces, dichos cambios para el BIOS a una memoria flash.

No obstante, la implementación de la memoria flash dentro de un teléfono celular presenta algunos problemas. En los teléfonos celulares, tal vez sea necesario realizar con mayor frecuencia muchas operaciones de lectura y de escritura en la memoria flash. Los teléfonos celulares consumen una cantidad considerable de energía durante su uso y, para resultar comercialmente atractivos, deben ser capaces de funcionar con eficacia durante largos períodos de tiempo entre recargas. Por este motivo, los teléfonos celulares suelen estar configurados de una forma que les permita interrumpir la alimentación de los componentes

internos tantas veces como sea posible. Muchos de los componentes de los teléfonos celulares CDMA, por ejemplo, son desactivados entre cada intervalo de radiobúsqueda consecutivo del sistema CDMA. (Los intervalos de radiobúsqueda tienen lugar cada 30 milisegundos). En consecuencia, no es posible acumular operaciones de escritura pendientes dentro de una memoria no volátil hasta que se realiza la operación final única de apagado. En su lugar, tal vez sea necesario escribir puntualmente los datos en la memoria flash antes de cada interrupción de energía temporal consecutiva. Por otra parte, la necesidad de reprogramar con frecuencia la memoria flash suele ser muy superior en un teléfono celular, particularmente en un teléfono celular inteligente, es decir, un teléfono celular configurado con un PDA para proporcionar, de ese modo, funciones de telefonía celular y funciones de PDA. Por lo que a los ordenadores se refiere, tal vez sólo sea necesario reprogramar las memorias flash en caso de que se produzca algún cambio en el BIOS u otros parámetros de configuración del sistema. En los teléfonos celulares inteligentes, tal vez se necesite reprogramar frecuentemente la memoria flash para registrar nuevos números de teléfonos, direcciones, fechas de calendario, fechas de reuniones y similares. En los teléfonos inteligentes configurados para registrar notas de voz, es posible que la memoria flash deba ser reprogramada cada vez que el teléfono se utiliza para registrar una nota de voz. En consecuencia, tal vez sea necesario realizar operaciones de lectura y escritura con mucha mayor frecuencia en relación con los teléfonos celulares y, entonces, el sistema de memoria flash convencional, que no permite realizar operaciones de lectura y escritura en la memoria flash de forma simultánea, puede resultar inadecuado.

Por otra parte, en las aplicaciones telefónicas celulares, puede que sea necesario acceder a la memoria flash con mucha más rapidez que en otras aplicaciones. Esto es particularmente cierto en caso de que los datos que se desean recuperar de la memoria flash deban ser utilizados en conexión con cualquier función en tiempo real del teléfono celular, tal como una llamada telefónica de voz. Para dichas funciones, cualquier retardo en la lectura de la memoria flash, debido a la necesidad de esperar a que finalice una operación de escritura previa, puede resultar significativo.

Además, aunque no sea necesario retardar una operación de lectura hasta que finalice una operación de escritura, los tiempos de lectura de las memorias flash convencionales pueden ser bastante lentos. Las memorias flash se degradan con el uso y, en consecuencia, el tiempo de lectura para las celdas flash particulares que han sido reescritas con frecuencia resulta lento en comparación con otras celdas flash que no han sido reescritas con frecuencia. Por ello, cuando un dispositivo que contiene una memoria flash ha sido utilizado durante cierto tiempo, algunas de sus celdas flash presentarán unos tiempos de lectura más lentos que otras. Para tener en cuenta una posible degradación, los dispositivos que contienen celdas flash habitualmente establecen un tiempo de lectura interno de la memoria flash relativamente lento. En este sentido, el sistema de bus conectado a la memoria flash dispuesto para recuperar los datos de la memoria flash se preprograma con un número de estados de espera suficiente para adaptarse a los tiempos de acceso potencialmente lentos de las celdas que pueden degradarse. Dicho de otro modo, el sistema de bus es preprogra-

mado para adaptarse a la peor situación hipotética por lo que al tiempo de acceso a la memoria flash se refiere. Por consiguiente, todos los accesos de lectura serán relativamente lentos, incluso en las ubicaciones de memoria flash que todavía no se han degradado. En muchos dispositivos, el lento tiempo de lectura no resulta problemático. No obstante, con respecto a los teléfonos celulares, es mucho más importante reducir al mínimo el tiempo necesario para cada acceso a la memoria flash, particularmente, mientras el teléfono celular está realizando funciones en tiempo real. En consecuencia, será sumamente deseable proporcionar un sistema de memoria flash mejorado, en particular, para ser utilizado dentro de teléfonos celulares o dispositivos similares, que superen las desventajas indicadas.

Habitualmente, en los teléfonos celulares, se utiliza una memoria flash, que permite el almacenamiento no volátil, en conjunción con una SRAM, que permite el almacenamiento volátil. Típicamente, los dispositivos de memoria flash y SRAM están separados entre sí y están montados también separados del ASIC principal del teléfono celular que incluye el microprocesador y los diversos componentes periféricos que se encargan de las funciones de telefonía celular. En dichas implementaciones, debido a que la memoria flash y la memoria SRAM son independientes del ASIC, el tiempo necesario para acceder a la memoria flash y la SRAM puede ser relativamente lento, entorpeciéndose pues el rendimiento global del sistema. En consecuencia, también es deseable proporcionar una arquitectura de sistema mejorada para utilizar dentro de los teléfonos celulares, que incluya una memoria flash, una SRAM y un ASIC central que permita un acceso ágil a la memoria flash y SRAM.

Asimismo, puesto que tal vez sea necesario acceder con frecuencia a la memoria flash del teléfono celular, existe el riesgo de que se sobrescriban involuntariamente algunas partes de los datos almacenados en la memoria flash. Esto es particularmente cierto en los teléfonos celulares de última generación que pueden incluir numerosos componentes de hardware, cada uno de los cuales es capaz de reprogramar partes de la memoria flash. Este problema se agrava debido al hecho de que habitualmente es necesario diseñar y comercializar con mucha rapidez el software que va a ser utilizado dentro de los teléfonos celulares, para adaptarlo a un mercado en constante cambio. Por consiguiente, existe un riesgo bastante significativo de que el software pueda provocar accidentalmente la reescritura o la supresión de algunas partes de los datos de la memoria flash. Este problema es particularmente serio cuando la parte de memoria flash borrada accidentalmente contenía números de teléfonos importantes, tales como los teléfonos de la policía, los bomberos o similares, o contenía programas de software importantes, tales como un cargador de arranque y similares, necesarios para el funcionamiento del teléfono. En consecuencia, será sumamente deseable proporcionar un sistema de memoria flash mejorado que reduzca al mínimo el riesgo de borrar accidentalmente algunas partes de la memoria flash. El documento de la técnica anterior WO99/35650 da a conocer una memoria flash con capacidad de lectura durante escritura.

### Sumario de la invención

Según la presente invención, se proporciona un sistema de memoria flash según la reivindicación 1.

Las celdas de la memoria flash se dividen en un conjunto de macros flash, a las que se puede acceder de forma independiente. Es posible realizar una operación de escritura en una de las macros flash mientras se realiza una operación de lectura en otra de las macros flash. De esta manera, el tiempo de respuesta global del sistema se reduce, debido, en parte, a la no necesidad de posponer las operaciones de lectura hasta la finalización de una operación de escritura. En realidad, puesto que las operaciones de escritura de la memoria flash suelen llevar mucho más tiempo que las operaciones de lectura de la memoria flash, es posible realizar numerosas operaciones de lectura en paralelo durante una sola operación de escritura de la memoria flash.

Según un aspecto de la presente invención, se proporciona un sistema de memoria flash con estados de espera programables. En un ejemplo de forma de realización, las celdas de la memoria flash también se disponen como un conjunto de macros flash. Un bus de memoria flash interconecta las macros flash y un controlador de memoria flash. El controlador de memoria flash incluye una unidad de registro de estados de espera para almacenar un número programable de estados de espera asociados a las macros flash, presentando cada flash macro un número programable de estados de espera. Asimismo, el controlador de memoria flash incluye una unidad de acceso a la macro flash para acceder a una macro flash seleccionada. La unidad de acceso a la macro flash accede a la macro flash seleccionada mediante el programa del bus de memoria flash con el número de estados de espera asociados a la macro flash seleccionada. Con esta disposición, es posible acceder a las partes de la memoria flash que son reprogramadas frecuentemente y que, por lo tanto, están sujetas a la degradación, utilizando un número de estados de espera superior al de otras partes de la memoria flash. Como consecuencia de lo anterior, el acceso a las partes de la memoria flash que no son reprogramadas frecuentemente puede tener lugar con mucha más rapidez que en los sistemas en los que todas las operaciones de lectura de la memoria flash son retrasadas un cierto numero de estados de espera para adaptarse al peor caso de tiempo de acceso a la memoria correspondiente al peor caso de degradación.

Según un aspecto de la presente invención, se proporciona un sistema de memoria flash con protección por contraseña. En un ejemplo de forma de realización, el sistema de memoria flash incluye celdas de memoria flash dispuestas como un conjunto de macros flash, junto con un controlador de memoria flash que presenta unos medios para almacenar una contraseña separada asociada a cada macro flash, siendo dichos medios, sensibles a la recepción de una contraseña válida desde una macro flash seleccionada, operativos para habilitar la programación de supresión de las celdas flash de la macro flash seleccionada y, al mismo tiempo, impedir la programación de supresión de las demás celdas flash. Con esta configuración, se reduce en gran medida el riesgo de supresión accidental de algunas partes de la memoria flash. Para poder realizar una operación de supresión, debe proporcionarse una contraseña válida. Por consiguiente, las operaciones de supresión accidentales resultantes de errores de software y similares se reducen mucho. Además, proporcionando contraseñas diferentes para las partes diferentes de la memoria flash, es posible restringir

las operaciones de supresión de los programas informáticos individuales o los componentes de hardware periféricos individuales, de tal forma que sólo sean aplicables a partes particulares de la memoria flash. De esta forma, los riesgos de supresión o reprogramación accidental de grandes partes de la memoria flash se reducen en gran medida. En una implementación específica, una parte de la memoria flash contiene un cargador de arranque que se utiliza para arrancar el sistema en el que reside la memoria flash. Se proporciona una contraseña separada asociada al cargador de arranque para reducir todavía más el riesgo de reprogramar accidentalmente el cargador de arranque.

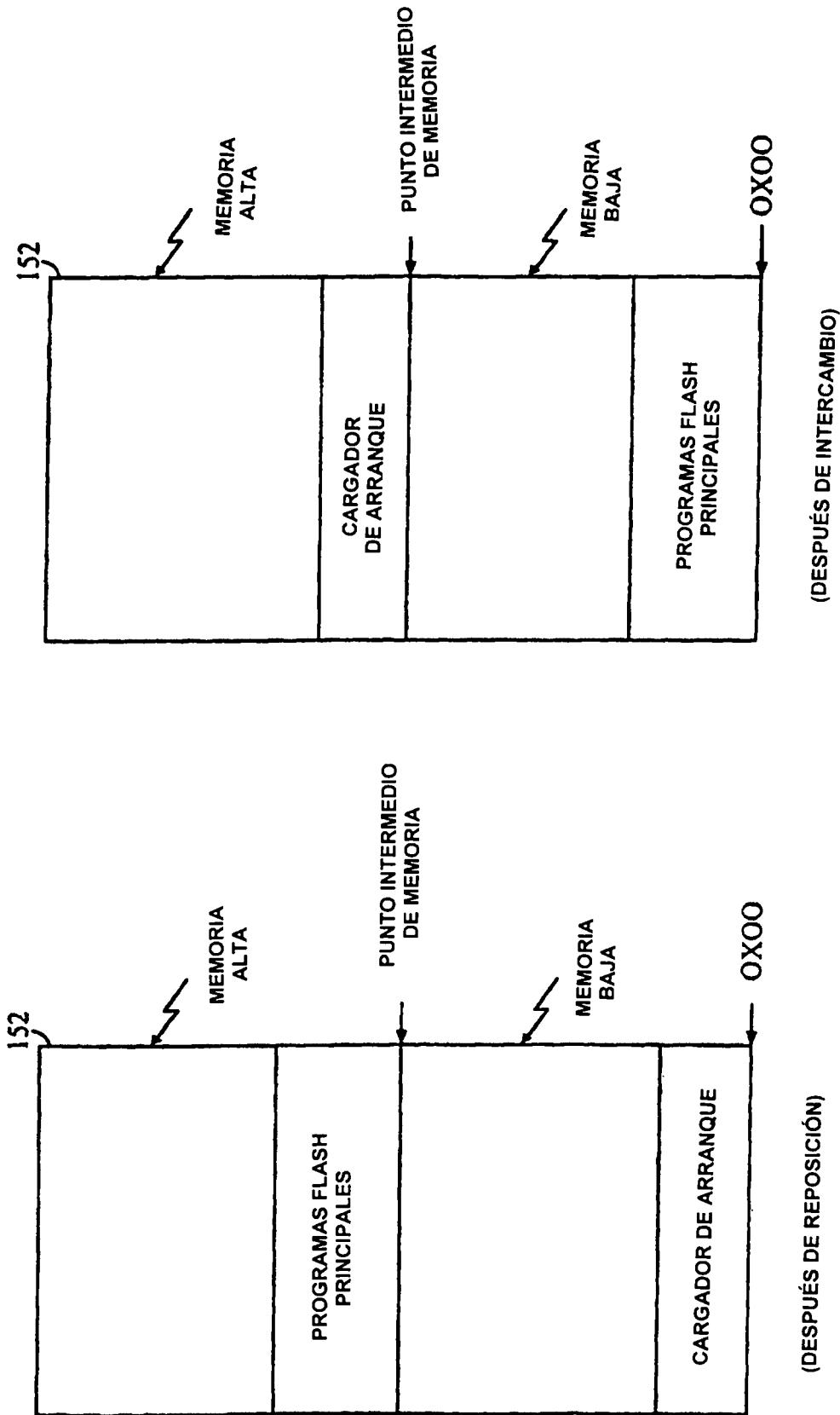

Según un aspecto de la presente invención, se proporciona un sistema de memoria flash con un mapa de memoria programable. El sistema de memoria flash incluye celdas de memoria flash y un controlador de memoria flash que está provisto de medios para dividir las celdas de memoria flash en posiciones altas y posiciones bajas de la memoria. En las celdas de memoria flash, se almacena un cargador de arranque empezando por la dirección de memoria más baja del espacio de la memoria flash. Los medios para dividir incluyen los medios para intercambiar las posiciones altas y bajas de la memoria una vez que han finalizado las operaciones realizadas por el cargador de arranque. Con esta disposición, el cargador de arranque, al cual se suele acceder sólo durante la operación de encendido inicial, es traspasado a la memoria alta para permitir que otros datos y programas a los cuales tal vez sea necesario acceder con más frecuencia sean almacenados en la memoria baja, facilitando de ese modo el acceso a los mismos.

Otros objetivos, características y ventajas de la presente invención se pondrán de manifiesto a partir de la siguiente descripción considerada conjuntamente con los dibujos adjuntos.

#### Breve descripción de los dibujos

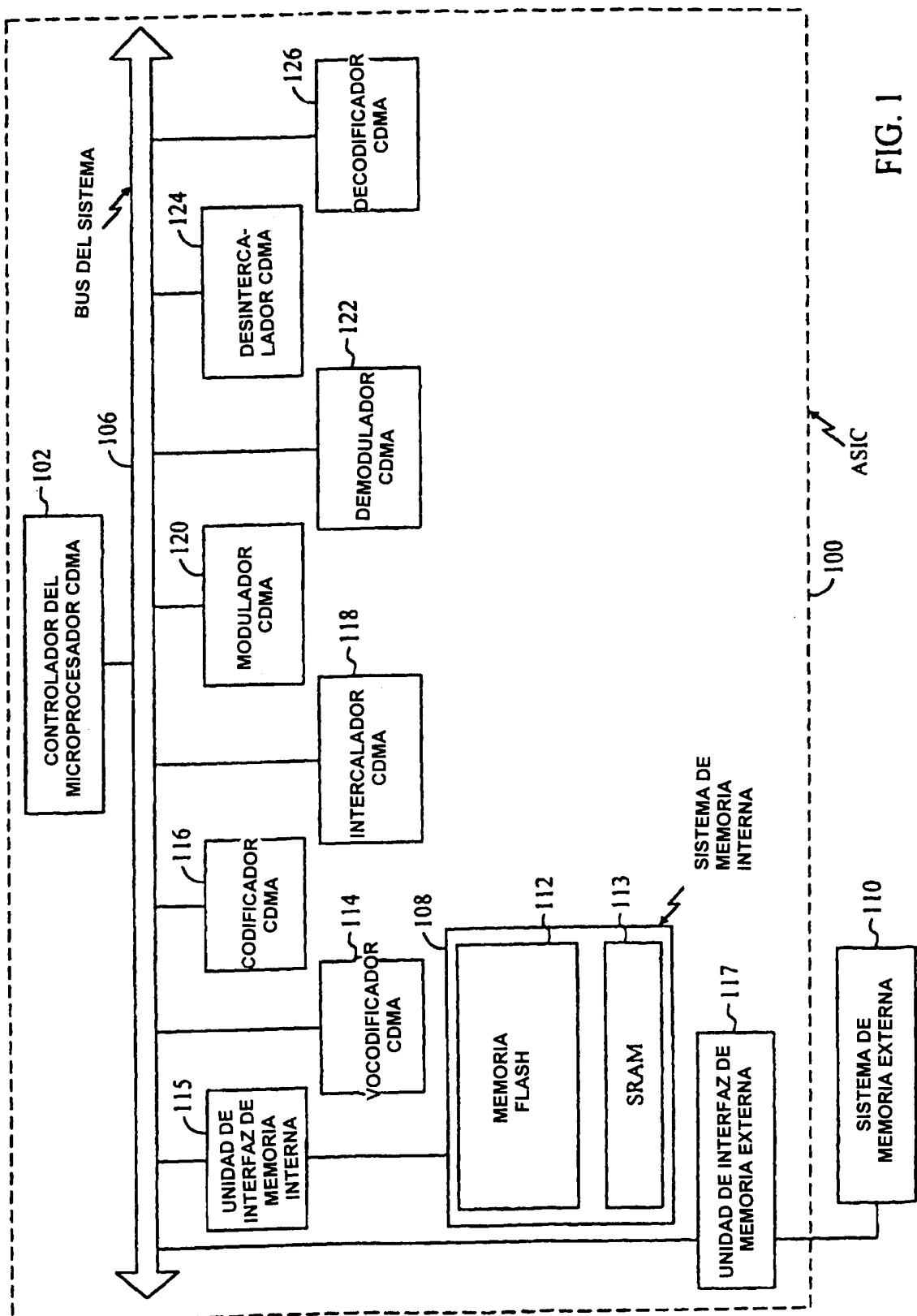

La Figura 1 es un diagrama de bloques de un ASIC de módem de voz y datos que presenta un sistema de memoria flash y SRAM incorporado e integrado para ser utilizado en un teléfono móvil.

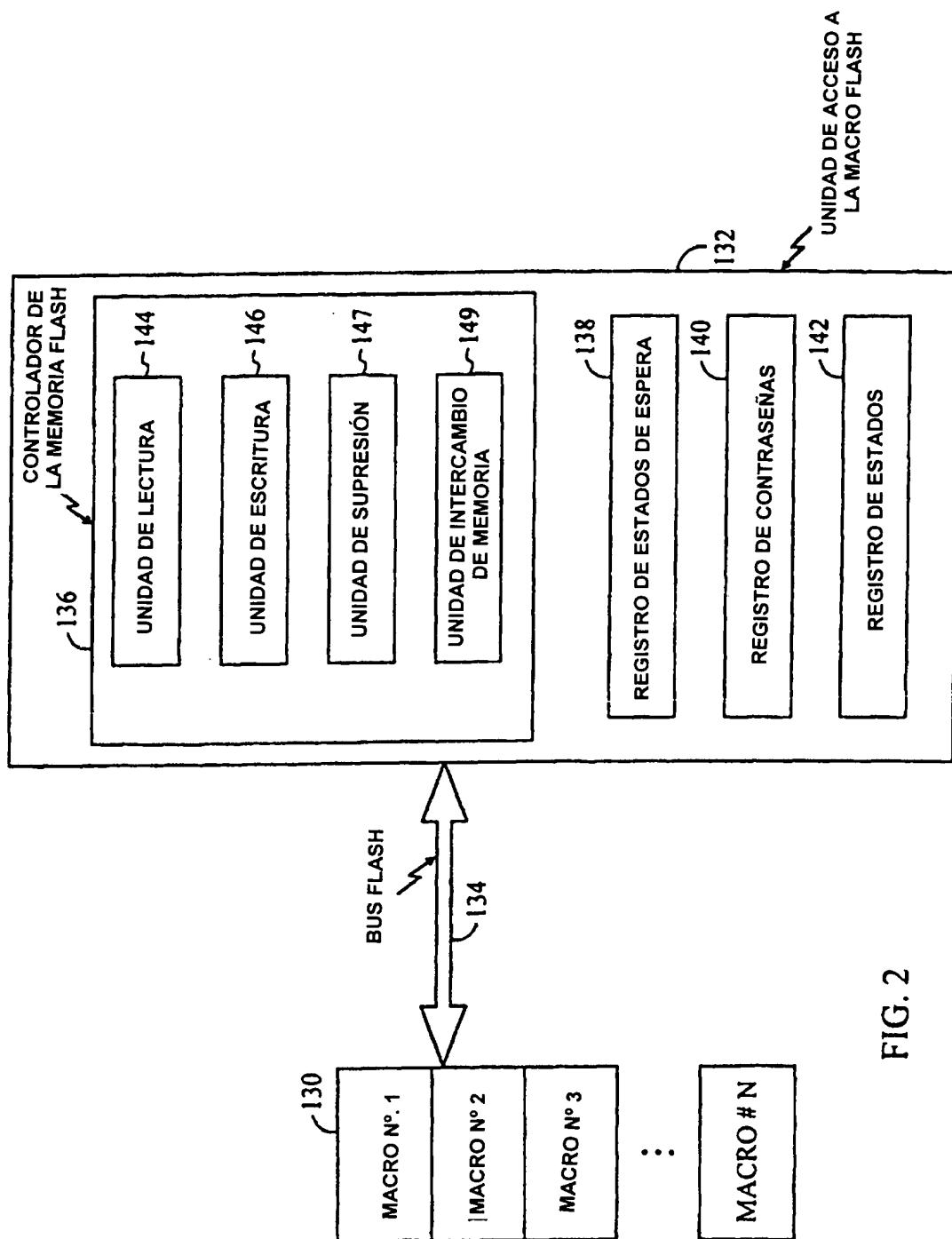

La Figura 2 es un diagrama de bloques del sistema de memoria flash del ASIC de la Figura 1.

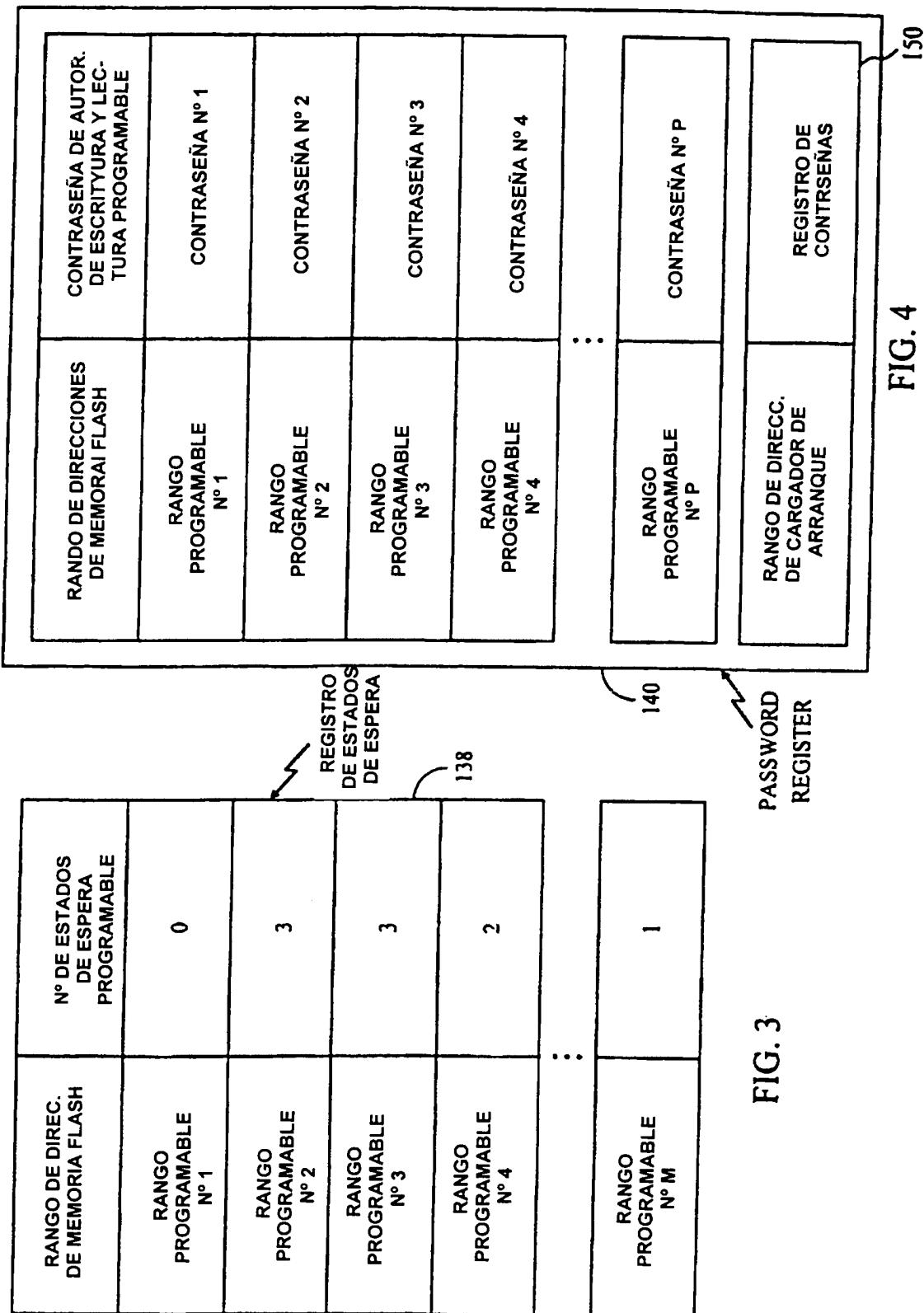

La Figura 3 es un diagrama de bloques de una memoria de estados de espera para ser utilizada en el sistema de memoria flash de la Figura 2.

La Figura 4 es un diagrama de bloques de una memoria de contraseñas para ser utilizada en el sistema de memoria flash de la Figura 2.

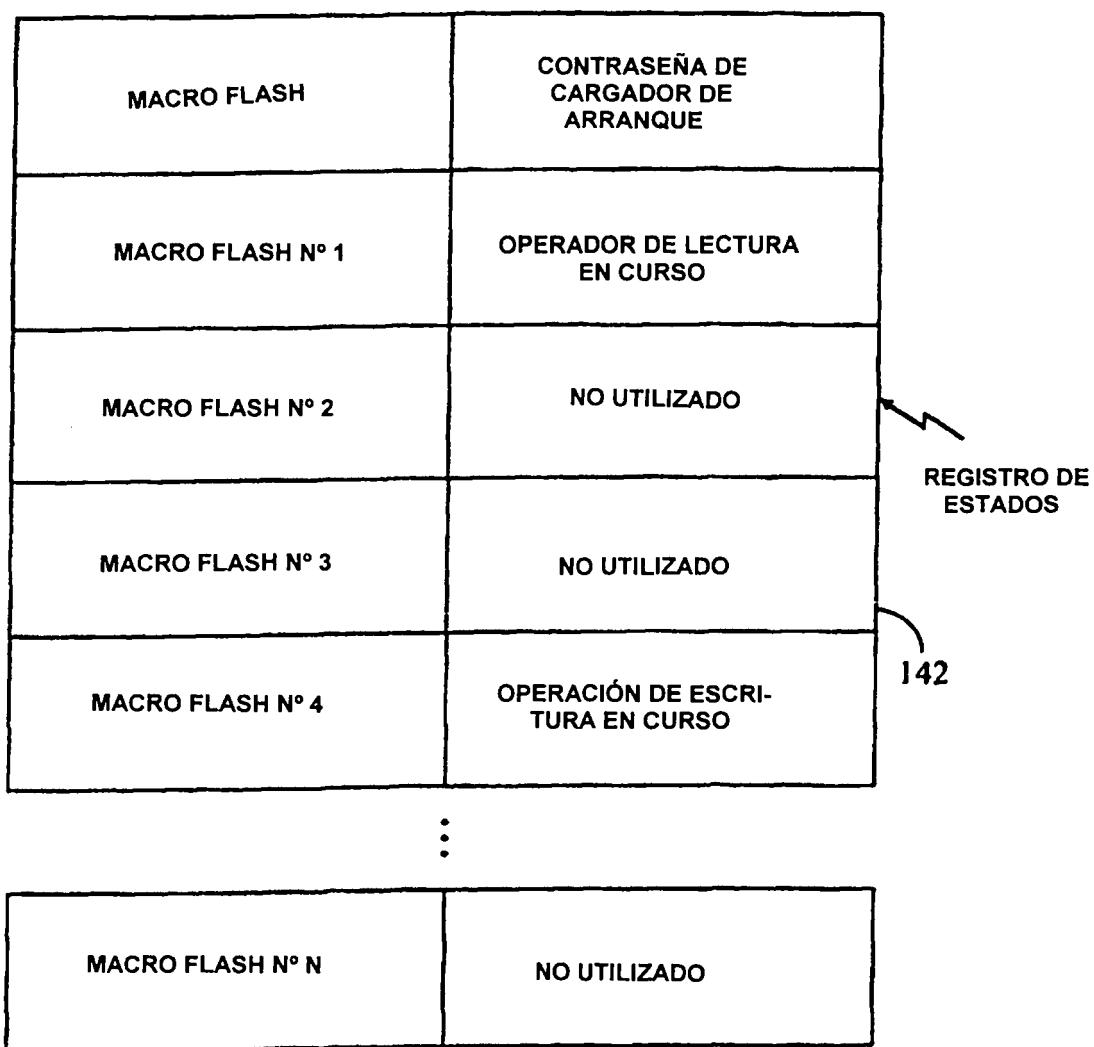

La Figura 5 es un diagrama de bloques de un registro de estados de memoria flash para ser utilizado con el sistema de memoria flash de la Figura 2.

La Figura 6 es un diagrama de bloques de un espacio de memoria divisible de la memoria flash de la Figura 2.

#### Descripción detallada de aspectos de la invención exemplares

Con referencia a las Figuras, se describirán a continuación algunos ejemplos de los aspectos de la presente invención. La presente invención se describirá principalmente con referencia a un sistema de memoria flash y SRAM incorporada e integrada para utilizar con un ASIC de módem de voz y datos de un teléfono celular CDMA. No obstante, los principios de la presente invención son también aplicables a otros sistemas.

La Figura 1 ilustra un ASIC de módem de voz

y datos 100 para ser utilizado en un dispositivo móvil de comunicaciones inalámbricas, tal como un teléfono celular configurado para funcionar dentro de un sistema de comunicación inalámbrica CDMA. El ASIC del módem de voz y datos incluye unos circuitos encargados de las funciones de telefonía del teléfono celular. Aunque no se representan, el teléfono celular puede incluir otros ASIC u otros circuitos integrados configurados para realizar otras funciones. Por ejemplo, si el teléfono celular está configurado como un teléfono inteligente para proporcionar tanto funciones de PDA como funciones de telefonía inalámbrica, puede proporcionarse un ASIC separado para controlar las funciones de PDA. Como alternativa, todas las funciones pueden integrarse dentro de un solo ASIC.

Para gestionar las funciones de telefonía inalámbrica del teléfono celular, el ASIC incluye un microprocesador 102 que controla las funciones del módem de voz y datos. El microprocesador puede ser, por ejemplo, un microprocesador de conjunto de instrucciones reducido (RISC), tal como el microprocesador ARM 7TDMI proporcionado por Arm, Inc. ARM 7TDMI y Arm, Inc. son marcas registradas de Arm, Inc. En otras implementaciones, se emplean otros microprocesadores que incluyen, por ejemplo, los microprocesadores de conjunto de instrucciones complejo (CISC). Dentro del ASIC, se incluyen diversos componentes periféricos, denotados de forma general por 104, que realizan funciones de telefonía inalámbrica CDMA específicas.

Un bus del sistema 106 interconecta el microprocesador y los diversos componentes CDMA periféricos. En funcionamiento, el microprocesador controla los diversos componentes CDMA periféricos, por medio del bus del sistema, para realizar diversas funciones relacionadas con el procesamiento de las comunicaciones inalámbricas CDMA, tales como la conversión de las señales CDMA recibidas desde una estación base (no representada) en señales de voz para reproducirlas a través de un altavoz del teléfono celular, o la conversión de las señales de voz recibidas desde el micrófono del teléfono celular en señales CDMA para transmitirlas a la estación base. Cuando se realizan estas y otras funciones, el microprocesador y los componentes periféricos almacenan datos u otro tipo de información, ya sea en un sistema de memoria interna 108 contenido en el ASIC, o bien en un sistema de memoria externa 110 que puede comprender uno o más chips de memoria SRAM, DRAM o flash montados dentro del teléfono celular y fuera del ASIC. En general, los datos u otro tipo de información a los que es necesario acceder con rapidez, tales como los datos utilizados con referencia al procesamiento en tiempo real de las llamadas telefónicas y similares, se almacenan dentro del sistema de memoria interna para facilitar el acceso. Los datos que no necesitan ser recuperados con tanta rapidez, tales como los datos que se van a utilizar en funciones de tiempo no real, se almacenan en el sistema de memoria externa.

El sistema de memoria interna incluye un sistema de memoria flash 112 y una SRAM 113 integrada como un solo sistema de memoria. En el ejemplo de implementación de la Figura 1, los circuitos del sistema de memoria único y los circuitos del microprocesador y los componentes CDMA periféricos están integrados en una sola placa de silicio. En otras implementaciones, los circuitos del sistema de memoria

único se proporcionan en una placa y el microprocesador y los componentes CDMA periféricos se proporcionan en otra placa. Preferentemente, en esta implementación, las dos placas de silicio separadas están integradas dentro de un solo chip. En cualquier caso, una unidad de interfaz de memoria interna 115 interconecta el sistema de memoria interna con el microprocesador y los componentes CDMA periféricos por medio del bus del sistema 106. Una unidad de interfaz de memoria externa 117 interconecta el sistema de memoria externa con el microprocesador y los componentes CDMA periféricos a través del bus del sistema 106 también.

La memoria flash del sistema de memoria flash 112 del sistema de memoria interna se utiliza principalmente para almacenar el código de software CDMA que va a ser utilizado por el microprocesador o los componentes CDMA periféricos. Habitualmente, la memoria flash incluye también un cargador de arranque que es recuperado y ejecutado por el microprocesador durante la operación de encendido inicial. El cargador de arranque incluye instrucciones para acceder a otros programas CDMA almacenados dentro de la memoria flash, y ejecutarlos. La memoria flash se emplea asimismo para permitir el almacenamiento no volátil de los datos utilizados en relación con el teléfono celular, tal como los nombres, los números de teléfono, las direcciones y similares. Si el teléfono celular está configurado como un teléfono inteligente para realizar además las operaciones de un PDA, entonces los datos utilizados por el PDA, tales como los datos de fechas de reuniones, calendarios de trabajo, horarios, notas de voz y similares se almacenan también en la memoria flash. En general, cualquier tipo de software o datos que sea necesario conservar aun cuando el teléfono celular haya sido completamente apagado se almacenará preferentemente en el sistema de memoria flash incorporado en el ASIC o en el sistema de memoria flash proporcionado dentro de la memoria externa, si lo hubiera.

La SRAM 113 incorporada permite el almacenamiento volátil de otros tipos de datos o programas de software empleados por el microprocesador o los componentes periféricos en relación con sus funciones. Por ejemplo, cuando se reciben señales CDMA desde una estación base durante una conversación telefónica celular, los diversos componentes periféricos pueden almacenar las señales, o las versiones procesadas de éstas, dentro de la SRAM. En un ejemplo específico, una vez que el decodificador de Viterbi ha procesado las señales de entrada, los símbolos decodificados para la voz se almacenan dentro de la SRAM en espera de ser procesados posteriormente por el vocodificador. La memoria externa puede emplearse también como una memoria volátil para almacenar datos y, particularmente, datos a los cuales no es necesario acceder a altas velocidades.

A continuación, haciendo referencia brevemente a los componentes CDMA periféricos del ASIC 100, para la transmisión de las señales, se proporciona un vocodificador 114 que puede incluir un DSP que convierte las señales de voz recibidas a través de un micrófono (no representado) en símbolos digitalizados u otros paquetes de información. Un codificador CDMA 116 codifica los símbolos generados por el vocodificador para detectar y corregir los errores. Un intercalador CDMA 118 intercala las señales codificadas para proporcionar diversidad en el tiempo y reducir,

de esta manera, la potencia de transmisión. Un modulador CDMA 120 modula las señales intercaladas que van a ser transmitidas posteriormente por medio de una antena (no representada). Para procesar las señales recibidas, un demodulador CDMA 122 demodula las señales, un desintercalador 124 desintercala las señales para eliminar el efecto de cualquier intercalación previa, y un decodificador CDMA 126 decodifica las señales para extraer las señales de voz o datos codificados en las mismas. En las comunicaciones de voz, las señales de voz decodificadas se proporcionan al usuario del teléfono a través de un altavoz (no representado). En las comunicaciones de datos, las señales de datos decodificadas son sometidas por otros componentes del teléfono a un procesamiento adicional, tal como, por ejemplo, un procesamiento para la presentación visual (en una pantalla no representada) utilizando un programa de navegador web, un programa de correo electrónico o un programa similar.

Por lo tanto, la Figura 1, ilustra, entre otras características, un ASIC que presenta una memoria flash y una SRAM incorporadas. La incorporación de la memoria flash y la SRAM en el ASIC permite el acercamiento físico entre el microprocesador, la memoria flash y la SRAM. En consecuencia, las señales del bus de datos y de control que se desplazan desde el microprocesador hasta la memoria, y viceversa, sufren menos retardos de encaminamiento y capacitancia que en las placas de circuito impreso cuando se utiliza memoria externa al chip. Esto reduce el tiempo global de acceso a la memoria y aumenta la velocidad de procesamiento global. Asimismo, gracias a la incorporación de la memoria flash y SRAM en el ASIC, es posible reducir el tamaño global de los componentes electrónicos del teléfono celular, en comparación con los sistemas que requieren que toda la memoria sea externa al ASIC. Por lo tanto, el teléfono celular puede configurarse utilizando un diseño de tamaño y grosor reducidos. La incorporación de la memoria flash y la SRAM en el ASIC permite también ahorrar una cantidad significativa de energía. En particular, si la memoria flash y la SRAM se proporcionan fuera del chip, se consume una cantidad considerable de potencia y energía en la commutación de los diversos pins de entrada/salida necesarios para acceder a la memoria flash y la SRAM y a las pistas de señal de la placa de circuito impreso. Por lo tanto, si se almacenan los datos y los programas a los que se necesita acceder con frecuencia en la memoria flash y la SRAM incorporadas, se conseguirá reducir el consumo de potencia y, con ello, el tiempo de espera del teléfono celular, pudiendo entonces el cliente prolongar el tiempo de utilización del teléfono antes de efectuar una recarga del mismo. Además, el consumo global de corriente mientras los dispositivos están activos es menor y, por lo tanto, todavía se reduce más el consumo de energía. Preferentemente, el bus del sistema, el microprocesador y el sistema de memoria interna están configurados para procesar trayectorias de datos de 32 bits. Habitualmente, se accede a la memoria flash y SRAM externas utilizando sólo una trayectoria de datos de 8 bits. Por lo tanto, si se incorpora una trayectoria de datos de 32 bits, los tiempos se reducirán todavía más. Por otra parte, puesto que es posible procesar una mayor cantidad de datos durante cada ciclo de reloj, las frecuencias de reloj globales de los componentes del ASIC pueden reducirse, disminuyendo aún más el consumo de potencia. En el caso

de la memoria externa al chip, no es habitual utilizar trayectorias de datos de 32 bits debido a limitaciones de pins y de encaminamiento. Otra de las ventajas de la provisión de la memoria flash y la SRAM incorporadas en el ASIC es que se reduce el número total de chips necesarios en la placa madre del teléfono celular y, gracias a la simplificación de los procesos de fabricación, se incrementa la fiabilidad.

Por lo tanto, el hecho de proporcionar una memoria flash y una SRAM incorporadas en el ASIC 100 aporta numerosas ventajas. En lo sucesivo, se describirán en mayor detalle las características específicas de la memoria flash y la SRAM del sistema de memoria interna. Estas características proporcionan, por ejemplo, un menor tiempo de acceso, una mayor protección contra las operaciones de reescritura accidentales u otras ventajas similares.

Con referencia a la Figura 2, el sistema de memoria flash incorporada incluye una matriz de memoria flash 130 y un controlador de memoria flash 132. La matriz de memoria flash 130 incluye celdas de memoria flash que definen hasta N macros flash diferentes a las que es posible acceder independientemente como se indicará más adelante. Dicho de otro modo, en una macro flash, puede realizarse una operación de lectura mientras se realiza una operación de escritura en otra de las macros flash. En un ejemplo concreto, N se establece en 4 y, entonces, la memoria flash puede subdividirse en un total de cuatro macros flash separadas. Un bus del sistema de memoria flash 134 interconecta la matriz de memoria flash y el controlador flash, y permite que el controlador flash acceda a la matriz de memoria flash para realizar operaciones de lectura o escritura. Preferentemente, los tres componentes se configuran para adaptarse a trayectorias de datos de 32 bits. El controlador flash 132 incluye una unidad de acceso a la macro flash 136 y diversos registros de memoria, incluido un registro de estados de espera programable 138, un registro de contraseñas programable 140 y un registro de estados 142. La unidad de acceso a la memoria flash utiliza la información almacenada en los diversos registros para controlar el acceso a las macros flash de la matriz de memoria flash. Más adelante, se describirá con mayor detalle la información almacenada en los registros y la manera en que se utiliza dicha información.

La unidad de acceso a la memoria flash 136 incluye una unidad de lectura de memoria flash 144 y una unidad de escritura de memoria flash 146. La unidad de lectura se utiliza para leer los datos o los programas de software almacenados en la unidad de memoria flash. La unidad de escritura se utiliza para reprogramar partes de la memoria flash para que almacenen nuevos datos o nuevos programas. Las unidades de lectura y escritura proporcionan conjuntamente unos medios de lectura durante escritura que permiten realizar simultáneamente una operación de lectura en una de las macros flash y una operación de escritura en otra de las macros flash. Por lo tanto, en un ejemplo específico, la unidad de lectura 144 puede realizar una operación de lectura en la macro flash nº 1, mientras la unidad de escritura realiza una operación de escritura en la macro flash nº 2. En una operación de lectura, se envía, a la matriz de memoria flash 130, un mandato de lectura en el que se especifica una dirección de memoria particular dentro del conjunto de la matriz de memoria, a través del bus flash 134. En el caso de una operación de lectura de la macro flash nº 1,

la dirección indicará una dirección de memoria de 32 bits de los espacios de dirección de la macro flash nº 1. Asimismo, en una operación de escritura, se envía un mandato de escritura a la memoria flash, a través del bus flash. El mandato de escritura indica una dirección de la macro flash y, además, indica los datos que se van a almacenar en ésta. Para una implementación de trayectoria de datos de 32 bits, el mandato de escritura proporcionará 32 bits de datos junto con la dirección de memoria. Además, como se describirá a continuación, las operaciones de escritura sólo se llevan a cabo si se recibe una contraseña correcta desde el microprocesador o un componente periférico, como una parte del mandato de escritura.

Las operaciones de escritura de la memoria flash llevan una cantidad de tiempo sustancialmente superior a la de las operaciones de lectura de la memoria flash. Las operaciones de lectura, por ejemplo, pueden realizarse en un solo ciclo de reloj. Las operaciones de escritura pueden precisar centenares de ciclos de reloj. En consecuencia, es posible realizar una cantidad muy elevada de operaciones de lectura individuales mientras se realiza una sola operación de escritura. Las operaciones de lectura se realizan en una macro cualquiera que no sea la macro sometida a la operación de escritura. Si se recibe, desde el microprocesador, una petición de lectura en la que se especifica una dirección de la macro flash que actualmente está siendo sometida a una operación de escritura, la unidad de acceso a la macro flash pospone la operación de lectura hasta que finalice la operación de escritura. Además, la unidad de acceso a la memoria flash envía, al microprocesador que controla el procesador, una señal para que se suspenda la operación hasta que finalice la operación de escritura. Esto puede realizarse utilizando una señal de interrupción u otra técnica convencional. En otras implementaciones, tales como las implementaciones en las que se emplea un microprocesador capaz de llevar a cabo un procesamiento especulativo, tal vez sea deseable permitir que el microprocesador continúe funcionando mientras se está realizando la operación de escritura.

Por consiguiente, se proporciona un mecanismo de lectura durante escritura. El mecanismo de lectura durante escritura proporciona tiempos de acceso de lectura más rápidos, por término medio, debido a que no es necesario posponer las operaciones de lectura hasta que finalice una operación de escritura pendiente, a menos que la petición de lectura especifique la misma macro flash. Así pues, el sistema global ganará en eficacia, puesto que será capaz de realizar más operaciones dentro de un período de tiempo determinado y podrá ser ejecutado a una frecuencia de reloj que generalmente será más baja, reduciéndose de ese modo el consumo de energía.

La unidad de acceso a la memoria flash incluye además una unidad de supresión 147 para suprimir partes de la memoria flash. La unidad de supresión recibe, desde el microprocesador u otro componente, un mandato de supresión en el que se indica una dirección de partida y la cantidad de datos que deben suprimirse. El mandato de supresión puede indicar la supresión de una sola palabra (32 bits), una página entera o toda la matriz de memoria flash. Como en las operaciones de escritura, las operaciones de lectura sólo se realizan si se recibe una contraseña correcta desde el microprocesador o un componente periférico, como una parte del mandato de supresión.

Durante una operación de supresión de toda la matriz de memoria flash, denominada operación de “supresión masiva” en la presente memoria, las demás peticiones de lectura o escritura para la memoria flash se bloquean hasta que finaliza la operación de supresión masiva. En el ejemplo de implementación, también se bloquean todas las operaciones de memoria flash cuando se suprime una página de la memoria flash, aunque la operación vaya a realizarse en una macro flash distinta de la macro flash que está siendo sometida a la supresión de una página. En otras implementaciones, se permiten operaciones de memoria flash en otras macros flash que no están afectadas por la supresión de la página. Asimismo, dependiendo de la implementación particular de la memoria flash, tal vez sea necesario realizar una operación de supresión antes de cualquier operación (o programa) de escritura. Más particularmente, si la memoria flash está configurada para que una operación de escritura sólo pueda provocar el cambio de un bit “uno” por un bit “cero”, entonces será necesario realizar una operación de supresión en la palabra o las palabras donde se va a escribir antes de realizar la operación de escritura concreta. La operación de supresión convierte todos los bits programados previamente como “cero” en bits “uno”, de tal forma que la subsiguiente operación de escritura puede reprogramar los bits seleccionados de la palabra como bits “cero”. En dicha implementación, por lo tanto, cuando la unidad de escritura de memoria flash 146 recibe un mandato de escritura, la unidad controla en primer lugar la unidad de supresión 147 para suprimir la palabra o las palabras sometidas a la operación de escritura antes de realizar la operación de escritura. Otra posibilidad, es que la unidad de escritura 146 no realice de forma automática una operación de supresión antes de una operación de escritura. En dicha implementación, los diseñadores de software deberán asegurarse de que el software que accede a la memoria flash realice las operaciones de supresión antes de las operaciones de escritura.

La unidad de acceso a la memoria flash incluye también una unidad de intercambio de memoria 149 para intercambiar las partes de memoria alta y baja del espacio de dirección de la memoria global de la matriz de memoria 130. La operación de la unidad de intercambio de memoria se describirá en mayor detalle con referencia a la Figura 5.

La Figura 3 ilustra el registro de memoria de estados de espera 138 para los estados de espera del bus flash, dispuesto para ser utilizado con diferentes partes de la matriz de la memoria flash. El registro de memoria de estados de espera incluye M registros de memoria separados para almacenar los valores de estado de espera asociados a M partes separadas de la matriz de memoria flash. En una implementación, M se establece en N, de tal forma que sólo existe un registro de estados de espera separado para cada macro flash. En otras implementaciones, pueden existir varios registros de estados de espera por cada macro flash o varias macros flash por cada registro de estados de espera. En una implementación específica, N se establece en cuatro y M se establece en 16. Cada registro de estados de espera contiene un valor de estados de espera para utilizar durante las operaciones de lectura en cualquier dirección de memoria de una correspondiente parte de la matriz de memoria. El valor de estados de espera indica el número de ciclos del bus de la memoria flash que la unidad de acceso a

la memoria flash debe esperar hasta que se recuperan los datos por medio de una operación de lectura. Si el valor de estados de espera se establece en cero, la unidad de acceso a la memoria flash accede al bus flash durante el ciclo de reloj inmediatamente posterior al ciclo de reloj en el que se ha validado una operación de lectura para la matriz flash. Si el valor de estados de espera se establece en 3, entonces la unidad de acceso a la memoria flash espera tres ciclos de reloj tras la aserción de una operación de lectura.

Las diferentes partes de la matriz de la memoria flash pueden presentar diferentes valores de estados de espera para adaptarse a los diferentes grados de degradación de las matrices de memoria flash. De manera esquemática, cuánto más a menudo se escriba en una celda flash, más lentamente responderá la celda flash a las subsiguientes operaciones de lectura. Debido a que en las diferentes partes de la memoria flash se almacenan tipos de datos o programas diferentes, se producirán diferentes grados de degradación del tiempo de lectura. Más particularmente, las partes de la memoria flash que se reescriben con frecuencia, tales como las partes utilizadas para almacenar notas de voz, están sometidas a una mayor cantidad de degradación que las partes de la memoria flash que se reescriben con poca frecuencia, tales como las partes en las que se almacena el cargador de arranque. (En una implementación descrita más adelante, el cargador de arranque se introduce y retira de la memoria alta dando por resultado cierto grado de degradación en las celdas de memoria utilizadas para almacenar el cargador de arranque.)

Por lo tanto, se almacena un valor de estados de espera separado en el registro de estados de espera de cada parte de la memoria, que depende del grado de degradación esperado de dicha memoria. Para aquellas partes de la memoria cuya reprogramación se preve que ocurra sólo de vez en cuando, se preprograma un estado de espera de cero dentro del correspondiente registro de la memoria de estados de espera. Para aquellas partes de la matriz cuya reprogramación se preve que ocurra con frecuencia, se preprograma un valor de estados de espera de 3, preferentemente. La cantidad de reprogramación esperada se determina de antemano, basándose en el diseño de hardware y software global del sistema. Por lo tanto, si ciertos componentes de hardware y software que realizan frecuentes operaciones de escritura en la memoria flash, tales como los componentes de notas de voz, están diseñados para utilizar sólo la macro flash nº 3, entonces el valor de estados de espera para la macro flash nº 3 se preestablece en 3. Otra posibilidad es que se preestablezca un valor de estados de espera 0 para la macro flash nº 1, un valor de estados de espera 1 para la macro flash nº 2, un valor de estados de espera 2 para la macro flash nº 3, y así sucesivamente. Los diseñadores de software y hardware pueden diseñar los sistemas para que éstos realicen las operaciones de escritura en las macros flash según la frecuencia de escritura esperada. Los diseñadores que crean un tipo de hardware o software que realiza frecuentes escrituras en la memoria flash configurarán los sistemas para que éstos escriban en la macro flash nº 4. Los diseñadores que crean un tipo de hardware o software que sólo escribe en la memoria flash de vez en cuando configurarán los sistemas para que éstos escriban en la macro flash nº 1. Otra posibilidad es que la unidad de acceso a la memoria flash esté configurada para

realizar el seguimiento del número de operaciones de escritura llevadas a cabo en cada macro flash, y para incrementar selectivamente el número de estados de espera asociados, en la medida que corresponda. Los registros de estados de espera se preestablecen todos en cero en el momento de la fabricación del teléfono celular. Más adelante, dependiendo del grado de reescritura al que son sometidas las diferentes macros flash durante la utilización del teléfono celular, los valores individuales almacenados dentro de los registros de estados de espera se pueden restablecer selectivamente en 1, luego en 2 tal vez y, finalmente, en 3 o un valor superior. Dependiendo de la memoria flash particular utilizada, y del uso que se hace del teléfono celular, los registros de estados de espera tal vez no se restablezcan del valor cero al valor uno hasta al cabo de un año o dos o tal vez no alcancen nunca el valor 3. En otros casos, quizás sea necesario restablecer los valores con más frecuencia. En otras implementaciones, se proporciona un número aún mayor de valores de estados de espera, incluidos, por ejemplo, los valores de estados de espera de cero a 10. El número total de valores de estados de espera y el número de operaciones de reprogramación realizadas antes de incrementar el número de estados de espera depende en gran medida de la matriz de memoria flash, el bus flash y el controlador flash particulares, así como de la frecuencia global del reloj utilizado para controlar los diversos componentes. No obstante, con cada selección de componentes y cada selección de señal de reloj, pueden realizarse experimentos rutinarios para determinar los valores aceptables u óptimos de los valores de estados de espera, y para determinar con qué frecuencia es necesario incrementar los valores de estados de espera. En cualquier caso, proporcionando valores de estados de espera programables, es posible reducir los tiempos medios de acceso a la memoria, e incrementar de ese modo todavía más la velocidad de procesamiento o utilizar un reloj más lento para conseguir velocidades de procesamiento similares.

La Figura 4 ilustra el registro de contraseñas de la memoria flash 140 en el que se almacenan las contraseñas asociadas a las diferentes partes de la matriz de memoria flash. En el registro de contraseñas de la memoria flash, se almacenan P contraseñas, cada una de las cuales está asociada a una correspondiente parte de la matriz de memoria flash. En un ejemplo, P se establece en 16. Para facilitar la programación, P puede establecerse en el mismo valor de M. En cada registro de contraseña particular, se almacena una contraseña exclusiva necesaria para poder realizar una operación de escritura o supresión en la parte correspondiente de la matriz de memoria. Por lo tanto, cada mandato de escritura recibido desde el microprocesador u otro componente del ASIC especifica una contraseña, junto con una dirección de memoria y los datos que se van a escribir en esa dirección. Cada mandato de supresión indica también una contraseña, junto con las direcciones de memoria que deben suprimirse. Cuando se recibe un mandato de escritura, la unidad de escritura 146 (Figura 2) compara la contraseña recibida dentro del mandato de escritura con la contraseña almacenada en el registro de contraseña de la dirección de memoria indicada en el mandato de escritura. Si las contraseñas coinciden, la unidad de escritura procede a realizar el mandato de escritura enviando la operación de escritura a la memoria flash. Si las contraseñas no coinciden, la unidad de escritura envía

una señal de error al componente que emite el mandato de escritura, en el que se le indica que el mandato de escritura no ha podido ser realizado debido a una contraseña incorrecta. Los mandatos de supresión son tratados de la misma manera.

De esta forma, pues, es como se proporciona la protección por contraseña. La protección por contraseña está destinada, en parte, a impedir la supresión o reprogramación accidental de algunas áreas de la memoria flash, que podría producirse quizás como consecuencia de un error de software o similar. En este sentido, es bastante improbable que un mandato de escritura o supresión accidental incluya la contraseña correcta. Asimismo, si el conjunto del sistema está configurado para que los diferentes componentes periféricos lean y escriban en partes diferentes de la memoria flash, entonces la protección por contraseña impide también que un componente periférico escriba accidentalmente en un área de la memoria reservada a otro componente. Por ejemplo, el vocodificador puede leer o escribir sólo en la memoria flash nº 2. Como alternativa, se pueden proporcionar otros protocolos de contraseña. Por ejemplo, en lugar de asociar una contraseña diferente a cada parte diferente de la memoria, es posible asociar directamente contraseñas diferentes a distintos componentes emisores. Por ello, será posible, por ejemplo, asociar una primera contraseña a los mandatos recibidos desde el microprocesador y una segunda contraseña a los mandatos recibidos desde el vocodificador. A pesar de que en esta implementación cada dispositivo puede leer o escribir potencialmente en cualquiera de las macros flash, el riesgo de realizar operaciones de escritura accidentales se reduce al mínimo. Cada contraseña puede ser, por ejemplo, una secuencia binaria exclusiva de 16 bits. Mediante la protección por contraseña, se evita la pérdida de datos importantes, tales como los números de teléfono de la policía, los bomberos o similares. Asimismo, se reduce el riesgo de que se alteren partes del código CDMA almacenado en la memoria flash. En un caso extremo, la alteración de uno o varios de los programas CDMA almacenados en la memoria flash podría provocar el fallo de todo el teléfono celular, hecho que obligaría al cliente a devolver el teléfono celular al fabricante para su reemplazo o reparación. En otras implementaciones, el usuario puede tener capacidad para registrar contraseñas particulares que serán utilizadas con los datos almacenados por el usuario. Por ejemplo, si una de las macros flash se utiliza exclusivamente para almacenar notas de voz, el usuario puede introducir una contraseña exclusiva, por medio del teclado del teléfono celular, impidiendo de ese modo el acceso no autorizado a la nota de voz por otro usuario del teléfono. Asimismo, las partes particulares de la memoria destinadas a almacenar números de teléfono, direcciones y similares pueden tener asociada, también, una contraseña introducida por el usuario para impedir el acceso no autorizado. Como puede apreciarse, existe una amplia diversidad de contextos diferentes para la utilización de contraseñas.

Como se ha indicado, una parte de la matriz de memoria flash puede ser empleada para almacenar un cargador de arranque. Se dispone de un registro de contraseña adicional e independiente 150 para la parte de memoria en la que se almacena el cargador de arranque. En consecuencia, no se ejecutará ningún mandato de escritura o supresión que afecte a la parte de la memoria en la que se almacena el carga-

dor de arranque, a menos que el mandato proporcione además la contraseña independiente del cargador de arranque. De esta forma, pues, se proporciona un nivel adicional de protección mediante contraseña al cargador de arranque, que es un elemento crucial, y se reduce al mínimo el riesgo de que el cargador de arranque sea alterado por error.

La Figura 5 ilustra el registro de estados de la memoria flash 142, en el que se almacena el estado de las macros flash de la matriz de memoria flash. El registro de estados incluye N elementos de memoria individuales en los que se almacena por separado el estado de cada una de las N macros flash. Cada registro de estado indica, entre otras características posibles, si la macro flash correspondiente está siendo sometida actualmente a una operación de lectura o escritura pendiente. Además, el registro de estado puede indicar también la entidad software o hardware que realiza la operación de lectura o escritura. Si se almacena la identidad del dispositivo a partir del cual se deriva la operación de lectura o escritura, el microprocesador podrá determinar, mediante unas tablas de asignación de prioridades adecuadas mantenidas por el microprocesador, si una operación de memoria flash recién solicitada es de prioridad más alta y, de ser así, el microprocesador podrá detener el controlador flash y hacer que éste cancele la operación de lectura o escritura para permitir que la operación de memoria flash de prioridad más alta sea realizada de inmediato.

Además, en los registros de estados, puede almacenarse, asimismo, cualquier indicación del estado de una operación de lectura o escritura actual. Por ejemplo, en el registro de estados, se puede registrar la hora a la que el mandato de lectura o escritura ha sido enviado a la matriz de memoria flash. Por lo tanto, el microprocesador puede acceder al valor de la hora y determinar cuando se prevé que haya finalizado el mandato. Basándose en el hecho de que una operación de escritura habitualmente lleva 100 ciclos de reloj, el microprocesador determina si el mandato de escritura pendiente ha sido emitido recientemente o está a punto de finalizar. El microprocesador podrá decidir, entonces, si interrumpe o no al controlador flash para realizar una operación de escritura de prioridad más alta. Por lo que a las operaciones de lectura respecta, el registro de estados puede indicar el número de ciclos de espera utilizados en relación con la operación de lectura particular. Como puede apreciarse, es po-

sible almacenar una gran variedad de información de estado dentro de un registro de estados, dependiendo de la preprogramación del sistema. En general, la información de estado se proporciona para mejorar la eficacia global del sistema y permitir la realización de un número mayor de operaciones dentro de un período de tiempo determinado, o utilizar una frecuencia de reloj inferior y realizar el mismo número de operaciones por segundo.

La Figura 6 ilustra el funcionamiento de la unidad de intercambio de memoria 149 (Figura 2) que es operativa para intercambiar partes de memoria alta y baja de un espacio de dirección de memoria global 152 de la matriz de memoria 130 (Figura 2). En funcionamiento, el cargador de arranque está almacenado inicialmente en una dirección de memoria más baja del espacio de la memoria (por ejemplo, la dirección 0 x 00). Los programas de software principales se almacenan empezando por una dirección de memoria alta, tal como la dirección 0 x 05800000. El cargador de arranque incluye mandatos que especifican cuál de los programas de software principales de la memoria flash debe ser ejecutado como una parte de una operación de encendido o de reposición. Una vez que el cargador de arranque ha finalizado sus operaciones, la unidad de intercambio de memoria intercambia la memoria alta y la memoria baja. Por lo tanto, después de la operación de intercambio, los programas de software flash principales se almacenan empezando por la posición de memoria 0 x 0. El cargador de arranque se almacena en una dirección de memoria alta, tal como la dirección 0 x 05800000. Por consiguiente, un salto a la memoria baja permite, entonces, entrar en el software principal de las macros flash. El acceso al software flash principal resultará más fácil de esta forma. Si a continuación se apaga y vuelve a encender el teléfono celular o si se realiza alguna operación de reposición, las direcciones de memoria se intercambian de nuevo y, entonces, el cargador de arranque residirá en la dirección de memoria más baja para permitir que éste empiece a funcionar correctamente.

La descripción anterior hace referencia a algunos ejemplos de los aspectos de un sistema de microprocesador basado en la tecnología CDMA, que presenta una memoria flash y una memoria SRAM incorporadas. Los principios de la presente invención son aplicables también a otros sistemas.

## REIVINDICACIONES

1. Sistema de memoria flash (112) que comprende:

unas celdas de memoria flash dispuestas como un conjunto de macros flash (130), y

unos medios de lectura durante escritura (144, 146) para escribir en una de dichas macros flash, mientras se lee simultáneamente en otra de dichas macros flash; en el que el sistema está conectado a un microprocesador (102) y en el que dichos medios de lectura durante escritura (144, 146) incluyen:

unos medios de escritura (146) para escribir las señales recibidas desde el microprocesador a una macro seleccionada de dichas macros flash (130); y

**caracterizado** porque dichos medios de lectura durante escritura incluyen además unos medios de suspensión, sensibles a la recepción de un mandato de lectura del microprocesador dirigido a dicha macro seleccionada de dichas macros flash, para suspender la operación del microprocesador hasta que los medios de escritura (146) hayan finalizado su operación, y para ejecutar el mandato de lectura.

2. Sistema según la reivindicación 1, que incluye además unos medios de almacenamiento (142) para almacenar un valor representativo del estado actual de los medios de lectura durante escritura (144, 146), siendo dicho valor accesible por el microprocesador.

3. Sistema según la reivindicación 1, que comprende además:

un controlador de memoria flash (132);

un bus de memoria flash (134) que interconecta las macros de memoria flash y el controlador de memoria flash;

en el que dicho controlador de memoria flash (132) incluye:

unos medios de almacenamiento (138) para almacenar un número programable de estados de espera asociados a las macros flash, correspondiendo un número programable de estados de espera a cada macro flash, y

unos medios de acceso para acceder a una macro flash seleccionada, que comprenden dichos medios de lectura durante escritura, accediendo dichos medios de acceso a la macro flash seleccionada utilizando el bus de memoria flash programado con el número de estados de espera asociado a la macro flash seleccionada.

4. Sistema según la reivindicación 3, en el que dichos medios de almacenamiento incluyen unas unidades de registro de estados de espera, siendo programable cada una de dichas unidades de registro de estados de espera para representar cualquier número entero de estados de espera.

5. Sistema según la reivindicación 1, que comprende además:

un controlador de memoria flash (132) que incluye:

unos medios de almacenamiento (140) para almacenar una contraseña separada asociada a cada macro flash, y

unos medios de habilitación, sensibles a la recepción de una contraseña válida para una macro seleccionada de dichas macros flash, para habilitar la programación o la supresión de celdas flash de dicha macro flash seleccionada mientras se impide, de forma simultánea, la programación o la supresión de todas las demás celdas flash.

6. Sistema de memoria flash según la reivindicación 5, en el que el software del cargador de arranque se almacena en una parte de las celdas flash de una de dichas macros flash.

7. Sistema de memoria flash según la reivindicación 6, que incluye además:

unos medios de almacenamiento para almacenar una contraseña asociada al cargador de arranque; y

unos medios de habilitación, sensibles a la recepción de una contraseña válida para el cargador de arranque, para habilitar la programación o la supresión de dichas celdas flash de dicho cargador de arranque.

8. Sistema de memoria flash según la reivindicación 6, que incluye además unos medios de supresión (147) para suprimir unas celdas flash seleccionadas de las macros flash, realizando dichos medios de supresión selectivamente una operación de supresión de palabra, una operación de supresión de página o una operación de supresión masiva.

9. Sistema de memoria flash según la reivindicación 6, en el que los medios de almacenamiento (140) para almacenar una contraseña separada asociada a cada macro flash almacenan las contraseñas en una memoria de cableado.

10. Sistema según la reivindicación 1, que comprende además:

un controlador de memoria flash (132) que incluye unos medios de división para dividir dichas celdas de memoria flash en posiciones altas y bajas de memoria;

en el que, en dichas celdas de memoria flash, se almacena un cargador de arranque empezando por la dirección de memoria más baja del espacio de la memoria flash y

en el que dichos medios de división incluyen unos medios de intercambio (149) para intercambiar las posiciones altas y bajas de memoria, una vez que las operaciones realizadas por el cargador de arranque han finalizado.

11. Sistema según la reivindicación 1, que comprende además una unidad de acceso a la memoria flash (136) que presenta dichos medios de lectura durante escritura (144, 146) para escribir en una de dichas macros flash mientras se lee, simultáneamente, otra de dichas macros flash.

FIG. 1

FIG. 2

FIG. 5

FIG. 6