(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6802666号

(P6802666)

(45) 発行日 令和2年12月16日(2020.12.16)

(24) 登録日 令和2年12月1日(2020.12.1)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H03K 19/096 (2006.01)H01L 29/78 617N

H01L 29/78 613Z

H01L 29/78 618B

H03K 19/096 230

請求項の数 5 (全 46 頁)

(21) 出願番号 特願2016-160535 (P2016-160535)

(22) 出願日 平成28年8月18日 (2016.8.18)

(65) 公開番号 特開2017-41635 (P2017-41635A)

(43) 公開日 平成29年2月23日 (2017.2.23)

審査請求日 令和1年8月5日 (2019.8.5)

(31) 優先権主張番号 特願2015-163532 (P2015-163532)

(32) 優先日 平成27年8月21日 (2015.8.21)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 松崎 隆徳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大貫 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 高橋 優斗

最終頁に続く

(54) 【発明の名称】半導体装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1トランジスタ乃至第4トランジスタと、容量素子と、を有し、

前記第1トランジスタ乃至前記第4トランジスタは、チャネルが形成される半導体層に酸化物半導体を含み、

前記第1トランジスタ乃至前記第4トランジスタのそれぞれは、第1ゲートおよび第2ゲートを有し、

前記第1トランジスタの第1ゲートは、第1配線と電気的に接続され、

前記第1トランジスタの第2ゲートは、前記第1配線と電気的に接続され、

前記第1トランジスタのソースまたはドレインの一方は、前記第1配線と電気的に接続され、 10

前記第1トランジスタのソースまたはドレインの他方は、前記第2トランジスタのソースまたはドレインの一方と電気的に接続され、

前記第2トランジスタのソースまたはドレインの他方は、第2配線と電気的に接続され、

前記第2トランジスタの第1ゲートは、前記第2トランジスタの第2ゲートと電気的に接続され、

前記第3トランジスタのソースまたはドレインの一方は、第3配線と電気的に接続され、

前記第3トランジスタの第1ゲートは、前記第1トランジスタのソースまたはドレイン

10

20

の他方と電気的に接続され、

前記第3トランジスタの第2ゲートは、前記第3トランジスタのソースまたはドレインの他方と電気的に接続され、

前記第4トランジスタのソースまたはドレインの一方は、前記第3トランジスタのソースまたはドレインの他方と電気的に接続され、

前記第4トランジスタのソースまたはドレインの他方は、第4配線と電気的に接続され、

前記第4トランジスタの第1ゲートは、前記第4トランジスタの第2ゲートと電気的に接続され、

前記第2トランジスタの第1ゲートは、前記第4トランジスタの第1ゲートと電気的に接続され、

前記容量素子の一方の電極は、前記第3トランジスタの第1ゲートと電気的に接続され、

前記容量素子の他方の電極は、前記第3トランジスタのソースまたはドレインの他方と電気的に接続されている半導体装置。

#### 【請求項2】

請求項1において、

前記第1トランジスタ乃至前記第4トランジスタのそれぞれが有する前記第1ゲートおよび前記第2ゲートのうち、一方はゲートとして機能し、他方はバックゲートとして機能する半導体装置。

10

20

#### 【請求項3】

請求項1又は請求項2において、

前記第1トランジスタのチャネル長よりも、前記第2トランジスタのチャネル長が短い半導体装置。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第1トランジスタのチャネル幅よりも、前記第2トランジスタのチャネル幅が長い半導体装置。

#### 【請求項5】

請求項1乃至請求項4のいずれか一項に記載の半導体装置と、モーター、蓄電装置、高周波加熱装置、または、スピーカと、を有する電子機器。

30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関するものである。または、本明細書等で開示する発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。特に、本明細書等で開示する発明の一態様は、半導体装置、および半導体装置を有する電子機器に関するものである。

##### 【0002】

40

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置（液晶表示装置、発光表示装置など）、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置および電子機器などは、半導体装置を有する場合がある。

##### 【背景技術】

##### 【0003】

近年、チャネルが形成される半導体層に酸化物半導体（O S : O x i d e S e m i c o n d u c t o r ）を用いたトランジスタ（以下、「O Sトランジスタ」ともいう。）が注目されている。酸化物半導体はスパッタリング法などを用いて成膜できるため、例えば、大型の表示装置を構成するトランジスタの半導体層に用いることができる。また、O Sト

50

ランジスタは、チャネルが形成される半導体層に非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。

#### 【0004】

また、OSトランジスタは、非導通状態において極めてリーク電流が少ないことが知られている。例えば、OSトランジスタの極めてリーク電流が少ないという特性を応用した低消費電力のCPUなどが開示されている（特許文献1参照。）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

10

【特許文献1】特開2012-257187号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、OSトランジスタではpチャネル型トランジスタが実現しにくいことが知られている。そのため、OSトランジスタのみを用いて論理回路を構成するには、単極性の論理回路を構成する必要がある。

#### 【0007】

一方、pチャネル型トランジスタが実現できたとしても、同一基板上にpチャネル型トランジスタとnチャネル型トランジスタを作り分けると作製工程数が増加し、半導体装置の作製コストの増大や、生産性の低下が生じる。そのため、同一基板上に作製する薄膜トランジスタは同じ導電型のトランジスタとすることが好ましい。ただし、同じ導電型のトランジスタで構成する単極性の論理回路では、出力電圧がトランジスタの閾値電圧に相当する分だけ低下するという問題がある。

20

#### 【0008】

本発明の一態様は、生産性の良い半導体装置などを提供することを課題の一とする。または、消費電力の少ない半導体装置などを提供することを課題の一とする。または、信頼性の良好な半導体装置などを提供することを課題の一とする。または、本発明の一態様は、単極性の論理回路を含む半導体装置などを提供することを課題の一とする。または、新規な半導体装置などを提供することを課題の一とする。

30

#### 【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様は、第1トランジスタ乃至第4トランジスタと、容量素子と、を有し、第1トランジスタのソースまたはドレインの一方は第1配線と電気的に接続され、第1トランジスタのゲートは第1配線と電気的に接続され、第1トランジスタのソースまたはドレインの他方は、第2トランジスタのソースまたはドレインの一方と電気的に接続され、第2トランジスタのソースまたはドレインの他方は第2配線と電気的に接続され、第2トランジスタのゲートは第4トランジスタのゲートと電気的に接続され、第3トランジスタのソースまたはドレインの一方は第3配線と電気的に接続され、第3トランジスタのソースまたはドレインの他方は、第4トランジスタのソースまたはドレインの一方と電気的に接続され、第3トランジスタのゲートは第1トランジスタのソースまたはドレインの他方と電気的に接続され、第4トランジスタのソースまたはドレインの他方は第4配線と電気的に接続され、容量素子の一方の電極は第3トランジスタのゲートと電気的に接続され、容量素子の他方の電極は第3トランジスタのソースまたはドレインの他方と電気的に接続されていることを特徴とする半導体装置である。

40

50

**【0011】**

または、本発明の一態様は、第1トランジスタ乃至第4トランジスタと、容量素子と、を有し、第1トランジスタ乃至第4トランジスタのそれぞれは、第1ゲートおよび第2ゲートを有し、第1トランジスタの第1ゲートは第1配線と電気的に接続され、第1トランジスタの第2ゲートは第1配線と電気的に接続され、第1トランジスタのソースまたはドレインの一方は第1配線と電気的に接続され、第1トランジスタのソースまたはドレインの他方は第2トランジスタのソースまたはドレインの一方と電気的に接続され、第2トランジスタのソースまたはドレインの他方は第2配線と電気的に接続され、第2トランジスタの第1ゲートは第2トランジスタの第2ゲートと電気的に接続され、第3トランジスタのソースまたはドレインの一方は第3配線と電気的に接続され、第3トランジスタの第1ゲートは第1トランジスタのソースまたはドレインの他方と電気的に接続され、第3トランジスタの第2ゲートは第3トランジスタのソースまたはドレインの他方と電気的に接続され、第4トランジスタのソースまたはドレインの一方は第3トランジスタのソースまたはドレインの他方と電気的に接続され、第4トランジスタのソースまたはドレインの一方は第4トランジスタの第2ゲートと電気的に接続され、第4トランジスタの第1ゲートは第4トランジスタの第1ゲートと電気的に接続され、容量素子の一方の電極は第3トランジスタの第1ゲートと電気的に接続され、容量素子の他方の電極は第3トランジスタのソースまたはドレインの他方と電気的に接続されていることを特徴とする半導体装置である。第1ゲートおよび第2ゲートの一方はゲートとして機能し、他方はバックゲートとして機能する。

10

20

**【0012】**

上記トランジスタは、チャネルが形成される半導体層に酸化物半導体を含むことが好ましい。

**【0013】**

第1トランジスタのチャネル長よりも、第2トランジスタのチャネル長が短いことが好ましい。また、第1トランジスタのチャネル幅よりも、第2トランジスタのチャネル幅が長いことが好ましい。

**【発明の効果】****【0014】**

生産性の良い半導体装置などを提供することができる。または、消費電力の少ない半導体装置などを提供することができる。または、信頼性の良好な半導体装置などを提供することができる。または、単極性の論理回路を含む半導体装置などを提供することができる。または、新規な半導体装置などを提供することができる。

30

**【0015】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

**【図面の簡単な説明】****【0016】**

40

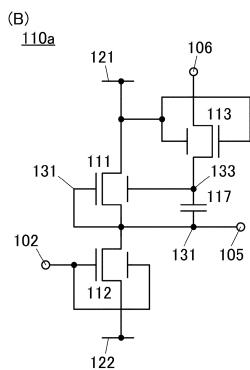

【図1】半導体装置を説明する回路図。

【図2】半導体装置の動作を説明するタイミングチャート。

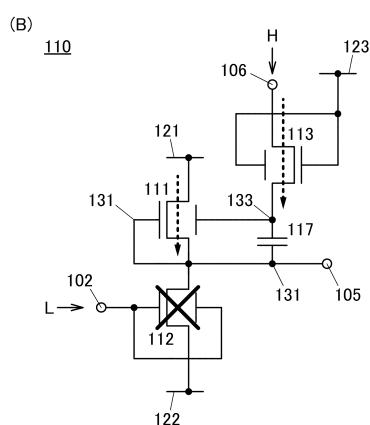

【図3】半導体装置の動作を説明する回路図。

【図4】半導体装置の動作を説明する回路図。

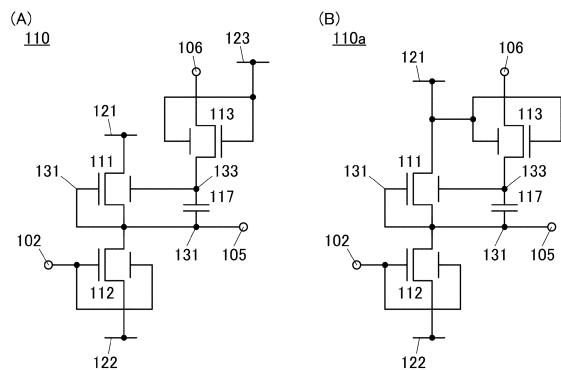

【図5】半導体装置を説明する回路図。

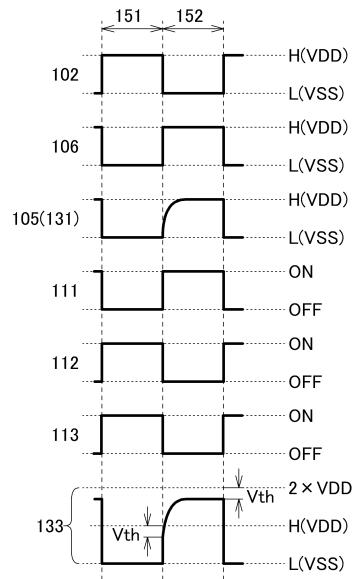

【図6】半導体装置の動作を説明するタイミングチャート。

【図7】半導体装置の動作を説明する回路図。

【図8】半導体装置の動作を説明する回路図。

【図9】半導体装置を説明する回路図。

【図10】トランジスタの一例を説明する図。

50

- 【図11】トランジスタの一例を説明する図。

- 【図12】トランジスタの一例を説明する図。

- 【図13】トランジスタの一例を説明する図。

- 【図14】トランジスタの一例を説明する図。

- 【図15】トランジスタの一例を説明する図。

- 【図16】トランジスタの一例を説明する図。

- 【図17】トランジスタの一例を説明する図。

- 【図18】トランジスタの一例を説明する図。

- 【図19】トランジスタの一例を説明する図。

- 【図20】エネルギー・バンド構造を説明する図。 10

- 【図21】電子部品の作製工程例を説明するフローチャートおよび斜視模式図。

- 【図22】電子機器の一例を説明する図。

- 【図23】電子機器の一例を説明する図。

- 【発明を実施するための形態】**

- 【0017】**

- 実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、 20 その繰り返しの説明は省略する場合がある。

- 【0018】**

- また、図面などにおいて示す各構成の、位置、大きさ、範囲などは、発明の理解を容易とするため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面などに開示された位置、大きさ、範囲などに限定されない。

- 【0019】**

- また、図面において、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。

- 【0020】**

- 本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、工程順または積層順など、なんらかの順番や順位を示すものではない。また、本明細書等において序数詞が付されていない用語であっても、構成要素の混同を避けるため、特許請求の範囲において序数詞が付される場合がある。また、本明細書等において序数詞が付されている用語であっても、特許請求の範囲において異なる序数詞が付される場合がある。また、本明細書等において序数詞が付されている用語であっても、特許請求の範囲などにおいて序数詞を省略する場合がある。 30

- 【0021】**

- また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。 40

- 【0022】**

- なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が直上または直下で、かつ、直接接していることを限定するものではない。例えば、「絶縁層A上の電極B」の表現であれば、絶縁層Aの上に電極Bが直接接して形成されている必要はなく、絶縁層Aと電極Bとの間に他の構成要素を含むものを除外しない。

- 【0023】**

- また、ソースおよびドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合など、動作条件などによって互いに入れ替わるため、いずれがソースまたはドレインであるかを限定することが困難である。このため、 50

本明細書においては、ソースおよびドレインの用語は、入れ替えて用いることができるものとする。

#### 【0024】

また、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

#### 【0025】

10

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。よって、「電気的に接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

#### 【0026】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域（「チャネル形成領域」ともいう。）における、ソース（ソース領域またはソース電極）とドレイン（ドレン領域またはドレン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

20

#### 【0027】

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

30

#### 【0028】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（「実効的なチャネル幅」ともいう。）と、トランジスタの上面図において示されるチャネル幅（「見かけ上のチャネル幅」ともいう。）と、が異なる場合がある。例えば、ゲート電極が半導体層の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲート電極が半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅が大きくなる。

40

#### 【0029】

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

#### 【0030】

そこで、本明細書では、見かけ上のチャネル幅を、「囲い込みチャネル幅（S C W : S u r r o u n d e d C h a n n e l W i d t h ）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネ

50

ル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面T E M像などを解析することなどによって、値を決定することができる。

#### 【0031】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

#### 【0032】

また、本明細書等に示すトランジスタは、明示されている場合を除き、エンハンスメント型（ノーマリーオフ型）の電界効果トランジスタとする。10

#### 【0033】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体のDOS (Density of States) が高くなることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、および酸化物半導体の主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。20

#### 【0034】

また、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」および「直交」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。30

#### 【0035】

なお、本明細書等において、計数値および計量値に関して「同一」、「同じ」、「等しい」または「均一」（これらの同意語を含む）などと言う場合は、明示されている場合を除き、プラスマイナス20%の誤差を含むものとする。

#### 【0036】

また、本明細書において、フォトリソグラフィ工程を行った後にエッチング工程を行う場合は、特段の説明がない限り、フォトリソグラフィ工程で形成したレジストマスクは、エッチング工程終了後に除去するものとする。

#### 【0037】

また、本明細書等において、高電源電位VDD（以下、単に「VDD」または「H電位」ともいう。）とは、低電源電位VSSよりも高い電位の電源電位を示す。また、低電源電位VSS（以下、単に「VSS」または「L電位」ともいう。）とは、高電源電位VDDよりも低い電位の電源電位を示す。また、接地電位をVDDまたはVSSとして用いることもできる。例えばVDDが接地電位の場合には、VSSは接地電位より低い電位であり、VSSが接地電位の場合には、VDDは接地電位より高い電位である。40

#### 【0038】

また、一般に「電圧」とは、ある電位と基準の電位（例えば、接地電位（GND電位）またはソース電位など）との電位差のことを示す場合が多い。また、「電位」は相対的なものであり、基準となる電位によって配線等に与える電位が変化する場合がある。よって「電圧」と「電位」は互いに言い換えることが可能な場合がある。なお、本明細書等では、50

明示される場合を除き、VSSを基準の電位とする。

**【0039】**

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

**【0040】**

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

**【0041】**

(実施の形態1)

10

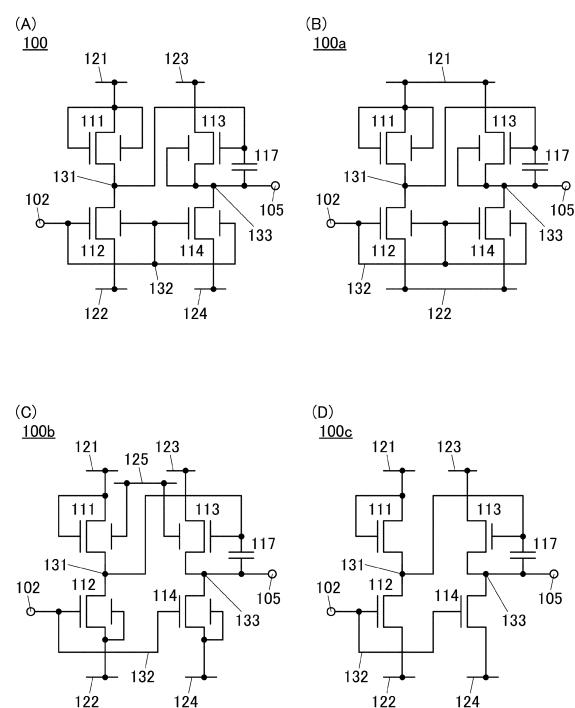

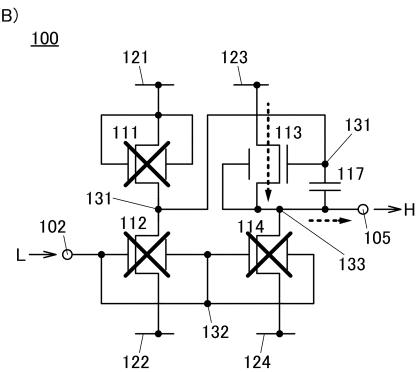

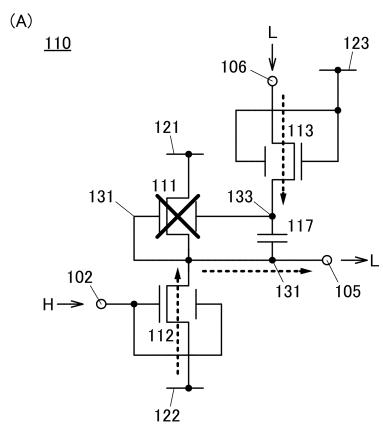

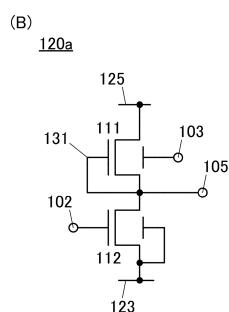

本発明の一態様の半導体装置100について、図面を用いて説明する。図1(A)は半導体装置100の構成を説明する回路図である。

**【0042】**

半導体装置100の構成例

図1(A)に示す半導体装置100は、トランジスタ111乃至トランジスタ114、および容量素子117を有する。トランジスタ111乃至トランジスタ114は、ソース、ドレイン、ゲート、およびバックゲートを有するnチャネル型のトランジスタである。

**【0043】**

ゲートとバックゲートは、両者で半導体層のチャネル形成領域を挟むように配置される。よって、バックゲートはゲートと同様に機能させることができる。なお、バックゲートの電位は、ゲートと同電位としてもよいし、接地電位(GND電位)や、任意の電位としてもよい。また、バックゲートの電位をゲートと連動させず独立して変化させることで、トランジスタの閾値電圧を変化させることができる。本明細書等では、ゲートまたはバックゲートのどちらか一方を、「第1ゲート」といい、他方を「第2ゲート」という場合がある。

20

**【0044】**

図1(A)に示す半導体装置100において、トランジスタ111の、第1ゲートおよび第2ゲートは配線121と電気的に接続され、ソースまたはドレインの一方は配線121と電気的に接続され、ソースまたはドレインの他方はノード131と電気的に接続されている。また、トランジスタ112の、ソースまたはドレインの一方はノード131と電気的に接続され、ソースまたはドレインの他方は配線122と電気的に接続され、第1ゲートおよび第2ゲートはノード132と電気的に接続されている。また、トランジスタ113の、ソースまたはドレインの一方は配線123と電気的に接続され、ソースまたはドレインの他方はノード133と電気的に接続され、第1ゲートまたは第2ゲートの一方はノード133と電気的に接続され、第1ゲートまたは第2ゲートの他方はノード131と電気的に接続されている。また、トランジスタ114の、ソースまたはドレインの一方はノード133と電気的に接続され、ソースまたはドレインの他方は配線124と電気的に接続され、第1ゲートおよび第2ゲートはノード132と電気的に接続されている。また、容量素子117の、一方の電極はノード131と電気的に接続され、他方の電極はノード133と電気的に接続されている。また、ノード132は端子102と電気的に接続され、ノード133は端子105と電気的に接続されている。

30

**【0045】**

ゲートに加えてバックゲートを設けることで、トランジスタがオン状態の時にキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタのオン電流が大きくなると共に、電界効果移動度が高くなる。したがって、バックゲートを有するトランジスタは、求められるオン電流に対してトランジスタの占有面積を小さくすることができる。また、半導体層をゲートおよびバックゲートで覆うことで、チャネル形成領域に対する外部からの電界の影響を軽減し、半導体装置の信頼性を高めることができる。なお、バックゲートに関しては、追って詳細に説明する。

40

50

**【0046】**

また、配線 121 と配線 123 に同じ電位が供給される場合は、どちらか一方の配線を省略してもよい。また、配線 122 と配線 124 に同じ電位が供給される場合は、どちらか一方の配線を省略してもよい。図 1 (B) に示す半導体装置 100a は、トランジスタ 111 のソースまたはドレインの一方と、トランジスタ 113 のソースまたはドレインの一方が配線 121 と電気的に接続されている。また、トランジスタ 112 のソースまたはドレインの他方と、トランジスタ 114 のソースまたはドレインの他方が配線 122 と電気的に接続されている。

**【0047】**

また、図 1 (C) に示す半導体装置 100b のように、トランジスタ 112 の第 1 ゲート 10 または第 2 ゲートの一方を配線 122 と電気的に接続してもよい。トランジスタ 114 の第 1 ゲートまたは第 2 ゲートの一方を配線 124 と電気的に接続してもよい。トランジスタ 111 の第 1 ゲートまたは第 2 ゲートの一方と、トランジスタ 113 の第 1 ゲートまたは第 2 ゲートの一方を配線 125 と電気的に接続してもよい。なお、配線 125 には、例えば VSS や、配線 122 または配線 124 と同等の電位が供給される。

**【0048】**

なお、必要に応じて、半導体装置 100 に含まれるトランジスタの一部または全部を、バックゲートを用いないトランジスタとすることもできる。バックゲートを用いないトランジスタで構成した半導体装置 100 の回路図を、図 1 (D) に半導体装置 100c として示す。

20

**【0049】**

また、トランジスタ 111 乃至トランジスタ 114 には、OSトランジスタを用いることが好ましい。酸化物半導体のバンドギャップは 2 eV 以上あるため、OSトランジスタは、オフ電流を極めて小さくすることができる。具体的には、ソースとドレイン間の電圧が 3.5 V、室温 (25) 下において、チャネル幅 1 μm当たりのオフ電流を  $1 \times 10^{-20} A$  未満、 $1 \times 10^{-22} A$  未満、あるいは  $1 \times 10^{-24} A$  未満とすることができる。すなわち、オンオフ比を 20 枠以上 150 枠以下とすることができます。また、OSトランジスタは、ソースとドレイン間の絶縁耐圧が高い。OSトランジスタを用いることで、大電力用の半導体装置を提供することができる。

**【0050】**

30

**半導体装置 100 の動作例**

半導体装置 100 は、インバータ回路として機能することができる。具体的には、端子 102 に H 電位が入力されると端子 105 から L 電位が出力され、端子 102 に L 電位が入力されると端子 105 から H 電位が出力される。

**【0051】**

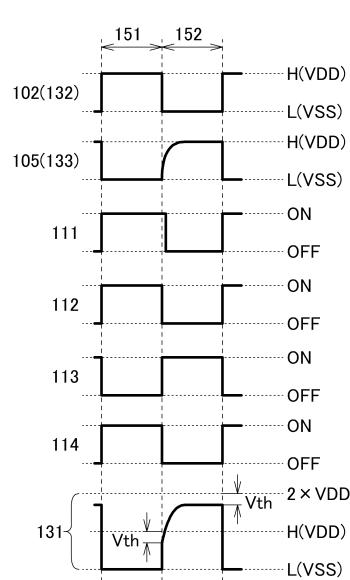

半導体装置 100 の動作例について、図 2 のタイミングチャートと、図 3 および図 4 の回路図を用いて説明する。また、配線 121 および配線 123 には H 電位 (VDD) が供給され、配線 122 および配線 124 には L 電位 (VSS) が供給されているものとする。また、トランジスタ 111 乃至トランジスタ 114 の閾値電圧は全て同じとし、本明細書等において「Vth」と示す。また、Vth は 0 ボルトより大きく、かつ、(VDD - VSS) / 2 未満とする。

40

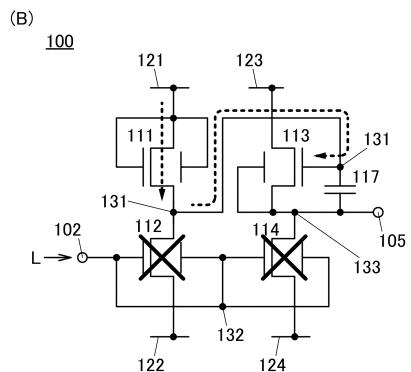

**【0052】****[期間 151 : H 電位入力期間]**

期間 151において、端子 102 に H 電位が入力されるとノード 132 が H 電位となり、トランジスタ 112 とトランジスタ 114 がオン状態となる。すると、ノード 131 およびノード 133 が L 電位となり、トランジスタ 113 がオフ状態となる。また、ノード 133 と電気的に接続される端子 105 から L 電位が出力される（図 3 (A) 参照。）。

**【0053】**

トランジスタ 111 とトランジスタ 112 は同時にオン状態となる。よって、ノード 131 の電位を L 電位に近づけるために、トランジスタ 112 のオン抵抗（トランジスタがオ

50

ン状態の時の、ソースとドレインの間の抵抗。)をトランジスタ111のオン抵抗よりも低くすることが好ましい。例えば、トランジスタ112のチャネル長を、トランジスタ111のチャネル長よりも短くすればよい。具体的には、トランジスタ112のチャネル長をトランジスタ111のチャネル長の1/2以下、好ましくは1/5以下、より好ましくは1/10以下、さらに好ましくは1/20以下とすればよい。また、例えば、トランジスタ112のチャネル幅を、トランジスタ111のチャネル幅よりも長くすればよい。具体的には、トランジスタ112のチャネル幅をトランジスタ111のチャネル幅の2倍以上、好ましくは5倍以上、より好ましくは10倍以上、さらに好ましくは20倍以上とすればよい。また、例えば、トランジスタ112にバックゲートを有するトランジスタを用い、トランジスタ111にバックゲートを有さないトランジスタを用いてもよい。

10

#### 【0054】

[期間152：L電位入力期間]

期間152において、端子102にL電位が入力されるとノード132がL電位となり、トランジスタ112とトランジスタ114がオフ状態となる。すると、配線121からトランジスタ111を介してノード131に電位が供給される。この時、ノード131の電位は、VDD - Vthとなる(図3(B)参照。)。

#### 【0055】

また、ノード131の電位はVthより大きいため、トランジスタ113がオン状態となる(図3(B)参照。)。すると、配線123からトランジスタ113を介してノード133に電位が供給される(図4(A)参照。)。この時、ノード133の電位は、VDD - Vthとなる。

20

#### 【0056】

ノード133に電位が供給されると、容量素子117を介して結合されたノード131の電位が上昇する。具体的には、ノード131の電位が $2 \times (VDD - Vth)$ となる。また、ノード133の電位は最終的に配線123と等しくなる。よって、ノード131の電位は $2 \times VDD - Vth$ の近傍まで上昇する。よって、トランジスタ111はオフ状態となる。また、端子105からH電位(VDD)が出力される(図4(B)参照。)。

#### 【0057】

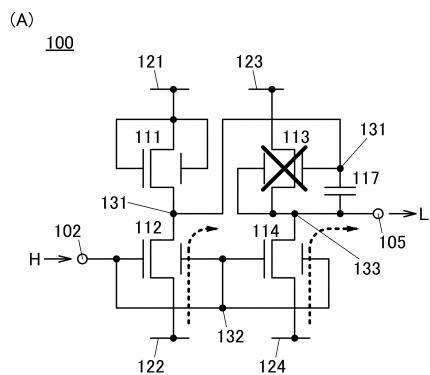

<変形例1>

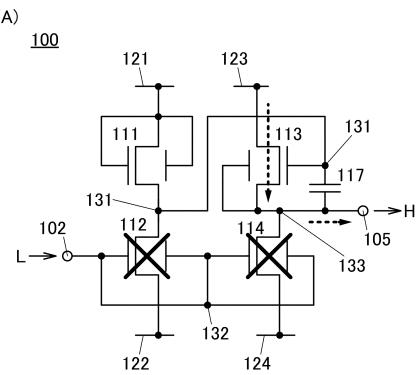

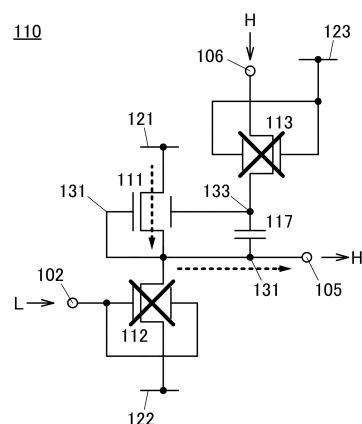

半導体装置100と異なる構成を有する半導体装置110の回路図を、図5(A)に示す。半導体装置110は、トランジスタ111乃至トランジスタ113、および容量素子117を有する。半導体装置110は、半導体装置100よりも少ないトランジスタで構成されるため、半導体装置100よりも占有面積を低減することができる。なお、説明の繰り返しを避けるため、主に半導体装置100と異なる部分について説明する。

30

#### 【0058】

半導体装置110の構成例

図5(A)に示す半導体装置110において、トランジスタ111の、ソースまたはドレインの一方は配線121と電気的に接続され、ソースまたはドレインの他方、および第1ゲートはノード131と電気的に接続され、第2ゲートはノード133と電気的に接続されている。また、トランジスタ112の、ソースまたはドレインの一方はノード131と電気的に接続され、他方は配線122と電気的に接続され、第1ゲートおよび第2ゲートは端子102と電気的に接続されている。また、トランジスタ113の、ソースまたはドレインの一方は端子106と電気的に接続され、ソースまたはドレインの他方はノード133と電気的に接続され、第1ゲートおよび第2ゲートは配線123と電気的に接続されている。また、容量素子117の一方の電極はノード131と電気的に接続され他方の電極はノード133と電気的に接続されている。また、ノード131は端子105と電気的に接続されている。

40

#### 【0059】

また、配線121と配線123に同じ電位が供給される場合は、どちらか一方の配線を省略してもよい。図5(B)に示す半導体装置110aは、トランジスタ113の第1ゲー

50

トおよび第2ゲートが、配線121と電気的に接続されている。

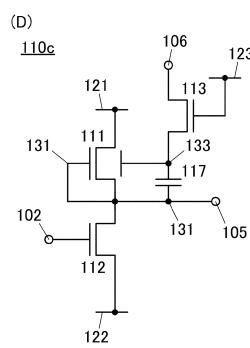

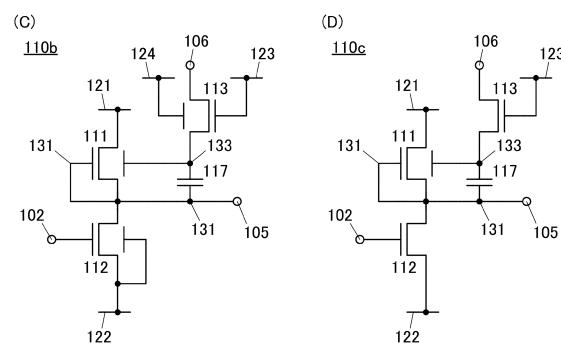

**【0060】**

また、図5(C)に示す半導体装置110bのように、トランジスタ112の第1ゲートまたは第2ゲートの一方を配線122と電気的に接続してもよい。トランジスタ113の第1ゲートまたは第2ゲートの一方を配線124と電気的に接続してもよい。なお、配線124にはVSSが供給される。

**【0061】**

なお、必要に応じて、トランジスタ112またはトランジスタ113の少なくとも一方を、バックゲートを用いないトランジスタとすることもできる。トランジスタ112およびトランジスタ113の両方を、バックゲートを用いないトランジスタとした半導体装置110の回路図を、図5(D)に半導体装置110cとして示す。

10

**【0062】**

半導体装置110の動作例

半導体装置110は、インバータ回路として機能することができる。具体的には、端子102にH電位が入力されると端子105からL電位が出力され、端子102にL電位が入力されると端子105からH電位が出力される。

20

**【0063】**

また、端子102と端子106には、互いに異なる電位が供給される。具体的には、端子102にH電位を供給する場合、端子106にL電位を供給する。端子102にL電位を供給する場合、端子106にH電位を供給する。

**【0064】**

半導体装置110の動作例について、図6のタイミングチャートと、図7および図8の回路図を用いて説明する。

**【0065】**

〔期間151：H電位入力期間〕

期間151において、端子102にH電位を入力し、端子106にL電位を入力する。すると、トランジスタ112およびトランジスタ113がオン状態となり、ノード131およびノード133にL電位が供給される。また、ノード131と電気的に接続される端子105からL電位が出力される(図7(A)参照。)。

30

**【0066】**

なお、半導体装置110では、トランジスタ111とトランジスタ112が同時にオン状態とならない。よって、半導体装置100にあった、トランジスタ111とトランジスタ112のオン抵抗に関する制約はない。

**【0067】**

〔期間152：L電位入力期間〕

期間152において、端子102にL電位を入力し、端子106にH電位を入力する。すると、トランジスタ112はオフ状態となる。また、トランジスタ113を介してノード133に端子106から電位が供給される。この時、トランジスタ113のゲートに配線123からH電位(VDD)が供給されているため、ノード131の電位はVDD-Vthとなる(図7(B)参照。)。

40

**【0068】**

また、ノード133の電位はVthより大きいため、トランジスタ111がオン状態となる(図7(B)参照。)。すると、配線121からトランジスタ111を介してノード131に電位が供給される。

**【0069】**

ノード131に電位が供給されると、容量素子117を介して結合されたノード133の電位が上昇する。最終的に、ノード133の電位は $2 \times VDD - Vth$ の近傍まで上昇する。よって、トランジスタ113はオフ状態となる。また、端子105からH電位(VDD)が出力される(図8参照。)。

**【0070】**

50

## &lt;変形例2&gt;

半導体装置110からさらにトランジスタを低減した半導体装置の回路図を、図9(A)に示す。図9(A)に示す半導体装置120は、トランジスタ111およびトランジスタ112を有する。半導体装置120は、半導体装置110よりも少ないトランジスタで構成されるため、半導体装置110よりも占有面積を低減することができる。

## 【0071】

## 半導体装置120の構成例

図9(A)に示す半導体装置120において、トランジスタ111の、ソースまたはドレインの一方は配線125と電気的に接続され、ソースまたはドレインの他方、および第1ゲートはノード131と電気的に接続され、第2ゲートは端子103と電気的に接続されている。また、トランジスタ112の、ソースまたはドレインの一方はノード131と電気的に接続され、他方は配線123と電気的に接続され、第1ゲートまたは第2ゲートの一方は端子102と電気的に接続され、第1ゲートまたは第2ゲートの他方は端子104と電気的に接続されている。また、ノード131は端子105と電気的に接続されている。

10

## 【0072】

また、図9(B)に示す半導体装置120aのように、トランジスタ112の、第1ゲートまたは第2ゲートの一方を配線123と電気的に接続してもよい。半導体装置120aは半導体装置120と比較して入力端子の数を低減することができるため、半導体装置の生産性を向上することができる。

20

## 【0073】

## 半導体装置120の動作例

半導体装置120は、インバータ回路として機能することができる。具体的には、端子102および端子104にH電位を入力し、端子103にL電位が入力されると、端子105からL電位が出力される。また、端子102および端子104にL電位を入力し、端子103にH電位が入力されると、端子105からVDD-Vthが出力される。なお、端子105からH電位を出力させるためには、端子103にVDD+Vth以上の電位を入力すればよい。

## 【0074】

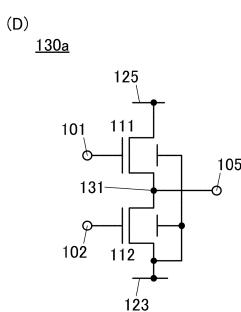

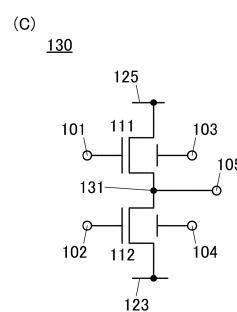

## &lt;変形例3&gt;

30

半導体装置110からさらにトランジスタを低減した半導体装置の回路図を、図9(C)に示す。図9(C)に示す半導体装置130は、トランジスタ111およびトランジスタ112を有する。半導体装置130は、半導体装置110よりも少ないトランジスタで構成されるため、半導体装置110よりも占有面積を低減することができる。

## 【0075】

## 半導体装置130の構成例

図9(C)に示す半導体装置130において、トランジスタ111の、ソースまたはドレインの一方は配線125と電気的に接続され、ソースまたはドレインの他方はノード131と電気的に接続され、第1ゲートまたは第2ゲートの一方は端子101と電気的に接続され、第1ゲートまたは第2ゲートの他方は端子103と電気的に接続されている。また、トランジスタ112の、ソースまたはドレインの一方はノード131と電気的に接続され、他方は配線123と電気的に接続され、第1ゲートまたは第2ゲートの一方は端子102と電気的に接続され、第1ゲートまたは第2ゲートの他方は端子104と電気的に接続されている。また、ノード131は端子105と電気的に接続されている。

40

## 【0076】

また、図9(D)に示す半導体装置130aのように、トランジスタ111の、第1ゲートまたは第2ゲートの一方を配線123と電気的に接続してもよい。トランジスタ112の、第1ゲートまたは第2ゲートの一方を配線123と電気的に接続してもよい。半導体装置130aは半導体装置130と比較して入力端子の数を低減することができるため、半導体装置の生産性を向上することができる。

50

## 【0077】

## 半導体装置130の動作例

半導体装置130は、インバータ回路として機能することができる。具体的には、端子102および端子104にH電位を入力し、端子101および端子103にL電位が入力されると、端子105からL電位が出力される。また、端子102および端子104にL電位を入力し、端子101および端子103にH電位が入力されると、端子105からVD<sub>D-Vth</sub>が出力される。なお、端子105からH電位を出力させるためには、端子101および端子103にVDD+Vth以上の電位を入力すればよい。

## 【0078】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0079】

## (実施の形態2)

本実施の形態では、上記実施の形態に示した半導体装置に用いることができるトランジスタの一例を示す。

## 【0080】

本発明の一態様の半導体装置は、ボトムゲート型のトランジスタや、トップゲート型トランジスタなどの様々な形態のトランジスタを用いて作製することができる。よって、既存の製造ラインに合わせて、使用する半導体層の材料やトランジスタ構造を容易に置き換えることができる。

20

## 【0081】

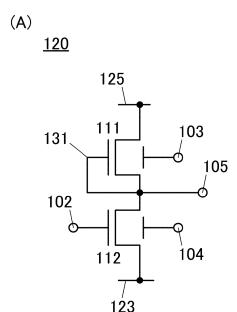

## 〔ボトムゲート型トランジスタ〕

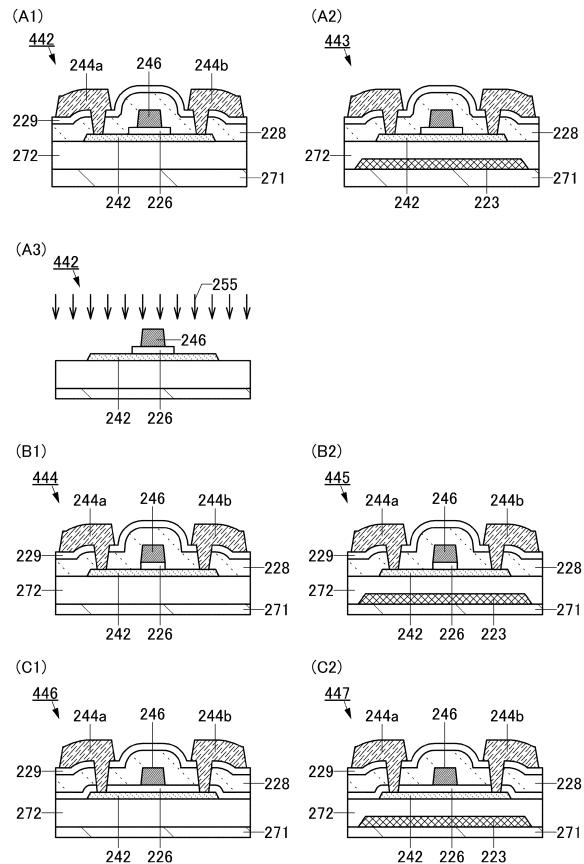

図10(A1)は、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ410の断面図である。トランジスタ410は、基板271上に絶縁層272を介して電極246を有する。また、電極246上に絶縁層226を介して半導体層242を有する。電極246はゲート電極として機能できる。絶縁層226はゲート絶縁層として機能できる。

## 【0082】

また、半導体層242のチャネル形成領域上に絶縁層225を有する。また、半導体層242の一部と接して、絶縁層226上に電極244aおよび電極244bを有する。電極244aの一部、および電極244bの一部は、絶縁層225上に形成される。

30

## 【0083】

絶縁層225は、チャネル保護層として機能できる。チャネル形成領域上に絶縁層225を設けることで、電極244aおよび電極244bの形成時に生じる半導体層242の露出を防ぐことができる。よって、電極244aおよび電極244bの形成時に、半導体層242のチャネル形成領域がエッチングされることを防ぐことができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。

## 【0084】

また、トランジスタ410は、電極244a、電極244bおよび絶縁層225上に絶縁層228を有し、絶縁層228の上に絶縁層229を有する。

40

## 【0085】

なお、半導体層242に酸化物半導体を用いる場合、電極244aおよび電極244bの、少なくとも半導体層242と接する部分に、半導体層242の一部から酸素を奪い、酸素欠損を生じさせることができが可能な材料を用いることが好ましい。半導体層242中の酸素欠損が生じた領域はキャリア濃度が増加し、当該領域はn型化し、n型領域(n<sup>+</sup>層)となる。したがって、当該領域はソース領域またはドレイン領域として機能することができる。酸化物半導体から酸素を奪い、酸素欠損を生じさせができるが可能な材料の一例として、タンゲステン、チタン等を挙げることができる。

## 【0086】

半導体層242にソース領域およびドレイン領域が形成されることにより、電極244a

50

および電極 244b と半導体層 242 の接触抵抗を低減することができる。よって、電界効果移動度や、しきい値電圧などの、トランジスタの電気特性を良好なものとすることができます。

#### 【0087】

半導体層 242 にシリコンなどの半導体を用いる場合は、半導体層 242 と電極 244a の間、および半導体層 242 と電極 244b の間に、n 型半導体または p 型半導体として機能する層を設けることが好ましい。n 型半導体または p 型半導体として機能する層は、トランジスタのソース領域またはドレイン領域として機能することができる。

#### 【0088】

絶縁層 229 は、外部からのトランジスタへの不純物の拡散を防ぐ、または低減する機能を有する材料を用いて形成することが好ましい。なお、必要に応じて絶縁層 229 を省略することもできる。10

#### 【0089】

なお、半導体層 242 に酸化物半導体を用いる場合、絶縁層 229 の形成前または形成後、もしくは絶縁層 229 の形成前後に加熱処理を行ってもよい。加熱処理を行うことで、絶縁層 229 や他の絶縁層中に含まれる酸素を半導体層 242 中に拡散させ、半導体層 242 中の酸素欠損を補填することができる。または、絶縁層 229 を加熱しながら成膜することで、半導体層 242 中の酸素欠損を補填することができる。

#### 【0090】

図 10 (A2) に示すトランジスタ 411 は、絶縁層 229 上にバックゲートとして機能できる電極 223 を有する点がトランジスタ 410 と異なる。電極 223 は、電極 246 と同様の材料および方法で形成することができる。20

#### 【0091】

<バックゲートについて>

一般に、バックゲートは導電層で形成され、ゲートとバックゲートで半導体層のチャネル形成領域を挟むように配置される。よって、バックゲートは、ゲートと同様に機能させることができる。バックゲートの電位は、ゲートと同電位としてもよいし、GND 電位や、任意の電位としてもよい。また、バックゲートの電位をゲートと連動させず独立して変化させることで、トランジスタのしきい値電圧を変化させることができる。

#### 【0092】

電極 246 および電極 223 は、どちらもゲートとして機能することができる。よって、絶縁層 226、絶縁層 225、絶縁層 228、および絶縁層 229 は、それぞれがゲート絶縁層として機能することができる。なお、電極 223 は、絶縁層 228 と絶縁層 229 の間に設けてもよい。30

#### 【0093】

なお、電極 246 または電極 223 の一方を、「ゲート」または「ゲート電極」という場合、他方を「バックゲート」または「バックゲート電極」という。例えば、トランジスタ 411において、電極 223 を「ゲート電極」と言う場合、電極 246 を「バックゲート電極」と言う。なお、電極 223 を「ゲート電極」として用いる場合は、トランジスタ 411 をトップゲート型のトランジスタの一種と考えることができる。また、電極 246 および電極 223 のどちらか一方を、「第 1 ゲート」または「第 1 ゲート電極」といい、他方を「第 2 ゲート」または「第 2 ゲート電極」という場合がある。40

#### 【0094】

半導体層 242 を挟んで電極 246 および電極 223 を設けることで、更には、電極 246 および電極 223 を同電位とすることで、半導体層 242 においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ 411 のオン電流が大きくなると共に、電界効果移動度が高くなる。

#### 【0095】

したがって、トランジスタ 411 は、占有面積に対して大きいオン電流を有するトランジスタである。すなわち、求められるオン電流に対して、トランジスタ 411 の占有面積を50

小さくすることができる。本発明の一態様によれば、トランジスタの占有面積を小さくすることができる。よって、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

#### 【0096】

また、ゲートとバックゲートは導電層で形成されるため、トランジスタの外部で生じる電界が、チャネルが形成される半導体層に作用しないようにする機能（特に静電気などに対する電界遮蔽機能）を有する。なお、バックゲートを半導体層よりも大きく形成し、バックゲートで半導体層を覆うことで、電界遮蔽機能を高めることができる。

#### 【0097】

また、電極246（ゲート）および電極223（バックゲート）は、それぞれが外部からの電界を遮蔽する機能を有するため、絶縁層272側もしくは電極223上方に生じる荷電粒子等の電荷が半導体層242のチャネル形成領域に影響しない。この結果、ストレス試験（例えば、ゲートに負の電荷を印加するNGBT（Negative Gate Bias - Temperature）ストレス試験（「NBT」または「NBTs」ともいう。）による劣化が抑制される。また、ドレイン電圧の大きさにより、オン電流が流れ始めるゲート電圧（立ち上がり電圧）が変化する現象を軽減することができる。なお、この効果は、電極246および電極223が、同電位、または異なる電位の場合において生じる。

#### 【0098】

また、バックゲートを有するトランジスタは、ゲートに正の電荷を印加するPGBT（Positive Gate Bias - Temperature）ストレス試験（「PBT」または「PBTs」ともいう。）前後におけるしきい値電圧の変動も、バックゲートを有さないトランジスタより小さい。

#### 【0099】

なお、NGBTおよびPGBTなどのBTストレス試験は加速試験の一種であり、長期間の使用によって起こるトランジスタの特性変化（経年変化）を短時間で評価することができる。特に、BTストレス試験前後におけるトランジスタのしきい値電圧の変動量は、信頼性を調べるための重要な指標となる。しきい値電圧の変動量が少ないほど、信頼性が高いトランジスタであるといえる。

#### 【0100】

また、電極246および電極223を有し、且つ電極246および電極223を同電位とすることで、しきい値電圧の変動量が低減される。このため、複数のトランジスタにおける電気特性のばらつきも同時に低減される。

#### 【0101】

また、バックゲートを、遮光性を有する導電膜で形成することで、バックゲート側から半導体層に光が入射することを防ぐことができる。よって、半導体層の光劣化を防ぎ、トランジスタのしきい値電圧がシフトするなどの電気特性の劣化を防ぐことができる。

#### 【0102】

本発明の一態様によれば、信頼性の良好なトランジスタを実現することができる。また、信頼性の良好な半導体装置を実現することができる。

#### 【0103】

図10（B1）に、ボトムゲート型のトランジスタの1つであるチャネル保護型のトランジスタ420の断面図を示す。トランジスタ420は、トランジスタ410とほぼ同様の構造を有しているが、絶縁層225が半導体層242を覆っている点が異なる。絶縁層225を設けることで、電極244aおよび電極244bの形成時に生じる半導体層242の露出を防ぐことができる。よって、電極244aおよび電極244bの形成時に半導体層242の薄膜化を防ぐことができる。

#### 【0104】

また、半導体層242と重なる絶縁層225の一部を選択的に除去して形成した開口部において、半導体層242と電極244aが電気的に接続している。また、半導体層242

10

20

30

40

50

と重なる絶縁層 225 の一部を選択的に除去して形成した他の開口部において、半導体層 242 と電極 244b が電気的に接続している。絶縁層 225 の、チャネル形成領域と重なる領域は、チャネル保護層として機能できる。

#### 【0105】

図 10 (B2) に示すトランジスタ 421 は、絶縁層 229 上にバックゲートとして機能できる電極 223 を有する点が、トランジスタ 420 と異なる。

#### 【0106】

また、トランジスタ 420 およびトランジスタ 421 は、トランジスタ 410 およびトランジスタ 411 よりも、電極 244a と電極 246 の間の距離と、電極 244b と電極 246 の間の距離が長くなる。よって、電極 244a と電極 246 の間に生じる寄生容量を小さくすることができる。また、電極 244b と電極 246 の間に生じる寄生容量を小さくすることができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現できる。10

#### 【0107】

図 10 (C1) に示すトランジスタ 425 は、ボトムゲート型のトランジスタの 1つであるチャネルエッチング型のトランジスタである。トランジスタ 425 は、絶縁層 225 を設けずに、半導体層 242 に接して電極 244a および電極 244b を形成する。このため、電極 244a および電極 244b の形成時に露出する半導体層 242 の一部がエッチングされる場合がある。一方、絶縁層 225 を設けないため、トランジスタの生産性を高めることができる。20

#### 【0108】

図 10 (C2) に示すトランジスタ 426 は、絶縁層 229 上にバックゲートとして機能できる電極 223 を有する点が、トランジスタ 425 と異なる。

#### 【0109】

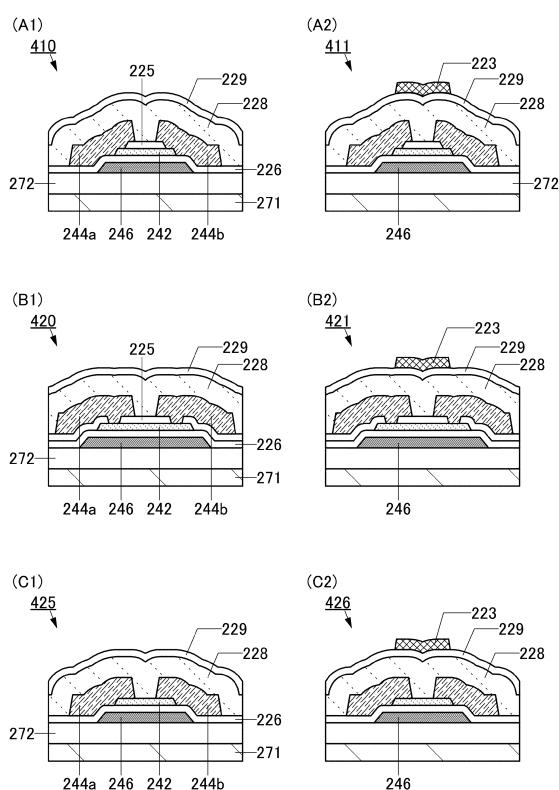

##### 〔トップゲート型トランジスタ〕

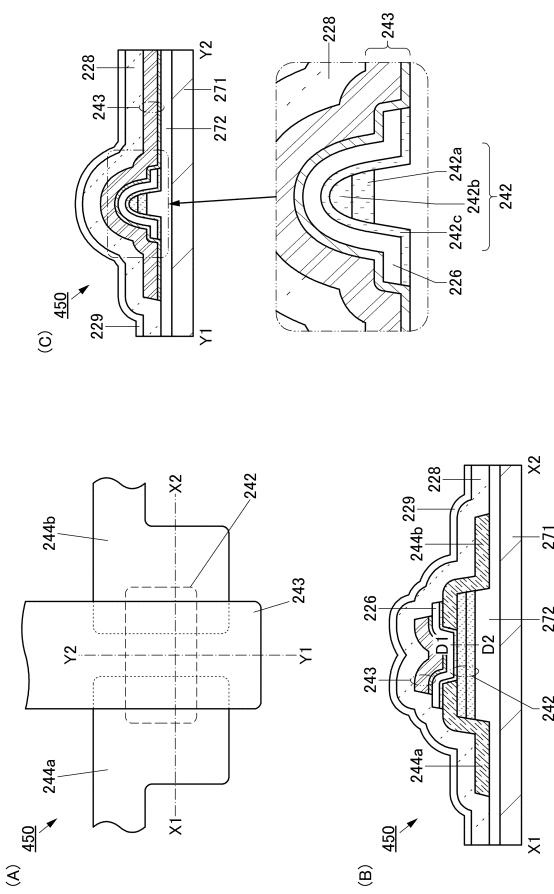

図 11 (A1) に、トップゲート型のトランジスタの一種であるトランジスタ 430 の断面図を示す。トランジスタ 430 は、基板 271 の上に絶縁層 272 を介して半導体層 242 を有し、半導体層 242 および絶縁層 272 上に、半導体層 242 の一部に接する電極 244a、および半導体層 242 の一部に接する電極 244b を有し、半導体層 242、電極 244a、および電極 244b 上に絶縁層 226 を有し、絶縁層 226 上に電極 246 を有する。30

#### 【0110】

トランジスタ 430 は、電極 246 および電極 244a、並びに、電極 246 および電極 244b が重ならないため、電極 246 および電極 244a の間に生じる寄生容量、並びに、電極 246 および電極 244b の間に生じる寄生容量を小さくすることができる。また、電極 246 を形成した後に、電極 246 をマスクとして用いて不純物 255 を半導体層 242 に導入することで、半導体層 242 中に自己整合（セルフアライメント）的に不純物領域を形成することができる（図 11 (A3) 参照）。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。

#### 【0111】

なお、不純物 255 の導入は、イオン注入装置、イオンドーピング装置またはプラズマ処理装置を用いて行うことができる。

#### 【0112】

不純物 255 としては、例えば、第 13 族元素または第 15 族元素のうち、少なくとも一種類の元素を用いることができる。また、半導体層 242 に酸化物半導体を用いる場合は、不純物 255 として、希ガス、水素、および窒素のうち、少なくとも一種類の元素を用いることも可能である。

#### 【0113】

図 11 (A2) に示すトランジスタ 431 は、電極 223 および絶縁層 227 を有する点がトランジスタ 430 と異なる。トランジスタ 431 は、絶縁層 272 の上に形成された

10

20

30

40

50

電極 223 を有し、電極 223 上に形成された絶縁層 227 を有する。電極 223 は、バックゲートとして機能することができる。よって、絶縁層 227 は、ゲート絶縁層として機能することができる。絶縁層 227 は、絶縁層 226 と同様の材料および方法により形成することができる。

#### 【0114】

トランジスタ 411 と同様に、トランジスタ 431 は、占有面積に対して大きいオン電流を有するトランジスタである。すなわち、求められるオン電流に対して、トランジスタ 431 の占有面積を小さくすることができる。本発明の一態様によれば、トランジスタの占有面積を小さくすることができる。よって、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

10

#### 【0115】

図 11 (B1) に例示するトランジスタ 440 は、トップゲート型のトランジスタの 1 つである。トランジスタ 440 は、電極 244a および電極 244b を形成した後に半導体層 242 を形成する点が、トランジスタ 430 と異なる。また、図 11 (B2) に例示するトランジスタ 441 は、電極 223 および絶縁層 227 を有する点が、トランジスタ 440 と異なる。トランジスタ 440 およびトランジスタ 441 において、半導体層 242 の一部は電極 244a 上に形成され、半導体層 242 の他の一部は電極 244b 上に形成される。

#### 【0116】

トランジスタ 411 と同様に、トランジスタ 441 は、占有面積に対して大きいオン電流を有するトランジスタである。すなわち、求められるオン電流に対して、トランジスタ 441 の占有面積を小さくすることができる。本発明の一態様によれば、トランジスタの占有面積を小さくすることができる。よって、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

20

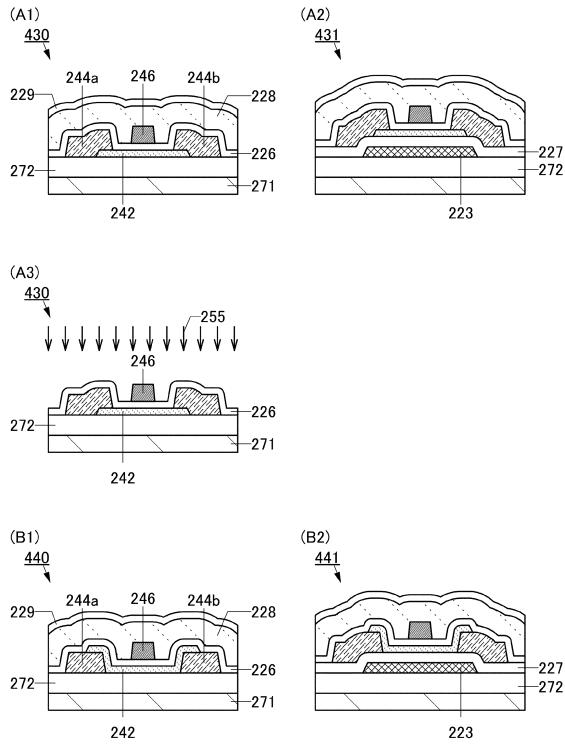

#### 【0117】

図 12 (A1) に例示するトランジスタ 442 は、トップゲート型のトランジスタの 1 つである。トランジスタ 442 は、絶縁層 229 上に電極 244a および電極 244b を有する。電極 244a および電極 244b は、絶縁層 228 および絶縁層 229 に形成した開口部において半導体層 242 と電気的に接続する。

#### 【0118】

30

また、電極 246 と重ならない絶縁層 226 の一部が除去されている。また、トランジスタ 442 が有する絶縁層 226 の一部は、電極 246 の端部を越えて延伸している。

#### 【0119】

電極 246 と絶縁層 226 をマスクとして用いて不純物 255 を半導体層 242 に導入することで、半導体層 242 中に自己整合 (セルフアライメント) 的に不純物領域を形成することができる (図 12 (A3) 参照)。

#### 【0120】

この時、半導体層 242 の電極 246 と重なる領域には不純物 255 が導入されず、電極 246 と重ならない領域に不純物 255 が導入される。また、半導体層 242 の絶縁層 226 を介して不純物 255 が導入された領域の不純物濃度は、絶縁層 226 を介さずに不純物 255 が導入された領域よりも低くなる。よって、半導体層 242 中の電極 246 と隣接する領域に LDD (Lightly Doped Drain) 領域が形成される。

40

#### 【0121】

図 12 (A2) に示すトランジスタ 443 は、半導体層 242 の下方に電極 223 を有する点がトランジスタ 442 と異なる。また、電極 223 は絶縁層 272 を介して半導体層 242 と重なる。電極 223 は、バックゲート電極として機能することができる。

#### 【0122】

また、図 12 (B1) に示すトランジスタ 444 および図 12 (B2) に示すトランジスタ 445 のように、絶縁層 226 の電極 246 と重ならない領域を全て除去してもよい。また、図 12 (C1) に示すトランジスタ 446 および図 12 (C2) に示すトランジス

50

タ447のように、絶縁層226の開口部以外を除去せずに残してもよい。

【0123】

トランジスタ444乃至トランジスタ447も、電極246を形成した後に、電極246をマスクとして用いて不純物255を半導体層242に導入することで、半導体層242中に自己整合的に不純物領域を形成することができる。

【0124】

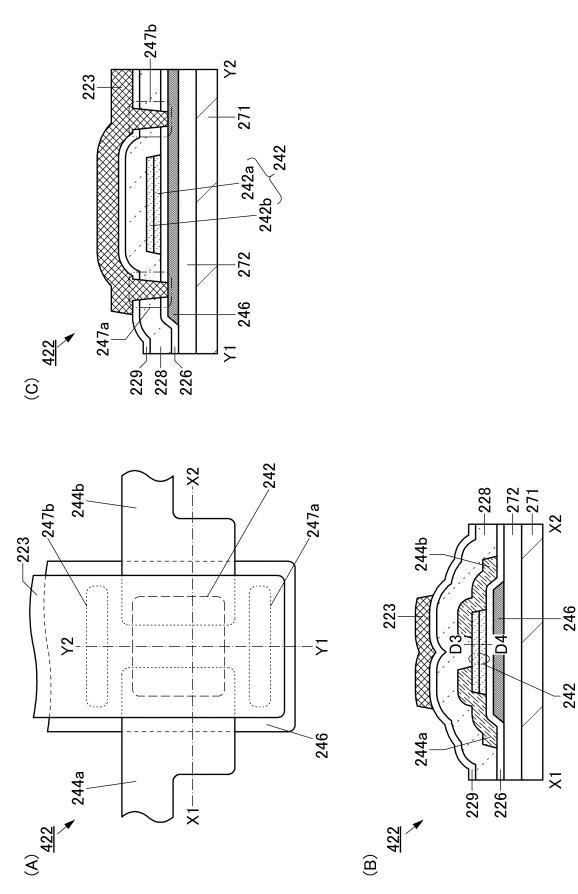

[s-channel型トランジスタ]

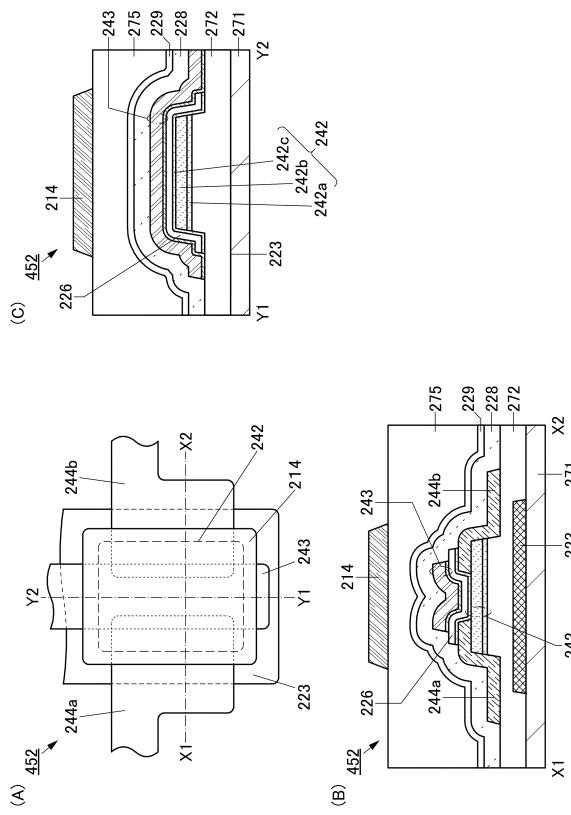

図13に、半導体層242として酸化物半導体を用いたトランジスタ構造の一例を示す。図13に例示するトランジスタ450は、半導体層242aの上に半導体層242bが形成され、半導体層242bの上面並びに半導体層242a及び半導体層242bの側面が半導体層242cに覆われた構造を有する。図13(A)はトランジスタ450の上面図である。図13(B)は、図13(A)中のX1-X2の一点鎖線で示した部位の断面図(チャネル長方向の断面図)である。図13(C)は、図13(A)中のY1-Y2の一点鎖線で示した部位の断面図(チャネル幅方向の断面図)である。

10

【0125】

また、トランジスタ450は、ゲート電極として機能する電極243を有する。電極243は、電極246と同様の材料および方法で形成することができる。本実施の形態では、電極243を2層の導電層の積層としている。

【0126】

半導体層242a、半導体層242b、および半導体層242cは、InもしくはGaの一方、または両方を含む材料で形成する。代表的には、In-Ga酸化物(InとGaを含む酸化物)、In-Zn酸化物(InとZnを含む酸化物)、In-M-Zn酸化物(Inと、元素Mと、Znを含む酸化物。元素Mは、Al、Ti、Ga、Y、Zr、La、Ce、NdまたはHfから選ばれた1種類以上の元素で、Inよりも酸素との結合力が強い金属元素である。)がある。

20

【0127】

半導体層242aおよび半導体層242cは、半導体層242bを構成する金属元素のうち、1種類以上の同じ金属元素を含む材料により形成されることが好ましい。このような材料を用いると、半導体層242aおよび半導体層242bとの界面、ならびに半導体層242cおよび半導体層242bとの界面に界面準位を生じにくくすることができる。よって、界面におけるキャリアの散乱や捕獲が生じにくく、トランジスタの電界効果移動度を向上させることができる。また、トランジスタのしきい値電圧のばらつきを低減することが可能となる。よって、良好な電気特性を有する半導体装置を実現することが可能となる。

30

【0128】

半導体層242aおよび半導体層242cの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、半導体層242bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

40

【0129】

また、半導体層242bがIn-M-Zn酸化物であり、半導体層242aおよび半導体層242cもIn-M-Zn酸化物であるとき、半導体層242aおよび半導体層242cをIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、半導体層242bをIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]とすると、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも大きくなるように半導体層242a、半導体層242c、および半導体層242bを選択することができる。好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも1.5倍以上大きくなるように半導体層242a、半導体層242c、および半導体層242bを選択する。さらに好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも2倍以上大きくなるように半導体層242a、半導体層242c、および半導体層242bを選択する。より好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも3倍以上大きくなるように半導体層242a、半導体層242cおよび半導体層242bを選択する。

50

層 2 4 2 b を選択する。  $y_1$  が  $x_1$  以上であるとトランジスタに安定した電気特性を付与できるため好ましい。ただし、 $y_1$  が  $x_1$  の 3 倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_1$  は  $x_1$  の 3 倍未満であると好ましい。半導体層 2 4 2 a および半導体層 2 4 2 c を上記構成とすることにより、半導体層 2 4 2 a および半導体層 2 4 2 c を、半導体層 2 4 2 b よりも酸素欠損が生じにくい層とすることができます。

#### 【 0 1 3 0 】

なお、半導体層 2 4 2 a および半導体層 2 4 2 c が In - M - Zn 酸化物であるとき、In および元素Mの和を 100 atomic %としたときの In と元素Mの原子数比率は、好ましくは In が 50 atomic %未満、元素Mが 50 atomic %以上、さらに好ましくは In が 25 atomic %未満、元素Mが 75 atomic %以上とする。また、半導体層 2 4 2 b が In - M - Zn 酸化物であるとき、In および元素Mの和を 100 atomic %としたときの In と元素Mの原子数比率は好ましくは In が 25 atomic %以上、元素Mが 75 atomic %未満、さらに好ましくは In が 34 atomic %以上、元素Mが 66 atomic %未満とする。

10

#### 【 0 1 3 1 】

例えば、In または Ga を含む半導体層 2 4 2 a 、および In または Ga を含む半導体層 2 4 2 c として In : Ga : Zn = 1 : 3 : 2 、 1 : 3 : 4 、 1 : 3 : 6 、 1 : 4 : 5 、 1 : 6 : 4 、または 1 : 9 : 6 などの原子数比のターゲットを用いて形成した In - Ga - Zn 酸化物や、 In : Ga = 1 : 9 などの原子数比のターゲットを用いて形成した In - Ga 酸化物や、酸化ガリウムなどを用いることができる。また、半導体層 2 4 2 b として In : Ga : Zn = 3 : 1 : 2 、 1 : 1 : 1 、 5 : 5 : 6 、 5 : 1 : 7 、または 4 : 2 : 4 . 1 などの原子数比のターゲットを用いて形成した In - Ga - Zn 酸化物を用いることができる。なお、半導体層 2 4 2 a 、半導体層 2 4 2 b 、および半導体層 2 4 2 c の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 20 % の変動を含む。

20

#### 【 0 1 3 2 】

半導体層 2 4 2 b を用いたトランジスタに安定した電気特性を付与するためには、半導体層 2 4 2 b 中の不純物および酸素欠損を低減して高純度真性化し、半導体層 2 4 2 b を高純度真性または実質的に高純度真性と見なせる酸化物半導体層とすることが好ましい。また、少なくとも半導体層 2 4 2 b 中のチャネル形成領域が高純度真性または実質的に高純度真性と見なせる半導体層とすることが好ましい。

30

#### 【 0 1 3 3 】

なお、実質的に高純度真性と見なせる酸化物半導体層とは、酸化物半導体層中のキャリア密度が、 $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上である酸化物半導体層をいう。

#### 【 0 1 3 4 】

図 14 に、半導体層 2 4 2 として酸化物半導体を用いたトランジスタ構造の一例を示す。図 14 に例示するトランジスタ 422 は、半導体層 2 4 2 a の上に半導体層 2 4 2 b が形成されている。トランジスタ 422 は、バックゲートを有するボトムゲート型のトランジスタの一種である。図 14 (A) はトランジスタ 422 の上面図である。図 14 (B) は、図 14 (A) 中の X1 - X2 の一点鎖線で示した部位の断面図 (チャネル長方向の断面図) である。図 14 (C) は、図 14 (A) 中の Y1 - Y2 の一点鎖線で示した部位の断面図 (チャネル幅方向の断面図) である。

40

#### 【 0 1 3 5 】

絶縁層 2 2 9 上に設けられた電極 2 2 3 は、絶縁層 2 2 6 、絶縁層 2 2 8 、および絶縁層 2 2 9 に設けられた開口 2 4 7 a および開口 2 4 7 b において、電極 2 4 6 と電気的に接続されている。よって、電極 2 2 3 と電極 2 4 6 には、同じ電位が供給される。また、開口 2 4 7 a および開口 2 4 7 b は、どちらか一方を設けなくてもよい。また、開口 2 4 7 a および開口 2 4 7 b の両方を設けなくともよい。開口 2 4 7 a および開口 2 4 7 b の両方を設けない場合は、電極 2 2 3 と電極 2 4 6 に異なる電位を供給することができる。

50

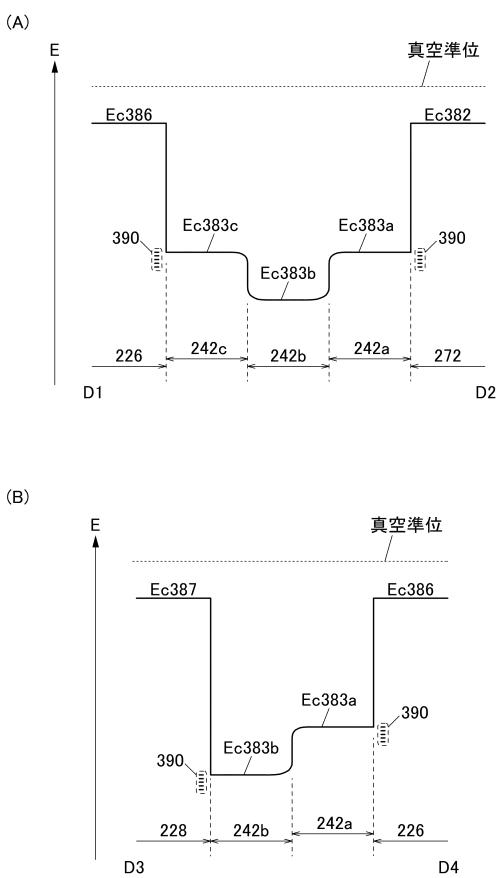

## 【0136】

[酸化物半導体のエネルギー-band構造]

ここで、半導体層242a、半導体層242b、および半導体層242cの積層により構成される半導体層242の機能およびその効果について、図20(A)および図20(B)に示すエネルギー-band構造図を用いて説明する。図20(A)は、図13(B)にD1-D2の一点鎖線で示す部位のエネルギー-band構造図である。図20(A)は、トランジスタ450のチャネル形成領域のエネルギー-band構造を示している。

## 【0137】

図20(A)中、Ec382、Ec383a、Ec383b、Ec383c、Ec386は、それぞれ、絶縁層272、半導体層242a、半導体層242b、半導体層242c、絶縁層226の伝導帯下端のエネルギーを示している。

10

## 【0138】

ここで、真空準位と伝導帯下端のエネルギーとの差(「電子親和力」ともいう。)は、真空準位と価電子帯上端のエネルギーとの差(イオン化ポテンシャルともいう。)からエネルギーギャップを引いた値となる。なお、エネルギーギャップは、分光エリプソメータ(例えば、HORIBA JOBIN YVON社 UT-300)を用いて測定できる。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS:Ultraviolet Photoelectron Spectroscopy)装置(例えば、PHI社 VersaProbe)を用いて測定できる。

20

## 【0139】

なお、原子数比がIn:Ga:Zn=1:3:2のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.5eV、電子親和力は約4.5eVである。また、原子数比がIn:Ga:Zn=1:3:4のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.4eV、電子親和力は約4.5eVである。また、原子数比がIn:Ga:Zn=1:3:6のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.3eV、電子親和力は約4.5eVである。また、原子数比がIn:Ga:Zn=1:6:2のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.9eV、電子親和力は約4.3eVである。また、原子数比がIn:Ga:Zn=1:6:8のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.5eV、電子親和力は約4.4eVである。また、原子数比がIn:Ga:Zn=1:6:10のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.5eV、電子親和力は約4.5eVである。また、原子数比がIn:Ga:Zn=1:1:1のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約3.2eV、電子親和力は約4.7eVである。また、原子数比がIn:Ga:Zn=3:1:2のターゲットを用いて形成したIn-Ga-Zn酸化物のエネルギーギャップは約2.8eV、電子親和力は約5.0eVである。

30

## 【0140】

絶縁層272と絶縁層226は絶縁物であるため、Ec382とEc386は、Ec383a、Ec383b、およびEc383cよりも真空準位に近い(電子親和力が小さい)。

40

## 【0141】

また、Ec383aは、Ec383bよりも真空準位に近い。具体的には、Ec383aは、Ec383bよりも0.05eV以上、0.07eV以上、0.1eV以上または0.15eV以上、かつ2eV以下、1eV以下、0.5eV以下または0.4eV以下真空準位に近いことが好ましい。

## 【0142】

また、Ec383cは、Ec383bよりも真空準位に近い。具体的には、Ec383cは、Ec383bよりも0.05eV以上、0.07eV以上、0.1eV以上または0.15eV以上、かつ2eV以下、1eV以下、0.5eV以下または0.4eV以下真

50

空準位に近いことが好ましい。

**【0143】**

また、半導体層242aと半導体層242bとの界面近傍、および、半導体層242bと半導体層242cとの界面近傍では、混合領域が形成されるため、伝導帯下端のエネルギーは連続的に変化する。即ち、これらの界面において、準位は存在しないか、ほとんどない。

**【0144】**

従って、当該エネルギー・バンド構造を有する積層構造において、電子は半導体層242bを主として移動することになる。そのため、半導体層242aと絶縁層272との界面、または、半導体層242cと絶縁層226との界面に準位が存在したとしても、当該準位は電子の移動にほとんど影響しない。また、半導体層242aと半導体層242bとの界面、および半導体層242cと半導体層242bとの界面に準位が存在しないか、ほとんどないため、当該領域において電子の移動を阻害することもない。従って、上記酸化物半導体の積層構造を有するトランジスタは、高い電界効果移動度を実現することができる。

10

**【0145】**

なお、図20(A)に示すように、半導体層242aと絶縁層272の界面、および半導体層242cと絶縁層226の界面近傍には、不純物や欠陥に起因したトラップ準位390が形成され得るもの、半導体層242a、および半導体層242cがあることにより、半導体層242bと当該トラップ準位とを遠ざけることができる。

20

**【0146】**

特に、本実施の形態に例示するトランジスタ134は、半導体層242bの上面と側面が半導体層242cと接し、半導体層242bの下面が半導体層242aと接して形成されている。このように、半導体層242bを半導体層242aと半導体層242cで覆う構成とすることで、上記トラップ準位の影響をさらに低減することができる。

**【0147】**

ただし、Ec383aまたはEc383cと、Ec383bとのエネルギー差が小さい場合、半導体層242bの電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されることで、絶縁層の界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

30

**【0148】**

従って、Ec383a、およびEc383cと、Ec383bとのエネルギー差を、それぞれ0.1eV以上、好ましくは0.15eV以上とすると、トランジスタのしきい値電圧の変動が低減され、トランジスタの電気特性を良好なものとすることができるため、好ましい。

**【0149】**

また、半導体層242a、および半導体層242cのバンドギャップは、半導体層242bのバンドギャップよりも広いほうが好ましい。

**【0150】**

図20(B)は、図14(B)にD3-D4の一点鎖線で示す部位のエネルギー・バンド構造図である。図20(B)は、トランジスタ422のチャネル形成領域のエネルギー・バンド構造を示している。

40

**【0151】**

図20(B)中、Ec387は、絶縁層228の伝導帯下端のエネルギーを示している。半導体層242を半導体層242aと半導体層242bの2層とすることで、トランジスタの生産性を高めることができる。なお、半導体層242cを設けない分、トラップ準位390の影響を受けやすくなるが、半導体層242を単層構造とした場合よりも高い電界効果移動度を実現することができる。

**【0152】**

本発明の一態様によれば、電気特性のばらつきが少ないトランジスタを実現することができる。よって、電気特性のばらつきが少ない半導体装置を実現することができる。本発明

50

の一態様によれば、信頼性の良好なトランジスタを実現することができる。よって、信頼性の良好な半導体装置を実現することができる。

#### 【0153】

また、酸化物半導体は、エネルギーギャップが2eV以上と大きく、可視光に対する透過率が大きい。また、酸化物半導体を適切な条件で加工して得られたトランジスタにおいては、オフ電流を使用時の温度条件下（例えば、25°C）において、 $100\text{zA}$  ( $1 \times 10^{-19}\text{A}$ ) 以下、もしくは $10\text{zA}$  ( $1 \times 10^{-20}\text{A}$ ) 以下、さらには $1\text{zA}$  ( $1 \times 10^{-21}\text{A}$ ) 以下とすることができます。このため、消費電力の少ない半導体装置を提供することができる。

#### 【0154】

本発明の一態様によれば、消費電力が少ないトランジスタを実現することができる。よって、消費電力が少ない表示素子や表示装置などの半導体装置を実現することができる。または、信頼性の良好な表示素子や表示装置などの半導体装置を実現することができる。

#### 【0155】

図13に示すトランジスタ450の説明にもどる。絶縁層272に設けた凸部上に半導体層242bを設けることによって、半導体層242bの側面も電極243で覆うことができる。すなわち、トランジスタ450は、電極243の電界によって、半導体層242bを電気的に取り囲むことができる構造を有している。このように、導電膜の電界によって、チャネルが形成される半導体層を電気的に取り囲むトランジスタの構造を、「surrounded channel (s-channel) 構造」とよぶ。また、s-channel構造を有するトランジスタを、「s-channel型トランジスタ」もしくは「s-channelトランジスタ」ともいう。

#### 【0156】

s-channel構造では、半導体層242bの全体（バルク）にチャネルを形成することもできる。s-channel構造では、トランジスタのドレン電流を大きくすることができ、さらに大きいオン電流を得ることができる。また、電極243の電界によって、半導体層242bに形成されるチャネル形成領域の全領域を空乏化することができる。したがって、s-channel構造では、トランジスタのオフ電流をさらに小さくすることができる。

#### 【0157】

なお、絶縁層272の凸部を高くし、また、チャネル幅を小さくすることで、s-channel構造によるオン電流の増大効果、オフ電流の低減効果などをより高めることができます。また、半導体層242bの形成時に、露出する半導体層242aを除去してもよい。この場合、半導体層242aと半導体層242bの側面が揃う場合がある。

#### 【0158】

また、図15に示すトランジスタ451のように、半導体層242の下方に、絶縁層を介して電極223を設けてもよい。図15(A)はトランジスタ451の上面図である。図15(B)は、図15(A)中のX1-X2の一点鎖線で示した部位の断面図である。図15(C)は、図15(A)中のY1-Y2の一点鎖線で示した部位の断面図である。

#### 【0159】

また、図16に示すトランジスタ452のように、電極243の上方に絶縁層275を設け、絶縁層275上に層214を設けてもよい。図16(A)はトランジスタ452の上面図である。図16(B)は、図16(A)中のX1-X2の一点鎖線で示した部位の断面図である。図16(C)は、図16(A)中のY1-Y2の一点鎖線で示した部位の断面図である。

#### 【0160】

なお、図16では、層214を絶縁層275上に設けているが、絶縁層228上、または絶縁層229上に設けてもよい。層214を、遮光性を有する材料で形成することで、光照射によるトランジスタの特性変動や、信頼性の低下などを防ぐことができる。なお、層214を少なくとも半導体層242bよりも大きく形成し、層214で半導体層242b

10

20

30

40

50

を覆うことで、上記の効果を高めることができる。層214は、有機物材料、無機物材料、又は金属材料を用いて作製することができる。また、層214を導電性材料で作製した場合、層214に電圧を供給してもよいし、電気的に浮遊した(フローティング)状態としてもよい。

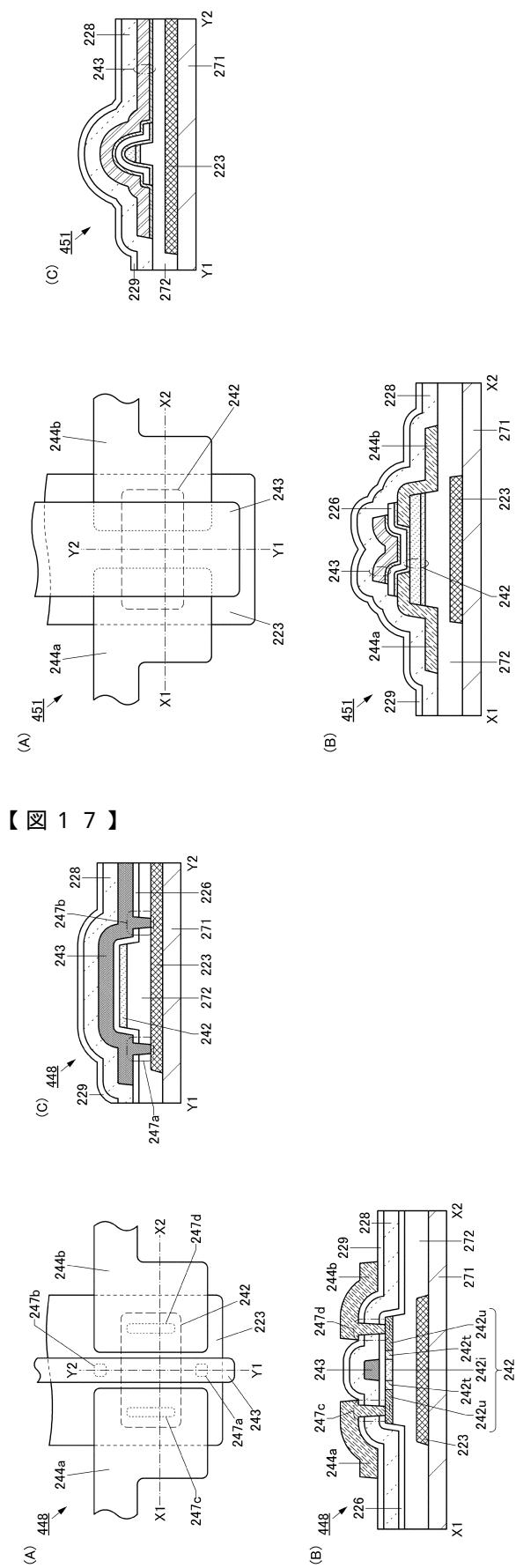

#### 【0161】

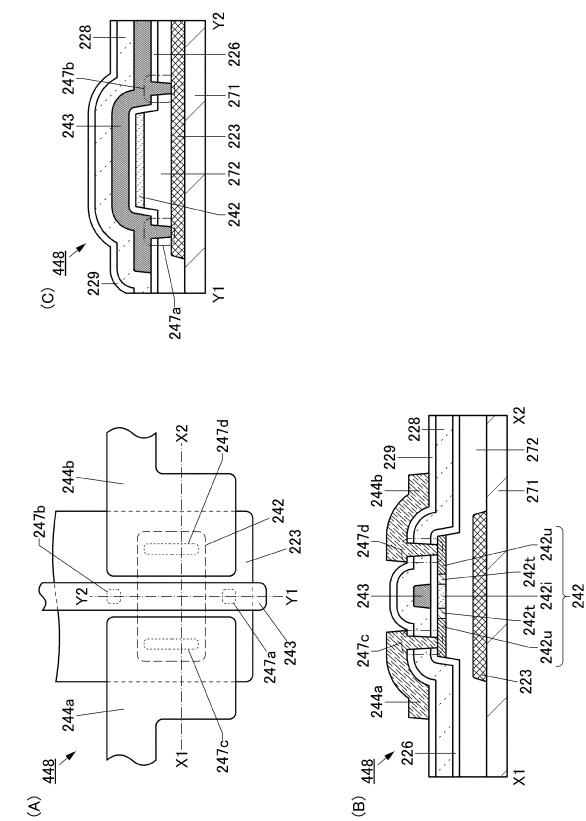

図17に、s-channel構造を有するトランジスタの一例を示す。図17に例示するトランジスタ448は、前述したトランジスタ447とほぼ同様の構成を有する。トランジスタ448は、絶縁層272が有する凸部の上に半導体層242が形成されている。トランジスタ448はバックゲート電極を有するトップゲート型のトランジスタの一種である。図17(A)はトランジスタ448の上面図である。図17(B)は、図17(A)中のX1-X2の一点鎖線で示した部位の断面図である。図17(C)は、図17(A)中のY1-Y2の一点鎖線で示した部位の断面図である。

10

#### 【0162】

図17では、トランジスタ448を構成する半導体層242にシリコンなどの無機半導体層を用いる場合を例示する。図17において、半導体層242は、ゲート電極と重なる領域に半導体層242iと、2つの半導体層242tと、2つの半導体層242uとを有する。半導体層242iは、2つの半導体層242tの間に配置されている。また、半導体層242iと2つの半導体層242tは、2つの半導体層242uの間に配置されている。

20

#### 【0163】

トランジスタ448がオン状態の時に半導体層242iにチャネルが形成される。よって、半導体層242iはチャネル形成領域として機能する。また、半導体層242tは低濃度不純物領域(LDD)として機能する。また、半導体層242uは高濃度不純物領域として機能する。なお、2つの半導体層242tのうち、一方または両方の半導体層242tを設けなくてもよい。また、2つの半導体層242uのうち、一方の半導体層242uはソース領域として機能し、他方の半導体層242uはドレイン領域として機能する。

#### 【0164】

絶縁層229上に設けられた電極244aは、絶縁層226、絶縁層228、および絶縁層229に設けられた開口247cにおいて、半導体層242uの一方と電気的に接続されている。また、絶縁層229上に設けられた電極244bは、絶縁層226、絶縁層228、および絶縁層229に設けられた開口247dにおいて、半導体層242uの他方と電気的に接続されている。

30

#### 【0165】

絶縁層226上に設けられた電極243は、絶縁層226、および絶縁層272に設けられた開口247aおよび開口247bにおいて、電極223と電気的に接続されている。よって、電極243と電極223には、同じ電位が供給される。また、開口247aおよび開口247bは、どちらか一方を設けなくてもよい。また、開口247aおよび開口247bの両方を設けなくてもよい。開口247aおよび開口247bの両方を設けない場合は、電極223と電極243に異なる電位を供給することができる。

#### 【0166】

40

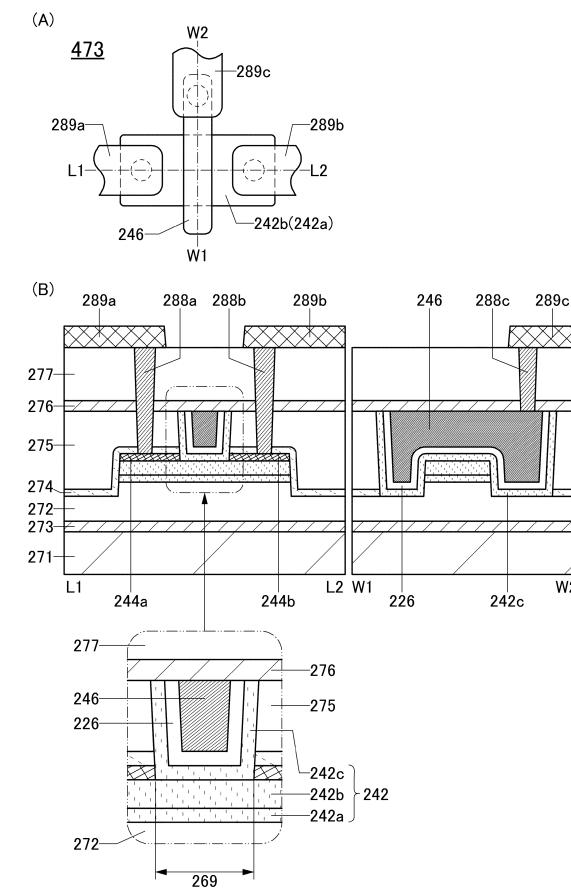

図18(A)および図18(B)にs-channel型トランジスタの他の一例を示す。図18(A)は、トランジスタ473の平面図である。また、図18(B)は、図18(A)にL1-L2の一点鎖線で示す部位と、W1-W2の一点鎖線で示す部位の断面図である。図18(B)において、L1-L2はトランジスタ473のチャネル長方向の断面図であり、W1-W2はトランジスタ473のチャネル幅方向の断面図である。

#### 【0167】

トランジスタ473は半導体層242、絶縁層226、電極246、電極244a、および電極244bを有する。電極246はゲート電極として機能できる。絶縁層226はゲート絶縁層として機能できる。電極244aは、ソース電極またはドレイン電極の一方として機能できる。電極244bは、ソース電極またはドレイン電極の他方として機能でき

50

る。また、トランジスタ473は、基板271上に、絶縁層273および絶縁層272を介して設けられている。

#### 【0168】

図18(B)において、基板271上に絶縁層273が設けられ、絶縁層273上に絶縁層272が設けられている。絶縁層272は凸部を有し、該凸部上に島状の半導体層242aと島状の半導体層242bが設けられている。また、半導体層242b上に電極244a、および電極244bが設けられている。半導体層242bの電極244aと重なる領域が、トランジスタ473のソースまたはドレインの一方として機能できる。半導体層242bの電極244bと重なる領域が、トランジスタ473のソースまたはドレインの他方として機能できる。よって、半導体層242bの、電極244aと電極244bに挟まれた領域269が、チャネル形成領域として機能できる。10

#### 【0169】

また、電極244a、および電極244b上に酸化物半導体層274が設けられ、酸化物半導体層274上に絶縁層275が設けられている。また、酸化物半導体層274と絶縁層275の領域269と重なる領域に開口が設けられ、該開口の側面および底面に沿って半導体層242cが設けられている。また、該開口内に、半導体層242cを介して、かつ、該開口の側面および底面に沿って、絶縁層226が設けられている。また、該開口内に、半導体層242cおよび絶縁層226を介して、かつ、該開口の側面および底面に沿って、電極246が設けられている。20

#### 【0170】

なお、該開口は、チャネル幅方向の断面において、半導体層242aおよび半導体層242bよりも大きく設けられている。よって、領域269において、半導体層242aおよび半導体層242bの側面は、半導体層242cに覆われている。領域269以外の半導体層242aおよび半導体層242bの側面は、酸化物半導体層274に覆われている。20

#### 【0171】

また、絶縁層275上に絶縁層276が設けられ、絶縁層276上に絶縁層277が設けられている。また、絶縁層277上に電極289a、電極289b、および電極289cが設けられている。電極289aは、絶縁層277、絶縁層276、絶縁層275、および酸化物半導体層274の一部を除去して形成した開口において、コンタクトプラグ288aを介して電極244aと電気的に接続されている。また、電極289bは、絶縁層277、絶縁層276、絶縁層275、および酸化物半導体層274の一部を除去して形成した開口において、コンタクトプラグ288bを介して電極244bと電気的に接続されている。また、電極289cは、絶縁層277および絶縁層276の一部を除去して形成した開口において、コンタクトプラグ288cを介して電極246と電気的に接続されている。30

#### 【0172】

また、図18(B)に示すように、トランジスタ473は、チャネル幅方向において、電極246が半導体層242bを覆っている。また、絶縁層272が凸部を有することによって、半導体層242bの側面も電極246で覆うことができる。40

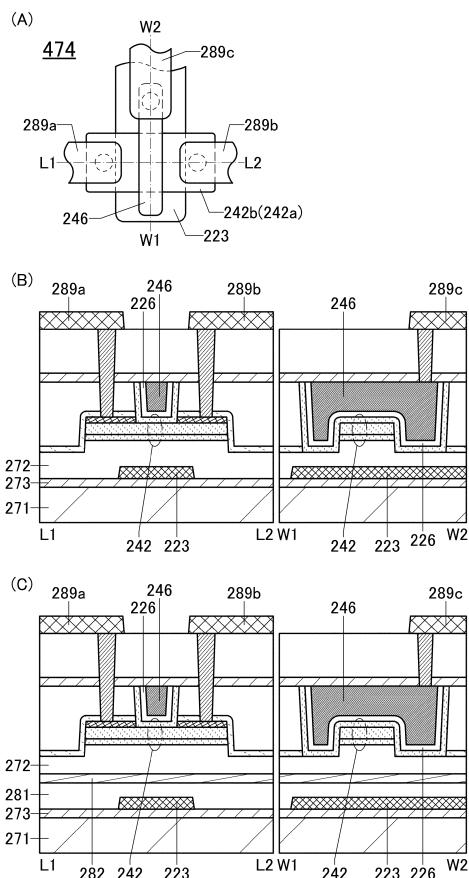

#### 【0173】

図19(A)および図19(B)に示すトランジスタ474は、絶縁層273と絶縁層272の間にバックゲート電極として機能する電極223を設けた点がトランジスタ473と異なる。図19(A)は、トランジスタ474の平面図である。図19(B)は、図19(A)にL1-L2の一点鎖線で示す部位と、W1-W2の一点鎖線で示す部位の断面図である。なお、電極223は、基板271と絶縁層273の間に設けても構わない。

#### 【0174】

電極246および電極223は、どちらもゲート電極として機能することができる。よって、絶縁層272、および絶縁層226は、それぞれがゲート絶縁層として機能することができる。

#### 【0175】

50

20

30

40

50

半導体層 242 を挟んで電極 246 および電極 223 を設けることで、更には、電極 246 および電極 223 を同電位とすることで、半導体層 242 においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ 474 のオン電流が大きくなると共に、電界効果移動度が高くなる。

#### 【 0176 】

また、例えば、図 19 (C) に示すように、電極 223 上に絶縁層 281 を形成し、絶縁層 281 上に絶縁層 282 を形成し、絶縁層 282 上に絶縁層 272 を形成してもよい。絶縁層 281 および絶縁層 282 は、絶縁層 272 と同様の材料および方法で形成することができる。

#### 【 0177 】

なお、絶縁層 282 を酸化ハフニウム、酸化アルミニウム、酸化タンタル、アルミニウムシリケートなどで形成することで、絶縁層 282 を電荷捕獲層として機能させることができる。絶縁層 282 に電子を注入することで、トランジスタのしきい値電圧を変動させることができるのである。絶縁層 282 への電子の注入は、例えば、トンネル効果を利用すればよい。電極 223 に正の電圧を印加することによって、トンネル電子を絶縁層 282 に注入することができる。

#### 【 0178 】

<成膜方法について>

本明細書等に示す電極などの導電層、絶縁層、および半導体層は、CVD法、蒸着法、またはスパッタリング法などを用いて形成することができる。一般に、CVD法は、プラズマを利用するプラズマCVD (PECVD : Plasma Enhanced CVD) 法、熱を利用する熱CVD (TCVD : Thermal CVD) 法などに分類できる。さらに用いる原料ガスによって金属CVD (MCVD : Metal CVD) 法、有機金属CVD (MOCVD : Metal Organic CVD) 法などに分類できる。

#### 【 0179 】

また、一般に、蒸着法は、抵抗加熱蒸着法、電子線蒸着法、MBE (Molecular Beam Epitaxy) 法、PLD (Pulsed Laser Deposition) 法、IAD (Ion beam Assisted Deposition) 法、ALD (Atomic Layer Deposition) 法などに分類できる。

#### 【 0180 】

プラズマCVD法は、比較的低温で高品質の膜が得られる。また、MOCVD法や蒸着法などの、成膜時にプラズマを用いない成膜方法を用いると、被形成面にダメージが生じにくく、また、欠陥の少ない膜が得られる。

#### 【 0181 】

また、一般に、スパッタリング法は、DCスパッタリング法、マグネットロンスパッタリング法、RFスパッタリング法、イオンビームスパッタリング法、ECR (Electron Cyclotron Resonance) スパッタリング法、対向ターゲットスパッタリング法などに分類できる。

#### 【 0182 】

対向ターゲットスパッタリング法では、プラズマがターゲット間に閉じこめられるため、基板へのプラズマダメージを低減することができる。また、ターゲットの傾きによっては、スパッタリング粒子の基板への入射角度を浅くすることができるため、段差被覆性を高めることができる。

#### 【 0183 】

なお、CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いる

10

20

30

40

50

ことが好ましい場合もある。

**【0184】**

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、トランジスタや半導体装置の生産性を高めることができる場合がある。

10

**【0185】**

<基板>

基板271として用いる材料に大きな制限はない。目的に応じて、透光性の有無や加熱処理に耐えうる程度の耐熱性などを勘案して決定すればよい。例えばバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、基板271として、半導体基板、可撓性基板(フレキシブル基板)、貼り合わせフィルム、基材フィルムなどを用いてもよい。

**【0186】**

半導体基板としては、例えば、シリコン、もしくはゲルマニウムなどを材料とした単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、もしくは酸化ガリウムを材料とした化合物半導体基板などがある。また、半導体基板は、単結晶半導体であってもよいし、多結晶半導体であってもよい。

20

**【0187】**

可撓性基板、貼り合わせフィルム、基材フィルムなどの材料としては、例えば、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、ポリテトラフルオロエチレン(PTFE)、ポリプロピレン、ポリエステル、ポリフッ化ビニル、ポリ塩化ビニル、ポリオレフィン、ポリアミド(ナイロン、アラミドなど)、ポリイミド、ポリカーボネート、アラミド、エポキシ樹脂、アクリル樹脂などを用いることができる。

**【0188】**

30

基板271に用いる可撓性基板は、線膨張率が低いほど環境による変形が抑制されて好ましい。基板271に用いる可撓性基板は、例えば、線膨張率が $1 \times 10^{-3} / K$ 以下、 $5 \times 10^{-5} / K$ 以下、または $1 \times 10^{-5} / K$ 以下の材質を用いればよい。特に、アラミドは、線膨張率が低いため、可撓性基板として好適である。

**【0189】**

<絶縁層>

絶縁層272、絶縁層226、絶縁層225、絶縁層228、および絶縁層229は、窒化アルミニウム、酸化アルミニウム、窒化酸化アルミニウム、酸化窒化アルミニウム、酸化マグネシウム、窒化シリコン、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタル、アルミニウムシリケートなどから選ばれた材料を、単層でまたは積層して用いる。また、酸化物材料、窒化物材料、酸化窒化物材料、窒化酸化物材料のうち、複数の材料を混合した材料を用いてもよい。

40

**【0190】**

なお、本明細書中において、窒化酸化物とは、酸素よりも窒素の含有量が多い化合物をいう。また、酸化窒化物とは、窒素よりも酸素の含有量が多い化合物をいう。なお、各元素の含有量は、例えば、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)等を用いて測定することができる。

**【0191】**

50

特に絶縁層 272 および絶縁層 229 は、不純物が透過しにくい絶縁性材料を用いて形成することが好ましい。例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁材料を、単層で、または積層で用いればよい。例えば、不純物が透過しにくい絶縁性材料として、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタル、窒化シリコンなどを挙げることができる。また、絶縁層 272 または絶縁層 229 として、絶縁性の高い酸化インジウム錫亜鉛 (In - Sn - Zn 酸化物) などを用いてもよい。

10

#### 【0192】

絶縁層 272 に不純物が透過しにくい絶縁性材料を用いることで、基板 271 側からの不純物の拡散を抑制し、トランジスタの信頼性を高めることができる。絶縁層 229 に不純物が透過しにくい絶縁性材料を用いることで、絶縁層 229 側からの不純物の拡散を抑制し、トランジスタの信頼性を高めることができる。

#### 【0193】

絶縁層 272、絶縁層 226、絶縁層 225、絶縁層 228、および絶縁層 229 として、これらの材料で形成される絶縁層を複数積層して用いてもよい。絶縁層 272、絶縁層 226、絶縁層 225、絶縁層 228、および絶縁層 229 の形成方法は特に限定されず、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法、スピンドル法などの各種形成方法を用いることができる。

20

#### 【0194】

例えば、熱 CVD 法を用いて、酸化アルミニウムを成膜する場合には、溶媒とアルミニウム前駆体化合物を含む液体 (トリメチルアルミニウム (TMA) など) を気化させた原料ガスと、酸化剤として H<sub>2</sub>O の 2 種類のガスを用いる。なお、トリメチルアルミニウムの化学式は Al (CH<sub>3</sub>)<sub>3</sub> である。また、他の材料液としては、トリス (ジメチルアミド) アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス (2,2,6,6-テトラメチル-3,5-ヘプタンジオナート) などがある。

#### 【0195】

また、半導体層 242 として酸化物半導体を用いる場合、半導体層 242 中の水素濃度の増加を防ぐために、絶縁層中の水素濃度を低減することが好ましい。特に、半導体層 242 と接する絶縁層中の水素濃度を低減することが好ましい。具体的には、絶縁層中の水素濃度を、SIMSにおいて、 $2 \times 10^{20}$  atoms/cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下とする。また、半導体層 242 中の窒素濃度の増加を防ぐために、絶縁層中の窒素濃度を低減することが好ましい。特に、半導体層 242 と接する絶縁層中の窒素濃度を低減することが好ましい。具体的には、絶縁層中の窒素濃度を、SIMSにおいて、 $5 \times 10^{19}$  atoms/cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下とする。

30

#### 【0196】

なお、SIMS 分析によって測定された濃度は、プラスマイナス 40 % の変動を含む場合がある。

#### 【0197】

また、半導体層 242 として酸化物半導体を用いる場合、絶縁層は、加熱により酸素が放出される絶縁層を用いて形成することが好ましい。特に、半導体層 242 と接する絶縁層は、加熱により酸素が放出される絶縁層が好ましい。例えば、絶縁層の表面温度が 100 以上 700 以下、好ましくは 100 以上 500 以下の加熱処理で行われる昇温脱離ガス分析法 (TDS : Thermal Desorption Spectroscopy) において、当該絶縁層の酸素原子に換算した酸素の脱離量は、 $1.0 \times 10^{18}$  a

40

50

$\text{atoms/cm}^3$  以上が好ましく、 $1.0 \times 10^{19} \text{ atoms/cm}^3$  以上がより好ましく、 $1.0 \times 10^{20} \text{ atoms/cm}^3$  がさらに好ましい。なお、本明細書などにおいて、加熱により放出される酸素を「過剰酸素」ともいう。

#### 【0198】

また、過剰酸素を含む絶縁層は、絶縁層に酸素を添加する処理を行って形成することもできる。酸素を添加する処理は、酸素雰囲気下による熱処理や、イオン注入装置、イオンドーピング装置またはプラズマ処理装置を用いて行うことができる。酸素を添加するためのガスとしては、 $^{16}\text{O}_2$  もしくは $^{18}\text{O}_2$ などの酸素ガス、亜酸化窒素ガスまたはオゾンガスなどを用いることができる。なお、本明細書では酸素を添加する処理を「酸素ドープ処理」ともいう。

10

#### 【0199】

また、絶縁層を、酸素を含む雰囲気中でスパッタリング法により成膜することで、被形成層に酸素を導入することができる。

#### 【0200】

また、一般に、容量素子は対向する二つの電極の間に誘電体を挟む構成を有し、誘電体の厚さが薄いほど（対向する二つの電極間距離が短いほど）、また、誘電体の誘電率が大きいほど容量値が大きくなる。ただし、容量素子の容量値を増やすために誘電体を薄くすると、トンネル効果などに起因して、二つの電極間に意図せずに流れる電流（以下、「リーク電流」ともいう。）が増加しやすくなり、また、容量素子の絶縁耐圧が低下しやすくなる。

20

#### 【0201】

トランジスタのゲート電極、ゲート絶縁層、半導体層が重畠する部分は、容量素子として機能する（以下、「ゲート容量」ともいう。）。なお、半導体層の、ゲート絶縁層を介してゲート電極と重畠する領域にチャネルが形成される。すなわち、ゲート電極とチャネル形成領域が、容量素子の二つの電極として機能する。また、ゲート絶縁層が容量素子の誘電体として機能する。ゲート容量の容量値は大きいほうが好ましいが、容量値を大きくするためにゲート絶縁層を薄くすると、前述のリーク電流の増加や、絶縁耐圧の低下といった問題が生じやすい。

#### 【0202】

そこで、誘電体として、ハフニウムシリケート ( $\text{HfSi}_x\text{O}_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $\text{HfSi}_x\text{O}_y\text{N}_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ ))、窒素が添加されたハフニウムアルミネート ( $\text{HfAl}_x\text{O}_y\text{N}_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ ))、酸化ハフニウム、または酸化イットリウムなどの $\text{high-k}$ 材料を用いると、誘電体を厚くしても、容量素子の容量値を十分確保することが可能となる。

30

#### 【0203】

例えば、誘電体として誘電率が大きい $\text{high-k}$ 材料を用いると、誘電体を厚くしても、誘電体として酸化シリコンを用いた場合と同等の容量値を実現できるため、容量素子を形成する二つの電極間に生じるリーク電流を低減できる。なお、誘電体を $\text{high-k}$ 材料と、他の絶縁材料との積層構造としてもよい。

#### 【0204】

また、絶縁層275は、平坦な表面を有する絶縁層である。絶縁層275としては、上記絶縁性材料のほかに、ポリイミド、アクリル系樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ系樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層してもよい。

40

#### 【0205】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成された $\text{Si-O-Si}$ 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有して

50

いても良い。

**【0206】**

絶縁層275の形成方法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法など）、印刷法（スクリーン印刷、オフセット印刷など）などを用いればよい。

**【0207】**

また、試料表面にCMP処理を行なってもよい。CMP処理を行うことにより、試料表面の凹凸を低減し、この後形成される絶縁層や導電層の被覆性を高めることができる。

**【0208】**

<半導体層>

10

半導体層242としては、単結晶半導体、多結晶半導体、微結晶半導体、非晶質半導体などを用いることができる。半導体材料としては、例えば、シリコンや、ゲルマニウムなどを用いることができる。また、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、酸化物半導体、窒化物半導体などの化合物半導体や、有機半導体などを用いることができる。

**【0209】**

また、半導体層242として有機物半導体を用いる場合は、芳香環をもつ低分子有機材料や電子共役系導電性高分子などを用いることができる。例えば、ルブレン、テトラセン、ペンタセン、ペリレンジイミド、テトラシアノキノジメタン、ポリチオフェン、ポリアセチレン、ポリパラフェニレンビニレンなどを用いることができる。

20

**【0210】**

また、前述した通り、酸化物半導体のバンドギャップは2eV以上あるため、半導体層242に酸化物半導体を用いると、オフ電流が極めて少ないトランジスタを実現することができる。また、OSトランジスタは、ソースとドレイン間の絶縁耐圧が高い。よって、信頼性の良好なトランジスタを提供できる。また、信頼性の良好な表示装置や半導体装置などを提供できる。

**【0211】**

本実施の形態では、半導体層242として酸化物半導体を用いる場合について説明する。半導体層242に用いる酸化物半導体は、例えば、インジウム（In）を含む酸化物半導体を用いることが好ましい。酸化物半導体は、例えば、インジウムを含むと、キャリア移動度（電子移動度）が高くなる。また、酸化物半導体は、元素Mを含むと好ましい。

30

**【0212】**

元素Mは、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどである。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、マグネシウムなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。元素Mは、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、酸化物半導体は、亜鉛を含むと好ましい。酸化物半導体は亜鉛を含むと結晶化しやすくなる場合がある。

40

**【0213】**

ただし、半導体層242に用いる酸化物半導体は、インジウムを含む酸化物に限定されない。酸化物半導体は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物、酸化ガリウムなどの、インジウムを含まず、亜鉛を含む酸化物、ガリウムを含む酸化物、スズを含む酸化物半導体などであっても構わない。

**【0214】**

例えば、半導体層242として、熱CVD法で $InGaZnO_x$  ( $X > 0$ ) 膜を成膜する場合には、トリメチルインジウム( $In(CH_3)_3$ )、トリメチルガリウム( $Ga(CH_3)_3$ )、およびジメチル亜鉛( $Zn(CH_3)_2$ )を用いる。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム( $Ga(C_2H_5)_3$ )

50

<sub>3</sub>) を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛 ( $Zn(C_2H_5)_2$ ) を用いることもできる。

#### 【0215】

例えば、半導体層242として、ALD法で、 $InGaZnO_x$  ( $X > 0$ ) 膜を成膜する場合には、 $In(CH_3)_3$  ガスと $O_3$  ガスを順次繰り返し導入して $InO_2$  層を形成し、その後、 $Ga(CH_3)_3$  ガスと $O_3$  ガスを順次繰り返し導入して $GaO$  層を形成し、更にその後 $Zn(CH_3)_2$  ガスと $O_3$  ガスを順次繰り返し導入して $ZnO$  層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを用いて $InGaO_2$  層や $InZnO_2$  層、 $GaInO$  層、 $ZnInO$  層、 $GaZnO$  層などの混合化合物層を形成しても良い。なお、 $O_3$  ガスに変えて $Ar$  等の不活性ガスで水をバーピングした $H_2O$  ガスを用いても良いが、 $H$  を含まない $O_3$  ガスを用いる方が好ましい。また、 $In(CH_3)_3$  ガスにかえて、 $In(C_2H_5)_3$  ガスやトリス(アセチルアセトナト)インジウムを用いても良い。なお、トリス(アセチルアセトナト)インジウムは、 $In(acac)_3$  とも呼ぶ。また、 $Ga(CH_3)_3$  ガスにかえて、 $Ga(C_2H_5)_3$  ガスやトリス(アセチルアセトナト)ガリウムを用いても良い。なお、トリス(アセチルアセトナト)ガリウムは、 $Ga(acac)_3$  とも呼ぶ。また、 $Zn(CH_3)_2$  ガスや、酢酸亜鉛を用いても良い。これらのガス種には限定されない。

#### 【0216】

酸化物半導体をスパッタリング法で成膜する場合、パーティクル数低減のため、インジウムを含むターゲットを用いると好ましい。また、元素Mの原子数比が高い酸化物ターゲットを用いた場合、ターゲットの導電性が低くなる場合がある。インジウムを含むターゲットを用いる場合、ターゲットの導電率を高めることができ、DC放電、AC放電が容易となるため、大面積の基板へ対応しやすくなる。したがって、半導体装置の生産性を高めることができる。

#### 【0217】

また、前述した通り、酸化物半導体をスパッタリング法で成膜する場合、ターゲットの原子数比を、例えば、 $In : M : Zn$  が  $3 : 1 : 1$ 、 $3 : 1 : 2$ 、 $3 : 1 : 4$ 、 $1 : 1 : 0.5$ 、 $1 : 1 : 1$ 、 $1 : 1 : 2$ 、 $1 : 4 : 4$ 、 $5 : 1 : 7$ 、 $4 : 2 : 4$ 、 $1$  などとすればよい。

#### 【0218】

なお、酸化物半導体をスパッタリング法で成膜すると、ターゲットの原子数比からずれた原子数比の酸化物半導体が成膜される場合がある。特に、亜鉛は、ターゲットの原子数比よりも成膜された膜の原子数比が小さくなる場合がある。具体的には、ターゲットに含まれる亜鉛の原子数比の 40 atom % 以上 90 atom % 程度以下となる場合がある。

#### 【0219】

また、OSトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物及び酸素欠損を低減して高純度真性化し、半導体層242を高純度真性または実質的に高純度真性と見なせる酸化物半導体層とすることが好ましい。また、少なくとも半導体層242中のチャネル形成領域が高純度真性または実質的に高純度真性と見なせる酸化物半導体層とすることが好ましい。

#### 【0220】

また、半導体層242に酸化物半導体を用いる場合は、CAAC-OS (CAAC-axis Aligned Crystalline Oxide Semiconductor) を用いることが好ましい。CAAC-OSは、c軸配向した複数の結晶部を有する酸化物半導体の一つである。

#### 【0221】

また、半導体層242に用いる酸化物半導体層は、CAACでない領域が当該酸化物半導体層全体の 20 % 未満であることが好ましい。

#### 【0222】

10

20

30

40

50

C A A C - O S は誘電率異方性を有する。具体的には、C A A C - O S は a 軸方向および b 軸方向の誘電率よりも、c 軸方向の誘電率が大きい。チャネルが形成される半導体層に C A A C - O S を用いて、ゲート電極を c 軸方向に配置したトランジスタは、c 軸方向の誘電率が大きいため、ゲート電極から生じる電界が C A A C - O S 全体に届きやすい。よって、サブスレッシュルドスイング値 (S 値) を小さくすることができる。また、半導体層に C A A C - O S を用いたトランジスタは、微細化による S 値の増大が生じにくい。

#### 【 0 2 2 3 】

また、C A A C - O S は a 軸方向および b 軸方向の誘電率が小さいため、ソースとドレイン間に生じる電界の影響が緩和される。よって、チャネル長変調効果や、短チャネル効果、などが生じにくく、トランジスタの信頼性を高めることができる。

10

#### 【 0 2 2 4 】

ここで、チャネル長変調効果とは、ドレイン電圧がしきい値電圧よりも高い場合に、ドレイン側から空乏層が広がり、実効上のチャネル長が短くなる現象を言う。また、短チャネル効果とは、チャネル長が短くなることにより、しきい値電圧の低下などの電気特性の悪化が生じる現象を言う。微細なトランジスタほど、これらの現象による電気特性の劣化が生じやすい。

#### 【 0 2 2 5 】

酸化物半導体層の形成後、酸素ドープ処理を行ってもよい。また、酸化物半導体層に含まれる水分または水素などの不純物をさらに低減して、酸化物半導体層を高純度化するために、加熱処理を行うことが好ましい。

20

#### 【 0 2 2 6 】

例えば、減圧雰囲気下、窒素や希ガスなどの不活性雰囲気下、酸化性雰囲気下、又は超乾燥エア (C R D S (キャビティリングダウンレーザー分光法) 方式の露点計を用いて測定した場合の水分量が 2 0 p p m (露点換算で - 5 5 ) 以下、好ましくは 1 p p m 以下、好ましくは 1 0 p p b 以下の空気) 雰囲気下で、酸化物半導体層に加熱処理を施す。なお、酸化性雰囲気とは、酸素、オゾンまたは窒化酸素などの酸化性ガスを 1 0 p p m 以上含有する雰囲気をいう。また、不活性雰囲気とは、前述の酸化性ガスが 1 0 p p m 未満であり、その他、窒素または希ガスで充填された雰囲気をいう。

#### 【 0 2 2 7 】

また、加熱処理を行うことにより、不純物の放出と同時に絶縁層 2 2 6 に含まれる酸素を酸化物半導体層中に拡散させ、当該酸化物半導体層に含まれる酸素欠損を低減することができる。なお、不活性雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 1 0 p p m 以上、1 % 以上または 1 0 % 以上含む雰囲気で加熱処理を行ってもよい。なお、加熱処理は、酸化物半導体層の形成後であればいつ行ってもよい。

30

#### 【 0 2 2 8 】

加熱処理に用いる加熱装置に特別な限定はなく、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置であってもよい。例えば、電気炉や、L R T A (L a m p R a p i d T h e r m a l A n n e a l) 装置、G R T A (G a s R a p i d T h e r m a l A n n e a l) 装置等のR T A (R a p i d T h e r m a l A n n e a l) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。

40

#### 【 0 2 2 9 】

加熱処理は、2 5 0 以上 6 5 0 以下、好ましくは 3 0 0 以上 5 0 0 以下で行えばよい。処理時間は 2 4 時間以内とする。2 4 時間を超える加熱処理は生産性の低下を招くため好ましくない。

#### 【 0 2 3 0 】

<電極>

電極 2 4 6 、電極 2 2 3 、電極 2 4 4 a 、電極 2 4 4 b 、電極 2 8 7 、電極 2 9 7 、電極

50

289a、電極289b、電極292a、電極292bを形成するための導電性材料としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニアム、ベリリウムなどから選ばれた金属元素を1種以上含む材料を用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。これらの材料で形成される導電層を複数積層して用いてもよい。

#### 【0231】

また、電極246、電極223、電極244a、電極244b、電極287、電極297、電極289a、電極289b、電極292a、電極292bを形成するための導電性材料に、インジウム錫酸化物(ITO: Indium Tin Oxide)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、インジウムガリウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物などの酸素を含む導電性材料、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を適用することもできる。また、前述した金属元素を含む材料と、酸素を含む導電性材料を組み合わせた積層構造とすることもできる。また、前述した金属元素を含む材料と、窒素を含む導電性材料を組み合わせた積層構造とすることもできる。また、前述した金属元素を含む材料、酸素を含む導電性材料、および窒素を含む導電性材料を組み合わせた積層構造とすることもできる。導電性材料の形成方法は特に限定されず、蒸着法、CVD法、スパッタリング法などの各種形成方法を用いることができる。

#### 【0232】

##### <コンタクトプラグ>

コンタクトプラグ288a、コンタクトプラグ288b、コンタクトプラグ288c、コンタクトプラグ298a、およびコンタクトプラグ298bとしては、例えば、タングステン、ポリシリコン等の埋め込み性の高い導電性材料を用いることができる。また、当該材料の側面および底面を、チタン層、窒化チタン層またはこれらの積層からなるバリア層(拡散防止層)で覆ってもよい。この場合、バリア層も含めてコンタクトプラグという場合がある。

#### 【0233】

本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。また、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

#### 【0234】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0235】

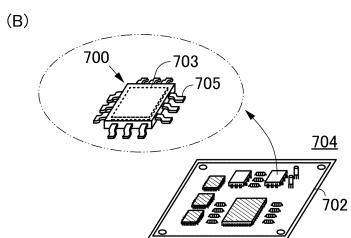

##### (実施の形態3)

本実施の形態では、上述の実施の形態で説明した半導体装置を電子部品に適用する例、および該電子部品を具備する電子機器の例について、図21、図22を用いて説明する。なお、電子部品は、半導体パッケージ、またはIC用パッケージともいう。電子部品は、端子取り出し方向や、端子の形状に応じて、複数の規格や名称が存在する。そこで、本実施の形態では、電子部品の一例について説明する。

#### 【0236】

電子部品は、組み立て工程(後工程)において、上記実施の形態に示した半導体装置と該半導体装置以外の部品が組み合わされて完成する。

#### 【0237】

図21(A)に示すフローチャートを用いて、後工程について説明する。前工程において上記実施の形態に示した半導体装置を有する素子基板が完成した後、該素子基板の裏面(半導体装置などが形成されていない面)を研削する「裏面研削工程」を行なう(ステップS1)。研削により素子基板を薄くすることで、素子基板の反りなどを低減し、電子部品

10

20

30

40

50

の小型化を図ることができる。

【0238】

次に、素子基板を複数のチップに分離する「ダイシング工程」を行う(ステップS2)。そして、分離したチップを個々ピックアップしてリードフレーム上に接合する「ダイボンディング工程」を行う(ステップS3)。ダイボンディング工程におけるチップとリードフレームとの接合は、樹脂による接合や、テープによる接合など、適宜製品に応じて適した方法を選択する。なお、リードフレームに代えてインターポーザ基板上にチップを接合してもよい。

【0239】

次いで、リードフレームのリードとチップ上の電極とを、金属の細線(ワイヤー)で電気的に接続する「ワイヤーボンディング工程」を行う(ステップS4)。金属の細線には、銀線や金線を用いることができる。また、ワイヤーボンディングは、ボールボンディングや、ウェッジボンディングを用いることができる。

10

【0240】

ワイヤーボンディングされたチップは、エポキシ樹脂などで封止される「封止工程(モールド工程)」が施される(ステップS5)。封止工程を行うことで電子部品の内部が樹脂で充填され、チップに内蔵される回路部やチップとリードを接続するワイヤーを機械的な外力から保護することができ、また水分や埃による特性の劣化(信頼性の低下)を低減することができる。

【0241】

20

次いで、リードフレームのリードをめっき処理する「リードめっき工程」を行なう(ステップS6)。めっき処理によりリードの錆を防止し、後にプリント基板に実装する際のはんだ付けをより確実に行なうことができる。次いで、リードを切断および成形加工する「成形工程」を行なう(ステップS7)。

【0242】

次いで、パッケージの表面に印字処理(マーキング)を施す「マーキング工程」を行なう(ステップS8)。そして外観形状の良否や動作不良の有無などを調べる「検査工程」(ステップS9)を経て、電子部品が完成する。

【0243】

以上説明した電子部品は、上述の実施の形態で説明したトランジスタを含む構成とすることができます。そのため、高温環境下における誤動作が低減され、且つ製造コストの抑制が図られた半導体装置を有する電子部品を実現することができる。該電子部品は、高温環境下における誤動作が低減され、且つ製造コストの抑制が図られた半導体装置を含むため、使用環境の制限が緩和され、小型化が図られた電子部品である。

30

【0244】

また、完成した電子部品の斜視模式図を図21(B)に示す。図21(B)では、電子部品の一例として、QFP(Quad Flat Package)の斜視模式図を示している。図21(B)に示す電子部品700は、リード705および半導体装置703を示している。半導体装置703としては、上記実施の形態に示した半導体装置などを用いることができる。

40

【0245】

図21(B)に示す電子部品700は、例えばプリント基板702に実装される。このような電子部品700が複数組み合わされて、それぞれがプリント基板702上で電気的に接続されることで電子部品が実装された基板(実装基板704)が完成する。完成した実装基板704は、電子機器などに用いられる。

【0246】

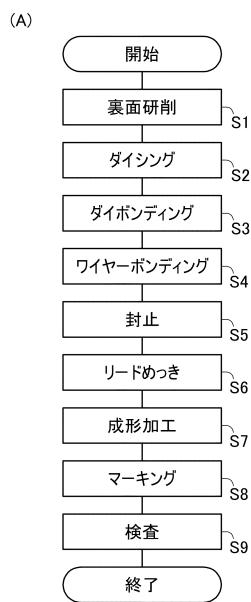

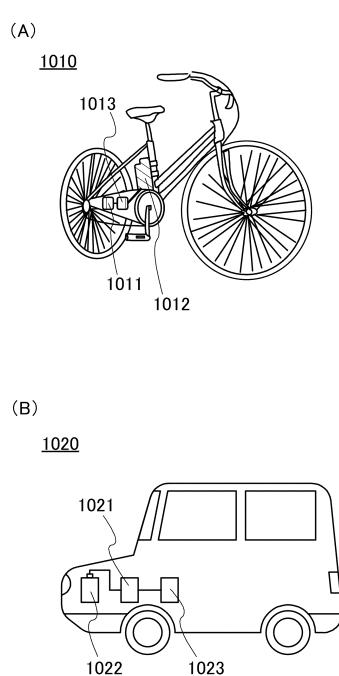

次いで図22を参照して、固定電源の電力で駆動する乗物類(自転車等)等に設けられる、インバータやモーターなどを駆動する駆動回路に、上述の電子部品を適用する応用例について説明する。

【0247】

50

図22(A)は、応用例として、電動自転車1010を示している。電動自転車1010は、モーター1011に電流を流すことによって動力を得るものである。また電動自転車1010は、モーター1011に流す電流を供給するための蓄電装置1012、およびモーターを駆動するための駆動回路1013、を有する。なお、図22(A)ではペダルを図示したが、なくてもよい。

#### 【0248】

駆動回路1013には、先の実施の形態に示す半導体装置を有する電子部品が設けられた実装基板が搭載されている。そのため、小型化が図られた電子部品を備えた電気自転車を実現することができる。また、消費電力が少なく、航続距離の長い電動自転車を実現することができる。また、信頼性の良好な電動自転車を実現することができる。

10

#### 【0249】

図22(B)は、別の応用例として、電気自動車1020を示している。電気自動車1020は、モーター1021に電流を流すことによって動力を得るものである。また電気自動車1020は、モーター1021に流す電流を供給するための蓄電装置1022、およびモーターを駆動するための駆動回路1023、を有する。

20

#### 【0250】

駆動回路1023には、先の実施の形態に示す半導体装置を有する電子部品が設けられた実装基板が搭載されている。そのため、小型化が図られた電子部品を備えた電気自動車を実現することができる。また、消費電力が少なく、航続距離の長い電動自動車を実現することができる。また、信頼性の良好な電動自動車を実現することができる。

#### 【0251】

また、先の実施の形態に示す半導体装置を有する電子部品は、電気自動車(EV)だけでなく、ハイブリッド車(HEV)やプラグインハイブリッド車(PHEV)などに用いることもできる。

#### 【0252】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置を有する電子部品が設けられた実装基板が搭載されている。このため、小型化が図られた電子部品を備えた電子機器を実現することができる。また、消費電力が少ない電子機器を実現することができる。また、信頼性の良好な電子機器を実現することができる。

30

#### 【0253】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0254】

##### (実施の形態4)

本発明の一態様に係る半導体装置は、様々な電子機器の制御回路に用いることができる。図23に、本発明の一態様に係る半導体装置を用いた電子機器の具体例を示す。

#### 【0255】

本発明の一態様に係る半導体装置を用いた電子機器として、テレビ、モニタ等の表示装置、照明装置、デスクトップ型或いはノート型のパーソナルコンピュータ、ワードプロセッサ、DVD(Digital Versatile Disc)などの記録媒体に記憶された静止画又は動画を再生する画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ、ステレオ、置き時計、壁掛け時計、コードレス電話子機、トランシーバ、携帯電話、自動車電話、携帯型ゲーム機、タブレット型端末、パチンコ機などの大型ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍端末、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、温水器、扇風機、毛髪乾燥機、エアコンディショナー、加湿器、除湿器などの空調設備、食器洗い器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、懐中電灯、チェーンソーなどの工具、煙感知器、透析装置などの医療機器などが挙げられる。

40

さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット

50

、電力貯蔵システム、電力の平準化やスマートグリッドのための蓄電装置などの産業機器が挙げられる。

#### 【0256】

また、蓄電装置からの電力を用いて電動機により推進する移動体なども、電子機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車（EV）、内燃機関と電動機を併せ持ったハイブリッド車（HEV）、プラグインハイブリッド車（PHEV）、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型又は大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船などが挙げられる。10

#### 【0257】

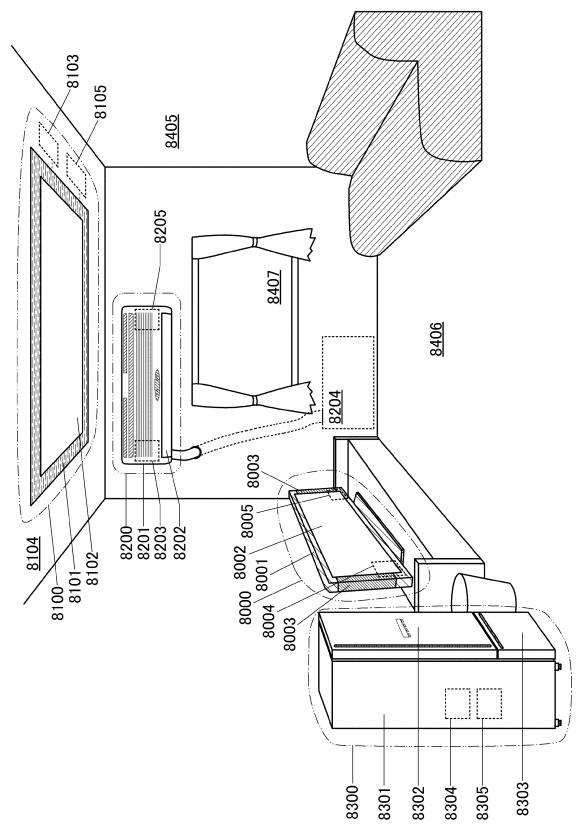

図23に、電子機器の一例を示す。図23において、表示装置8000は、本発明の一態様に係る半導体装置8004を用いた電子機器の一例である。具体的に、表示装置8000は、TV放送受信用の表示装置に相当し、筐体8001、表示部8002、スピーカ部8003、半導体装置8004、蓄電装置8005などを有する。本発明の一態様に係る半導体装置8004は、筐体8001の内部に設けられている。半導体装置8004により、表示装置8000内部にある冷却ファンの駆動や発光輝度の調整などを制御することができる。また、表示装置8000は、商用電源から電力の供給を受けることもできるし、蓄電装置8005に蓄積された電力を用いることもできる。20

#### 【0258】

表示部8002には、液晶表示装置、有機EL素子などの発光素子を各画素に備えた発光装置、電気泳動表示装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)などの表示装置を用いることができる。20

#### 【0259】

なお、表示装置には、TV放送受信用の他、パーソナルコンピュータ用、広告表示用など、全ての情報表示用表示装置が含まれる。

#### 【0260】

図23において、据え付け型の照明装置8100は、本発明の一態様に係る半導体装置8103を用いた電子機器の一例である。具体的に、照明装置8100は、筐体8101、光源8102、半導体装置8103、蓄電装置8105などを有する。図23では、半導体装置8103が、筐体8101及び光源8102が据え付けられた天井8104の内部に設けられている場合を例示しているが、半導体装置8103は、筐体8101の内部に設けられていても良い。半導体装置8103により、光源8102の発光輝度などを制御することができる。また、照明装置8100は、商用電源から電力の供給を受けることもできるし、蓄電装置に蓄積された電力を用いることもできる。30

#### 【0261】

なお、図23では天井8104に設けられた据え付け型の照明装置8100を例示しているが、本発明の一態様に係る半導体装置は、天井8104以外、例えば側壁8405、床8406、窓8407などに設けられた据え付け型の照明装置に用いることもできるし、卓上型の照明装置などに用いることもできる。40

#### 【0262】

また、光源8102には、電力を利用して人工的に光を得る人工光源を用いることができる。具体的には、白熱電球、蛍光灯などの放電ランプ、LEDや有機EL素子などの発光素子が、上記人工光源の一例として挙げられる。

#### 【0263】

図23において、室内機8200及び室外機8204を有するエアコンディショナーは、本発明の一態様に係る半導体装置8203を用いた電子機器の一例である。具体的に、室内機8200は、筐体8201、送風口8202、半導体装置8203、蓄電装置8205などを有する。図23では、半導体装置8203が、室内機8200に設けられている50

場合を例示しているが、半導体装置 8203 は室外機 8204 に設けられていても良い。或いは、室内機 8200 と室外機 8204 の両方に、半導体装置 8203 が設けられても良い。半導体装置 8203 により、エアコンディショナーのコンプレッサに用いられるモーターの動作を制御することができる。また、エアコンディショナーは、商用電源から電力の供給を受けることもできるし、蓄電装置 8205 に蓄積された電力を用いることもできる。

#### 【0264】

なお、図23では、室内機と室外機で構成されるセパレート型のエアコンディショナーを例示しているが、室内機の機能と室外機の機能とを1つの筐体に有する一体型のエアコンディショナーに、本発明の一態様に係る半導体装置を用いることもできる。

10

#### 【0265】

図23において、電気冷凍冷蔵庫 8300 は、本発明の一態様に係る半導体装置 8304 を用いた電子機器の一例である。具体的に、電気冷凍冷蔵庫 8300 は、筐体 8301、冷蔵室用扉 8302、冷凍室用扉 8303、半導体装置 8304、蓄電装置 8305 などを有する。図23では、筐体 8301 の内部に設けられている半導体装置 8304 により、電気冷凍冷蔵庫 8300 のコンプレッサに用いられるモーターの動作を制御することができる。また、電気冷凍冷蔵庫 8300 は、商用電源から電力の供給を受けることもできるし、蓄電装置 8305 に蓄積された電力を用いることもできる。

#### 【0266】

なお、上述した電子機器のうち、電子レンジなどの高周波加熱装置、電気炊飯器などの電子機器は、短時間で高い電力を必要とする。また、一定期間安定して高い電力を制御する必要がある。本発明の一態様に係る半導体装置を用いることで、電力の制御を安定して行なうことができるため、信頼性の高い電子機器を実現することができる。

20

#### 【0267】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【符号の説明】

#### 【0268】

|     |        |    |

|-----|--------|----|

| 100 | 半導体装置  |    |

| 101 | 端子     |    |

| 102 | 端子     | 30 |

| 103 | 端子     |    |

| 104 | 端子     |    |

| 105 | 端子     |    |

| 106 | 端子     |    |

| 110 | 半導体装置  |    |

| 111 | トランジスタ |    |

| 112 | トランジスタ |    |

| 113 | トランジスタ |    |

| 114 | トランジスタ |    |

| 117 | 容量素子   | 40 |

| 120 | 半導体装置  |    |

| 121 | 配線     |    |

| 122 | 配線     |    |

| 123 | 配線     |    |

| 124 | 配線     |    |

| 125 | 配線     |    |

| 130 | 半導体装置  |    |

| 131 | ノード    |    |

| 132 | ノード    |    |

| 133 | ノード    | 50 |

|       |         |    |

|-------|---------|----|

| 1 5 1 | 期間      |    |

| 1 5 2 | 期間      |    |

| 2 1 4 | 層       |    |

| 2 2 3 | 電極      |    |

| 2 2 5 | 絶縁層     |    |

| 2 2 6 | 絶縁層     |    |

| 2 2 7 | 絶縁層     |    |

| 2 2 8 | 絶縁層     |    |

| 2 2 9 | 絶縁層     |    |

| 2 4 2 | 半導体層    | 10 |

| 2 4 3 | 電極      |    |

| 2 4 6 | 電極      |    |

| 2 5 5 | 不純物     |    |

| 2 6 9 | 領域      |    |

| 2 7 1 | 基板      |    |

| 2 7 2 | 絶縁層     |    |

| 2 7 3 | 絶縁層     |    |

| 2 7 4 | 酸化物半導体層 |    |

| 2 7 5 | 絶縁層     |    |

| 2 7 6 | 絶縁層     | 20 |

| 2 7 7 | 絶縁層     |    |

| 2 8 1 | 絶縁層     |    |

| 2 8 2 | 絶縁層     |    |

| 2 8 7 | 電極      |    |

| 2 9 7 | 電極      |    |

| 3 8 2 | E c     |    |

| 3 8 6 | E c     |    |

| 3 8 7 | E c     |    |

| 3 9 0 | トラップ準位  |    |

| 4 1 0 | トランジスタ  | 30 |

| 4 1 1 | トランジスタ  |    |

| 4 2 0 | トランジスタ  |    |

| 4 2 1 | トランジスタ  |    |

| 4 2 2 | トランジスタ  |    |

| 4 2 5 | トランジスタ  |    |

| 4 2 6 | トランジスタ  |    |

| 4 3 0 | トランジスタ  |    |

| 4 3 1 | トランジスタ  |    |

| 4 4 0 | トランジスタ  |    |

| 4 4 1 | トランジスタ  | 40 |

| 4 4 2 | トランジスタ  |    |

| 4 4 3 | トランジスタ  |    |

| 4 4 4 | トランジスタ  |    |

| 4 4 5 | トランジスタ  |    |

| 4 4 6 | トランジスタ  |    |

| 4 4 7 | トランジスタ  |    |

| 4 4 8 | トランジスタ  |    |

| 4 5 0 | トランジスタ  |    |

| 4 5 1 | トランジスタ  |    |

| 4 5 2 | トランジスタ  | 50 |

|         |         |    |

|---------|---------|----|

| 4 7 3   | トランジスタ  |    |

| 4 7 4   | トランジスタ  |    |

| 7 0 0   | 電子部品    |    |

| 7 0 2   | プリント基板  |    |

| 7 0 3   | 半導体装置   |    |

| 7 0 4   | 実装基板    |    |

| 7 0 5   | リード     |    |

| 1 0 1 0 | 電動自転車   |    |

| 1 0 1 1 | モーター    |    |

| 1 0 1 2 | 蓄電装置    | 10 |

| 1 0 1 3 | 駆動回路    |    |

| 1 0 2 0 | 電気自動車   |    |

| 1 0 2 1 | モーター    |    |

| 1 0 2 2 | 蓄電装置    |    |

| 1 0 2 3 | 駆動回路    |    |

| 8 0 0 0 | 表示装置    |    |

| 8 0 0 1 | 筐体      |    |

| 8 0 0 2 | 表示部     |    |

| 8 0 0 3 | スピーカ部   |    |

| 8 0 0 4 | 半導体装置   | 20 |

| 8 0 0 5 | 蓄電装置    |    |

| 8 1 0 0 | 照明装置    |    |

| 8 1 0 1 | 筐体      |    |

| 8 1 0 2 | 光源      |    |

| 8 1 0 3 | 半導体装置   |    |

| 8 1 0 4 | 天井      |    |

| 8 1 0 5 | 蓄電装置    |    |

| 8 2 0 0 | 室内機     |    |

| 8 2 0 1 | 筐体      |    |

| 8 2 0 2 | 送風口     | 30 |

| 8 2 0 3 | 半導体装置   |    |

| 8 2 0 4 | 室外機     |    |

| 8 2 0 5 | 蓄電装置    |    |

| 8 3 0 0 | 電気冷凍冷蔵庫 |    |

| 8 3 0 1 | 筐体      |    |

| 8 3 0 2 | 冷蔵室用扉   |    |

| 8 3 0 3 | 冷凍室用扉   |    |

| 8 3 0 4 | 半導体装置   |    |

| 8 3 0 5 | 蓄電装置    |    |

| 8 4 0 5 | 側壁      | 40 |

| 8 4 0 6 | 床       |    |

| 8 4 0 7 | 窓       |    |

| 1 0 0 a | 半導体装置   |    |

| 1 0 0 b | 半導体装置   |    |

| 1 0 0 c | 半導体装置   |    |

| 1 1 0 a | 半導体装置   |    |

| 1 1 0 b | 半導体装置   |    |

| 1 1 0 c | 半導体装置   |    |

| 1 2 0 a | 半導体装置   |    |

| 1 3 0 a | 半導体装置   | 50 |

|         |          |

|---------|----------|

| 2 4 2 a | 半導体層     |

| 2 4 2 b | 半導体層     |

| 2 4 2 c | 半導体層     |

| 2 4 2 i | 半導体層     |

| 2 4 2 t | 半導体層     |

| 2 4 2 u | 半導体層     |

| 2 4 4 a | 電極       |

| 2 4 4 b | 電極       |

| 2 4 7 a | 開口       |

| 2 4 7 b | 開口       |

| 2 4 7 c | 開口       |

| 2 4 7 d | 開口       |

| 2 8 8 a | コンタクトプラグ |

| 2 8 8 b | コンタクトプラグ |

| 2 8 8 c | コンタクトプラグ |

| 2 8 9 a | 電極       |

| 2 8 9 b | 電極       |

| 2 8 9 c | 電極       |

| 2 9 2 a | 電極       |

| 2 9 2 b | 電極       |

| 2 9 8 a | コンタクトプラグ |

| 2 9 8 b | コンタクトプラグ |

| 3 8 3 a | E c      |

| 3 8 3 b | E c      |

| 3 8 3 c | E c      |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(56)参考文献 特開2014-003619(JP,A)

特開2014-016621(JP,A)

特開2014-067027(JP,A)

特開2013-041283(JP,A)

特開2014-241559(JP,A)

特開2014-075692(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L21/336,

H01L21/8232-21/8238,

H01L21/8249,

H01L27/06,

H01L27/07,

H01L27/085-27/092,

H01L27/118,

H01L29/786,

H03K19/00,

H03K19/01-19/082,

H03K19/094-19/096