(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2014-521222

(P2014-521222A)

(43) 公表日 平成26年8月25日(2014.8.25)

(51) Int.Cl.

F 1

テーマコード (参考)

|               |               |                  |        |       |   |

|---------------|---------------|------------------|--------|-------|---|

| <b>HO 1 L</b> | <b>25/04</b>  | <b>(2014.01)</b> | HO 1 L | 25/04 | Z |

| <b>HO 1 L</b> | <b>25/18</b>  | <b>(2006.01)</b> | HO 1 L | 25/08 | C |

| <b>HO 1 L</b> | <b>25/065</b> | <b>(2006.01)</b> | HO 1 L | 25/08 | Y |

| <b>HO 1 L</b> | <b>25/07</b>  | <b>(2006.01)</b> | HO 1 L | 25/08 | G |

審査請求 未請求 予備審査請求 未請求 (全 40 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2014-520276 (P2014-520276) |

| (86) (22) 出願日 | 平成24年7月11日 (2012.7.11)       |

| (85) 翻訳文提出日   | 平成26年3月5日 (2014.3.5)         |

| (86) 國際出願番号   | PCT/US2012/046249            |

| (87) 國際公開番号   | W02013/009866                |

| (87) 國際公開日    | 平成25年1月17日 (2013.1.17)       |

| (31) 優先権主張番号  | 61/542,495                   |

| (32) 優先日      | 平成23年10月3日 (2011.10.3)       |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 61/542,488                   |

| (32) 優先日      | 平成23年10月3日 (2011.10.3)       |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 13/346,201                   |

| (32) 優先日      | 平成24年1月9日 (2012.1.9)         |

| (33) 優先権主張国   | 米国 (US)                      |

|          |                                                                                           |

|----------|-------------------------------------------------------------------------------------------|

| (71) 出願人 | 309034272<br>インヴェンサンス・コーポレイション<br>アメリカ合衆国 カリフォルニア州 95<br>134、サン・ホセ、オーチャード・パー<br>クウェイ 3025 |

| (74) 代理人 | 100099623<br>弁理士 奥山 尚一                                                                    |

| (74) 代理人 | 100096769<br>弁理士 有原 幸一                                                                    |

| (74) 代理人 | 100107319<br>弁理士 松島 鉄男                                                                    |

| (74) 代理人 | 100114591<br>弁理士 河村 英文                                                                    |

| (74) 代理人 | 100125380<br>弁理士 中村 純子                                                                    |

最終頁に続く

(54) 【発明の名称】パッケージ内のメモリモジュール

## (57) 【要約】

超小型電子パッケージ10は、対向する第1の表面21及び第2の表面22を有する基板20と、第1の超小型電子素子30a、第2の超小型電子素子30b、第3の超小型電子素子30c、及び第4の超小型電子素子30dと、第2の表面に露出した端子25とを備える。各超小型電子素子30は、基板20の第1の表面21の方に向いた前面31と、前面31に複数のコンタクト35とを有する。超小型電子素子30の前面31は、第1の表面21に対し平行であり表面21の上に重なる単一の平面に配置できる。各超小型電子素子30は、前面に露しそれぞれの第1の軸29aと第2の軸29bと第3の軸29cと第4の軸29dとに沿って配置されたコンタクト35の列を有する。第1の軸29a及び第3の軸29cは互いに平行である。第2の軸29b及び第4の軸29dは第1の軸29a及び第3の軸29cに対し横向きである。

【選択図】図1A

**【特許請求の範囲】****【請求項 1】**

超小型電子パッケージであって、

対向する第1の表面及び第2の表面を有する基板と、

第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子であって、各超小型電子素子は、前記基板の前記第1の表面の方に向いた前面と、該前面における複数のコンタクトとを有し、該超小型電子素子の前記前面は、前記第1の表面に対して平行であるとともに前記第1の表面の上に重なる単一の平面内に配置され、各超小型電子素子は、前記前面に露出するとともにそれぞれの第1の軸、第2の軸、第3の軸、及び第4の軸に沿って配置されたコンタクトの列を有し、前記第1の軸及び前記第3の軸は互いに平行であり、前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して横向きである、第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子と、

前記第2の表面に露出した複数の端子であって、該端子は、該超小型電子パッケージの外部の少なくとも1つの構成要素に該超小型電子パッケージを接続するように構成されている、複数の端子と、

各超小型電子素子の前記コンタクトのうちの少なくとも幾つかから前記端子のうちの少なくとも幾つかに延在する電気的接続部と

を備えてなる、超小型電子パッケージ。

**【請求項 2】**

前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して直交している、請求項1に記載の超小型電子パッケージ。

**【請求項 3】**

各超小型電子素子の前記コンタクトの列は、前記それぞれの超小型電子素子の前記前面の中央領域に配置されている、請求項1に記載の超小型電子パッケージ。

**【請求項 4】**

前記端子は、エリアアレイに配置され、前記端子は、互いに同一平面上にある露出した接触面を有する、請求項1に記載の超小型電子パッケージ。

**【請求項 5】**

前記電気的接続部は、下側超小型電子素子のそれぞれのコンタクトと、前記基板の前記第1の表面に露出した導電性ボンドパッドとの間に延在するフリップチップ接続部を含む、請求項1に記載の超小型電子パッケージ。

**【請求項 6】**

各超小型電子素子の前記コンタクトは、8つのデータI/Oコンタクトを含む、請求項1に記載の超小型電子パッケージ。

**【請求項 7】**

各超小型電子素子の前記コンタクトは、9つのデータI/Oコンタクトを含む、請求項1に記載の超小型電子パッケージ。

**【請求項 8】**

各超小型電子素子の前記コンタクトは、16個のデータI/Oコンタクトを含む、請求項1に記載の超小型電子パッケージ。

**【請求項 9】**

請求項1に記載の超小型電子パッケージであって、該超小型電子パッケージにおいて、前記端子のうちの少なくとも幾つかと、前記超小型電子素子のうちの1つ以上のものとに電気的に接続されたバッファ素子を更に備え、該バッファ素子は、該超小型電子パッケージの前記端子のうちの1つ以上のものにおいて受信された少なくとも1つの信号を再生成するように構成されている、請求項1に記載の超小型電子パッケージ。

**【請求項 10】**

前記バッファ素子は、前記基板の前記第1の表面に実装される、請求項9に記載の超小型電子パッケージ。

10

20

30

40

50

**【請求項 1 1】**

前記バッファ素子は、前記基板の前記第2の表面に実装される、請求項9に記載の超小型電子パッケージ。

**【請求項 1 2】**

前記少なくとも1つの信号は、該超小型電子パッケージに転送されるアドレス信号の全てを含む、請求項9に記載の超小型電子パッケージ。

**【請求項 1 3】**

前記少なくとも1つの信号は、該超小型電子パッケージに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号の全てを含み、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックである、請求項9に記載の超小型電子パッケージ。

10

**【請求項 1 4】**

前記少なくとも1つの信号は、該超小型電子パッケージによって受信されたデータ信号の全てを含む、請求項9に記載の超小型電子パッケージ。

**【請求項 1 5】**

前記基板に実装されるとともに識別情報を記憶するように構成された不揮発性メモリ素子を更に備え、該不揮発性メモリ素子は、前記超小型電子素子のうちの1つ以上のものに電気的に接続されている、請求項1に記載の超小型電子パッケージ。

20

**【請求項 1 6】**

温度センサを更に備える、請求項1に記載の超小型電子パッケージ。

**【請求項 1 7】**

前記基板に実装されたデカップリングコンデンサ素子を更に備え、該デカップリングコンデンサ素子は、前記超小型電子素子のうちの1つ以上のものに電気的に接続されている、請求項1に記載の超小型電子パッケージ。

**【請求項 1 8】**

前記基板は、該基板の平面における熱膨張係数が12 ppm / 未満である材料から基本的になる要素である、請求項1に記載の超小型電子パッケージ。

**【請求項 1 9】**

前記基板は、該基板の平面における熱膨張係数が30 ppm / 未満である材料から基本的になる誘電体素子を備える、請求項1に記載の超小型電子パッケージ。

30

**【請求項 2 0】**

前記超小型電子素子は、アドレス指定可能メモリモジュールとともに機能するように構成され、該超小型電子パッケージは、前記超小型電子素子のそれぞれにおいて受信されたデータの一部を記憶するように構成されている、請求項1に記載の超小型電子パッケージ。

**【請求項 2 1】**

請求項20に記載の超小型電子パッケージであって、該超小型電子パッケージは、デュアルインラインメモリモジュールとして機能するように構成されている、請求項20に記載の超小型電子パッケージ。

40

**【請求項 2 2】**

請求項21に記載の超小型電子パッケージであって、該超小型電子パッケージは、同じコマンド及び信号インターフェースを有し、デュアルインラインメモリモジュールと同じ量のデータを転送するように構成されている、請求項21に記載の超小型電子パッケージ。

**【請求項 2 3】**

前記超小型電子素子のそれぞれは、主としてメモリ記憶アレイ機能を提供するように構成されている、請求項1に記載の超小型電子パッケージ。

**【請求項 2 4】**

前記超小型電子素子のそれぞれは、ダイナミックランダムアクセスメモリ(「DRAM」)集積回路チップを含む、請求項1に記載の超小型電子パッケージ。

50

**【請求項 2 5】**

前記超小型電子素子のそれぞれは、該超小型電子素子のうちの他のものと機能的及び機械的に同等である、請求項 1 に記載の超小型電子パッケージ。

**【請求項 2 6】**

前記超小型電子素子のうちの少なくとも 1 つと熱連通する放熱体を更に備える、請求項 1 に記載の超小型電子パッケージ。

**【請求項 2 7】**

前記放熱体は、前記超小型電子素子のそれぞれの背面の上に少なくとも部分的に重なる、請求項 2 6 に記載の超小型電子パッケージ。

**【請求項 2 8】**

各超小型電子素子は、下側超小型電子素子であり、各超小型電子パッケージは、各下側超小型電子素子に対応する上側超小型電子素子を備え、各上側超小型電子素子は、前記下側超小型電子素子のうちの前記対応するものの背面の上に少なくとも部分的に重なる表面を有する、請求項 1 に記載の超小型電子パッケージ。

**【請求項 2 9】**

前記上側超小型電子素子のうちの少なくとも 1 つは、前記下側超小型電子素子を貫通して延在する少なくとも 1 つの導電性ビアを通じて、前記下側超小型電子素子のうちの対応するものと電気的に接続されている、請求項 2 8 に記載の超小型電子パッケージ。

**【請求項 3 0】**

請求項 1 に記載の複数の超小型電子パッケージを備える超小型電子アセンブリであって、パネルコンタクトを有する回路パネルを更に備え、前記パッケージの前記端子は、前記パネルコンタクトにボンディングされる、請求項 1 に記載の複数の超小型電子パッケージを備える超小型電子アセンブリ。

**【請求項 3 1】**

前記回路パネルは、前記超小型電子パッケージのそれぞれに及びそれぞれから信号をトランスポートする共通の電気インターフェースを有する、請求項 3 0 に記載の超小型電子アセンブリ。

**【請求項 3 2】**

前記超小型電子パッケージのそれぞれは、デュアルオンラインメモリモジュールと同じ機能を有するように構成されている、請求項 3 0 に記載の超小型電子アセンブリ。

**【請求項 3 3】**

前記回路パネルはマザーボードである、請求項 3 0 に記載の超小型電子アセンブリ。

**【請求項 3 4】**

前記回路パネルは、マザーボードに取り付けられるように構成されたモジュールである、請求項 3 0 に記載の超小型電子アセンブリ。

**【請求項 3 5】**

前記回路パネルに実装されるとともに前記超小型電子パッケージのうちの少なくとも幾つかに電気的に接続されたバッファ素子を更に備え、該バッファ素子は、前記超小型電子パッケージの前記端子のうちの 1 つ以上のものにおいて受信された少なくとも 1 つの信号を再生成するように構成されている、請求項 3 0 に記載の超小型電子アセンブリ。

**【請求項 3 6】**

前記少なくとも 1 つの信号は、該超小型電子アセンブリに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号の全てを含み、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックである、請求項 3 5 に記載の超小型電子アセンブリ。

**【請求項 3 7】**

前記少なくとも 1 つの信号は、該超小型電子アセンブリによって受信されたデータ信号の全てを含む、請求項 3 5 に記載の超小型電子アセンブリ。

**【請求項 3 8】**

10

20

30

40

50

各超小型電子アセンブリは、該超小型電子アセンブリのそれぞれに及びそれぞれから信号をトランスポートする第2の回路パネルに電気的に結合されている、請求項30に記載の複数の超小型電子アセンブリを備えるモジュール。

【請求項39】

請求項1に記載の超小型電子パッケージと、該超小型電子パッケージに電気的に接続された1つ以上の他の電子構成要素とを備える、システム。

【請求項40】

ハウジングを更に備え、前記超小型電子パッケージ及び前記他の電子構成要素が該ハウジングに実装されている、請求項39に記載のシステム。

【請求項41】

超小型電子パッケージであって、

対向する第1の表面及び第2の表面を有する基板と、

第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子であって、各超小型電子素子は、前記基板の前記第1の表面の方に向いた前面と、該前面における複数のコンタクトとを有し、該超小型電子素子の前記前面は、前記第1の表面に対して平行であるとともに前記第1の表面の上に重なる単一の平面内に配置され、各超小型電子素子は、前記基板の前記第1の表面と前記第2の表面との間に延在する少なくとも1つの開口部の上に少なくとも部分的に重なり、各開口部は、それぞれの第1の軸、第2の軸、第3の軸、及び第4の軸に沿った長さを有し、前記第1の軸及び前記第3の軸は互いに平行であり、前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して横向きである、第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子と、

前記第2の表面に露出した複数の端子であって、該端子は、前記超小型電子パッケージを該超小型電子パッケージの外部の少なくとも1つの構成要素に接続するように構成されている、複数の端子と、

各超小型電子素子の前記コンタクトのうちの少なくとも幾つかから前記端子のうちの少なくとも幾つかに延在する電気的接続部であって、少なくとも、前記少なくとも1つの開口部と位置合わせされた部分を有するリードを含む、電気的接続部と

を備えてなる、超小型電子パッケージ。

【請求項42】

前記リードのうちの少なくとも幾つかは、前記開口部のうちの少なくとも1つを通って延在するワイヤボンドを含む、請求項41に記載の超小型電子パッケージ。

【請求項43】

前記リードの全てが、前記開口部のうちの少なくとも1つを通って延在するワイヤボンドである、請求項41に記載の超小型電子パッケージ。

【請求項44】

前記リードのうちの少なくとも幾つかは、リードボンドを含む、請求項41に記載の超小型電子パッケージ。

【請求項45】

各超小型電子素子の前記コンタクトのうちの前記少なくとも幾つかは、前記それぞれの超小型電子素子の前記前面の中央領域において列に配置される、請求項41に記載の超小型電子パッケージ。

【請求項46】

各超小型電子素子の前記コンタクトの列は、前記開口部のうちの対応するものと位置合わせされている、請求項45に記載の超小型電子パッケージ。

【請求項47】

前記開口部のそれぞれは、前記それぞれの軸に対して横向きの方向に幅を有し、各開口部の前記幅は、該開口部の前記幅と同じ方向において、該開口部の上に少なくとも部分的に重なる前記超小型電子素子の幅よりも大きくなき、請求項41に記載の超小型電子パッケージ。

10

20

30

40

50

**【請求項 4 8】**

前記基板の前記第2の表面は、その中央部分を占有する中央領域を有し、該中央領域は、前記第1の軸、前記第2の軸、前記第3の軸、及び前記第4の軸によって画定され、前記端子のうちの少なくとも幾つかは、前記中央領域に配置された第1の端子である、請求項4 1に記載の超小型電子パッケージ。

**【請求項 4 9】**

前記第1の端子は、該超小型電子パッケージに転送されるアドレス信号の全てを搬送するように構成されている、請求項4 8に記載の超小型電子パッケージ。

**【請求項 5 0】**

前記第1の端子は、該超小型電子パッケージに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号のうちの少なくとも幾つかを搬送するように構成され、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックであり、前記第1の端子は、前記超小型電子素子のうちの少なくとも2つによって共有される、請求項4 8に記載の超小型電子パッケージ。

10

**【請求項 5 1】**

前記第1の端子は、前記超小型電子素子のそれぞれによって共有される、請求項5 0に記載の超小型電子パッケージ。

**【請求項 5 2】**

請求項4 1に記載の超小型電子パッケージであって、該超小型電子パッケージにおいて、前記端子のうちの少なくとも幾つかと、前記超小型電子素子のうちの1つ以上のものとに電気的に接続されたバッファ素子を更に備え、該バッファ素子は、該超小型電子パッケージの前記端子のうちの1つ以上のものにおいて受信された少なくとも1つの信号を再生成するように構成されている、請求項4 1に記載の超小型電子パッケージ。

20

**【請求項 5 3】**

前記バッファ素子は、前記基板の前記第1の表面に実装される、請求項5 2に記載の超小型電子パッケージ。

**【請求項 5 4】**

前記バッファ素子は、前記基板の前記第2の表面に実装される、請求項5 2に記載の超小型電子パッケージ。

30

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本出願の主題は、超小型電子パッケージ及び超小型電子パッケージを組み込んだアセンブリに関する。

**【0 0 0 2】****[関連出願の相互参照]**

本出願は、2012年1月9日に出願された米国特許出願第13/346,201号の継続出願である。この米国特許出願は、全てが2011年10月3日に出願された米国仮特許出願第61/542,488号、第61/542,495号、及び第61/542,553号と、2011年7月12日に出願された米国仮特許出願第61/506,889号との出願日の利益を主張する。これらの米国仮特許出願の開示内容は、引用することによって本明細書の一部をなすものとする。

40

**【背景技術】****【0 0 0 3】**

半導体チップは、一般に、事前にパッケージされた個々のユニットとして提供される。標準的なチップは、平坦な方形の本体を有し、この本体は、チップの内部回路部に接続されたコンタクトを有する大きな前面を備えている。個々の各チップは、通常、チップのコンタクトに接続された外部端子を有するパッケージ内に含まれている。また、端子、すな

50

わちパッケージの外部接続点は、プリント回路基板等の回路パネルに電気的に接続するように構成されている。多くの従来の設計では、チップパッケージは、チップ自体の面積よりもかなり大きな回路パネルの面積を占有する。「チップの面積」とは、本明細書において、前面を有する平坦なチップに関して用いられるとき、前面の面積を指すものとして理解されるべきである。

#### 【0004】

「フリップチップ」設計では、チップの前面は、パッケージ誘電体素子、すなわち、パッケージの基板の面に向き合い、チップ上のコンタクトは、はんだバンプ又は他の接続素子によってこの基板の面上のコンタクトに直接ボンディングされる。また、この基板は、当該基板上に重なる外部端子を通じて回路パネルにボンディングすることができる。「フリップチップ」設計は、比較的コンパクトな構成を提供し、各パッケージは、例えば、本願と同一の譲受人に譲渡された米国特許第5,148,265号、同第5,148,266号、及び同第5,679,977号の或る特定の実施形態に開示されているように、チップの前面の面積に等しいか又はそれよりも僅かに大きな回路パネルの面積を占有する。これらの米国特許の開示内容は、引用することによって本明細書の一部をなすものとする。或る特定の革新的な実装技法が、従来のフリップチップボンディングのコンパクト性に匹敵するコンパクト性又はそれに等しいコンパクト性を提供する。チップ自体の面積に等しいか又はそれよりも僅かに大きな回路パネルの面積内に単一のチップを収容することができるパッケージは、一般に、「チップスケールパッケージ」と呼ばれる。

10

#### 【0005】

チップのいかなる物理的構成においても、サイズは重要な考慮事項である。チップのより小型の物理的構成に対する要求は、携帯型電子デバイスの急速な発展により、更に強くなっている。単に例として、一般に「スマートフォン」と呼ばれるデバイスは、携帯電話の機能を、強力なデータプロセッサ、メモリ、並びに全地球測位システム受信機、電子カメラ及びローカルエリアネットワーク接続等の補助デバイスと、高解像度ディスプレイ及び関連する画像処理チップとともに一体化している。このようなデバイスは、完全なインターネット接続、最大解像度の映像を含むエンターテイメント、ナビゲーション、電子銀行等の機能を、全てポケットサイズのデバイスで提供することができる。複雑な携帯型デバイスでは、多数のチップを小さい空間に詰め込む必要がある。さらに、チップのうちのいくつかは、一般に「I/O」と呼ばれる多くの入出力接続を有している。これらのI/Oを、他のチップのI/Oと相互接続しなければならない。相互接続を形成するコンポーネントは、アセンブリのサイズを大幅に増大させるべきではない。同様の必要性は、例えば、インターネット検索エンジンで使用されるもの等の、性能の増大及びサイズの低減が必要とされるデータサーバにおける用途等の、他の用途でも発生する。

20

30

#### 【0006】

メモリ記憶アレイ、特にダイナミックランダムアクセスメモリチップ(DRAM:dynamic random access memory chip)及びフラッシュメモリチップを含む半導体チップは、一般に、單一チップ又は複数チップのパッケージ及びアセンブリにパッケージされる。各パッケージは、端子と、その中のチップとの間で信号を搬送し、電源及び接地を接続するために数多くの電気的接続を有する。それらの電気的接続は、チップのコンタクト支持面に対して水平方向に延在する水平導体、例えば、トレース、ビームリード等、及びチップの表面に対して垂直方向に延在するビア等の垂直導体、並びにチップの表面に対して水平及び垂直の両方向に延在するワイヤボンド等の、異なる種類の導体を含みうる。

40

#### 【0007】

マルチチップパッケージ内で、そのパッケージの複数のチップに信号を送信することは、特に、メモリチップに対するクロック信号、アドレス信号及びストローブ信号等の、パッケージ内の2つ以上のチップに共通の信号の場合、課題をもたらす。そのようなマルチチップパッケージ内では、パッケージの端子とチップとの間の接続経路の長さが異なる可能性がある。経路長が異なると、信号が端子と各チップとの間を進行するのにかかる時間が長くなるか又は短くなる可能性がある。2点間の信号の進行時間は「伝搬遅延」と呼ば

50

れ、導体長、導体の構造、及びその導体に近接している他の誘電体又は導体構造の関数である。

#### 【0008】

2つの異なる信号が特定の場所に到着する時間差も「スキュー」と呼ぶことができる。2つ以上の場所において特定の信号の到着時間に生じるスキューは、伝搬遅延と、その特定の信号がそれらの場所に向かって進行し始める時刻との両方の結果である。スキューは回路性能に影響を与える場合も、与えない場合もある。同期している信号群内の全ての信号に一斉にスキューが生じているとき、その場合、動作のために必要とされる全ての信号が、必要なときに一緒に到着するので、スキューは多くの場合に性能にほとんど影響を及ぼさない。しかしながら、動作のために必要とされる同期している信号群の異なる信号が異なる時刻に到着するとき、これは当てはまらない。この場合、必要とされる全ての信号が到着しない限り、動作を実行することができないので、スキューは性能に影響を与える。本明細書において説明する実施形態は、同時係属中の米国仮特許出願第61/506,889号(TESSERA3.8-664)に開示されているスキューを最小にする特徴を含みうる。この米国仮特許出願の開示内容は、引用することによって本明細書の一部となすものとする。

#### 【0009】

従来の超小型電子パッケージは、メモリ記憶アレイ機能を主として提供するように構成された超小型電子素子、すなわち、メモリ記憶アレイ機能を提供する能動デバイスを他のいずれの機能よりも多く具現化する超小型電子素子を組み込むことができる。この超小型電子素子は、DRAMチップ、又はそのような半導体チップを積重して電気的に相互接続したアセンブリでありうるし、それらを含むこともある。通常、そのようなパッケージの端子の全ては、超小型電子素子が実装されるパッケージ基板の1つ以上の周縁部に隣接して数組の列に配置される。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

上記に鑑みると、電気的性能を改良するために、マルチチップ超小型電子パッケージ及びアセンブリに対して或る特定の改良を行うことができる。本発明のこれらの特質は、以下に説明するような超小型電子パッケージ及びアセンブリを構築することによって達成することができる。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様によれば、超小型電子パッケージが、対向する第1の表面及び第2の表面を有する基板と、第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子と、前記第2の表面に露出した複数の端子と、各超小型電子素子の前記コンタクトのうちの少なくとも幾つかから前記端子のうちの少なくとも幾つかに延在する電気的接続部とを備えることができる。各超小型電子素子は、前記基板の前記第1の表面の方に向いた前面と、該前面における複数のコンタクトとを有することができる。該超小型電子素子の前記前面は、前記第1の表面に対して平行であるとともに前記第1の表面の上に重なる単一の平面内に配置することができる。各超小型電子素子は、前記前面に露出するとともにそれぞれの第1の軸、第2の軸、第3の軸、及び第4の軸に沿って配置されたコンタクトの列を有することができる。前記第1の軸及び前記第3の軸は互いに平行とすることができます。前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して横向きとすることができます。前記端子は、該超小型電子パッケージの外部の少なくとも1つの構成要素に該超小型電子パッケージを接続するように構成することができる。

#### 【0012】

例示的な実施形態において、前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して直交することができる。特定の例において、各超小型電子素子の前記コ

ンタクトの列は、前記それぞれの超小型電子素子の前記前面の中央領域に配置することができる。一実施形態において、前記端子は、エリアアレイに配置することができる。前記端子は、互いに同一平面上にある露出した接触面を有することができる。特定の実施形態において、前記電気的接続部は、下側超小型電子素子のそれぞれのコンタクトと、前記基板の前記第1の表面に露出した導電性ボンドパッドとの間に延在するフリップチップ接続部を含みうる。一例において、各超小型電子素子の前記コンタクトは、8つのデータI/Oコンタクトを含みうる。特定の例において、各超小型電子素子の前記コンタクトは、9つのデータI/Oコンタクトを含みうる。例示的な実施形態において、各超小型電子素子の前記コンタクトは、16個のデータI/Oコンタクトを含みうる。

## 【0013】

10

一実施形態において、前記超小型電子パッケージは、該超小型電子パッケージにおいて、前記端子のうちの少なくとも幾つかと、前記超小型電子素子のうちの1つ以上のものとに電気的に接続されたバッファ素子も備えることができる。該バッファ素子は、該超小型電子パッケージの前記端子のうちの1つ以上のものにおいて受信された少なくとも1つの信号を再生成するように構成することができる。特定の実施形態において、前記バッファ素子は、前記基板の前記第1の表面に実装することができる。超小型電子パッケージ。一例において、前記バッファ素子は、前記基板の前記第2の表面に実装することができる。特定の例において、前記少なくとも1つの信号は、該超小型電子パッケージに転送されるアドレス信号の全てを含みうる。例示的な実施形態において、前記少なくとも1つの信号は、該超小型電子パッケージに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号の全てを含むことがあり、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックである。特定の実施形態において、前記少なくとも1つの信号は、該超小型電子パッケージによって受信されたデータ信号の全てを含みうる。

20

## 【0014】

一例において、前記基板に実装されるとともに識別情報を記憶するように構成された不揮発性メモリ素子も備えることができる。該不揮発性メモリ素子は、前記超小型電子素子のうちの1つ以上のものに電気的に接続することができる。特定の例において、前記超小型電子パッケージは温度センサも備えることができる。例示的な実施形態において、前記超小型電子パッケージは、前記基板に実装されたデカップリングコンデンサ素子も備えることができる。該デカップリングコンデンサ素子は、前記超小型電子素子のうちの1つ以上のものに電気的に接続することができる。一実施形態において、前記基板は、該基板の平面におけるCTEが12 ppm / 未満である材料から基本的になる要素とすることができます。一例において、前記基板は、該基板の平面におけるCTEが30 ppm / 未満である材料から基本的になる誘電体素子を備えることができる。

30

## 【0015】

特定の実施形態において、前記超小型電子素子は、アドレス指定可能メモリモジュールとしてともに機能するように構成することができる。該超小型電子パッケージは、前記超小型電子素子のそれぞれにおいて受信されたデータの一部を記憶するように構成することができる。一例において、該超小型電子パッケージは、デュアルインラインメモリモジュールとして機能することができる。例示的な実施形態において、該超小型電子パッケージは、同じコマンド及び信号インターフェースを有することができ、デュアルインラインメモリモジュールと同じ量のデータを転送するように構成することができる。特定の例において、前記超小型電子素子のそれぞれは、主としてメモリ記憶アレイ機能を提供するように構成することができる。一実施形態において、前記超小型電子素子のそれぞれは、ダイナミックランダムアクセスメモリ(「DRAM」)集積回路チップを含みうる。特定の実施形態において、前記超小型電子素子のそれぞれは、該超小型電子素子のうちの他のものと機能的及び機械的に同等とすることができます。

40

## 【0016】

50

例示的な実施形態において、前記超小型電子素子のうちの少なくとも1つと熱連通する放熱体も備えることができる。一例において、前記放熱体は、前記超小型電子素子のそれぞれの背面の上に少なくとも部分的に重なることができる。特定の実施形態において、各超小型電子素子は、下側超小型電子素子とすることができる、各超小型電子パッケージは、各下側超小型電子素子の対応する上側超小型電子素子を備えることができる。各上側超小型電子素子は、前記下側超小型電子素子のうちの前記対応するものの背面の上に少なくとも部分的に重なる表面を有することができる。一実施形態において、前記上側超小型電子素子のうちの少なくとも1つは、前記下側超小型電子素子を貫通して延在する少なくとも1つの導電性ピアを通じて、前記下側超小型電子素子のうちの対応するものと電気的に接続することができる。

10

## 【0017】

本発明の一態様によれば、超小型電子アセンブリが、上記で説明したような複数の超小型電子パッケージを含みうる。該超小型電子アセンブリは、パネルコンタクトを有する回路パネルも備えることができる。前記パッケージの前記端子は、前記パネルコンタクトにボンディングすることができる。一例において、前記回路パネルは、前記超小型電子パッケージのそれぞれに及びそれぞれから信号をトランスポートする共通の電気インタフェースを有することができる。特定の実施形態において、前記超小型電子パッケージのそれぞれは、デュアルインラインメモリモジュールと同じ機能を有するように構成することができる。例示的な実施形態において、前記回路パネルはマザーボードでありうる。一実施形態において、前記回路パネルは、マザーボードに取り付けられるように構成されたモジュールでありうる。

20

## 【0018】

特定の例において、前記超小型電子アセンブリは、前記回路パネルに実装されるとともに前記超小型電子パッケージのうちの少なくとも幾つかに電気的に接続されたバッファ素子も備えることができる。該バッファ素子は、前記超小型電子パッケージの前記端子のうちの1つ以上のものにおいて受信された少なくとも1つの信号を再生成するように構成することができる。特定の例において、前記少なくとも1つの信号は、該超小型電子アセンブリによって受信されたアドレス信号の全てを含みうる。一実施形態において、前記少なくとも1つの信号は、該超小型電子アセンブリに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号の全てを含むことがあり、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックである。例示的な実施形態において、前記少なくとも1つの信号は、該超小型電子アセンブリによって受信されたデータ信号の全てを含みうる。

30

## 【0019】

本発明の一態様によれば、モジュールが、上記で説明したような複数の超小型電子アセンブリを含みうる。各超小型電子アセンブリは、該超小型電子アセンブリのそれぞれに及びそれぞれから信号をトランスポートする第2の回路パネルに電気的に結合することができる。本発明の更なる態様は、本発明の上記態様による超小型電子アセンブリ、本発明の上記態様による複合チップ、又は双方を、それらに電気的に接続された他の電子構成要素とともに組み込んだシステムを提供することができる。例えば、このシステムは、ポータブルハウジングとすることができる単一のハウジングに配置及び/又は実装することができる。本発明のこの態様における好ましい実施形態によるシステムは、比較可能な従来のシステムよりもコンパクトにすることができる。

40

## 【0020】

本発明の別の態様によれば、超小型電子パッケージが、対向する第1の表面及び第2の表面を有する基板と、第1の超小型電子素子、第2の超小型電子素子、第3の超小型電子素子、及び第4の超小型電子素子と、前記第2の表面に露出した複数の端子と、各超小型電子素子の前記コンタクトのうちの少なくとも幾つかから前記端子のうちの少なくとも幾つかに延在する電気的接続部とを備えることができる。各超小型電子素子は、前記基板の

50

前記第1の表面の方に向いた前面と、該前面における複数のコンタクトとを有することができる。該超小型電子素子の前記前面は、前記第1の表面に対して平行であるとともに前記第1の表面の上に重なる単一の平面内に配置することができる。各超小型電子素子は、前記基板の前記第1の表面と前記第2の表面との間に延在する少なくとも1つの開口部の上に少なくとも部分的に重なることができる。各開口部は、それぞれの第1の軸、第2の軸、第3の軸、及び第4の軸に沿った長さを有することができる。前記第1の軸及び前記第3の軸は互いに平行とすることができる。前記第2の軸及び前記第4の軸は、前記第1の軸及び前記第3の軸に対して横向きとすることができる。前記端子は、前記超小型電子パッケージを該超小型電子パッケージの外部の少なくとも1つの構成要素に接続するよう構成することができる。前記電気的接続部は、少なくとも、前記少なくとも1つの開口部と位置合わせされた部分を有するリードを含みうる。

10

#### 【0021】

1つの例において、前記リードのうちの少なくとも幾つかは、前記開口部のうちの少なくとも1つを通って延在するワイヤボンドを含みうる。特定の実施形態において、前記リードの全てが、前記開口部のうちの少なくとも1つを通って延在するワイヤボンドであることができる。例示的な実施形態において、前記リードのうちの少なくとも幾つかは、リードボンドを含みうる。一実施形態において、各超小型電子素子の前記コンタクトのうちの前記少なくとも幾つかは、前記それぞれの超小型電子素子の前記前面の中央領域において列に配置することができる。特定の例において、各超小型電子素子の前記コンタクトの列は、前記開口部のうちの対応するものと位置合わせすることができる。一例において、前記開口部のそれは、前記それぞれの軸に対して横向きの方向に幅を有することができ、各開口部の前記幅は、該開口部の前記幅と同じ方向において、該開口部の上に少なくとも部分的に重なる前記超小型電子素子の幅よりも大きくない。一実施形態において、前記基板の前記第2の表面は、その中央部分を占有する中央領域を有することができる。該中央領域は、前記第1の軸、前記第2の軸、前記第3の軸、及び前記第4の軸によって画定することができる。前記端子のうちの少なくとも幾つかは、前記中央領域に配置された第1の端子でありうる。

20

#### 【0022】

一例において、前記第1の端子は、該超小型電子パッケージに転送されるアドレス信号の全てを搬送するように構成することができる。特定の例において、前記第1の端子は、該超小型電子パッケージに転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号のうちの少なくとも幾つかを搬送するように構成することができ、前記コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、前記クロック信号は、前記アドレス信号をサンプリングするのに用いられるサンプリングクロックであり、前記第1の端子は、前記超小型電子素子のうちの少なくとも2つによって共有される。一実施形態において、前記第1の端子は、前記超小型電子素子のそれによつて共有することができる。

30

#### 【0023】

例示的な実施形態において、前記超小型電子パッケージは、該超小型電子パッケージにおいて、前記端子のうちの少なくとも幾つかと、前記超小型電子素子のうちの1つ以上のものとに電気的に接続されたバッファ素子も備えることができる。該バッファ素子は、該超小型電子パッケージの前記端子のうちの1つ以上のものにおいて受信された少なくとも1つの信号を再生成するように構成することができる。特定の例において、前記バッファ素子は、前記基板の前記第1の表面に実装することができる。一実施形態において、前記バッファ素子は、前記基板の前記第2の表面に実装することができる。

40

#### 【図面の簡単な説明】

#### 【0024】

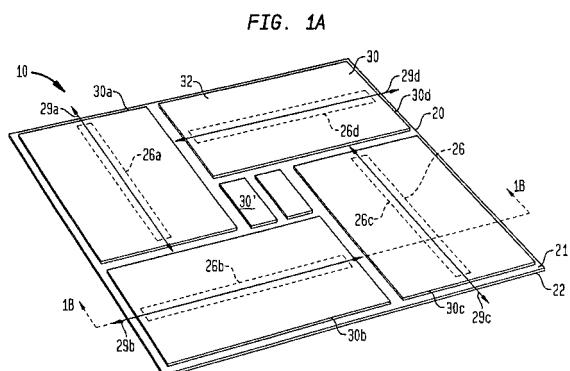

【図1A】本発明の一実施形態による超小型電子パッケージの概略斜視図である。

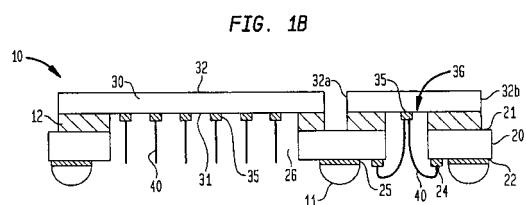

【図1B】図1Aの1B-1Bの線に沿って取られた図1Aの超小型電子パッケージの側断面図である。

50

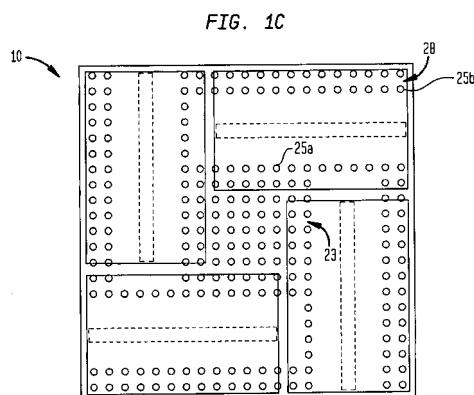

【図 1 C】超小型電子素子のロケーションを示す、図 1 A の超小型電子パッケージの底面図である。

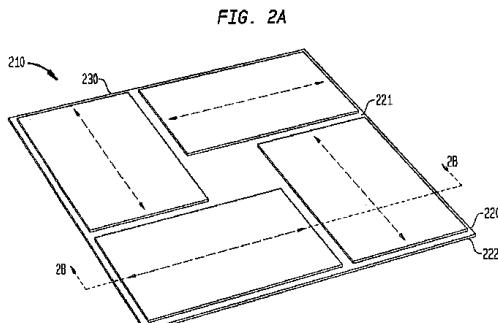

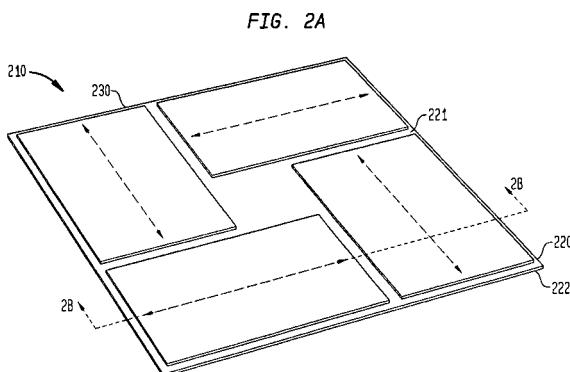

【図 2 A】基板に実装された超小型電子素子フリップチップを有する別の実施形態による超小型電子パッケージの概略斜視図である。

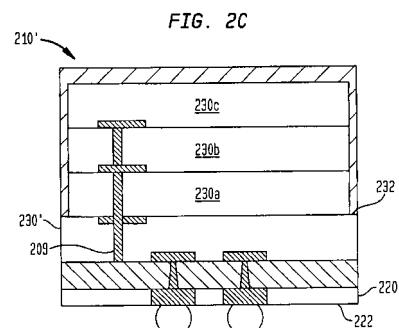

【図 2 B】図 2 A の 2 B - 2 B の線に沿って取られた図 2 A の超小型電子パッケージの側断面図である。

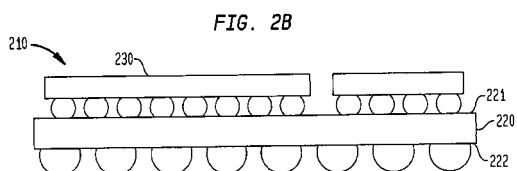

【図 2 C】対応する下側超小型電子素子の上に少なくとも部分的に重なっている 1 つ以上のものの上側超小型電子素子を有する、図 2 A の超小型電子パッケージの変形形態の側断面図である。

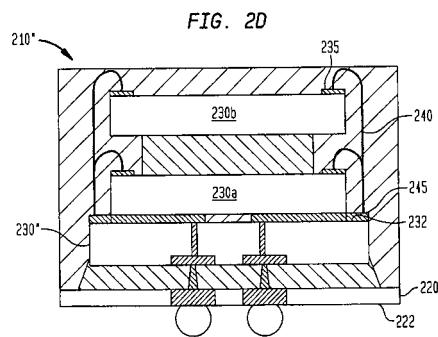

【図 2 D】対応する下側超小型電子素子の上に少なくとも部分的に重なっている 1 つ以上のものの上側超小型電子素子を有する、図 2 A の超小型電子パッケージの変形形態の側断面図である。 10

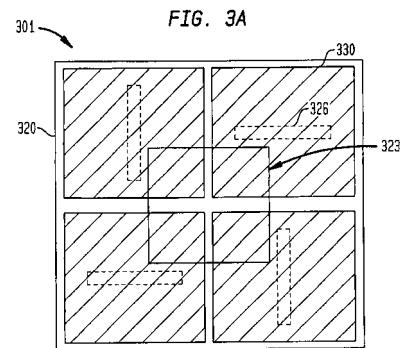

【図 3 A】ボンド窓及び中央領域のロケーションを示す、更なる実施形態による 4 つの超小型電子素子を有する超小型電子パッケージの上面図である。

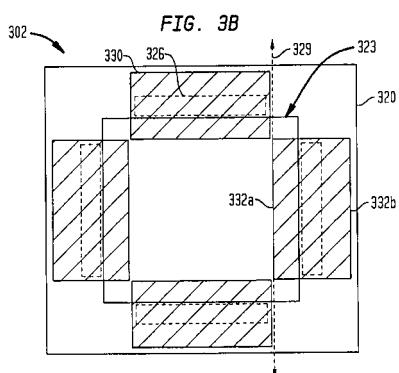

【図 3 B】ボンド窓及び中央領域のロケーションを示す、更なる実施形態による 4 つの超小型電子素子を有する超小型電子パッケージの上面図である。

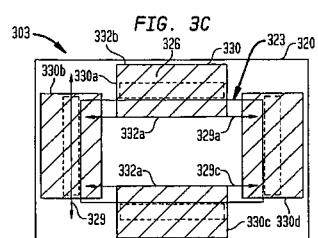

【図 3 C】ボンド窓及び中央領域のロケーションを示す、更なる実施形態による 4 つの超小型電子素子を有する超小型電子パッケージの上面図である。

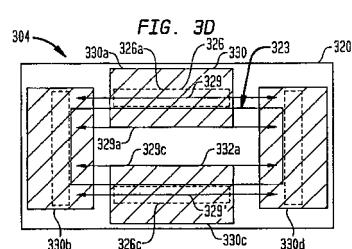

【図 3 D】ボンド窓及び中央領域のロケーションを示す、更なる実施形態による 4 つの超小型電子素子を有する超小型電子パッケージの上面図である。 20

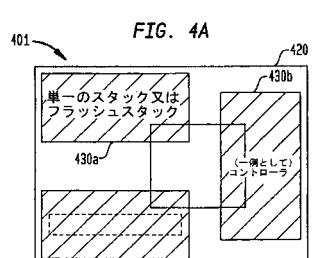

【図 4 A】ボンド窓及び中央領域のロケーションを示す、別の更なる実施形態による 3 つの超小型電子素子を有する超小型電子パッケージの上面図である。

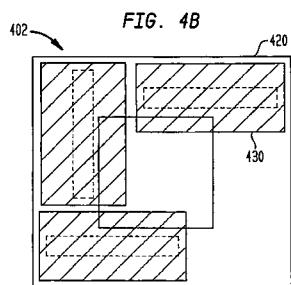

【図 4 B】ボンド窓及び中央領域のロケーションを示す、別の更なる実施形態による 3 つの超小型電子素子を有する超小型電子パッケージの上面図である。

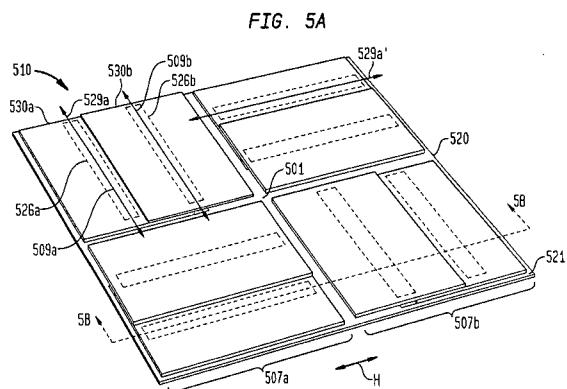

【図 5 A】積重された超小型電子素子を有する更に別の実施形態による超小型電子パッケージの概略斜視図である。 30

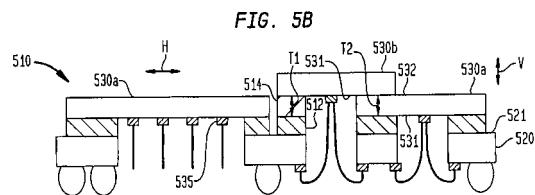

【図 5 B】図 5 A の 5 B - 5 B の線に沿って取られた、図 5 A の超小型電子パッケージの側断面図である。

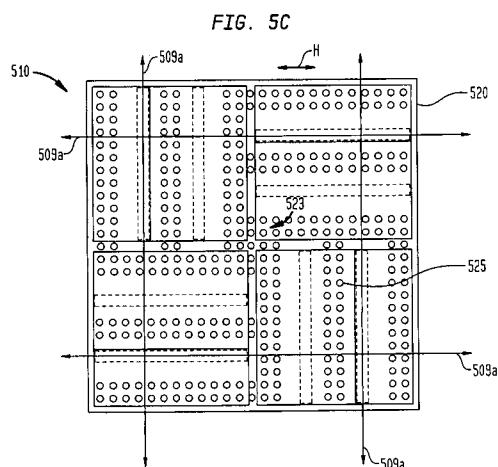

【図 5 C】超小型電子素子のロケーションを示す、図 5 A の超小型電子パッケージの底面図である。

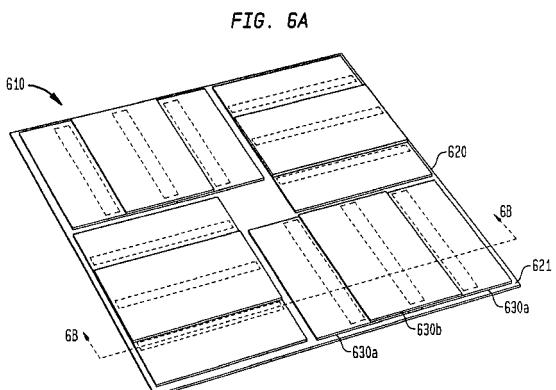

【図 6 A】積重された超小型電子素子を有する更に別の実施形態による超小型電子パッケージの概略斜視図である。 30

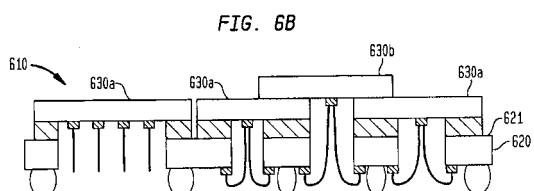

【図 6 B】図 6 A の 6 B - 6 B の線に沿って取られた、図 6 A の超小型電子パッケージの側断面図である。

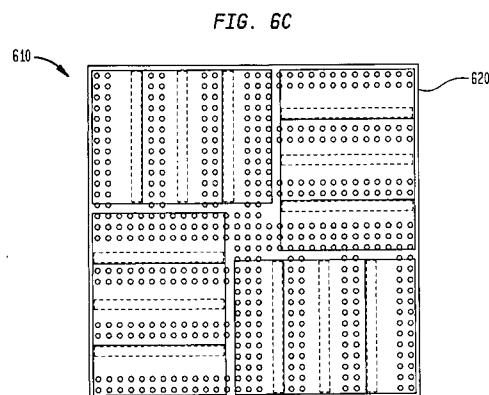

【図 6 C】超小型電子素子のロケーションを示す、図 6 A の超小型電子パッケージの底面図である。

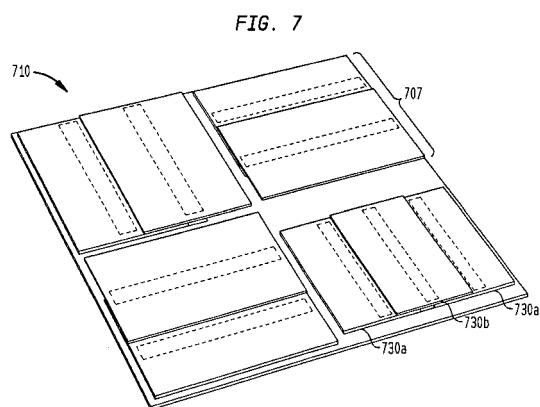

【図 7】積重された超小型電子素子を有する更に別の実施形態による超小型電子パッケージの概略斜視図である。

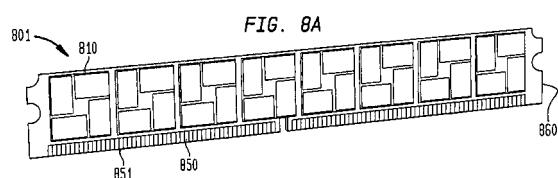

【図 8 A】回路パネルに実装された複数の超小型電子パッケージを有する超小型電子アセンブリの概略斜視図である。 40

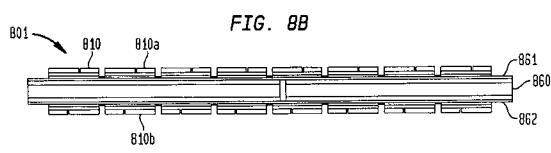

【図 8 B】図 8 A の超小型電子アセンブリの底面図である。

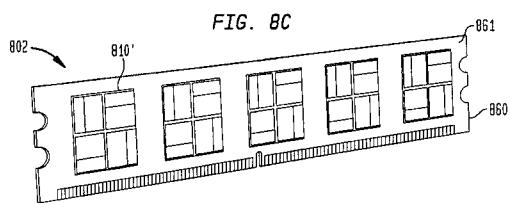

【図 8 C】回路パネルに実装された複数の超小型電子パッケージを有する更なる実施形態による超小型電子アセンブリの概略斜視図である。

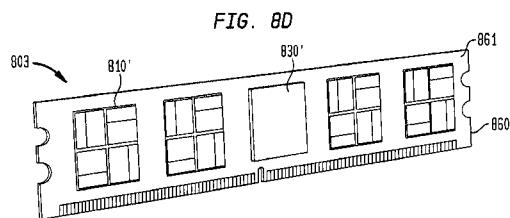

【図 8 D】回路パネルに実装された複数の超小型電子パッケージを有する更なる実施形態による超小型電子アセンブリの概略斜視図である。

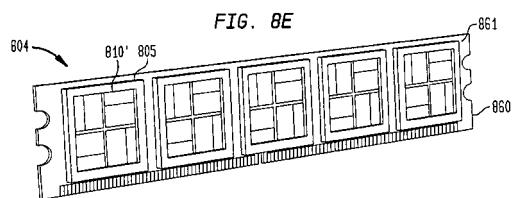

【図 8 E】回路パネルに実装された複数の超小型電子パッケージを有する更なる実施形態による超小型電子アセンブリの概略斜視図である。

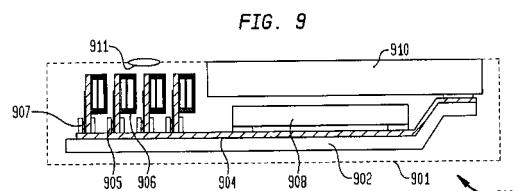

【図 9】複数のモジュールを備える一実施形態によるシステムの概略図である。

【発明を実施するための形態】

【0025】

10

20

30

40

50

本発明の或る特定の実施形態は、超小型電子素子、例えば、半導体チップ、又は半導体チップを積重配置したものが、メモリ記憶アレイ機能を主として提供するように構成されているパッケージ又は超小型電子アセンブリを提供する。そのような超小型電子素子では、メモリ記憶アレイ機能を提供するように構成された、すなわち、そのように構築されて他のデバイスと相互接続された、その素子内の能動デバイス、例えばトランジスタの数は、他のいずれかの機能を提供するように構成された能動デバイスの数よりも多い。したがって、一例では、DRAMチップ等の超小型電子素子は、その主要な又は唯一の機能としてメモリ記憶アレイ機能を有することができる。代替的に、別の例では、そのような超小型電子素子は、混合用途を有することができ、メモリ記憶アレイ機能を提供するように構成された能動デバイスを組み込むことができるとともに、プロセッサ機能、すなわち、数ある中でも信号プロセッサ機能又はグラフィックスプロセッサ機能等の別の機能を提供するように構成された他の能動デバイスも組み込むことができる。この場合も、超小型電子素子は、依然として、メモリ記憶アレイ機能を提供するように構成された能動デバイスを、超小型電子素子の他のいずれの機能よりも多く有することができる。

10

## 【0026】

本明細書における本発明の実施形態は、その中に2つ以上の半導体チップ、すなわち、超小型電子素子を有するパッケージを提供する。多チップパッケージは、その中にあるチップを、数ある中でも、ボールグリッドアレイ、ランドグリッドアレイ又はピングリッドアレイ等の端子のアレイを通してそのパッケージが電気的に、かつ機械的に接続される場合がある回路パネル、例えば、プリント配線板に接続するのに必要とされる面積及び空間の量を削減することができる。そのような接続空間は、小型又はポータブル計算デバイス、例えば、通常パーソナルコンピュータの機能と広範な世界への無線接続性とを併せ持つ「スマートフォン」又はタブレット等のハンドヘルドデバイスでは特に制限される。マルチチップパッケージは、高度な高性能ダイナミックランダムアクセスメモリ(「DRAM」)チップ、例えば、DDR3タイプDRAMチップ及びその後続製品等の、大量の相対的に安価なメモリをシステムが利用できるようにするために特に役に立つ可能性がある。

20

## 【0027】

マルチチップパッケージを接続するのに必要とされる回路パネルの面積の量は、パッケージ内の2つ以上のチップに至る途中に、少なくとも幾つかの信号がその中を通って進行する共通端子をパッケージ上に設けることによって削減することができる。しかしながら、高性能動作をサポートしながら、それを果たすには課題がある。無終端スタブに起因した信号の望ましくない反射等の望ましくない影響を回避するには、パッケージの外面にある端子を回路パネル上のグローバル配線と電気的に接続する回路パネル上のトレース、ビア、及び他の導体は長すぎてはならない。放熱も、高度なチップにとって課題を提示し、そのため、各チップの大きな平坦面のうちの少なくとも1つは、放熱体に結合されるか、又は設置されたシステム内の空気の流れに暴露されるか若しくは熱連通していることが望ましい。以下に説明するパッケージは、これらの更なる目標に役立つことがある。

30

## 【0028】

図1A～図1Cは、本発明の一実施形態による特定のタイプの超小型電子パッケージ10を示している。図1A～図1Cに見られるように、超小型電子パッケージ10は、パッケージ構造、例えば、対向する第1の表面21及び第2の表面22を有する基板20を備えることができる。場合によっては、基板20は、(基板の第1の表面21に対して平行な方向の)基板の平面において低い熱膨張係数(「CTE( : coefficient of thermal expansion)」)、すなわち、12パーツパーセント/摂氏温度(以下、「ppm/」)未満のCTEを有する材料から基本的になることができ、半導体材料、例えばシリコン、又はセラミック材料若しくは二酸化シリコン、例えばガラス等の誘電体材料等から基本的になることができる。代替的に、基板20は、シート状基板を含むことがあり、このシート状基板は、ポリイミド、エポキシ樹脂、熱可塑性物質、熱硬化プラスチック等の高分子材料、又は他の適した高分子材料から基本的になることもあるか、又は数ある中でもBTF樹脂(ビスマレイミドトリアジン)のガラス強化構造又はFR4等のエポキシ樹脂ガラ

40

50

ス等の合成高分子無機材料を含むか又はそれらの材料から基本的になる。一例では、そのような基板 20 は、基板の平面、すなわちその表面に沿った方向において 30 ppm / 未満の CTE を有する材料から基本的になることがある。

#### 【0029】

図 1A ~ 図 1C において、基板 20 の第 1 の表面 21 に対して平行な方向は、本明細書では「水平」方向又は「横」方向と呼ばれるのに対して、第 1 の表面に対して垂直な方向は、本明細書では、上向き方向又は下向き方向と呼ばれ、本明細書では、「垂直」方向とも呼ばれる。本明細書で言及するこれらの方向は、言及する構造の基準系におけるものである。したがって、これらの方向は、重力基準系における通常の「上」方向又は「下」方向に対して任意の向きとなりうる。

10

#### 【0030】

1 つの特徴部が別の特徴部よりも「表面の上方において」高い高さに配置されているという記述は、その 1 つの特徴部が表面から同じ直交方向においてその別の特徴部よりも大きく離れた距離にあることを意味する。逆に、1 つの特徴部が別の特徴部よりも「表面の上方において」低い高さに配置されているという記述は、その 1 つの特徴部が表面から同じ直交方向においてその別の特徴部よりも小さく離れた距離にあることを意味する。

#### 【0031】

少なくとも 1 つの開口部 26 が、基板 20 の第 1 の表面 21 と第 2 の表面 22 との間に延在することができる。図 1A に見て取ることができるように、基板 20 は、当該基板を貫通して延在する 4 つの開口部 26 を有することができる。基板 20 は、当該基板上に複数の端子 25、例えば、導電性パッド、ランド、又は導電性ポスト若しくは導電性ピンを有することができる。そのような端子 25 は、基板 20 の第 2 の表面 22 に露出することができる。端子 25 は、超小型電子パッケージ 10 と外部の構成要素の対応する導電性素子との接続用の端点として機能することができる。この外部の構成要素は、特に、回路パネル、例えば、プリント配線板、フレキシブル回路パネル、ソケット、他の超小型電子アセンブリ若しくはパッケージ、インタポーラ、又は受動構成要素アセンブリ（例えば、図 8A に示す回路パネル）等である。一例では、そのような回路パネルは、マザーボード又はDIMM モジュールボードとすることができます。特定の実施形態では、端子は、数ある中でも、ボールグリッドアレイ（BGA : ball-grid array）（以下に説明するような接合素子 11 を備える）、ランドグリッドアレイ（LGA : land-grid array）、又はピングリッドアレイ（PGA : pin-grid array）等のエリアアレイに配置することができる。一実施形態では、端子 25 は、基板 20 の第 2 の表面 22 の周辺部に沿って配置することができる。

20

#### 【0032】

一例示の実施形態では、端子 25 は、銅、銅合金、金、ニッケル等の導電性材料から作製された実質的に剛性のポストを含みうる。端子 25 は、例えば、レジストマスクにおける開口内に導電性材料をめっきすることによって、又は例えば、銅、銅合金、ニッケル、若しくはそれらの組み合わせから作製されたポストを形成することによって形成することができる。そのようなポストは、例えば、金属シート又は他の金属構造体を基板 20 から離れる方向に延在するポストにサブトラクティブパターンングすることによって、超小型電子パッケージ 10 を例えば以下に説明する回路パネル 860 等の外部の構成要素と電気的に相互接続する端子として形成することができる。端子 25 は、例えば、米国特許第 6,177,636 号に記載されているような他の構成を有する実質的に剛性のポストとすることができる。この米国特許の開示内容は、引用することによって本明細書の一部をなすものとする。一例では、端子 25 は、互いに同一平面上の露出した接触面を有することができる。

30

#### 【0033】

超小型電子パッケージ 10 は、外部の構成要素との接続用の端子 25 に取り付けられた接合素子 11 を備えることができる。この接合素子 11 は、例えば、はんだ、スズ、インジウム、共晶組成、若しくはそれらの組み合わせ等のボンドメタル又は導電性ペースト若

40

50

しくは導電性接着剤等の別の接合材料の塊とすることができる。特定の実施形態では、端子 25 と外部の構成要素（例えば、図 8A に示す回路パネル 860）のコンタクトとの間の接合部は、所有者が共通する米国特許出願第 13/155,719 号及び第 13/158,797 号に記載されているような導電性マトリックス材を含みうる。これらの米国特許出願の開示内容は、引用することによって本明細書の一部をなすものとする。特定の実施形態では、これらの接合部は、これらの米国特許出願に記載されているものと同様の構造を有することもできるし、これらの米国特許出願に記載されているような方法で形成することもできる。

#### 【0034】

導電性素子が構造体の表面「に露出する」という記述は、本明細書において用いられるとき、その導電性素子が、表面に対して垂直な方向に、構造体の外側からその表面に向かって移動する理論的な点との接触に利用可能であることを示す。したがって、構造体の表面に露出する端子又は他の導電性素子は、そのような表面から突出することもできるし、そのような表面と同一平面をなすことともできるし、そのような表面に対して陥凹して、構造体内の孔又は窪みを通じて露出することもできる。

10

#### 【0035】

端子 25 は、基板 20 の第 2 の表面 22 の中央領域 23 に露出する第 1 の端子 25a と、中央領域の外側にある第 2 の表面の周辺領域 28 に露出する第 2 の端子 25b を含みうる。図 1A ~ 図 1C に示す配置は、或る超小型電子素子が他のいずれの超小型電子素子の上にも重なる必要なく、超小型電子素子 30 のコンパクトな配置と、比較的広範囲の中央領域 23 とを提供することができる。

20

#### 【0036】

第 1 の端子 25a は、外部の構成要素から超小型電子パッケージ 10 に転送されるコマンド信号、アドレス信号、バンクアドレス信号、及びクロック信号の全てを搬送するように構成することができる。例えばダイナミックランダムアクセスメモリ（「DRAM」）用のダイナミックメモリ記憶アレイを備える超小型電子素子では、そのような超小型電子素子がダイナミックランダムアクセスメモリ記憶デバイスであるとき、例えば、コマンド信号は、超小型電子パッケージ 10 内の超小型電子素子によって用いられる書き込みインエーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号である。オンダイ終端（ODT：on die termination）、チップセレクト、クロックイネーブル等の他の信号は、第 1 の端子 25a によって搬送する必要があるコマンド信号の一部ではない。

30

#### 【0037】

クロック信号は、アドレス信号をサンプリングするのに用いられるサンプリングクロックとすることができます。第 2 の端子 25b のうちの少なくとも幾つかは、第 1 の端子 25a によって搬送されるコマンド信号、アドレス信号、及びクロック信号以外の信号を搬送するように構成することができる。チップセレクト、リセット、電源電圧、例えば Vdd、Vddq、並びに接地、例えば Vss 及び Vssq 等の信号又は基準電位は、第 2 の端子 25b によって搬送することができる。これらの信号又は基準電位のいずれも、第 1 の端子 25a によって搬送する必要はない。

30

#### 【0038】

図 1C に示す例等の特定の例では、第 2 の端子 25b は、各周辺領域 28 において少なくとも 1 つの列に配置することができる。一実施形態では、コマンド信号、アドレス信号、及びクロック信号以外の信号を搬送するように構成された第 2 の端子 25b のうちの少なくとも幾つかは、基板 20 の第 2 の表面 22 の中央領域 23 に露出することができる。

40

#### 【0039】

超小型電子パッケージ 10 は、それぞれが基板 20 の第 1 の表面 21 の方に向いた前面 31 を有する複数の超小型電子素子 30 も備えることができる。一例では、超小型電子素子 30 のそれぞれは、それぞれがダイナミックランダムアクセスメモリ（「DRAM」）記憶アレイ等のメモリ記憶素子又は主として DRAM 記憶アレイ（例えば、DRAM 集積回路チップ）として機能するように構成された記憶素子を組み込んだベアチップ又は超小

50

型電子ユニットとすることができます。「メモリ記憶素子」とは、本明細書において用いられるとき、電気インターフェースを介してデータをトランスポート等するように、データを記憶及び検索するのに使用可能な回路部とともにアレイに配置された多数のメモリセルを指す。特定の例では、シングルインラインメモリモジュール（「S I M M（:single in-line memory module）」）又はデュアルインラインメモリモジュール（「D I M M（:dual in-line memory module）」）に超小型電子パッケージ10を含めることができる。

#### 【0040】

特定の例では、メモリ記憶素子を備える超小型電子素子30は、少なくともメモリ記憶アレイ機能を有することができるが、この超小型電子素子は、フル機能メモリチップでない場合がある。そのような超小型電子素子は、それ自体バッファリング機能を有しない場合があるが、超小型電子素子のスタック内の他の超小型電子素子に電気的に接続される場合があり、そのスタック内の少なくとも1つの超小型電子素子が、バッファリング機能を有する（バッファリング超小型電子素子は、バッファチップ、フル機能メモリチップ、又はコントローラチップでありうる）。

10

#### 【0041】

他の例では、本明細書において説明するパッケージの任意のものにおける超小型電子素子のうちの1つ以上のものが、例えば、フラッシュメモリ、D R A M又は他のタイプのメモリのような他のいずれの機能よりも多くの数のメモリ記憶アレイ機能を提供する能動デバイスを具現化することができ、別の超小型電子素子又は主として論理機能を提供するよう構成された「論理チップ」とともにパッケージ内に配置することができる。特定の実施形態では、論理チップは、マイクロプロセッサ又は他の汎用計算素子等の、プログラマブル又はプロセッサ素子でありうる。その論理チップは、マイクロコントローラ素子、グラフィックスプロセッサ、浮動小数点プロセッサ、コプロセッサ、デジタルシグナルプロセッサ等でありうる。特定の実施形態では、論理チップは、ハードウェア状態機械機能を主に実行することができるか、又は特定の機能若しくは目的を果たすように別の方法でハードコード化することができる。代替的には、論理チップは、特定用途向け集積回路（「A S I C：application specific integrated circuit」）又はフィールドプログラマブルゲートアレイ（「F P G A：field programmable gate array」）チップとすることができます。そして、そのような変形形態では、パッケージは「システムインパッケージ」（「S I P：system in a package」）でありうる。

20

#### 【0042】

別の変形形態では、本明細書において説明されるパッケージのうちの任意のものにおける超小型電子素子は、同じ超小型電子素子内に共に埋め込まれた1つ以上の関連するメモリ記憶アレイを有するプログラマブルプロセッサ等の、その中に埋め込まれた論理機能及びメモリ機能を併せ持つことができる。そのような超小型電子素子は、プロセッサ等の論理機能が、メモリ記憶アレイ、又は特殊化した機能の場合がある幾つかの他の機能を実行する回路等の他の回路とともに埋め込まれるという点で、「システムオンチップ」（「S O C：system-on-a-chip」）と呼ばれる場合もある。

30

#### 【0043】

特定の例では、超小型電子素子30のそれぞれは、超小型電子素子の他のものと機能的及び機械的に同等とすることができます。そのため、各超小型電子素子は、同じ機能を有する同じパターンの導電性コンタクト35を前面31に有することができる。ただし、各超小型電子素子の長さ、幅、及び高さの特定の寸法は、他の超小型電子素子のものと異なることができる。

40

#### 【0044】

各超小型電子素子30は、その前面31に露出する複数の導電性コンタクト35を有することができる。各超小型電子素子30のコンタクト35は、前面のエリアの中央部分を占有する前面31の中央領域36に配置される1つ以上の列に配置することができる。中央領域36は、例えば、超小型電子素子30の対向する周縁部32a、32b間の最短距離の中央3分の1を含む前面31のエリアを占有することができる。各超小型電子素子3

50

0の前面31は、周縁部32aに隣接する第1の周辺領域と、もう1つの周縁部32bに隣接する第2の周辺領域と、第1の周辺領域と第2の周辺領域との間に配置された中央領域36とを有すると考えることができる。図1Bに示すように、各超小型電子素子30のコンタクト35は、開口部26のうちの少なくとも1つと位置を合わせることができる。

#### 【0045】

超小型電子素子の表面又は面、例えば、超小型電子素子30の前面31の中央領域36は、本明細書において用いられるとき、表面の第1の周辺領域と第2の周辺領域との間に配置される表面の部分を意味する。これらの周辺領域は、超小型電子素子の対向するそれぞれの第1の周縁部及び第2の周縁部（例えば、超小型電子素子30の対向する周縁部32a、32b）に隣接して配置される。第1の周辺領域及び第2の周辺領域並びに中央領域のそれぞれは、等しい幅を有し、そのため、中央領域は、そのような超小型電子素子の対向する第1の周縁部と第2の周縁部との間の最短距離の中央3分の1に延在する表面のエリアを占有する。

10

#### 【0046】

特定の実施形態では、超小型電子パッケージ10は、4つの超小型電子素子30を有することができ、各超小型電子素子のコンタクト35は、8つのデータI/Oコンタクトを含む。別の実施形態では、超小型電子パッケージ10は、4つの超小型電子素子30を有することができ、各超小型電子素子のコンタクト35は、16個のデータI/Oコンタクトを含む。特定の例では、超小型電子パッケージ10（及び本明細書において説明する他の超小型電子パッケージのうちの任意のもの）は、クロックサイクルごとに32個のデータビットを並列に転送、すなわち、パッケージによって受信又はパッケージから送信するように構成することができる。別の例では、超小型電子パッケージ10（及び本明細書において説明する他の超小型電子パッケージのうちの任意のもの）は、クロックサイクルごとに64個のデータビットを並列に転送するように構成することができる。複数の他のデータ転送量が可能であり、その中でも、数個のそのような転送量のみについて言及するが、限定するものではない。例えば、超小型電子パッケージ10（及び本明細書において説明する他の超小型電子パッケージのうちの任意のもの）は、クロックサイクルごとに72個のデータビットを転送するように構成することができる。この72個のデータビットは、データを表す64個の基本ビット（underlying bits）と、64個の基本ビットのための誤り訂正符号（「ECC（:error correction code）」）ビットである8つのビットとのセットを含みうる。96個のデータビット、108個のビット（データビット及びECCビット）、128個のデータビット、及び144個のビット（データビット及びECCビット）は、超小型電子パッケージ10（及び本明細書において説明する他の超小型電子パッケージのうちの任意のもの）がサポートするように構成することができる、サイクル当たりのデータ転送幅の他の例である。

20

#### 【0047】

図1A～図1Cの実施形態では、パッケージの第1の端子25aを通過する少なくとも幾つかの信号は、超小型電子素子30のうちの少なくとも2つと共に通にすることができる。これらの信号は、第1の端子25aから、基板20の第2の表面22に対して平行な方向に延在する導電性トレース等の接続部を通って超小型電子素子30の対応するコンタクト35に送ることができる。超小型電子パッケージ10は、複数の超小型電子素子30に共通の信号を、超小型電子素子のうちの特定の1つにそれぞれ専用化されたパッケージの2つ以上の端子を通してではなく、パッケージの共通の第1の端子25aを通して送ることができる。このようにして、そのような端子25によって占有される基板20の面積量を削減することができる。

30

#### 【0048】

図1Aは、風車の形状に類似した、基板20上の超小型電子素子30a、30b、30c、及び30dの特定の配置を示している。この場合、各超小型電子素子30の複数のコンタクト35のうちの少なくとも幾つかは、それぞれの第1の軸29a、第2の軸29b、第3の軸29c、及び第4の軸29d（総称して軸29）を規定するコンタクトのそれ

40

50

それの列に配置することができる。図 1 A に示す例では、第 1 の軸 29 a 及び第 3 の軸 29 c は、互いに平行にすることができ、第 2 の軸 29 b 及び第 4 の軸 29 d は、互いに平行にすることができ、第 1 の軸及び第 3 の軸は、第 2 の軸及び第 4 の軸に対して横向きにすることができる。特定の実施形態では、第 1 の軸 29 a 及び第 3 の軸 29 c は、第 2 の軸 29 b 及び第 4 の軸 29 d に対して直交することができる。一例では、第 1 の軸 29 a 、第 2 の軸 29 b 、第 3 の軸 29 c 、及び第 4 の軸 29 d のそれぞれは、開口部 26 を上述したような風車の構成に配置することができるよう、開口部 26 a 、 26 b 、 26 c 、及び 26 d のうちの対応するものの長さによって規定することができる。

## 【0049】

図 1 A に示す特定の例では、各超小型電子素子 30 の軸 29 は、それぞれの超小型電子素子を二分することができ、超小型電子パッケージ 10 内の正確に 1 つの他の超小型電子素子のエリアと交差することができる。例えば、第 1 の軸 29 a は、第 1 の超小型電子素子 30 a を二分することができ、正確に 1 つの他の超小型電子素子 30 のエリアと交差することができる。同様に、第 2 の軸 29 b は、第 2 の超小型電子素子 30 b を二分することができ、正確に 1 つの他の超小型電子素子 30 のエリアと交差することができる。同じことは、第 3 の超小型電子素子 30 c を二分することができ、正確に 1 つの他の超小型電子素子 30 のエリアと交差することができる第 3 の軸 29 c にも当てはまる。確かに、これは、第 4 の超小型電子素子 30 d を二分することができ、正確に 1 つの他の超小型電子素子 30 のエリアと交差することができる第 4 の軸 29 d にも当てはまる。

## 【0050】

コンタクト 35 と端子 25 との間の電気的接続部は、オプションのリード、例えば、ワイヤボンド 40 、又はリードの少なくとも一部分が開口部 26 のうちの少なくとも 1 つと位置合わせされている他の可能な構造を含みうる。例えば、図 1 B に見られるように、電気的接続部のうちの少なくとも幾つかは、基板内の開口部 26 の縁部を越えて延在するワイヤボンド 40 を含むことがあり、コンタクト 35 及び基板の導電性素子 24 に接合される。一実施形態では、電気的接続部のうちの少なくとも幾つかは、リードボンドを含みうる。そのような接続部は、導電性素子 24 と端子 25 との間を、基板 20 の第 1 の表面 21 及び第 2 の表面 22 のいずれか又は双方に沿って延在するリードを含みうる。特定の例では、そのようなリードは、各超小型電子素子 30 のコンタクト 35 と端子 25 との間に電気的に接続することができ、各リードは、開口部 26 のうちの少なくとも 1 つと位置合わせされた部分を有する。

## 【0051】

一例では、開口部 26 のそれぞれは、それぞれの軸 29 に対して横向きの方向に幅を有することができ、各開口部の幅は、その開口部の幅と同じ方向において、その開口部の上に少なくとも部分的に重なる超小型電子素子 30 の幅よりも大きくない。

## 【0052】

一例では、基板 20 の第 1 の表面 21 ( 図 1 A ) 又は第 2 の表面 22 の方に向いた表面 31' を有する 1 つ以上の追加のチップ 30' を基板 20 に実装することができる。そのような追加のチップ 30' は、基板 20 の第 1 の表面 21 に露出した導電性コンタクトにフリップチップボンディングすることができる。

## 【0053】

追加のチップ 30' のうちの 1 つ以上のものは、超小型電子パッケージ 10 の外部の構成要素に対する超小型電子素子 30 のそれぞれの信号絶縁を提供するのに役立つように構成することができるバッファリングチップとすることができる。一例では、そのようなバッファリングチップ又はバッファ素子は、超小型電子パッケージ 10 において、端子 25 のうちの少なくとも幾つかと、超小型電子素子 30 のうちの 1 つ以上のものとに電気的に接続することができ、バッファ素子は、超小型電子パッケージ 10 の端子のうちの 1 つ以上のものにおいて受信された少なくとも 1 つの信号を再生成するように構成されている。一実施形態では、超小型電子パッケージ 10 は、レジスタ DIMM であり、少なくとも 1 つの信号は、パッケージに転送されるコマンド信号、アドレス信号、バンクアドレス信号

10

20

30

40

50

、及びクロック信号の全てを含むことがあり、コマンド信号は、書き込みイネーブル信号、行アドレスストローブ信号、及び列アドレスストローブ信号であり、クロック信号は、アドレス信号をサンプリングするのに用いられるサンプリングクロックである。特定の例では、超小型電子パッケージ 10 が、負荷軽減 DIMM (「LRDIMM ( : load-reduced DIMM )」) であるとき、少なくとも 1 つの信号は、超小型電子パッケージによって受信されたデータ信号の全てを含みうる。

#### 【0054】

特定の実施形態では、追加のチップ 30' のうちの 1 つ以上のものは、デカップリングコンデンサとすることができます。1 つ以上のデカップリングコンデンサは、上述したバッファリングチップの代わりに又はそれに加えて、超小型電子素子 30' 間に配置することができます。そのようなデカップリングコンデンサは、超小型電子パッケージ 10 の内部の電源バス及び接地バスに電気的に接続することができます。

10

#### 【0055】

一実施形態では、追加のチップ 30' のうちの 1 つは、基板 20 に実装されるとともに、超小型電子パッケージのデータ幅及びデータ深度等の超小型電子パッケージ 10 の識別情報を永久的に記憶するように構成された電気的消去可能プログラマブル読み出し専用メモリ (「EEPROM ( : electrical erasable programmable read only memory )」) 等の不揮発性メモリ素子でありうる。そのような不揮発性メモリ素子は、超小型電子素子 30' のうちの 1 つ以上のものに電気的に接続することができる。

20

#### 【0056】

一例では、追加のチップ 30' のうちの 1 つは、温度センサでありうる。そのような温度センサは、超小型電子素子 30' のうちの 1 つ以上のものに電気的に接続することができる。一例では、温度センサは、ダイオードを含むことがあり、基板 20 に実装することができる。特定の実施形態では、追加のチップ 30' のうちの 1 つは、基板 20 に実装された直列プレゼンス検出素子でありうる。

20

#### 【0057】

超小型電子パッケージ 10 は、超小型電子素子 30' の前面 31 と基板 20 の第 1 の表面 21 との間に接着剤 12 を更に備えることができる。超小型電子パッケージ 10 は、超小型電子素子 30' の背面 32 を任意選択的に覆うか、部分的に覆うか、又は覆いのないままとすることができる封入材 (図示せず) も備えることができる。例えば、図 1A ~ 図 1C に示すパッケージには、超小型電子素子 30' の背面 32 に封入材を流し込むことができるか、ステンシル印刷することができるか、スクリーン印刷することができるか、又は分注することができる。別の例では、封入材は、オーバモールドによってその上に形成される成形化合物でありうる。

30

#### 【0058】

上記の実施形態の変形形態では、超小型電子素子のコンタクトは、その表面の中央領域内に配置されないようにすることができる。むしろ、それらのコンタクトは、そのような超小型電子素子の縁部に隣接する 1 つ以上の行内に配置される場合がある。別の変形形態では、超小型電子素子のコンタクトは、そのような超小型電子素子の 2 つの対向する縁部に隣接して配置することができる。更に別の変形形態では、超小型電子素子のコンタクトは、任意の 2 つの縁部に隣接して配置することができるか、又はそのような超小型電子素子の 3 つ以上の縁部に隣接して配置することができる。そのような場合、基板内の開口部の場所は、超小型電子素子のそのような 1 つ以上の縁部に隣接して配置されるコンタクトの場所に対応するように変更することができる。

40

#### 【0059】

図 2A 及び図 2B は、図 1A ~ 図 1C に関して上述した実施形態の一変形形態を示している。この変形形態では、超小型電子素子 230 が、基板 220 の第 1 の表面 221 にフリップチップボンディングされている。そのような一実施形態では、超小型電子素子 230 と基板 220 との間の電気的接続部は、超小型電子素子のそれぞれのコンタクトと、基板の第 1 の表面 221 に露出した導電性ボンドパッドとの間に延在するフリップチップ接

50

続部を含む。

**【0060】**

図2Cは、図2A及び図2Bに関して上述した実施形態の一変形形態を示している。この変形形態では、超小型電子素子230のうちの1つ以上のものは、下側超小型電子素子230'であり、超小型電子パッケージ210'は、上側超小型電子素子230a、230b、及び230cを備え、各上側超小型電子素子は、下側超小型電子素子の背面232の上に少なくとも部分的に重なる表面を有する。図2Cに示すように、上側超小型電子素子230a、230b、及び230cは、下側超小型電子素子を貫通して延在する少なくとも1つの導電性ピア209を通じて下側超小型電子素子230'と電気的に接続されている。特定の実施形態では、下側超小型電子素子230'を、基板220の第2の表面222に露出した導電性コンタクトにワイヤボンディングでありうる。10

**【0061】**

図2Dは、図2A及び図2Bに関して上述した実施形態の一変形形態を示している。この一変形形態では、超小型電子素子230のうちの1つ以上のものは、下側超小型電子素子230"であり、超小型電子パッケージ210"は、上側超小型電子素子230a及び230bを備え、各上側超小型電子素子は、下側超小型電子素子の背面232の上に少なくとも部分的に重なる表面を有する。図2Dに示すように、上側超小型電子素子230a及び230bは、上側超小型電子素子のコンタクト235と、下側超小型電子素子230"の背面232に露出した導電性素子245との間に延在するワイヤボンド240を通じて下側超小型電子素子230"と電気的に接続されている。特定の実施形態では、下側超小型電子素子230"は、基板220の第2の表面222に露出した導電性コンタクトにワイヤボンディングでありうる。20

**【0062】**

図3A～図3Dは、基板の第1の表面に対する超小型電子素子の異なるロケーションを有する、図1A～図1Cに示す超小型電子パッケージ10の追加の変形形態を示している。図3A～図3Dにおいて、それぞれの超小型電子パッケージ301、302、303、及び304は、4つの超小型電子素子330をそれぞれ備えることができ、各超小型電子素子は、基板320の第2の表面に露出した導電性コンタクトにそれぞれの開口部326を通ってワイヤボンディングされたコンタクトを有する。開口部326は、基板の第2の表面の中央領域323の境界の部分を規定することができ、この中央領域には、超小型電子素子330のうちの少なくとも2つに接続された共有される第1の端子が位置することができる。30

**【0063】**

図3Aにおいて、超小型電子パッケージ301は、図1A～図1Cの超小型電子素子30と同様に配置された超小型電子素子330を有するが、超小型電子素子330はそれぞれ、実質的に正方形の形状を有し、そのため、基板320の第1の表面には、超小型電子素子間に位置する空所がほとんどない。

**【0064】**

図3Bにおいて、超小型電子素子330のそれぞれは、それぞれの開口部326の長さに対して平行に向いた第1の縁部332a及び対向する縁部332bを有する。超小型電子素子330のそれぞれの第1の縁部332aは、他の超小型電子素子のいずれのエリアも通って延在していない軸329を規定することができる。そのような実施形態では、基板320の第1の表面において、超小型電子素子330間に位置するより大きな空所があり、基板の第2の表面の中央領域323は、比較的大きくすることができる。40

**【0065】**

図3Cにおいて、超小型電子素子330のそれぞれは、他の超小型電子素子のいずれのエリアも通って延在していない軸329を規定するそれぞれの開口部326の上に重なることができる。しかしながら、図3Bと比較すると、超小型電子素子のうちの2つ330a及び330cは、基板320の第1の表面の中央により近く移動している。超小型電子素子330のそれぞれは、それぞれの開口部326の長さに対して平行に向いた第1の縁50

部332a及び対向する縁部332bを有する。第1の超小型電子素子330a及び第3の超小型電子素子330cの第1の縁部332aは、第2の超小型電子素子330b及び第4の超小型電子素子330dのエリアを通って延在するそれぞれの軸329a及び329cを規定することができる。

#### 【0066】

図3Dは、超小型電子素子のうちの2つ330a及び330cが基板320の第1の表面の中央により一層近く移動している、図3Cの一変形形態である。第1の超小型電子素子330a及び第3の超小型電子素子330cは、第2の超小型電子素子330b及び第4の超小型電子素子330dのエリアを通って延在するそれぞれの軸329及び329'を規定するそれぞれの開口部326a及び326cの上に重なることができる。また、超小型電子素子330のそれぞれは、それぞれの開口部326の長さに対して平行に向いた第1の縁部332a及び対向する縁部332bを有する。第1の超小型電子素子330a及び第3の超小型電子素子330cの第1の縁部332aは、同様に、第2の超小型電子素子330b及び第4の超小型電子素子330dのエリアを通って延在するそれぞれの軸329a及び329cを規定することができる。

#### 【0067】

図4A及び図4Bは、基板420の第1の表面に対して平行な单一の平面に配置された前面を有する3つの超小型電子素子を有する、図1A～図1Cに示す超小型電子パッケージ10の追加の変形形態を示している。図4Aにおいて、超小型電子パッケージ401は、基板420の第1の側に実装された3つの超小型電子素子430を有する。超小型電子素子のうちの第1のもの430aは、例えば、図2C又は図2Dに示すような方法で、当該第1の超小型電子素子の上に少なくとも部分的に重なるとともに当該第1の超小型電子素子と電気的に接続された追加の超小型電子素子を有することがある。超小型電子素子のうちの第2のもの430bは、例えば、コントローラでありうる。図4Bにおいて、超小型電子パッケージ402は、風車構成の超小型電子素子430のうちの1つが省略され、基板420の第1の表面に対して平行な单一の平面に配置された前面を有する3つの超小型電子素子が残されていることを除いて、図1A～図1Cに示す超小型電子パッケージ10と同じである。

#### 【0068】

図5A～図5Cは、図1A～図1Cに関して上述した実施形態の一変形形態を示している。超小型電子パッケージ510は、図1A～図1Cに示す超小型電子パッケージ10と同様である。しかしながら、パッケージ510は、下側超小型電子素子530a及び上側超小型電子素子530bの複数の対507を含む。そのような各対507において、上側超小型電子素子530bの前面531は、下側超小型電子素子530aの背面とすることができますそのような下側超小型電子素子530aの表面532の上に少なくとも部分的に重なる。第1の対507a及び第2の対507b等の超小型電子素子の隣接する対507は、基板520の第1の表面521に対して平行な水平方向Hに互いに十分離間させることができる。特定の例では、超小型電子素子530a及び530bはともに、他のいずれの機能よりもメモリ記憶アレイ機能を提供する能動デバイスを多く具現化することができる。

#### 【0069】

一実施形態では、超小型電子パッケージ510は、8つの超小型電子素子530(4つの下側超小型電子素子530a及び4つの上側超小型電子素子530bを含む)を有することができ、各超小型電子素子は、8つのデータI/Oコンタクトを備える。別の実施形態では、超小型電子パッケージ510は、8つの超小型電子素子530(4つの下側超小型電子素子530a及び4つの上側超小型電子素子530bを含む)を有することができ、各超小型電子素子は、9つのデータI/Oコンタクトを備える。

#### 【0070】

特定の例では、超小型電子素子の隣接する対の下側超小型電子素子530aの前面531に露出した導電性コンタクト535のうちの少なくとも幾つかは、第1の軸529a及

10

20

30

40

50

び第2の軸529a'を規定するコンタクトのそれぞれの列に配置することができる。図5Aに示すように、そのような第1の軸529a及び第2の軸529a'は、互いに対し横向きにすることができる。特定の例では、第1の軸529a及び第2の軸529a'は、互い直交することができる。一実施形態では、第1の軸529a及び第2の軸529a'は、互いに平行にすることができる。

#### 【0071】

一実施形態では、超小型電子素子の各対507は、基板520の第1の表面521と第2の表面522との間に延在する外側開口部526aの上に少なくとも部分的に重なることができる。各外側開口部526aは、第1の表面及び第2の表面に対して平行な方向に延在する外側軸509aを規定する長さを有することができる。4つの外側軸509aは、上述したような風車構成に配置することができ、外側軸509aは、外側軸の2つ平行な対に配置することができ、各対は、他方の対に対して横向きである。基板520の第2の表面522の中央部分を占有する中央領域523は、図5Cに示すように、4つの外側軸509aによって境界を定めることができる。基板520の第2の表面522の中央領域523に露出した端子525のうちの少なくとも幾つかは、上述した第1の端子25aと同様の機能を有する第1の端子とすることができる。

10

#### 【0072】

一例示の実施形態では、超小型電子素子の各対507は、図5Aに示すように、同じ超小型電子素子の対内の外側開口部526aのうちの対応するものに隣接する、基板520の第1の表面521と第2の表面522との間に延在する内側開口部526bの上にも少なくとも部分的に重なることができる。各内側開口部526bは、第1の表面及び第2の表面に対して平行な方向に延在する軸509bを規定する長さを有することができ、各内側軸509bは、外側開口部526aのうちの対応するものの長さによって規定される軸509aよりも基板の重心501に近い。

20

#### 【0073】

図5Aに示すように、各下側超小型電子素子530aは、外側開口部526aの上に重なり、各上側超小型電子素子530bは、内側開口部526bの上に重なる。特定の実施形態では、各上側超小型電子素子530bは、外側開口部526aの上に重なることができ、各下側超小型電子素子530aは、内側開口部526bの上に重なることができる。一例では、下側超小型電子素子530aのうちの1つ以上のものは、対応する外側開口部526aの上に重なることができ、他の下側超小型電子素子は、対応する内側開口部526bの上に重なる一方、上側超小型電子素子530bのうちの1つ以上のものは、対応する外側開口部の上に重なることができ、他の上側超小型電子素子は、対応する内側の開口部の上に重なることができる。

30

#### 【0074】

特定の例では、各上側超小型電子素子530bは、内側開口部526b又は外側開口部526aのいずれかとすることができる第1の開口部の上に重なることができる。第1の開口部のそれぞれは、その長さに対して横向きの方向に幅を有することができ、第1の開口部のそれぞれの幅は、第1の開口部の幅と同じ方向において第1の開口部の上に重なる上側超小型電子素子530bのうちの対応するものの幅よりも大きくない。

40

#### 【0075】

一例では、各下側超小型電子素子530aは、内側開口部526b又は外側開口部526aのいずれかとすることができる第2の開口部の上に重なることができる。第2の開口部のそれぞれは、その長さに対して横向きの方向に幅を有することができ、第2の開口部のそれぞれの幅は、第2の開口部の幅と同じ方向において第2の開口部の上に重なる下側超小型電子素子530aのうちの対応するものの幅よりも大きくない。

#### 【0076】

上側超小型電子素子530bの前面531と、基板520の第1の表面521の一部分との間にスペーサ514を位置決めすることができ、当該スペーサと基板の第1の表面との間に位置する接着剤512の有無は問わない。そのようなスペーサ514は、例えば、

50

二酸化シリコン等の誘電体材料、シリコン等の半導体材料、又は1つ以上の接着剤層から作製することができる。スペーサ514が接着剤を含む場合、それらの接着剤は、上側超小型電子素子530bを基板520に接続することができる。一実施形態では、スペーサ514は、基板520の第1の表面521に対して実質的に垂直な垂直方向Vにおいて、前面531と背面532との間の下側超小型電子素子530aの厚さT2と実質的に同じ厚さT1を有することができる。特定の実施形態では、例えば、スペーサ514が、接着材料から作製されているとき、スペーサ514は、上述した接着剤12等の接着剤512なしで用いることができる。

#### 【0077】

図6A～図6Cは、図5A～図5Cに関して上述した実施形態の一変形形態を示している。

10

超小型電子パッケージ610は、当該超小型電子パッケージ610では、上側超小型電子素子630bの前面631が、2つの下側超小型電子素子630aの背面632の上に少なくとも部分的に重なることを除いて、図5A～図5Cに示す超小型電子パッケージ510と同様である。下側超小型電子素子630aの全ては、基板620の第1の表面621に対して平行な単一の平面に配置された前面631を有することができる。

#### 【0078】

図7は、図5A～図5Cに関して上述した実施形態の別の変形形態を示している。

20

超小型電子パッケージ710は、当該超小型電子パッケージ710が、超小型電子素子の3つの対707を備え、各対が下側超小型電子素子730a及び上側超小型電子素子730bを有することを除いて、図5A～図5Cに示す超小型電子パッケージ510と同じである。

超小型電子素子の第4の対707の代わりに、超小型電子パッケージ710は、2つの下側超小型電子素子730aと、上側超小型電子素子のそれぞれの背面732の上に少なくとも部分的に重なる前面731を有する1つの対応する上側超小型電子素子730bとをグループ化したものを備える。一例では、超小型電子パッケージ710は、それぞれ8つのデータI/Oコンタクトを備える9つの超小型電子素子730を有することができる。

#### 【0079】

図8A及び図8Bを参照すると、超小型電子アセンブリ801は、共通の回路パネル860に実装することができる複数の超小型電子パッケージ810を備えることができる。

30

超小型電子パッケージ810のそれぞれは、図1A～図1Cからの超小型電子パッケージ10として示されているが、そのような超小型電子パッケージ810は、図1A～図7を参照して上述した超小型電子パッケージの任意のものとすることができる。回路パネル860は、対向する第1の表面861及び第2の表面862と、それぞれの第1の表面及び第2の表面に露出した複数の導電性パネルコンタクトとを有することができる。超小型電子パッケージ810は、例えば、各超小型電子パッケージの端子とパネルコンタクトとの間に延在することができる図1Bに示す接合素子11によって、パネルコンタクトに実装することができる。図8Bに示すように、第1の超小型電子パッケージ810aの基板の第2の表面と、第2の超小型電子パッケージ810bの基板の第2の表面とは、互いの上に少なくとも部分的に重なることができる。特定の例では、回路パネル860は、30pm/未満のCTEを有する素子を備えることができる。一実施形態では、そのような素子は、半導体、ガラス、セラミック、又は液晶ポリマ材料から基本的になることがある。

#### 【0080】

特定の実施形態では、回路パネル860は、超小型電子アセンブリ801がソケット(図9に示す)に挿入されたときに、ソケットの対応するコンタクトと接続する複数の平行な露出した縁部コンタクト850を、第1の表面861及び第2の表面862のうちの少なくとも一方の挿入縁部851に隣接して有することができる。縁部コンタクト850のうちの一部又は全ては、超小型電子アセンブリ801の第1の表面861又は第2の表面862のいずれか又は双方に露出することができる。一例では、回路パネル860は、マザーボードでありうる。一例示の実施形態では、回路パネル860は、マザーボード等の別の回路パネルに取り付けるように構成することができるメモリサブシステム等のモジュ

10

20

30

40

50

ールでありうる。別の回路パネルへの回路パネル 860 のそのような取り付けは、以下に説明するようなものとすることができます。

#### 【0081】

露出した縁部コンタクト 850 及び挿入縁部 851 は、マザーボード上に設けることができるようなシステムの他のコネクタの対応するソケット（図9）内への挿入用にサイズ決めすることができる。そのような露出した縁部コンタクト 850 は、そのようなソケットコネクタ内の複数の対応するばねコンタクト（図9）と接続するのに適することができる。そのようなばねコンタクトは、露出した縁部コンタクト 850 のうちの対応するものと接続するように、各スロットの单一又は複数の側に配置することができる。一例では、縁部コンタクト 850 のうちの少なくとも幾つかは、それぞれの縁部コンタクトと、超小型電子パッケージ 810 のうちの1つ以上のものとの間で信号又は基準電位のうちの少なくとも一方を搬送するのに使用可能でありうる。特定の実施形態では、超小型電子アセンブリ 801 は、デュアルオンラインメモリモジュールと同じ信号インターフェースを有することができる。10

#### 【0082】

図8C～図8Eは、図5A～図5Cからの超小型電子パッケージ 510 として示されている超小型電子パッケージ 810' を備える、図8A及び図8Bに示す超小型電子アセンブリ 801 の変形形態を示している。図8Cにおいて、超小型電子パッケージ 802 は、回路パネル 860 の第1の側 861 に実装された5つの超小型電子パッケージ 810' を有する。20

#### 【0083】

図8Dにおいて、超小型電子パッケージ 803 は、回路パネル 860 の第1の表面 861 に実装された5つの超小型電子パッケージ 810' を有し、回路パネルの第1の表面の方に向いた表面を有する、図1Aに示す追加のチップ 30' のような追加のチップ 830' が示されている。そのような追加のチップ 830' は、例えば、超小型電子アセンブリ 803 の外部の構成要素に対する超小型電子パッケージ 810' のそれぞれの信号絶縁を提供するのに役立つように構成することができるバッファリングチップを備える、図1A～図1Cを参照して上述した追加のチップのタイプのうちの任意のものとすることができます。一例では、追加のチップ 830' は、メモリコントローラを含みうる。30

#### 【0084】

図8Eにおいて、超小型電子パッケージ 804 は、それぞれのソケット 805 にそれぞれ実装された5つの超小型電子パッケージ 810' を有し、各ソケットは、回路パネル 860 の第1の表面 861 に実装されている。30

#### 【0085】

図1～図8Eを参照して上述した超小型電子パッケージ及び超小型電子アセンブリは、図9に示すシステム 900 等の多様な電子システムの構成において利用することができる。例えば、本発明の更なる実施形態によるシステム 900 は、上述したような超小型電子パッケージ及び超小型電子アセンブリ等の複数のモジュール又は構成要素 906 を、他の電子構成要素 908 及び 910 とともに備える。40

#### 【0086】

システム 900 は、複数のソケット 905 を備えることができ、各ソケットは、当該ソケットの一方又は双方の側に複数のコンタクト 907 を備え、各ソケット 905 が、対応するモジュール又は構成要素 906 の対応する露出した縁部コンタクト又は露出したモジュールコンタクトと接続するのに適することができるようになっている。図示する例示のシステム 900 では、システムは、フレキシブルプリント回路基板等の回路パネル又はマザーボード 902 を備えることができ、この回路パネルは、モジュール又は構成要素 906 を互いに相互接続する多数の導体 904 を備えることができ、これらの導体のうちの1つのみが図9に示されている。そのような回路パネル 902 は、システム 900 に備えられた超小型電子パッケージ 10 又は 110 のそれに及びそれから信号をトランスポートすることができる。しかしながら、これは、単なる例示にすぎない。モジュール又50

は構成要素 906 間の電気的接続部を作製する任意の適した構造を用いることができる。特定の例では、モジュール又は構成要素 906 を、ソケット 905 を通じて回路パネル 902 に結合するのではなく、超小型電子パッケージ 10 等のモジュール又は構成要素 906 のうちの 1 つ以上のものを回路パネル 902 に直接実装することができる。

#### 【0087】

特定の実施形態では、システム 900 は、半導体チップ 908 等のプロセッサも備えることができ、各モジュール又は構成要素 906 は、クロックサイクルにおいて N 個のデータビットを並列に転送するように構成することができ、プロセッサは、クロックサイクルにおいて M 個のデータビットを並列に転送するように構成することができるようになっている。M は N 以上である。

10

#### 【0088】

一例では、システム 900 は、クロックサイクルにおいて 32 個のデータビットを並列に転送するように構成されたプロセッサチップ 908 を備えることができ、このシステムは、図 1A ~ 図 1C を参照して説明したモジュール 10 等の 4 つのモジュール 906 も備えることができ、各モジュール 906 は、8 個のデータビットをクロックサイクルにおいて 8 個のデータビットを並列に転送するように構成されている（すなわち、各モジュール 906 は、第 1 の超小型電子素子及び第 2 の超小型電子素子を備えることができ、これらの 2 つの超小型電子素子のそれぞれは、クロックサイクルにおいて 4 個のデータビットを並列に転送するように構成されている）。

20

#### 【0089】

別の例では、システム 900 は、クロックサイクルにおいて 64 個のデータビットを並列に転送するように構成されたプロセッサチップ 908 を備えることができ、このシステムは、図 9 を参照して説明したモジュール 1000 等の 4 つのモジュール 906 も備えることができ、各モジュール 906 は、クロックサイクルにおいて 16 個のデータビットを並列に転送するように構成されている（すなわち、各モジュール 906 は、第 1 の超小型電子素子及び第 2 の超小型電子素子からなる 2 つセットを備えることができ、これらの 4 つの超小型電子素子のそれぞれは、クロックサイクルにおいて 4 個のデータビットを並列に転送するように構成されている）。

20

#### 【0090】

図 9 に示す例では、構成要素 908 は半導体チップであり、構成要素 910 はディスプレイスクリーンであるが、他の任意の構成要素をシステム 900 において用いることができる。もちろん、説明図を明瞭にするために、図 9 には 2 つの追加の構成要素 908 及び 910 しか示されていないが、システム 900 は、任意の数のそのような構成要素を備えることができる。

30

#### 【0091】

モジュール又は構成要素 906 並びに構成要素 908 及び 910 は、破線で概略的に示す共通のハウジング 901 内に実装することができ、必要に応じて互いに電気的に相互接続して所望の回路を形成することができる。ハウジング 901 は、例えば、携帯電話又は携帯情報端末において使用可能なタイプのポータブルハウジングとして示され、スクリーン 910 は、このハウジングの表面に露出することができる。構成 906 が撮像チップ等の光感知素子を備える実施形態では、光をこの構造体に送るレンズ 911 又は他の光学デバイスも設けることができる。ここでも、図 9 に示す単純化したシステムは単なる例示にすぎず、デスクトップコンピュータやルータ等の固定構造と一般に考えられるシステムを含む他のシステムを、上記で議論した構造体を用いて作製することができる。

40

#### 【0092】

上記で説明した超小型電子パッケージのいずれか又は全てにおいて、超小型電子素子のうちの 1 つ以上のものは、製造の完了後に超小型電子パッケージの外表面において少なくとも部分的に露出させることができる。したがって、図 1A に関して上述した超小型電子パッケージ 10 において、超小型電子素子 30 の背面 32 は、完成した超小型電子パッケージ 10 内の封入材の外表面において部分的又は全面的に露出させることができる。

50

**【 0 0 9 3 】**

上述した実施形態のいずれかにおいて、超小型電子パッケージは、任意の適した熱伝導性材料から部分的又は全体的に作製された放熱体を備えることができる。適した熱伝導性材料の例には、金属、グラファイト、熱伝導性接着剤、例えば、熱伝導性エポキシ樹脂、はんだ等、又はそのような材料の組み合わせが含まれるが、これらに限定されるものではない。一例では、放熱体は、実質的に連続した金属シートとすることができる。

**【 0 0 9 4 】**

一実施形態では、放熱体は、超小型電子素子のうちの1つ以上のものに隣接して配置された金属層を備えることができる。この金属層は、超小型電子パッケージの背面に露出することができる。代替的に、放熱体は、超小型電子素子の少なくとも背面をカバーするオーバーモールド又は封入材を含みうる。一例では、放熱体は、図1A及び図1Bに示す超小型電子素子30等の超小型電子素子のそれぞれの前面及び背面のうちの少なくとも一方と熱連通することができる。放熱体は、超小型電子素子のうちの隣接するものの隣接する縁部間に延在することができる。放熱体は、周囲環境への放熱を改善することができる。

10

**【 0 0 9 5 】**

特定の実施形態では、金属製又は他の熱伝導性材料製の事前に形成された放熱体を、熱伝導性接着剤又は熱伝導性グリース等の熱伝導性材料を用いて、超小型電子素子のうちの1つ以上のものの背面に取り付けるか又は配置することができる。接着剤が存在する場合、この接着剤は、例えば、コンプライアントに取り付けられた素子間の熱膨張差を吸収するように、放熱体と、この放熱体が取り付けられた超小型電子素子との間の相対的な移動を可能にするコンプライアント材料とすることができる。放熱体は、モノリシック構造とすることができます。代替的に、放熱体は、互いに離間した複数のスプレッダ部を備えることができる。特定の実施形態では、放熱体は、図1A及び図1Bに示す超小型電子素子30等の超小型電子素子のうちの1つ以上のものの背面の少なくとも一部分に直接接合されたはんだの層とすることができますか、又はこのはんだの層を含みうる。

20

**【 0 0 9 6 】**

本発明は特定の実施形態を参照しながら本明細書において説明されてきたが、これらの実施形態は本発明の原理及び応用形態を例示するにすぎないことは理解されたい。それゆえ、添付の特許請求の範囲によって規定されるような本発明の趣旨及び範囲から逸脱することなく、例示的な実施形態に数多くの変更を加えることができること、及び他の構成を考案することは理解されたい。

30

**【 0 0 9 7 】**

様々な従属請求項及びそこに記載した特徴を、初期の請求項に提示したものとは異なる方法で組み合わせることができることが認識されるであろう。個々の実施形態について説明した特徴は、説明した実施形態の他のものと共有することができることも認識されるであろう。

**【 産業上の利用可能性】****【 0 0 9 8 】**

本発明は、超小型電子パッケージ及び超小型電子パッケージを製造する方法を含むが、これらに限定されるものではない幅広い産業上の利用可能性を享有する。

40

【図 1 A】

【図 1 C】

【図 1 B】

【図 2 A】

【図 2 C】

【図 2 B】

【図 2 D】

【図 3 A】

【図 3 B】

【図 3 D】

【図 4 A】

【図 3 C】

【図 4 B】

【図 5 B】

【図 5 A】

【図 5 C】

【図 6 A】

【図 6 B】

【図 6 C】

【図 7】

【図 8 A】

【図 8 B】

【図 8 E】

【図 8 C】

【図 9】

【図 8 D】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                           | International application No<br>PCT/US2012/046249 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. H01L25/065 H01L23/13<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                           |                                                   |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                           |                                                   |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                           |                                                   |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |                                                   |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                           |                                                   |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                           |                                                   |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                        | Relevant to claim No.                             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2011/042824 A1 (KOIDE MASATERU [JP])<br>24 February 2011 (2011-02-24)<br>paragraph [0018] - paragraph [0019];<br>figures 1,2<br>-----                                                                  | 1                                                 |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 6 252 264 B1 (BAILEY ROGER NED [US] ET AL) 26 June 2001 (2001-06-26)<br>column 2, lines 36-57, 59-60; figure 1<br>column 3, paragraph 61-64<br>column 4, lines 23-29<br>column 1, lines 59-61<br>----- | 1,2,4,5,<br>25                                    |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 5 936 305 A (AKRAM SALMAN [US])<br>10 August 1999 (1999-08-10)<br>column 4, line 8 - line 13; figures 1-5<br>column 4, line 60 - column 5, line 16<br>column 3, line 66 - column 4, line 12<br>-----   | 41-43                                             |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input checked="" type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                           |                                                   |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                                                                                           |                                                   |

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family |                                                                                                                                                                                                           |                                                   |

| Date of the actual completion of the international search<br><br>7 March 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report<br><br>20/03/2013                                                                                                                                      |                                                   |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Authorized officer<br><br>Manook, Rhoda                                                                                                                                                                   |                                                   |

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2012/046249

**Box No. II Observations where certain claims were found unsearchable (Continuation of Item 2 of first sheet)**

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box No. III Observations where unity of invention is lacking (Continuation of Item 3 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

**see additional sheet**

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

**1, 2, 4, 5, 25, 41-43**

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

- The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

- No protest accompanied the payment of additional search fees.

International Application No. PCT/ US2012/ 046249

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1, 2

Concerning the non-inventive subject matter of claim 1 (not inventive according to document US6252264 (D2) and knowledge of the skilled person - argumentation detailed in section 1.4.1 of this search report) : a microelectronic package, comprising:a substrate having first and second opposed surfaces; first, second, third, and fourth microelectronic elements, each microelectronic element having a front surface facing the first surface of the substrate and a plurality of contacts at the front surface, the front surfaces of the microelectronic elements being arranged in a single plane parallel to and overlying the first surface, each microelectronic element having a column of contacts exposed at the front surface and arranged along respective first, second, third, and fourth axes, the first and third axes being parallel to one another, the second and fourth axes being transverse to the first and third axes; a plurality of terminals exposed at the second surface, the terminals configured for connecting the microelectronic package to at least one component external to the microelectronic package; and electrical connections extending from at least some of the contacts of each microelectronic element to at least some of the terminals.

Re. cl. 2, the special technical feature with respect to the known claim 1 is: the second and fourth axes are orthogonal to the first and third axes.

1.1. claims: 4, 5, 25

Although the special technical features of the dependent claims 4,5 and 25 are not the same as that of claim 2, they could be searched without any additional effort and thus they form the basis of the 1st searched invention.

---

2. claims: 3, 18, 19

Re. cl. 3, the special technical feature with respect to the known claim 1 is: the column of contacts of each microelectronic element is disposed in a central region of the front surface of the respective microelectronic element.

Re. cl. 18, the special technical feature with respect to the known claim 1 is: the substrate is an element consisting essentially of a material having a CTE in a plane of the substrate less than 12 ppm/ $^{\circ}$ C.

Re. cl. 19, the special technical feature with respect to the known claim 1 is: the substrate includes a dielectric element consisting essentially of a material having a CTE in a plane of the substrate less than 30 ppm/ $^{\circ}$ C.

Thus the objective problem of claims 3,18 and 19 to be solved can be construed as: minimising the warping which may

International Application No. PCT/ US2012/ 046249

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

occur between the microelectronic elements and the substrate.

---

3. claims: 6-8

Re. cl. 6, the special technical feature with respect to the known claim 1 is: the contacts of each microelectronic element include eight data I/O contacts.

Re. cl. 7, the special technical feature with respect to the known claim 1 is: the contacts of each microelectronic element include nine data I/O contacts.

Re. cl. 8, the special technical feature with respect to the known claim 1 is: the contacts of each microelectronic element include sixteen data I/O contacts.

Thus the objective problem of claims 6-8 to be solved can be construed as: enabling the microelectronic elements to deal with predefined amounts of data transfer in parallel per clock cycle.

---

4. claims: 9-14

Re. cl. 9, the special technical feature with respect to the known claim 1 is: further comprising a buffer element electrically connected to at least some of the terminals and one or more of the microelectronic elements in the microelectronic package, the buffer element configured to regenerate at least one signal received at one or more of the terminals of the microelectronic package.

Thus the objective problem of claim 9 to be solved can be construed as: enabling the microelectronic package to cache data (see par. 71 of the application) with respect to components external to the package.

---

5. claim: 15

Re. cl. 15, the special technical feature with respect to the known claim 1 is: further comprising a nonvolatile memory element mounted to the substrate and configured to store identifying information, the nonvolatile memory element electrically connected to one or more of the microelectronic elements.

Thus the objective problem of claim 15 to be solved can be construed as: to provide means for permanently storing the package ID (see app. par. 73).

---

6. claim: 16

Re. cl. 16, the special technical feature with respect to the known claim 1 is: further comprising a temperature sensor.

Thus the objective problem of claim 16 to be solved can be

International Application No. PCT/US2012/046249

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

construed as: to enable a triggering function if the microelectronic element overheats.

---

**7. claim: 17**

Re. cl. 17, the special technical feature with respect to the known claim 1 is: further comprising a decoupling capacitor element mounted to the substrate, the decoupling capacitor element electrically connected to one or more of the microelectronic elements.

Thus the objective problem of claim 17 to be solved can be construed as: to ensure the package is protected against voltage swings.

---

**8. claims: 20-24**

Re. cl. 20, the special technical feature with respect to the known claim 1 is: the microelectronic elements are configured to function together as an addressable memory module, the microelectronic package configured to store part of data received in each of the microelectronic elements.

Re. cl. 23, the special technical feature with respect to the known claim 1 is: each of the microelectronic elements is configured to predominantly provide memory storage array function.

Re. cl. 24, the special technical feature with respect to the known claim 1 is: each of the microelectronic elements includes a dynamic random access memory ("DRAM") integrated circuit chip.

Thus the objective problem of claims 20, 23 and 24 to be solved can be construed as: enabling the package to store information.

---

**9. claims: 26, 27**

Re. cl. 26, the special technical feature with respect to the known claim 1 is: further comprising a heat spreader in thermal communication with at least one of the microelectronic elements.

Thus the objective problem of claim 26 to be solved can be construed as: ensuring the package is able to effectively dissipate heat.

---

**10. claims: 28, 29**

Re. cl. 28, the special technical feature with respect to the known claim 1 is: each microelectronic element is a lower microelectronic element, and each microelectronic package includes a corresponding upper microelectronic element for each lower microelectronic element, each upper microelectronic element having a surface at least partially

International Application No. PCT/US2012/046249

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

overlying a rear surface of the corresponding one of the lower microelectronic elements.

Thus the objective problem of claim 28 to be solved can be construed as: increasing the density of the microelectronic package.

---

11. claims: 30-38

Re. cl. 30, the special technical feature with respect to the known claim 1 is: further comprising a circuit panel having panel contacts, wherein the terminals of the package are bonded to the panel contacts.

Thus the objective problem of claim 30 to be solved can be construed as: configuring a module.

---

12. claims: 39, 40

Re. cl. 39, the special technical feature with respect to the known claim 1 is: one or more other electronic components electrically connected to the microelectronic package.

Thus the objective problem of claim 39 to be solved can be construed as: use of the microelectronic package itself in combination with other electronic components external to the package.

---

13. claims: 41-43

The common concept between dependent claims 42, 43, 44, 45, 47, 48 and 52 is the subject matter of claim 41 and this common concept is not new according to document US 5 936 305 (D3), in the sense of Art. 33(2) PCT, and therefore the criteria of Art. 33(1) PCT are not met:

D3 discloses: A microelectronic package (figs. 1-5), comprising: a substrate (12) having first (underside) and second (22) opposed surfaces; first, second, third, and fourth microelectronic elements (32 and other dice (col. 5, line 14-16)), each microelectronic element having a front surface (38) facing the first surface of the substrate and a plurality of contacts (50) at the front surface, the front surfaces of the microelectronic elements being arranged in a single plane parallel to and overlying the first surface (col. 4, line 8-13; col. 4, line 60-col. 5, line 16 and fig. 3,5), each microelectronic element at least partially overlying at least one aperture (20,21) extending between the first and second surfaces of the substrate, each aperture having a length (col. 3, line 66 - col. 4, line 12) along respective first, second, third, and fourth axes, the first and third axes being parallel to one another (fig. 1 (21)), the second and fourth axes being transverse to the first and third axes (fig. 1 (20)); a plurality of terminals exposed at the second surface (18), the terminals configured

International Application No. PCT/US2012/046249

## FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

for connecting the microelectronic package to at least one component external to the microelectronic package (col. 3, line 54-58); and electrical connections (fig. 3 (42) and fig. 5 (64)) extending from at least some of the contacts of each microelectronic element (32) to at least some of the terminals, the electrical connections including leads having at least portions aligned with the at least one aperture (figs. 3 and 5).

As a consequence of the above, the following claimed separate invention groups have been identified in the sense of Rule 13(2) PCT:

Invention 2a: Claims 41-43 (c.f. claim 42)

Re. cl. 42, the special technical feature with respect to the known common general concept is: at least some of the leads include wire bonds extending through at least one of the apertures.

Although the special technical features of the dependent claims 43 are not the same, they could be searched without any additional effort and thus they form the basis of the searched invention group 2a.

---

14. claim: 44

Re. cl. 44, the special technical feature with respect to the known common general concept is: at least some of the leads include lead bonds.

Thus the objective problem of claim 44 to be solved can be construed as: providing batch processing on wafer scale.

---

15. claims: 45, 46

Re. cl. 45, the special technical feature with respect to the known common general concept is: at least some of the contacts of each microelectronic element are disposed in a column in a central region of the front surface of the respective microelectronic element.

Thus the objective problem of claim 45 to be solved can be construed as: minimising the warping which may occur between the microelectronic elements and the substrate.

---

16. claim: 47

Re. cl. 47, the special technical feature with respect to the known common general concept is: each of the apertures has a width in a direction transverse to the respective axis, the width of each aperture being not larger than a width of the microelectronic element at least partially overlying the aperture in the same direction as the width of the aperture.

1.2 Thus the objective problem of claim 47 to be solved can be construed as: defining the apertures to ensure that the microelectronic element is still supported by the

International Application No. PCT/ US2012/ 046249

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

substrate.

---

17. claims: 48-51