(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6784609号

(P6784609)

(45) 発行日 令和2年11月11日(2020.11.11)

(24) 登録日 令和2年10月27日(2020.10.27)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO4N 5/369 (2011.01)  | HO4N 5/369    |

| HO4N 5/374 (2011.01)  | HO4N 5/374    |

| HO4N 9/07 (2006.01)   | HO4N 9/07 A   |

| HO1L 27/146 (2006.01) | HO1L 27/146 E |

|                       | HO1L 27/146 D |

請求項の数 15 (全 35 頁)

(21) 出願番号 特願2017-33712 (P2017-33712)

(22) 出願日 平成29年2月24日 (2017.2.24)

(65) 公開番号 特開2018-139375 (P2018-139375A)

(43) 公開日 平成30年9月6日 (2018.9.6)

審査請求日 令和2年1月31日 (2020.1.31)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 笹子 知弥

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置、撮像システム及び移動体

## (57) 【特許請求の範囲】

## 【請求項1】

第1の電極と、第2の電極と、前記第1の電極及び前記第2の電極の間に配された光電変換層と、を各々が含む複数の画素を含む画素アレイであって、

前記複数の画素は、第1のカラーフィルタを有する第1の画素と、前記第1のカラーフィルタとは異なる第2のカラーフィルタを有する第2の画素とを含む、画素アレイと、

前記第1の画素の前記第1の電極と、前記第2の画素の前記第1の電極とに対し電位を供給する電位供給線と、

前記第1の画素の感度の前記光電変換層へのバイアス電圧に対する依存性と、前記第2の画素の感度の前記光電変換層へのバイアス電圧に対する依存性との違いを補償するよう 10 に、前記第1の画素の前記第2の電極と、前記第2の画素の前記第2の電極とに対し、互いに異なる電位を供給可能である、制御線と、

を備え、

前記制御線は、前記第1の画素の感度と前記第2の画素の感度とが所定の比率になるバイアス電圧が前記第1の画素の前記光電変換層と前記第2の画素の前記光電変換層とに印加されるように、前記第1の画素の前記第2の電極と、前記第2の画素の前記第2の電極とに対し、互いに異なる電位を供給する

ことを特徴とする光電変換装置。

## 【請求項2】

第1の電極と、第2の電極と、前記第1の電極及び前記第2の電極の間に配された光電

変換層と、を各々が含む複数の画素を含む画素アレイであって、

前記複数の画素は、第1のカラーフィルタを有する第1の画素と、前記第1のカラーフィルタとは異なる第2のカラーフィルタを有する第2の画素とを含む、画素アレイと、

前記第1の画素の前記第1の電極と、前記第2の画素の前記第1の電極とに対し電位を供給する電位供給線と、

前記第1の画素の感度の前記光電変換層へのバイアス電圧に対する依存性と、前記第2の画素の感度の前記光電変換層へのバイアス電圧に対する依存性との違いを補償するよう、前記第1の画素の前記第2の電極と、前記第2の画素の前記第2の電極とに対し、互いに異なる電位を供給可能である、制御線と、

を備え、

10

第3のバイアス電圧よりも低い第1のバイアス電圧が前記光電変換層に印加される場合、前記第1の画素の感度は前記第2の画素の感度よりも低く、

前記第3のバイアス電圧よりも高い第2のバイアス電圧が前記光電変換層に印加される場合、前記第1の画素の感度は前記第2の画素の感度よりも高く、

前記第3のバイアス電圧が前記光電変換層に印加される場合、前記第1の画素の感度は前記第2の画素の感度と等しく、

前記第1の画素及び前記第2の画素の前記光電変換層に印加されるバイアス電圧が前記第3のバイアス電圧よりも低い場合、前記制御線は、前記第1の画素の前記光電変換層に印加されるバイアス電圧が前記第2の画素の前記光電変換層に印加されるバイアス電圧よりも高くなるように電位を供給し、

20

前記第1の画素及び前記第2の画素の前記光電変換層に印加されるバイアス電圧が前記第3のバイアス電圧よりも高い場合、前記制御線は、前記第1の画素の前記光電変換層に印加されるバイアス電圧が前記第2の画素の前記光電変換層に印加されるバイアス電圧よりも低くなるように電位を供給する

ことを特徴とする光電変換装置。

#### 【請求項3】

前記複数の画素の各々は、

前記第2の電極と接続された入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅部と、

前記制御線と前記入力ノードとの間に接続された画素容量と、

30

を更に含むことを特徴とする請求項1又は2に記載の光電変換装置。

#### 【請求項4】

前記複数の画素は、

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第2のカラーフィルタを有する第3の画素と、

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第1のカラーフィルタ及び前記第2のカラーフィルタのいずれとも異なる第3のカラーフィルタを有する第4の画素と、

を更に含み、

前記第2の画素の前記第2の電極と、前記第3の画素の前記第2の電極とには、共通の前記制御線から同一の電位が供給される

40

ことを特徴とする請求項1乃至3のいずれか1項に記載の光電変換装置。

#### 【請求項5】

前記複数の画素の各々は、

前記第2の電極と接続された入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅部

を更に含み、

前記複数の画素は、

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第2のカラーフィルタを有する第3の画素と、

50

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第1のカラーフィルタ及び前記第2のカラーフィルタのいずれとも異なる第3のカラーフィルタを有する第4の画素と、

を更に含み、

前記制御線は、第1の制御線と第2の制御線とを含み、

前記第1の画素は、前記第1の制御線と前記第1の画素の前記入力ノードとの間に接続された第1の画素容量を更に含み、

前記第2の画素は、前記第1の制御線と前記第2の画素の前記入力ノードとの間に接続された第2の画素容量を更に含み、

前記第3の画素は、前記第2の制御線と前記第3の画素の前記入力ノードとの間に接続された第3の画素容量を更に含み、

前記第4の画素は、前記第2の制御線と前記第4の画素の前記入力ノードとの間に接続された第4の画素容量を更に含み、

前記第1の画素容量の容量値と前記第2の画素容量の容量値とが互いに異なり、かつ、前記第3の画素容量の容量値と前記第4の画素容量の容量値とが互いに異なる

ことを特徴とする請求項1又は2に記載の光電変換装置。

#### 【請求項6】

前記第1の画素は、入射光のうちの赤色の波長成分に応じた信号を出力するR画素であり、

前記第2の画素は、入射光のうちの緑色の波長成分に応じた信号を出力するGr画素であり、

前記第3の画素は、入射光のうちの緑色の波長成分に応じた信号を出力するGb画素であり、

前記第4の画素は、入射光のうちの青色の波長成分に応じた信号を出力するB画素であり、

前記第1の画素、前記第2の画素、前記第3の画素及び前記第4の画素は、ベイヤ配列をなしている

ことを特徴とする請求項4又は5に記載の光電変換装置。

#### 【請求項7】

前記複数の画素の各々は、

前記光電変換層の前記第2の電極が配された側の面に配された第3の電極と、

前記第3の電極と接続された入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する增幅部と、

を更に含むことを特徴とする請求項1又は2に記載の光電変換装置。

#### 【請求項8】

前記複数の画素は、

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第1のカラーフィルタ及び前記第2のカラーフィルタのいずれとも異なる第3のカラーフィルタを有する第4の画素と、

前記第1の電極と、前記第2の電極と、前記光電変換層とを含み、前記第1のカラーフィルタ、前記第2のカラーフィルタ及び前記第3のカラーフィルタをいずれも有しない第5の画素と、

を更に含むことを特徴とする請求項1、2又は7に記載の光電変換装置。

#### 【請求項9】

前記第1の画素は、入射光のうちの赤色の波長成分に応じた信号を出力するR画素であり、

前記第2の画素は、入射光のうちの緑色の波長成分に応じた信号を出力するG画素であり、

前記第4の画素は、入射光のうちの青色の波長成分に応じた信号を出力するB画素であり、

10

20

30

40

50

前記第5の画素は、入射光のうちの赤色から青色の波長成分に応じた信号を出力するW画素である

ことを特徴とする請求項8に記載の光電変換装置。

【請求項10】

前記複数の画素の各々は、

前記第1の電極及び前記光電変換層の間に配されたブロッキング層と、

前記光電変換層及び前記第2の電極の間に配された絶縁層と、

前記第2の電極と接続された入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅部と、

前記制御線と前記入力ノードとの間に接続された画素容量と、

を更に含むことを特徴とする請求項1又は2に記載の光電変換装置。

【請求項11】

前記第1の電極と、前記第2の電極との間の電圧に応じて、前記複数の画素の各々は、

前記光電変換層の残留電荷を排出するリセット動作と、

前記光電変換層に電荷を蓄積する蓄積動作と、

前記蓄積動作において前記光電変換層に蓄積された電荷を前記光電変換層から排出する排出動作と、

を行うよう制御されることを特徴とする請求項10に記載の光電変換装置。

【請求項12】

前記電位供給線は、前記第1の画素の前記第1の電極と、前記第2の画素の前記第1の電極とに対し共通の電位を供給することを特徴とする請求項1乃至11のいずれか1項に記載の光電変換装置。

【請求項13】

前記制御線は、フレームごとに異なる電位を前記第2の電極に供給可能であることを特徴とする請求項1乃至12のいずれか1項の記載の光電変換装置。

【請求項14】

請求項1乃至13のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号を処理する信号処理部と、

を備えることを特徴とする撮像システム。

【請求項15】

移動体であって、

請求項1乃至13のいずれか1項に記載の光電変換装置と、

前記光電変換装置の前記画素から出力される信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、

を備えることを特徴とする移動体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置、撮像システム及び移動体に関する。

【背景技術】

【0002】

カメラのイメージセンサ等に用いられる光電変換装置として、積層型の光電変換装置が提案されている。特許文献1記載の光電変換装置は、光電変換層（光電変換膜）と、光電変換層の上に配された上部電極と、光電変換層の下に配された画素電極及び補助電極を有する。特許文献1には、補助電極の電圧を制御することによって、光電変換層の感度を調整することができる事が記載されている。また、特許文献1には、画素の色に応じて個別に感度調整を行うこともできる旨も記載されている。

【先行技術文献】

【特許文献】

10

20

30

40

50

## 【0003】

【特許文献1】特開2016-86407号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

特許文献1に記載されているような色の異なる画素ごとに感度調整を行うことができる光電変換装置において、より出力信号の精度を向上させるため、感度調整の精度向上が課題となり得る。

## 【0005】

このような課題に鑑み、本発明は、感度調整の精度をより向上させることができない光電変換装置を提供することを目的とする。

10

## 【課題を解決するための手段】

## 【0006】

本発明の1つの側面に係る実施形態の光電変換装置は、第1の電極と、第2の電極と、前記第1の電極及び前記第2の電極の間に配された光電変換層と、を各々が含む複数の画素を含む画素アレイであって、前記複数の画素は、第1のカラーフィルタを有する第1の画素と、前記第1のカラーフィルタとは異なる第2のカラーフィルタを有する第2の画素とを含む、画素アレイと、前記第1の画素の前記第1の電極と、前記第2の画素の前記第1の電極とに対し電位を供給する電位供給線と、前記第1の画素の感度の前記光電変換層へのバイアス電圧に対する依存性と、前記第2の画素の感度の前記光電変換層へのバイアス電圧に対する依存性との違いを補償するように、前記第1の画素の前記第2の電極と、前記第2の画素の前記第2の電極とに対し、互いに異なる電位を供給可能である、制御線とを備え、前記制御線は、前記第1の画素の感度と前記第2の画素の感度とが所定の比率になるバイアス電圧が前記第1の画素の前記光電変換層と前記第2の画素の前記光電変換層とに印加されるように、前記第1の画素の前記第2の電極と、前記第2の画素の前記第2の電極とに対し、互いに異なる電位を供給する。

20

## 【発明の効果】

## 【0007】

本発明によれば、感度調整の精度をより向上させることができる。

30

## 【図面の簡単な説明】

## 【0008】

【図1】本発明の第1実施形態における光電変換装置の画素を模式的に示す図である。

【図2】本発明の第1実施形態における光電変換装置の回路ブロック図である。

【図3】本発明の第1実施形態における列増幅回路の等価回路図である。

【図4】本発明の第1実施形態における光電変換装置の画素の平面構造を模式的に示す図である。

【図5】本発明の第1実施形態における光電変換装置の断面構造を模式的に示す図である。

【図6】本発明の第1実施形態における光電変換部の感度のバイアス電圧依存性を示すグラフである。

40

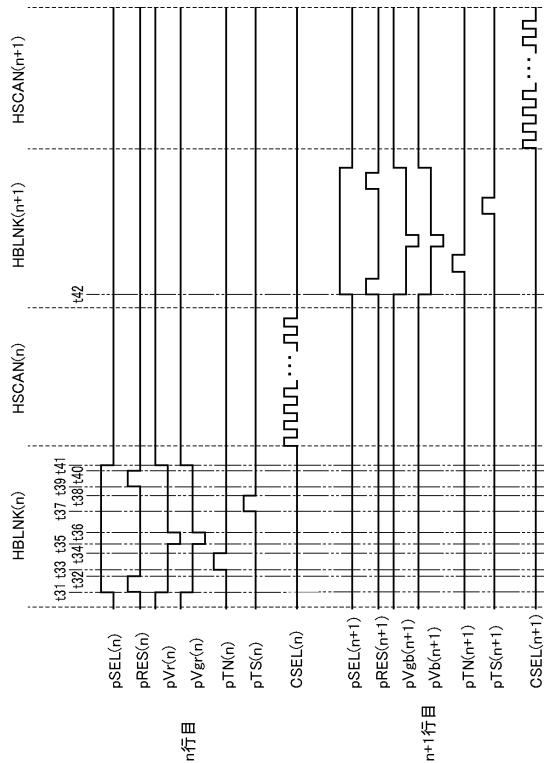

【図7】本発明の第1実施形態における光電変換装置のタイミングチャートである。

【図8】本発明の第2実施形態における光電変換装置の画素の構成を模式的に示す図である。

【図9】本発明の第2実施形態における光電変換装置の画素の平面構造を模式的に示す図である。

【図10】本発明の第2実施形態における光電変換装置のタイミングチャートである。

【図11】本発明の第3実施形態における光電変換装置の画素の平面構造を模式的に示す図である。

【図12】本発明の第3実施形態における光電変換装置の画素を模式的に示す図である。

【図13】本発明の第3実施形態における光電変換装置の画素の平面構造及び断面構造を

50

模式的に示す図である。

【図14】本発明の第3実施形態における光電変換装置の画素の平面構造及び断面構造を模式的に示す図である。

【図15】本発明の第4実施形態における光電変換部の感度のバイアス電圧依存性を示すグラフである。

【図16】本発明の第5実施形態における光電変換装置のタイミングチャートである。

【図17】本発明の第6実施形態における光電変換部の構成を模式的に示す図である。

【図18】本発明の第6実施形態における光電変換部のポテンシャルを模式的に示す図である。

【図19】本発明の第6実施形態における光電変換装置のタイミングチャートである。 10

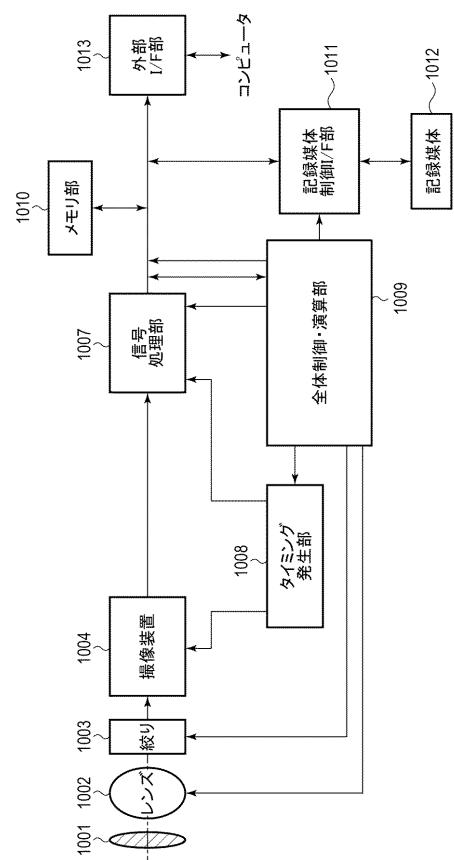

【図20】本発明の第6実施形態における撮像システムのブロック図である。

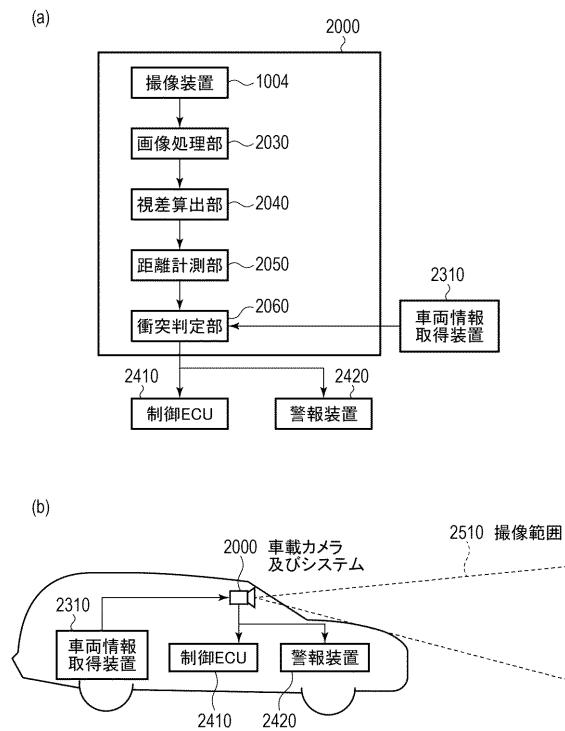

【図21】本発明の第7実施形態における車載カメラに関する撮像システムのブロック図である。

【発明を実施するための形態】

【0009】

本発明の1つの実施形態における光電変換装置は、光電変換層（光電変換膜）を含む。光電変換層に入射した光を電荷に光電変換するように、光電変換層は構成される。なお、光電変換層の全体が光電変換の機能を有している必要はない。半導体基板には、光電変換層で生じた信号電荷に基づく信号を受ける回路部が配される。いくつかの実施形態においては、光電変換装置が複数の画素を含む。これらの実施形態においては、複数の画素に対応して複数の回路部が配される。複数の回路部のそれぞれは、信号を増幅する増幅部を含み得る。いくつかの実施形態においては、光電変換層で生じる信号電荷は電子とするが、ホールを信号電荷とする構成であってもよく、同様の効果が得られる。 20

【0010】

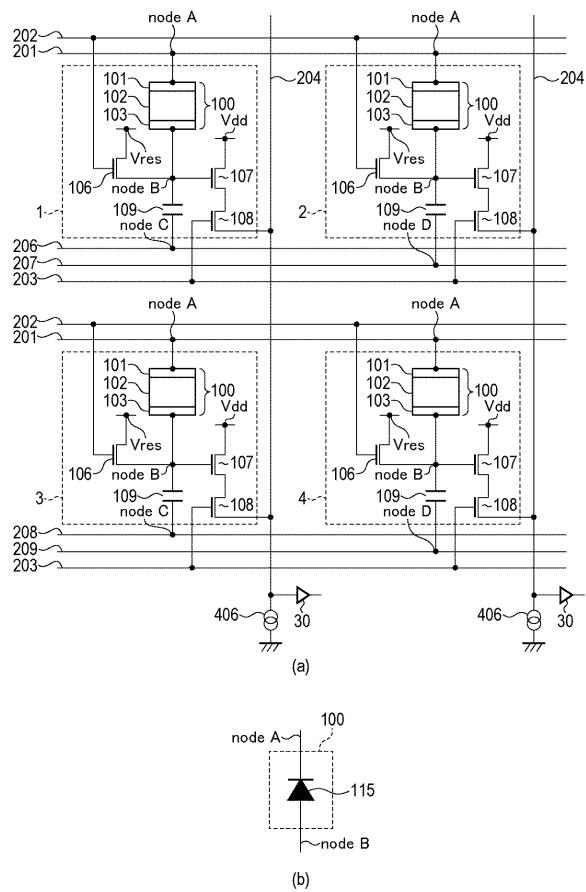

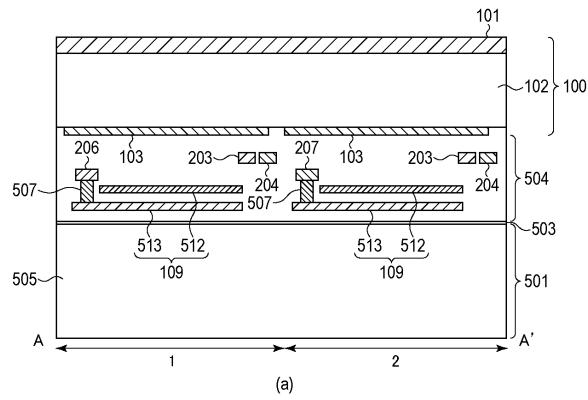

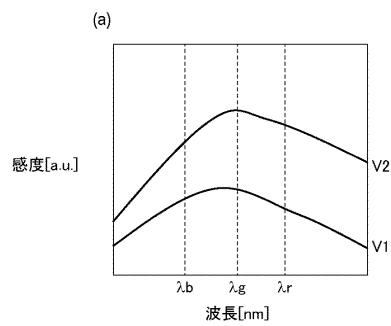

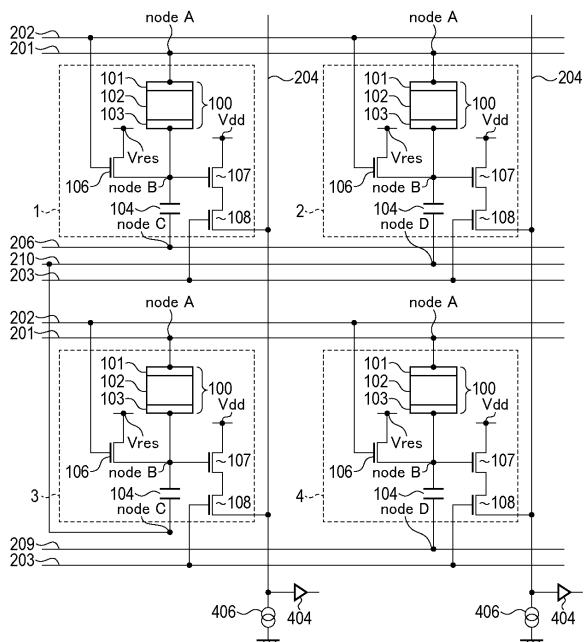

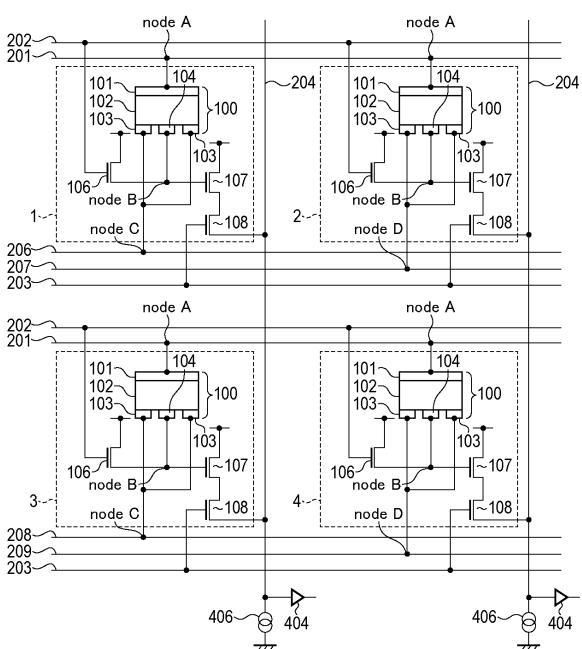

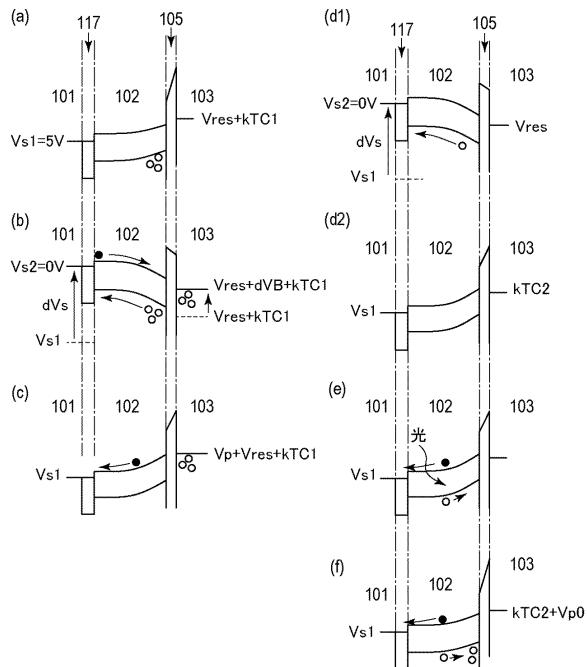

図1(a)には、本発明の1つの実施形態における光電変換装置のR画素1(第1の画素)、Gr画素2(第2の画素)、Gb画素3(第3の画素)、B画素4(第4の画素)の構成が模式的に示されている。図5(a)には、光電変換装置のR画素1、Gr画素2の断面構造が模式的に示されている。図6(a)には、分光感度特性のバイアス電圧依存性が示されている。

【0011】

図5(a)において、半導体基板501の上には第1の電極101が配される。第1の電極101と半導体基板501との間には第2の電極103が配される。第1の電極101と第2の電極103との間には、光電変換層102が配される。 30

【0012】

図1(a)において、R画素1には、第2の電極103に電位を供給する制御線206が接続される。また、Gr画素2には、第2の電極103に電位を供給する制御線207が接続される。Gb画素3には、第2の電極103に電位を供給する制御線208が接続される。B画素4には、第2の電極103に電位を供給する制御線209が接続される。

【0013】

本発明の1つの実施形態においては、図6(a)及び図6(b)に示されるような、各画素の感度のバイアス電圧依存性の違いを補償するように、各画素の第2の電極103に互いに異なる電位を供給可能である。 40

【0014】

[第1実施形態]

<画素の構成>

図1(a)は、本実施形態における光電変換装置のR画素1、Gr画素2、Gb画素3及びB画素4の構成を模式的に示し、図1(b)は光電変換部100の等価回路を示している。図1(a)には、行方向及び列方向に配列される複数の画素で構成される画素アレイの配列のうち、ベイヤ配列の一単位である4つの画素が例示されている。R画素1は、主として入射光のうちの赤色の波長成分に応じた信号を生成して出力する画素である。G 50

r 画素 2 及び G b 画素 3 は、主として入射光のうちの緑色の波長成分に応じた信号を生成して出力する画素である。B 画素 4 は、主として入射光のうちの青色の波長成分に応じた信号を生成して出力する画素である。

【 0 0 1 5 】

また、図 1 ( a ) には、電位供給線 2 0 1 、リセット信号線 2 0 2 、駆動信号線 2 0 3 、列信号線 2 0 4 、制御線 2 0 6 、2 0 7 、2 0 8 、2 0 9 の配置が図示されている。電位供給線 2 0 1 、リセット信号線 2 0 2 、駆動信号線 2 0 3 、制御線 2 0 6 、2 0 7 、2 0 8 、2 0 9 は、画素アレイの行ごとに設けられている。列信号線 2 0 4 は、画素アレイの列ごとに設けられている。列信号線 2 0 4 には、電流源 4 0 6 及び列増幅回路 3 0 が接続されている。

10

【 0 0 1 6 】

各画素は、光電変換部 1 0 0 、リセットトランジスタ 1 0 6 、増幅トランジスタ 1 0 7 、選択トランジスタ 1 0 8 を含む。各トランジスタは、M O S ( Metal Oxide Semiconductor ) トランジスタによって構成される。光電変換部 1 0 0 は、第 1 の電極 ( 共通電極 ) 1 0 1 、光電変換層 1 0 2 、第 2 の電極 ( 画素電極 ) 1 0 3 を含む。図 1 ( a ) はベイヤ配列をなす R 画素 1 、G r 画素 2 、G b 画素 3 及び B 画素 4 を示しているが、本実施形態の光電変換装置は、ベイヤ配列を用いたものに限定されない。

【 0 0 1 7 】

光電変換部 1 0 0 は、ノード ( node ) A に接続された第 1 の端子、及び、ノード B に接続された第 2 の端子を有するダイオード 1 1 5 ( フォトダイオード ) を形成する。ノード A には、電位供給線 2 0 1 を介して後述の電圧制御部 4 0 1 等の電圧源から電位 V s が供給される。

20

【 0 0 1 8 】

ノード B は、増幅トランジスタ 1 0 7 のゲート、リセットトランジスタ 1 0 6 のソース、及び画素容量 1 0 9 の一端に接続される。R 画素 1 において、画素容量 1 0 9 の他端であるノード C は制御線 2 0 6 に接続される。G r 画素 2 において、画素容量 1 0 9 の他端であるノード D は制御線 2 0 7 に接続される。G b 画素 3 において、画素容量 1 0 9 の他端であるノード C は制御線 2 0 8 に接続される。B 画素 4 において、画素容量 1 0 9 の他端であるノード D は制御線 2 0 9 に接続される。制御線 2 0 6 、2 0 7 、2 0 8 、2 0 9 は、電圧制御部 4 0 1 に接続されており、個別に第 2 の電極 1 0 3 の電位を制御することができる。

30

【 0 0 1 9 】

リセットトランジスタ 1 0 6 のドレインはリセット電位 V r e s が供給されているリセット電位線に接続される。リセット電位 V r e s は、例えば、3 . 3 V とすることができる。増幅トランジスタ 1 0 7 のゲートは、増幅トランジスタ 1 0 7 、電流源 4 0 6 等により構成される増幅部の入力ノードである。このように、増幅部は、光電変換部 1 0 0 で生じた電荷を受ける入力ノードを有し、入力ノードの電荷に応じた信号を出力することができる。また、言い換えると、本実施形態では、光電変換によって生じた電荷に基づく信号を受ける回路部が増幅部を含んでいる。

【 0 0 2 0 】

40

増幅トランジスタ 1 0 7 のドレインは、電源電位 V d d が供給されている電源電位線に接続される。電源電位 V d d は、例えば、リセット電位 V r e s と同様の 3 . 3 V とすることができる。この場合、1 つの電源線が電源電位線及びリセット電位線を兼ねることもできる。増幅トランジスタ 1 0 7 のソースは、選択トランジスタ 1 0 8 を介して、列信号線 2 0 4 に接続される。選択トランジスタ 1 0 8 のゲートには、行ごとに設けられた駆動信号線 2 0 3 を介して駆動信号が入力され、選択トランジスタ 1 0 8 は、接続状態又は非接続状態に制御される。列信号線 2 0 4 には、電流源 4 0 6 が接続される。増幅トランジスタ 1 0 7 及び電流源 4 0 6 はソースフォロワ回路を構成し、光電変換部 1 0 0 で生じた電荷に基づく信号を列信号線 2 0 4 に出力する。列信号線 2 0 4 には、更に列増幅回路 3 0 が接続される。列信号線 2 0 4 に出力された画素からの信号は、列増幅回路 3 0 に入力

50

される。

【0021】

本実施形態の光電変換装置においては、ベイヤ配列をなすR画素1、Gr画素2、Gb画素3、B画素4のそれぞれに対し第2の電極103の電位を供給する制御線206、207、208、209が設けられている。これにより、R画素1、Gr画素2、Gb画素3、B画素4のそれぞれの第2の電極103の電位に対し互いに異なる電位を供給可能である。

【0022】

＜撮像装置の構成＞

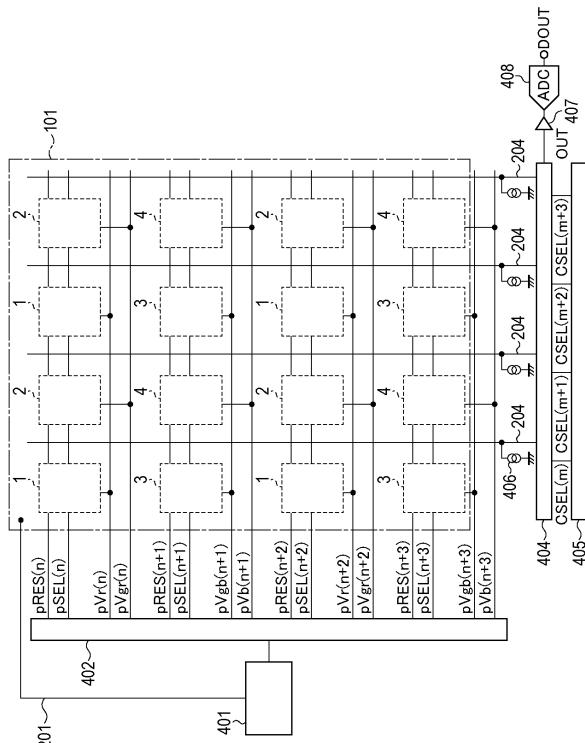

図2は、本実施形態の光電変換装置の回路ブロック図である。図1と同じ機能を有する部分には、同じ符号が付されている。光電変換装置は、R画素1、Gr画素2、Gb画素3、B画素4を一単位として行方向及び列方向に沿って二次元行列状に配置された画素アレイを備える。更に、光電変換装置は、電圧制御部401、行駆動回路402、列回路404、列駆動回路405、出力回路407及びアナログ-デジタル変換回路(ADC)408を備える。

10

【0023】

図2には、ベイヤ配列に従って4行4列の行列状に配された16個の画素が示されているが、画素の個数は限定されない。各列に含まれる複数の画素は、1つの列信号線204に接続される。なお、本明細書において、行方向とは図面における水平方向を示し、列方向とは図面において垂直方向を示すものとする。画素上にはマイクロレンズ及びカラーフィルタが配置され得る。本実施形態では、カラーフィルタは赤、緑、青の原色フィルタであって、ベイヤ配列に従って各画素に設けられている。言い換えると、R画素1は、赤色の原色フィルタ(第1のカラーフィルタ)が配置された画素である。同様に、Gr画素2及びGb画素3(これらをG画素と総称することもある)は、緑色の原色フィルタ(第2のカラーフィルタ)が配置された画素であり、B画素4は、青色の原色フィルタ(第3のカラーフィルタ)が配置された画素である。カラーフィルタを設けることにより、各画素は、赤、緑、青等の色を示す所定の波長帯域を高感度波長帯域とする分光感度特性を有する。言い換えると、R画素、G画素、B画素は、分光感度特性の高感度波長帯域が互いに異なる。なお、カラーフィルタの色は上述の色、すなわち赤、緑、青の原色に限定されるものではなく、その他の色であってもよい。

20

【0024】

また、画素アレイに配置される画素は、OB画素(オプティカル・ブラック画素)を更に含んでもよい。OB画素は、遮光されている画素であり黒レベルの検出に用いられる。また、測距の機能が要求される場合には、画素アレイには、焦点検出用の信号を出力する焦点検出画素が配された測距行と、画像を生成するための信号を出力する撮像画素が配された複数の撮像行とが設けられていてもよい。

30

【0025】

行駆動回路402は、駆動信号pRES、pSEL、制御信号pVr、pVgr、pVgb、pVbを供給する。駆動信号pSEL、pRES、制御信号pVr、pVgr、pVgb、pVbをそれぞれ伝達するリセット信号線202、駆動信号線203及び制御線206、207、208、209は、行ごとに共通に設けられている。なお、図2では、異なる行に供給される駆動信号を区別するために、(n)、(n+1)等の行を表す符号を付している。

40

【0026】

行駆動回路402は、リセット信号線202を介して、各画素のリセットトランジスタ106のゲートに駆動信号pRESを供給する。駆動信号pRESに応じて、各画素内のノードBがリセット電位Vresにリセットされる。また、行駆動回路402は、駆動信号線203を介して、各画素内の選択トランジスタ108のゲートに駆動信号pSELを供給する。駆動信号にpSELに応じて、選択トランジスタ108が接続状態又は非接続状態に制御される。

50

## 【0027】

行駆動回路402は、制御線206を介して、R画素1の画素容量109に制御信号pVrを供給し、制御線207を介して、Gr画素2の画素容量109に制御信号pVgrを供給する。また、行駆動回路402は、制御線208を介して、Gb画素3の画素容量109に制御信号pVgbを供給し、制御線209を介して、B画素4の画素容量109に制御信号pVbを供給する。制御信号pVr、pVgr、pVgb、pVbの電位に応じて、各画素のノードB、すなわち、第2の電極103の電位が個別に制御される。

## 【0028】

行駆動回路402は不図示のタイミングジェネレータによって制御される。電圧制御部401は定電圧回路、バッファ回路、デジタル-アナログ変換回路等から構成され、制御信号pVr、pVgr、pVgb、pVbを生成するための複数の異なる電位を生成し、行駆動回路402に供給する。なお、電圧制御部401は、光電変換装置内ではなく、光電変換装置が搭載される外部の装置（例えば、撮像システム）に設けられていてもよい。

## 【0029】

第1の電極101は、光電変換部100の第1の端子（図1のノードA）を構成する。図2に示されるように、複数の画素の光電変換部100の第1の端子は、共通の第1の電極101によって構成される。第1の電極101には、電位供給線201を介して電位Vsが供給される。第1の電極101に供給される電位と第2の電極103の供給される電位との差が光電変換層102に印加されるバイアス電圧Vbiasとなる。

## 【0030】

列回路404は、各列の列増幅回路30を含み、列増幅回路30は列信号線204に接続される。列駆動回路405は、列回路404を列ごとに駆動する。列信号線204には画素の増幅トランジスタ107の負荷となる電流源406が接続されている。列増幅回路30は列信号線204に出力された信号を増幅するとともに保持する。列駆動回路405はシフトレジスタ等から構成され、第m列の列増幅回路30に駆動信号CSEL(m)を供給している。なお、図2では、異なる列に供給される駆動信号を区別するために、(m)、(m+1)等の列を表す符号を付している。出回路407はクランプ回路、差動増幅回路、バッファ回路等から構成され、入力された信号をアナログ-デジタル変換回路408に出力する。アナログ-デジタル変換回路408はランプ信号発生回路、差動増幅回路等から構成され、入力された信号をデジタルデータに変換し、出力端子DOUTから出力する。このような構成により、行ごとに並列に読み出された信号を、順次、出力することができる。

## 【0031】

図3は、本実施形態における列増幅回路30の等価回路であって、m列目及びm+1列目の列増幅回路30を示している。列回路404の他の列増幅回路30は図示されていないが、同様の構成を有している。列増幅回路30は増幅器301、サンプル・アンド・ホールド(S/H)スイッチ303、305、水平転送スイッチ307、309、容量CTS1、CTN1を備える。増幅器301の入力ノードには列信号線204が接続され、増幅器301は列信号線204から入力された信号を増幅する。増幅器301の出力ノードは、S/Hスイッチ303を介して容量CTS1に接続されている。また、増幅器301の出力ノードは、S/Hスイッチ305を介して容量CTN1に接続されている。S/Hスイッチ303、305は、それぞれ、駆動信号pTS、pTNによって制御される。S/Hスイッチ305がオンとなることで、画素からの増幅トランジスタ107の閾値ばらつきを含む信号Nが容量CTN1に保持される。また、S/Hスイッチ303がオンとなることで、光信号と閾値ばらつきを含む信号Sが容量CTS1に保持される。

## 【0032】

容量CTS1は、水平転送スイッチ307を介して水平出力線311に接続されている。容量CTN1は、水平転送スイッチ309を介して水平出力線313に接続されている。水平転送スイッチ307、309は、列駆動回路405からの駆動信号CSELによって制御される。水平転送スイッチ307がオンとなることで、信号Sが容量CTS1から

10

20

30

40

50

水平出力線 311 に出力され、容量 CTS2 に保持される。水平転送スイッチ 309 がオンとなることで、信号 N が容量 CTN1 から水平出力線 313 に出力され、容量 CTN2 に保持される。

#### 【0033】

水平出力線 311 と水平出力線 313 とは出力回路 407 に接続されている。出力回路 407 は、水平出力線 311 の信号 S と水平出力線 313 の信号 N との差分をアナログ - デジタル変換回路 408 に出力する。信号 S と信号 N の差分をとることで、増幅トランジスタ 107 の閾値ばらつきを除去することができる。アナログ - デジタル変換回路 408 は、入力されたアナログ信号をデジタル信号に変換する。

#### 【0034】

なお、列増幅回路 30 はアナログ - デジタル変換回路を含んでもよい。この場合、アナログ - デジタル変換回路は、メモリ、カウンタ等のデジタル信号を保持する保持部を有する。信号 S と信号 N とがそれぞれデジタル信号に変換され、保持部に保持される。デジタル信号に変換された信号 S と信号 N との差分を演算することで閾値ばらつき等のノイズ成分が除去された信号を得ることができる。

#### 【0035】

＜光電変換装置の平面構造・断面構造＞

次に、本実施形態の光電変換装置の平面構造、断面構造を説明する。

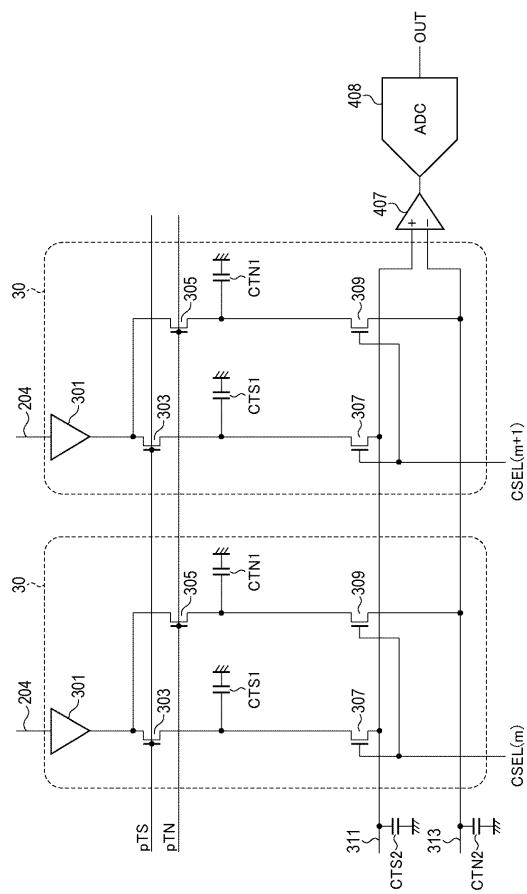

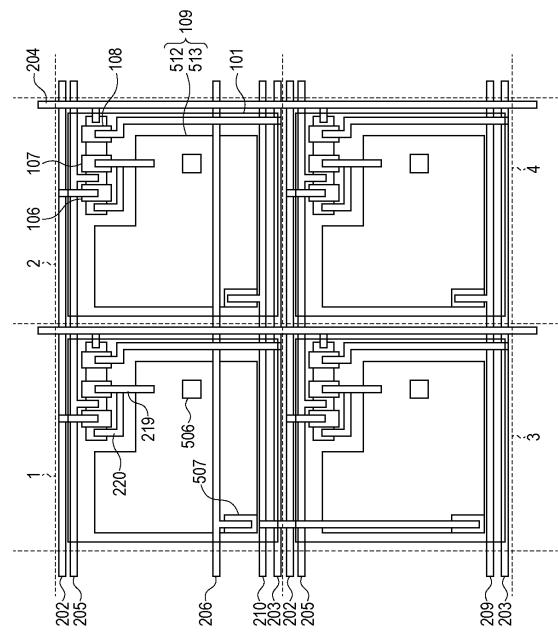

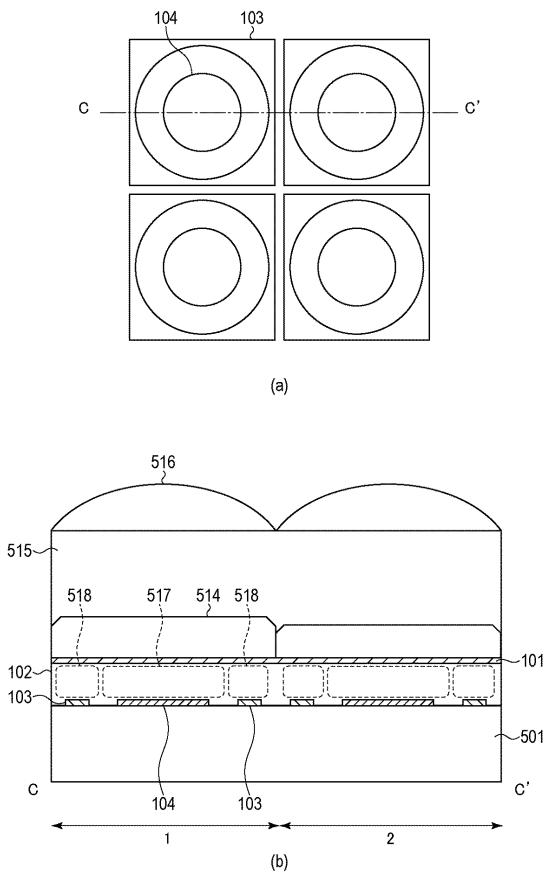

#### 【0036】

図 4 は、2 行 2 列の行列状に配された R 画素 1、Gr 画素 2、Gb 画素 3 及び B 画素 4 の平面構造を模式的に示している。その他の画素も同様に構成されている。図 4 では画素を構成する構造のうち下層から第 2 の電極 103 までが図示されており、第 2 の電極 103 よりも上部に積層される構造は図示を省略している。なお、図 4 及び後述する図 5 において、図 1、図 2 と同じ機能を有する部分には同じ符号が付されている。また、トランジスタについては対応するゲート電極に符号が付されている。

#### 【0037】

各画素には第 2 の電極 103 が配され、各画素の右上角部にはリセットトランジスタ 106、増幅トランジスタ 107 及び選択トランジスタ 108 が配されている。リセットトランジスタ 106 及び増幅トランジスタ 107 のドレインには、電源電位 Vdd 及びリセット電位 Vres を供給する電源線 205 が接続されている。各画素の右上角部を除く部分には上部電極 512 及び下部電極 513 により構成される画素容量 109 が配されている。下部電極 513 と各制御線はコンタクトプラグ 507 で接続されている。上部電極 512 と接続線 219、220 はコンタクトプラグ 506 で接続されている。接続線 219、220 は上部電極 512 とノード B とを接続する配線である。なお、画素内の素子配置及び各素子の形状は図 4 に示されたものに限定されず、様々な構成を採用し得る。

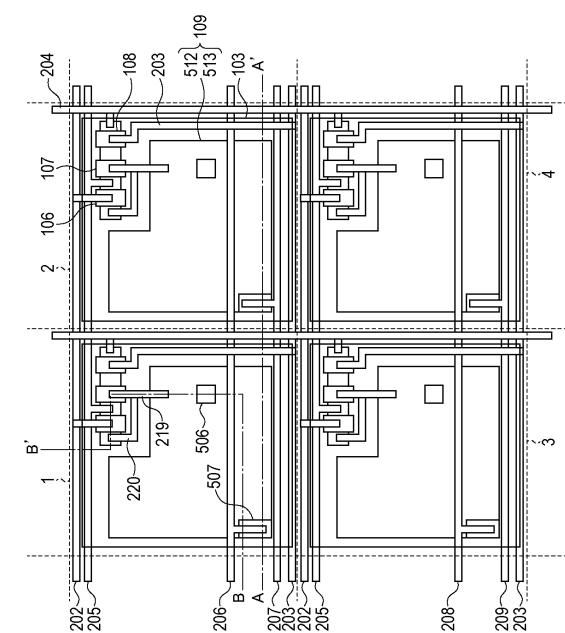

#### 【0038】

図 5 (a) は、図 4 の一点鎖線 A - A' に沿った光電変換装置の断面構造を模式的に示している。図 5 (b) は、図 4 の一点鎖線 B - B' に沿った光電変換装置の断面構造を模式的に示している。図 5 (a) 及び図 5 (b) では光電変換部 100 の構成図示されている。

#### 【0039】

図 4、図 5 (a) 及び図 5 (b) を参照しつつ、光電変換装置の構成をより詳細に説明する。光電変換装置は、シリコン基板等の半導体基板 501 を含む。半導体基板 501 には、リセットトランジスタ 106、増幅トランジスタ 107 及び選択トランジスタ 108 のソース及びドレインをなす、不純物半導体領域（不純物拡散部）502 が配される。半導体基板 501 の上には、シリコン酸化膜等からなるゲート絶縁膜 503 を間に介してポリシリコン等からなるゲート電極が形成されている。その上には、アルミニウム、銅、タンゲステン、ポリシリコン等の導電部材を含む配線層 504 が配される。配線層 504 は複数の層を含む。配線層 504 の上には、光電変換部 100 が配されている。

#### 【0040】

10

20

30

40

50

半導体基板 501 の上には、第 1 の電極 101 が配される。第 1 の電極 101 と半導体基板 501 との間には第 2 の電極 103 が配される。第 1 の電極 101 と第 2 の電極 103 との間には光電変換層 102 が配される。第 2 の電極 103 はコンタクトプラグ 506、接続線 219 等を介して、増幅トランジスタ 107 のゲート電極に接続される。

【0041】

図 1 (a)、図 5 (a) 及び図 5 (b) に示されるように、各画素の光電変換部 100 は、第 1 の電極 (共通電極) 101 と、光電変換層 102 と、第 2 の電極 (画素電極) 103 とを少なくとも含む。

【0042】

第 1 の電極 101 は、図 2 及び、図 5 (a) に示されるように、複数の画素に渡って共通の導電部材で構成される。そのため、第 1 の電極 101 は共通電極とも称される。これにより、電位供給線 201 から、R 画素 1、G r 画素 2、G b 画素 3、B 画素 4 に共通に設けられる第 1 の電極 101 に対し、共通の電位が供給される。 10

【0043】

各画素の第 2 の電極 103 は、他の画素の第 2 の電極から電気的に絶縁されている。言い換えると、複数の画素のそれぞれに対して個別に第 2 の電極が設けられている。そのため、第 2 の電極は画素電極とも称される。また、光電変換層 102 は、複数の画素に渡って連続して配されている。

【0044】

図 4、図 5 (a) 及び図 5 (b) に示されるように、画素容量 109 は、上部電極 512 と下部電極 513 とを含む。上部電極 512 及び下部電極 513 は、間に絶縁体を介して互いに対向している。この構造では、フォトリソグラフィー等の半導体プロセスを用いることにより、上部電極 512 及び下部電極 513 の平面形状を自由に構成できるため、画素容量 109 の容量値の設計自由度を高くすることができる。なお、上部電極 512 と下部電極 513 とを含む構成以外の構造を画素容量 109 に用いてもよい。他の例としては、P N 接合容量であってもよい。 20

【0045】

また、画素容量 109 の上部電極 512 及び下部電極 513 は、光電変換部 100 の第 2 の電極 103 よりも下の配線層に配されている。上部電極 512 及び下部電極 513 は、平面視において、第 1 の電極 101 又は第 2 の電極 103 と少なくとも部分的に重なっている。このような構成によれば、画素のサイズを小さくすることができる。また、上部電極 512 及び下部電極 513 は、それぞれ、リセットトランジスタ 106 及び増幅トランジスタ 107 のいずれとも重なっていない部分を含んでいる。 30

【0046】

本実施形態の画素容量 109 は、例えば、M I M (Metal Insulator Metal) 容量である。この場合、上部電極 512 と下部電極 513 は、それぞれ、金属によって構成される。あるいは、画素容量 109 は、P I P (Poly-Si Insulator Poly-Si) 容量であってもよい。この場合、上部電極 512 と下部電極 513 は、それぞれ、ポリシリコンによって構成される。あるいは、画素容量 109 は、M O S (Metal Oxide Semiconductor) 容量であってもよい。この場合、上部電極 512 が金属又は高濃度にドープされたポリシリコン等の金属的な性質を示す導電部材で構成され、下部電極 513 が半導体領域で構成される。 40

【0047】

R 画素 1 において、画素容量 109 の下部電極 513 は、コンタクトプラグ 507 を介して制御線 206 に接続されている。G r 画素 2 において、画素容量 109 の下部電極 513 は、コンタクトプラグ 507 を介して制御線 207 に接続されている。G b 画素 3 において、画素容量 109 の下部電極 513 は、コンタクトプラグ 507 を介して制御線 208 に接続されている。B 画素 4 において、画素容量 109 の下部電極 513 は、コンタクトプラグ 507 を介して制御線 209 に接続されている。制御線 206 は、行駆動回路 402 からの制御信号 p V r に基づく電位を供給する。制御線 207 は、行駆動回路 40 50

2からの制御信号 p V g r に基づく電位を供給する。制御線 208 は、行駆動回路 402 からの制御信号 p V g b に基づく電位を供給する。制御線 209 は、行駆動回路 402 からの制御信号 p V b に基づく電位を供給する。制御線 206 は、画素アレイ内の各行の R 画素 1 ごとに配され、他の画素の制御線とは絶縁されている。制御線 207 は、画素アレイ内の各行の G r 画素 2 ごとに配され、他の画素の制御線とは絶縁されている。制御線 208 は、画素アレイ内の各行の G b 画素 3 ごとに配され、他の画素の制御線とは絶縁されている。制御線 209 は、画素アレイ内の各行の B 画素 4 ごとに配され、他の画素の制御線とは絶縁されている。このような構成により、R 画素 1、G r 画素 2、G b 画素 3 及び B 画素 4 のそれぞれに対し独立して画素容量 109 の第 2 の端子（ノード C 又はノード D）の電位を制御することができる。

10

#### 【0048】

第 1 の電極 101 は、光の透過率が高い導電部材、例えば、ITO (Indium Tin Oxide) 等のインジウム又はスズを含む化合物、ZnO 等の化合物等から構成され得る。このような構成によれば、多くの光を光電変換層 102 に入射させることができ、光電変換部 100 の感度を向上させることができる。なお、光を透過し得るように薄く形成されたポリシリコン又は金属を、第 1 の電極 101 として用いてもよい。金属の電気抵抗は低いため、金属を第 1 の電極 101 の材料に用いた場合、更なる低消費電力化及び高速化を実現し得る。

#### 【0049】

光電変換層 102 は、光電変換層 102 に入射した光を電荷に光電変換する。光電変換層 102 の少なくとも一部が、光電変換の機能を有していればよい。光電変換層 102 は、真性のアモルファスシリコン（以下、a-Si とも称する）、低濃度の P 型の a-Si、低濃度の N 型の a-Si 等の半導体材料で形成され得る。あるいは、光電変換層 102 は、化合物半導体材料で形成されてもよい。例えば、BN、GaAs、GaP、AlSb、GaAlAsP 等の II - V 族化合物半導体、CdSe、ZnS、HgTe 等の II - VI 族化合物半導体、PbS、PbTe、CuO 等の IV - VI 族化合物半導体が挙げられる。あるいは、光電変換層 102 は、有機半導体材料で形成されてもよい。例えば、フラー-レン、クマリン 6 (C6)、ローダミン 6 G (R6G)、亜鉛フタロシアニン (ZnPc)、キナクリドン、フタロシアニン系化合物、ナフタロシアニン系化合物等を用いることができる。更に、上述の半導体材料で構成された量子ドットを含む層を光電変換層 102 に用いることができる。量子ドットは、20.0 nm 以下の粒径を有する粒子であることが望ましい。

20

#### 【0050】

光電変換層 102 が半導体材料で構成される場合、当該半導体材料は低濃度の不純物でドープされ、あるいは、当該半導体材料は真性半導体であることが望ましい。このような構成によれば、光電変換層 102 に空乏層を十分に広げることができため、高感度化、ノイズ低減等の効果を得ることができる。

30

#### 【0051】

第 2 の電極 103 は金属等の導電部材から構成される。第 2 の電極 103 には、配線を構成する導電部材、あるいは、外部と接続するためのパッド電極を構成する導電部材と同じ材料が用いられ得る。例えば、Al、Cu、TiN 等の材料を適宜用いることができる。このような構成によれば、第 2 の電極 103 と、配線を構成する導電部材、あるいは、パッド電極とを同時に形成することができる。したがって、製造プロセスを簡略化することができる。

40

#### 【0052】

<分光感度特性とバイアス電圧の関係>

図 6 (a) は、光電変換層 102 に印加されるバイアス電圧 Vbias が V1 の場合と V2 (V2 > V1) の場合の分光感度特性の一例を示すグラフである。図 6 (a) において、縦軸は光電変換部 100 の入射光に対する感度を示しており、横軸は入射光の波長を示している。ここで、分光感度特性とは、波長に対する感度の依存性を意味する。なお、

50

図6(a)に示す感度は、カラーフィルタの波長選択性による影響を考慮しない、光電変換層102自体の感度である。光電変換層の分光感度特性は、図6(a)に示されるように、光電変換層102に印加するバイアス電圧Vbiasに応じて変化する場合がある。波長b(例えば、青色の光である波長450nm)、波長g(例えば、緑色の光である波長550nm)、波長r(例えば、赤色の光である波長650nm)の3点を比較する。図6(a)に示される例では、波長が長いほど、バイアス電圧Vbiasの変化による感度の変化率が大きいため、バイアス電圧Vbiasを大きくすると長波長の光がより高感度で光電変換される。そのため、バイアス電圧Vbiasの違いにより色のバランスの変化が生じ得ることがわかる。特に、光電変換層に有機半導体を用いた場合には、この変化が顕著になり得る。

10

#### 【0053】

図6(b)は、主に波長rに感度を持つR画素、主に波長gに感度を持つG画素(Gr画素及びGb画素)、主に波長bに感度を持つB画素についての、感度とバイアス電圧Vbiasの依存性を示すグラフである。バイアス電圧がV1のときのR画素、G画素、B画素の感度をそれぞれSr1、Sg1、Sb1とする。また、バイアス電圧がV2のときのR画素、G画素、B画素の感度をそれぞれSr2、Sg2、Sb2とする。図6(b)より理解されるように、Sb1:Sb2の比の値、Sg1:Sg2の比の値、Sr1:Sr2の比の値はそれぞれ異なっている。このことより、バイアス電圧の変化に対する感度の変化の比率は、波長によって異なるといえる。これを言い換えると、Sr1:Sg1:Sb1の比を色比1、Sr2:Sg2:Sb2の比を色比2とした場合、分光感度特性がバイアス電圧に依存することにより、色比1と色比2は異なる値となる。したがって、この色比の調整を行わない場合には、感度調整の精度が不十分となる場合がある。

20

#### 【0054】

上述のように本実施形態では、R画素1、Gr画素2、Gb画素3及びB画素4のそれに対し独立して異なるバイアス電圧を供給することが可能である。そして、分光感度特性のバイアス電圧に対する依存性を考慮して、各画素の光電変換部100に印加されるバイアス電圧Vbiasを調整することにより、色比を一定とする調整が可能となっている。そのため、分光感度特性のバイアス電圧依存性の影響を低減することができ、感度調整の精度をより向上させることができる。

30

#### 【0055】

色比の調整について一例を挙げて説明する。調整後の目標とするR画素、G画素、B画素の感度がそれぞれa、b、cであるものとする。また、分光感度特性のバイアス電圧依存性が既知であり、R画素、G画素、B画素の感度のバイアス電圧依存性が、関数Sr(V)、Sg(V)、Sb(V)で表されているものとする。このとき、R画素、G画素、B画素に対するバイアス電圧Vr、Vg、Vbを、それぞれ、 $Vr = Sr^{-1}(a)$ 、 $Vg = Sg^{-1}(b)$ 、 $Vb = Sb^{-1}(c)$ と設定すれば、所望の感度を与えるバイアス電圧を設定することができる。そして、この感度調整をa:b:cの比が一定となる制約条件のもとで行うことにより色比を一定とするバイアス電圧の調整が可能となる。しかしながら、色比の調整方法はこれに限られるものではなく、分光感度特性のバイアス電圧に対する依存性が考慮されていれば他の手法を用いることもできる。

40

#### 【0056】

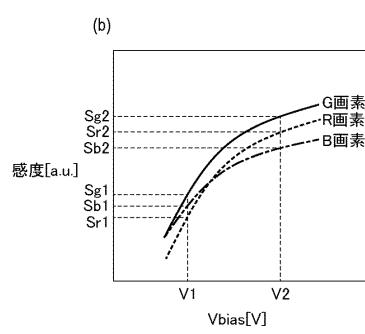

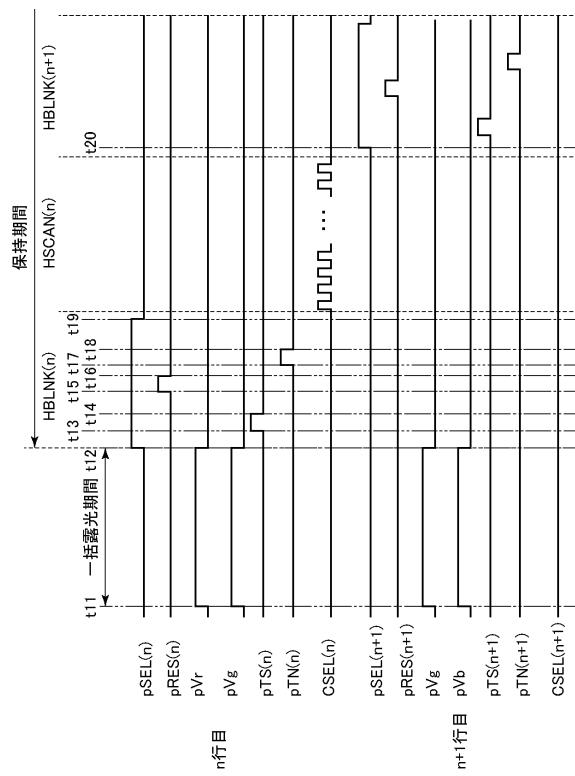

##### <光電変換装置の駆動方法>

次に、本実施形態による光電変換装置の駆動方法について説明する。図7は、本実施形態の光電変換装置に用いられるローリングシャッター動作時の駆動信号のタイミングチャートを示している。図7には、n行目とn+1行目の2行分の信号の読み出し動作に対応した駆動信号が示されている。

#### 【0057】

駆動信号pSEL、pTN、pTS、CSEL、pRESがハイレベルのときに、対応するトランジスタ又はスイッチがオン状態になる。また、駆動信号pSEL、pTN、pTS、CSEL、pRESがローレベルのときに、対応するトランジスタ又はスイッチが

50

オフ状態になる。

【0058】

本実施形態の光電変換装置の駆動では、いわゆるローリングシャッター動作が行われる。時刻  $t_1$  より前において、 $n$  行目の画素の光電変換部 100、及び、 $n+1$  行目の画素の光電変換部 100 は信号電荷を蓄積している状態である。信号電荷の蓄積時には、制御信号  $pVr(n)$ 、 $pVgr(n)$ 、 $pVgb(n+1)$ 、 $pVb(n+1)$  はハイレベルであり、感度調整がオンの状態である。

【0059】

まず、 $n$  行目の画素からの読み出しを行う期間  $HBLNK(n)$  の動作について説明する。時刻  $t_1$  において、駆動信号  $pSEL(n)$  がハイレベルになり、 $n$  行目の画素の選択トランジスタ 108 がオンになる。これにより、 $n$  行目の画素の増幅トランジスタ 107 から、ノード B に蓄積された光信号と増幅トランジスタ 107 の閾値ばらつきによるノイズ信号とを含む信号 S が列信号線 204 に出力される。また、時刻  $t_1$  において、制御信号  $pVr(n)$ 、 $pVgr(n)$  がローレベルになり、感度調整がオフの状態になる。

10

【0060】

時刻  $t_2$  において、駆動信号  $pT S(n)$  がハイレベルになり、増幅器 301 によって増幅された信号 S が、容量  $CTS1$  に出力される。時刻  $t_3$  において、駆動信号  $pT S(n)$  がローレベルになった後においても、信号 S が容量  $CTS1$  に保持される。

【0061】

時刻  $t_4$  において、駆動信号  $pRES(n)$  がハイレベルになり、 $n$  行目の画素のリセットトランジスタ 106 がオンになる。これにより  $n$  行目の画素のノード B の電位がリセット電位  $Vres$  に応じた電位にリセットされる。その後、時刻  $t_5$  において、駆動信号  $pRES(n)$  がローレベルになり、リセットトランジスタ 106 はオフになる。このとき、増幅トランジスタ 107 は閾値ばらつきによるノイズを含む信号 N を選択トランジスタ 108 を介して列信号線 204 に出力する。

20

【0062】

時刻  $t_6$  において、駆動信号  $pTN(n)$  が、ハイレベルになり、信号 N が、列回路 404 の容量  $CTN1$  に出力される。時刻  $t_7$  において、駆動信号  $pTN(n)$  がローレベルになり、信号 N が容量  $CTN1$  に保持される。

【0063】

30

時刻  $t_8$  において、駆動信号  $pSEL(n)$  がローレベルになり、選択トランジスタ 108 がオフとなることで、 $n$  行目の画素から列回路 404 への信号の読み出しが終了する。

【0064】

また、時刻  $t_8$  において、制御信号  $pVr(n)$ 、 $pVgr(n)$  がハイレベルになり、感度調整がオンの状態になる。

この後、 $n$  行目の画素は、次のフレームの信号電荷の蓄積を開始する。

【0065】

続いて、期間  $HSCAN(n)$  において、各列の駆動信号  $CSEL(n)$  が順次、ハイレベルとなり、容量  $CTS1$  から信号 S が水平出力線 311 に出力され、容量  $CTN1$  から信号 N が水平出力線 313 に出力される。

40

【0066】

すなわち、列回路 404 に読み出された信号 N と信号 S は、列ごとに出力回路 407 に出力される。出力回路 407 は信号 S と信号 N との差分をアナログ - デジタル変換回路 408 に出力する。これにより、閾値のばらつき等によるノイズが除去された信号 S が得られる。

【0067】

時刻  $t_9$  において、駆動信号  $pSEL(n+1)$  がハイレベルになり、 $(n+1)$  行目の画素の選択トランジスタ 108 がオンになる。以降、期間  $HBLNK(n+1)$  において、 $(n+1)$  行目の画素からの信号の読み出しが行われ、期間  $HSCAN(n+1)$  に

50

おいて各列の信号が順次出力される。

【0068】

本実施形態によれば、分光感度特性のバイアス電圧依存性の影響を低減することができ、感度調整の精度をより向上させることができる。したがって、より出力信号の精度が向上した光電変換装置が提供される。

【0069】

[第2実施形態]

<画素の構成>

第2実施形態は、第2の電極103の電位を制御する制御線の本数及び駆動方法が第1実施形態と異なる。そこで、本実施形態の説明では、主として第1実施形態と異なる部分を説明し、第1実施形態と共通する部分については、説明を省略又は簡略化する。

10

【0070】

図8は、第2実施形態における光電変換装置のR画素1、Gr画素2、Gb画素3、B画素4の構成を模式的に示している。図9は、2行2列の行列状に配されたR画素1、Gr画素2、Gb画素3、B画素4の平面構造を模式的に示している。その他の画素も同様の平面構造を有している。図9では画素を構成する構造のうち下層から第2の電極103までが図示されており、第2の電極103よりも上部に積層される光電変換部は図示を省略している。図8及び図9において、第1実施形態で説明した図と同じ機能を有する部分には、同じ符号が付されている。以下、図8及び図9を用いて本実施形態の構成を説明する。

20

【0071】

R画素1において、ノードCは制御線206に接続される。Gr画素2において、ノードDは制御線210に接続される。Gb画素3において、ノードCは制御線210に接続される。B画素4において、ノードDは制御線209に接続される。すなわち、Gr画素2のノードDとGb画素3のノードCには共通の制御線210が接続され、同一の電位が供給される。行駆動回路402は、制御線206、209、210を介して第2の電極103の電位を制御する。

【0072】

<光電変換装置の駆動方法>

次に、本実施形態による光電変換装置の駆動方法について説明する。図10は、本実施形態の光電変換装置に用いられるグローバルシャッター動作時の駆動信号のタイミングチャートを示している。図10には、n行目と(n+1)行目の2行分の信号の読み出し動作に対応した駆動信号が示されている。なお、制御線206を介してR画素1に供給される制御信号をpVr、制御線210を介してGr画素2及びGb画素3に供給される制御信号をpVg、制御線209を介してB画素4に供給される制御信号をpVbとする。これらの制御信号は全行に共通のタイミングで変化するため、行を示す符号の表示は省略されている。なお、制御信号pVr、pVg、pVbがハイレベルの状態は、感度調整がオンの状態を意味する。また、制御信号pVr、pVg、pVbがローレベルの状態は、光電変換部100の感度が実質的にゼロになるように第2の電極103の電位が調整されている状態を意味する。

30

【0073】

本実施形態の光電変換装置の駆動では、いわゆるグローバルシャッター動作が行われる。時刻t11から時刻t12の間の期間において、全画素の光電変換部100は信号電荷を蓄積している状態(一括露光期間)である。信号電荷の蓄積時には、制御信号pVr、pVg、pVbはハイレベルであり、感度調整がオンの状態である。

40

【0074】

まず、n行目の画素からの読み出しを行う期間HBLNK(n)の動作について説明する。時刻t12において、制御信号pVr、pVg、pVbがローレベルになり、光電変換部100の感度がゼロの状態になる。この動作を一括シャッター動作と称する。この一括シャッター動作以降、順次信号読み出しが行われるまでの間、信号電荷がノードBに保

50

持される保持期間となる。このようにして、一括露光と一括シャッター動作を行うことにより、グローバルシャッター動作が実現される。また、時刻  $t_{12}$  において、駆動信号  $p_{SEL}(n)$  がハイレベルになり、 $n$  行目の画素の選択トランジスタ  $108$  がオンになる。これにより、 $n$  行目の画素の増幅トランジスタ  $107$  から、ノード  $B$  に蓄積された光信号と増幅トランジスタ  $107$  の閾値ばらつきによるノイズ信号とを含む信号  $S$  が列信号線  $204$  に出力される。

#### 【0075】

時刻  $t_{13}$  において、駆動信号  $p_{TS}(n)$  が、ハイレベルになり、増幅器  $301$  によって増幅された信号  $S$  が、容量  $CTS1$  に出力される。時刻  $t_{14}$  において、駆動信号  $p_{TS}(n)$  がローレベルになった後においても、信号  $S$  が容量  $CTS1$  に保持される。 10

#### 【0076】

時刻  $t_{15}$  において、駆動信号  $p_{RES}(n)$  がハイレベルになり、 $n$  行目の画素のリセットトランジスタ  $106$  がオンになる。これにより  $n$  行目の画素のノード  $B$  の電位がリセット電位  $V_{reset}$  に応じた電位にリセットされる。その後、時刻  $t_{16}$  において、駆動信号  $p_{RES}(n)$  がローレベルになり、リセットトランジスタ  $106$  はオフになる。このとき、増幅トランジスタ  $107$  は閾値ばらつきによるノイズを含む信号  $N$  を選択トランジスタ  $108$  を介して列信号線  $204$  に出力する。

#### 【0077】

時刻  $t_{17}$  において、駆動信号  $p_{TN}(n)$  が、ハイレベルになり、信号  $N$  が、列回路  $404$  の容量  $CTN1$  に出力される。時刻  $t_{18}$  において、駆動信号  $p_{TN}(n)$  がローレベルになり、信号  $N$  が容量  $CTN1$  に保持される。 20

#### 【0078】

時刻  $t_{19}$  において、駆動信号  $p_{SEL}(n)$  がローレベルになり、選択トランジスタ  $108$  がオフとなることで、 $n$  行目の画素から列回路  $404$  への信号の読み出しが終了する。

#### 【0079】

その後、期間  $HSCAN(n)$  において、各列の駆動信号  $CSEL(n)$  が順次、ハイレベルとなり、容量  $CTS1$  から信号  $S$  が水平出力線  $311$  に出力され、容量  $CTN1$  から信号  $N$  が水平出力線  $313$  に出力される。すなわち、列回路  $404$  に読み出された信号  $N$  と信号  $S$  は、列ごとに出力回路  $407$  に出力される。出力回路  $407$  は信号  $S$  と信号  $N$  との差分をアナログ - デジタル変換回路  $408$  に出力する。これにより、閾値のばらつき等によるノイズが除去された信号  $S$  が得られる。 30

#### 【0080】

時刻  $t_{20}$  において、駆動信号  $p_{SEL}(n+1)$  がハイレベルになり、 $(n+1)$  行目の画素の選択トランジスタ  $108$  がオンになる。以降、期間  $HBLNK(n+1)$  において各列の信号が順次出力される。以降の動作は同様であるため説明を省略する。

#### 【0081】

本実施形態では、 $G_r$  画素  $2$  及び  $G_b$  画素  $3$  の第  $2$  の電極  $103$  の電位が共通の制御線  $210$  により制御されている。これにより、第  $1$  実施形態では、 $2$  行あたり  $4$  本の制御線  $206$ 、 $207$ 、 $208$ 、 $209$  が設けられていたが、本実施形態では、 $2$  行あたり  $3$  本の制御線  $206$ 、 $209$ 、 $210$  が設けられており、制御線の本数を削減することができる。したがって、本実施によれば、第  $1$  実施形態と同様に感度調整の精度を向上させることができ、これに加え、第  $1$  実施形態よりも制御線の本数を少なくすることができる。 40

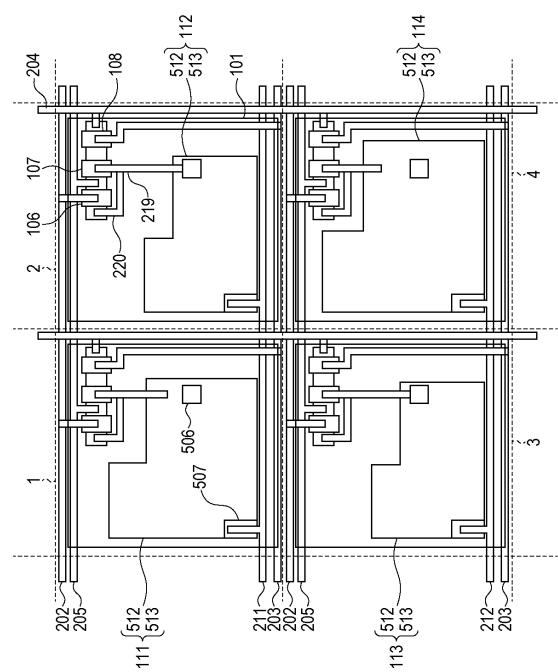

#### 【0082】

##### <第2実施形態の変形例>

次に第  $2$  実施形態の変形例について説明する。本変形例では、制御線の本数及び画素容量の構成が変形されている。図  $11$  は、 $2$  行  $2$  列の行列状に配された  $R$  画素  $1$ 、 $G_r$  画素  $2$ 、 $G_b$  画素  $3$ 、 $B$  画素  $4$  の平面構造を模式的に示している。その他の画素も同様の平面構造を有している。既に説明した図と同じ機能を有する部分には、同じ符号が付されてある。以下、図  $11$  を用いて本変形例について特徴を説明する。 50

## 【0083】

本変形例において、R画素1は、R画素容量111（第1の画素容量）を有する。Gr画素2は、Gr画素容量112（第2の画素容量）を有する。Gb画素3は、Gb画素容量113（第3の画素容量）を有する。B画素4は、B画素容量114（第4の画素容量）を有する。すなわち、本変形例では、図11に示されるように、各画素が異なる面積の画素容量を備え得る。

## 【0084】

また、R画素1及びGr画素2の第2の電極103の電位は、共通の制御線211（第1の制御線）により制御される。Gb画素3及びB画素4の第2の電極103の電位は、共通の制御線212（第2の制御線）に接続される。行駆動回路402は、制御線211、212を介して第2の電極103の電位を制御する。10

## 【0085】

ノードBの電位は、制御線から供給される電位を画素容量と光電変換部の容量とにより分圧して得られる電位となる。本変形例では、感度の異なるR画素1、Gr画素2が共通の制御線211により制御される。また、感度の異なるGb画素3、B画素4も共通の制御線212により駆動される。

## 【0086】

ノードBの電位は、制御線から供給される電位を画素容量と光電変換部の容量とにより分圧して得られる電位となる。図11に示されるように、Gr画素容量112及びGb画素容量113は、同じ容量値（同じ面積）とする。また、R画素容量111とGr画素容量112とは互いに異なる容量値（異なる面積）とし、かつ、B画素容量114は、Gb画素容量113とは互いに異なる容量値（異なる面積）とする。これにより、画素の感度の違いを補正するように画素容量の容量値を異ならせることができ、共通の制御線を用いても感度の異なる画素の感度比を調整することができる。20

## 【0087】

例えば、R画素1及びB画素4は、Gr画素2及びGb画素3よりも感度が低いので、R画素容量111及びB画素容量114の容量値は、Gr画素容量112及びGb画素容量113よりも、大きい値とする。このように、各画素容量の容量値を適宜設定することで、共通の制御線を用いて互いに感度の異なる画素の感度比を調整することができる。ただし、各画素容量は、半導体基板上に作りこまれるものでありバイアス電圧に応じて事後的に容量値を変更することができないため、感度調整の自由度は小さくなる。30

## 【0088】

本変形例では、R画素1及びGr画素2の第2の電極103の電位は、共通の制御線211により制御され、Gb画素3及びB画素4の第2の電極103の電位は、共通の制御線212に接続される。これにより、本変形例では、2行あたり2本の制御線211、212が設けられる構成であるため、制御線の本数を更に削減することができる。

## 【0089】

## [第3実施形態]

## &lt;画素の構成&gt;

第3実施形態は、第2の電極103（補助電極）が制御線に接続されるものの、ノードBには接続されていない点が第1実施形態と異なる。そこで、本実施形態の説明では、主として第1実施形態と異なる部分を説明し、第1実施形態と共通する部分については、説明を省略又は簡略化する。40

## 【0090】

図12は、第3実施形態における光電変換装置のR画素1、Gr画素2、Gb画素3、B画素4の構成を模式的に示している。図1と同じ機能を有する部分には、同じ符号が付されている。各画素は、光電変換部100、リセットトランジスタ106、増幅トランジスタ107、選択トランジスタ108を含む。光電変換部100は、第1の電極（共通電極）101、光電変換層102、第2の電極（補助電極）103、第3の電極104（画素電極）を含む。ここで、第2の電極103（補助電極）は、リセットトランジスタ10

6 及び増幅トランジスタ 107 には接続されない。また、第3の電極 104 (画素電極) はリセットトランジスタ 106 のソース及び増幅トランジスタ 107 のゲート (増幅部の入力ノード) に接続される。第3の電極 104 は、光電変換層 102 の第2の電極が配された側の面 (第1の電極が配された側の面と対向する面) に配されている。

#### 【0091】

ノード B は、増幅トランジスタ 107 のゲート、リセットトランジスタ 106 のソース及び第3の電極 104 に接続される。R 画素 1 において、ノード C は制御線 206 に接続される。G<sub>r</sub> 画素 2 において、ノード D は制御線 207 に接続される。G<sub>b</sub> 画素 3 において、ノード C は制御線 208 に接続される。B 画素 4 において、ノード D は制御線 209 に接続される。

10

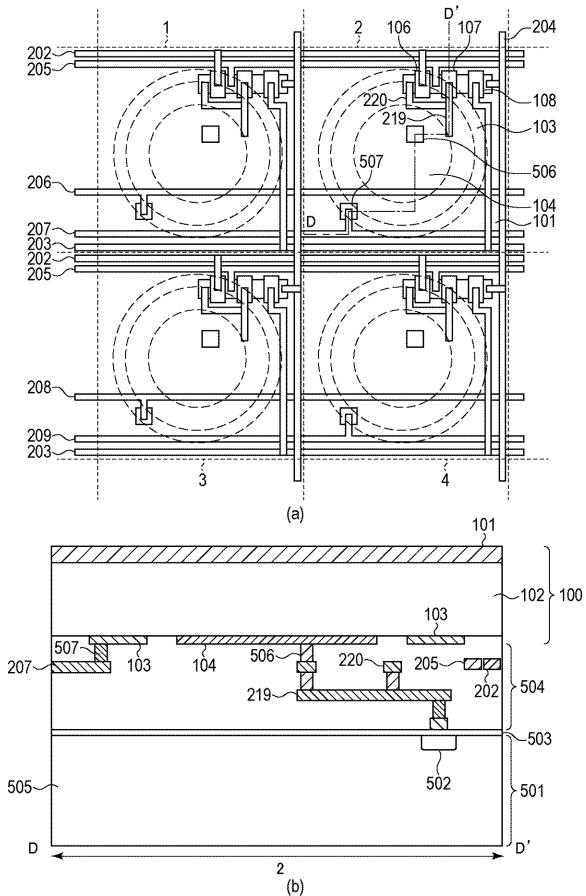

#### 【0092】

##### <光電変換装置の平面構造・断面構造>

次に、本実施形態の光電変換装置の平面構造、断面構造を説明する。図 13 (a) は、光電変換装置の平面構造を模式的に示している。図 13 (a) は 2 行 2 列の行列状に配された画素の第2の電極 103、第3の電極 104 の形状のみを示す。図 13 (b) は、光電変換装置の断面構造を模式的に示している。図 13 (b) に示された断面は、図 13 (a) における一点鎖線 C - C' に沿った断面に対応する。図 13 (b) には、マイクロレンズ 516、平坦化層 515、カラーフィルタ 514、第1の電極 101、光電変換層 102、第2の電極 103、第3の電極 104、半導体基板 501 が示されている。また、光電変換層 102 には、入射光に対する感度が高い領域を示す高感度領域 517 と、入射光に対する感度が低い領域を示す低感度領域 518 とがそれぞれ破線で示されている。

20

#### 【0093】

第3の電極 104 は、平面視において円形の形状をなしている。第2の電極 103 は、平面視において、第3の電極 104 の外側に、第3の電極 104 を囲うように配されている。第3の電極 104 と第2の電極 103 の間の空隙は、平面視において、円環状をなしている。第1の電極 101 の上にはカラーフィルタ 514 が配されており、カラーフィルタ 514 の上には平坦化層 515 を介してマイクロレンズ 516 が配されている。マイクロレンズ 516 は入射光を光電変換部に集光する機能を有する。

#### 【0094】

光電変換が行われているときの光電変換層 102 内の電界分布は、第2の電極 103 及び第3の電極 104 に与えられている電位によって変化する。これにより、高感度領域 517 と低感度領域 518 の大きさを調整することができる。信号電荷が電子の場合、第2の電極 103 に第3の電極 104 よりも高い電位を与えることで、低感度領域 518 は大きくなり、高感度領域 517 は小さくなる。また、信号電荷がホールの場合は、第2の電極 103 に第3の電極 104 よりも低い電位を与えることで、低感度領域 518 は大きくなり、高感度領域 517 は小さくなる。光電変換によって発生した電荷は第3の電極 104 に収集される。第3の電極 104 の外周に第2の電極 103 が配されているため、第2の電極 103 に与える電位を制御することにより、高感度領域 517 と低感度領域 518 の大きさを調整することができる。

30

#### 【0095】

次に、本実施形態の光電変換装置の回路部分の平面構造、断面構造について説明する。図 14 (a) は、光電変換装置の回路部分の平面構造を模式的に示す図であり、図 14 (b) は、光電変換装置の回路部分の断面構造を模式的に示す図である。図 14 (a) は、2 行 2 列の行列状に配された R 画素 1、G<sub>r</sub> 画素 2、G<sub>b</sub> 画素 3、B 画素 4 を示している。図 14 (b) に示された断面は、図 14 (a) における一点鎖線 D - D' に沿った断面に対応する。なお、第2の電極 103、第3の電極 104 の形状に相当する部分は破線で示されている。

40

#### 【0096】

図 14 (a) において、コンタクトプラグ 506 は第3の電極 104 と増幅トランジスタ 107 とを接続するコンタクトプラグを示す。コンタクトプラグ 507 は第2の電極 1

50

03と制御線とを接続するコンタクトプラグを示す。

【0097】

R画素1の第2の電極103は制御線206に接続される。Gr画素2の第2の電極103は制御線207に接続される。Gb画素3の第2の電極103は制御線208に接続される。B画素4の第2の電極103は制御線209に接続される。すなわち、第1実施形態と同様に、R画素1、Gr画素2、Gb画素3及びB画素4のそれぞれに対し独立して設けられており、独立して第2の電極103の電位を制御することができる。

【0098】

本実施形態では、第2の電極103が、制御線には接続されているものの、リセットトランジスタ106及び増幅トランジスタ107に接続されていない(すなわち、ノードBに接続されていない)。このような構成であっても第1実施形態と同様に画素ごとに感度調整を行うことができ、感度調整の精度をより向上させることができる。

【0099】

【第4実施形態】

第4実施形態は、第1実施形態の構成において、Gr画素2又はGb画素3のいずれか一方をW画素(第5の画素)に置き換えたものである。その他の構成については第1実施形態と同様であり説明を省略する。ここで、W画素は、入射光のうちの少なくとも赤色から青色の範囲に応じた信号を生成する画素であり、R画素、G画素及びB画素の高感度波長帯域を全て含む分光感度特性となっている。より具体的には、W画素は、例えば、カラーフィルタを有しない画素、あるいは、カラーフィルタが赤色から青色の範囲において実質的に透明である画素であり得る。

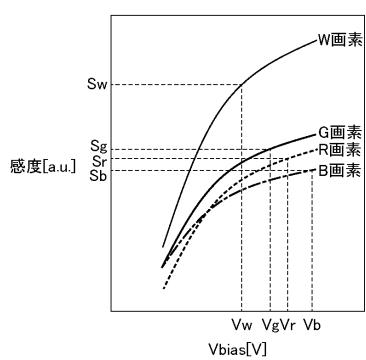

【0100】

図15は、R画素、G画素、B画素、W画素についての感度とバイアス電圧Vbiasの依存性を示すグラフである。図15において、縦軸は感度を示しており、横軸は光電変換部100に印加されるバイアス電圧Vbiasを示している。

【0101】

R画素、G画素、B画素、W画素のそれぞれについて、印加されるバイアス電圧がVr、Vg、Vb、Vwである場合の、感度をそれぞれSr、Sg、Sb、Swとする。このとき、第1実施形態で述べたものと同様の手法により、R画素、G画素、B画素については、Sr:Sg:Sbの色比が一定となるようにバイアス電圧を制御する。また、W画素はRGB画素とは独立してバイアス電圧を制御する。これにより、R画素、G画素、B画素により色情報を取得し、W画素により輝度情報を取得することができる。光電変換装置の内部又は外部に設けられた画像処理部において、色情報と輝度情報を合成することによりダイナミックレンジを向上させることができる。

【0102】

本実施形態によれば、第1実施形態と同様の効果が得られることに加え、R画素、G画素、B画素で色情報、W画素で輝度情報を取得することができ、ダイナミックレンジを向上させることができる。

【0103】

【第5実施形態】

第5実施形態は、動画像の撮影においてフレームごとに異なる電位を光電変換部100の第2の電極に供給可能とすることにより、バイアス電圧をフレームごとに変更する点が第1実施形態と異なる。ここで、本実施形態の説明では、主として第1実施形態と異なる部分を説明し、第1実施形態と共通する部分については、説明を省略又は簡略化する。

【0104】

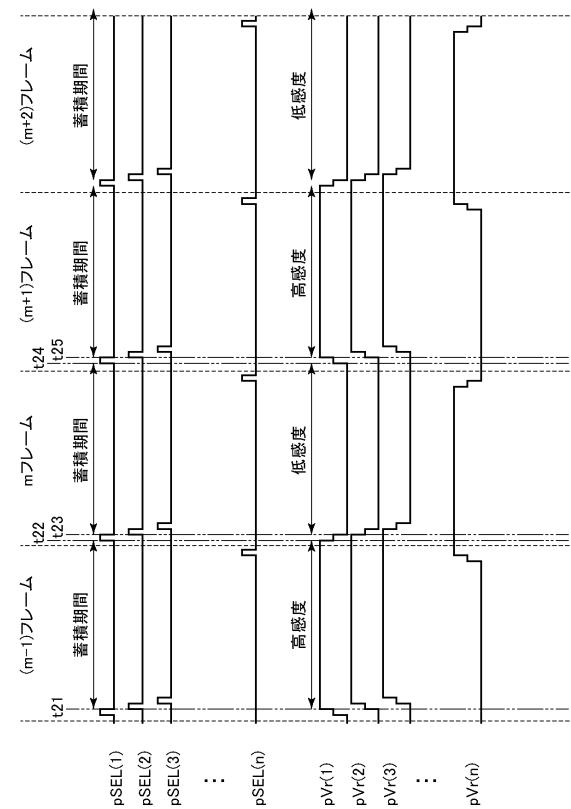

図16は、本実施形態の光電変換装置に用いられる駆動信号のタイミングチャートを示している。なお、図16では、R画素1に関するタイミングのみが示されているが、他の画素についても同様である。また、図16には、(m-1)フレームから(m+2)フレームにおける1行目からn行目までの信号の読み出し動作に対応した駆動信号が示されている。ここでは、1行目の駆動について説明する。

10

20

30

40

50

## 【0105】

時刻  $t_{21}$  において、駆動信号  $p_{SEL}(1)$  はローレベルになり、選択トランジスタ  $108$  がオフとなることで、1行目の画素から列回路  $404$  への  $(m-1)$  フレームの信号の読み出しが終了する。また、時刻  $t_{21}$  において、制御信号  $p_{VR}(1)$  はハイレベルになり、光電変換部  $100$  が高感度の状態になる。

## 【0106】

時刻  $t_{21}$  から時刻  $t_{22}$  の期間（蓄積期間）において、1行目の画素の光電変換部  $100$  は、 $m$  フレームの信号電荷を蓄積している状態である。 $m$  フレームの信号電荷の蓄積時には、制御信号  $p_{VR}(1)$  はハイレベルであるため、高感度で電荷の蓄積を行う。

## 【0107】

時刻  $t_{22}$  において、駆動信号  $p_{SEL}(1)$  は、ハイレベルになり、選択トランジスタ  $108$  がオンとなることで、 $m$  フレームの読み出しのため、再び1行目の画素が選択される。時刻  $t_{22}$  において、制御信号  $p_{VR}(1)$  は、ミドルレベルになる。これにより、読み出し期間中の電位をトランジスタの動作範囲内として信号を読み出すことができる。

## 【0108】

時刻  $t_{23}$  において、駆動信号  $p_{SEL}(1)$  はローレベルになり、選択トランジスタ  $108$  がオフとなることで、1行目の画素から列回路  $404$  への  $m$  フレームの信号の読み出しが終了する。また、時刻  $t_{23}$  において、制御信号  $p_{VR}(1)$  は、ローレベルになり、光電変換部  $100$  が低感度の状態になる。

## 【0109】

時刻  $t_{23}$  から  $t_{24}$  の期間（蓄積期間）において、 $(m+1)$  フレームの画素の光電変換部  $100$  は信号電荷を蓄積している状態である。 $(m+1)$  フレームの信号電荷の蓄積時には、制御信号  $p_{VR}(1)$  はローレベルであるため、低感度で電荷の蓄積を行う。

## 【0110】

時刻  $t_{24}$  において、駆動信号  $p_{SEL}(1)$  は、ハイレベルになり、選択トランジスタ  $108$  がオンとなることで、 $(m+1)$  フレームの読み出しのため、再び1行目の画素が選択される。時刻  $t_{24}$  において、制御信号  $p_{VR}(1)$  は、ミドルレベルになる。これにより、読み出し期間中の電位をトランジスタの動作範囲内として信号を読み出すことができる。

## 【0111】

時刻  $t_{25}$  において、駆動信号  $p_{SEL}(1)$  はローレベルになり、選択トランジスタ  $108$  がオフとなることで、1行目の画素から列回路  $404$  への  $(m+1)$  フレームの信号の読み出しが終了する。また、時刻  $t_{25}$  において、制御信号  $p_{VR}(1)$  は、ハイレベルになり、光電変換部  $100$  が高感度の状態になる。以降のフレームの動作は、同様であるため、説明を省略する。

## 【0112】

このような駆動方法を用いることにより、 $m$  フレームにおいて、高感度で蓄積された信号電荷を読み出し、 $(m+1)$  フレームにおいて低感度で蓄積された信号電荷を読み出すことができる。その後、光電変換装置の内部又は外部に設けられた画像処理部において、 $m$  フレームに読み出された画像と  $(m+1)$  フレームに読み出された画像とを合成することにより、ダイナミックレンジを向上させた画像を得ることができる。

## 【0113】

本実施形態によれば、フレームごとに異なる電位を光電変換部  $100$  の第2の電極  $103$  に供給可能であり、バイアス電圧をフレームごとに変更することができる。これにより、フレームごとに、R画素、G<sub>r</sub>画素、G<sub>b</sub>画素、B画素の感度比を調整するとともに、感度が異なる複数の画像を取得して合成することで、第1実施形態と同様の効果が得られ、更にダイナミックレンジを向上させることができる。

## 【0114】

第6実施形態は、光電変換部100の構成及び駆動方法が第1実施形態と異なる。そこで、本実施形態の説明では、主として第1実施形態と異なる部分を説明し、第1実施形態と共通する部分については、説明を省略又は簡略化する。

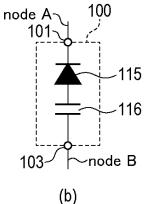

【0115】

図17(a)は、本実施形態の光電変換部100の構成を模式的に示す図であり、図17(b)は、本実施形態の光電変換部100の等価回路を示す図である。図1に示したものと同じ機能を有する部分には、同じ符号が付されている。

【0116】

<光電変換部の構成>

図17(a)において、光電変換部100は、第1の電極101、プロッキング層117、光電変換層102、絶縁層105、及び、第2の電極103を含む。第1の電極101は、電圧制御部401に接続される。このような構成により、光電変換部100での信号電荷の蓄積、及び、光電変換部100からの信号電荷の排出を行うことができる。なお、信号電荷の排出は、光電変換部100で生じた信号を読み出すために行われる。

【0117】

電圧制御部401は、少なくとも第1の電位Vs1、及び、第1の電位Vs1とは異なる第2の電位Vs2を光電変換部100の第1の電極101に供給する。信号電荷がホールの場合、第2の電位Vs2は第1の電位Vs1より低い電位である。信号電荷がホールの場合、例えば、第1の電位Vs1は5Vであり、第2の電位Vs2は0Vである。信号電荷が電子の場合、第2の電位Vs2は第1の電位Vs1より高い電位である。信号電荷が電子の場合、例えば、第1の電位Vs1が0Vであり、第2の電位Vs2が5Vである。なお、本明細書では、特に言及した場合を除き、接地されたノードの電位を0Vとしている。

【0118】

本実施形態の光電変換部100は、信号電荷を蓄積するように構成された光電変換層102と、絶縁層105とを含む。したがって、光電変換部100は、第1の電極101及び第2の電極103との間に直列に容量成分を含む。図17(b)の等価回路は、この容量成分を光電変換部100の第1の電極101及び第2の電極103の間に配された容量116として示している。なお、光電変換部100はプロッキング層117を含んでいるため、図17(b)では、プロッキング層117及び光電変換層102が等価的にダイオード115として示されている。

【0119】

プロッキング層117は、第1の電極101から光電変換層102へ信号電荷と同じ導電型の電荷が注入されることを阻止する。光電変換層102は、第1の電極101に印加される電位Vsに応じて空乏化する。また第1の電極101に印加される電位Vsと第2の電極103(ノードB)の電位との関係に応じて、光電変換層102のポテンシャルの傾きが反転する。このような構成により、光電変換部100は、信号電荷の蓄積、及び、蓄積された信号電荷の排出を行うことができる。光電変換部100の動作については後述する。

【0120】

本実施形態では、光電変換部100の第1の電極101に供給される電位Vsと、リセット電位V<sub>reset</sub>との大小関係を制御することで、光電変換部100における信号電荷の蓄積、及び、光電変換部100からの信号電荷の排出を行う。リセット電位V<sub>reset</sub>は、例えば、第1の電位Vs1と第2の電位Vs2との中間の値である。この場合において、信号電荷がホールの場合には、リセット電位V<sub>reset</sub>は第1の電位Vs1より低く、第2の電位Vs2より高い電位である。信号電荷が電子の場合、リセット電位V<sub>reset</sub>は、第1の電位Vs1より高く、第2の電位Vs2より低い電位である。本実施形態において、リセット電位V<sub>reset</sub>は、例えば、3.3Vである。このリセット電位V<sub>reset</sub>は、電源電位よりも低く、接地されたノードに供給される電位よりも高い。

【0121】

10

20

30

40

50

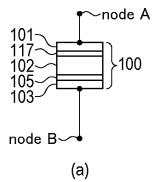

## &lt;光電変換部の動作&gt;

次に、本実施形態における光電変換部100の動作について説明する。図18(a)乃至図18(f)は、光電変換部100におけるエネルギー・バンドを模式的に示している。図18(a)乃至図18(f)には、第1の電極101、ブロッキング層117、光電変換層102、絶縁層105、第2の電極103のエネルギー・バンドが示されている。また、黒丸は電子を示しており、白丸はホールを示している。図18(a)乃至図18(f)の縦軸は電子に対するポテンシャルを表しており、図中の上方向が電子に対するポテンシャルが高く、すなわち、電位が低い方向を示している。また、第1の電極101及び第2の電極103については、自由電子のエネルギー準位が示されている。ブロッキング層117及び光電変換層102については、伝導帯のエネルギー準位と価電子帯のエネルギー準位との間のバンドギャップが示されている。なお、光電変換層102と絶縁層105との界面における光電変換層102のポテンシャルを、便宜的に、光電変換層102の表面ポテンシャル、あるいは、単に表面ポテンシャルと呼ぶ。

## 【0122】

光電変換部100の動作としては、以下のステップ(1)～(6)が繰り返し行われる。すなわち、ステップ(1)は、増幅部の入力ノードのリセット(FDリセット)である。ステップ(2)は、信号Nの読み出し(N読み)である。ステップ(3)は、光電変換部100からの信号電荷の排出動作である。ステップ(4)は、信号Sの読み出し(S読み)である。ステップ(5)は、光電変換部100からの残留電荷の排出と信号電荷の蓄積の開始前の準備のための光電変換層102のリセット動作である。ステップ(6)は、信号電荷の蓄積動作である。以下、それぞれのステップについて説明する。

## 【0123】

図18(a)は、ステップ(1)からステップ(2)における光電変換部100の状態を示している。第1の電極101には、電圧制御部401から第1の電位Vs1が供給されている。第1の電位Vs1は、例えば、5Vである。光電変換層102には、露光期間中に生じた信号電荷として、白丸で示されたホールが蓄積されている。蓄積されたホールの量に応じて、光電変換層102の表面ポテンシャルは低くなる方向(電位が高くなる方向)へ変化する。なお、蓄積される電荷が電子の場合、蓄積された電子の量に応じて、表面ポテンシャルは高くなる方向(電位が低くなる方向)へ変化する。

## 【0124】

この状態でリセットトランジスタ106がオンになると、第2の電極103を含むノード、すなわち、図17のノードBの電位がリセット電位Vresにリセットされる(ステップ(1)のFDリセット)。本実施形態では、ノードBに増幅トランジスタ107のゲートが含まれている。そのため、増幅トランジスタ107のゲートの電位がリセットされる。リセット電位Vresは、例えば、3.3Vである。

## 【0125】

その後、リセットトランジスタ106がオフになると、ノードBが電気的にフローティングになる。このときリセットトランジスタ106によるリセットノイズ(図18(a)等のノイズkTC1)が発生し得る。

## 【0126】

リセット動作による第2の電極103の電位の変化に応じて、光電変換層102の表面ポテンシャルは変化し得る。この時の第2の電極103の電位の変化の方向は、信号電荷が蓄積することによって生じた第2の電極103の電位の変化とは反対の方向である。そのため、信号電荷のホールは、光電変換層102に蓄積されたままである。また、ブロッキング層117によって第1の電極101からのホールの注入は阻止されるため、光電変換層102に蓄積された信号電荷の量は変動しない。

## 【0127】

このとき、選択トランジスタ108がオン状態であれば、増幅トランジスタ107は、リセットノイズを含む信号N(Vres+kTC1)を出力する(ステップ(2)のN読み)。信号Nは、列回路404の容量CTN1に保持される。

10

20

30

40

50

## 【0128】

図18 (b) 及び図18 (c) は、ステップ (3) における光電変換部100の状態を示している。まず、第1の電極101に第2の電位Vs2が供給される。信号電荷としてホールを用いているため、第2の電位Vs2は第1の電位Vs1より低い電位である。第2の電位Vs2は、例えば、0Vである。

## 【0129】

このとき、第2の電極103 (ノードB) の電位は、第1の電極101の電位の変化と同じ方向に向かって変化する。第2の電極103の電位の変化量dVBは、第2の電極103に接続された画素容量109の容量値C1と、光電変換部100が有する容量116の容量値C2との比に応じて定まる。第1の電極101の電位の変化量dVsに対して、第2の電極103の電位の変化量dVBは、 $dVB = dVs \times C2 / (C1 + C2)$ と表される。なお、第2の電極103を含むノードBはこれ以外の容量成分を含み得る。しかしながら、他の容量成分は画素容量109の容量値C1にくらべて十分に小さい。そのため、ノードBの容量値は、画素容量109の容量値C1と実質的に等しいと考えてよい。

10

## 【0130】

本実施形態では、第1の電極101の電位の変化量dVsが、第2の電極103の電位の変化量dVBよりも十分に大きい。そのため、第2の電極103のポテンシャルは、第1の電極101のポテンシャルよりも低くなり、光電変換層102のポテンシャルの傾きが反転する。これにより、黒丸で示された電子が第1の電極101から光電変換層102に注入される。また、信号電荷として光電変換層102に蓄積されたホールの一部又は全部が、ブロッキング層117の側に移動する。移動したホールは、ブロッキング層117の多数キャリアと再結合して消滅する。その結果、光電変換層102のホールが光電変換層102から排出される。光電変換層102の全体が空乏化する場合には、信号電荷として蓄積されたホールの全部が排出される。

20

## 【0131】

次に、図18 (c) に示される状態においては、第1の電極101に第1の電位Vs1が供給される。これにより、光電変換層102のポテンシャルの傾きが再び反転する。そのため、図18 (b) の状態の時に光電変換層102に注入されていた電子は、光電変換層102から排出される。一方、ブロッキング層117が、第1の電極101から光電変換層102へのホールの注入を阻止する。したがって、光電変換層102の表面ポテンシャルは、蓄積されていたホールの量に応じて変化する。表面ポテンシャルの変化に対応して、第2の電極103の電位は、リセットされた状態から、消滅したホールの量に応じた電圧Vpだけ変化する。つまり、信号電荷として蓄積されたホールの量に応じた電圧VpがノードBの電位に加算される。蓄積されたホールの量に応じた電圧Vpを、光信号成分と呼ぶ。

30

## 【0132】

ここで、図18 (c) に示される状態において、選択トランジスタ108がオン状態になる。これにより、增幅トランジスタ107は、信号S ( $Vp + Vres + kT C1$ ) を出力する (ステップ (4) のS読み)。信号Sは、列回路404の容量CTSに保持される。ステップ (2) で読み出された信号N ( $Vres + kT C1$ ) と、ステップ (4) で読み出された信号S ( $Vp + Vres + kT C1$ )との差分が、蓄積された信号電荷に応じた電圧Vpに基づく信号 (光信号成分) である。

40

## 【0133】

図18 (d1) 及び図18 (d2) は、ステップ (5) における光電変換部100の状態を示している。リセットトランジスタ106がオン状態になり、ノードBの電位がリセット電位Vresにリセット (FDリセット) される。図18 (b) と同様に、第1の電極101の電位を第1の電位Vs1 第2の電位Vs2 第1の電位Vs1と変化させる。これにより、図18 (c) の動作から蓄積開始前のリセットまでの期間に光電変換膜に蓄積された暗電荷及び光電荷、並びに、図18 (b) の電荷排出過程で排出されず光電変換膜中に残留している光電荷を排出することができる (光電変換層リセット)。なお、本

50

実施形態では、常時入射光が光電変換部 100 に入射されており、これらの期間にも光電荷が発生し得る。この動作により、前のフレームの残留電荷等が次のフレームの光信号成分に影響を与えることを防ぐことができる。その後、リセットトランジスタ 106 がオフになる。このように、信号電荷の蓄積を開始する前にノード B のリセットを行うことにより、ノード B に蓄積された前フレームの光信号成分等を除去できる。またノード B に電荷が蓄積されることにより、ダイナミックレンジが狭くなることを抑制することができる。

#### 【0134】

このときにも、リセットトランジスタ 106 によるリセットノイズ（図 18 のノイズ k T C 2）が発生し得る。しかしながら、ここで発生するリセットノイズは、蓄積期間の終了後に、ステップ（1）のリセット動作を行うことで除去することができる。

10

#### 【0135】

図 18 (e) 及び図 (f) は、ステップ（6）における光電変換部 100 の状態を示している。この時点において、第 1 の電極 101 には第 1 の電位 V s 1 が供給され、ノード B にはリセット電位 V reset が供給される。リセット電位 V reset は第 1 の電位 V s 1 よりも低いため、光電変換層 102 の電子は第 1 の電極 101 に排出される。一方、光電変換層 102 のホールは、光電変換層 102 と絶縁層 105 との界面に向かって移動する。しかしながら、ホールは絶縁層 105 に移動できないため、光電変換層 102 に蓄積される。また、前述のとおり、ブロッキング層 117 が、ホールが光電変換層 102 に注入されることを阻止する。したがって、この状態で光電変換層 102 に光が入射すると、光電変換によって生じた電子・ホール対のうち、ホールのみが信号電荷として光電変換層 102 に蓄積される。一定期間の蓄積が行われた後、ステップ（1）乃至ステップ（6）の動作が繰り返される。

20

#### 【0136】

蓄積されたホールによって光電変換層 102 の表面ポテンシャルが変化する。この表面ポテンシャルの変化に応じて、第 2 の電極 103 の電位が上昇する。この電位変化が図 18 (f) に示される電圧 V p 0 である。図 18 (a) のリセット時には、上述のとおり、変化した電圧 V p 0 を打ち消すように、第 2 の電極 103 の電位が変化する。つまり、第 2 の電極 103 の電位が低下する。したがって、光電変換層 102 の表面ポテンシャルは高くなる方向に変化する。

30

#### 【0137】

なお、信号電荷が電子の場合には、第 2 の電位 V s 2 は第 1 の電位 V s 1 より高い電位であり、図 18 (a) 乃至図 18 (f) でのポテンシャルの傾きが逆になる。その他の点は同様である。

#### 【0138】

本実施形態によるノイズ低減の効果について説明する。上述の動作においては、図 18 (b) の状態から光電変換層 102 のポテンシャルの傾きが反転することで、蓄積された信号電荷の排出を行っている。光電変換層 102 のポテンシャルの傾きを十分に反転させることができないと、排出されない電荷が生じるため、排出されない電荷に起因するノイズが生じる可能性がある。ここで、第 1 の電極 101 の電位の変化量 d V s が、第 2 の電極 103 (ノード B) の電位の変化量 d V B に比べて大きいほど、ポテンシャルの傾きを反転させやすい。すなわち、第 1 の電極 101 の電位の変化量 d V s が、第 2 の電極 103 の電位の変化量 d V B に比べて大きいほど、ノイズを低減することができる。

40

#### 【0139】

上述のとおり、第 1 の電極 101 の電位の変化量 d V s とノード B の電位の変化量 d V B との間には、 $d V B = d V s \times C 2 / (C 1 + C 2)$  という関係がある。この式を変形すると、第 1 の電極 101 の電位の変化量 d V s は、 $d V s = d V B + (C 1 / C 2) \times d V B$  と表される。すなわち、第 1 の電極 101 の電位の変化量 d V s は、第 2 の電極 103 の電位の変化量 d V B よりも、 $(C 1 / C 2) \times d V B$  だけ大きい。したがって、ノード B の容量値 C 1 が大きいほど、第 1 の電極 101 の電位の変化量 d V s と第 2 の電極 103 の電位の変化量 d V B との差が大きくなる。

50

## 【0140】

本実施形態では、第2の電極103に画素容量109が接続されている。そのため、ノードBの容量値C1を大きくすることができる。このような構成によれば、第1の電極101の電位の変化量dVsを、第2の電極103の電位の変化量dVBに比べて大きくすることができる。結果として、光電変換層102を空乏化しやすくなるため、排出されない電荷を低減できる。このように、本実施形態によれば、ノイズを低減することができる。

## 【0141】

## &lt;光電変換装置の駆動方法&gt;

次に、本実施形態による光電変換装置の駆動方法について説明する。図19は、本実施形態の光電変換装置に用いられるローリングシャッター動作時の駆動信号のタイミングチャートを示している。図19には、n行目とn+1行目の2行分の信号の読み出し動作に対応した駆動信号が示されている。

## 【0142】

本実施形態の光電変換装置の駆動では、いわゆるローリングシャッター動作が行われる。時刻t31より前において、n行目の画素の光電変換部100、及び、n+1行目の画素の光電変換部100は信号電荷を蓄積している状態である。信号電荷の蓄積時には、制御信号pVr(n)、pVgr(n)、pVgb(n+1)、pVb(n+1)はハイレベルであり、感度調整がオンの状態である。まず、n行目の画素からの読み出しを行う期間HBLNK(n)の動作について説明する。時刻t31において、駆動信号pSEL(n)がハイレベルになり、n行目の画素の選択トランジスタ108がオンになる。これにより、n行目の画素の増幅トランジスタ107が列信号線204に信号を出力する状態となる。

## 【0143】

時刻t31において、駆動信号pRES(n)がハイレベルになり、n行目の画素のリセットトランジスタ106がオンになる。これにより、n行目の画素のノードBの電位がリセット電位Vresに応じた電位にリセットされる。また、時刻t31において、制御信号pVr(n)、pVgr(n)がミドルレベルになり、感度調整をオフの状態にする。これにより、読み出し期間中の電位をトランジスタの動作範囲内として信号を読み出すことができる。その後、時刻t32において、駆動信号pRES(n)がローレベルになり、リセットトランジスタ106はオフになる。

## 【0144】

時刻t33において、駆動信号pTN(n)がハイレベルになり、信号Nが、列回路404の容量CTN1に出力される。時刻t34において、駆動信号pTN(n)がローレベルになり、リセットノイズを含む信号Nが、列回路404の容量CTN1に保持される。

## 【0145】

時刻t35において、制御信号pVr(n)、pVgr(n)がミドルレベルからローレベルに遷移する。続いて、時刻t36において、制御信号pVr(n)、pVgr(n)がローレベルからミドルレベルに遷移する。時刻t35から時刻t36の動作によって、信号電荷の転送が行われる。したがって、ノードBには蓄積された信号電荷の量に応じた電圧Vpが生じる。

## 【0146】

時刻t37において、駆動信号pTS(n)がハイレベルになり、増幅器301によって増幅された信号Sが、容量CTS1に出力される。時刻t38において、駆動信号pTS(n)がローレベルになった後においても、電圧Vpとリセットノイズ(図6のkTC1)とを含む信号Sが、列回路404の容量CTS1に保持される。

## 【0147】

時刻t39において、駆動信号pRES(n)がハイレベルになり、n行目の画素のリセットトランジスタ106がオンになる。時刻t40においてローレベルになり、n行目

10

20

30

40

50

の画素のリセットトランジスタ 106 がオフになる。これにより、再び、n 行目の画素のノード B の電位がリセット電位 V<sub>res</sub> にリセットされる。

その後、n 行目の画素は、次のフレームの信号電荷の蓄積を開始する。

#### 【0148】

時刻 t<sub>41</sub>において、駆動信号 PSEL(n) がローレベルになり、n 行目の画素の選択トランジスタ 108 がオフになる。これにより、n 行目の画素から列回路 404 への信号の読み出しが終了する。

#### 【0149】

続いて、期間 HSCAN(n)において、各列の駆動信号 CSEL(m) が順次、ハイレベルとなり、容量 CTS1 から信号 S が水平出力線 311 に出力され、容量 CTN1 から信号 N が水平出力線 313 に出力される。すなわち、列回路 404 に読み出された信号 N と信号 S は、列ごとに出力回路 407 に出力される。出力回路 407 は信号 S と信号 N との差分をアナログ - デジタル変換回路 408 に出力する。

#### 【0150】

時刻 t<sub>42</sub>以降、n + 1 行目の画素からの信号の読み出しが行われる。この動作は時刻 t<sub>31</sub>から時刻 t<sub>41</sub>と同様なので、説明を省略する。

#### 【0151】

本実施形態によれば、プロッキング層 117 及び絶縁層 105 を備えた光電変換部 100 の構造を用いた場合において、第 1 実施形態と同様に、分光感度特性のバイアス電圧依存性の影響を低減することができ、感度調整の精度をより向上させることができる。更に、本実施形態では、画素容量 109 が接続されることにより、光電変換層 102 を空乏化しやすくでき、ノイズを低減することができる。

#### 【0152】

##### 【第 7 実施形態】

上述の実施形態における光電変換装置は種々の撮像システムに適用可能である。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星、監視カメラ等があげられる。図 20 に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

#### 【0153】

図 20 に示す撮像システムは、バリア 1001、レンズ 1002、絞り 1003、撮像装置（光電変換装置）1004、信号処理部 1007、タイミング発生部 1008、全体制御・演算部 1009 を含む。撮像システムは、更に、メモリ部 1010、記録媒体制御 I/F 部 1011、記録媒体 1012、外部 I/F 部 1013 を含む。バリア 1001 はレンズを保護し、レンズ 1002 は被写体の光学像を撮像装置 1004 に結像させる。絞り 1003 はレンズ 1002 を通った光量を可変にする。撮像装置 1004 は上述の実施形態で説明した光電変換装置を備え、レンズ 1002 により結像された光学像を画像データとして変換する。ここで、撮像装置 1004 の半導体基板には A/D 変換部が形成されているものとする。

#### 【0154】

信号処理部 1007 は撮像装置 1004 より出力された撮像データに対し、各種の補正及びデータの圧縮を行う。タイミング発生部 1008 は撮像装置 1004 及び信号処理部 1007 に、各種タイミング信号を出力する。全体制御・演算部 1009 はデジタルスチルカメラ全体を制御し、メモリ部 1010 は画像データを一時的に記憶する。記録媒体制御 I/F 部 1011 は記録媒体 1012 に画像データの記録又は読み出しを行うためのインターフェースであり、記録媒体 1012 は撮像データの記録又は読み出しを行うための半導体メモリ等の着脱可能な記録媒体である。外部 I/F 部 1013 は外部コンピュータ等と通信するためのインターフェースである。タイミング信号等は撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置 1004 と、撮像装置 1004 から出力された撮像信号を処理する信号処理部 1007 とを有すればよい。

#### 【0155】

10

20

30

40

50

本実施形態では、撮像装置 1004 と A/D 変換部とが別の半導体基板に設けられた構成を説明した。しかしながら、撮像装置 1004 と A/D 変換部とが同一の半導体基板に形成されていてもよい。また、撮像装置 1004 と信号処理部 1007 とが同一の半導体基板に形成されていてもよい。

【0156】

また、それぞれの画素が第 1 の光電変換部と、第 2 の光電変換部を含んでもよい。信号処理部 1007 は、第 1 の光電変換部で生じた電荷に基づく信号と、第 2 の光電変換部で生じた電荷に基づく信号とを処理し、撮像装置 1004 から被写体までの距離情報を取得するように構成されてもよい。

【0157】

撮像システムの実施形態において、撮像装置 1004 には、上述の実施形態のいずれかの光電変換装置が用いられる。このような構成によれば、画素ごとに精度良く感度調整がなされた画像を取得することができる。

【0158】

[第 8 実施形態]

図 21(a) 及び図 21(b) は、本発明の第 8 実施形態における車載カメラに関する撮像システムの一例を示したものである。撮像システム 2000 は、上述した実施形態の撮像装置(光電変換装置) 1004 を有する。撮像システム 2000 は、撮像装置 1004 により取得された複数の画像データに対し、画像処理を行う画像処理部 2030 と、撮像システム 2000 により取得された複数の画像データから視差(視差画像の位相差)の算出を行う視差算出部 2040 とを有する。また、撮像システム 2000 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 2050 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 2060 とを有する。ここで、視差算出部 2040、距離計測部 2050 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 2060 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA(Field Programmable Gate Array)、ASIC(Application Specific Integrated Circuit)によって実現されてもよいし、これらの組合せによって実現されてもよい。

【0159】

撮像システム 2000 は車両情報取得装置 2310 と接続されており、車速、ヨーレート、舵角等の車両情報を取得することができる。また、撮像システム 2000 は、衝突判定部 2060 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 2410 が接続されている。また、撮像システム 2000 は、衝突判定部 2060 での判定結果に基づいて、ドライバーへ警報を発する警報装置 2420 とも接続されている。例えば、衝突判定部 2060 の判定結果として衝突可能性が高い場合、制御 ECU 2410 はブレーキをかける、アクセルを戻す、エンジン出力を抑制する等して衝突を回避、被害を軽減する車両制御を行う。警報装置 2420 は音等の警報を鳴らす、カーナビゲーションシステム等の画面に警報情報を表示する、シートベルトやステアリングに振動を与える等してユーザに警告を行う。撮像システム 2000 は上述のように車両を制御する動作の制御を行う制御手段として機能する。

【0160】

本実施形態では車両の周囲、例えば前方又は後方を撮像システム 2000 で撮像する。図 21(b) に、車両前方(撮像範囲 2510)を撮像する場合の撮像システムを示した。撮像制御手段としての車両情報取得装置 2310 が、上述の実施形態に記載した動作を行うように撮像システム 2000 又は撮像装置 1004 に指示を送る。撮像装置 1004 の動作は、上述の実施形態と同じなので、ここでは説明を省略する。このような構成により、測距の精度をより向上させることができる。

【0161】

10

20

30

40

50

上述では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御、車線からはみ出さないように自動運転する制御等にも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボット等の移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【0162】

##### 【他の実施形態】

本発明は、上述の実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

10

#### 【0163】

上述の実施形態では、各画素のトランジスタをN型トランジスタにより構成する場合を想定して説明を行ったが、各画素のトランジスタをP型トランジスタにより構成するようにしてもよい。この場合、上述した各駆動信号のレベルは逆になる。また、各画素の回路構成は、図1等に示したものに限定されるものではなく、適宜変更が可能である。例えば、各画素は、1つの画素に2つの光電変換部を有するデュアルピクセル構造であってもよい。

#### 【0164】

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

20

#### 【0165】

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならない。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0166】

30

|                         |                   |

|-------------------------|-------------------|

| 1                       | R画素               |

| 2                       | G <sub>r</sub> 画素 |

| 3                       | G <sub>b</sub> 画素 |

| 4                       | B画素               |

| 1 0 0                   | 光電変換部             |

| 1 0 1                   | 第1の電極             |

| 1 0 2                   | 光電変換層             |

| 1 0 3                   | 第2の電極             |

| 2 0 1                   | 電位供給線             |

| 2 0 6、2 0 7、2 0 8、2 0 9 | 制御線               |

40

【 図 1 】

【図2】

【 図 3 】

【 四 4 】

【図5】

【 図 6 】

Diagram (b) shows a cross-section of a memory cell structure. The structure is bounded by a top layer 101 and a bottom layer 501. A floating gate 506 is positioned above a control gate 502. The floating gate 506 is connected to a bit line 505 through a contact 507. The control gate 502 is connected to a word line 503 through a contact 205. The structure is labeled with various reference numerals: 101, 102, 100, 206, 103, 506, 219, 205, 205, 202, 507, 504, 503, 505, 513, 512, 109, 220, 107, 106, 502, 502, 502, 1, and (b).

## 【 四 7 】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 田代 和昭

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2016-086407 (JP, A)

特開2016-021445 (JP, A)

国際公開第2013/001809 (WO, A1)

特開2009-296276 (JP, A)

特開2016-131367 (JP, A)

特開2015-233027 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 9/04 - 9/11

H01L 27/14 - 27/148