# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 102007901523105 |  |

|--------------------|-----------------|--|

| Data Deposito      | 16/05/2007      |  |

| Data Pubblicazione | 16/11/2008      |  |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 11     | В           |        |             |

Titolo

LETTURA DI CELLE DI MEMORIA NON VOLATILE A LIVELLO MULTIPLO.

## DESCRIZIONE

## Campo tecnico

La presente descrizione fra riferimento genericamente a dispositivi a semiconduttori e, più in particolare, a dispositivi di memoria aventi celle di memoria non volatili a livello multiplo.

#### Fondamento

I dispositivi di memoria sono di norma forniti come circuiti integrati interni, a semiconduttore, in computer o altri dispositivi elettronici. Vi sono molti tipi differenti di memorie, comprese, tra le altre, la memoria ad accesso casuale (RAM), la memoria a sola lettura (ROM), la memoria ad accesso casuale dinamico (DRAM), la memoria ad accesso casuale dinamico sincrono (SDRAM), e la memoria flash.

I dispositivi di memoria flash vengono impiegati come memoria non volatile per un'ampia gamma di applicazioni elettroniche. I dispositivi di memoria flash impiegano di norma una cella di memoria ad un transistore che consente alte densità di memoria, alta affidabilità, e basso consumo di energia elettrica.

Le utilizzazioni per memoria flash includono la memoria per personal computer, assistenti

digitali personali (PDA), videocamere digitali, e telefoni cellulari. Dati di codici di programma e di sistema, quale il sistema di base di ingresso/uscita (BIOS) sono di norma memorizzati in dispositivi di memoria flash. Questa informazione può essere impiegata, tra gli altri, in sistemi a personal computer.

Due tipi comuni di architetture a schiera di memoria flash sono le architetture "NAND" e "NOR", così chiamate per la forma logica in cui è disposta la configurazione base delle celle di memoria di ciascuna.

Una architettura a schiera NAND dispone la sua schiera di celle di memoria a porta flottante in una matrice in modo tale che le porte di ciascuna cella di memoria a porta flottante della schiera siano accoppiate mediante righe a file di selezione di parole. Tuttavia, ciascuna cella di memoria non accoppiata direttamente ad una fila dei bit di colonna mediante il suo pozzo. Invece, le celle di memoria della schiera sono accoppiate insieme in serie, da sorgente a pozzo, tra una fila di sorgenti ed una fila dei bit di colonna.

Le celle di memoria in una architettura a schiera NAND possono essere configurate, ad esempio

programmate, ad uno stato desiderato. Cioè, carica elettrica può essere posta sulla o rimossa dalla porta flottante di una cella di memoria per porre la cella in un numero di stati memorizzati. Ad esempio, una cella a livello singolo (SLC) può rappresentare due stati binari, ad esempio 1 o 0. celle di memoria flash Le possono memorizzare più di due stati binari, ad esempio 1111, 0111, 0011, 1011, 1001, 0001, 0101, 1101, 1100, 0100, 0000, 1000, 1010, 0010, 0110, e 1110. Tali celle possono essere indicate come celle di memoria a multistrato, celle a multibit, o celle a livello multiplo (MLC). Le MLC possono consentire la produzione di memorie a densità maggiore senza aumentare il numero di celle di memoria, dal momento che ciascuna cella può rappresentare più di un bit. Le MLC possono avere più di uno stato programmato, ad esempio una cella in grado di rappresentare quattro bit può avere quindici stati programmati ed uno stato cancellato.

Dal momento che una memoria flash NAND viene soppesata, l'accoppiamento di capacità parassite tra porte flottanti di celle di memoria adiacenti diventa un problema. Un'interferenza da porta flottante a porta flottante può determinare una

distribuzione Vt più ampia quando la distribuzione dovrebbe essere più stretta. Le distribuzioni più ampie possono avere come conseguenza una prestazione degradata di programmazione nonché altri problemi.

Questi problemi per una schiera NAND di celle a livello singolo (SLC) sono perfino maggiori in una schiera NAND di celle a livello multiplo (MLC). Una memoria MLC memorizza più bit su ciascuna cella impiegando differenti livelli di soglia per ciascuno stato che è memorizzato. La differenza tra distribuzioni di tensione di soglie adiacenti può essere molto piccola come confrontata con un dispositivo di memoria SLC. Perciò, gli effetti di un accoppiamento da porta flottante a porta flottante in un dispositivo MLC sono notevolmente aumentati.

## Breve descrizione dei disegni

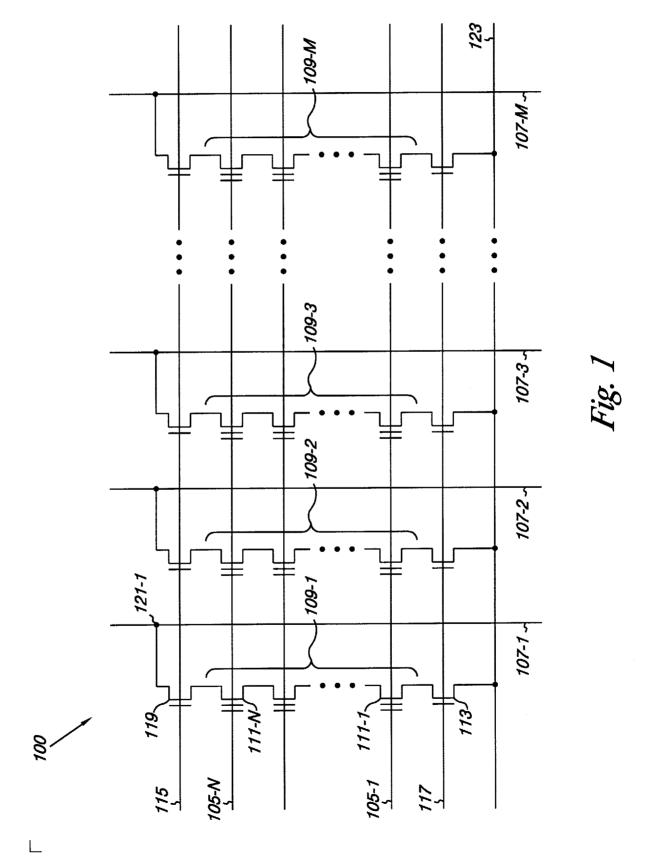

La figura 1 è uno schema di una parte di una schiera di memoria non volatile che può essere impiegata con forme di realizzazione della presente descrizione.

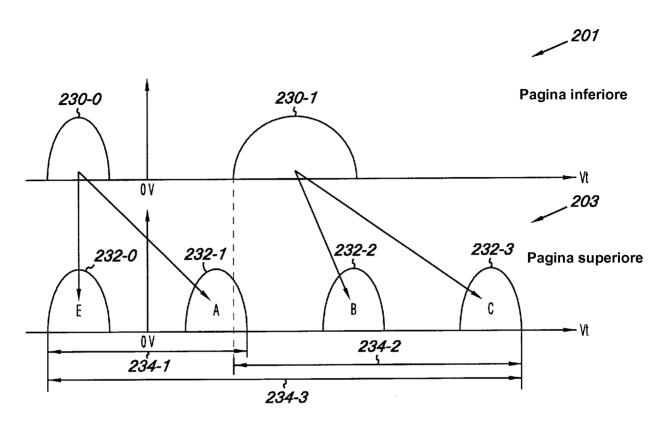

La figura 2A illustra un metodo di programmazione di tecnica antecedente per ridurre l'interferenza da porta flottante a porta

- 7 -

flottante.

La figura 2B illustra un numero di celle di memoria programmate secondo il metodo illustrato in figura 2A.

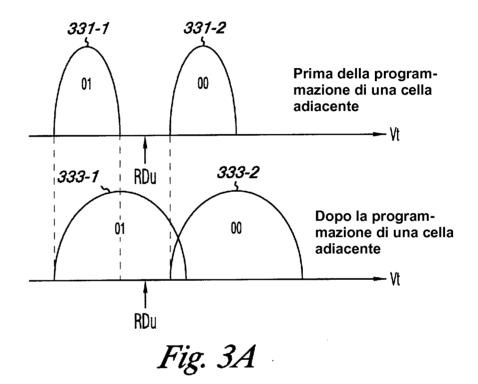

La figura 3A illustra uno schema di distribuzioni Vt associate a celle di memoria prima e dopo interferenza tra porta flottante a porta flottante per effetto della programmazione di celle di memoria adiacenti.

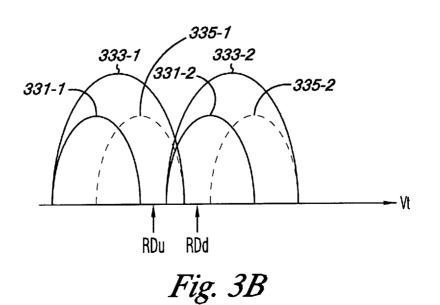

La figura 3B illustra le distribuzioni Vt di figura 3A, comprese componenti di distribuzione Vt perturbate e non perturbate.

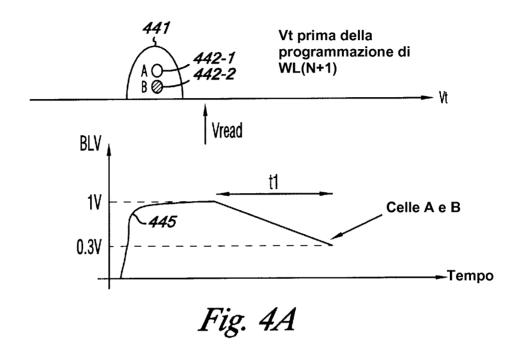

La figura 4A illustra un grafico associato a leggere dati da celle di memoria prima che le celle sperimentino una interferenza da porta flottante a porta flottante.

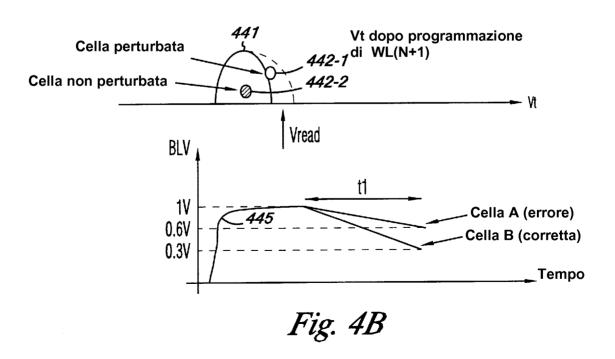

La figura 4B illustra un grafico associato al leggere dati da celle di memoria dopo che le celle hanno sperimentato una interferenza da porta flottante a porta flottante.

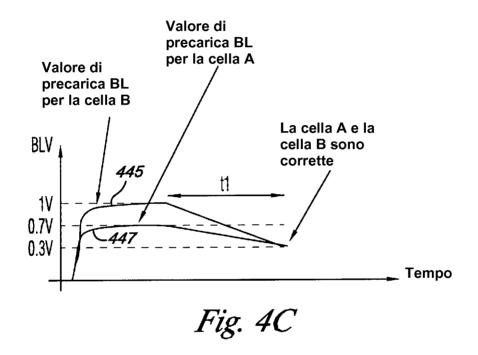

La figura 4C illustra un grafico associato a leggere dati da celle di memoria impiegando un parametro di rilevazione regolato in base alla lettura di celle di memoria adiacenti secondo una forma di realizzazione della presente descrizione.

- 8 -

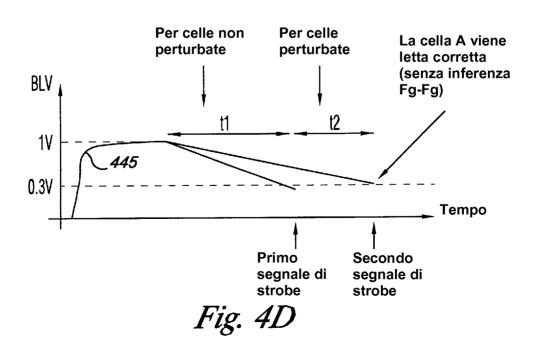

La figura 4D illustra un grafico associato a leggere dati da celle di memoria impiegando un parametro di rilevazione regolato in base ad una lettura di celle di memoria adiacenti secondo un'altra forma di realizzazione della presente descrizione.

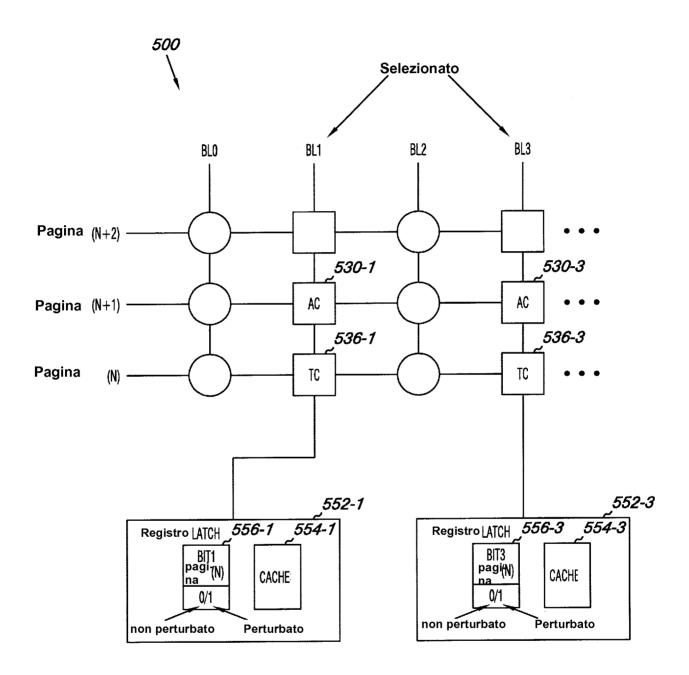

La figura 5 è uno schema di una parte di una schiera di memoria che include celle di memoria che possono essere lette secondo forme di realizzazione della presente descrizione.

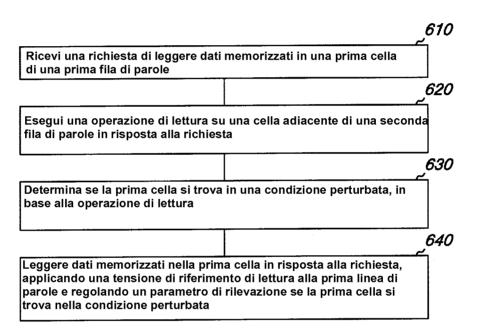

La figura 6 è uno schema a blocchi di un metodo per leggere celle di memoria non volatile a livello multiplo secondo una forma di realizzazione della presente descrizione.

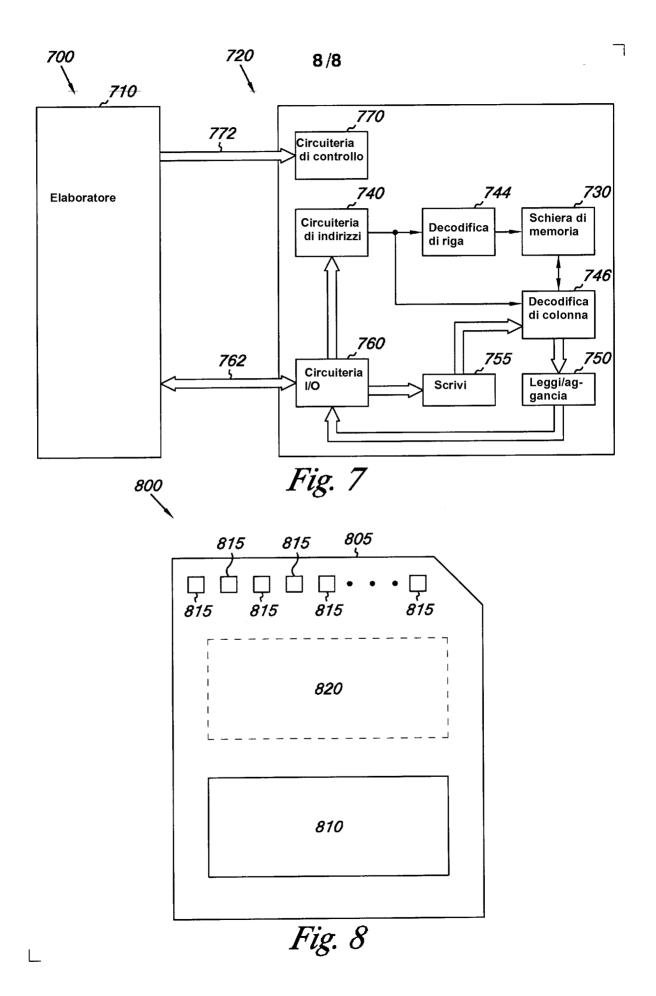

La figura 7 è uno schema a blocchi funzionale di un sistema a memoria elettronica avente almeno un dispositivo di memoria secondo una forma di realizzazione della presente descrizione.

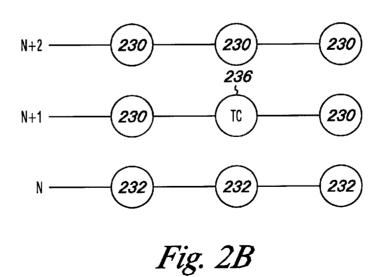

La figura 8 è uno schema a blocchi funzionale di un modulo di memoria avente almeno un dispositivo di memoria secondo una forma di realizzazione della presente descrizione.

# DESCRIZIONE DETTAGLIATA

Le forme di realizzazione della presente invenzione forniscono metodi, dispositivi, moduli,

sistemi per leggere celle di memoria non volatile a livello multiplo. Le varie forme di realizzazione possono compensare sfalsamenti di tensione soglia (Vt) di celle di memoria determinate effetti interferenza da porta flottante a porta flottante (Fg-Fg). Il compensare tali effetti di interferenza Fg-Fg può ridurre o impedire errori di lettura. Le forme di realizzazione della presente descrizione possono compensare una interferenza Fg-Fa dovuta а celle adiacenti, cioè vicine, accoppiate ad una fila adiacente di parole oppure accoppiate ad una fila adiacente di bit.

Una forma di realizzazione di un metodo per leggere celle di memoria in una schiera di celle di memoria non volatile a livello multiplo include ricevere una richiesta di leggere dati memorizzati in una prima cella di una prima fila di parole, eseguire una operazione di lettura sotto una cella adiacente di una seconda fila di parole in risposta alla richiesta, determinare se la prima cella si trova in una condizione perturbata in base alla operazione di lettura. Nelle varie forme di realizzazione, il determinare se la prima cella si trova in una condizione perturbata include il determinare se la Vt della cella adiacente è

aumentata dalla programmazione della prima cella. Il metodo include il leggere dati memorizzati nella prima cella in risposta alla richiesta di lettura applicando alla prima fila di parole una tensione di riferimento di lettura, e regolando un parametro di rilevazione se la prima cella si trova nella condizione perturbata.

Nelle varie forme di realizzazione, la cella accadente alla prima cella può essere sulla stessa fila di parole, ad esempio la prima cella può essere una cella di fila di bit dispari, e la cella adiacente può essere una cella di fila di bit pari. In tali forme di realizzazione, in risposta ad una richiesta di leggere dati memorizzati nella prima cella, ad esempio cella di fila di bit dispari, viene eseguita una operazione di lettura su una cella adiacente accoppiata alla stessa fila di parole, ad esempio una cella di fila di bit pari.

Il parametro di rilevazione regolato può essere modificato in base ad uno stato di dati determinato della cella adiacente. Nella varie forme di realizzazione, la regolazione del parametro di rilevazione include la regolazione della tensione di precarica ella fila di bit in base alla operazione di lettura eseguita sulla

cella adiacente. Nelle varie forme di realizzazione, la regolazione del parametro di rilevazione include la regolazione del periodo di tempo di rilevazione in base alla operazione di lettura eseguita sulla cella adiacente.

Nelle varie forme di realizzazione, la stessa tensione di riferimento di lettura può essere applicata alla prima fila di parole per leggere i dati memorizzati nella prima indipendentemente dal fatto che la prima cella si trovi nella condizione perturbata oppure no. Vale a dire, la stessa tensione di riferimento di lettura può essere impiegata per leggere dati dalla prima cella, indipendentemente dal fatto che la prima cella abbia sperimentato una interferenza Fg-Fg dovuta alla programmazione di una cella adiacente, oppure no. In talune forme di realizzazione, l'eseguire una operazione di lettura sulla cella adiacente include applicare soltanto una tensione di riferimento di lettura alla cella adiacente durante l'operazione di lettura. In tali forme di realizzazione, la tensione di riferimento di lettura può essere una tensione impiegata per determinare se la cella adiacente si trova in uno stato di cancellazione oppure in uno di numerosi stati di programma.

Nella sequente descrizione dettagliata della presente esposizione, si fa riferimento ai disegni annessi che formano una sua parte, ed in cui viene mostrato a titolo di illustrazione come possano essere realizzate le varie forme di realizzazione della descrizione. Oueste forme di realizzazione vengono descritte in dettaglio sufficiente per consentire a coloro che sono di capacità ordinaria nel ramo di realizzare le forme di realizzazione di questa descrizione, e si deve comprendere che impiegate altre forme di possono essere realizzazione, e che variazioni di procedimento elettriche oppure meccaniche possono essere effettuate senza allontanarsi dall'ambito della presente descrizione.

La figura 1 è uno schema di una parte di una schiera di memoria non volatile 100 che può essere impiegata con forme di realizzazione della presente descrizione. La forma di realizzazione di figura 1 illustra una memoria non volatile ad architettura NAND. Tuttavia, le forme di realizzazione descritte in questa sede non sono limitate a questo esempio. Come mostrato in figura 1, la schiera di memoria 100 include file di parole 105-1,...,105-N, e file

di intersezione di bit 107-1,...107-M. Per facilità di indirizzamento nell'ambiente digitale, il numero delle file di parole 105-1,...,105-N ed il numero delle file di bit 107-1,...,107-M sono ciascuna di una potenza di due, ad esempio 256 file di parole per 4096 file di bit.

La schiera di memoria 100 include stringhe NAND 109-1,...,109-M. Ciascuna stringa NAND include celle di memoria non volatile 111-1,...,111-N, ciascuna localizzata alla intersezione di una fila di parole 105-1,...,105-N, ed una fila locale di bit 107-1,...,107-M. Le celle di memoria non volatile 111-1,...,111-N di ciascuna stringa NAND 109-1,...,109-N sono collegate in serie da sorgente a pozzo tra una porta di selezione di sorgente (SGS), ad esempio un transistore ad effetto di campo (FET) 113, ed una porta di selezione di pozzo (SGD), ad esempio un FET 119. La porta di selezione di sorgente 113 è localizzata all'intersezione di una fila locale di bit 107-1 ed una fila di selezione di sorgente 117, mentre la porta di pozzo 119 selezione di è localizzata all'intersezione di una fila locale di bit 107-1 ed una fila di selezione di pozzo 115.

Come mostrato nella forma di realizzazione

illustrata in figura 1, una sorgente di porta 113 di selezione di sorgente è collegata ad una fila 123 di sorgenti comuni. Il pozzo della porta 113 di selezione di sorgente è collegato alla sorgente della cella di memoria 111-1 della corrispondente stringa NAND 109-1. Il pozzo della porta 119 di selezione di pozzo è collegata alla fila locale di bit 107-1 per la corrispondente stringa NAND 109-1 in un contatto di pozzo 121-1. La sorgente della porta 119 di selezione di pozzo è collegata al pozzo dell'ultima cella di memoria 111-N, ad esempio il transistore a porta flottante, della corrispondente stringa NAND 109-1.

forme Nelle varie di realizzazione, la costruzione di celle di memoria non volatile 111-1,...,111-N include una sorgente, un pozzo, una porta flottante o uno strato di immagazzinamento di carica, ed una porta di controllo. Celle di memoria non volatile 111-1,...,111-N hanno le loro porte di controllo accoppiate ad una fila di parole, rispettivamente 105-1,...,105-N. Una colonna delle celle di memoria non volatile 111-1,...,111-N forma stringe NAND, ad esempio 109-1,...,109-N le accoppiate rispettivamente ad una data fila di bit locale, ad esempio 107-1,...,107-M. Una riga delle celle di memoria non volatile è accoppiata in comune ad una data fila di parole, ad esempio 105-1,...,105-N. Una architettura a schiera AND verrebbe disposta in modo simile, tranne che la stringa di celle di memoria sarebbe accoppiata in parallelo tra le porte di selezione.

Sebbene non mostrato in figura 1, come una persona di capacità ordinaria nel ramo comprenderà, e come descritto ulteriormente in questa sede, la schiera 100 è accoppiata ad una varia circuiteria per scrivere dati nelle e leggere dati dalle celle di memoria. Ad esempio, come mostrato in figura 5, le file di bit, ad esempio da 107-1 a 107-M, sono accoppiate ad una circuiteria di rilevazione, ad esempio 552-1 e 552-3 mostrata in figura 5, che può essere impiegata per determinare i dati memorizzati nelle celle di memoria selezionate da 111-1 a 111-N.

La figura 2A illustra un metodo di programmazione di tecnica antecedente per ridurre l'interferenza da porta flottante а flottante, e la figura 2B illustra un numero di celle di memoria programmate secondo il metodo illustrato in figura 2A. Nella figura 2A, il grafico 201 illustra distribuzioni Vt 230-0 e 230-1 per celle dopo un procedimento di programmazione di pagina inferiore, mentre il grafico 203 illustra le distribuzioni di Vt 232-0, 232-1, 232-1 e 232-3 dopo un procedimento di programmazione di pagina superiore. Come una persona di capacità ordinaria nella tecnica comprenderà, le celle di memoria a livello multiplo possono presentare più pagine logiche associate ad esse, che possono essere programmate in passi di programmazione multipli, ad esempio le pagine possono essere programmate in istanti differenti. Il numero di pagine logiche può dipendere dal numero di bit memorizzati dalle celle.

Il metodo mostrato in figura 2A è per celle di memoria non volatile a livello multiplo che memorizzano due bit di dati. Come tale, le celle sono programmate ad uno di quattro stati di dati, ad esempio E, A, B, o C, come mostrato, dopo che è stata programmata sia la pagina inferiore sia la pagina superiore. Vale a dire, nel metodo mostrato nella figura 2, si ipotizza che ciascuna cella di memoria sia una MLC a due bit. Tuttavia, le forme di realizzazione della presente descrizione non sono limitate a MLC che rappresentano 2 bit/cella, ad esempio, in talune forme di realizzazione, la

MLC può rappresentare più o meno di 2 bit/cella.

Nel metodo mostrato in figura 2A, le celle all'interno della distribuzione 230-0, dopo che la loro pagina inferiore è stata programmata, vengono programmate alla distribuzione 232-0 (stato distribuzione 232-1 alla (stato oppure A) corrispondente allo sfalsamento di Vt 234-1, esempio, la quantità massima di sfalsamento di Vt per celle programmate allo stato E o A dalla distribuzione 230-0, ad esempio, uno stato cancellazione. Nel metodo mostrato in figura 2A, le celle all'interno della distribuzione 230-1, dopo che è stata programmata la loro pagina inferiore, vengono programmate alla distribuzione 232-2 (stato oppure alla distribuzione 232-3 B) (stato C) corrispondente allo sfalsamento di Vt 234-2, ad esempio, la quantità massima di sfalsamento di Vt per celle programmate allo stato B oppure C dalla distribuzione 230-1.

La figura 2A illustra inoltre una quantità di sfalsamento di Vt 234-3 corrispondente a ciò che la massima quantità di sfalsamento di Vt delle celle sarebbe se queste fossero programmate secondo un metodo differente, in cui le celle sono state programmate dalla distribuzione 230-0, ad esempio,

lo stato di cancellazione, allo stato di programma superiore C, ad esempio 232-3. Come descritto ulteriormente appresso in collegamento alla figura 2B, le quantità di sfalsamento di Vt associate a celle di memoria di programmazione influenzano gli effetti di interferenza Fg-Fg sperimentate da celle adiacenti programmate in precedenza. Ad esempio, maggiori sono gli sfalsamenti di Vt di una cella che sta venendo programmata, maggiore l'effetto Fg-Fg su una cella adiacente.

Il programmare le pagine logiche associate a celle di memoria a livello multiplo in istanti differenti e/oppure in sequenze differenti è stato inoltre impiegato per ridurre gli effetti di interferenza Fg-Fg. Ad esempio, la figura 2B illustra un numero di celle di memoria adiacenti ad una cella bersaglio (TC) 236. La cella bersaglio 236 è accoppiata ad una fila di parole N+1, che è adiacente alle file di parole N e N+2. In figura 2B, le celle di memoria 232 sulla fila di parole N sono programmate ad un stato finale, ad esempio le celle 232 non ricevono ulteriore programmazione per sfalsare i loro livelli di Vt. Le celle di memoria programmate ad uno stato finale fanno riferimento a celle aventi ciascuna delle loro pagine logiche programmate. Ad esempio, per celle di livello multiplo a due bit, le celle 232 avrebbero programmate sia le loro pagine superiori sia le loro pagine inferiori. Se le celle fossero celle di quattro bit aventi quattro pagine logiche associate, allora tali celle si troverebbero nello stato finale quando tutte e quattro le pagine logiche fossero state programmate.

In figura 2B, le celle 230 adiacenti alla cella 236 sulla fila di parole N+1 e N+2 hanno le loro pagine inferiori associate programmate, ad esempio, si trovano nella distribuzione 230-0 o 230-1 mostrate in figura 2A. La cella di memoria 236 rappresenta una cella programmata ad uno stato finale, ad esempio, una cella programmata allo stato E, A, B, oppure C mostrati in figura 2A. Dal momento che le celle 232 sono programmate ad uno stato finale, i loro livelli di Vt non verranno sfalsati da ulteriori impulsi di programmazione, il che impedisce alle celle 232 di sfalsare il livello Vt programmato della cella bersaglio 236 per effetto dell'interferenza Fg-Fg. Giacché le pagine inferiori delle celle 230 sono state programmate, i loro livelli di Vt verranno sfalsati, al massimo, di una quantità di sfalsamento 234-1 o 234-2 mostrata in figura 2A. Così, il programmare celle di memoria di figura 2B secondo il metodo 2A riduce l'effetto in figura di mostrato interferenza Fq-Fq sperimentato dalla cella bersaglio programmata 236 impedendo alle celle adiacenti 230 di sperimentare una quantità sfalsamento 234-3 dovuta a programmare le celle da uno stato di cancellazione, ad esempio 230-0, ad uno stato di programma superiore 232-3.

Come una persona di capacità ordinaria nella tecnica comprenderà, possono essere impiegati vari schemi di codifica e/oppure algoritmi di programmazione per ridurre l'interferenza Fg-Fg. Le forme di realizzazione della presente descrizione, per leggere celle di memoria non volatile a livello multiplo, possono essere applicate a celle di memoria programmate secondo vari algoritmi, e non sono limitate ad un particolare procedimento di programmazione o schema di codifica quale quello descritto in collegamento con le figure 2A e 2B.

La figura 3A illustra uno schema di distribuzioni di Vt associate a celle di memoria prima (grafico superiore) e dopo (grafico inferiore) dell'interferenza da porta flottante a porta flottante per effetto della programmazione di

celle di memoria adiacenti. La figura 3B illustra la distribuzione di Vt di figura 3A, che includono le componenti di distribuzione di Vt perturbate e non perturbate.

L'esempio illustrato in figura 3A mostra due distribuzioni adiacenti di programma 331-1 e 331-2 associate a celle di memoria prima che sia stata programmata una cella di memoria adiacente, ad esempio prima dell'interferenza Fg-Fg. In questo esempio, la distribuzione 331-1 rappresenta celle che memorizzano dati logici "01", ad esempio, "1" è memorizzato nella sua pagina inferiore, e "0" è memorizzato nella sua pagina superiore. La distribuzione 331-2 rappresenta celle che memorizzano dati logici "00", ad esempio, "0" è memorizzato nella sua pagina inferiore e nella sua pagina superiore. Come sopra descritto, le pagine inferiori e superiori associate a celle di memoria non volatile a livello multiplo possono essere programmate separatamente, ad esempio programmate in istanti differenti. Inoltre, un'operazione di lettura su una cella, avente associate pagine multiple, può includere leggere una delle pagine, ad esempio la pagina superiore o la pagina inferiore.

L'esempio illustrato nella figura 3A include inoltre una tensione di riferimento di lettura RDu. La tensione di riferimento di lettura RDu può essere applicata alla fila di parole di una cella selezionata durante una operazione di lettura, per determinare se la cella memorizza dati "01" o "00", ad esempio per distinguere tra gli stati dei dati determinando se la Vt della cella selezionata sia sopra o sotto il livello di RDu. Come una persona di capacità ordinaria nella tecnica comprenderà, le celle di memoria non volatile di livello multiplo possono avere un insieme, ad esempio un numero di tensioni di riferimento di lettura associate aventi valori tra stati adiacenti di programma, che possono essere impiegati per determinare lo stato reale dei dati della cella durante una operazione di lettura.

Le distribuzioni di Vt 333-1 e 333-2 mostrate in figura ЗА illustrano le rispettivamente distribuzioni di Vt 331-1 e 332-1, dopo sperimentato uno sfalsamento di Vt corrispondente ad interferenza Fq-Fq determinata dalla una programmazione di una cella di memoria adiacente, ad esempio una cella di memoria su una fila vicina di parole. Vale a dire, le distribuzioni di Vt 3331 e 333-2 rappresentano le distribuzioni totali di Vt per celle di memoria che hanno e non hanno sperimentato interferenza di Fg-Fg per effetto della programmazione di celle adiacenti.

Come mostrato nel grafico inferiore di figura 3A. l'interferenza Fq-Fq può determinare sovrapposizione delle distribuzioni di Vt 333-1 e 333-2, in modo tale che la tensione di riferimento di lettura RDu non possa più essere impiegata per distinguere accuratamente tra i due stati di dati "01" e "00". Vale a dire, alcune celle programmate all'interno di una distribuzione 331-1 possono essere state perturbate, ad esempio sperimentato uno sfalsamento di Vt verso l'alto, per effetto della programmazione di una cella adiacente, in modo tale che l'utilizzare RDu per leggere dati da celle programmate a "01" può avere come conseguenza che la cella viene letta come memorizzante dati incorretti, ad esempio, "00" invece di "01".

La figura 3B illustra le distribuzioni totali di Vt 333-1 e 333-2 di figura 3A, che includono le componenti di distribuzione di Vt perturbate e non perturbate. Nell'esempio di figura 3B, le distribuzioni di Vt 331-1e 331-2 sono stati adiacenti di programma, ad esempio "01" e "00" in

questo esempio, che non sono stati perturbati, ad esempio non hanno sperimentato uno sfalsamento di Vt per effetto della programmazione di una cella di memoria adiacente. Le distribuzioni di Vt 335-1 e 335-2 rappresentano distribuzioni perturbate. Vale distribuzioni 335-1 dire. le е 335 - 2rappresentano uno sfalsamento di Vt verso l'alto delle celle che sono state programmate rispettivamente ad uno stato di dati 331-1 e 331-2.

Per esempio, consideriamo un numero di celle di una fila di parole selezionate, alcune delle quali sono state programmate ad uno stato di dati 331-1 ("01") ed alcune delle quali sono state programmate a uno stato di dati 331-2 ("00"). In seguito alla programmazione delle celle della fila di parole selezionata, un numero di celle adiacenti alle celle della fila di parole selezionata, ad esempio le celle di una fila di parole adiacenti che condividono una fila di bit, sperimentano una programmazione. Alcune delle celle adiacenti presenteranno un livello Vt aumentato per effetto della programmazione successiva, e perturberanno le celle programmate della fila di parole selezionata, ad esempio i livelli di Vt modificati delle celle adiacenti determineranno una crescita del livello Vt delle celle della fila di parole selezionata in modo tale che quelle celle della fila di parole selezionata appartengano a distribuzioni di Vt 335-1 e 335-2 perturbate.

D'altro canto, celle adiacenti che non presentano un livello Vt aumentato per effetto della programmazione successiva non perturberanno celle programmate della fila di parole selezionata, in modo tale che quelle appartengano a distribuzioni di Vt non perturbate 331-1 e 331-2. Come tale, in questo esempio, le celle di memoria programmate della fila di parole selezionata apparterranno a distribuzioni perturbate 331-1 e 331-2 oppure a distribuzioni perturbate 335-1 e 335-2, a seconda degli sfalsamenti di livello Vt sperimentati dalle celle successivamente. adiacenti programmate Come mostrato in figura 3B, la tensione di riferimento di lettura RDu può essere impiegate per leggere celle non perturbate, ad esempio per distinguere tra celle all'interno della distribuzione 331-1 e 331-2. La tensione di riferimento di lettura RDd impiegata per leggere può essere le celle perturbate, ad esempio per distinguere tra celle all'interno della distribuzione 335-1 e 335-2.

Perciò, l'eseguire una operazione lettura su una cella adiacente, ad esempio una cella vicina accoppiata ad una fila di parole adiacente e che condivide una fila di bit con una cella bersaglio da leggere oppure una cella vicina accoppiata ad una fila di bit adiacente alla fila di bit della cella bersaglio, óuq essere impiegata determinare se la cella bersaglio appartenga ad una distribuzione perturbata, ad esempio 335-1 e 335-2, oppure ad una distribuzione non perturbata, ad esempio 331-1 e 331-2. La lettura della cella adiacente può essere impiegata per determinare se cella adiacente la abbia sperimentato sfalsamento di Vt successivo alla programmazione della cella bersaglio ad uno stato finale.

Come tale, in varie forme di realizzazione della presente descrizione, viene eseguita una operazione di lettura su una cella adiacente ad una cella bersaglio in risposta ad una richiesta di leggere dati memorizzati nella cella bersaglio. Vale a dire, quando viene ricevuta una richiesta di leggere dati da una cella bersaglio, viene dapprima eseguita la lettura di una cella adiacente. In tali forme di realizzazione, la lettura della cella adiacente viene impiegata per determinare un

parametro di rilevazione da impiegare per leggere la cella bersaglio.

Nelle varie forme di realizzazione, e come descritto in maggiore dettaglio in collegamento con le figure 4-6, il leggere dati memorizzati in una cella bersaglio in risposta ad una richiesta di include l'applicare lettura una tensione di riferimento di lettura alla fila di parole della cella bersaglio, e regolare un parametro rilevazione se viene determinato che la cella bersaglio si trova in una condizione perturbata, in base ad una operazione di lettura eseguita su una cella adiacente. Nelle varie forme di realizzazione, la regolazione del parametro regolazione, quale la tensione di precarica della fila di bit oppure il periodo di rilevazione della fila di bit, può compensare l'interferenza Fg-Fg e può ridurre o impedire letture erronee di dati.

La figura 4A illustra un grafico associato a leggere dati da celle di memoria di una fila di parole selezionata, ad esempio WL(N), prima che le l'interferenza celle sperimentino da porta flottante a porta flottante, ad esempio prima che i livelli di Vt delle celle sperimentino sfalsamento per effetto di una programmazione

successiva di celle adiacenti su una fila di parole adiacente, ad esempio WL(N+1). La forma realizzazione illustrata in figura 4A mostra due celle di memoria, ad esempio la cella A 442-1 e la cella B 442-2 aventi livelli di Vt all'interno della distribuzione di Vt 441. La distribuzione 441 rappresenta uno stato di programma particolare, ad esempio "01", "00", "10", oppure "11", al quale sono state programmate le celle 442-1 e 442-2. Le celle 442-1 e 442-2 sono celle di una fila di parole selezionata che possono essere programmate e lette allo stesso tempo. Ad esempio, le celle 442-1 e 442-2 possono essere celle corrispondenti ad una pagina di dati particolare. In talune forme di realizzazione, le celle 442-1 e 442-2 possono essere entrambe associate ad una fila di bit pari oppure ad una fila di bit dispari, ad esempio una pagina pari oppure una pagina dispari di dati.

Durante una operazione di lettura, una tensione di riferimento di lettura, Vread, viene applicata alla fila di parole selezionata, ad esempio alla porta di controllo delle celle 442-1 e 442-2, mentre una tensione passante viene applicata a file di parole non selezionata, in modo tale che le celle delle file di parole non selezionata

vengano fatte diventare "on", e conducano corrente tra la sua sorgente ed il pozzo. Se Vread è minore del livello Vt della cella, allora la cella sarà "off", e non condurrà corrente oppure condurrà meno corrente di quando la cella è "on". Nelle varie forme di realizzazione, il livello di tensione di una fila di bit può essere rilevato da un modulo di rilevazione accoppiato alla fila di bit, ad esempio il modulo di rilevazione 552-1 oppure 552-3 mostrato in figura 5.

Nelle varie forme di realizzazione, le file di bit associate alle celle che stanno venendo lette, esempio le celle 442-1 e 442-2, vengono ad precaricate ad un livello particolare di tensione di precarica, ad esempio il livello di tensione di precarica 445. In questo esempio, il livello della tensione di precarica 445 è 1,0 V. Tuttavia, le forme di realizzazione della presente descrizione non sono limitate ad una particolare tensione della fila di bit di precarica. In tali forme di realizzazione, il livello di tensione della fila di bit diminuisce appena la corrente fluisce tra sorgente e pozzo, a seconda della tensione di riferimento di lettura applicata alla fila di parole selezionata. Nelle varie forme di realizzazione, lo stato di una cella che sta venendo letta può essere determinato in base al fatto che la tensione della fila di bit si scarichi di una quantità predeterminata durante un periodo predeterminato di rilevazione della fila di bit, oppure in base al fatto che la tensione della fila di bit raggiunga un predeterminato valore di soglia durante il predeterminato periodo di rilevazione.

esempio, nelle forme di realizzazione mostrate nelle figure 4A-4D, una cella di memoria 442-1/442-2 viene considerata essere "off", ad esempio nello stato 441, se la tensione della fila di bit BLV si scarica più di 500 mV, ad esempio se la BLV diminuisce di più di 500 mV dalla tensione di precarica di 1,0V 445 durante il periodo tl di rilevazione della fila di bit. Se la BLV si scarica meno di 500 mV durante il periodo di rilevazione tl, allora la cella viene considerata essere "on" ad esempio non nello stato 441. Nelle varie forme di realizzazione, il periodo di rilevazione tl può essere circa 5 millisecondi. Tuttavia, il tempo del periodo di rilevazione tl può dipendere da vari fattori, e le forme di realizzazione della presente descrizione non sono limitate ad un particolare periodo di rilevazione della fila di bit.

Come mostrato nella forma di realizzazione illustrata nella figura 4A, la tensione della fila di bit per entrambe le celle 442-1 e 442-2 si scarica per più della quantità predeterminata, ad esempio 500 mV, durante il periodo di rilevazione tl. In questo esempio, la BLV si scarica di 700 mV, ad esempio dalla tensione di precarica di 1,0 V 445 a 0,3 V, durante il periodo di rilevazione tl. Vale a dire, prima della programmazione di celle su una fila di parole adiacente alla fila di parole selezionata, entrambe le celle 442-1 e 442-2 vengono determinate essere nello stato corretto di programma 441, ad esempio lo stato al quale le celle 442-1 e 442-1 sono state programmate durante la lettura di dati.

La figura 4B illustra un grafico associato a leggere dati da celle di memoria di una fila di parole selezionata, ad esempio WL(N), dopo che le celle hanno sperimentato una interferenza da porta flottante a porta flottante, ad esempio dopo che celle adiacenti di una fila di parole adiacente, ad esempio WL(N+1), hanno sperimentato una programmazione successiva che può influenzare i livelli di Vt delle celle che stanno venendo lette. La forma di realizzazione illustrata in figura 4B

mostra le due celle di memoria programmate 442-1 e 442-2 di figura 4A, dopo che le celle adiacenti alle celle 442-1 e 442-2 hanno sperimentato una programmazione, ad esempio le celle adiacenti sono state programmate successivamente alle celle 442-1 e 442-2.

Nell'esempio mostrato in figura 4B, la cella 442-1 rappresenta una cella perturbata e la cella 442-2 rappresenta una cella non perturbata. Vale a dire, come mostrato in figura 4B, il livello Vt della cella 442-1 è stato sfalsato verso l'alto per effetto dell'interferenza Fg-Fg a causa programmazione di una cella su una fila di parole adiacente, ad esempio WL(N+1), mentre il livello Vt della cella 442-2 non viene influenzato dalla programmazione successiva della cella della fila di parole adiacente. Vale a dire, come mostrato nel figura 4B, dopo che grafico di sono state programmate le celle adiacenti su WL(N+1), leggere una cella A 442-1 impiegando Vread ha come consequenza un errore di lettura. Vale a dire, in questo esempio, il leggere una cella A in Vread ha come consequenza che la tensione della fila di bit BLV corrispondente alla cella A 442-1 si scarichi di 400 mV, ad esempio dalla BLV di precarica di 1,0

V a 0,6 V, durante il periodo di rilevazione tl. Deriva un errore di lettura dal momento che la BLV associata alla cella A si scarica di meno della quantità predeterminata, ad esempio 500 mV in questo esempio, durante tl. La scarica di 400 mV della fila di bit della cella A durante tl indica che la cella A è "off" in modo tale che un modulo di rilevazione accoppiato alla fila di bit della cella A dovrebbe determinare che la cella A non si trova nello stato 441 al quale la cella A era stata programmata.

D'altro canto, la BLV associata alla cella non perturbata, ad esempio la cella B 442-2, si scarica di più di 500 mV, ad esempio di 700 mV in questo caso, in risposta alla tensione di riferimento di lettura applicata Vread. Vale a dire, la BLV associata alla cella B dopo il periodo di rilevazione tl indica che la cella B è "on", in modo tale che un modulo di rilevazione dovrebbe determinare che la cella B si trova nello stato 441, ad esempi lo stato corretto al quale la cella B era stata programmata.

Come una persona di capacità ordinaria nella tecnica comprenderà, e come sopra descritto, la quantità di interferenza Fg-Fg, per esempio la

quantità di sfalsamento del livello Vt. sperimentata da una cella bersaglio, ad esempio una cella su WL(N), può dipendere dallo stato dei dati al quale era stata programmata la cella adiacente, esempio la cella adiacente su WL(N+1). esempio, se le celle adiacenti su WL(N+1) vengono programmate secondo il metodo mostrato nella figura 2A, in modo tale che le celle di WL(N+1) si trovino nello stato di dati E, A, B, oppure C, allora interferenza Fg-Fg sperimentata dalle celle su WL(N) sarà differente, a seconda delle differenti quantità di sfalsamento di Vt 234-1, 234-2, 234-3 delle celle WL(N+1).

Le varie forme di realizzazione della presente descrizione possono ridurre o impedire errori associati alla lettura di celle di memoria di una prima fila di parole, ad esempio WL(N), compensando gli effetti dell'interferenza Fg/Fg determinati dalla programmazione di celle adiacenti di una fila di parole adiacente, ad esempio WL(N+1). Ad esempio, come descritto ulteriormente appresso in collegamento con le figura 4C e 4D, in varie forme di realizzazione, un parametro di relazione, impiegato per leggere le celle A e B mostrate nelle figura 4A e 4B può essere regolato in base ad una

operazione di lettura eseguita su celle di una fila di parole adiacente  $WL\left(N+1\right)$ .

Nelle varie forme di realizzazione, ilparametro di rilevazione regolato può essere una tensione regolata della fila di bit di precarica e/oppure un periodo regolato di rilevazione della fila di bit. In tali forme di realizzazione, e come descritto ulteriormente in collegamento con figure 4C e 4D, l'impiegare il parametro rilevazione regolato può compensare gli effetti di interferenza Fg-Fg leggendo la cella perturbata come se questa avesse un livello Vt non perturbato, ad esempio come se il livello Vt della cella perturbata fosse minore del livello Vt attuale della cella. In tali forme di realizzazione, viene impiegato un parametro di rilevazione non regolato per leggere dati da celle che è stato determinato trovarsi in una condizione non perturbata in base alla operazione di lettura eseguita sulla cella della fila di parole adiacente.

Nelle varie forme di realizzazione, in risposta ad una richiesta di leggere dati da una cella bersaglio WL(N), viene eseguita una operazione di lettura su una cella WL(N+1) adiacente alla cella bersaglio, per compensare

possibili effetti di interferenza Fg-Fg della cella WL(N+1) sullo stato programmato della bersaglio WL(N). In talune forme di realizzazione, la lettura eseguita sulla cella adiacente include il determinare i dati reali WL(N+1)memorizzati nella cella adiacente, ad esempio lo stato programmato dei dati della cella adiacente. In tali forme di realizzazione, possono essere eseguite più operazioni di lettura impiegando differenti tensioni di riferimento di lettura applicate a WL(N+1) per determinare uno stato particolare dei dati della cella adiacente. I dati di WL(N+1) determinati possono essere memorizzati in una cache, ad esempio la cache 554-1/554-3 mostrata in figura 5. Ciascuno degli stati dei dati programmati della cella adiacente di WL(N+1) può presentare un differente effetto di interferenza Fg-Fg sul livello Vt della cella bersaglio di WL(N), dipendendo ad esempio dallo schema codifica oppure dall'algoritmo di programmazione ecc.

Perciò, nelle varie forme di realizzazione, non tutti gli stati dei dati a cui può essere programmata la cella adiacente sono stati per cui l'interferenza Fg-Fg viene compensata. Vale a dire,

nelle varie forme di realizzazione, un parametro di rilevazione regolato, ad esempio una tensione della fila di bit di precarica regolata, viene impiegato soltanto per leggere una cella bersaglio di WL(N) se lo stato dei dati determinato dalla lettura della cella adiacente WL(N+1) si trova in uno stato avente una quantità associata di sfalsamento di Vt, ad esempio 234-1, 234-2 oppure 234-3 mostrata in figura 2A, a oppure sopra un preciso valore di soglia, ad esempio, tra gli altri valori, 1,5 V, 2,0 V, oppure 2,5 V. In tali forme di realizzazione, una tensione di precarica regolata impiegata per leggere una cella WL(N) bersaglio perturbata può essere modificata in base ai dati determinati della cella WL(N+1) e/oppure in base alla quantità di sfalsamento di Vt associata ad essi. Vale a dire, possono essere impiegate differenti tensioni regolate di precarica della fila di bit, ad esempio 0,4 V, 0,6 V, 0,8 V per leggere una cella bersaglio WL(N) perturbata, a seconda dello stato particolare o del livello Vt della cella adiacente WL(N+1).

In talune forme di realizzazione, l'operazione di lettura eseguita sulla cella adiacente WL(N+1) non coinvolge il determinare i dati reali

memorizzati nella cella adiacente. Ad esempio, in talune forme di realizzazione, la lettura della cella WL(N+1) include l'impiegare un'unica tensione di riferimento di lettura per determinare se cella WL(N+1) abbia un livello Vt sopra o sotto il particolare valore della tensione di riferimento di esempio, in talune lettura. Come forme realizzazione, l'operazione di lettura eseguita sulla cella WL(N+1) viene effettuata impiegando un'unica tensione di riferimento di lettura per determinare se la cella WL(N+1) si trovi in uno di cancellazione. In tali forme di stato realizzazione, la tensione di riferimento di lettura può essere 0 V oppure un'altra tensione, ad esempio 0,1 V, 0,5 V, tra le altre tensioni di riferimento di lettura che possono essere impiegate per distinguere tra uno stato di cancellazione ed uno o più stati di programma.

Una indicazione se la cella WL(N+1) si trovi nello stato di cancellazione può essere memorizzata in un registro latch di dati associato alla corrispondente fila di bit della cella WL(N+1).Ad esempio, il registro latch di dati può memorizzare livello logico basso, ad esempio "0", se la cella WL(N+1) si trova nello stato di cancellazione, e

una livello logico alto, ad esempio "1", se la WL(N+1) si trova in uno stato diverso dallo stato di cancellazione, ad esempio lo stato A, B, oppure C.

In tali forme di realizzazione, la circuiteria di rilevazione, ad esempio il modulo di rilevazione 552-1/552-3 mostrato in figura 5, associato alla fila di bit corrispondente alla cella bersaglio della fila di parole WL(N), può verificare il registro latch di dati durante una lettura di dati eseguita sulla cella bersaglio. Un primo parametro di rilevazione può essere impiegato per leggere dati dalla cella bersaglio di WL(N) se il registro latch di dati memorizza uno "0" logico, ad esempio la cella adiacente di WL(N+1) si trova nello stato di cancellazione. Un parametro di rilevazione differente può essere impiegato per leggere dati dalla cella bersaglio di WL(N), se il registro latch di dati memorizza un "1" logico, ad esempio la cella adiacente di WL(N+1) non si trova nello di cancellazione. In tali stato forme di realizzazione, la cella può essere determinata essere in una condizione non perturbata se il registro latch di dati memorizza uno "0" logico, e può essere determinato trovarsi in una condizione non perturbata se il registro latch di memorizza un "1" logico. Vale a dire, si ipotizzare che la cella adiacente di WL(N+1) abbia influenzato la cella bersaglio WL(N) se cella WL(N+1)si trova nello stato di cancellazione, dal momento che il suo livello Vt livello sfalsato dalla di stato cancellazione durante una programmazione.

Come esempio, e come mostrato nella figura 4C, óuq essere impiegata una prima tensione precarica della fila di bit, ad esempio 1,0 V, per leggere dati dalla cella bersaglio di WL(N) se il registro latch di dati memorizza uno "0" logico, ed tensione della fila di bit di precarica una differente, ad esempio una tensione regolata della fila di bit di precarica, per leggere dati dalla cella bersaglio di WL(N) se il registro latch di dati memorizza un "1" logico. In tali forme di realizzazione, la stessa tensione di riferimento di lettura può essere impiegata per leggere i dati della cella bersaglio indipendentemente dal fatto che il registro latch di dati memorizzi uno "0" oppure un "1". Vale a dire, la stessa tensione, ad esempio Vread, di quella mostrata nelle figure 4A e 4B può essere applicata alla fila bersaglio di parole WL(N), indipendentemente dal fatto che si determini che la cella bersaglio si trova in una condizione perturbata oppure no. In questo modo, i dati della cella bersaglio possono essere determinati senza dover più applicare tensioni di di alla fila riferimento lettura di bersaglio WL(N).

La figura 4C illustra un grafico associato a leggere dati da celle di memoria impiegando un parametro di rilevazione regolato in base ad una lettura di celle di memoria adiacenti secondo la forma di realizzazione della presente descrizione. Il grafico mostrato nella forma di realizzazione di figura 4C illustra una prima tensione di precarica 445 delle file di bit impiegata per leggere una cella di memoria 442-2 mostrata nelle figura 4A e 4B, ad esempio una cella di memoria su una fila di parole selezionata, quale WL(N), programmata allo stato di dati 442, e determinata trovarsi in una condizione non perturbata in base ad una operazione di lettura eseguita su una cella adiacente della fila di parole WL(N+1). Il grafico mostrato nella forma di realizzazione di figura 4C illustra inoltre una differente tensione di precarica 447 della fila di bit, ad esempio una tensione di

precarica regolata della fila di bit, impiegata per leggere una cella di memoria 442-1 mostrata nelle figura 4A e 4B, ad esempio una cella di memoria su una parola selezionata WL(N) programmata allo stato dei dati 442 e determinata trovarsi in una condizione perturbata in base ad una operazione di lettura eseguita sulla cella adiacente della fila di parole WL(N+1).

menzionato е descritto Come sopra ulteriormente in collegamento la figura 5, un indicatore di stato di perturbazione può essere memorizzato in un registro latch di dati associato alla fila di bit della cella di memoria bersaglio WL(N) ed alla cella adiacente WL(N+1) in base ad una operazione di lettura eseguita sulla cella WL(N+1). Ad esempio, un "1" logico può essere memorizzato nel registro latch di dati per indicare che il livello Vt della cella adiacente di WL(N+1) si è sfalsato, successivamente alla programmazione della cella bersaglio di WL(N), di una quantità sufficiente a porre la cella bersaglio in una condizione perturbata. In tali casi, uno "0" logico può essere memorizzato nel latch di dati per indicare che il livello Vt della cella adiacente di alla WL(N+1) non si è sfalsato in seguito

programmazione della cella bersaglio di WL(N), di una quantità sufficiente a porre la cella bersaglio in una condizione perturbata. In tali forme di realizzazione, può essere verificato l'indicatore dello stato di perturbazione memorizzato nel registro latch di dati, per determinare, se oppure no, un parametro di rilevazione regolato, ad esempio una tensione di precarica regolata della fila di bit e/oppure un periodo regolato di rilevazione della fila di bit venga impiegato per leggere la cella bersaglio di WL(N).

Ιl grafico mostrato nella forma di realizzazione di figura 4C illustra un metodo per leggere dati memorizzati in celle di memoria, ad esempio 442-1 e 442-2, che sono state programmate allo stesso stato di dati, ad esempio 441, tuttavia possono avere sperimentato differenti effetti di effetto interferenza Fq-Fq per di programmazione successiva di celle di memoria adiacenti. Il metodo mostrato in figura 4C illustra la compensazione di effetti di interferenza Fg-Fg sperimentati da una cella programmata A 442-1, in modo tale che sia la cella A 442-1, ad esempio una cella perturbata, sia la cella 442-2, ad esempio cella non perturbata, vengano una lette correttamente in base ad una particolare tensione di riferimento di lettura applicata, ad esempio Vread, come mostrato nelle figure 4A e 4B.

Nella forma di realizzazione di figura 4C, una tensione di precarica regolata della fila di bit impiegata per 447 viene leggere una cella perturbata 442-1 per compensare la quantità di sfalsamento di Vt sperimentata dalla cella 442-1 per effetto dell'interferenza Fg-Fg. Nella forma di realizzazione di figura 4C, l'impiegare tensione di precarica regolata 447 della fila di bit, ad esempio 0,7 V in questo esempio, ha come una circuiteria di consequenza rilevazione accoppiata alla corrispondente fila di bit che determina che la cella 442-1 è diventata "off" in risposta all'applicazione di Vread alla fila di parole WL(N), ad esempio alla porta di controllo della cella 442-1 durante il periodo di rilevazione tl. Vale a dire, in figura 4, si determina che la cella A 442-1 ha un livello Vt minore di Vread, ad esempio, un livello Vt corrispondente allo stato di dati 441 mostrato in figura 4B, piuttosto che si determina che ha un livello Vt maggiore di Vread, ad esempio, un livello Vt corrispondente ad uno stato di dati differente da 441, avendo come

conseguenza un errore di lettura come mostrato in figura 4B.

Come sopra descritto in collegamento con figura 4B, l'impiegare la stessa tensione di precarica 445 della fila di bit, ad esempio, 1,0 V, per leggere sia una cella A perturbata 442-1, sia cella perturbata 442-2 ha una В non conseguenza che la fila di bit associata alla cella A perturbata viene scaricata meno della quantità di soglia, ad esempio meno di 500 mV nell'esempio di figura 4B, durante il periodo di rilevazione tl, per effetto del livello Vt aumentato della cella A perturbata. Come mostrato in figura 4C, l'impiegare una tensione di precarica ridotta 447 della fila di bit, ad esempio 0,7 V nell'esempio, per leggere la cella A perturbata 442-1, può compensare il livello accresciuto di Vt della cella A per effetto dell'interferenza Fg-Fg facendo sì che la tensione della fila di bit si scarichi allo stesso livello, ad esempio, 0,3 V, come mostrato, per la cella A perturbata 442-1 e per la cella B non perturbata 442-2.

Nella forma di realizzazione illustrata in figura 4C, un unico segnale di strobe, ad esempio, un'unica operazione di rilevazione, può essere

impiegato per leggere le celle perturbate, ad esempio la cella A 442-1, e le celle perturbate, ad esempio la cella B 442-2, su una fila di parole selezionata, ad esempio WL(N). Ad esempio, unica operazione di lettura impiegante una particolare tensione di riferimento di lettura, ad esempio Vread, applicata alla fila di selezionata WL(N), ed un particolare periodo di rilevazione, ad esempio tl, possono essere impiegati per leggere le celle perturbate e non perturbate programmate ad un particolare stato di dati, ad esempio 441, come mostrato in figura 4B. Durante l'unico segnale di strobe, le celle WL(N) che è stato determinato che si trovano nella condizione non perturbata, in base ad una lettura delle celle adiacenti WL(N+1), presentano le loro corrispondenti file di bit precaricate alla tensione di precarica non regolata 445 della fila di bit, e le celle che è stato determinato che si trovano nella condizione perturbata, in base alla lettura delle celle WL(N+1) adiacenti, avranno le loro corrispondenti file di bit precaricate alla tensione di precarica regolata 447 della fila di bit. L'impiegare un unico segnale di strobe con una tensione di riferimento di lettura ed un periodo di rilevazione particolari può ridurre il tempo richiesto per leggere dati dalle celle  $WL\left(N\right)$  selezionate.

Come sopra descritto, la particolare tensione di precarica regolata della fila di bit impiegata per leggere le celle di memoria WL(N) che è stato determinato che si trovano in una condizione perturbata, in base ad una operazione di lettura eseguita su una WL(N+1) adiacente, può dipendere dai dati WL(N+1) determinati, ad esempio lo stato particolare dei dati della cella WL(N+1) adiacente e/oppure la quantità di sfalsamento del livello Vt associata alla sua programmazione. Vale a dire, la tensione di precarica della fila di bit impiegata per leggere celle WL(N), che è stato determinato che si trovano in una condizione non perturbata, e la tensione di precarica regolata della fila di bit impiegata per leggere le celle WL(N), che è stato determinato che si trovano in una condizione perturbata, non sono limitate agli esempi mostrati nelle figure 4A-4D.

La figura 4D illustra un grafico associato a leggere dati da celle di memoria impiegando un parametro di rilevazione regolato in base ad una lettura di celle di memoria adiacenti secondo

un'altra forma di realizzazione della presente descrizione. Il grafico mostrato nella forma di realizzazione di figura 4D illustra un periodo di rilevazione t1 impiegato per leggere una cella di memoria 442-2 mostrata nelle figure 4A e 4B, ad esempio, una cella di memoria su una fila di parole selezionata, quale WL(N), programmata allo stato di dati 441 e che è stato determinato che si trova in una condizione non perturbata in base ad una operazione di lettura eseguita su una cella adiacente della fila di parole WL(N+1). Il grafico mostrato nella forma di realizzazione di figura 4D illustra inoltre un periodo in relazione differente t1+t2, ad esempio un periodo regolato di rilevazione della fila di bit, impiegato per leggere la cella di memoria 442-1 mostrata nelle figure 4A e 4B, ad esempio, una cella di memoria su una parola selezionata WL(N) programmata allo stato 441 dei dati, e che è stato determinato che si trova in una condizione perturbata in base ad lettura eseguita sulla cella un'operazione di adiacente della fila di parole WL(N+1). Nelle varie forme di realizzazione, il periodo di rilevazione t1 è circa di 5 microsecondi, ed il periodo di rilevazione t2 è di circa 2 microsecondi. Tuttavia,

i periodi di rilevazione t1 e t2 possono dipendere da vari fattori quale, fra gli altri fattori, lo stato di dati determinato della cella adiacente WL(N+1), e le forme di realizzazione della presente descrizione non sono limitate ad un particolare valore di tempo per rilevare un periodo t1 e/oppure t2.

grafico mostrato nella forma di realizzazione di figura 4D illustra un metodo per leggere dati memorizzati in celle di memoria, ad esempio 442-1 e 442-2, che sono state programmate allo stesso stato di dati, ad esempio 441, tuttavia possono avere sperimentato differenti effetti di interferenza Fg-Fg dovuti ad una programmazione successiva di celle di memoria adiacenti. Il metodo mostrato in figura 4D illustra la compensazione per gli effetti di interferenza Fg-Fg sperimentati dalla cella programmata A 442-1 in modo tale che sia la cella A 442-1, ad esempio, una cella perturbata, sia la cella 442-2, ad esempio, una cella non perturbata, vengano lette correttamente in base ad una particolare tensione di riferimento lettura applicata, ad esempio Vread, di mostrato nelle figure 4A e 4B. Nella forma di realizzazione di figura 4D, viene impiegato un periodo regolato di rilevazione della fila di bit t1+t2 per leggere una cella perturbata 442-1 per compensare la quantità di sfalsamento di Vt sperimentata dalla cella 442-1 dovuta all'interferenza Fg-Fg determinata dalla programmazione di una cella adiacente su una fila di parole adiacente successiva alla cella 442-1 che sta venendo programmata allo stato di dati 441.

Nella forma di realizzazione di figura 4D, l'impiegare un periodo di rilevazione regolato t1t2, ad esempio 7 microsecondi, ha come consequenza una circuiteria di rilevazione accoppiata alla corrispondente fila di bit, determinando che la cella 442-1, fatta diventare "off" in risposta all'applicazione di Vread alla fila di parole WL(N), ad esempio alla porta di controllo della cella 442-1, durante un periodo di rilevazione t1t2. Vale a dire, in figura 4D, si è determinato che la cella A 442-1 presenta un livello Vt minore di Vread, ad esempio, un livello Vt corrispondente allo stato 441 dei dati mostrato in figura 4B, piuttosto che viene determinato avere un livello Vt maggiore di Vread, ad esempio un livello Vt corrispondente ad uno stato dei dati differente da 441, avendo come conseguenza un errore di lettura come mostrato nella figura 4B.

Nella forma di realizzazione illustrata figura 4D, possono essere impiegati due segnali di strobe per leggere le celle perturbate, ad esempio la cella A 442-1, e le celle non perturbate, ad esempio la cella B 442-2, su una fila di parole selezionata, ad esempio WL(N). Ad esempio, un primo segnale di strobe che impiega una particolare tensione di riferimento di lettura, ad esempio Vread, applicata alla fila di parole selezionata WL(N), ed un particolare periodo di rilevazione di fila di bit, ad esempio t1, possono impiegati per leggere le celle non perturbate programmate ad un particolare stato di dati, ad esempio 441, come mostrato in figura 4B. Un secondo segnale di strobe, impiegante la stessa tensione di riferimento di lettura, ad esempio Vread, applicato alla fila di parole selezionata WL(N), ed un differente periodo di rilevazione particolare, ad esempio t1+t2, possono essere impiegati per leggere le celle perturbate programmate al particolare stato di dati, ad esempio 441, come mostrato in figura 4B. Durante il primo segnale di strobe ed il secondo segnale di strobe, le celle WL(N)determinate trovarsi nella condizione non

perturbata, in base ad una lettura delle celle WL(N+1) adiacenti, avranno le loro corrispondenti file di bit precaricate alla tensione di precarica 445della fila di bit, e le celle WL(N), determinate trovarsi nella condizione perturbata, in base alla lettura delle celle WL(N+1) adiacenti, avranno le loro corrispondenti file di bit precaricate alla stessa tensione di precarica 445della fila di bit, ad esempio 1,0 V in questo esempio.

Come mostrato in figura 4D, l'eseguire un secondo segnale di strobe impiegando il periodo regolato di rilevazione della fila di bit t1+t2 per leggere le celle perturbate, ad esempio la cella A 442-1, ha come consequenza, nella corrispondente tensione della fila di bit, lo scarico di un ulteriore 300 mV. Vale a dire, come mostrato in figura 4B, la tensione della fila di bit della cella A si scarica di 400 mV, ad esempio da 1,0 V a 0,6 V, durante il periodo di rilevazione t1. Come mostrato in figura 4D, il periodo di rilevazione aumentato t1 + t2 fa sì che la tensione della fila di bit si scarichi di un ulteriore 300 mV durante il periodo di rilevazione t2, ad esempio, da 600 mV a 300 mV. Vale a dire, durante il periodo regolato di rilevazione t1+t2, la tensione della fila di bit associata alla corrispondente fila di bit scarica di più della quantità di soglia, ad esempio 500 mV in questo esempio. Come tale, il tempo di rilevazione regolato t1+t2 associato al secondo segnale di strobe ha come consequenza la compensazione di Fg-Fg, ad esempio le celle WL(N) che è stato determinato che si trovano in condizione perturbata vengono lette come se fossero state perturbate dall'interferenza Fg-Fg delle celle adiacenti WL(N+1).

Nelle forme di realizzazione illustrate nelle figure 4A-4D, si ipotizza che la cella adiacente alla cella bersaglio condivida una fila di bit con la cella bersaglio, ad esempio la cella adiacente e la cella bersaglio si trovano su file di parole vicine. Tuttavia, le forme di realizzazione non sono limitate agli esempi mostrati nella figure 4A-4D. Ad esempio, nelle varie forme di realizzazione, la cella adiacente e la cella bersaglio sono accoppiate alle file di bit vicine e si trovano sulla stessa fila di parole. In tali forme di realizzazione, la figura 4A può essere considerata illustrare un grafico associato a leggere dati da celle di memoria di una fila di parole di memoria di una fila di parole di memoria le

celle della fila di bit dispari, prima delle celle che stanno sperimentando l'interferenza da porta flottante a porta flottante, ad esempio prima dei livelli Vt delle celle che stanno sperimentando uno sfalsamento per effetto di una programmazione successiva di celle vicine della fila di parole selezionata, ad esempio le celle della fila di bit pari. In tali forme di realizzazione, le celle della fila di bit dispari possono essere associate ad una pagina dispari dei dati, e le celle della fila di bit pari possono essere associate ad una pagina pari dei dati. Nelle varie forme di realizzazione, le celle accoppiate a file di bit pari, ad esempio le celle associate ad una pagina pari, vengono programmate ad uno stato finale prima delle celle accoppiate a file di bit dispari, ad esempio le celle associate ad una pagina dispari, essendo programmate ad uno stato finale. Tuttavia, le forme di realizzazione non sono così limitate, ad esempio le celle della fila di bit dispari possono essere programmate allo stato finale prima delle celle della fila di bit pari.

La figura 5 è uno schema di una parte di una schiera di memoria 500 che include celle di memoria che possono essere lette secondo le forme di

realizzazione della presente descrizione. Nella forma di realizzazione illustrata in figura 5, le celle di memoria accoppiate a file di bit numerate esempio BLO, BL2,..., pari, ad rappresentate da cerchi, e le celle di memoria accoppiate alle file di bit numerate dispari, ad esempio BL1, BL3,..., vengono rappresentate da quadrati. Nelle varie forme di realizzazione, le celle delle file di bit pari accoppiate ad una fila di parole selezionata vengono programmate e lette insieme, e le celle delle file di bit dispari accoppiate ad una fila di parole selezionata vengono programmate e lette insieme. Tuttavia, le forme di realizzazione non sono così limitate, ad esempio, nelle varie forme di realizzazione, le celle delle file di bit pari e dispari possono essere lette allo stesso tempo.

La forma di realizzazione mostrata in figura 5 include celle bersaglio (TC) 536-1 e 536-3 corrispondenti rispettivamente a BL1 e BL3. Le celle bersaglio 536-1 e 536-3 sono celle programmate accoppiate ad una fila di parole selezionata, ad esempio la fila di parole N. Le celle bersaglio 536-1 e 536-3 possono essere lette insieme come una parte di una pagina logica di

dati, ad esempio PAGE(N) associata ad una fila di parole N.

La forma di realizzazione mostrata in figura 5 include inoltre celle adiacenti (AC) 530-1 e 530-3, che condividono file bit rispettivamente con celle bersaglio 536-1 e 536-3, e possono determinare effetti di interferenza Fq-Fq sulle celle bersaglio 536-3 536-1 e dovute ad una programmazione successiva. Le celle 530-1 e 530-3 sono accoppiate ad una fila di parole, ad esempio la fila di parole N+1, adiacente alla fila di parole N selezionata, e possono essere lette insieme come una parte di una pagina logica di dati, ad esempio PAGE (N+1)associata alla fila di parole N+1.

Nella forma di realizzazione illustrata in figura 5, le file di bit dispari BL1 e BL3 sono modulo di rilevazione, accoppiate ad un 552**-**1 e 552-3. I rispettivamente moduli di rilevazione 552-1 e 552-3 possono includere una circuiteria di rilevazione, ad esempio amplificatore di rilevazione, tra l'altra (non circuiteria mostrata), che può essere impiegato per precaricare file di bit, ad esempio BL1 e BL3, a vari livelli di tensione, e possono rilevare scariche dei livelli di tensione della

fila di bit durante l'operazione di lettura di dati. Durante l'operazione di lettura di dati, il livello di tensione della fila di bit diminuisce appena la corrente fluisce tra sorgente e pozzo, a seconda della tensione di riferimento di lettura applicata alla fila di parole selezionata. Come descritto nelle figure 4A-4D, lo stato di una cella che sta venendo letta può essere determinato in base al fatto che la tensione della fila di bit si scarichi di una quantità predeterminata durante un periodo di rilevazione predeterminato oppure no, o in base ad una quantità predeterminata durante un periodo di rilevazione predeterminato, oppure in base al fatto che la tensione della fila di bit raggiunga un valore di soglia predeterminato durante il periodo di rilevazione predeterminato.

Come una persona di capacità ordinaria nella tecnica comprenderà, i moduli di rilevazione 552-1 e 552-3 possono essere accoppiati ad una circuiteria di controllo, ad esempio la circuiteria di controllo 770 mostrata in figura 7, che può includere e/oppure essere accoppiata ad una unità di controllo e/oppure un elaboratore. Sebbene non mostrato in figura 5, le file di bit pari, ad esempio BLO e BL2, possono inoltre essere

accoppiate ad un modulo di rilevazione. In talune forme di realizzazione, file di bit alternate possono condividere un modulo di rilevazione. Ad esempio, BLO e BL1 possono essere entrambe accoppiate al modulo 552-1, e BL2 e BL3 possono essere entrambe accoppiate al modulo 552-3.

Come mostrato in figura 5, i moduli rilevazione 552-1 e 552-3 includono rispettivi registri latch di dati 556-1 e 556-3, e cache 554-1 e 554-3. I registri latch di dati 556-1 e 556-3 possono memorizzare un indicatore di stato di perturbazione in base ad una operazione di lettura eseguita sulle celle adiacenti 530-1 e 530-3. Come sopra descritto in collegamento con le figure 4A-4D, lo stato dei registri latch 530-1 e 530-3 possono determinare una parametro di rilevazione impiegato dai moduli di rilevazione 552-1 e 552-3 per leggere dati dalle celle bersaglio 536-1 e 536-3. Ad esempio, in questa forma di realizzazione, se un registro latch 556-1 memorizza uno "0", allora il modulo di rilevazione 552-1 considererà che la cella bersaglio 536-1 si trova in una condizione "non perturbata", ed impiegherà un primo parametro rilevazione, ad esempio una tensione di regolata di precarica della fila di bit oppure un periodo di rilevazione non regolato, per leggere la cella bersaglio 536-1. D'altro canto, il registro latch 556-1 memorizza un "1", allora ilmodulo di rilevazione 552-1 considererà che la cella bersaglio 536-1 si trova in una condizione "perturbata", ed impiegherà un parametro rilevazione differente, ad esempio una tensione di precarica regolata della fila di bit oppure un periodo di rilevazione regolato, per leggere la cella bersaglio 536-1. Le cache 554-1 e 554-3 possono essere impiegate per memorizzare dati letti da celle di memoria accoppiate rispettivamente alle file di bit BL1 e BL3.

Come sopra descritto in questa sede, nelle varie forme di realizzazione della presente descrizione, in base ad una richiesta di leggere dati da celle bersaglio di una prima fila di parole, ad esempio 536-1 e 536-3 della fila di parole N, viene dapprima eseguita una operazione di lettura sulle celle adiacenti alle celle bersaglio, ad esempio le celle adiacenti 530-1 e 530-3 della fila di parole N+1. L'operazione di lettura eseguita su celle adiacenti 530-1 e 530-3 può essere impiegata per determinare se le celle bersaglio 536-1 e/oppure 536-3 si troveranno in una condizione perturbata a causa degli effetti di interferenza Fq-Fq. La determinazione se le celle bersaglio 536-1 e 536-3 sono perturbate dipendere dallo stato dei dati delle celle adiacenti, rispettivamente 530-1 e 530-3. Una cella bersaglio, ad esempio 536-1 e/oppure considerata trovarsi in una condizione perturbata, presenterà un livello Vt superiore per effetto dell'interferenza Fg-Fg da una cella adiacente. Le varie forme di realizzazione della presente il descrizione possono compensare livello Vt aumentato per effetto dell'interferenza Fg-Fg, ad esempio la cella perturbata può essere letta come se il suo livello Vt fosse minore del suo valore reale, il che può ridurre od impedire che una lettura della cella perturbata produca un errore.

La figura 6 è uno schema a blocchi di un metodo per leggere celle di memoria non volatile a livello multiplo secondo una forma di realizzazione della presente descrizione. Nel blocco 610, il metodo include il ricevere una richiesta di leggere dati memorizzati in una prima cella di una prima fila di parole, ad esempio una cella bersaglio di una fila di parole selezionata WL(N).

Nel blocco 620, il metodo include l'eseguire

una operazione di lettura su una cella adiacente di una seconda fila di parole, ad esempio una fila di parole adiacente WL(N+1), in risposta alla richiesta. Vale a dire, per leggere dati da una cella bersaglio di WL(N), viene dapprima eseguita una operazione di lettura su una cella adiacente alla cella bersaglio su WL(N+1), ad esempio una cella su WL(N+1) che condivide una fila di bit con la cella bersaglio su WL(N).

Nel blocco 630, il metodo include il determinare se la prima cella, ad esempio la cella bersaglio, si trova in una condizione perturbata in base all'operazione di lettura, ad esempio in base all'operazione di lettura eseguita sulla cella WL(N+1). Nelle varie forme di realizzazione, il metodo include il memorizzare un indicatore dello stato di perturbazione in un registro associato ad una fila di bit della cella bersaglio e della cella adiacente, in base alla operazione di lettura. In talune forme di realizzazione, il registro latch di dati può memorizzare un "1" logico, per indicare che la cella WL(N+1) si trova in uno stato non associato alla interferenza Fg-Fg della cella bersaglio su WL(N).

Nel blocco 640, il metodo include il leggere

dati memorizzati nella cella bersaglio in risposta alla richiesta, applicando una tensione di riferimento di lettura alla prima fila di parole WL(N), e regolando un parametro di rilevazione se la cella bersaglio si trova nella condizione perturbata. Nelle varie forme di realizzazione, il metodo include l'applicare la stessa tensione di riferimento di lettura alla fila di parole WL(N) per leggere dati memorizzati nella cella bersaglio, indipendentemente dal fatto che la cella bersaglio si trovi nella condizione perturbata oppure no.

Nelle varie forme di realizzazione, e come descritto in collegamento con le figure 4A-4C, la regolazione del parametro di rilevazione includere la regolazione della tensione di precarica della fila di bit se la cella bersaglio di WL(N) si trova nella condizione perturbata. In tali forme di realizzazione, una prima tensione di precarica della fila di bit può essere impiegata leggere la cella bersaglio, se la cella bersaglio si trova in una condizione non perturbata.

Nelle varie forme di realizzazione, la determinazione se la cella bersaglio si trovi in una condizione perturbata è basata sui dati reali

della cella WL(N+1). Il metodo può includere la modifica del parametro di rilevazione regolato in base ad uno stato di dati determinato della cella adiacente, ad esempio la cella WL(N+1).

Nelle varie forme di realizzazione, e come descritto in collegamento con le figure 4A, 4B e 4D la regolazione del parametro di rilevazione può includere la regolazione del periodo di rilevazione se la cella bersaglio di WL(N) si trova nella condizione perturbata. In tali forme di realizzazione, può essere impiegato un primo segnale di strobe con un primo periodo di rilevazione per leggere la cella bersaglio se la cella bersaglio si trova in una condizione non perturbata. Un secondo segnale di strobe con un periodo di rilevazione differente, ad esempio più lungo, può essere impiegato per leggere la cella bersaglio, se la cella bersaglio si trova in una condizione perturbata.

Nelle varie forme di realizzazione, l'eseguire l'operazione di lettura sulla cella adiacente include soltanto l'applicazione di una tensione di riferimento di lettura alla fila di parole WL(N+1). In talune forme di realizzazione, si determina che la cella bersaglio si trova in una condizione non

perturbata se la lettura eseguita sulla cella adiacente WL(N+1)ha come consequenza determinazione che la cella WL(N+1) si trova nello cancellazione. tali di Ιn forme stato di realizzazione, si può determinare che la cella bersaglio si trova in una condizione perturbata se la lettura eseguita sulla cella adiacente WL(N+1) ha come consequenza una determinazione che la cella WL(N+1) non si trova nello stato di cancellazione, ad esempio il livello Vt della cella WL(N+1) si è spostato per effetto della programmazione eseguita sulla cella WL(N+1) successiva alla cella bersaglio che sta venendo programmata ad uno stato di dati particolare.

La figura 7 è uno schema funzionale a blocchi di un sistema di memorizzazione elettronico avente almeno un dispositivo di memoria secondo la forma di realizzazione della presente descrizione. Il sistema di memoria 700 include un elaboratore 710 accoppiato ad un dispositivo di memoria non volatile 720 che include una schiera di memoria 730 di celle non volatili a livello multiplo. Il sistema di memoria 700 può includere circuiti integrati separati, oppure sia l'elaboratore 710 sia il dispositivo di memoria 720 possono trovarsi

sullo stesso circuito integrato. L'elaboratore 710 può essere un microprocessore o un altro tipo di circuiteria di controllo, quale un circuito integrato di applicazione specifica (ASIC).

Per chiarezza, il sistema di memorizzazione 700 è eleettronico stato semplificato focalizzarsi su caratteristiche con rilevanza particolare alla presente descrizione. dispositivo di memoria 720 include una schiera di celle di memoria non volatili 730 che possono essere celle di memoria flash a porta flottante con architettura NAND. Le porte di controllo di delle celle di ciascuna riga memoria sono accoppiate ad una fila di parole, mentre le regioni di pozzo delle celle di memoria sono accoppiate a file di bit. Le regioni di sorgente delle celle di memoria sono accoppiate a file di sorgenti, come lo stesso è stato illustrato in figura 1. Come verrà compreso da coloro che sono di capacità ordinaria nel ramo, il modo di collegamento delle celle di memoria alle file di bit ed alle file di sorgenti dipende se la schiera è una architettura NAND, una architettura NOR, ed una architettura AND, oppure un'altra architettura di schiera di memoria.

La forma di realizzazione di figura 7 include

una circuiteria di indirizzo 740 per agganciare segnali di indirizzo forniti su collegamenti I/O 762 attraverso una circuiteria I/O 760. I segnali di indirizzo vengono ricevuti e decodificati da un decodificatore di riga 744 ed un decodificatore di colonna 746 per accedere alla scheda di memoria 730. Alla luce della presente descrizione, verrà compreso da coloro che sono esperti nel ramo che il numero dei collegamenti di indirizzi di ingresso dipende dalla densità e dall'architettura della schiera di memoria 730, e che il numero di indirizzi aumenta sia con i numeri aumentati di celle di memoria sia con i numeri aumentati di blocchi e schiere di memoria.

La schiera di memoria 730 di celle non volatili può includere celle di memoria volatile a livello multiplo lette secondo forme di realizzazione in descritte questa sede. Ildispositivo di memoria 720 legge dati nella schiera di memoria 730 rilevando variazioni di tensione e/oppure corrente nelle colonne della schiera di memoria impiegando una circuiteria di rilevazione/buffer che, in questa forma di di realizzazione, può essere una circuiteria 750. di lettura/aggancio La circuiteria

lettura/aggancio 750 può includere un numero di moduli di rilevazione, ad esempio 552-1 e 552-3 mostrati in figura 5, e può leggere ed agganciare una pagina oppure una riga di dati dalla schiera di memoria 730. Una circuiteria di I/O 760 è inclusa per comunicazione di dati bidirezionale sui collegamenti I/O 762 con l'elaboratore 710. Una circuiteria di scrittura 755 è inclusa per scrivere dati nella schiera di memoria 730.

Una circuiteria di controllo 770 decodifica segnali forniti mediante collegamenti di controllo 772 dall'elaboratore 710. Questi segnali possono includere segnali di chip, segnali di abilitazione di scrittura, e segnali di aggancio di indirizzo, che vengono impiegati per controllare le operazioni sulla schiera di memoria 730, incluse operazioni di lettura di dati, di scrittura di dati e di cancellazione di dati. Nelle varie forme di realizzazione, la circuiteria di controllo 770 è in grado di eseguire istruzioni dall'elaboratore 710 per eseguire le forme di realizzazione operative e di programmazione della presente descrizione. La circuiteria di controllo 770 può essere macchina a stati, un sequenziatore, oppure un altro tipo di unità di controllo. Verrà compreso da

coloro che sono esperti nel ramo che possono essere forniti ulteriori segnali di controllo e circuiteria, e che il dettaglio del dispositivo di memoria di figura 7 è stato ridotto per semplificare la facilità di illustrazione.

La figura 8 è uno schema funzionale a blocchi di modulo di memoria นท avente almeno dispositivo di memoria secondo una forma di realizzazione della presente descrizione. Un modulo di memoria 800 viene illustrato come una scheda di sebbene i concetti discussi memoria, con riferimento al modulo di memoria 800 siano applicabili ad altri tipi di memoria amovibile o portatile (ad esempio, unità flash USB), e sono intesi essere nell'ambito di "modulo di memoria" come impiegato in questa sede. Inoltre, sebbene in figura 8 venga illustrato un fattore di forma esemplificativo, questi concetti sono applicabili pure ad altri fattori di forma.

In talune forme di realizzazione, il modulo di memoria 800 includerà un alloggiamento 805 (come descritto) per racchiudere uno o più dispositivi di memoria 810, sebbene tale alloggiamento non sia essenziale a tutti i dispositivi o alle applicazioni di dispositivi. Almeno un dispositivo