(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6894360号

(P6894360)

(45) 発行日 令和3年6月30日(2021.6.30)

(24) 登録日 令和3年6月7日(2021.6.7)

(51) Int.Cl.

F 1

H03M 1/10 (2006.01)

H03M 1/20 (2006.01)H03M 1/10

H03M 1/20

A

請求項の数 6 外国語出願 (全 25 頁)

(21) 出願番号 特願2017-234085 (P2017-234085)

(22) 出願日 平成29年12月6日 (2017.12.6)

(65) 公開番号 特開2018-98788 (P2018-98788A)

(43) 公開日 平成30年6月21日 (2018.6.21)

審査請求日 令和2年12月4日 (2020.12.4)

(31) 優先権主張番号 16202934.2

(32) 優先日 平成28年12月8日 (2016.12.8)

(33) 優先権主張国・地域又は機関

歐州特許庁 (EP)

早期審査対象出願

(73) 特許権者 508223789

スティヒティング・イメック・ネーデルラント

S t i c h t i n g I M E C N e d e r l a n d

オランダ5656アーエー・エイントホーフェン、ハイ・テク・キャンパス31番

(74) 代理人 100101454

弁理士 山田 卓二

(72) 発明者 ディン・ミン

ベルギー3001ルーヴァン、カペルドリーフ75番 アイメック・ヴェーゼットウェー内

最終頁に続く

(54) 【発明の名称】逐次比較レジスタ型A/D変換器における利得較正方法、及び逐次比較レジスタ型アナログデジタル変換器

## (57) 【特許請求の範囲】

## 【請求項1】

アナログ入力信号( $V_{IN}$ )を、 $m$ 個の最上位ビット( $B_{MSB}$ )と $n$ 個の最下位ビット( $B_{LSB}$ )によって形成されたデジタル信号( $C_{OUT}$ )に変換するように構成された逐次比較レジスタ型アナログデジタル変換器(SARADC)(200;700)の利得較正方法であって、

前記方法は、

a) 第1段のADC(210;710)が、前記アナログ入力信号( $V_{IN}$ )に対応する前記デジタル信号( $C_{OUT}$ )の最上位ビット( $B_{MSB}$ )の出力値を決定するステップと、

b) 利得係数を有する利得モジュール(230;730)が、前記第1段のADC(210;710)から出力される残差信号( $V_{RES}$ )を増幅するステップであって、前記 $n$ 個の最下位ビット( $B_{LSB}$ )のうちの最上位ビットが前記 $m$ 個の最上位ビット( $B_{MSB}$ )に前記利得係数を乗算したものに等しいステップと、

c) 第2段のADC(220;720)が前記アナログ入力信号( $V_{IN}$ )に対応する前記デジタル信号( $C_{OUT}$ )の最下位ビット( $B_{LSB}$ )の出力値を決定するステップと、

d) 前記アナログ入力信号( $V_{IN}$ )から決定されたバイナリコードがバイナリトリガコードと一致するか否かを検出し、前記バイナリコードが前記バイナリトリガコードと一致しないときは、較正処理がトリガされず、前記SARADC(200;700)の標準動

10

20

作が、アナログ入力信号全体がデジタル信号に変換されるまで、もしくは、前記バイナリコードが前記バイナリトリガコードと一致するまで、継続されるステップと、

e) 前記バイナリコードが前記バイナリトリガコードと一致するときは、較正処理がトリガされ、メモリモジュール(242；742)から、前記バイナリトリガコードに関連する予め設定されたバイナリ較正コードを検索し、前記バイナリトリガコードと同じデジタル信号( $C_{OUT}$ )を与えるステップと、

f) 前記バイナリコードを使用して、前記アナログ入力信号( $V_{IN}$ )と、前記バイナリ較正コードの最初のmビットを表すアナログ信号( $V^*_{MSB}$ )との間の差を計算することによって、前記第1段のADC(210；710)における較正残差信号( $V^*_{RES}$ )を決定するステップと、

g) 利得モジュール(230；730)が、すべての最下位ビット( $B_{LSB}$ )が前記第2段のADC(220；720)によって決定されるまで、前記較正残差信号( $V^*_{RES}$ )を一時的に格納するステップと、

h) ステップg)の後、前記利得モジュール(230；730)が、前記較正残差信号( $V^*_{RES}$ )を増幅して、増幅された較正残差信号( $V^*_{AMP}$ )を形成するステップと、

i) 前記バイナリ較正コードを使用して、前記増幅された較正残差信号( $V^*_{AMP}$ )を、前記バイナリ較正コードの最後のnビットを表す別のアナログ信号( $V^*_{LSB}$ )と比較することによって、前記第2段のADC(220；720)における較正ビット( $B^*_{LSB}$ )を決定するステップと、

j) 前記デジタル信号( $C_{OUT}$ )の最下位ビットと較正ビット( $B^*_{LSB}$ )が互いに異なり、前記利得モジュール(230；730)に利得誤差が存在することを示すか否かを判断するステップと、

k) 前記利得誤差の存在が、前記第2段のADC(220；720)における調整可能な複数のキャパシタ(224a，224b，…，224n；724a，724b，…，724n)の少なくとも1つに調整することによって決定される場合に、前記利得モジュール(230；730)における利得誤差を較正するステップとを含む、SARADC(200；700)の利得較正方法。

#### 【請求項2】

前記ステップj)はさらに、前記デジタル信号( $C_{OUT}$ )の最下位ビットと、前記較正ビット( $B^*_{LSB}$ )との間の差がゼロ以外であり、DACのミスマッチの存在を示すか否かを判断するステップと、

前記最下位ビットの値を決定し、前記最下位ビットの値が1の値を有する場合に下方較正を示し、前記最下位ビットの値が0の値を有する場合に上方較正を示す、請求項1に記載の方法。

#### 【請求項3】

前記ステップj)は、前記最下位ビットの値及び前記較正ビット( $B^*_{LSB}$ )の値を決定することをさらに含み、

前記最下位ビットと前記較正ビット( $B^*_{LSB}$ )の両方の値が0の場合、前記利得モジュール(230；730)において前記利得誤差が存在することを示さず、

前記最下位ビットと前記較正ビット( $B^*_{LSB}$ )の両方の値が1の場合、前記利得モジュール(230；730)において前記利得誤差が存在することを示さず、

前記最下位ビットの値が0でありかつ前記較正ビット( $B^*_{LSB}$ )の値は1である場合に、前記利得モジュール(230；730)において前記利得誤差が存在することを上方較正で示し、

前記最下位ビットの値が1でありかつ前記較正ビット( $B^*_{LSB}$ )の値は0である場合に、前記利得モジュール(230；730)において前記利得誤差が存在することを下方較正で示す、

請求項1に記載の方法。

#### 【請求項4】

10

20

30

40

50

アナログ入力信号 ( $V_{IN}$ ) を、 $m$  個の最上位ビット ( $B_{MSB}$ ) と  $n$  個の最下位ビット ( $B_{LSB}$ ) によって形成されるデジタル信号 ( $C_{OUT}$ ) に変換するように構成される逐次比較レジスタ型アナログ - デジタル変換器 (SARADC) (200; 700) であって、

前記 SARADC (200; 700) は、

前記アナログ入力信号 ( $V_{IN}$ ) に対応する前記デジタル信号 ( $C_{OUT}$ ) の最上位ビット ( $B_{MSB}$ ) の出力値を決定するように構成され、前記デジタル信号 ( $C_{OUT}$ ) の最下位ビット ( $B_{LSB}$ ) の数に対応する残差信号 ( $V_{RES}$ ) を出力する第1段の ADC (210; 710) と、

前記第1段の ADC (210; 710) から出力された残差信号 ( $V_{RES}$ ) を受信し、利得係数を用いて前記残差信号 ( $V_{RES}$ ) を増幅し、増幅された残差信号 ( $V_{AMP}$ ) を出力するように構成された利得モジュール (230; 730) であって、前記  $n$  個の最下位ビット ( $B_{LSB}$ ) の最上位ビットが前記  $m$  個の最上位ビット ( $B_{MSB}$ ) の最下位ビットに前記利得係数を乗算したものに等しい利得モジュール (230; 730) と、

前記増幅された残差信号 ( $V_{AMP}$ ) を受信し、前記増幅された残差信号 ( $V_{AMP}$ ) から、前記アナログ入力信号 ( $V_{IN}$ ) に対応する前記デジタル信号 ( $C_{OUT}$ ) の最下位ビット ( $B_{LSB}$ ) の出力値を決定するように構成された第2段の ADC (220; 720) と、

制御モジュール (240; 740) とを備え、

前記制御モジュール (240; 740) は、

前記第1段の ADC (210; 710) と、前記利得モジュール (230; 730) と、前記第2段の ADC (220; 720) とを制御するように構成され、

前記アナログ入力信号 ( $V_{IN}$ ) に対応する前記デジタル信号 ( $C_{OUT}$ ) を出力し、バイナリトリガコードを格納し、

前記アナログ入力信号 ( $V_{IN}$ ) から決定されたバイナリコードが前記バイナリトリガコードと一致するか否かを検出し、

前記バイナリコードが前記バイナリトリガコードと一致しないときは、較正処理がトリガされず、前記 SARADC (200; 700) の標準動作が、アナログ入力信号全体がデジタル信号に変換されるまで、もしくは、前記バイナリコードが前記バイナリトリガコードと一致するまで、継続され、

前記バイナリコードが前記バイナリトリガコードと一致するときは、較正処理がトリガされ、メモリモジュール (242; 742) から、前記バイナリトリガコードに関連する予め設定されたバイナリ較正コードを検索し、前記バイナリトリガコードと同じデジタル信号 ( $C_{OUT}$ ) を生成し、

上記バイナリ較正コードを前記第1段の ADC (210; 710) に提供し、

前記第1段の ADC (210; 710) はさらに、前記アナログ入力信号 ( $V_{IN}$ ) と、前記バイナリ較正コードの最初の  $m$  ビットを表すアナログ信号 ( $V_{MSB}^*$ ) との間の差を計算することによって、較正残差信号 ( $V_{RES}^*$ ) を決定するように構成された残差生成モジュール (219; 719) を備え、

前記制御モジュール (240; 740) は、

複数の制御信号を前記利得モジュール (230; 730) に提供し、

前記利得モジュール (230; 730) はさらに、すべての最下位ビット ( $B_{LSB}$ ) が前記第2段の ADC (220; 720) によって決定されるまで、前記較正残差信号 ( $V_{RES}^*$ ) を一時的に格納するように構成され、その後、前記較正残差信号 ( $V_{RES}^*$ ) を増幅して、増幅された較正残差信号 ( $V_{AMP}^*$ ) を形成し、

前記制御モジュール (240; 740) は、

上記バイナリ較正コードを前記第2段の ADC (220; 720) に提供し、

前記第2段の ADC (220; 720) はさらに、前記増幅された較正残差信号 ( $V_{AMP}^*$ ) を、前記バイナリ較正コードの最後の  $n$  ビットを表す別のアナログ信号 ( $V_{LSB}^*$ ) と比較することによって、較正ビット ( $B_{LSB}^*$ ) を決定するように構成された

10

20

30

40

50

コンパレータ(226;726)を備え、

前記制御モジュール(240;740)は、

前記デジタル信号( $C_{OUT}$ )の最下位ビットと較正ビット( $B^*_{LSB}$ )が互いに異なり、前記利得モジュール(230;730)に利得誤差が存在することを示すか否かを決定し、前記利得誤差の存在が、利得モジュール(230;730)の利得誤差の存在を示す信号を前記第2段のADCに(220;720)に送信することにより、決定された場合に、前記利得モジュール(230;730)において利得誤差を較正することを開始し。

前記第2段のADC(220;720)は、前記信号に従って調整されるように構成された複数の調整可能なキャパシタ(224a, 224b, ..., 224n; 724a, 724b, ..., 724n)を備える、

SARADC(200;700)。

#### 【請求項5】

前記利得モジュール(230;730)は、

第1の増幅器(232;732)と、

第2の増幅器(236;736)と、

前記第1の増幅器(232;732)と第2の増幅器(236;736)との間に設けられた第1のスイッチ(234;734)と、

前記第2の増幅器(236;736)の後段に設けられた第2のスイッチ(238;738)とを備え、

前記制御モジュール(240;740)は、

すべての最下位ビット( $B_{LSB}$ )が前記第2段のADC(220;720)によって決定されるまで、前記第1のスイッチ(234;734)の後段のキャパシタ( $C_S$ )に、前記較正残差信号( $V^*_{RES}$ )を一時的に格納するように、前記第1のスイッチ(234;734)及び前記第2のスイッチ(238;738)を制御するように構成される、

請求項4に記載のSARADC(200;700)。

#### 【請求項6】

前記制御モジュール(240;740)はさらに、

前記最下位ビットと前記較正ビット( $B^*_{LSB}$ )の差がゼロ以外であり、前記利得モジュール(230;730)において前記利得誤差が存在することを示すか否かを判断するように構成された差計算モジュール(247;747)と、

前記最下位ビットの値を決定するように構成された利得較正モジュール(245;745)とを備え、

前記最下位ビットの値が1の値を有する場合に下方較正を示し、

前記最下位ビットの値が0の値を有する場合に上方較正を示す、

請求項4又は5に記載のSARADC(200;700)。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、逐次近似レジスタ型アナログデジタル変換器(SARADC)における利得較正方法に関する。本発明はまた、逐次比較レジスタ型アナログデジタル変換器に関する。

##### 【背景技術】

##### 【0002】

アナログデジタル変換器(ADC)は一般に知られており、アナログフロントエンドと後続のデジタル処理ブロックとの間のインターフェースとして使用されている。現代の無線通信システムは、通常、高分解能(すなわち、12~14ビット)の低電力を必要とする。十分に高い電力効率を提供するために、本質的に電力効率が高いので、SARADCが使用される。SARADCの欠点は、DACキャパシタのミスマッチと比較器のノイズ

10

20

30

40

50

のためにわずか 8 ~ 12 ビットの分解能に制限されていることである。

#### 【0003】

近年、解像度を高めることができる 2 段パイプライン SARADC が提案されている。2 段パイプライン SARADC は、2 つの独立した中分解能 SARADC と段間残差増幅器で構成されている。このパイプライン構造は第 2 段のノイズ要件を緩和するが、段間増幅器には低ノイズで正確な利得条件を課す。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

2 段 SARADC に関する既知の問題は、一般に高分解能 ADC を有する場合、最高の性能を達成するために較正が必要である。具体的には、10

(1) 各段の ADC は互いに較正する必要がある。

(2) 増幅器は、較正する必要があるオフセットを有することができる。

(3) 各段の ADC の比較器をオフセットすることができます。

(4) 増幅器は、較正する必要がある利得誤差を有することができる。

しかしながら、既知の較正プロセスでは、SARADC の通常の動作を停止させる必要がある。このように、SARADC は入力信号を連続的に変換することができない。別の利点は、既知の較正プロセスが、環境影響による経時変化を考慮していないことである。

#### 【0005】

本開示の目的は、SARADC の通常動作を中断しない、逐次近似レジスタ型アナログデジタル変換器 (SARADC) における利得較正方法を提供することにある。20

#### 【課題を解決するための手段】

#### 【0006】

#### 開示の概要

前記目的は、SARADC における以下の利得較正方法によって達成され、前記方法は

、

a ) 第 1 段の ADC が、アナログ入力信号に対応するデジタル信号の複数の最上位ビットを決定するステップと、

b ) 利得モジュールが、第 1 段の ADC から出力された残差信号を増幅するステップと、

c ) 第 2 段の ADC が、アナログ入力信号に対応するデジタル信号の複数の最下位ビットを決定するステップと、30

d ) 前記アナログ入力信号 ( $V_{IN}$ ) から決定されたバイナリコードが少なくとも 1 つのトリガコードと一致するか否かを検出するステップと、

e ) 少なくとも 1 つのトリガコードに対応する少なくとも 1 つの設定コードを用いて、前記第 1 段の ADC における較正残差信号と、第 2 段の ADC における較正ビットとを決定するステップと、

f ) デジタル信号の最下位ビット及び較正ビットを解析するステップと、

g ) 前記解析から、前記利得モジュールにおける利得誤差の存在の表示を決定するステップと、

h ) 利得誤差の存在が決定されたときに、利得モジュールにおける利得誤差を較正するステップとを含む。40

#### 【0007】

較正ビットの決定は、第 2 段の ADC において 1 つの追加の比較しか必要としないので、通常の動作と比較して、SARADC の正常動作に大きな影響はない。具体的には、通常の操作を中断する必要はなく、ただ 1 つの追加の比較ステップが存在する。さらに、利得誤差があるか否かを決定すること、誤差がある場合に較正することは、SARADC の通常の動作に影響を与えるプロセスではない。従って、較正はバックグラウンドで行うことができ、それ故、頻繁に行うことができ、それによって、環境効果による経時変化を考慮に入れることができる。

#### 【0008】

一実施形態では、前記ステップe)はさらに、アナログ入力信号と、少なくとも1つの設定コードの一部を表すアナログ信号との間の差を計算することによって、較正残差信号を決定するステップを含む。

#### 【0009】

一実施形態では、前記ステップe)はさらに、増幅された較正残差信号を、少なくとも1つの設定コードの一部を表す別のアナログ信号と比較することによって、較正ビットを決定するステップを含む。

#### 【0010】

一実施形態では、前記ステップe)はさらに、利得モジュールが、較正残差信号を一時的に記憶することを、最下位ビットが決定されるまで繰り返すステップを含む。 10

#### 【0011】

一実施形態では、前記ステップg)はさらに、最下位ビットと較正ビットが異なるか否かを決定し、利得モジュールにおける利得誤差の存在を示すステップを含む。好ましくは、前記ステップg)はさらに、最下位ビットの値を決定し、前記値が「1」の値を有するときに下方較正を示し、前記値が「0」の値を有するときに上方較正を示すステップを含む。

#### 【0012】

代替実施形態では、前記ステップg)はさらに、最下位ビット及び較正ビットの値を決定し、 20

最下位ビットと較正ビットの両方の値が「0」であるときに、利得モジュールに利得誤差の存在を示さず、

最下位ビットと較正ビットの両方の値が「1」であるときに、利得モジュールに利得誤差の存在を示さず、

最下位ビットの値が「0」でありかつ較正ビットの値が「1」であるときに、利得モジュールにおける利得誤差の存在を上方較正で示し、

最下位ビットの値が「1」でありかつ較正ビットの値が「0」であるときに、利得モジュール内に利得誤差の存在を下方較正で示すステップを含む。 30

#### 【0013】

一実施形態では、前記ステップh)はさらに、利得モジュールにおける利得誤差の存在が検出されたときに、複数の調整可能なキャパシタのうちの少なくとも1つを調整することによって第2段のADCを較正するステップを含む。 30

#### 【0014】

本開示の別の目的は、SARADCの通常の動作を中断することなく利得誤差較正を受けることができる、逐次比較レジスタ型アナログデジタル変換器(SARADC)を提供することにある。

#### 【0015】

前記目的は、以下のSARADCによって達成され、前記SARADCは、

アナログ入力信号に対応するデジタル信号の複数の最上位ビットを決定し、前記デジタル信号の複数の最下位ビットに対応する残差信号を出力するように構成された第1段のADCと、 40

前記第1段のADCから出力された残差信号を受信し、残差信号を増幅して出力する利得モジュールと、

増幅された残差信号を受信し、増幅された残差信号から入力アナログ信号に対応するデジタル信号の複数の最下位ビットを決定するように構成された第2段のADCと、

前記第1段のADC、前記利得モジュール、及び前記第2段のADCを制御するように構成された制御モジュールとを備え、

前記制御モジュールは、

入力されたアナログ信号に対応するデジタル出力信号を出力し、

少なくとも1つのトリガコードを格納し、

アナログ入力信号から決定されたバイナリコードが少なくとも1つのトリガコードと一 50

致するか否かを検出し、

少なくとも 1 つのトリガコードに対応する少なくとも 1 つの設定コードを、較正残差信号を決定するようにさらに構成された第 1 段の A D C 、並びに、較正ビットを決定するようにさらに構成された第 2 段の A D C に提供し、

デジタル信号の最下位ビット及び較正ビットを解析し、

前記解析から、前記利得モジュールにおける利得誤差の存在の指示子を決定し、

前記利得誤差の存在が決定された場合、利得モジュールにおける較正利得誤差を開始するように構成される。

#### 【 0 0 1 6 】

この S A R A D C は、既に上述した方法と同じ利点を有する。 10

#### 【 0 0 1 7 】

一実施形態では、前記第 1 段の A D C は、アナログ入力信号と、少なくとも 1 つの設定コードの一部を表すアナログ信号との間の差を計算することによって較正残差信号を決定するように構成される残差生成モジュールを備える。

#### 【 0 0 1 8 】

一実施形態では、前記第 2 段の A D C は、増幅された較正残差信号を、少なくとも 1 つの設定コードの一部を表す別のアナログ信号と比較することによって、較正ビットを決定するように構成された比較器を備える。

#### 【 0 0 1 9 】

一実施形態では、前記利得モジュールは、 20

第 1 の増幅器と、

第 2 の増幅器と、

第 1 の増幅器と第 2 の増幅器との間の第 1 のスイッチと、

第 2 の増幅器の後段の第 2 のスイッチとを備え、

前記制御モジュールは、較正残差信号を、第 1 のスイッチの後段のコンデンサに一時的に格納することを、前記第 2 段の A D C が最下位ビットを決定するまで繰り返すように、第 1 のスイッチ及び第 2 のスイッチを制御する。

#### 【 0 0 2 0 】

一実施形態では、前記制御モジュールはさらに、最下位ビットと較正ビットとが異なるか否かを決定し、利得モジュール内の利得誤差の存在を示す差分計算モジュールを備える。好ましくは、前記制御モジュールは、最下位ビットの値を決定し、前記値が「 1 」の値を有するときに下方較正を示し、前記値が「 0 」の値を有するときに上方較正を示すように構成された利得較正モジュールを備える。 30

#### 【 0 0 2 1 】

代替実施形態では、前記制御モジュールは、最下位ビット及び較正ビットの値を決定するように構成された利得較正モジュールを備え、

最下位ビットと較正ビットの両方の値が「 0 」であるときに、利得モジュールに利得誤差の存在を示さず、

最下位ビットと較正ビットの両方の値が「 1 」であるときに、利得モジュールに利得誤差の存在を示さず、 40

最下位ビットの値が「 0 」でありかつ較正ビットの値が「 1 」であるときに、利得モジュールにおける利得誤差の存在を上方較正で示し、

最下位ビットの値が「 1 」でありかつ較正ビットの値が「 0 」であるときに、利得モジュールにおける利得誤差の存在を下方較正で示す。

#### 【 0 0 2 2 】

一実施形態では、前記制御モジュールは、利得モジュール内の利得誤差の存在を示す信号を、前記信号に応じて調整されるように構成された複数の調整可能なキャパシタを備えた第 2 段の A D C に送るようにさらに構成される。

#### 【 0 0 2 3 】

本開示は、以下の説明及び添付の図面によってさらに説明される。 50

**【図面の簡単な説明】****【0024】**

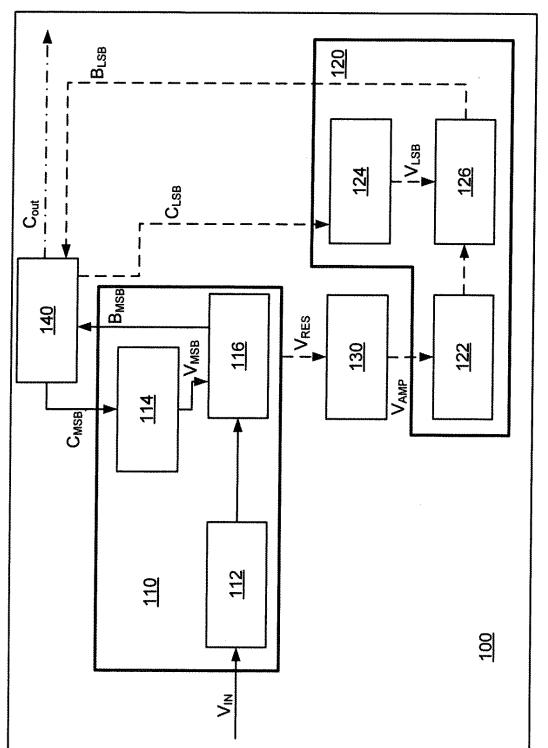

【図1】従来の2段パイプライン逐次比較レジスタ(SAR)型アナログデジタル変換器(ADC)のブロック図を示す。

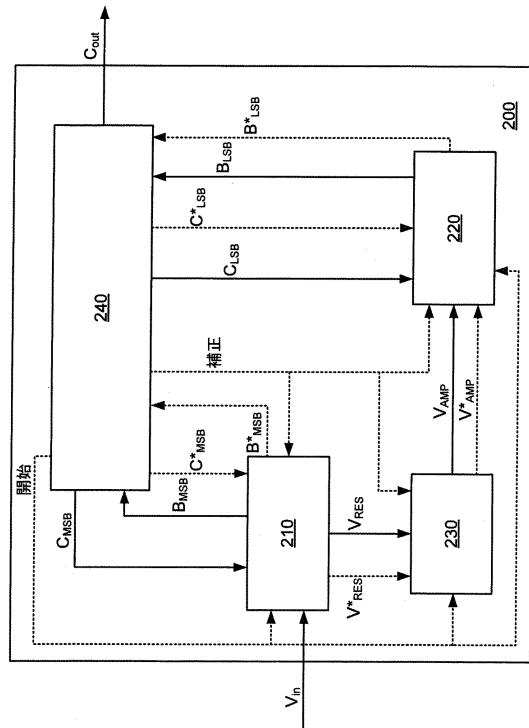

【図2A】本開示にかかる2段パイプラインSARADCのブロック図を示す。

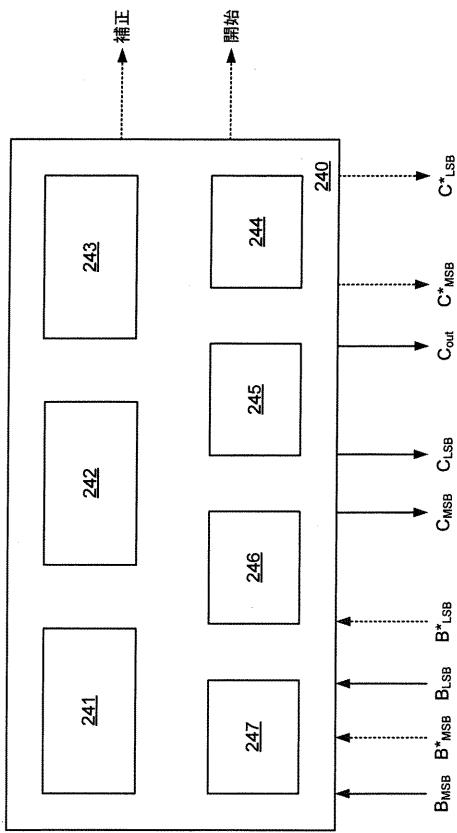

【図2B】図2Aの2段パイプラインSARADCの制御モジュールのブロック図を示す。

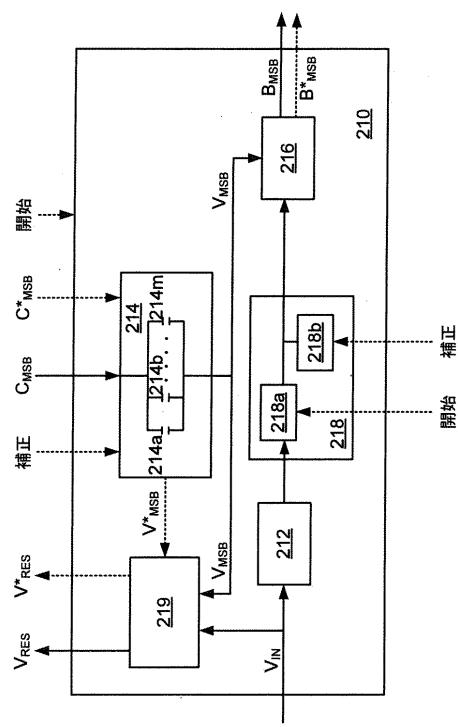

【図2C】図2Aの2段パイプラインSARADCの第1のSARADCのブロック図を示す。

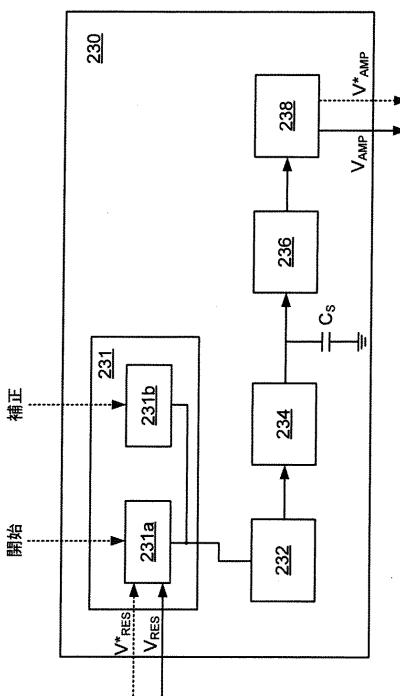

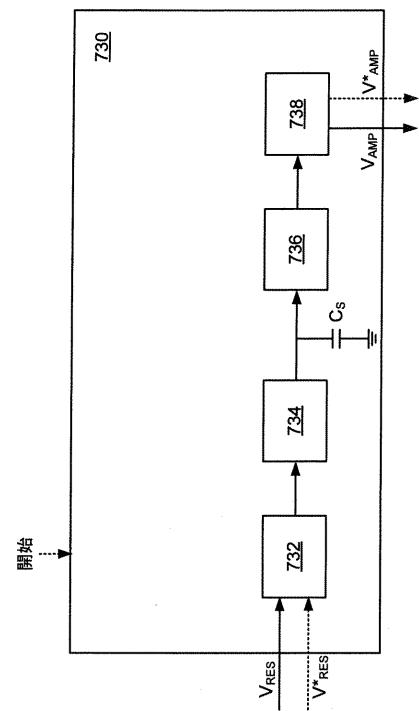

【図2D】図2Aの2段パイプラインSARADCの利得モジュールのブロック図を示す。 10

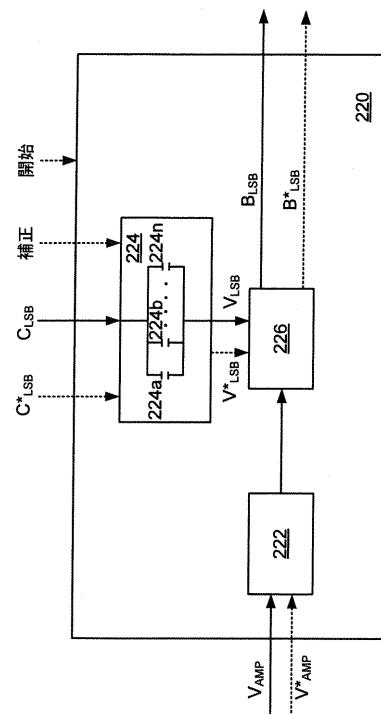

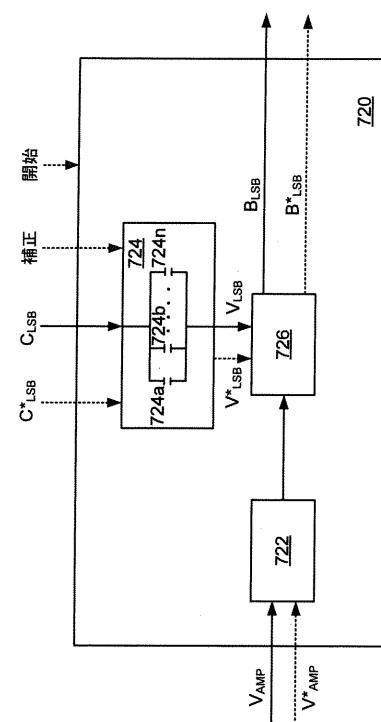

【図2E】図2Aの2段パイプラインSARADCの第2のSARADCのブロック図を示す。

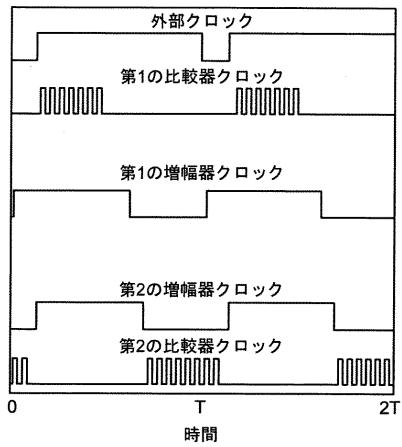

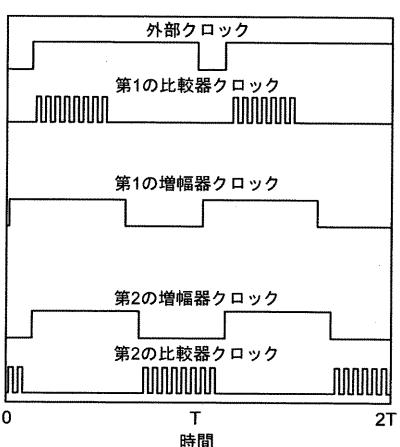

【図3】通常動作中の図2Aの2段パイプラインSARADCのタイミング図を示す。

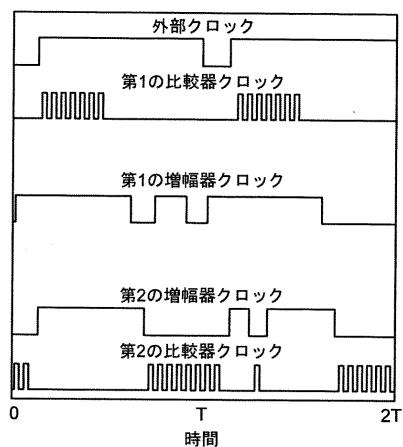

【図4】DACミスマッチの較正、増幅器利得の較正、又は第2の比較器のオフセット較正中の、図2Aの2段パイプラインSARADCのタイミング図を示す。

【図5】第1の比較器のオフセット較正中の図2Aの2段パイプラインSARADCのタイミング図を示す。

【図6A】利得誤差の較正を伴う本開示にかかる2段パイプラインSARADCのブロック図を示す。 20

【図6B】図6Aの2段パイプラインSARADCの制御モジュールのブロック図を示す。

【図6C】図6Aの2段パイプラインSARADCの第1のSARADCのブロック図を示す。

【図6D】図6Aの2段パイプラインSARADCの利得モジュールのブロック図を示す。

【図6E】図6Aの2段パイプラインSARADCの第2のSARADCのブロック図を示す。

**【発明を実施するための形態】****【0025】**

30

本開示の説明

本開示は、特定の実施形態に関して、及び特定の図面を参照して説明されるが、本開示はそれに限定されず、請求項によってのみ限定される。記載された図面は概略的なものに過ぎず、限定的ではない。図面において、要素のいくつかのサイズは、説明のために誇張されており、縮尺通りに描かれていない場合がある。寸法及び相対的な寸法は、本開示の実施のための実際の縮小に必ずしも対応していない。

**【0026】**

さらに、明細書及び特許請求の範囲における第1、第2、第3などの用語は、類似の要素を区別するために使用され、必ずしも逐次的又は時間的な順序を説明するためではない。これらの用語は、適切な状況下で交換可能であり、本開示の実施形態は、本明細書に記載又は例示されている以外の順序で動作することができる。 40

**【0027】**

さらに、説明及び特許請求の範囲における上部、下部、上、下などの用語は、説明目的で使用され、必ずしも相対的な位置を説明するためではない。そのように使用される用語は、適切な状況下で交換可能である。本明細書に記載された開示の実施形態は、本明細書に記載又は図示されている以外の向きで動作することができる。

**【0028】**

さらに、様々な実施形態は、「好ましい」と呼ばれるが、例示的な方法として解釈されるべきである。この開示は、本開示の範囲を限定するものではなく実装されてもよい。

**【0029】**

50

図1は、従来の2段パイプライン逐次近似レジスタ(SAR)型アナログデジタル変換器(ADC)100のブロック図を示す。2段パイプラインSAR ADC 100は、第1のSAR ADC 110と、第2のSAR ADC 120と、第1のSAR ADC 110の出力信号を増幅する利得モジュール130と、2段パイプラインSAR ADC 100を制御する制御モジュール140とを備える。図1では、フルラインは、第1のSAR ADC 110がその動作を終了するまで送信される信号を示すために使用され、破線は、第1のSAR ADC 110がその動作を終了した後、第2のSAR ADC 120がその動作を終了するまでの送信される信号を示すために使用され、一点鎖線は、第2のSAR ADC 120がその動作を終了した後に送信される信号を示すために使用される。

## 【0030】

10

動作中、アナログ入力信号 $V_{IN}$ は、複数の最上位ビット(Most Significant Bits: MSB)を決定する第1のSAR ADC 110に入力される。複数のMSBは、アナログ入力信号 $V_{IN}$ を、入力信号 $V_{IN}$ をサンプリングする第1の追跡及び保持モジュール112に供給することで決定される。制御モジュール140は、デジタルコードCMSBを第1のデジタルアナログ変換器(DAC)114に入力し、第1のデジタルアナログ変換器(DAC)114はデジタルコード $C_{MSB}$ を対応するアナログ信号 $V_{MSB}$ に変換する。第1の比較器116は、入力信号 $V_{IN}$ とアナログ信号 $V_{MSB}$ とを比較して、2つの信号のうちのどちらが大きいかを決定する。比較結果に応じて、第1の比較器116はバイナリ値 $B_{MSB}$ を出力する。

## 【0031】

20

バイナリ値 $B_{MSB}$ が「1」であるとき、入力信号 $V_{IN}$ はアナログ信号 $V_{MSB}$ より大きい。同様に、バイナリ値 $B_{MSB}$ が「0」の場合、入力信号 $V_{IN}$ はアナログ信号 $V_{MSB}$ より小さい。バイナリ検索アルゴリズムを使用して、制御モジュール140は、入力信号 $V_{IN}$ に対応するデジタル信号のMSBが決定されるまで、デジタルコード $C_{MSB}$ を変更する。

## 【0032】

少なくとも1つのクロック信号(図1には図示せず)は、2段パイプラインSAR ADC 100のタイミングを制御して、アナログ入力信号 $V_{IN}$ に対応するデジタル信号のMSB及びLSBの決定の反復を提供するために設けられることが容易に理解されるであろう。

30

## 【0033】

例えば、一実施形態では、制御モジュール140は、デジタルコード $C_{MSB}$ を「1000」として初期化する。バイナリ値 $B_{MSB}$ に応じて、次の反復において、制御モジュール140は、デジタルコード $C_{MSB}$ を、バイナリ値 $B_{MSB}$ が「1」であるときに「1100」にセットし、バイナリ値 $B_{MSB}$ が「0」であるときに「0100」にセットする。この実施形態では、4回の反復が実行されて、入力信号 $V_{IN}$ に対応する4個のMSBを決定する。

## 【0034】

当業者であれば、任意の数のMSBが、あらかじめ設定された回数の反復を使用することで、第1のSAR ADC 110によって決定され得ることが明らかである。

40

## 【0035】

MSBが第1のSAR ADC 110によって決定された後、すなわち、予め設定された反復回数が実行された後、第1のSAR ADC 110は、入力信号 $V_{IN}$ と、デジタルコード $C_{MSB}$ に対応するアナログ信号 $V_{MSB}$ との差を表すアナログ残差信号 $V_{RES}$ を出力する。このアナログ信号 $V_{RES}$ は、入力信号 $V_{IN}$ のLSB(Least Significant Bits)に関する情報を含む。信号 $V_{RES}$ は、当該信号を増幅するために利得モジュール130を介して送信される。

## 【0036】

動作中に、利得モジュール130からの増幅された信号 $V_{AMP}$ は、複数のLSBを決定する第2のSAR ADC 120に入力される。具体的には、増幅された信号 $V_{AMP}$ を

50

、増幅された信号 $V_{AMP}$ をサンプリングする第2の追跡及び保持モジュール122に供給することで複数の LSB が決定される。制御モジュール140は、デジタルコード $C_{LSB}$ を第2のDAC124に入力し、第2のDAC124はデジタルコード $C_{LSB}$ を対応するアナログ信号 $V_{LSB}$ に変換する。第2の比較器126は、増幅された信号 $V_{AMP}$ とアナログ信号 $V_{LSB}$ とを比較して、2つの信号のどちらが大きいかを決定する。比較結果に応じて、第2の比較器126はバイナリ値 $B_{LSB}$ を出力する。

#### 【0037】

バイナリ値 $B_{LSB}$ が「1」であるとき、増幅信号 $V_{AMP}$ はアナログ信号 $V_{LSB}$ より大きい。同様に、バイナリ値 $B_{LSB}$ が「0」の場合、入力信号 $V_{AMP}$ はアナログ信号 $V_{LSB}$ より小さい。バイナリ検索アルゴリズムを用いて、制御モジュール140は、

10

入力信号 $V_{IN}$ に対応するデジタル信号の LSB が決定されるまで、デジタルコード $C_{LSB}$ を変更する。

#### 【0038】

第2のSARADC120が予め設定された反復回数を終了した後、制御モジュール140は、入力信号 $V_{IN}$ に対応するデジタルコード $C_{OUT}$ を出力する。 $C_{OUT}$ は、第1のSARADC110によって決定されたMSBに関する情報と、及び第2のSARADC120によって決定された LSBに関する情報を組み合わせることで、制御モジュールによって決定される。

#### 【0039】

図2Aは、以下を修正するバックグラウンド較正を有する2段パイプラインSARADC200のブロック図を示す。

20

(1) SARADC210, 220間のDACミスマッチ誤差；

(2) 利得モジュール230のプロセス、電圧及び温度(PVT)変動に起因する増幅器利得誤差；及び

(3) 比較器216, 226のオフセット誤差。

#### 【0040】

図2Aでは、フルラインは、2段パイプラインSARADC200の通常動作中に発生する信号を示すために使用される一方、点線は、バックグラウンド較正のために実行されていた、又は実行された余分なステップに関連している、送信される信号を示すために使用される。

30

#### 【0041】

2段パイプラインSARADC200の通常の動作は、図1に示す従来の2段パイプラインSARADC100と同一である。具体的には、入力信号 $V_{IN}$ が第1のSARADC210に入力され、第1のSARADC210は上記のように多数のMSBを反復的に決定する。第1のSARADC210は、残差信号 $V_{RES} = V_{IN} - V_{MSB}$ を出力し、残差信号 $V_{RES}$ は利得モジュール230で増幅され、増幅された信号 $V_{AMP}$ は第2のSARADC220に入力される。第2のSARADC220は、増幅された信号 $V_{AMP}$ に基づいて入力信号 $V_{IN}$ の LSB を決定する。MSBとLSBの両方が制御モジュール240に格納され、ここで、それらが結合され、制御モジュール240は、入力信号 $V_{IN}$ に対応するデジタルコード $C_{OUT}$ を出力する。

40

#### 【0042】

一実施形態では、第1のSARADC210は、7ビットデジタルコード $C_{MSB}$ を使用し、7つの比較を行って、入力信号 $V_{IN}$ に対応するデジタル信号の7ビットを決定し、第2のSARADC220は8ビットデジタルコード $C_{LSB}$ を使用し、従って8つの比較を実行する。しかしながら、第2のSARADC220は、2段パイプラインSARADC200の冗長性のために、入力信号 $V_{IN}$ の7ビットだけを決定する。このように、この実施形態では、入力信号 $V_{IN}$ に対応する14ビットデジタル信号を決定するために合計15個の比較が実行される。これにより、第1のSARADC210の LSB が利得モジュール230によって第2のSARADC220のMSB に直接リンクされるので、段間冗長性が生じ、すなわち次式を得る。

50

## 【0043】

$Gain * LSB_{1st} = MSB_{2nd}$  (1)

## 【0044】

この実施形態のタイミング図は、変換プロセスの2サイクルにわたって図3に示されている。外部クロック信号（制御モジュール240のタイミングモジュール（図示せず）によって生成される）は、変換プロセスを開始する。

## 【0045】

第1の比較器クロック信号は、第1のSARADC210の第1の比較器（図2Aには図示せず）の動作を制御する。第1の比較器は7つの動作サイクルを有することは明らかである。第1の比較器がその動作を終了した後、利得モジュール230が起動される。

10

## 【0046】

以下に説明するように、利得モジュール230は2段増幅器を備える。このように、第1の増幅器クロック信号は、2段増幅器の第1の増幅器がアクティブであるときを示す（すなわち、第1の増幅器クロック信号のハイからローへの遷移と、ローからハイへの遷移との間の期間を示す）。

## 【0047】

同様に、第2の増幅器クロック信号は、2段増幅器の第2の増幅器がアクティブであることを示す（すなわち、第2の増幅器制御（又はクロック信号）のハイからローへの遷移と、ローからハイへの遷移との間の期間を示す）。

## 【0048】

第2の比較器クロック信号は、第2のSARADC220の第2の比較器（図2Aには図示せず）の動作を制御する。第2の比較器は、第2の増幅器クロック信号によって示される第2の増幅器がアクティブであると同時に8つの動作サイクルを有することは明らかである。

20

## 【0049】

各SARADC210, 220はまた、2段パイプラインSARADC200が使用されるアーキテクチャに応じて別の数の比較を実行してもよいことは理解されるであろう。しかしながら、直接にリンクする段間の冗長性が維持されていなければならず、第1のSARADC210のLSBは、第2のSARADC220のMSBに直接リンクされることが重要である。

30

## 【0050】

図2Aに戻ると、本開示の2段パイプラインSARADC200では、制御モジュール240は、MSBが第2のSARADC220によって決定された後に、検出ステップを実行する。具体的には、制御モジュール240は、第1のSARADC210のMSB及び第2のSARADC220のLSBのMSBを含むバイナリコードが、プリセットバイナリコードと一致するか否かを決定する。以下では $C_{DET}$ （図示せず）と呼ばれるこのコードが実際にプリセットされたバイナリコードと一致する場合、以下で説明するよう、較正プロセスがトリガされる。一方、このコードがあらかじめ設定されたバイナリコードと一致しない場合は、較正プロセスがトリガされず、2段パイプラインSARADC200の標準動作が、アナログ入力信号 $V_{IN}$ 全体がデジタル信号に変換されるまで、もしくは、コード $C_{DET}$ がプリセットバイナリコードと一致するまで、継続される。

40

## 【0051】

図2Bは、図2Aの2段パイプラインSARADC200の制御モジュール240のブロック図を示す。制御モジュール240は、インターフェースモジュール241を備え、インターフェースモジュール241は、様々な入力信号を受信し、様々な出力信号を2段パイプラインSARADC200の他のモジュールに送信するために使用される。

## 【0052】

制御モジュール240は、メモリモジュール242を備え、メモリモジュール242は、入力信号 $V_{IN}$ の逐次近似の間ににおいて、各SARADC210, 220によって検出されたバイナリコードを格納することができる。さらに、メモリモジュール242はまた

50

、後述するように較正プロセスをトリガする適切なプリセットバイナリコードを格納してもよい。

#### 【0053】

制御モジュール240はまた、検出モジュール243を備える。検出モジュール243は、コード $C_{DET}$ がメモリモジュール242に記憶されているプリセットバイナリコードと一致するか否かを検出する。プリセットバイナリコードが検出された場合、この検出は関連する較正モジュールに伝達され、すなわち、関連する較正モジュールは、DACミスマッチ較正モジュール244、増幅器利得較正モジュール245、及びオフセット較正モジュール246のうちの1つである。

#### 【0054】

さらに、制御モジュール240は、2つのビット値の間の差を決定する差分計算モジュール247を備える。差分計算モジュール247は、後述するように較正に使用される。

#### 【0055】

当業者であれば、制御モジュール240は、他のモジュールとの間で信号を送受信し、かつ／又は他のモジュールから信号を受信するために、異なるモジュール間に適切な内部接続（図示せず）をさらに備えることは明らかである。

#### 【0056】

図2Cは、本開示の2段パイプラインSARADC200の第1のSARADC210のブロック図を示す。図1に示す従来のSARADC110のように、第1のSARADC210は、アナログ入力信号 $V_{IN}$ のm個のMSBを決定するために使用され、追跡及び保持モジュール212と、第1のDAC214と、第1の比較器216とを備える。追跡及び保持モジュール212は、入力信号 $V_{IN}$ をサンプリングして、第1の比較器オフセット補正モジュール218（その動作は以下に説明される）を介して第1の比較器216に供給する。

#### 【0057】

第1のDAC214は、m個のキャパシタ $214a, 214b, \dots, 214m$ を備え、各キャパシタは、決定されるm個のMSBのビットに関連する。第1のDAC214で受信されたデジタルコード $C_{MSB}$ に応じて、キャパシタ $214a, 214b, \dots, 214m$ の1つ以上がスイッチオンされ、デジタルコード $C_{MSB}$ をアナログ信号 $V_{MSB}$ に変換する。

#### 【0058】

通常動作時には、第1の比較器216は、 $V_{IN}$ と $V_{MSB}$ との比較に基づいてバイナリ値 $B_{MSB}$ を出力する。MSBが決定された後、第1のSARADC210の残差生成モジュール219は、残差信号 $V_{RES} = V_{IN} - V_{MSB}$ を生成し、残差信号 $V_{RES}$ は第1のSARADC210から出力される。

#### 【0059】

図2Aに関して上述したように、検出モジュール243が、コード $C_{DET}$ がDACミスマッチ較正に関連するプリセットバイナリコードと一致することを検出するとき、検出モジュール243は、DACミスマッチ較正モジュール244に較正が行われることを示す信号を送る。次に、DACミスマッチ較正モジュール244は、特定のデジタル較正コード $C^*_{MSB}$ を第1のDAC214に送り、アナログ較正信号 $V^*_{MSB}$ を生成する。

#### 【0060】

第1のSARADC210がMSBの決定を終了した後、コード $C_{DET}$ が決定されるだけなので、信号 $V_{RES}$ は既に第1のSARADC210から出力されている。しかしながら、DACミスマッチ較正がトリガされると、DACミスマッチ較正モジュール244は、第1のSARADC210における追加のステップをトリガする。この追加のステップは、較正残差信号を計算し、すなわち、 $V^*_{RES} = V_{IN} - V^*_{MSB}$ を計算し、これは、入力信号 $V_{IN}$ とアナログ較正信号 $V^*_{MSB}$ との間の差である。この計算の出力は、図2Cに点線で示され、これは、通常の動作中には発生しない付加的な動作である。較正残差信号 $V^*_{RES}$ の出力後、第1のSARADC210は再び入力信号 $V_{IN}$ の

10

20

30

40

50

サンプリングを開始し、次の通常動作サイクルを開始する。

**【0061】**

DACミスマッチ較正中の2段パイプラインSARADCのタイミング図を図4に示します。図3に示すように、外部クロック信号は制御モジュールにより発生され、第1の比較器クロック信号は、第1のSARADC210の第1の比較器216の動作を制御し、第1の増幅器クロック信号は、2段増幅器の第1の増幅器がアクティブであるときを示し、第2の増幅器クロック信号は、2段増幅器の第2の増幅器がアクティブであることを示し、第2の比較器クロック信号は、第2のSARADC220における第2の比較器の動作を制御する。

**【0062】**

図4から、DACミスマッチ較正の間に、第1及び第2の増幅器クロック信号が変更されることが明らかである。具体的には、コード $C_{DET}$ が決定された後に第1の増幅器がリセットされ、すなわち、第2のSARADC220のLSBのMSBが決定された後である。

**【0063】**

図2Dは、本開示の2段パイプラインSARADC200の利得モジュール230のブロック図を示す。上記のように、利得モジュール230は、2段増幅器の形態であり、第1の増幅器232と第2の増幅器236とを備える。増幅器232, 236の間には、回路を開閉することができる第1のスイッチ234がある。キャパシタ $C_s$ は、第1のスイッチ234の後段に配置され、閉じたときにアナログ信号を記憶することができるよう配置される。

**【0064】**

第2の増幅器232の後に、利得モジュール230は、回路を開閉することができる第2のスイッチ238を備える。第2のスイッチ238が閉じられると、増幅された信号 $V_{AMP}$ が利得モジュール230から出力される。利得モジュール230はまた、オフセット補正モジュール231を備え、その動作を以下に説明する。

**【0065】**

図3から、通常動作時には、第1及び第2のスイッチ234及び238は、信号 $V_{RES}$ が中断されることなく利得モジュール230内で増幅され、 $V_{AMP}$ がLSBを決定することができる第2のSARADC220に出力されるように、第1及び第2の増幅器クロック信号のそれに従って閉じられることは明らかである。

**【0066】**

しかしながら、DACミスマッチ較正プロセスの間に、第2のSARADC220が入力信号 $V_{IN}$ のLSBの決定を終了する前に、較正残差信号 $V^{*}_{RES}$ は既に決定されている。このため、第2のSARADC220が $V_{RES}$ に対応する増幅された信号 $V_{AMP}$ のビットを決定できることを確実にするために、そのビットは入力信号 $V_{IN}$ のLSBに対応し、較正残差信号 $V^{*}_{RES}$ に対応する増幅された較正信号 $V^{*}_{AMP}$ は、第2のSARADC220がLSBの決定を終了する前に、利得モジュール230から出力され得ない。較正残差信号 $V^{*}_{RES}$ を受信してから増幅された較正信号 $V^{*}_{AMP}$ を出力するまでのレイテンシを達成するために、図2Dに示す2段増幅器が有利である。

**【0067】**

図4に示すように、 $V_{RES}$ が第1のSARADC210によって決定された後、第1の増幅器232はアクティブになり、信号 $V_{RES}$ を増幅し、直ちに $V_{AMP}$ を生成する第2の増幅器236に通す。このように、第1及び第2のスイッチ234及び238の両方が閉じられる。しかしながら、第1のSARADC210が較正残差信号 $V^{*}_{RES}$ を決定しているとき、第1のスイッチ234が開き、第1の増幅器232がリセットされる。第1のSARADC210が較正残差信号 $V^{*}_{RES}$ を出力すると、第1のスイッチ234は再び閉じられ、第1の増幅器232は較正残差信号 $V^{*}_{RES}$ を増幅する。この中間増幅された信号は、その後、蓄積キャパシタ $C_s$ 上に記憶され、第1のスイッチ234は再び閉じられる。このように、第1のSARADC210は、蓄積キャパシタ $C_s$ に蓄

10

20

30

40

50

積された中間増幅信号に影響を与えることなく、次のサイクルの通常のサンプリング動作を継続することができる。第2のSARADC220が最後の比較を終了すると、すなわち、入力信号 $V_{IN}$ のすべてのLSBを決定した後、第2のスイッチ238を開くことによって第2の増幅器236がリセットされる。リセットされた後、第2の増幅器236は、蓄積キャパシタ $C_S$ に蓄積された中間増幅信号を増幅し、増幅された較正信号 $V_{AMP}^*$ を第2のSARADC220に出力する。以下に説明するように、第2のSARADC220は、余分な比較を実行する。

#### 【0068】

図2Eは、本開示の2段パイプラインSARADC200の第2のSARADC220のブロック図を示す。図1に示す従来のSARADC120のように、第2のSARADC220は、アナログ入力信号 $V_{IN}$ の複数n個のLSBを決定するために使用され、追跡及び保持モジュール222と、第2のDAC224と、第2の比較器226とを備える。

10

#### 【0069】

追跡及び保持モジュール222は、入力信号 $V_{AMP}$ をサンプリングして第2の比較器226に供給する。第2のDAC224は、n個のキャパシタ224a, 224b, ..., 224nを備え、各キャパシタは、決定されるべきn個のLSBのビットに関連する。第2のDAC224で受信されるデジタルコードCLSBに依存して、キャパシタ224a, 224b, ..., 224nのうちの1つ以上がスイッチオンされ、デジタルコードCLSBをアナログ信号 $V_{LSB}$ に変換する。通常動作時には、第2の比較器226は、 $V_{AMP}$ と $V_{LSB}$ の比較に基づいてバイナリ値 $B_{LSB}$ を出力する。

20

#### 【0070】

上記のように、検出モジュール243が、コード $C_{DET}$ がDACミスマッチ較正に関連するプリセットバイナリコードと一致することを検出するとき、検出モジュール243は、「開始」信号を用いて図2Aの点線で示されるように較正が行われることを示す信号をDACミスマッチ較正モジュール244に送る。

#### 【0071】

上記のように、第1のSARADC210は、利得モジュール230によって較正信号 $V_{AMP}^*$ に増幅された較正残差信号 $V_{RES}^*$ を出力し、当該増幅された較正残差信号 $V_{RES}^*$ は、入力信号 $V_{IN}$ に対応するデジタル信号のLSBを決定することが終了した後、第2のSARADC220に入力される。次に、DACミスマッチ較正モジュール244は、特定のデジタル較正コード $C_{LSB}^*$ を第2のDAC224に送り、アナログ較正信号 $V_{LSB}^*$ を生成する。さらに、第2のSARADC220において追加の比較サイクルがトリガされる。次いで、この追加のサイクルは、入力信号、すなわち増幅された残差信号 $V_{AMP}^*$ を、アナログ較正信号 $V_{LSB}^*$ と比較する。この比較の出力は、 $B_{LSB}^*$ で示される較正ビットであり、制御モジュール240に送られる。

30

#### 【0072】

次に、差分計算モジュール247は、 $C_{OUT}$ の最後のビットと較正ビット $B_{LSB}^*$ との差を計算する。この比較の結果に応じて、第1のDAC214のキャパシタ214a, 214b, ..., 214mの容量値は、第1のSARADC210の第1のDACと第2のSARADC220の第2のDACとの間のキャパシタミスマッチに対応するように変更される。

40

#### 【0073】

この種の較正の利点は、それはバックグラウンドで実行することができ、すなわち、2段パイプラインSARADC200の通常動作が中断されない。第2のSARDAC220には1つの追加の比較サイクルしか存在しないが、図3及び図4のタイミング図に示すように、2段パイプラインSARADC200の合計タイミングに大きな影響はない。

#### 【0074】

DACミスマッチ較正は、正しいプリセットバイナリコード $C_{DET}$ の選択に基づいている。既に上述したように、第1のSARADC210の残差信号は次式で与えられる。

50

$$V_{RES} = V_{IN} - V_{MSB}, \text{ 及び}$$

$$V^*_{RES} = V_{IN} - V^*_{MSB}$$

【0075】

さらに、同様の式が第2のSARADC220の残差信号に適用される。

$$V_{RES2} = Gain * V_{RES} - V_{LSB}, \text{ 及び}$$

$$V^*_{RES2} = Gain * V^*_{RES} - V^*_{LSB}$$

これらの式を組み合わせると、次式を得る。

【0076】

$$V^*_{RES2} - V_{RES} \\ = Gain * (V_{MSB} - V^*_{MSB}) - (V^*_{LSB} - V_{LSB})$$

10

(2)

【0077】

増幅器の利得が理想的であると仮定すると、すなわち、方程式(1)が有効であると仮定することによって、これにより、次の式が導かれる。

【0078】

$$V^*_{RES2} - V_{RES} \\ = (MSB_{2nd} / LSB_{1st}) * (V_{MSB} - V^*_{MSB}) - (V^*_{LSB} - V_{LSB})$$

(3)

【0079】

プリセットコード  $C_{DET}$  の値、及びそれに応答してバイナリ較正コード  $C^*_{MSB}$  及び  $C^*_{LSB}$  が設定される値に応じて、式(3)の符号は既知である。

【0080】

一実施形態では、第1のDACの第1のキャパシタ214aを較正して第2のDACの第1のキャパシタ224aと良好に一致させるときに、次式を得る。

プリセットコード  $C_{DET} = 1000000 0XXXXXXX$

ここで、Xは、第2のSARADC220によってまだ決定されていないバイナリ値を示す。この実施形態では、第1のSARADC210は、7ビットデジタルコード  $C_{MSB}$  を使用して7つの比較を行って、入力信号  $V_{IN}$  に対応するデジタル信号の7ビットを決定する一方、第2のSARADC220は、8ビットデジタルコード  $C_{LSB}$  を使用して、従って8つの比較を実行する。上記のように、段間の冗長性のために、第1のSARADC210のLSBは、第2のSARADC220のMSBに直接リンクされる。この特定コード  $C_{DET}$  が入力信号  $V_{IN}$  の変換中に遭遇すると、検出モジュール243は、DACミスマッチ較正モジュール244を起動し、 $C^*_{MSB} = 0111111$  を第1のDACに入力する。この較正コードに基づいて、較正残差信号  $V^*_{RES}$  が生成される。第2のSARADC220が入力信号  $V_{IN}$  に対応するデジタルコードの最後のLSBを決定した後、DACミスマッチ較正モジュール244は、較正コード  $C^*_{LSB} = 1YY YYYY$  を第2のDACに入力し、ここで、Yは、第2のSARADC220によって決定されたバイナリ値を示す。これらのバイナリコードに基づいて、理想的には、利得誤差とオフセット誤差が正しく較正されていると仮定すると、次式を得る。

$$V_{MSB} - V^*_{MSB} = LSB_{1st}, \text{ 及び}$$

$$V^*_{LSB} - V_{LSB} = MSB_{2nd}$$

このことは、 $V^*_{RES2} - V_{RES} = 0$  であることを示す。

【0081】

このため、 $V_{RES2}$  と  $V^*_{RES2}$  の符号は同一でなければならず、 $C_{OUT}$  と  $B^*_{LSB}$  の最後のビットに反映されるのは、まさにこれらの符号である。このため、これらのビットの差が非ゼロである場合、第1のDACの第1のキャパシタ214aと第2のDACの第1のキャパシタ224aとの間にDAC較正ミスマッチが存在する。

【0082】

誤差が検出された後、すなわち、最後の2ビット、すなわち  $C_{OUT}$  及び  $B^*_{LSB}$  の

10

20

30

40

50

最後のビットが「01」又は「10」のいずれかを形成する場合、誤差を修正する必要がある。この補正は、第1のD A Cの第1のキャパシタ214aの容量を調整することによって行われる。具体的には、ビットが「01」を形成する場合、第1のキャパシタ214aに補正信号を送って静電容量を減少させる一方、ビットが「10」を形成する場合、第1のキャパシタ214aに補正信号を送り、容量を増加させる。この信号は、図2Aの点線で示され、「補正」と呼ばれる。

#### 【0083】

同様の方法で、他のプリセットされたバイナリコードが第1のD A Cの他のキャパシタに使用され、その結果、これらの特定のキャパシタに対して同一の容量調整が行われる。具体的には、

10

$C_{D E T} = 0100000 \quad 0XXXXXXX$ 、及び

$C^*_{D E T} = 0011111 \quad 1YYYYYYY$

である。ここで、 $C^*_{D E T}$ は、第1のD A Cの第2のキャパシタ214bのための、 $C_{D E T}$ に対する事前に設定された較正応答コードである。第1のD A Cの第3のキャパシタ214cのために、

$C_{D E T} = 0110000 \quad 0XXXXXXX$ 、及び

$C^*_{D E T} = 0101111 \quad 1YYYYYYY$

である。

第1のD A Cの第4のキャパシタ214dのために、

$C_{D E T} = 0111000 \quad 0XXXXXXX$ 、及び

20

$C^*_{D E T} = 0110111 \quad 1YYYYYYY$

である。

第1のD A Cの第5のキャパシタ214eのために、

$C_{D E T} = 0111100 \quad 0XXXXXXX$ 、及び

$C^*_{D E T} = 0111011 \quad 1YYYYYYY$

などである。

ここで、Xは、第2のS A R A D C 220によってまだ決定されていないバイナリ値を示し、Yは第2のS A R A D C 220によって決定されたバイナリ値を示す。

#### 【0084】

これらのプリセットコードは、それぞれのS A R A D Cで決定される他のビット数に対して発生されることが理解されるであろう。

30

#### 【0085】

本開示の2段パイプラインS A R A D C 200は、P V T変動に起因する増幅器利得の変化を補正するために使用することもできる。上述した増幅器利得較正とD A Cミスマッチ較正の主な違いは、プリセットバイナリコード $C_{D E T}$ 及び $C^*_{D E T}$ であり、補正が第2のS A R A D Cモジュール220の第2のD A Cで実行されることである。具体的には、第1のD A Cと第2のD A Cとの間にキャパシタミスマッチがないと仮定すると、式(2)は以下の式となる。

#### 【0086】

$$V^*_{R E S 2} - V_{R E S} = M S B_{2 n d} - G a i n * L S B_{1 s t} \quad (4)$$

40

#### 【0087】

利得が正しく較正されている場合は0になる。しかしながら、利得が正確に較正されない場合、式(4)の符号は利得誤差の方向を示す。従来通り、 $V_{R E S}$ と $V^*_{R E S}$ の符号は $C_{O U T}$ と $B^*_{L S B}$ の最後のビットに反映され、これらのビットの差が非ゼロである場合、利得較正誤差が存在する。

#### 【0088】

利得較正のために、プリセットコードは次式で表される。

$C_{D E T} = 1001000 \quad 1XXXXXXX$ 、及び

$C^*_{D E T} = 1001001 \quad 0YYYYYYY$ 。

50

ここで、Xは、第2のSARADC220によってまだ決定されていないバイナリ値を示し、Yは第2のSARADC220によって決定されたバイナリ値を示す。これらのコードの場合において、利得誤差がなければ同一のアナログ値が得られることが予想される。しかしながら、他のプリセットコードも可能であり、例えば、

$C_{DET} = ZZZZZZ01\ 1XXXXXXX$ 、及び

$C^{*}_{DET} = ZZZZZZ10\ 0YYYYYYY$

である。ここで、Xは、第2のSARADC220によってまだ決定されていないバイナリ値を示し、Yは、第2のSARADC220によって決定されたバイナリ値を示し、Zは未指定の2進数を示す。 $C_{DET}$ と $C^{*}_{DET}$ の選択における唯一の他の制限は、それらがDACミスマッチ較正をトリガするプリセットバイナリコードと一致してはならないことである。

#### 【0089】

このため、プリセット利得較正コードが検出されると、検出モジュール243は、増幅器利得較正モジュール245を起動する。次に、このモジュールは、検出されたコード $C_{DET}$ に対応する較正コード $C^{*}_{DET}$ を決定し、較正コード $C^{*}_{DET}$ をインターフェースモジュール241に送り、インターフェースモジュール241は、第1のSARADC210、第2のSARADC220、及び利得モジュール230への「開始」信号と共に第1及び第2のDACのそれぞれに送る。

#### 【0090】

DACミスマッチ較正と同様の方法で、較正ビット $B^{*}_{LSB}$ が第2のSARADC220から出力され、制御モジュール240に送られる。差分計算モジュール247は、差分を計算し、誤りがあるか否かを検出する。誤差が検出された後、すなわち、最後の2ビット、すなわち、 $C_{OUT}$ 及び $B^{*}_{LSB}$ の最後のビットが「01」又は「10」を形成したときに、誤差を修正する必要がある。この補正是、第2のDAC224のキャパシタ $224a, 224b, \dots, 224n$ の容量値を調整することによって行われる。具体的には、ビットが「01」を形成する場合、容量を増加させるために補正信号が送られ、ビットが「10」を形成する場合には、静電容量を減少させるために補正信号が送られる。この信号は、図2Aの点線で示され、「補正」と呼ばれる。

#### 【0091】

本開示の2段パイプラインSARADC200は、第1の比較器216、利得モジュール230、及び第2の比較器226のうちの少なくとも1つのオフセットのために、誤りを訂正するために使用することもできる。第1の比較器216、利得モジュール230、及び第2の比較器226のオフセットをそれぞれ $V_1, V_2, V_3$ とすると、最終残差 $V_{RES2}$ 上のオフセットは次式で表される。

#### 【0092】

$$V_1 + V_2 - V_3 / Gain$$

#### 【0093】

ここで、Gainは増幅器の利得を示す。このオフセット値が冗長度より大きい場合、2段パイプラインSARADC200が間違ったデジタルコードを出力することが予想される。従って、第2のSARADC220の残差は次式で表される。

$$V_{RES2} = Gain * (V_{IN} + V_2) - V_{LSB} - V_3$$

#### 【0094】

本開示の一実施形態では、利得モジュール230と第2の比較器226による累積オフセット誤差が同時に補正され、DACミスマッチ較正及び利得較正と同様の方法で実行される。このオフセット較正のために、プリセットコードは任意のバイナリ値をとることができるが、DACミスマッチ較正又は利得誤差較正のいずれかに使用されるプリセットコードのいずれとも一致しないプリセットバイナリコードが選択される。

#### 【0095】

プリセットオフセット較正コード $C_{DET}$ が検出された場合、検出モジュール243は、オフセット較正モジュール246に信号を送信し、オフセット較正モジュールは対応す

10

20

30

40

50

る較正コード  $C^*_{DET}$  をインターフェース 241 に送る。次いで、インターフェース 241 は、このコード対応コードを「開始」信号とともに第 1 の SARADC210、第 2 の SARADC220、及び利得モジュール 230 に送る。

#### 【0096】

オフセット較正では、 $C_{MSB}$  と  $C_{LSB}$  の DAC コードをそれぞれ  $C^*_{MSB}$  と  $C^*_{LSB}$  に変更するだけでなく、利得モジュール 230 のオフセット補正モジュール 231 にも信号が送られる。具体的には、この信号はオフセット補正モジュール 231 の交差モジュール 231a に送られる（図 2D 参照）。この信号を受信すると、交差モジュール 231a は入力を切り替える。

#### 【0097】

一実施形態では、2段パイプライン SARADC200 は差動回路として実現される。この実施形態では、交差モジュール 231a は単に正の信号と負の信号と交差し、これらの信号をオフセット補正モジュール 231 に入力する。

#### 【0098】

代替実施形態では、2段パイプライン SARADC200 は、非差動回路として実現される。この実施形態では、交差モジュール 231a は入力信号と交差し、オフセット補正モジュールに供給される基準信号と共にオフセット補正モジュール 231 に入力される。

#### 【0099】

到来する信号を横切るのに続いて、第 1 及び第 2 の DAC もまた反転される。言い換えると、較正コード  $C^*_{DET}$  は  $C_{DET}$  の論理逆数である。従って、第 2 の SARADC220 の残差は次式で表される。

$$V^*_{RES2} = Gain * (-V_{IN} + V_2) - V^*_{LSB} - V_3$$

これにより、次式が導かれる。

#### 【0100】

$$V^*_{RES2} + V_{RES} = 2 * Gain * (V_2 - V_3 / Gain) \quad (5)$$

#### 【0101】

DAC ミスマッチ較正と同様の方法で、較正ビット  $B^*_{LSB}$  が第 2 の SARADC220 から出力され、制御モジュール 240 に送られる。そして、差分計算モジュール 247 は、式 (5) の符号に対応する差分を計算し、誤差があるか否かを検出する。誤差が検出された後、すなわち、 $C_{OUT}$  及び  $B^*_{LSB}$  の最後の 2 ビットが「00」又は「11」のいずれかを形成する場合、誤差を修正する必要がある。この修正は、図 2D に示すように、利得モジュール 230 のオフセット補正モジュール 231 の第 2 の可変キャパシタモジュール 231b を調整することによって（「第 2」という用語は、回路の第 2 の部分、すなわち、この場合は利得モジュール 230 を指す）実行される。具体的には、ビットが「00」を形成する場合、容量を増加させるために補正信号が送られる一方、ビットが「11」を形成する場合、静電容量を減少させるために補正信号が送られる。この信号は、図 2A の点線で示され、「補正」と呼ばれる。

#### 【0102】

誤差が現在 2 ビットによって検出された理由、すなわち、 $C_{OUT}$  と  $B^*_{LSB}$  の最後のビットは同一のである理由は、信号を交差させることによって、利得モジュール 230 又は第 2 の比較器 226 のいずれにもオフセット誤差がない場合、両方のビットは互いに反対であるためである。このため、そうでない場合は、すなわち、両方のビットが等しい場合、利得モジュール 230 及び第 2 の比較器 226 の少なくとも一方にオフセット誤差が存在する。

#### 【0103】

補正信号は、第 1 の増幅器 232 及び第 2 の増幅器 236 の前段であって、第 2 の ADC 段 220 の第 2 の比較器 226 の前段において配置された可変キャパシタモジュール 231b に送られるので、オフセット信号のこれらの可能なソースのすべてを同時に補正す

10

20

30

40

50

るために同一の信号を使用できる。

**【0104】**

上記のように、第1の比較器216のオフセット誤差も較正することができる。原則として、利得モジュール230及び第2の比較器226におけるオフセットを較正するのと同一の技術が使用され、本開示にかかる2段パイプラインSARADC200のタイミングは、上記の較正プロセスに関して異なる。

**【0105】**

図2Cに示すように、第1のSARADC210は、交差モジュール218a及び第1の可変キャパシタモジュール218bを備える（「第1の」という用語は、回路の第1の部分、すなわち、この場合は第1のSARADC210を指す）第1の比較器オフセット補正モジュール218を備える。

10

**【0106】**

利得モジュール230及び第2の比較器226におけるオフセットを較正することに関しては、交差モジュール218aは、較正がトリガされたときに入力信号を切り替える。このことは、ここでも、2段パイプラインSARADC200が差動回路又は到来信号であり、非差動回路に対する基準である場合には、正の信号及び負の信号ができる。従来通り、プリセットバイナリコード $C_{D E T}$ の必要もなく、他の較正方法のためのプリセットコードのいずれとも一致しないプリセットバイナリコードを割り当てることが勧められる。信号を交差させると、第1のDAC214も反転され、すなわち、較正コード $C_{D E T}^*$ はコード $C_{D E T}$ のバイナリ逆数となる。

20

**【0107】**

この較正では、較正残差信号 $V_{R E S}^*$ は生成されず、第1のSARADC210には1つの追加の比較サイクルしか存在しない。従って、他の較正方法に関して上述した、利得モジュール230における複雑なタイミングの必要もない。

**【0108】**

この較正方法における2段パイプラインSARADC200のタイミング図を図5に示す。第1の比較器216によって実行される余分な比較は1つだけである一方、残りのタイミングは通常の動作（図3参照）と同一のであることが明らかである。追加の比較の結果は、1つの較正ビット $B_{M S B}^*$ （図2Aに点線で示す）を得て差分計算モジュール247に送られる。

30

**【0109】**

そして、差分計算モジュール247は、誤差があるか否かを検出する。誤差が検出された後、すなわち、最後の2ビットすなわち $C_{O U T}$ 及び $B_{M S B}^*$ におけるMSBの最後のビットが「00」又は「11」のいずれかを形成した後、誤差を修正する必要がある。この補正は、第1のSARADC210のオフセット補正モジュール218の第1の可変キャパシタモジュール218bを調整することによって行われる。具体的には、ビットが「00」を形成する場合、静電容量を減少させるために補正信号が送られる一方、ビットが「11」を形成する場合、容量を増加させるために補正信号が送られる。この信号は、図2Aの点線で示され、「補正」と呼ばれる。

**【0110】**

40

バックグラウンドDACミスマッチ較正、バックグラウンド利得誤差較正、及びバックグラウンド比較器オフセット誤差較正について、別々に、より詳細に説明する。各タイプのバックグラウンド較正は、単独で、又は1つ又は複数の他のタイプのバックグラウンド較正と組み合わせて使用することができるよう容易に理解されるであろう。

**【0111】**

図2A～図2Eを参照して先に説明した要素又は構成要素は、同じ最後の2桁を有するが、「7」が先行する符号を有する（図6A～6E）。

**【0112】**

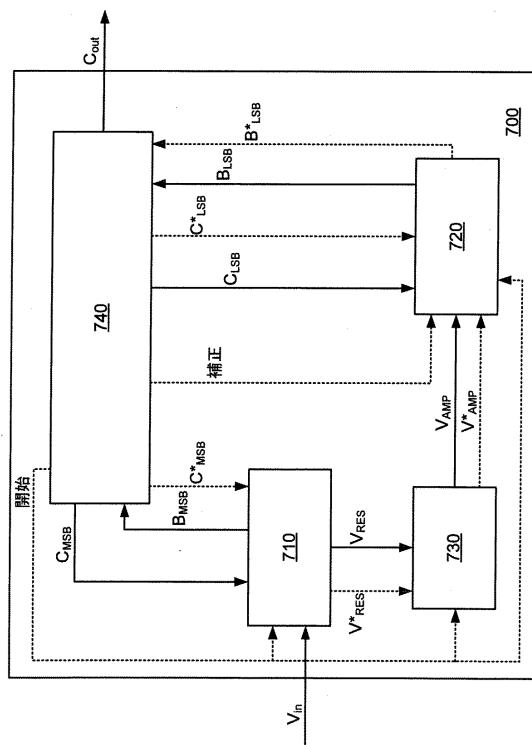

図6Aは、本開示にかかる2段パイプラインSARADC700のブロック図を示す。2段パイプラインSARADC700は、利得誤差較正のみを備える。2段パイプライン

50

S A R A D C 7 0 0 は、第1のS A R A D C 7 1 0 、第2のS A R A D C 7 2 0 、利得モジュール7 3 0 、及び制御モジュール7 4 0 を備える。2段パイプラインS A R A D C 7 0 0 の通常の動作は、図2A～図2Eを参照して上述し、図3に示すタイミング図と同一のタイミング図を有して、2段パイプラインS A R A D C 2 0 0 の通常の動作と同じである。

#### 【0113】

さらに、利得誤差較正中の2段パイプラインS A R A D C 7 0 0 の動作もまた、2段パイプラインS A R A D C 2 0 0 に関して上述したものと同じである。従って、同じタイミング図（図4に示す）が適用される。2段パイプラインS A R A D C 7 0 0 と2段パイプラインS A R A D C 2 0 0 の主な違いは、2段パイプラインS A R A D C 7 0 0 は、少ないモジュール数を有し、モジュール間の少ない接続数を有する。10

#### 【0114】

具体的には、利得誤差較正中に、入力信号 $V_{IN}$ は、第1のS A R A D C 7 1 0 に送られ、第1のS A R A D C 7 1 0 は入力信号に対応するデジタル信号のM S B を生成し、残差信号 $V_{RES}$ を出力する。さらに、第1のS A R A D C 7 1 0 は較正コード $C^{*}_{MSB}$ も受信し、それに基づいて較正残差信号 $V^{*}_{RES}$ が計算される。利得モジュール7 3 0 は、これらの両方を残差信号と較正残差信号とを増幅し、増幅された信号 $V_{AMP}$ 及び増幅された較正残差信号 $V^{*}_{AMP}$ の両方を第2のS A R A D C 7 2 0 に出力する。増幅された信号に基づいて、第2のS A R A D C 7 2 0 は、入力信号 $V_{IN}$ のL S B を決定する。第1のL S B を決定した後、制御モジュール7 4 0 は、較正コード $C^{*}_{MSB}$ を含む較正コード $C^{*}_{DET}$ を決定し、すべてのL S B が決定された後、 $C^{*}_{LSB}$ となる。較正コード $C^{*}_{LSB}$ 及び増幅された較正信号 $V^{*}_{AMP}$ を受信すると、第2のS A R A D C 7 2 0 は、利得誤差があるか否かを決定するために制御モジュール内で使用される較正ビット $B^{*}_{LSB}$ を計算する。利得誤差がある場合、制御モジュール7 4 0 はまた、第2のS A R A D C 7 2 0 に送信される補正信号を提供する。20

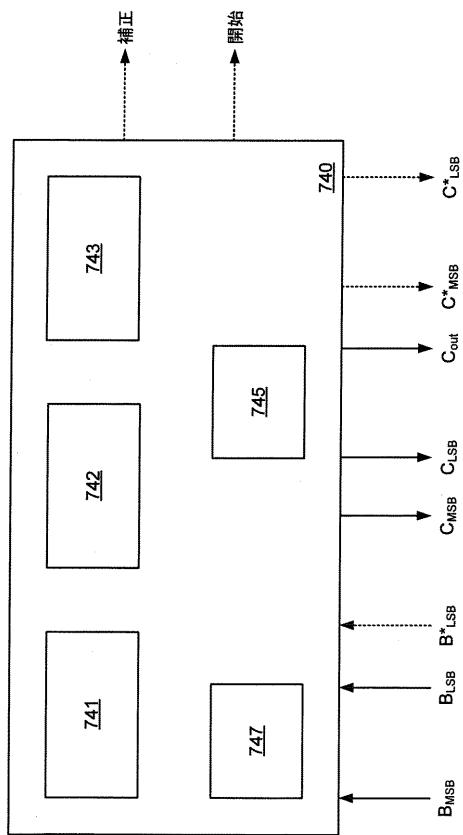

#### 【0115】

図6Bに示すように、制御モジュール7 4 0 は、インターフェースモジュール7 4 1 、メモリモジュール7 4 2 、検出モジュール7 4 3 、増幅器利得較正モジュール7 4 5 、及び差分計算モジュール7 4 7 を備える。これらのモジュールは、2段パイプラインS A R A D C 2 0 0 の利得誤差較正に関して既に説明したのと同じ機能を実行する。しかしながら、メモリモジュール7 4 2 は、利得誤差較正をトリガするコード $C_{DET}$ 及び $C^{*}_{DET}$ のみを記憶する。コード $C_{DET}$ 及び $C^{*}_{DET}$ は、利得誤差の較正に関して上記で説明したのと同じコードとすることができます。しかしながら、利得誤差校正のみが行われるため、コード $C_{DET}$ 及び $C^{*}_{DET}$ は、それらが、予め設定されたバイナリコードと一致しないことという制限を満たす必要はない。ここで、予め設定されたバイナリコードは、D A C ミスマッチ較正がないために、これらのコードは2段パイプラインS A R A D C 7 0 0 で使用されないので、D A C ミスマッチ較正をトリガするものである。30

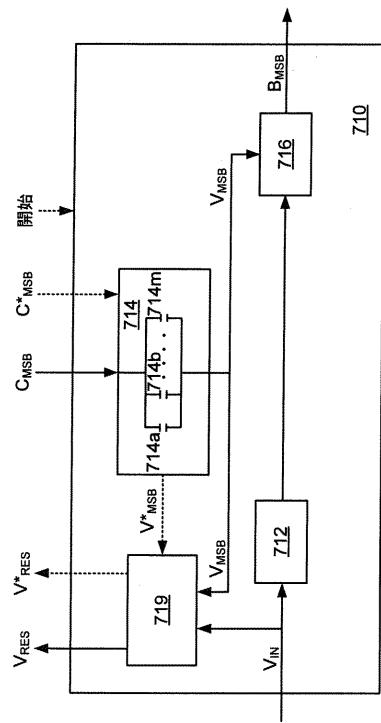

#### 【0116】

図7Cは、第1のS A R A D C 7 1 0 の詳細を示す。この第1のS A R A D C 7 1 0 は、第1のS A R A D C 6 1 0 に非常に類似している。第1のS A R A D C 7 1 0 と第1のS A R A D C 2 1 0 の主な違いは、第1の比較器オフセット較正モジュール2 1 8 は、2段パイプラインS A R A D C 7 0 0 にオフセット較正がないので存在しないことである。40

#### 【0117】

第1のS A R A D C 7 1 0 は、トラックアンドホールドモジュール7 1 2 と、キャパシタ7 1 4 a , 7 1 4 b , … , 7 1 4 m を有する第1のD A C 7 1 4 と、第1の比較器7 1 6 と、残差生成モジュール7 1 9 とを備える。特に、D A C ミスマッチ較正がないので、コンデンサ7 1 4 a , 7 1 4 b , … , 7 1 4 m はこの実施形態では調整可能である必要はない。従って、入力される「補正」信号も存在しない。さらに、これらのモジュールは、2段パイプラインS A R A D C 2 0 0 (図2C) の利得誤差較正に関して既に説明したのと同じ機能を果たす。50

## 【0118】

図6Dは、利得モジュール730の詳細を示す。この利得モジュール730は、利得モジュール630と同一であり、このように、利得モジュール730と利得モジュール230との間の主な差異は、比較器オフセット較正モジュール231は、2段パイプラインSARADC700にオフセット較正が存在しないことである。

## 【0119】

利得モジュール730は、第1の増幅器732と、第2の増幅器736と、第1のスイッチ734と、コンデンサ $C_s$ と、第2のスイッチ738とを備える。利得モジュール230に関して説明したように、これらのモジュールは、残差信号を増幅し、一時的にコンデンサ $C_s$ に信号を蓄積することができ、第2のSARADC720が、較正ビット $B_{LSB}^{*}$ を決定するために追加の比較を実行する必要がある入力信号のLSBの決定を終了することを可能にする。

10

## 【0120】

図6Eは、第2のSARADC720を示す。このSARADC720は、第2のSARADC220と同一である。第2のSARADC720は、トラックアンドホールドモジュール722と、第2のDAC724と、第2の比較器726とを備える。さらに、第2のDAC724のコンデンサ724a, 724b, ..., 724nは、利得誤差補正として調整可能であり、補正信号に送られ、コンデンサ724a, 724b, ..., 724nの少なくとも1つの容量を増減するために使用される。

## 【0121】

特定の実施形態に関して本開示の態様を説明したが、これらの態様は他の形態で実施されてもよいことは容易に理解されるであろう。

20

【図1】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図3】

【図4】

【図5】

【図6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

---

フロントページの続き

(72)発明者 ピーテル・ハルペ

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 7 5 番 アイメック・ヴェーゼットウェー内

(72)発明者 リィ・ハンユエ

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 7 5 番 アイメック・ヴェーゼットウェー内

審査官 渡井 高広

(56)参考文献 特表 2 0 1 6 - 5 3 1 5 3 2 (JP, A)

特開 2 0 1 5 - 2 3 1 2 3 9 (JP, A)

米国特許第 0 9 2 1 9 4 9 2 (US, B1)

特開 2 0 1 7 - 5 3 3 2 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 3 M 1 / 1 0

H 0 3 M 1 / 2 0