(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5227411号

(P5227411)

(45) 発行日 平成25年7月3日(2013.7.3)

(24) 登録日 平成25年3月22日(2013.3.22)

(51) Int.Cl.

F 1

H02M 3/07 (2006.01)

H02M 3/07

H01L 21/822 (2006.01)

H01L 27/04

H01L 27/04 (2006.01)

G

請求項の数 6 (全 20 頁)

(21) 出願番号 特願2010-529701 (P2010-529701)

(86) (22) 出願日 平成21年8月25日 (2009.8.25)

(86) 国際出願番号 PCT/JP2009/064767

(87) 国際公開番号 WO2010/032589

(87) 国際公開日 平成22年3月25日 (2010.3.25)

審査請求日 平成22年4月21日 (2010.4.21)

(31) 優先権主張番号 特願2008-237473 (P2008-237473)

(32) 優先日 平成20年9月17日 (2008.9.17)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 303046277

旭化成エレクトロニクス株式会社

東京都千代田区神田神保町一丁目105番

地

(74) 代理人 100066980

弁理士 森 哲也

(74) 代理人 100103850

弁理士 田中 秀▲てつ▼

(72) 発明者 浜田 剛志

東京都千代田区神田神保町一丁目105番

地

審査官 服部 俊樹

最終頁に続く

(54) 【発明の名称】チャージ・ポンプ回路及び半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項1】

入力電源からの電荷をキャパシタに蓄積する第1の状態と前記キャパシタに蓄積された電荷を電源供給部に転送する第2の状態とを交互に繰り返すことで所定の極性の出力電源を生成するチャージ・ポンプ回路であって、

前記出力電源で駆動されるアンプ回路の出力段を構成する複数のトランジスタのうち、前記出力電源側のトランジスタの出力電流である第1の電流に比例する第2の電流を発生する、前記第1の電流とカレントミラーの関係にある電流発生部と、

該電流発生部において発生した第2の電流に基づき、前記キャパシタに電荷を蓄積するときの電流の供給量を制御する供給電流量制御手段と、

を備えることを特徴とするチャージ・ポンプ回路。

## 【請求項2】

前記供給電流量制御手段は、前記キャパシタに供給する電流の量を、該電流の量と前記アンプ回路に流れる電流の量との間に正の相関が成立するよう制御することを特徴とする請求項1に記載のチャージ・ポンプ回路。

## 【請求項3】

前記供給電流量制御手段は、前記キャパシタに供給する電流の量を、該電流の量が前記アンプ回路に流れる電流の量よりも予め設定された量だけ多くなるように制御することを特徴とする請求項2に記載のチャージ・ポンプ回路。

## 【請求項4】

10

20

前記キャパシタの両端間の電圧を検出する電圧検出手段と、

前記電圧検出手段で検出された電圧のレベルと所定のレベルとを比較する電圧レベル比較手段と、

前記電圧レベル比較手段の比較結果に基づき、前記第1の状態において前記検出された電圧のレベルが前記所定のレベルに到達したときに、前記第1の状態を前記第2の状態に切り替える切替制御手段と、を備えることを特徴とする請求項1乃至請求項3のいずれか1項に記載のチャージ・ポンプ回路。\_\_\_\_\_

**【請求項5】**

前記入力電源から、該入力電源の極性とは反対の極性の出力電源を生成し、

前記電源供給部は、前記出力電源と、前記出力電源とは反対の極性の電源との間の電圧範囲の電源を前記アンプ回路に供給する構成となっていることを特徴とする請求項1乃至請求項4のいずれか1項に記載のチャージ・ポンプ回路。10

**【請求項6】**

請求項1乃至請求項5のいずれか1項に記載のチャージ・ポンプ回路を含んで構成される回路を半導体基板上に集積化して成ることを特徴とする半導体集積回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、被駆動回路に電源を供給するチャージ・ポンプ回路に係り、特に、キャパシタに電荷を蓄積するときに発生するノイズを小さくするのに好適なチャージ・ポンプ回路及び半導体集積回路に関する。20

**【背景技術】**

**【0002】**

従来、単電源すなわち一つの正電源下で駆動され、グランド終端される小抵抗に対して信号を出力する回路として、図13に示すようなビデオアンプを駆動するチャージ・ポンプ回路の技術が特許文献1に開示されている。この従来技術は、正電源(VCC)とグランド電圧(GND)からチャージ・ポンプ回路で負電源(VEE)を発生し、正電源(VCC)と負電源(VEE)との間で駆動される被駆動回路で、グランド電圧(GND)を中心レベルとしてDC(直流)カット用のキャパシタを用いて直接負荷を駆動し、信号を出力するものである。30

**【0003】**

ここで用いられるチャージ・ポンプ回路は、クロック信号の第1の期間で与えられた正電圧とグランド電圧の間にキャパシタを直接接続して電荷を蓄積し、第2の期間でグランド電圧と負電圧を発生する負電圧端子の間で該キャパシタを直接接続して、蓄積された電荷を転送させる。この一連の動作を繰り返し行うことで負電圧を発生する。

このチャージ・ポンプ回路において、キャパシタに電荷を蓄積する期間における電流量は、期間の前半は大きいが時間の経過と共に減少し、期間の後半は小さくなる。ビデオアンプ及びその負荷で消費する電流量が大きいときは、この期間の前半に流れる大きな電流が原因となって、電源ノイズ、電流供給能力の超過などの問題が発生する。40

**【0004】**

この問題を解決するための技術として、図14に示すビデオアンプを駆動するチャージ・ポンプ回路の技術が特許文献2に開示されている。この技術では、チャージ・ポンプ回路のキャパシタに電荷を蓄積する期間における電流量を一定にすることを行う。この技術は、ビデオアンプで消費する電流の大きさに関わらず、内部の定電流回路を用いて一定の電流を作り出し、この定電流でキャパシタに電荷を蓄積するため、電荷を蓄積する期間の前半と後半で同等の電流が流れ、期間の前半だけに大きな電流が流れることを防ぐことができる。

**【先行技術文献】**

**【特許文献】**

## 【0005】

【特許文献1】特許公報 特開2001-309400

【特許文献2】特許公報 特開2005-151777

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、上記特許文献2の従来技術においては、ビデオアンプで消費する電流量の大きさに関わらず、キャパシタに電荷を蓄積する電流が一定であることから、この定電流値はビデオアンプで消費する電流が最大の時にチャージ・ポンプ回路が問題なく動作できる大きめの値に設定する必要があった。そのため、通常使用範囲では必要以上に大きな電流が流れるため、電源ノイズが大きくなり、さらに、電源としては、大きな電流供給能力のあるものが必要であった。

10

## 【0007】

そこで、本発明は、このような従来の技術の有する未解決の課題に着目してなされたものであって、電源を発生し、発生された電源で被駆動回路を駆動するチャージ・ポンプ回路において、チャージ・ポンプ回路のキャパシタに電荷を蓄積するときに発生するノイズを小さくするのに好適なチャージ・ポンプ回路及び半導体集積回路を提供することを目的とするものである。

20

## 【課題を解決するための手段】

## 【0008】

〔発明1〕上記目的を達成するために、発明1のチャージ・ポンプ回路は、入力電源からの電荷をキャパシタに蓄積する第1の状態と前記キャパシタに蓄積された電荷を電源供給部に転送する第2の状態とを交互に繰り返すことで所定の極性の出力電源を生成するチャージ・ポンプ回路であって、前記出力電源で駆動されるアンプ回路の出力段を構成する複数のトランジスタのうち、前記出力電源側のトランジスタの出力電流である第1の電流に比例する第2の電流を発生する、前記第1の電流とカレントミラーの関係にある電流発生部と、該電流発生部において発生した第2の電流に基づき、前記キャパシタに電荷を蓄積するときの電流の供給量を制御する供給電流量制御手段と、を備える。

## 【0009】

このような構成であれば、供給電流量制御手段において、出力電源で駆動されるアンプ回路の出力段を構成する複数のトランジスタのうち、出力電源側のトランジスタに流れる電流の量（以下、電流量と称す）の増減に追随して、キャパシタに供給する電流量（以下、供給電流量と称す）を増減する制御を行うことが可能である。

30

これによって、アンプ回路で消費される電流量と、キャパシタに電荷を蓄積する（以下、充電と称す）ときの供給電流量との差を小さくすることができるので、アンプ回路に電流を過供給するのを防ぐことができると共に、キャパシタを充電するときに発生するノイズを小さくすることができるという効果が得られる。

## 【0010】

〔発明2〕更に、発明2のチャージ・ポンプ回路は、発明1のチャージ・ポンプ回路において、前記供給電流量制御手段は、前記キャパシタに供給する電流の量を、該電流の量と前記被駆動回路に流れる電流の量との間に正の相関が成立するように制御する。

40

このような構成であれば、発明1と同等の作用及び効果を得ることができる。

## 【0011】

〔発明3〕更に、発明3のチャージ・ポンプ回路は、発明1又は2のチャージ・ポンプ回路において、前記供給電流量制御手段は、前記キャパシタに供給する電流の量を、該電流の量が前記被駆動回路に流れる電流の量よりも予め設定された量だけ多くなるように制御する。

このような構成であれば、供給電流量に余裕を持たせることができるので、負荷（被駆動回路）に流れる電流量が0のときや、負荷に流れる電流量がばらついて供給電流量の追随が間に合わないときなどにおいても、チャージ・ポンプ回路を正常に動作させることができ

50

できるという効果が得られる。

【0012】

〔発明4〕更に、発明4のチャージ・ポンプ回路は、発明1乃至3のいずれか1のチャージ・ポンプ回路において、前記キャパシタの両端間の電圧を検出する電圧検出手段と、前記電圧検出手段で検出された電圧のレベルと所定のレベルとを比較する電圧レベル比較手段と、前記電圧レベル比較手段の比較結果に基づき、前記第1の状態において前記検出された電圧のレベルが前記所定のレベルに到達したときに、前記第1の状態を前記第2の状態に切り替える切替制御手段と、を備える。

このような構成であれば、キャパシタの両端間の電圧のレベルが所定のレベルに到達するまではキャパシタを充電し、所定のレベルに到達したときに、キャパシタの充電を止めて、充電された電荷の転送を行わせることができる。

これによって、所定のレベルを所望の電圧のレベルに設定することで、所望の電圧の出力電源を生成することができるという効果が得られる。

【0013】

〔発明5〕更に、発明5のチャージ・ポンプ回路は、発明1乃至4のいずれか1のチャージ・ポンプ回路において、前記供給電流量制御手段は、複数の前記被駆動回路を駆動するときに、前記複数の被駆動回路に流れる電流の量の総和に基づき、前記キャパシタに電荷を蓄積するときの電流の供給量を制御する。

このような構成であれば、供給電流量制御手段において、例えば、複数の被駆動回路に流れる電流量の総和の増減に追随して、キャパシタの供給電流量を増減する制御を行うことが可能である。

これによって、複数の被駆動回路で消費される電流量の総和と、キャパシタを充電するときの供給電流量との差を小さくすることができるので、複数の被駆動回路に対して電流を過供給するのを防ぐことができると共に、キャパシタを充電するときに発生するノイズを小さくすることができるという効果が得られる。

【0014】

〔発明6〕更に、発明6のチャージ・ポンプ回路は、発明1乃至5のいずれか1のチャージ・ポンプ回路において、前記供給電流量制御手段は、前記被駆動回路の出力部に流れる電流の量に基づき、前記キャパシタに電荷を蓄積するときの電流の供給量を制御する。

このような構成であれば、被駆動回路の出力部に流れる電流の量に基づきキャパシタの供給電流量を制御することができるので、出力部に流れる電流をチャージ・ポンプ回路にフィードバックすることで、比較的簡易な構成で供給電流量の制御を行うことができるという効果が得られる。

【0015】

〔発明7〕更に、発明7のチャージ・ポンプ回路は、発明1乃至6のいずれか1のチャージ・ポンプ回路において、前記被駆動回路がアンプ回路である。

このような構成であれば、被駆動回路がアンプ回路であることから、容易に半導体集積回路で実現することができるという効果が得られる。

【0016】

〔発明8〕更に、発明8のチャージ・ポンプ回路は、発明1乃至7のいずれか1のチャージ・ポンプ回路において、前記供給電流量制御手段は、前記アンプ回路の出力段の出力電流である第1の電流に比例する第2の電流を発生する、前記第1の電流とカレントミラーの関係にある電流発生部を備え、該電流発生部において発生した第2の電流に基づき、前記第1の状態において前記キャパシタに電荷を蓄積するときの電流の供給量を制御する。

このような構成であれば、アンプ回路から負荷に流れる第1の電流に比例した第2の電流の電流量に基づきキャパシタに供給する供給電流量を制御することができる。

【0017】

従って、第1の電流の電流量の増減に追随して、キャパシタに供給する供給電流量を増

10

20

30

40

50

減する制御を容易に行うことが可能である。

これによって、被駆動回路に対する負荷で消費される電流量と、キャパシタに供給する供給電流量との差を小さくすることができるので、被駆動回路に電流を過供給するのを防ぐことができると共に、キャパシタを充電するときに発生するノイズを小さくすることができるという効果が得られる。

#### 【0018】

〔発明9〕更に、発明9のチャージ・ポンプ回路は、発明1乃至8のいずれか1のチャージ・ポンプ回路において、前記入力電源から、該入力電源の極性とは反対の極性の出力電源を生成し、前記電源供給部は、前記出力電源と、前記出力電源とは反対の極性の電源との間の電圧範囲の電源を前記被駆動回路に供給する構成となっている。

10

このような構成であれば、電源供給部において、例えば、グランド電圧を基準にして、入力電源と同極の正電圧の電源と、当該チャージ・ポンプ回路で生成した負電圧の電源とを被駆動回路に供給することが可能である。

これによって、グランド電圧を基準として、正電源及び負電源の双方を用いて駆動する被駆動回路を駆動させることができるという効果が得られる。

#### 【0019】

〔発明10〕一方、上記目的を達成するために、発明10の半導体集積回路は、発明1乃至9のいずれか1項に記載のチャージ・ポンプ回路を含んでなる回路を半導体基板上に集積化して成る。

このような構成であれば、上記発明1乃至9のいずれか1に記載のチャージ・ポンプ回路と同等の作用及び効果が得られる半導体集積回路を得ることができる。

20

#### 【図面の簡単な説明】

#### 【0020】

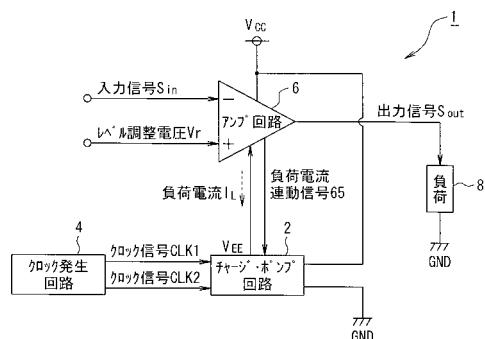

【図1】負荷駆動システム1の構成を示すブロック図である。

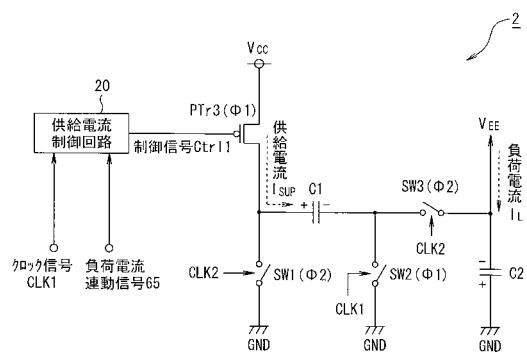

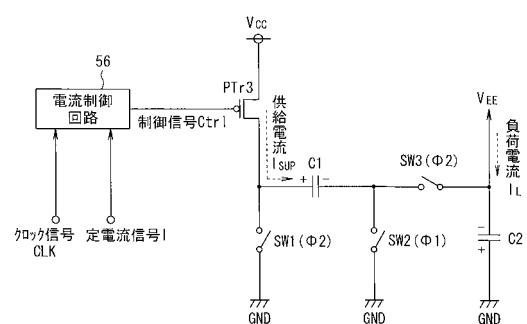

【図2】チャージ・ポンプ回路2の詳細な構成を示す回路図である。

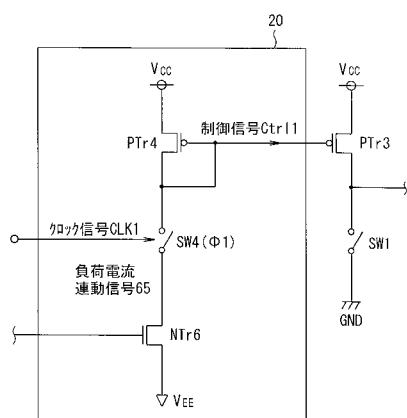

【図3】供給電流制御回路20の詳細な構成を示す回路図である。

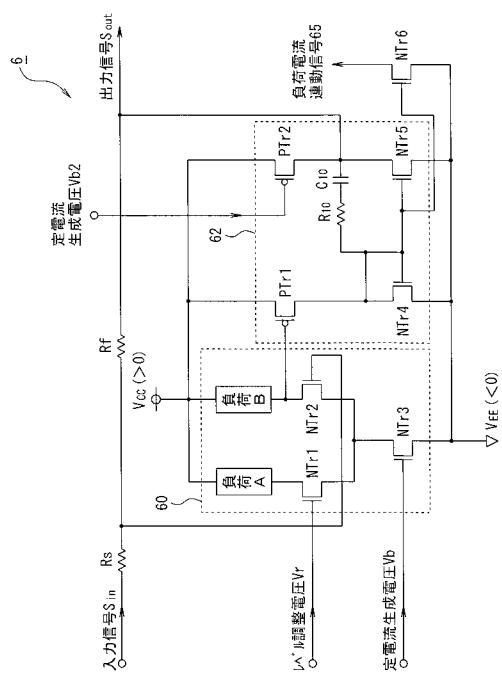

【図4】アンプ回路6の詳細な構成を示す回路図である。

【図5】チャージ・ポンプ回路2、クロック発生回路4及びアンプ回路6を流れる信号のタイミングチャートである。

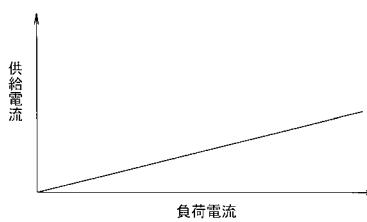

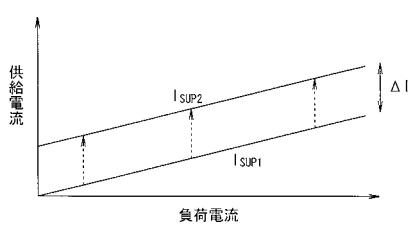

【図6】負荷電流 $I_L$ と供給電流 $I_{SUP}$ との関係を示す図である。

30

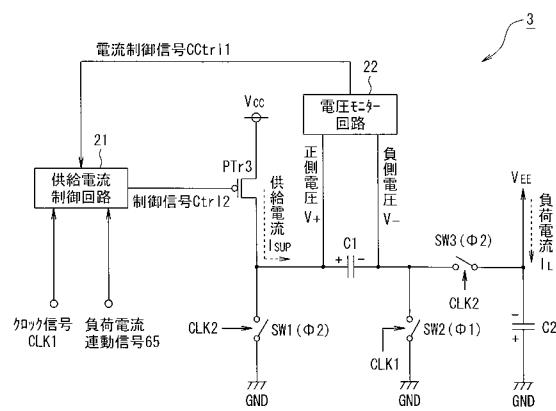

【図7】チャージ・ポンプ回路3の詳細な構成を示す回路図である。

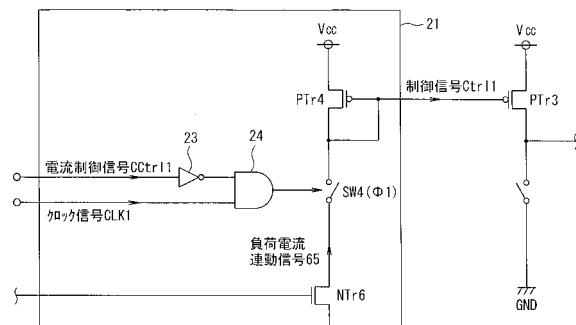

【図8】供給電流制御回路21の詳細な構成を示す回路図である。

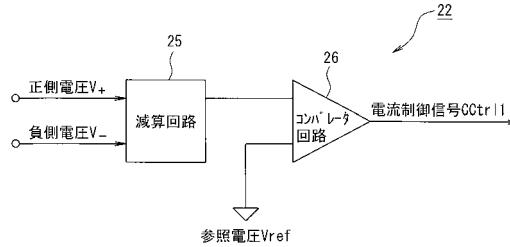

【図9】電圧モニター回路22の詳細な構成を示す回路図である。

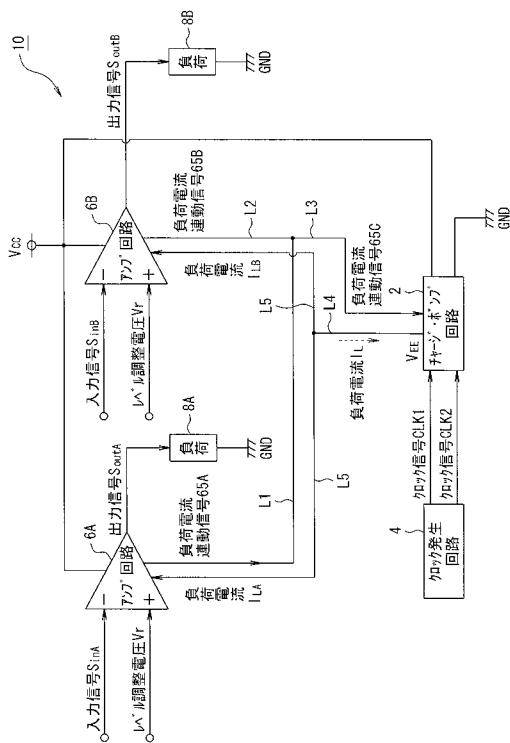

【図10】負荷駆動システム10の構成を示すブロック図である。

【図11】負荷駆動システム11の構成を示すブロック図である。

【図12】供給電流 $I_{SUP1}$ 及び $I_{SUP2}$ と負荷電流 $I_L$ との関係を示す図である。

【図13】従来のビデオアンプを駆動するチャージ・ポンプ回路の例を示す図である。

【図14】従来のビデオアンプを駆動するチャージ・ポンプ回路の他の例を示す図である。

【発明を実施するための形態】

40

#### 【0021】

#### 〔第1の実施の形態〕

以下、本発明の第1の実施の形態を図面に基づき説明する。図1～図6は、本発明に係るチャージ・ポンプ回路及び半導体集積回路の第1の実施の形態を示す図である。

本実施の形態では、本発明に係るチャージ・ポンプ回路を、被駆動回路であるアンプ回路に適用し、このアンプ回路によって入力信号を増幅して負荷に供給するシステムを構成する。

#### 【0022】

まず、本発明に係る負荷駆動システム1の構成を図1に基づき説明する。図1は、本発明の第1の実施の形態に係る負荷駆動システム1の構成を示すブロック図である。

50

負荷駆動システム 1 は、図 1 に示すように、チャージ・ポンプ回路 2 と、クロック発生回路 4 と、アンプ回路 6 と、負荷 8 とを含んで構成される。

チャージ・ポンプ回路 2 は、キャパシタとスイッチング素子とを用いたチャージ・ポンプ方式によって、正極の入力電源  $V_{CC}$  から負極の出力電源  $V_{EE}$  を生成し、この生成する機能を有している。この生成した  $V_{EE}$  はアンプ回路 6 に供給される。

#### 【 0 0 2 3 】

クロック発生回路 4 は、水晶振動子、セラミック振動子などの振動子を備え、チャージ・ポンプ回路 2 の有するスイッチング素子のオン・オフを制御する 2 種類のクロック信号 CLK1、CLK2 ( 以下、単に CLK1、CLK2 と称す ) を発生する機能を有している。なお、CLK1 と CLK2 とは、同じ周期及び同じ振幅の信号であり、一方に対して他方の位相が半周期ずれた信号である。つまり、クロック信号 CLK1 がハイレベルのときにクロック信号 CLK2 がローレベルとなり、クロック信号 CLK1 がローレベルのときにクロック信号 CLK2 がハイレベルとなる。また、発生したクロック信号 CLK1、CLK2 は、チャージ・ポンプ回路 2 に供給される。

#### 【 0 0 2 4 】

アンプ回路 6 は、OP アンプを含んで構成される反転增幅回路であって、反転入力端子 ( - ) に入力された入力信号  $S_{in}$  と、非反転入力端子 ( + ) に入力されたオフセット電圧のレベル調整電圧  $V_r$  との差分の信号を反転增幅してなる出力信号  $S_{out}$  を出力する機能を有している。

負荷 8 は、アンプ回路 6 からの出力信号  $S_{out}$  によって駆動される負荷であり、例えば、入力信号  $S_{in}$  が音声入力信号であれば、スピーカやヘッドホンなどが該当する。また、後段となるスピーカやヘッドホンを駆動するバッファ回路なども該当する。

#### 【 0 0 2 5 】

次に、図 2 に基づき、チャージ・ポンプ回路 2 の詳細な構成を説明する。

ここで、図 2 は、チャージ・ポンプ回路 2 の詳細な構成を示す回路図である。

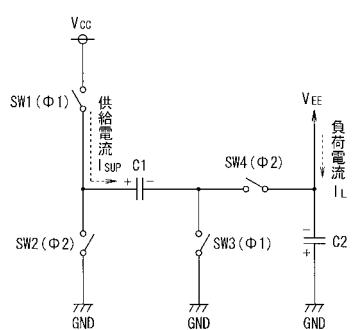

本実施の形態のチャージ・ポンプ回路 2 は、図 2 に示すように、P チャンネル型の MOS トランジスタである PTr3 と、キャパシタ C1、C2 と、スイッチング素子 SW1、SW2、SW3 と、供給電流制御回路 20 を含んで構成される。

#### 【 0 0 2 6 】

本実施の形態において、スイッチング素子 SW1、SW2 及び SW3 は、N チャンネル型の MOS トランジスタから構成されている。なお、N チャンネル型の MOS トランジスタに限らず P チャンネル型の MOS トランジスタで構成することも可能である。

供給電流制御回路 20 の制御信号出力端子 ( 不図示 ) は、PTr3 のゲート端子に電気的に接続され、PTr3 のソース端子は、電源  $V_{CC}$  の入力端子に電気的に接続されている。なお、この入力端子には、電圧  $V_{CC}$  の電源の電源供給端子が電気的に接続されている。

#### 【 0 0 2 7 】

PTr3 のドレイン端子は、C1 の正極側の端子と SW1 のドレイン端子とにそれぞれ電気的に接続されており、SW1 のソース端子はグランド端子 ( GND ) に電気的に接続されている。なお、このグランド端子には、グランド電位 ( 0 [V] ) が接続されている。

更に、図示していないが、SW1 のゲート端子は、クロック発生回路 4 の CLK1 の出力端子と電気的に接続されている。

#### 【 0 0 2 8 】

C1 の負極側の端子は、SW2 及び SW3 のドレイン端子にそれぞれ電気的に接続され、SW2 のソース端子はグランド端子に電気的に接続され、SW3 のソース端子は C2 の負極側の端子に電気的に接続されている。

更に、図示していないが、SW2 のゲート端子は、クロック発生回路 4 のクロック信号 CLK1 の出力端子と電気的に接続され、SW3 のゲート端子は、クロック発生回路 4 の CLK2 の出力端子と電気的に接続されている。

#### 【 0 0 2 9 】

次に、図 3 に基づき、供給電流制御回路 20 の詳細な構成を説明する。

ここで、図 3 は、供給電流制御回路 20 の詳細な構成を示す回路図である。

10

20

30

40

50

本実施の形態の供給電流制御回路20は、図3に示すように、Pチャンネル型のMOSトランジスタであるPTr4と、スイッチング素子SW4と、Nチャンネル型のMOSトランジスタであるNTr6とを含んで構成される。

本実施の形態において、スイッチング素子SW4は、Nチャンネル型のMOSトランジスタから構成されている。なお、Nチャンネル型のMOSトランジスタに限らずPチャンネル型のMOSトランジスタで構成することも可能である。

#### 【0030】

PTr4のソース端子は、電源 $V_{CC}$ の入力端子に電気的に接続されており、ドレイン端子は、SW4のドレイン端子にそれぞれ電気的に接続されている。なお、この入力端子には、電源 $V_{CC}$ の電源供給端子が電気的に接続されている。

PTr4のゲート端子は、PTr4のドレイン端子及びPTr3のゲート端子とそれぞれ電気的に接続されており、PTr3とPTr4とでカレントミラー回路を構成している。

#### 【0031】

SW4のソース端子は、NTr6のドレイン端子に電気的に接続され、ゲート端子は、クロック発振回路4のCLK1の出力端子と電気的に接続されている。

NTr6のソース端子は、出力電源である負電圧 $V_{EE}$ に電気的に接続されており、ゲート端子は、アンプ回路6を構成するNチャンネル型のMOSトランジスタであるNTr5(後述)のゲート端子と電気的に接続されている。

そして、NTr6及びSW4がオンのときに、NTr6のドレイン-ソース間を流れる電流信号である負荷電流運動信号65が、SW4を介してPTr4のゲート端子及びドレイン端子と、PTr3のゲート端子とに供給される。

#### 【0032】

上記構成によって、チャージ・ポンプ回路2は、クロック発生回路4からのCLK1がハイレベルのときにSW2及びSW4がオンになり、ローレベルのときにオフとなる。また、クロック信号CLK2がハイレベルのときにSW1及びSW3がオンになり、ローレベルのときにオフとなる。但し、SW2とSW3は負電圧領域でパスをオン・オフするために適切にレベルシフトされて用いられる。

#### 【0033】

そして、SW2及びSW4がオンで、SW1及びSW3がオフのときに、制御信号Ctrl1がPTr3の駆動電位(PTr3をオンにする電位)のときは、PTr3がオンとなって、電源 $V_{CC}$ からの供給電流 $I_{SUP}$ がC1に供給され、この第1の期間(1)においてC1が充電される。

また、SW2及びSW4がオフで、SW1及びSW3がオンのときは、PTr3がオフとなって、電源 $V_{CC}$ からの供給電流がC1に供給されなくなり、この第2の期間(2)においてはC1が充電されない。

#### 【0034】

一方、SW2及びSW4がオフで、SW1及びSW3がオンのときは、GND-SW1-C1-SW3-C2-GNDの閉ループが構成され、C1に蓄積された電荷が、図2に示す極性でC2へと転送される。

SW2及びSW4のオン・オフと、SW1及びSW3のオン・オフとの切り替えを、上記のCLK1及びCLK2による切り替えタイミングで繰り返し(継続して)行うことで、グランド端子と出力電源の供給端子との間に、正電圧 $V_{CC}$ の極性を反転させた電圧と略同じレベルの負電圧 $V_{EE}$ を発生させることができる。

#### 【0035】

また、制御信号Ctrl1の電位は、負荷電流運動信号65の電流レベルに応じて変化し、負荷電流運動信号65の電流レベルが大きければ大きいほど制御信号Ctrl1の電位が低くなる。従って、負荷電流運動信号65の電流レベルが大きければ大きいほどPTr3のゲート-ソース間の電圧 $V_{GS}$ が負方向に大きくなり、これにより、供給電流 $I_{SUP}$ が大きくなる。

10

20

30

40

50

つまり、負荷電流連動信号 65 と、供給電流  $I_{SUP}$  との間には正の相関が成立し、負荷電流連動信号 65 の電流レベルの増減に応じて、キャパシタ C1 への供給電流量が増減する。

#### 【0036】

次に、図 4 に基づき、アンプ回路 6 の詳細な構成を説明する。

ここで、図 4 は、アンプ回路 6 の詳細な構成を示す回路図である。

アンプ回路 6 は、図 4 に示すように、入力段差動回路 60 と、出力段回路 62 と、抵抗  $R_s$ ,  $R_f$  とを含んで構成される。

入力段差動回路 60 は、負荷 A と、負荷 B と、N チャンネル型の MOS トランジスタである NTr1, NTr2, NTr3 とを含んで構成される。 10

出力段回路 62 は、P チャンネル型の MOS トランジスタである PTr1, PTr2、N チャンネル型の MOS トランジスタである NTr4, NTr5 と、位相補償のための抵抗  $R_{10}$  及びキャパシタ  $C_{10}$  とを含んで構成される。

#### 【0037】

抵抗  $R_s$ ,  $R_f$  は、アンプ回路 6 の電圧利得を決めると共に出力信号  $S_{out}$  を反転入力端子 ( - ) である NTr2 のゲート端子に帰還させる役割を有している。

つまり、アンプ回路 6 は、差動対となる入力段差動回路 60 と出力段回路 62 とから構成される OP アンプと、抵抗  $R_s$  及び  $R_f$  とを含んで構成される反転増幅回路となる。

本実施の形態において、負荷 A 及び負荷 B は、抵抗素子  $R_A$  及び  $R_B$  とする。なお、負荷 A 及び負荷 B は、MOS トランジスタを用いたカレントミラー回路として構成するなど、他の素子を用いて構成してもよい。 20

#### 【0038】

また、アンプ回路 6 の正電源入力端子及び負電源入力端子には、チャージ・ポンプ回路 2 から、正電圧  $V_{CC}$  の正電源と、負電圧  $V_{EE}$  の負電源とが供給されている。

入力段差動回路 60 を構成する、 $R_A$  及び  $R_B$  の一端は、電源  $V_{CC}$  の正電源入力端子にそれぞれ電気的に接続され、 $R_A$  の他端は、NTr1 のドレイン端子に電気的に接続され、 $R_B$  の他端は、NTr2 のドレイン端子に電気的に接続されている。

#### 【0039】

更に、NTr1 及び NTr2 のソース端子は、NTr3 のドレイン端子に電気的に接続され、NTr3 のソース端子は、電源  $V_{EE}$  の負電源入力端子に電気的に接続されている。 30

更に、NTr2 のゲート端子は、入力信号  $S_{in}$  の入力端子になっており、外部の装置(不図示)から入力信号  $S_{in}$  が入力される。

更に、NTr1 のゲート端子は、レベル調整電圧  $V_r$  が印加され、NTr3 のゲート端子には、NTr3 を飽和領域で駆動させるのに十分な定電流生成電圧  $V_b$  が印加される。

#### 【0040】

出力段回路 62 を構成する、PTr1, PTr2 のソース端子は、正電源入力端子に電気的に接続され、PTr1 のゲート端子は、NTr2 のドレイン端子に電気的に接続されており、PTr2 のゲート端子には、PTr2 を飽和領域で駆動させるのに十分な定電流生成電圧  $V_{b2}$  が印加される。

更に、PTr1 のドレイン端子は、NTr4 のドレイン端子と電気的に接続され、PTr2 のドレイン端子は、NTr5 のドレイン端子と電気的に接続され、NTr4 及び NTr5 のソース端子は、負電源入力端子と電気的に接続されている。 40

#### 【0041】

更に、NTr5 のゲート端子は、抵抗  $R_{10}$  の一端と電気的に接続され、 $R_{10}$  の他端はキャパシタ  $C_{10}$  の一端と電気的に接続され、 $C_{10}$  の他端は NTr5 のドレイン端子及び信号出力端子にそれぞれ電気的に接続されている。また、信号出力端子は、負荷 8 と電気的に接続されている。

更に、NTr4 のゲート端子と NTr5 のゲート端子とは電気的に接続されており、NTr4 のゲート端子とドレイン端子とは電気的に接続されている。この構成により、NTr4 と NTr5 とカレントミラー回路を構成する。 50

## 【0042】

また、NTr4及びNTr5のゲート端子は、NTr6のゲート端子と電気的に接続されており、NTr5のドレイン-ソース間を流れる第1の電流と、NTr6のドレイン-ソース間を流れる第2の電流との間にカレントミラーの関係が成立している。なお、第1の電流は、負荷8に流れる電流 $I_L$ であり、第2の電流は、負荷電流 $I_L$ に比例した電流となり、この電流信号が負荷電流連動信号65である。つまり、負荷電流連動信号65は、NTr5とNTr6とのサイズの比(チャンネル幅及びチャンネル長の比)によって決まる。双方ともサイズが同じであれば、負荷電流連動信号65は、負荷電流 $I_L$ と略同じレベルの電流信号となる。

## 【0043】

10

また、抵抗 $R_s$ の一端は信号入力端子と電気的に接続され、他端は、抵抗 $R_f$ の一端及びNTr2のゲート端子とそれぞれ電気的に接続され、 $R_f$ の他端は、信号出力端子と電気的に接続されている。

上記構成のアンプ回路6は、チャージ・ポンプ回路2で生成されると共に同回路2から供給される負電圧 $V_{EE}$ の負電源と、正電圧 $V_{CC}$ の正電源とによって駆動され、入力信号 $S_{in}$ を、抵抗 $R_s$ 、 $R_f$ によって決まる増幅度でレベル調整電圧 $V_r$ を中心に反転増幅し、グランド電圧(0[V])中心の出力信号 $S_{out}$ として出力する。

## 【0044】

また、出力段回路62は相補型のPTr2とNTr5とから最終出力段が構成され、それぞれVb2及びNTr4からの信号が与えられ制御される。

20

この構成によって、出力信号 $S_{out}$ はグランド電圧の上下の電圧範囲にわたって出力される。

本実施の形態において、上記説明したチャージ・ポンプ回路2及びアンプ回路6のうち少なくともチャージ・ポンプ回路2は、半導体基板上にMOSトランジスタを用いて集積された半導体集積回路として構成される。

## 【0045】

次に、図5に基づき、本実施の形態の負荷駆動システム1のより具体的な動作を説明する。

ここで、図5は、チャージ・ポンプ回路2、クロック発生回路4及びアンプ回路6を流れる信号のタイミングチャートである。

30

図5において、クロック信号CLK1、CLK2、入力信号 $S_{in}$ は電圧波形であり、負電圧 $V_{EE}$ の電源の供給端子に流れ込む負荷電流 $I_L$ は、電流の絶対値の波形である。また、発生電圧 $V_G$ は、負電圧 $V_{EE}$ (定電圧)を基準としたときに発生する電圧である。

負荷駆動システム1の各回路に電源を供給すると、各回路が起動し、図5に示すタイミングで、クロック信号CLK1がSW2及びSW4のゲート端子に供給され、クロック信号CLK2がSW1及びSW3のゲート端子に供給され、入力信号 $S_{in}$ がアンプ回路6の反転入力端子(-)に入力される。

## 【0046】

これにより、入力信号 $S_{in}$ が負電圧の期間において、CLK1がハイレベルの期間(1)は、CLK2がローレベルとなり、チャージ・ポンプ回路2のSW2及びSW4がオン、SW1及びSW3がオフ、PTr4がオンとなる。しかし、入力信号 $S_{in}$ が負電圧であるため、正電圧 $V_{CC}$ の電源から負荷8に電流が供給され、負電圧 $V_{EE}$ の電源からは負荷8に負荷電流 $I_L$ が供給されない。そのため、制御信号Ctrl1の電位が $V_{CC}$ と略同じ電位となり、PTr3がオフとなる。従って、C1には供給電流 $I_{SUP}$ が供給されないため、C1は充電されない。

40

## 【0047】

引き続き、CLK2がハイレベルの期間(2)は、CLK1がローレベルになり、チャージ・ポンプ回路2のSW2及びSW4がオフ、且つSW1及びSW3がオンとなる。しかし、入力信号 $S_{in}$ が負電圧の期間は、1の期間にC1に供給電流 $I_{SUP}$ が供給されないため、C1からC2への電荷の転送が行われない。また、PTr3及びPTr4もオフとなる

50

。

以上より、入力信号  $S_{in}$  が負電圧の期間は、図 5 に示すように、負荷電流  $I_L$ 、供給電流  $I_{SUP}$  及び、電圧  $V_{EE}$  を基準とした発生電圧  $V_G$  はいずれも「0」となる。

#### 【0048】

一方、入力信号  $S_{in}$  が正電圧の期間において、CLK1がハイレベルの期間(1)は、CLK2がローレベルとなり、チャージ・ポンプ回路2のSW2及びSW4がオン、SW1及びSW3がオフとなる。入力信号  $S_{in}$  が正電圧のときは、負電圧  $V_{EE}$  の電源から負荷8に負荷電流  $I_L$  が供給される。このとき、チャージ・ポンプ回路2の供給電流制御回路20のNTr6もオンとなる。

#### 【0049】

従って、負荷電流  $I_L$  に比例した負荷電流運動信号65が、NTr6のドレイン-ソース間を流れる。また、1の期間は、SW4がオンとなり、負荷電流運動信号65がPTr4及びPTr3のゲート端子に供給され、制御信号Ctrl1の電位が負荷電流運動信号65の電流レベルに応じた電位(低電位)となり、PTr3の  $V_{GS}$  が駆動電位となってPTr3がオンとなる。これにより、1の期間において、図5に示すように、負荷電流  $I_L$  の電流レベルに比例した供給電流  $I_{SUP}$  がC1に供給され、C1が充電される。

10

#### 【0050】

引き続き、CLK2がハイレベルの期間(2)は、CLK1がローレベルになり、チャージ・ポンプ回路2のSW2及びSW4がオフ、且つSW1及びSW3がオン、PTr3及びPTr4がオフとなる。これによって、1の期間にC1に蓄積された電荷がC2に転送され、C2が充電される。更に、負電圧  $V_{EE}$  の電源から負荷8に負荷電流  $I_L$  が供給される。

20

#### 【0051】

以上より、入力信号  $S_{in}$  が正電圧の期間は、図5に示すように、供給電流  $I_{SUP}$  は、負荷電流  $I_L$  のレベルに応じた出力値となり、発生電圧  $V_G$  は、供給電流  $I_{SUP}$  のレベル(供給量)に応じた出力値となる。

具体的に、発生電圧  $V_G$  は、1の期間では負荷電流  $I_L$  によって、グランド方向に上昇するが、2の期間でキャパシタC1に蓄えられた電荷が転送されて負電圧方向に下降する。このとき、転送される電荷量は、1の期間にキャパシタC1に蓄積される電荷量(供給電流  $I_{SUP}$ )と正の相関がある。

30

#### 【0052】

また、1と2の期間が交互に繰り返されることで発生電圧  $V_G$  が生じて、負電圧  $V_{EE}$  は上昇と下降がバランスする電圧領域で微小な上下を繰り返す。しかし、負電圧  $V_{EE}$  の微小な上下は、チャージ・ポンプ回路2に適切に大きな容量値のキャパシタC1、C2(この容量値は駆動する負荷の大きさ等に依存して決まり、一般に、0.01 [μF] ~ 100 [μF] で、好ましくは1 [μF] となる)を用いることで吸収することができる。これによって、負電圧  $V_{EE}$  として、正電圧  $V_{CC}$  と絶対値が同じ負の電圧に十分近い電圧を作ることができる。このようにして生成した負電圧  $V_{EE}$  によって、アンプ回路6は、入力信号  $S_{in}$  の正電圧部分の信号を適切に増幅することができると共に、負荷8を十分に駆動できるものとなる。

40

#### 【0053】

以上、本実施の形態のチャージ・ポンプ回路2は、アンプ回路6のNTr5とカレントミラーの関係にあるNTr6によって、負荷電流  $I_L$  に比例したレベルの電流を流す負荷電流運動信号65を生成して、PTr3のソース-ドレイン間に流れる電流(供給電流  $I_{SUP}$ )を制御し、図6に示すように負荷電流  $I_L$  と供給電流  $I_{SUP}$  に正の相関を持たせることで、2の期間にキャパシタC1から転送される電荷量と負荷電流  $I_L$  の間に正の相関を生じさせることができる。

#### 【0054】

ここで、図6は、負荷電流  $I_L$  と供給電流  $I_{SUP}$  との関係を示す図である。

これにより、負電圧  $V_{EE}$  の電源供給端子に流れ込む負荷電流  $I_L$  を効率よく転送させる

50

ことができると共に、アンプ回路6の動作条件に応じた供給電流 $I_{SUP}$ をキャパシタC1に供給することが可能になり、通常使用範囲において発生する電源ノイズを小さくすることができる。

上記第1の実施の形態において、供給電流制御回路20は、発明1、2、6及び8のいずれか1に記載の供給電流量制御手段に対応する。

#### 【0055】

##### 〔第2の実施の形態〕

次に、本発明の第2の実施の形態を図面に基づき説明する。図7～図9は、本発明に係るチャージ・ポンプ回路及び半導体集積回路の第2の実施の形態を示す図である。

上記第1の実施の形態のチャージ・ポンプ回路2は、キャパシタC1を充電して、正電圧 $V_{CC}$ と絶対値が略同じ負電圧 $V_{EE}$ を生成していたが、これに対して、本実施の形態のチャージ・ポンプ回路3は、キャパシタC1の両端の電圧を監視し、所定の電圧に到達したときにC1への電荷の蓄積を終了させることができる点が上記第1の実施の形態のチャージ・ポンプ回路2と異なる。

#### 【0056】

従って、チャージ・ポンプ回路以外の他の構成部は、上記第1の実施の形態と同様となる。以下、上記第1の実施の形態のチャージ・ポンプ回路2と異なる部分を詳細に説明し、同様の部分は同じ符号を付して説明を適宜省略する。

まず、図7に基づき、本実施の形態のチャージ・ポンプ回路3の詳細な構成を説明する。

ここで、図7は、チャージ・ポンプ回路3の詳細な構成を示す回路図である。

本実施の形態のチャージ・ポンプ回路3は、図7に示すように、Pチャンネル型のMOSトランジスタであるPTr3と、キャパシタC1、C2と、スイッチング素子SW1、SW2、SW3と、供給電流制御回路21と、電圧モニター回路22とを含んで構成される。

#### 【0057】

供給電流制御回路21の制御信号出力端子(不図示)は、PTr3のゲート端子に電気的に接続され、PTr3のソース端子は、電源 $V_{CC}$ の入力端子に電気的に接続されている。なお、この入力端子には、電圧 $V_{CC}$ の電源の電源供給端子が電気的に接続されている。

電圧モニター回路22の、正電圧監視用端子はC1の正極側の端子に電気的に接続され、負電圧監視用端子はC1の負極側の端子に電気的に接続され、制御信号出力端子は供給電流制御回路21の制御信号入力端子と電気的に接続されている。

他の接続構成は、上記第1の実施の形態のチャージ・ポンプ回路2と同様となる。

#### 【0058】

次に、図8に基づき、供給電流制御回路21の詳細な構成を説明する。

ここで、図8は、供給電流制御回路21の詳細な構成を示す回路図である。

本実施の形態の供給電流制御回路21は、図8に示すように、Pチャンネル型のMOSトランジスタであるPTr4と、スイッチング素子SW4と、Nチャンネル型のMOSトランジスタであるNTr6と、NOT回路23と、AND回路24とを含んで構成される。

#### 【0059】

SW4のゲート端子は、AND回路24の出力端子に電気的に接続され、AND回路24の第1の入力端子は、NOT回路23の出力端子に電気的に接続され、AND回路24の第2の入力端子は、クロック発振回路4のCLK1の出力端子と電気的に接続されている。

更に、NOT回路23の入力端子(制御信号入力端子)は、電圧モニター回路22の制御信号出力端子と電気的に接続されている。

なお、他の接続構成は、上記第1の実施の形態の供給電流制御回路20と同様となる。

#### 【0060】

次に、図9に基づき、電圧モニター回路22の詳細な構成を説明する。

ここで、図9は、電圧モニター回路22の詳細な構成を示す回路図である。

10

20

30

40

50

電圧モニター回路 2 2 は、図 9 に示すように、減算回路 2 5 と、コンパレータ回路 2 6 とを含んで構成される。

減算回路 2 5 は、上記した正電圧監視用端子、上記した負電圧監視用端子及び減算結果出力端子を備え、減算結果出力端子は、コンパレータ回路 2 6 の比較電圧入力端子と電気的に接続されている。

更に、減算回路 2 5 は、正電圧監視用端子に入力される正側電圧  $V_+$  から、負電圧監視用端子に入力される負側電圧  $V_-$  を減算し、減算結果に応じた電圧  $V_d$  を減算結果出力端子から出力する。

#### 【 0 0 6 1 】

コンパレータ回路 2 6 は、比較電圧入力端子、参照電圧入力端子及び上記した制御信号出力端子を備え、比較電圧入力端子に入力される電圧  $V_d$  と、参照電圧入力端子に入力される参照電圧  $V_{ref}$  ( $V_{ref} < V_{CC}$ ) とを比較し、 $V_d$  が  $V_{ref}$  未満のときは制御信号出力端子からローレベルの電流制御信号  $CCtrl1$  を出力し、 $V_d$  が  $V_{ref}$  以上のときは制御信号出力端子からハイレベルの電流制御信号  $CCtrl1$  を出力する。 10

#### 【 0 0 6 2 】

上記構成によって、チャージ・ポンプ回路 3 は、クロック発生回路 4 からの  $CLK1$  がハイレベルで且つ電流制御信号  $CCtrl1$  がローレベルのときに、 $SW2$  及び  $SW4$  がオンになり、 $CLK1$  がローレベル又は  $CCtrl1$  がハイレベルのときにオフとなる。

つまり、 $C1$  の両端間電圧  $V_d$  が参照電圧  $V_{ref}$  未満のときは、電流制御信号  $CCtrl1$  がローレベルになり、 $AND$  回路 2 4 の第 1 の入力端子には  $NOT$  回路 2 3 でハイレベルへと反転された  $CCtrl1$  が入力され、 $AND$  回路 2 4 の出力は、 $CLK1$  がハイレベルのときにハイレベルとなる。 20

#### 【 0 0 6 3 】

一方、 $C1$  の両端間電圧  $V_d$  が参照電圧  $V_{ref}$  以上のときは、電流制御信号  $CCtrl1$  がハイレベルとなり、 $AND$  回路 2 4 の第 1 の入力端子には  $NOT$  回路 2 3 でローレベルへと反転された  $CCtrl1$  が入力され、 $AND$  回路 2 4 の出力は、 $CLK1$  がハイレベル又はローレベルのいずれであってもローレベルとなる。

いま、 $CLK1$  がハイレベルで且つ  $CCtrl1$  がローレベルになって  $SW2$  及び  $SW4$  がオンになり、 $CLK2$  がローレベルになって  $SW1$  及び  $SW3$  がオフになると、 $PTr3$  がオンとなる。これによって、電源  $V_{CC}$  からの負荷電流  $I_L$  と正の相関にある供給電流  $I_{SUP}$  が  $C1$  に供給され  $C1$  の充電が開始される。 30

#### 【 0 0 6 4 】

一方、 $C1$  が充電中において ( $CLK1$  がハイレベルである 1 の期間において)  $CCtrl1$  がハイレベルになると、 $SW4$  がオフとなって、 $PTr3$  及び  $PTr4$  もオフとなり、 $C1$  の充電は強制的に終了される。これによって、 $C1$  の両端間電圧を略  $V_{ref}$  とすることができる。

引き続き、 $CLK1$  がローレベルになって  $SW2$  及び  $SW4$  がオフになり、 $CLK2$  がハイレベルになって  $SW1$  及び  $SW3$  がオンになると、 $GND - SW1 - C1 - SW3 - C2 - GND$  のループが構成され、 $C1$  に蓄積された電荷が、図 7 に示す極性で  $C2$  へと転送される。これにより、供給端子の  $V_{EE}$  の電圧レベルを  $V_{ref}$  のレベルとすることができます。 40

なお、その他の動作については、上記第 1 の実施の形態のチャージ・ポンプ回路 2 と同様となる。

#### 【 0 0 6 5 】

以上、本実施の形態の負荷駆動システム 1 は、供給電流制御回路 2 1 によって、アンプ回路 6 を流れる負荷電流  $I_L$  と正の相関を持った供給電流  $I_{SUP}$  によって、チャージ・ポンプ回路 3 の  $C1$  を充電することができる。

更に、電圧モニター回路 2 2 によって、 $C1$  の両端の電圧を監視し、両端間の電圧が  $V_{ref}$  以上になったときに、供給電流制御回路 2 1 によって、 $SW4$  をオフにし  $C1$  への充電を  $V_{CC}$  よりも小さい  $V_{ref}$  で終了させることができる。

つまり、 $V_{ref}$  を所望の電圧とすることで、 $V_{EE}$  を  $V_{CC}$  よりも低い所望の電圧にするこ

10

20

30

40

50

とができる。

【0066】

従来のチャージ・ポンプ回路を用いてこのような構成にした場合、キャパシタC1の充電が不十分の状態で電荷の蓄積を終了させるため、供給電流が非常に大きくなってしまう。一方、本実施の形態のチャージ・ポンプ回路3では、アンプ回路6の動作条件に応じた供給電流 $I_{SUP}$ をキャパシタC1に供給することが可能になり、Vrefの段階でC1の充電を終了する使い方をしても、そのときに発生する電源ノイズを小さくすることができる。

【0067】

上記第2の実施の形態において、供給電流制御回路21は、発明1、2、6及び8のいずれか1に記載の供給電流量制御手段に対応し、電圧モニター回路22は、発明4に記載の電圧レベル比較手段に対応し、供給電流制御回路21における電圧モニター回路22からの電流制御信号CCtrl1に基づきSW4を切り替える処理は、発明4に記載の切替制御手段に対応する。

【0068】

〔第3の実施の形態〕

次に、本発明の第3の実施の形態を図面に基づき説明する。図10は、本発明に係るチャージ・ポンプ回路及び半導体集積回路の第3の実施の形態を示す図である。

上記第1の実施の形態の負荷駆動システム1は、チャージ・ポンプ回路2の被駆動回路として、1つのアンプ回路6を駆動する構成にしていたが、本実施の形態の負荷駆動システム10は、チャージ・ポンプ回路2の被駆動回路として、2つのアンプ回路6A及び6Bを駆動する点が上記第1の実施の形態と異なる。

【0069】

更に、本実施の形態の負荷駆動システム10は、キャパシタC1の充電を行うときに、アンプ回路6Aに流れる負荷電流 $I_{LA}$ と正の相関を有する負荷電流連動信号65Aと、アンプ回路6Bに流れる負荷電流 $I_{LB}$ と正の相関を有する負荷電流連動信号65Bとの和からなる負荷電流連動信号65Cと正の相関を有する（比例する）供給電流 $I_{SUP}$ によって、C1を充電する点が上記第1の実施の形態と異なる。

従って、アンプ回路6が、アンプ回路6A及び6Bになる点と、負荷電流連動信号65A及び65Bの和をSW4を介してPTr3及びPTr4に供給する点以外の他の構成部は、上記第1の実施の形態と同様となる。以下、上記第1の実施の形態と異なる部分を詳細に説明し、同様の部分は同じ符号を付して説明を適宜省略する。

【0070】

図10に基づき、本実施の形態の負荷駆動システム10の構成を説明する。

ここで、図10は、負荷駆動システム10の構成を示すブロック図である。

負荷駆動システム10は、図10に示すように、チャージ・ポンプ回路2と、クロック発生回路4と、アンプ回路6A及び6Bと、負荷8A及び8Bとを含んで構成される。

アンプ回路6Aからは、上記第1の実施の形態のNTr6と同様の役割を果たすNTr6Aを介して、アンプ回路6Aを流れる負荷電流 $I_{LA}$ と正の相関を有する負荷電流連動信号65Aを伝送する導電性のラインL1がチャージ・ポンプ回路2に向けて伸びている。

【0071】

また、アンプ回路6Bからは、上記第1の実施の形態のNTr6と同様の役割を果たす、NTr6Bを介して、アンプ回路6Bを流れる負荷電流 $I_{LB}$ と正の相関を有する負荷電流連動信号65Bを伝送する導電性のラインL2がチャージ・ポンプ回路2に向けて伸びている。

従って、本実施の形態では、NTr6Aは、アンプ回路6A側に設け、NTr6Bはアンプ回路6B側に設けている。なお、NTr6A及び6Bを、チャージ・ポンプ回路2側に設ける構成としてもよい。

【0072】

そして、ラインL1とL2とはチャージ・ポンプ回路2の手前で合流してラインL3となり、ラインL3がチャージ・ポンプ回路2のSW4と電気的に接続される。

10

20

30

40

50

これにより、ライン L 1 を流れる負荷電流連動信号 65 A と、ライン L 2 を流れる負荷電流連動信号 65 B とが合流してライン L 3 には、負荷電流連動信号 65 A と負荷電流連動信号 65 B とを合算した信号である負荷電流連動信号 65 C が流れる。

【0073】

更に、チャージ・ポンプ回路 2 からは、電圧  $V_{EE}$  の電源を供給する導電性のライン L 4 がアンプ回路 6 A 及び 6 B に向けて伸びており、ライン L 4 は、途中でアンプ回路 6 A に向けて伸びるライン L 5 とアンプ回路 6 B に向けて伸びるライン L 6 とに分岐して、それぞれ、アンプ回路 6 A 及び 6 B の負電源供給端子に電気的に接続される。

従って、ライン L 4 を流れる負荷電流  $I_L$  は、ライン L 5 を流れる負荷電流  $I_{LA}$  と、ライン L 6 を流れる負荷電流  $I_{LB}$  とを合算した電流 ( $I_L = I_{LA} + I_{LB}$ ) となる。 10

【0074】

なお、説明の便宜上、ラインという言葉を用いて説明したが、信号を伝送可能な導電性のパターンであればラインに限らない。また、同じ状態を作り出せれば、加算器を用いるなどどのような構成でもよい。

更に、負荷 8 A は、アンプ回路 6 A によって駆動される負荷であり、負荷 8 B は、アンプ回路 6 B によって駆動される負荷である。

また、アンプ回路 6 A 及び 6 B は、入力信号 ( $S_{inA}$ 、 $S_{inB}$ ) 及び駆動する負荷 (8 A、8 B) が異なる (同じ内容でも良い) だけで、上記第 1 の実施の形態のアンプ回路 6 と同様の構成及び動作となる。

【0075】

また、説明の便宜上、図 10 に示す例では、2つのアンプ回路 6 A 及び 6 B を駆動する構成としたが、これに限らず、3つ以上のアンプ回路を駆動する構成としてもよい。また、アンプ回路に限らず、他の被駆動回路を複数駆動する構成としてもよい。また、本実施の形態の構成は、上記第 2 の実施の形態にも適用することが可能である。 20

上記構成によって、チャージ・ポンプ回路 2 は、1の期間において、負荷電流連動信号 65 C に比例する供給電流  $I_{SUP}$  によって C 1 を充電することができる。

【0076】

以上より、本実施の形態の負荷駆動システム 10 は、チャージ・ポンプ回路 2 の被駆動回路である、アンプ回路 6 A 及び 6 B を流れる負荷電流  $I_{LA}$  及び  $I_{LB}$  の和の電流と正の相関のある供給電流  $I_{SUP}$  によって C 1 を充電することができる。 30

これにより、例えば、ステレオヘッドホンアンプなどの複数のアンプ回路を含むデバイスを効率よく駆動することができる。

上記第 3 の実施の形態において、供給電流制御回路 20 は、発明 1、2、5、6 及び 8 のいずれか 1 に記載の供給電流量制御手段に対応する。

【0077】

〔第 4 の実施の形態〕

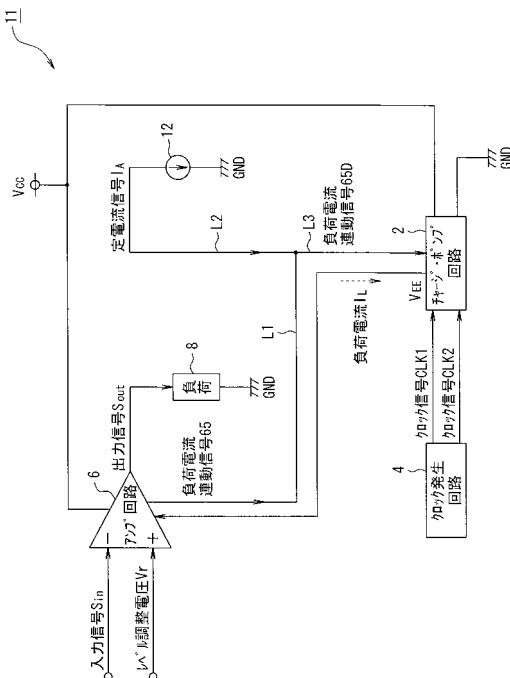

次に、本発明の第 4 の実施の形態を図面に基づき説明する。図 11 ~ 図 12 は、本発明に係るチャージ・ポンプ回路及び半導体集積回路の第 4 の実施の形態を示す図である。

上記第 1 の実施の形態の負荷駆動システム 1 は、チャージ・ポンプ回路 2 において、アンプ回路 6 を流れる負荷電流  $I_L$  と正の相関を持った供給電流  $I_{SUP}$  によって、C 1 を充電する構成としたが、本実施の形態の負荷駆動システム 11 は、負荷電流  $I_L$  と正の相関を持った負荷電流連動信号 65 に、予め設定したレベルの定電流を加算して負荷電流連動信号 65 D を生成し、この信号と比例する供給電流  $I_{SUP}$  によって、C 1 を充電する点が上記第 1 の実施の形態と異なる。 40

従って、負荷電流連動信号 65 に、予め設定したレベルの定電流を加算する定電流源を追加した以外は、上記第 1 の実施の形態と同様となる。以下、上記第 1 の実施の形態と異なる部分を詳細に説明し、同様の部分は同じ符号を付して説明を適宜省略する。

【0078】

図 11 に基づき、本実施の形態の負荷駆動システム 11 の構成を説明する。

ここで、図 11 は、負荷駆動システム 11 の構成を示すブロック図である。 50

負荷駆動システム 11 は、図 11 に示すように、チャージ・ポンプ回路 2 と、クロック発生回路 4 と、アンプ回路 6 と、負荷 8 と、定電流源 12 とを含んで構成される。

アンプ回路 6 からは、NTr 6 を介して、アンプ回路 6 を流れる負荷電流  $I_L$  と正の相関を有する負荷電流連動信号 65 を伝送する導電性のライン L1 がチャージ・ポンプ回路 2 に向けて伸びている。

#### 【0079】

従って、本実施の形態では、NTr 6 は、アンプ回路 6 側に設けている。なお、NTr 6 を、チャージ・ポンプ回路 2 側に設ける構成としてもよい。

定電流源 12 は、予め定められた電流レベルの定電流信号  $I_A$  を出力する機能を有している。定電流源 12 からは、定電流信号  $I_A$  を伝送する導電性のライン L2 がチャージ・ポンプ回路 2 に向けて伸びている。 10

ライン L1 とライン L2 とは、チャージ・ポンプ回路 2 の手前で合流してライン L3 となり、ライン L3 がチャージ・ポンプ回路 2 の SW4 と電気的に接続される。

これにより、ライン L1 を流れる負荷電流連動信号 65 と、ライン L2 を流れる定電流信号  $I_A$  とが合流してライン L3 には、負荷電流連動信号 65 と定電流信号  $I_A$  とを合算した信号である負荷電流連動信号 65D が流れる。

#### 【0080】

なお、説明の便宜上、ラインという言葉を用いて説明したが、信号を伝送可能な導電性のパターンであればラインに限らない。同じ状態を作り出せれば、例えば、加算器を設けるなどどのような構成でもよい。 20

上記構成によって、チャージ・ポンプ回路 2 は、1 の期間において、負荷電流連動信号 65D に比例する供給電流  $I_{SUP}$  によって C1 を充電することができる。

#### 【0081】

具体的に、上記第 1 の実施の形態の供給電流を  $I_{SUP1}$  とし、本実施の形態の供給電流を  $I_{SUP2}$  とし、定電流信号  $I_A$  の上乗せ分を  $I$  とすると、図 12 に示すように、供給電流  $I_{SUP2}$  は、供給電流  $I_{SUP1}$  と比較して、 $I_{SUP1}$  に常に  $I$  分が加算された状態となる。従って、 $I$  を任意の値に設定することで、負荷電流連動信号 65 に縛られずに、それよりも  $I$  だけ高い電流レベルの信号と正の相関を有する供給電流  $I_{SUP2}$  によって、C1 を充電することができる。 30

#### 【0082】

ここで、図 12 は、チャージ・ポンプ回路 2 を駆動させる上で最低限必要な供給電流  $I_{SUP1}$  と負荷電流  $I_L$  の関係と、供給電流  $I_{SUP1}$  をあらかじめ設定された値大きくした供給電流  $I_{SUP2}$  と負荷電流  $I_L$  との関係とを示す図である。

以上より、本実施の形態の負荷駆動システム 11 は、チャージ・ポンプ回路 2 の被駆動回路であるアンプ回路 6 を流れる負荷電流  $I_L$  と正の相関のある負荷電流連動信号 65 に定電流信号  $I_A$  を加算してなる負荷電流連動信号 65D に比例する供給電流  $I_{SUP}$  によって C1 を充電することができる。 40

#### 【0083】

これによって、定電流を加算して、供給電流  $I_{SUP2}$  を少し大きめに設定することで、負荷電流  $I_L$  が 0 のときや供給電流量がばらついた時でもチャージ・ポンプ回路 2 を余裕をもって駆動させることができる。

上記第 4 の実施の形態において、供給電流制御回路 20 は、発明 1、2、3、6 及び 8 のいずれか 1 に記載の供給電流量制御手段に対応する。

なお、上記第 1 ~ 第 4 の実施の形態においては、チャージ・ポンプ回路 2 において、キャパシタ C1 及び C2 とによって正電圧  $V_{CC}$  の極性を反転した電圧と略同じレベルの負電圧  $V_{EE}$  の負電源を生成する構成としたが、この構成に限らず、キャパシタをもっと多段接続して、キャパシタの数に応じた倍圧の負電圧の負電源を生成する構成としてもよい。

#### 【0084】

また、上記第 1 の実施の形態においては、チャージ・ポンプ回路 2 において正電圧  $V_{CC}$  の極性を反転した電圧と略同じレベルの負電圧  $V_{EE}$  の負電源を生成するときに、該負電源

10

20

30

40

50

を供給するアンプ回路 6 に流れる負荷電流  $I_L$  と正の相関を有した負荷電流連動信号を生成し、これにより、負荷電流  $I_L$  と正の相関を有した供給電流  $I_{SUP}$  で、キャパシタ C 1 を供給する構成について説明したが、この構成に限らない。

【 0 0 8 5 】

例えば、所望の正電源を生成するチャージ・ポンプ回路を用いた場合でも同様に負荷電流連動信号を生成することが可能である。

また、上記第 1 ~ 第 4 の実施の形態においては、負荷電流連動信号 6 5 を、出力段回路 6 2 の N T r 5 と供給電流制御回路 2 0 の N T r 6 とから生成したが、これに限らず、入力段差動回路 6 0 の N T r 3 を用いて生成することもできる。

【 0 0 8 6 】

また、上記第 1 ~ 第 4 の実施の形態においては、被駆動回路として、アンプ回路を適用したが、これに限らず、アウトプットバッファやマイク素子のバイアス電流供給回路など他の回路にも適用させることができる。

なお、上記第 1 ~ 第 4 の実施の形態において、チャージ・ポンプ回路 2 、 3 を構成する P T r 3 及び P T r 4 として P チャンネル型の M O S トランジスタを用いて構成したが、これに限らず、N チャンネル型の M O S トランジスタを用いて構成してもよい。

【 0 0 8 7 】

また、上記第 1 ~ 第 4 の実施の形態においては、半導体集積回路を構成するために、M O S トランジスタを用いて各回路を構成しているが、この構成に限らず、バイポーラトランジスタなど他のトランジスタで構成してもよい。

また、上記第 1 ~ 第 4 の実施の形態は、本発明の好適な具体例であり、技術的に好ましい種々の限定が付されているが、本発明の範囲は、上記の説明において特に本発明を限定する旨の記載がない限り、これらの形態に限られるものではない。また、上記の説明で用いる図面は、図示の便宜上、部材ないし部分の縦横の縮尺は実際のものとは異なる模式図である。

また、本発明は上記第 1 ~ 第 4 の実施の形態に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

【 符号の説明 】

【 0 0 8 8 】

1 , 1 0 , 1 1 ... 負荷駆動システム、 2 , 3 ... チャージ・ポンプ回路、 4 ... クロック発生回路、 6 , 6 A , 6 B ... アンプ回路、 8 , 8 A , 8 B ... 負荷、 1 2 ... 定電流源、 2 0 , 2 1 ... 供給電流制御回路、 2 2 ... 電圧モニター回路、 2 3 ... N O T 回路、 2 4 ... A N D 回路、 2 5 ... 減算回路、 2 6 ... コンパレータ回路、 P T r 1 ~ P T r 4 ... P チャンネル型の M O S トランジスタ、 N T r 1 ~ N T r 6 ... N チャンネル型の M O S トランジスタ、 S W 1 ~ S W 4 ... スイッチング素子、 C 1 , C 2 , C 1 0 ... キャパシタ、 R <sub>s</sub> , R <sub>f</sub> , R 1 0 ... 抵抗

10

20

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2005-033865(JP,A)

特開2005-020922(JP,A)

特開2005-151777(JP,A)

特開2008-125220(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/07

H01L 21/822

H01L 27/04