(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5615211号

(P5615211)

(45) 発行日 平成26年10月29日(2014.10.29)

(24) 登録日 平成26年9月19日(2014.9.19)

(51) Int.Cl.

F 1

G06F 3/041 (2006.01)

G06F 3/044 (2006.01)G06F 3/041 522

G06F 3/044 129

請求項の数 7 (全 13 頁)

|           |                               |           |                                            |

|-----------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号 | 特願2011-52554 (P2011-52554)    | (73) 特許権者 | 000010098<br>アルプス電気株式会社<br>東京都大田区雪谷大塚町1番7号 |

| (22) 出願日  | 平成23年3月10日(2011.3.10)         | (74) 代理人  | 100085453<br>弁理士 野▲崎▼ 照夫                   |

| (65) 公開番号 | 特開2012-190217 (P2012-190217A) | (74) 代理人  | 100121049<br>弁理士 三輪 正義                     |

| (43) 公開日  | 平成24年10月4日(2012.10.4)         | (72) 発明者  | 重高 寛<br>東京都大田区雪谷大塚町1番7号 アルプス電気株式会社内        |

| 審査請求日     | 平成25年12月11日(2013.12.11)       | 審査官       | 中田 剛史                                      |

最終頁に続く

(54) 【発明の名称】 静電容量式入力装置

## (57) 【特許請求の範囲】

## 【請求項 1】

フィルム基材と、前記フィルム基材のセンサ部側にパターン形成された駆動電極と、前記駆動電極とセンサ側絶縁層を介して対向し前記駆動電極との間の静電容量を検出するパターン形成された検出電極と、を有する静電容量式入力装置において、

前記フィルム基材の前記センサ部とは反対側の回路部側には、回路側絶縁層を介して対向する第1導体層と第2導体層とがパターン形成されてなるリファレンスキャパシタ部が設けられ、前記第1導体層と前記第2導体層間に前記駆動電極と前記検出電極間の静電容量に対する基準静電容量が形成されていることを特徴とする静電容量式入力装置。

## 【請求項 2】

前記第1導体層は、前記フィルム基材を貫通して前記検出電極と導通している請求項1記載の静電容量式入力装置。

## 【請求項 3】

前記第1導体層と前記第2導体層は、前記基準静電容量に応じて、所定の長さ寸法にて直線状に延出形成されている請求項1又は2に記載の静電容量式入力装置。

## 【請求項 4】

前記回路部には、前記フィルム基材から離れる方向に向けてグランド層、回路側絶縁層及び回路配線層が順に積層されており、前記第1導体層は前記グランド層と同じ工程で形成され、前記第2導体層は前記回路配線層と同じ工程で形成される請求項1ないし3のいずれか1項に記載の静電容量式入力装置。

**【請求項 5】**

前記回路側絶縁層は、前記センサ側絶縁層と同じ層構成で形成される請求項 1ないし 4 のいずれか 1 項に記載の静電容量式入力装置。

**【請求項 6】**

前記センサ部に、互いに絶縁されて直交する向きに形成された第 1 の駆動電極および第 2 の駆動電極と、前記第 1 の駆動電極および前記第 2 の駆動電極に距離を開けて対向する前記検出電極とが設けられており、前記リファレンスキャパシタ部は、前記第 1 の駆動電極と前記検出電極間の静電容量に対する基準静電容量を備える第 1 リファレンスキャパシタ部と、前記第 2 の駆動電極と前記検出電極間の静電容量に対する基準静電容量を備える第 2 リファレンスキャパシタ部とを有する請求項 1ないし 5 のいずれか 1 項に記載の静電容量式入力装置。 10

**【請求項 7】**

前記リファレンスキャパシタ部には、前記基準静電容量に対する微調整用コンデンサチップが設けられている請求項 1ないし 6 のいずれか 1 項に記載の静電容量式入力装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、駆動電極と検出電極間の静電容量の変化によって指等の接近を検出する静電容量式入力装置に係り、特に回路部側にリファレンスキャパシタ部を有する構成に関する。 20

**【背景技術】****【0002】**

静電容量式入力装置は、以下の特許文献に記載されているように、基材及び電極パターンを備えるセンサ部と、センサ部の電極パターンと導通接続される回路部とを有して構成される。

**【0003】**

特許文献 1 及び特許文献 2 ではセンサ部と回路部とを別体で設けているが特許文献 3 のようにセンサ部と回路部とを共通のフィルム基材上に設けた構成も知られている。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献 1】特開平 9 - 54650 号公報

【特許文献 2】特開 2003 - 271311 号公報

【特許文献 3】U.S. R E 40 , 867 E

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

従来、センサ部を構成する電極パターンをフィルム基材に形成した構成では、環境変化に伴うフィルム基材や絶縁層の誘電率の変化により、電極パターン間の静電容量が環境によりばらついてしまい、その結果、位置検出精度が低下する問題があった。 40

**【0006】**

そこで本発明は上記従来の課題を解決するものであり、特に位置検出精度の向上とともに薄型化、部品点数の削減を可能とした静電容量式入力装置を提供することを目的としている。

**【課題を解決するための手段】****【0007】**

本発明は、フィルム基材と、前記フィルム基材のセンサ部側にパターン形成された駆動電極と、前記駆動電極とセンサ側絶縁層を介して対向し前記駆動電極との間の静電容量を検出するパターン形成された検出電極と、を有する静電容量式入力装置において、

前記フィルム基材の前記センサ部とは反対側の回路部側には、回路側絶縁層を介して対 50

向する第1導体層と第2導体層とがパターン形成されてなるリファレンスキャパシタ部が設けられ、前記第1導体層と前記第2導体層間に前記駆動電極と前記検出電極間の静電容量に対する基準静電容量が形成されていることを特徴とするものである。

#### 【0008】

このようにリファレンスキャパシタ部を構成する第1導体層と第2導体層を夫々パターン形成することで、リファレンスキャパシタ部とセンサ部の双方に、フィルム基材や絶縁層に対する誘電率依存性を持たせることができる。すなわちセンサ部の電極間の静電容量は、環境変化に伴うフィルム基材や絶縁層の誘電率変化により変動するが、同じように、リファレンスキャパシタ部の基準静電容量も変動させることができるために、電極間の静電容量の温湿度ドリフトによっても検出誤差を小さくでき優れた位置検出精度を得ることが可能になる。10

#### 【0009】

またリファレンスキャパシタ部をコンデンサチップとする構成では、リファレンスキャパシタ部にセンサ部と同様の、フィルム基材や絶縁層に対する誘電率依存性を持たせることができないため、位置検出精度の向上を適切に図ることができない。

#### 【0010】

本発明では、リファレンスキャパシタ部をパターン形成することで、コンデンサチップを設ける構成に比べて、位置検出精度を適切に向上させることができるとともに部品点数の削減及び薄型化を促進することが可能になる。

#### 【0011】

本発明では、前記第1導体層は、前記フィルム基材を貫通して前記検出電極と導通していることが、検出回路を簡素化でき、また簡単な構造でリファレンスキャパシタ部を形成できて好ましい。20

#### 【0012】

また本発明では、前記第1導体層と前記第2導体層は、前記基準静電容量に応じて、所定の長さ寸法にて直線状に延出形成されていることが好ましい。

#### 【0013】

また本発明では、前記回路部には、前記フィルム基材から離れる方向に向けてグランド層、回路側絶縁層及び回路配線層が順に積層されており、前記第1導体層は前記グランド層と同じ工程で形成され、前記第2導体層は前記回路配線層と同じ工程で形成されることが好ましい。これによりリファレンスキャパシタ部の形成を容易化でき製造コストの低減を図ることが出来る。30

#### 【0014】

また本発明では、前記回路側絶縁層は、前記センサ側絶縁層と同じ層構成で形成されることが好ましい。センサ部とリファレンスキャパシタ部とで、絶縁層に対する誘電率依存性を同じにでき、より効果的に位置検出精度の向上を図ることが可能になる。

#### 【0015】

また本発明では、前記センサ部に、互いに絶縁されて直交する向きに形成された第1の駆動電極および第2の駆動電極と、前記第1の駆動電極および前記第2の駆動電極に距離を開けて対向する前記検出電極とが設けられており、前記リファレンスキャパシタ部は、前記第1の駆動電極と前記検出電極間の静電容量に対する基準静電容量を備える第1リファレンスキャパシタ部と、前記第2の駆動電極と前記検出電極間の静電容量に対する基準静電容量を備える第2リファレンスキャパシタ部とを有することが好ましい。40

#### 【0016】

また本発明では、前記リファレンスキャパシタ部には、前記基準静電容量に対する微調整用コンデンサチップが設けられていてよい。

#### 【発明の効果】

#### 【0017】

本発明では、リファレンスキャパシタ部をパターン形成することで、リファレンスキャパシタ部とセンサ部の双方に、フィルム基材や絶縁層に対する誘電率依存性を持たせるこ50

とができ、電極間の静電容量の温湿度ドリフトによっても優れた位置検出精度を得ることが可能になる。またリファレンスキャパシタ部をチップコンデンサで構成する形態に比べて、位置検出精度の向上とともに部品点数の削減及び薄型化を促進できる。

**【図面の簡単な説明】**

**【0018】**

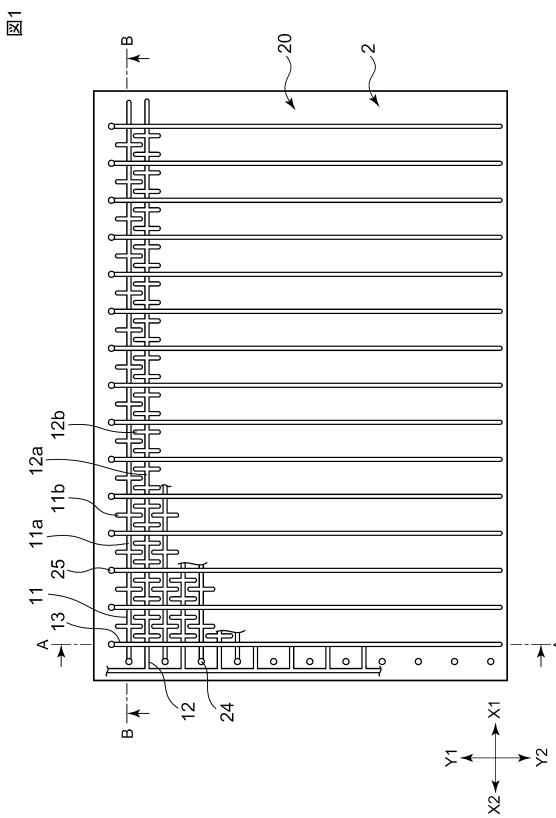

【図1】本実施形態における静電容量式入力装置の平面図、

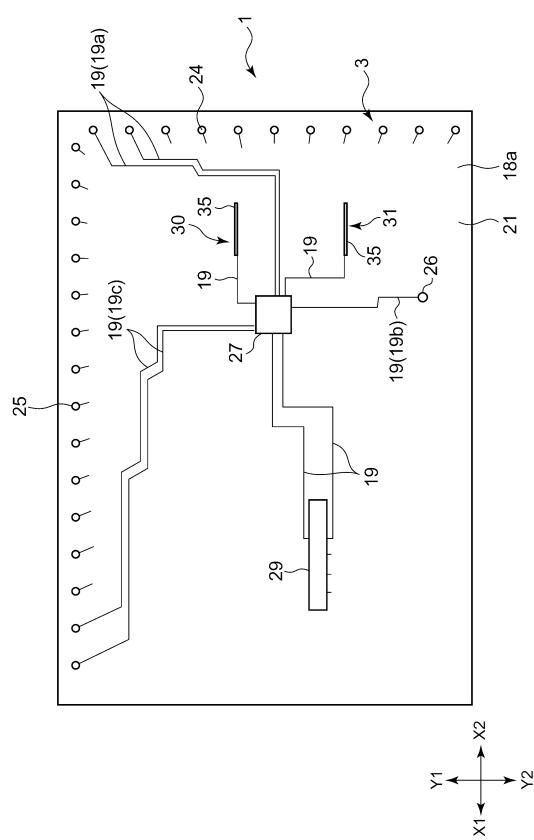

【図2】本実施形態における静電容量式入力装置の裏面図、

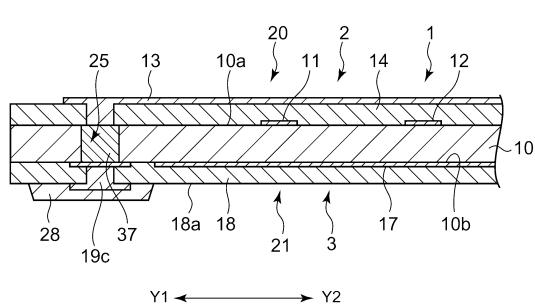

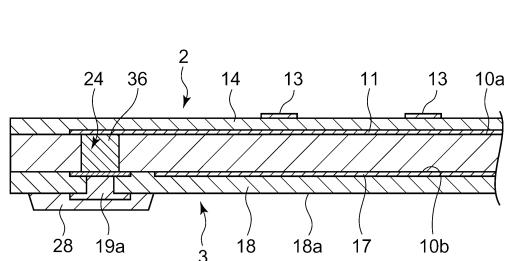

【図3】図1に示すA-A線に沿って切断し矢印方向から見た静電容量式入力装置の部分拡大縦断面図、

【図4】図1に示すB-B線に沿って切断し矢印方向から見た静電容量式入力装置の部分拡大縦断面図、

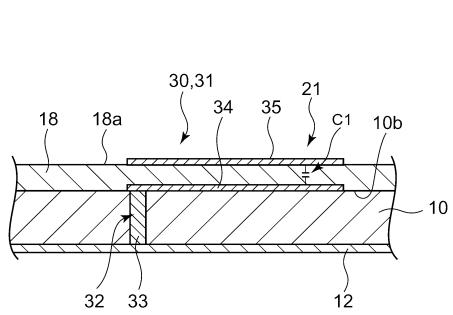

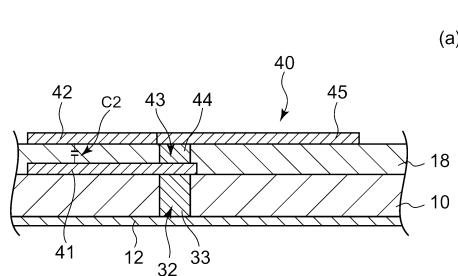

【図5】第1実施形態におけるリファレンスキャパシタ部の部分拡大縦断面図、

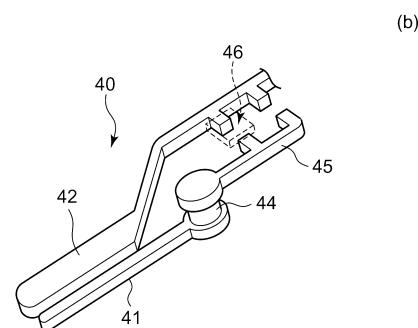

【図6】(a)は、第2実施形態におけるリファレンスキャパシタ部の部分拡大縦断面図、(b)は、第2実施形態におけるリファレンスキャパシタ部の斜視図、

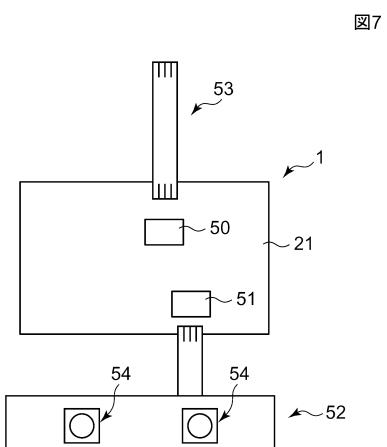

【図7】本実施形態における静電容量式入力装置を用いたポインティングデバイスの模式図、

【図8】本実施形態における静電容量式入力装置を用いたポインティングデバイスの模式図、

【図9】本実施形態における静電容量式入力装置を用いたポインティングデバイスの模式図、

【図10】本実施形態における静電容量式入力装置を用いたポインティングデバイスの模式図。

10

20

**【発明を実施するための形態】**

**【0019】**

図1は、本実施形態における静電容量式入力装置1の平面図、図2は静電容量式入力装置1の裏面図、図3は、図1に示すA-A線に沿って切断し矢印方向から見た部分拡大縦断面図、図4は図1に示すB-B線に沿って切断し矢印方向から見た部分拡大縦断面図、図5は、第1実施形態におけるリファレンスキャパシタ部の部分拡大縦断面図、図6(a)は、第2実施形態におけるリファレンスキャパシタ部の部分拡大縦断面図、図6(b)は、第2実施形態におけるリファレンスキャパシタ部の斜視図、である。ただし図5、図6では、静電容量式入力装置1の裏面側(回路部側)を上側に向けて図示した。

30

**【0020】**

図3、図4の断面図に示すように、静電容量式入力装置1は、表側2と裏側3を有している。図1は静電容量式入力装置1を表側2から見た状態を示しており、図2は静電容量式入力装置1を裏側3から見た状態を示している。

**【0021】**

図1に示すように、表側2にはそのほぼ全域にX駆動電極(第1の駆動電極)13およびY駆動電極(第2の駆動電極)11と検出電極12が設けられている。なお図1には一つのX駆動電極に対して符号13を付した。また図1では、Y駆動電極及び検出電極を一部だけ図示し、また一つのY駆動電極及び一つの検出電極に対して符号11、12を付した。

40

各電極11、12、13は印刷にてパターン形成されている。

**【0022】**

図3、図4に示すように、静電容量式入力装置1は樹脂フィルム、樹脂シートからなる可撓性のフィルム基材10を有する。フィルム基材10を構成する合成樹脂は、例えばPET(ポリエチレン・テレフタレート)である。

**【0023】**

フィルム基材10の表側2はセンサ部20を構成し、フィルム基材10の表面10aに、直接にまたは絶縁層を介して、図1に示す複数のY駆動電極11と複数の検出電極12とが形成されている。

50

**【0024】**

またY駆動電極11と検出電極12の表面にセンサ側絶縁層14が設けられ、X駆動電極13はセンサ側絶縁層14上に形成されている。このX駆動電極13の表面は図示しない表面絶縁層で覆われている。

**【0025】**

図1に示すように、それぞれのY駆動電極11はX1-X2方向へ直線的に延びる電極本体部11aを有している。複数のY駆動電極11は、電極本体部11aがY1-Y2方向に一定の間隔を空けて平行に延びるように形成されている。検出電極12は、X1-X2方向へ直線的に延びる電極本体部12aを有しており、複数の検出電極12は、電極本体部12aがY1-Y2方向へ一定の間隔を空けて平行に延びるように形成されている。

Y駆動電極11の電極本体部11aと検出電極12の電極本体部12aは、Y1-Y2方向に交互に配列しており、電極本体部11aと電極本体部12aは互いに平行である。

10

**【0026】**

図1に示すように、X駆動電極13は、Y1-Y2方向に直線的に延びており、X1-X2方向に一定の間隔を空けて互いに平行に形成されている。

**【0027】**

図1に示すように、Y駆動電極11は、枝電極部11bを有している。枝電極部11bは、X1-X2方向に間隔を空けて複数本形成されており、それぞれが電極本体部11aと導通して電極本体部11aからY1方向とY2方向へ向けて短く突出している。検出電極12も枝電極部12bを有している。枝電極部12bは、X1-X2方向へ間隔を空けて複数本設けられている。それぞれの枝電極部12bは、電極本体部12aと導通し、電極本体部12aからY1方向とY2方向へ向けて短く突出している。

20

**【0028】**

図1に示すように、X駆動電極13は、Y駆動電極11の電極本体部11aと検出電極12の電極本体部12aの上方を交差するように通過している。また、検出電極12に枝電極部12bが設けられていることで、検出電極12の電極本体部11aとX駆動電極13との交差部分において、検出電極12とX駆動電極13との結合容量を増大でき、しかも操作面の全域において、検出電極12とX駆動電極13との結合容量の大きなばらつきが発生しないように調整されている。

30

**【0029】**

図1に示す実施の形態では、X駆動電極13に枝電極部が設けられていないが、X駆動電極13に枝電極部が設けられていてもよい。

**【0030】**

Y駆動電極11の電極本体部11aと検出電極12の電極本体部12aが互いに平行に対向しているとともに、Y駆動電極11の枝電極部11bと検出電極12の一対の枝電極部12bとが、X1-X2方向にて対向するように配置されている。前記枝電極部11bと枝電極部12bが設けられていることで、Y駆動電極11と検出電極12との結合容量を増大でき、しかも操作面の全域において、Y駆動電極11と検出電極12との結合容量の大きなばらつきが発生しないように調整されている。

40

**【0031】**

図2に示すように、フィルム基材10の裏側3は回路部21を構成し、フィルム基材10の裏面10bには、図3、図4に示すように、導電性材料で形成されたグランド層(シールド層)17が形成されている。グランド層17は、操作面のほぼ全域を裏側から覆うように形成されている。

**【0032】**

図3、図4に示すように、グランド層17の裏面は回路側絶縁層18で覆われている。この回路側絶縁層18の裏面18aに図2、図3、図4に示すように、回路配線層19が形成されている。なお図2には一部の回路配線層19のみを図示した。

**【0033】**

図2に示すように、回路配線層19は、Y配線層19aと検出配線層19bおよびX配

50

線層 19c を有している。

**【0034】**

図1に示すように、操作面の縁部に沿って、スルーホール24, 25が形成されている。なお図1, 図2には、各一つのスルーホールにのみ符号24, 25を付した。図3, 図4に示すように、スルーホール24, 25は、フィルム基材10を貫通して形成されており、内部に導電層36, 37が充填されている。そして、それぞれのスルーホール24内の導電層36を介して複数本のY駆動電極11とY配線層19aとが個別に導通している。同様に、それぞれのスルーホール25内の導電層37を介して複数本のX駆動電極13とX配線層19cとが個別に導通している。

**【0035】**

また検出電極12に対するスルーホール26は図2に示すように一つであり、このスルーホール26もフィルム基材10を貫通して形成されており、内部に導電層が充填されている。そして、検出電極12は一本に纏められて、スルーホール26を介して検出電極12と導通した一本の検出配線層19bが回路部21側に形成されている。

**【0036】**

図2に示すように、回路部21には回路側絶縁層18の裏面18aに、電子素子としてICパッケージ27が実装されており、各回路配線層19がICパッケージ27内の回路に導通している。ICパッケージ27内には、駆動回路や検出回路が含まれている。またICパッケージ27から回路配線層19が延出してコネクタ部29に接続されている。

**【0037】**

また図3, 図4に示すように回路配線層19は、配線絶縁層28で覆われている。ただし実装ランド部(図示せず)の部分に配線絶縁層28は形成されておらず、実装ランド部は露出した状態となっている。

**【0038】**

本実施形態では各層の材質を特に限定するものではないが、印刷形成可能とされ、例えば、各電極11, 12, 13、回路配線層19、さらには後述するリファレンスキャパシタ部を構成する導体層は、銀を含む導電層、カーボンを含む導電層、あるいはこれらの層の積層構造等で形成される。また、絶縁層14, 18, 28は例えばレジストで形成される。

**【0039】**

ICパッケージ27内の駆動回路によって、Y配線層19aを介してY駆動電極11にパルス状の電圧が一定の時間間隔で与えられる。このパルス状の電圧は複数のY駆動電極11に順番に与えられる。また、駆動回路によって、X配線層19cを介してX駆動電極13にパルス状の電圧が一定の時間間隔で与えられ、このときもパルス状の電圧が複数のX駆動電極13に順番に与えられる。ただし、Y駆動電極11とX駆動電極13には、異なる時間に電圧が与えられる。

**【0040】**

それぞれのY駆動電極11と検出電極12との間には静電容量が形成されている。いずれかのY駆動電極11にパルス状の電圧が印加されると、電圧の立ち上がりに同期して、電圧が与えられたY駆動電極11に隣接する検出電極12に瞬間的な電流が流れる。ほぼ接地電位の人の指(操作体)がセンサ部20の操作面に触れて、指がいずれかのY駆動電極11に接近すると、指とY駆動電極11との間に静電容量が形成され且つ指と検出電極12との間に静電容量が形成されるために、指が接近しているY駆動電極11と検出電極12との間の静電容量が変化する。検出電極12に流れる電流量は前記静電容量の変動に応じて変化するため、指の近くに位置するY駆動電極11に電圧が与えられたときに検出電極12に流れる電流量と、指が接近していないY駆動電極11に電圧を与えたときに検出電極12に流れる電流量との間に変化が生じる。

**【0041】**

本実施形態では、回路部21に二つのリファレンスキャパシタ部30, 31が形成されている。各リファレンスキャパシタ部30, 31には基準静電容量が設定されている。

10

20

30

40

50

**【0042】**

ここでリファレンスキャパシタ部30, 31の構成について説明する。図5(図2に示す回路部21側を上面側に図示した)に示すように、フィルム基材10にスルーホール32が形成され、スルーホール32内に充填された導電層33と検出電極12とが導通している。

**【0043】**

図5に示すように、回路部21側では、グランド層17と同じ形成面(フィルム基材10の裏面10b)に第1導体層34が印刷でパターン形成されている。図5に示すように検出電極12と第1導体層34は導電層33を介して導通している。

**【0044】**

さらに図5に示すように、回路配線層19と同じ形成面(回路側絶縁層18の裏面18a)に第2導体層35が形成されている。第2導体層35は、第1導体層34と回路側絶縁層18を介して対向し、第1導体層34と第2導体層35との間に基準静電容量C1を形成している。図2に示すように第2導体層35は印刷でパターン形成されており、ICパッケージ27に回路配線層19を介して接続される。なお第2導体層35と回路配線層19とを一体に形成することができる。

**【0045】**

例えば図2に示す符号30がX駆動電極13と検出電極12間の静電容量に対する基準静電容量C1を備えた第1リファレンスキャパシタ部30であり、符号31が、Y駆動電極11と検出電極12間の静電容量に対する基準静電容量C1を備えた第2リファレンスキャパシタ部31である。

**【0046】**

上記したように、各Y駆動電極11に対して次々にパルス状の電圧を与え、検出電極12に流れる電流量を検出する。更に、第2リファレンスキャパシタ部31の第2導体層35に対してパルス状の電圧を与える。すると、第2リファレンスキャパシタ部31の基準静電容量C1に基づいて検出電極12および検出配線層19bにより基準電流値が検出される。

**【0047】**

ICパッケージ27の検出回路では、この基準電流値と、各Y駆動電極11と検出電極12間の静電容量に基づく電流値を対比する。操作面に指を触れていないと、各Y駆動電極に電圧を与えて得られた各電流値と、基準電流値との差が所定範囲内に収められ、指が接近していないと判断できる。一方、指が操作面上に接近すると、指に近いY駆動電極11に電圧を印加したときに得られる電流値は、指が接近していないときの電流値に比べて変化するので、各Y駆動電極11に電圧を印加したときに得られた各電流値が基準電流値に対してどの程度変化しているかによって、指が接近している箇所のY座標上の位置を推定することができる。同様に、各X駆動電極13と第1リファレンスキャパシタ部30の第2導体層35に次々にパルス状の電圧を与え、検出電極12に流れる電流量を検出する。そして各X駆動電極13に電圧を印加したときに得られた各電流値が基準電流値に対してどの程度変化しているかによって、指が接近している箇所のX座標上の位置を推定することができる。

**【0048】**

また本実施形態の基準静電容量を有するリファレンスキャパシタ部を備えた静電容量式入力装置によれば、例えば、操作面全体を手で触った状態をも検出することが可能である。

**【0049】**

本実施形態の静電容量式入力装置1の特徴的部は、回路部21側に、回路側絶縁層18を介して対向する第1導体層34と第2導体層35とをパターン形成して基準静電容量を備えるリファレンスキャパシタ部30, 31を設けた点にある。

**【0050】**

これにより、フィルム基材10の裏側3に設けたリファレンスキャパシタ部30, 31

10

20

30

40

50

とフィルム基材 10 の表側 2 に設けたセンサ部 20 の双方に、フィルム基材 10 や各絶縁層 14、18 に対する誘電率依存性を持たせることができる。上記したようにフィルム基材 10 は P E T フィルム等であり環境変化によって誘電率が変化しやすい。また各絶縁層 14、18 もレジスト等で形成され環境変化によって誘電率が変化しやすい。このためセンサ部 20 のパターン形成された電極間の静電容量は、環境変化に伴うフィルム基材 10 や各絶縁層 14、18 の誘電率変化により変動しやすいが、本実施形態ではリファレンスキャパシタ部 30、31 をパターン形成することで、リファレンスキャパシタ部 30、31 の基準静電容量をセンサ部 20 側と同様に、フィルム基材 10 や各絶縁層 14、18 の誘電率変化に基づいて変動させることができるために、電極間の静電容量の温湿度ドリフトによっても検出誤差を小さくでき優れた位置検出精度を得ることが可能になる。

10

#### 【 0 0 5 1 】

また基準静電容量を有するリファレンスキャパシタ部をコンデンサチップとする構成では、リファレンスキャパシタ部にセンサ部と同様の、フィルム基材 10 や各絶縁層 14、18 に対する誘電率依存性を持たせることができないため、位置検出精度の向上を適切に図ることができない。

#### 【 0 0 5 2 】

本実施形態では、リファレンスキャパシタ部 30、31 をパターン形成することで、コンデンサチップを設ける構成に比べて、位置検出精度を適切に向上させることができるとともに、部品点数の削減及び薄型化を促進することが可能になる。また本実施形態では、フィルム基材 10 の表側 2 及び裏側 3 の双方にて各導電層を印刷形成でき、リファレンスキャパシタ部 30、31 の形成も第 1 導体層 34 をグランド層 17 と同じ工程で印刷形成でき、第 2 導体層 35 を回路配線層 19 と同じ工程で印刷形成できる。よってリファレンスキャパシタ部 30、31 の形成のために製造工程が増えることがなく、リファレンスキャパシタ部としてコンデンサチップを設ける構成に比べて製造コストの低減を図ることが可能である。

20

#### 【 0 0 5 3 】

本実施形態では、図 5 に示したように、リファレンスキャパシタ部 30、31 を、フィルム基材 10 のスルーホール 32 内の導電層 33 を介して検出電極 12 と導通する第 1 導体層 34 と、第 1 導体層 34 と回路側絶縁層 18 を介して対向する第 2 導体層 35 とをして構成しているため、センサ部 20 側から回路部 21 側の I C パッケージ 27 に向う配線パターン（電気回路）を簡易化でき、また簡単な構造でリファレンスキャパシタ部 30、31 を形成できる。

30

#### 【 0 0 5 4 】

また、本実施形態では、図 2、図 5 に示すように、第 1 導体層 34 及び第 2 導体層 35 を、基準静電容量 C1 に応じて、所定の長さ寸法にて直線状に延出形成することが好適である。簡単な構成で所望の基準静電容量 C1 を備えるリファレンスキャパシタ部 30、31 を形成できる。

#### 【 0 0 5 5 】

また本実施形態ではセンサ部 20 側に設けられるセンサ側絶縁層 14 と、回路部 21 側に設けられる回路側絶縁層 18 とを同じ層構成で形成することが好ましい。ここで「同じ層構成」とは同じ材質で、さらにはほぼ同じ厚みであることを意味する。これにより、センサ部 20 とリファレンスキャパシタ部 30、31 とで絶縁層に対する誘電率依存性を同じにでき、より効果的に位置検出精度の向上を図ることができる。

40

#### 【 0 0 5 6 】

図 6 は、リファレンスキャパシタ部 40 の第 2 実施形態を示すものである。図 6 ( a ) ( b ) に示すように、リファレンスキャパシタ部 40 は、第 1 導体層 41 と第 2 導体層 42 とを有し、第 1 導体層 41 は、検出電極 12 と導電層 33 を介して導通している。導電層 33 はフィルム基材 10 に形成されたスルーホール 32 内に形成されている。

#### 【 0 0 5 7 】

図 6 ( a ) に示すように第 1 導体層 41 と第 2 導体層 42 とは回路側絶縁層 18 を介し

50

て対向しており、第1導体層41と第2導体層42間に基準静電容量C2が形成されている。

**【0058】**

さらに図6に示すリファレンスキャパシタ部40は、回路側絶縁層18にスルーホール43が形成され、スルーホール43内を導電層44が埋めている。そして第1導体層41と第3導体層45とが導電層44を介して導通している。

**【0059】**

図6(b)に示すように、第2導体層42は第3導体層45と平面視にて対向する位置まで延出してあり、第2導体層42と第3導体層45との間に基準静電容量C2に対する微調整用のコンデンサチップ46が設けられている。なお、基準静電容量C2に対して微調整用コンデンサチップ46の静電容量は十分に小さく例えば基準静電容量C2に対して1/10程度である。10

**【0060】**

微調整用コンデンサチップ46は、リファレンスキャパシタ部40を構成する第1導体層41及び第2導体層42を印刷した際、基準静電容量C2がばらつく等の不具合発生時に微調整できるように取り付けたものであるが、微調整用コンデンサチップ46の取り付けの有無は任意に決定することが出来る。

**【0061】**

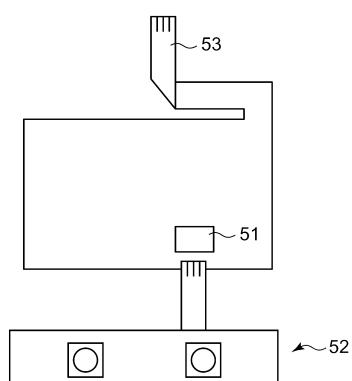

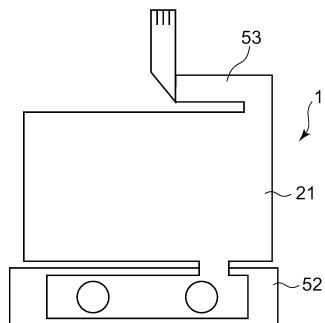

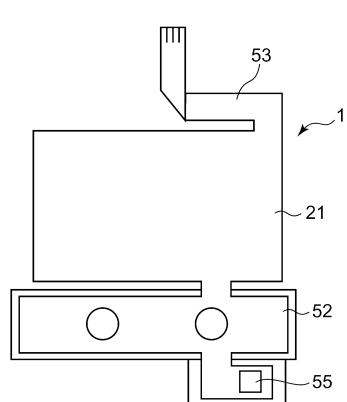

本実施形態における静電容量式入力装置1はノートパソコン等に搭載されるポインティングデバイスとして用いることができ、例えば図7のように静電容量式入力装置1の裏側の回路部21には、二つのコネクタ部50, 51が取り付けられている。そして一方のコネクタ部50にはフレキシブルフラットケーブル53が接続され、他方のコネクタ部51にはスイッチ部54, 54と金属プレートを備えるフレキシブルプリント基板52が接続されている。20

**【0062】**

また図8に示すように本実施形態の静電容量式入力装置1を構成するフィルム基材を延在させて図7に示したフレキシブルフラットケーブル53を一体にすることも可能である。これにより図8では図7に比べてコネクタ部50を少なくでき部品点数を減らすことが可能になる。

**【0063】**

さらには図9に示すように、フィルム基材をフレキシブルフラットケーブル53用として延在させるとともにフレキシブルプリント基板52用としても延在させて図7に示したフレキシブルプリント基板52も一体的に形成することができ、これにより図7で示したコネクタ部50, 51の双方を削除できる。30

また図10では、さらにフィルム基材を延長させてホールIC55を取り付けている。

**【符号の説明】**

**【0064】**

- 1 静電容量式入力装置

- 2 表側

- 3 裏側

- 10 フィルム基材

- 11 Y駆動電極

- 12 検出電極

- 13 X駆動電極

- 14 センサ側絶縁層

- 17 グランド層

- 18 回路側絶縁層

- 19 回路配線層

- 20 センサ部

- 21 回路部

10

20

30

40

50

24、25、26、32、43 スルーホール

27 I C パッケージ

30、31、40 リファレンスキャパシタ部

34、41 第1導体層

35、42 第2導体層

45 第3導体層

46 微調整用コンデンサチップ

29、50、51 コネクタ部

52 フレキシブルプリント基板

53 フレキシブルフラットケーブル

10

【図1】

【図2】

【図3】

【図5】

【図4】

図4

【図6】

(a)

(b)

【図7】

図7

【図8】

【図9】

【図10】

図10

図8

図9

---

フロントページの続き

(56)参考文献 特開2002-366304(JP,A)

特開2003-028606(JP,A)

特開2005-140612(JP,A)

特開2003-099185(JP,A)

特開2011-197942(JP,A)

特開2007-179230(JP,A)

特開2010-218535(JP,A)

特開2012-043275(JP,A)

特開2010-273020(JP,A)

特開2006-012110(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041

G 06 F 3 / 044