(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6123408号

(P6123408)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

|              |                         |

|--------------|-------------------------|

| (51) Int.Cl. | F 1                     |

| C 30B 29/36  | (2006.01) C 30B 29/36 A |

| C 30B 25/20  | (2006.01) C 30B 25/20   |

| C 23C 16/42  | (2006.01) C 23C 16/42   |

| H 01L 21/205 | (2006.01) H 01L 21/205  |

請求項の数 17 (全 8 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-64365 (P2013-64365)    |

| (22) 出願日  | 平成25年3月26日 (2013.3.26)        |

| (65) 公開番号 | 特開2014-189422 (P2014-189422A) |

| (43) 公開日  | 平成26年10月6日 (2014.10.6)        |

| 審査請求日     | 平成28年2月18日 (2016.2.18)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100082175<br>弁理士 高田 守                      |

| (74) 代理人  | 100106150<br>弁理士 高橋 英樹                     |

| (74) 代理人  | 100148057<br>弁理士 久野 淑己                     |

| (72) 発明者  | 大野 彰仁<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

| (72) 発明者  | 川津 善平<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

最終頁に続く

(54) 【発明の名称】 単結晶4H-SiC基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

平坦性を有する4H-SiCバルク単結晶基板を準備する工程と、前記4H-SiCバルク単結晶基板上に凹部を有する第1の単結晶4H-SiC層をエピタキシャル成長させる工程とを備え、

前記第1の単結晶4H-SiC層の膜厚をX [μm] とすると、前記凹部の直径Y [μm] は0.2×X以上、2×X以下であり、かつ前記凹部の深さZ [μm] は(0.95×X+0.5)×0.001以上、0.01×X以下であり、

前記第1の単結晶4H-SiC層の表面の前記凹部の密度が10個/cm<sup>2</sup>以上であることを特徴とする単結晶4H-SiC基板の製造方法。

## 【請求項2】

前記第1の単結晶4H-SiC層を形成する際に、前記第1の単結晶4H-SiC層の成長表面に前記凹部が形成されるように成長炉内の圧力と温度を設定することを特徴とする請求項1に記載の単結晶4H-SiC基板の製造方法。

## 【請求項3】

前記凹部の直径Y [μm] は2μm以上20μm以下であり、前記凹部の深さZ [μm] は0.01μm以上0.1μm以下であることを特徴とする請求項1又は2に記載の単結晶4H-SiC基板の製造方法。

## 【請求項4】

前記第1の単結晶4H-SiC層の膜厚X [μm] は0.3μm以上10μm以下であ

10

20

ることを特徴とする請求項 1 ~ 3 の何れか 1 項に記載の単結晶 4 H - SiC 基板の製造方法。

**【請求項 5】**

前記第 1 の単結晶 4 H - SiC 層の欠陥密度は 2 個 / cm<sup>2</sup> 以下であることを特徴とする請求項 1 ~ 4 の何れか 1 項に記載の単結晶 4 H - SiC 基板の製造方法。

**【請求項 6】**

前記第 1 の単結晶 4 H - SiC 層は N 型不純物がドーピングされていることを特徴とする請求項 1 ~ 5 の何れか 1 項に記載の単結晶 4 H - SiC 基板の製造方法。

**【請求項 7】**

前記第 1 の単結晶 4 H - SiC 層上に、前記凹部を埋め込むように第 2 の単結晶 4 H - SiC 層をエピタキシャル成長させる工程を更に備えることを特徴とする請求項 1 ~ 6 の何れか 1 項に記載の単結晶 4 H - SiC 基板の製造方法。 10

**【請求項 8】**

前記第 2 の単結晶 4 H - SiC 層は N 型不純物がドーピングされていることを特徴とする請求項 7 に記載の単結晶 4 H - SiC 基板の製造方法。

**【請求項 9】**

前記第 2 の単結晶 4 H - SiC 層の表面平均粗さは 0 . 3 nm 以下であることを特徴とする請求項 7 又は 8 に記載の単結晶 4 H - SiC 基板の製造方法。

**【請求項 10】**

平坦性を有する 4 H - SiC バルク単結晶基板と、 20

前記 4 H - SiC バルク単結晶基板上に形成され、凹部を有する第 1 の単結晶 4 H - SiC 層とを備え、

前記第 1 の単結晶 4 H - SiC 層の膜厚を X [ μm ] とすると、前記凹部の直径 Y [ μm ] は 0 . 2 × X 以上、2 × X 以下であり、かつ前記凹部の深さ Z [ μm ] は ( 0 . 95 × X + 0 . 5 ) × 0 . 001 以上、0 . 01 × X 以下であり、

前記第 1 の単結晶 4 H - SiC 層の表面の前記凹部の密度が 10 個 / cm<sup>2</sup> 以上であることを特徴とする単結晶 4 H - SiC 基板。

**【請求項 11】**

前記凹部の直径 Y [ μm ] は 2 μm 以上 20 μm 以下であり、前記凹部の深さ Z [ μm ] は 0 . 01 μm 以上 0 . 1 μm 以下であることを特徴とする請求項 10 に記載の単結晶 4 H - SiC 基板。 30

**【請求項 12】**

前記第 1 の単結晶 4 H - SiC 層の膜厚 X [ μm ] は 0 . 3 μm 以上 10 μm 以下であることを特徴とする請求項 10 又は 11 に記載の単結晶 4 H - SiC 基板。

**【請求項 13】**

前記第 1 の単結晶 4 H - SiC 層の欠陥密度は 2 個 / cm<sup>2</sup> 以下であることを特徴とする請求項 10 ~ 12 の何れか 1 項に記載の単結晶 4 H - SiC 基板。

**【請求項 14】**

前記第 1 の単結晶 4 H - SiC 層は N 型不純物がドーピングされていることを特徴とする請求項 10 ~ 13 の何れか 1 項に記載の単結晶 4 H - SiC 基板。 40

**【請求項 15】**

前記第 1 の単結晶 4 H - SiC 層上に形成された第 2 の単結晶 4 H - SiC 層を更に備え、

前記凹部は前記第 2 の単結晶 4 H - SiC 層に埋め込まれていることを特徴とする請求項 10 ~ 14 の何れか 1 項に記載の単結晶 4 H - SiC 基板。

**【請求項 16】**

前記第 2 の単結晶 4 H - SiC 層は N 型不純物がドーピングされていることを特徴とする請求項 15 に記載の単結晶 4 H - SiC 基板。

**【請求項 17】**

前記第 2 の単結晶 4 H - SiC 層の表面平均粗さは 0 . 3 nm 以下であることを特徴と 50

する請求項1 5に記載の単結晶4H-SiC基板。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、結晶欠陥を低減することができる単結晶4H-SiC基板及びその製造方法に関する。

【背景技術】

【0002】

近年、バンドギャップ、絶縁破壊電界強度、飽和ドリフト速度、熱伝導度がシリコンに比べて相対的に大きい炭化珪素（以下SiCと記す）が、主に電力制御用パワーデバイス材料として注目されている。このSiCを用いたパワーデバイスは、電力損失の大幅な低減、小型化などが可能であり、電源電力変換時の省エネルギー化が実現できるため、電気自動車の高性能化、太陽電池システム等の高機能化等、低炭素社会実現の上でキーデバイスとなる。

【0003】

SiCパワーデバイスの仕様によりドーピング密度及び膜厚がほぼ既定され、通常、バルク単結晶基板より高い精度が求められる。そこで、4H-SiCバルク単結晶基板上に予め半導体デバイスの活性領域が熱CVD法（熱化学気相堆積法）等によりエピタキシャル成長される。ここでいう活性領域とは、結晶中におけるドーピング密度及び膜厚が精密に制御された領域のことである。

【0004】

4H-SiCバルク単結晶基板には、c軸方向に伝播するらせん転位、刃状転位、c軸と垂直方向に伝播する転位（基底面転位）が内在している。これらの転位は、基板上に成長させたエピタキシャル膜に伝播する。更にエピタキシャル成長時に新たな転位ループや積層欠陥が導入される。これらの結晶欠陥は、このSiC基板を用いたデバイスの耐電圧特性、信頼性、歩留りを低下させ、実用化の弊害となる場合がある。

【0005】

なお、単結晶3C-SiC基板の製造方法として、平坦面に表面ピットが点在する表面状態となるように単結晶3C-SiC層を形成することで、結晶欠陥を低減する方法が提案されている（例えば、特許文献1参照）。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2011-225421号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

立方晶である3C-SiCと六方晶である4H-SiCは、結晶構造、即ち原子配列が異なるため、成長条件が大きく異なる。例えば3C-SiCの成長温度は1000～1100であるのに対し、4H-SiCの成長温度は1600～1800と非常に高温になる。従って、単結晶3C-SiC基板の結晶欠陥を低減する方法は単結晶4H-SiC基板には適用できず、単結晶4H-SiC基板において結晶欠陥を低減する方法は知られていなかった。

【0008】

本発明は、上述のような課題を解決するためになされたもので、その目的は結晶欠陥を低減することができる単結晶4H-SiC基板及びその製造方法を得るものである。

【課題を解決するための手段】

【0009】

本発明に係る単結晶4H-SiC基板の製造方法は、平坦性を有する4H-SiCバルク単結晶基板を準備する工程と、前記4H-SiCバルク単結晶基板上に凹部を有する第

10

20

30

40

50

1の単結晶4H-SiC層をエピタキシャル成長させる工程とを備え、前記第1の単結晶4H-SiC層の膜厚をX[μm]とすると、前記凹部の直径Y[μm]は0.2×X以上、2×X以下であり、かつ前記凹部の深さZ[μm]は(0.95×X+0.5)×0.001以上、0.01×X以下であり、前記第1の単結晶4H-SiC層の表面の前記凹部の密度が10個/cm<sup>2</sup>以上である。

**【発明の効果】**

**【0010】**

本発明により、結晶欠陥を低減することができる。

**【図面の簡単な説明】**

**【0011】**

10

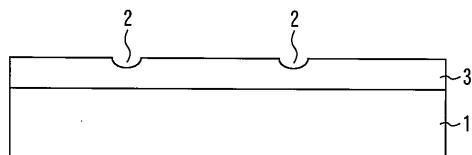

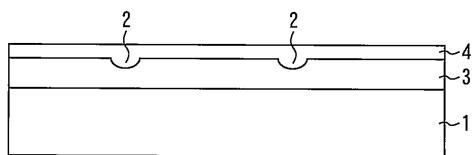

**【図1】**本発明の実施の形態1に係る単結晶4H-SiC基板の製造方法を示す断面図である。

**【図2】**本発明の実施の形態1に係る単結晶4H-SiC基板の製造方法を示す断面図である。

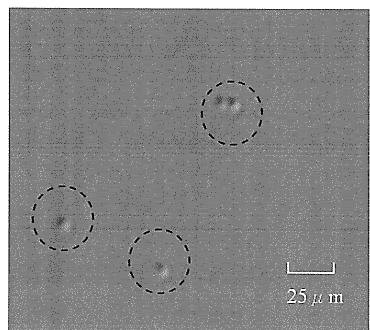

**【図3】**単結晶4H-SiC層の成長表面に形成された凹部を光学顕微鏡で観察した顕微鏡写真像である。

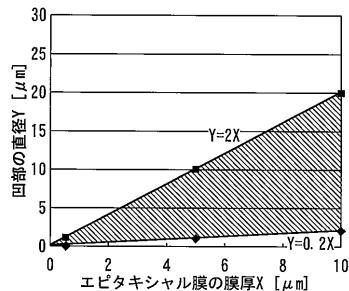

**【図4】**凹部の直径とエピタキシャル膜の膜厚の関係を示す図である。

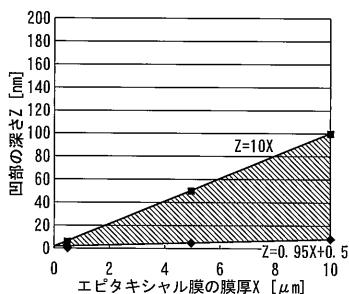

**【図5】**凹部の深さとエピタキシャル膜の膜厚の関係を示す図である。

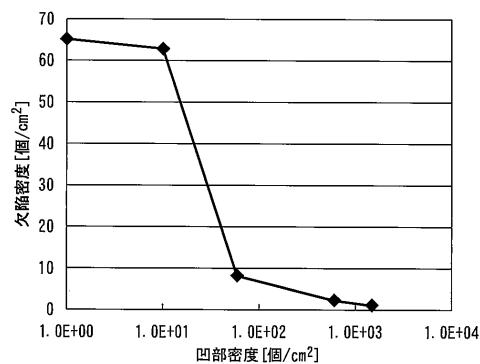

**【図6】**単結晶4H-SiC層の表面の凹部の密度と欠陥密度の関係を示す図である。

**【図7】**本発明の実施の形態2に係る単結晶4H-SiC基板の製造方法を示す断面図である。

20

**【発明を実施するための形態】**

**【0012】**

本発明の実施の形態に係る単結晶4H-SiC基板及びその製造方法について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

**【0013】**

実施の形態1.

以下、本発明の実施の形態1に係る単結晶4H-SiC基板の製造方法について説明する。図1及び図2は、本発明の実施の形態1に係る単結晶4H-SiC基板の製造方法を示す断面図である。

30

**【0014】**

まず、図1に示すように、主面となる(0001)面(C面)に対して<11-20>方向へ4度のオフ角を有する4H-SiCバルク単結晶基板1を準備する。ここで、オフ角は4度に限ったものではなく、2度~10度の範囲内であればよい。

**【0015】**

具体的には、4H-SiCバルク単結晶基板1に対し、機械研磨、及び酸性又はアルカリ性を呈する薬液を用いた化学機械研磨により平坦化処理を行う。さらに、アセトンを用いて超音波洗浄を施し有機物を除去する。次に、4H-SiCバルク単結晶基板1に対してもいわゆるRCA洗浄を行う。即ち、75(±5)に加熱したアンモニア水と過酸化水素水の混合液(1:9)に10分間浸した後に、75(±5)に加熱した塩酸と過酸化水素水(1:9)に浸す。さらに、体積比率で5%程度のフッ酸を含む水溶液に浸し、更に純水により置換処理を施すことにより、4H-SiCバルク単結晶基板1に対する表面洗浄を行う。

40

**【0016】**

次に、4H-SiCバルク単結晶基板1をCVD装置に導入する。約1×10<sup>-7</sup>kPa程度にまで真空引きを行う。その後、1400~1700程度まで加熱し、還元性ガス雰囲気中でのアニール工程を実施する。次に、図2に示すように、原料ガスを供給して、4H-SiCバルク単結晶基板1上に、直径2~20μm、最深部の深さ10~100nmの凹部2を有する単結晶4H-SiC層3をエピタキシャル成長させる。原料ガス

50

には、例えば、Si原子の供給源としてシランガス(SiH<sub>4</sub>)を用い、C原子の供給源としてプロパンガス(C<sub>3</sub>H<sub>8</sub>)を用い、N型ドーピングとして窒素ガスを用いる。ここでは、SiH<sub>4</sub>ガスを500sccm、C<sub>3</sub>H<sub>8</sub>ガスを200sccmの流量で供給を行い、膜厚10μmの単結晶4H-SiC層3を成膜する。また、基板界面ではキャリア濃度が1×10<sup>17</sup>/cm<sup>3</sup>となり、活性領域ではキャリア濃度が8×10<sup>15</sup>/cm<sup>3</sup>となるようにN型ドーピングとして窒素ガスを供給した。その後、原料ガスの供給を停止し、室温まで降温させる。

#### 【0017】

ここで、発明者は、単結晶4H-SiC層3を形成する際に、成長炉内の圧力と温度を適切に設定することで、単結晶4H-SiC層3の成長表面に非常に微小な凹部2が形成されることを発見した。図3は、単結晶4H-SiC層の成長表面に形成された凹部を光学顕微鏡で観察した顕微鏡写真像である。光学顕微鏡により凹部2の密度を算出したところ、その密度は約600個/cm<sup>2</sup>であった。この凹部2の表面形状を原子間力顕微鏡(Atomic Force Microscope)により測定したところ、形は非対称な橈円錐型であり、直径2~20μm、最深部の深さ10~100nmであった。さらに詳細な実験を繰り返した結果、凹部の大きさは成膜されるエピタキシャル膜の膜厚によって異なっており、膜が厚い方が凹部の直径や深さも大きくなることが分かった。図4は凹部の直径とエピタキシャル膜の膜厚の関係を示す図である。図5は凹部の深さとエピタキシャル膜の膜厚の関係を示す図である。実験の結果、エピタキシャル膜の膜厚をX[μm]とすると、凹部の直径Y[μm]は0.2×X[μm]以上、2×X[μm]以下であり、かつ凹部の深さZ[nm]は0.95×X[μm]+0.5[nm]以上、10×X[μm]以下であることが分かった。

#### 【0018】

図6は、単結晶4H-SiC層の表面の凹部の密度と欠陥密度の関係を示す図である。欠陥密度はフォトルミネッセンストポグラフィー法(PL-TOPO法)により観測した。ここでは、欠陥密度をPL-TOPO法で観察される発光異常領域と定義する。一般的な成長条件を用いて単結晶4H-SiC層を成膜させた従来の基板の場合、光学顕微鏡では凹部はほとんど観察されず、その密度は10個/cm<sup>2</sup>より少ない。この場合の欠陥密度は60個/cm<sup>2</sup>以上となる。デバイス電極の面積が1~2mm角以上と大きいものもあり、従来の単結晶4H-SiC基板を用いると電極下に1個以上の欠陥が存在することになり、デバイスの耐電圧特性等が劣化する。

#### 【0019】

一方、凹部2の密度を10個/cm<sup>2</sup>以上とした本実施の形態に係る単結晶4H-SiC基板の場合には、欠陥密度は2個/cm<sup>2</sup>と大幅に低減できる。凹部2の密度を150個/cm<sup>2</sup>とした場合には欠陥密度は1個/cm<sup>2</sup>と非常に低密度となった。

#### 【0020】

以上説明したように、本実施の形態では、直径Y[μm]が0.2×X[μm]以上、2×X[μm]以下であり、かつ深さZ[nm]が0.95×X[μm]+0.5[nm]以上、10×X[μm]以下である凹部を有する単結晶4H-SiC層3をエピタキシャル成長させる。これにより、結晶欠陥を低減することができる。さらに、この高品質な単結晶4H-SiC基板を用いたデバイスの耐電圧特性、信頼性、歩留りを向上させることができる。

#### 【0021】

なお、単結晶4H-SiC層3を形成する際に、必要に応じてP型ドーピング用にAl、B、Beを含む有機金属材料を供給してもよい。また、成長の高速化を図るために、塩素を含むガスを併用してもよい。また、原料ガス流量を変えることで単結晶4H-SiC層3の成長速度を変えることができ、成長速度が1μm/hであっても、10μm/hであっても同様の効果があることを確認した。

#### 【0022】

また、凹部2の密度は成長炉内の圧力と温度を適切に設定することで調整できることを

10

20

30

40

50

見出した。ただし、その条件は一義的に決定されるものでは無く、CVD装置の炉内構成、構造等により大きく依存すると考えられ、それぞれの場合において好適な条件が決まる。

#### 【0023】

実施の形態2.

以下、本発明の実施の形態2に係る単結晶4H-SiC基板の製造方法について説明する。図7は、本発明の実施の形態2に係る単結晶4H-SiC基板の製造方法を示す断面図である。

#### 【0024】

まず、実施の形態1と同様に、成長表面に凹部2を有する単結晶4H-SiC層3をエピタキシャル成長により膜厚300nmで形成する。なお、単結晶4H-SiC層3の膜厚は300nmに限らず、50nm～10μmの範囲であればよい。次に、図7に示すように、単結晶4H-SiC層3上に、凹部2を埋め込むように単結晶4H-SiC層4をエピタキシャル成長により膜厚10μmで形成する。

#### 【0025】

このとき、SiH<sub>4</sub>ガスを900sccm、C<sub>3</sub>H<sub>8</sub>ガスを360sccmの流量で供給し、N型ドーピングとしてキャリア濃度が8×10<sup>15</sup>/cm<sup>3</sup>となるよう窒素ガスを供給する。その後、原料ガスの供給を停止し、室温まで降温させる。その他の構成及び製造工程は、実施の形態1と同様である。

#### 【0026】

ここで、成長温度等を適宜設定して、ステップフロー成長と呼ばれる成長モードが支配的な成長条件で単結晶4H-SiC層4を成長させれば、単結晶4H-SiC層3の凹部2を埋め込むことができる。

#### 【0027】

本実施の形態に係る単結晶4H-SiC基板の表面の凹部2の密度を光学顕微鏡により算出したところ、約1個/cm<sup>2</sup>と非常に低密度であった。さらに、10μm角正方領域を原子間力顕微鏡により評価したところ、ステップパンチングと呼ばれる異常成長の発生も無く、平均荒さ(Ra)は0.3nm以下と非常に良好な結果であった。また、PL-TOPO法で観測した結果、欠陥密度は2個/cm<sup>2</sup>と非常に低く、単結晶4H-SiC層3の成膜時に得られた低い欠陥密度を維持できていることを確認した。

#### 【0028】

本実施の形態では、単結晶4H-SiC層3の凹部2を埋め込むように単結晶4H-SiC層4を形成する。これにより、結晶欠陥を低減することができ、かつ単結晶4H-SiC基板の平坦性を向上させることもできる。

#### 【0029】

なお、実施の形態2のように単結晶4H-SiC層を2層構造とした場合にも、図6に示した凹部の密度と欠陥密度の関係が得られる。また、凹部が形成された単結晶4H-SiC層3は、必ずしも4H-SiCバルク単結晶基板1と接する必要はなく、例えば単結晶4H-SiC層4の層間にあっても同様に結晶欠陥を低減することができる。従って、要求されるデバイスの仕様により、単結晶4H-SiC層3の層位置を自由に変更することができる。この結果、活性領域のキャリア濃度と膜厚を精密に制御しながら、同時に欠陥密度の制御も可能となる。

#### 【符号の説明】

#### 【0030】

1　4H-SiCバルク単結晶基板、2　凹部、3　単結晶4H-SiC層(第1の単結晶4H-SiC層)、4　単結晶4H-SiC層(第2の単結晶4H-SiC層)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 富田 信之

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 田中 貴規

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 三谷 陽一郎

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 浜野 健一

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

審査官 村岡 一磨

(56)参考文献 特開2013-251419 (JP, A)

特開2007-299877 (JP, A)

国際公開第03/078702 (WO, A1)

特開2013-018659 (JP, A)

特表2007-529901 (JP, A)

特開2006-328455 (JP, A)

特開2012-116732 (JP, A)

(58)調査した分野(Int.Cl., DB名)

C30B 1/00-35-00

C23C 16/00-16/56

H01L 21/205