(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5864053号

(P5864053)

(45) 発行日 平成28年2月17日(2016.2.17)

(24) 登録日 平成28年1月8日(2016.1.8)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

H01L 29/786 (2006.01)

H01L 29/78 612C

請求項の数 6 (全 23 頁)

(21) 出願番号 特願2011-273480 (P2011-273480)

(22) 出願日 平成23年12月14日 (2011.12.14)

(65) 公開番号 特開2012-145927 (P2012-145927A)

(43) 公開日 平成24年8月2日 (2012.8.2)

審査請求日 平成26年12月1日 (2014.12.1)

(31) 優先権主張番号 特願2010-282635 (P2010-282635)

(32) 優先日 平成22年12月20日 (2010.12.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 広瀬 篤志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 右田 昌士

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

走査線と、

前記走査線と交差する領域において、第1の電極として機能することができる領域を有する信号線と、

前記走査線に沿う方向に延在する容量配線と、

前記第1の電極に対向するように配置された第2の電極と、

前記第1の電極に対向するように配置された第3の電極と、

前記第2の電極と電気的に接続された第1の画素電極と、

前記第3の電極と電気的に接続された第2の画素電極と、

前記第1の電極、前記第2の電極、及び前記第3の電極と電気的に接続され、且つ前記走査線と重なる領域を有する半導体膜と、を有し、

前記第1の電極として機能することができる前記領域は、前記走査線が延在する方向に突出して配置されており、

前記走査線は、開口部を有する領域を有し、

前記第1の電極は、前記開口部と重なる領域を有し、

前記容量配線は、前記信号線と重なる領域を有し、

前記半導体膜は、前記信号線が延在する方向に延びた領域を有し、

前記半導体膜は、前記容量配線と前記信号線とが重なる領域の外側に、端部を有することを特徴とする表示装置。

10

20

## 【請求項 2】

請求項 1 において、

前記走査線と前記半導体膜との間にゲート絶縁膜を有し、

前記走査線、前記ゲート絶縁膜、前記半導体膜、前記第 1 の電極、及び前記第 2 の電極により第 1 の薄膜トランジスタが構成され、

前記走査線、前記ゲート絶縁膜、前記半導体膜、前記第 1 の電極、及び前記第 3 の電極により第 2 の薄膜トランジスタが構成されることを特徴とする表示装置。

## 【請求項 3】

請求項 1 又は 2 において、

前記走査線に沿う方向に延在する容量配線を有し、

10

前記容量配線は、前記信号線と重なる領域を有し、

前記第 3 の半導体膜は、前記信号線が延在する方向に延びた領域を有し、

前記第 3 の半導体膜は、前記容量配線と前記信号線とが重なる領域の外側に、端部を有することを特徴とする表示装置。

## 【請求項 4】

請求項 1 乃至 3 のいずれか一項において、

前記表示装置を上方からみたとき、前記第 1 の電極は、前記第 2 の電極と前記第 3 の電極との間に配置されていることを特徴とする表示装置。

## 【請求項 5】

請求項 1 乃至 4 のいずれか一項において、

20

前記表示装置を上方からみたとき、前記第 2 の電極及び前記第 3 の電極は、前記第 1 の電極の一方の辺側に配置されていることを特徴とする表示装置。

## 【請求項 6】

請求項 1 乃至 5 のいずれか一項において、

前記走査線は、前記開口部を有する前記領域において、前記開口部を介して対向する第 1 の部分と第 2 の部分とを有し、

前記走査線は、前記第 1 の部分において第 1 の幅と、前記第 2 の部分において第 2 の幅と、前記領域とは異なる領域において第 3 の幅と、を有し、

前記第 1 の幅と前記第 2 の幅の合計は、前記第 3 の幅以上であることを特徴とする表示装置。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、表示装置及びその作製方法に関する。

## 【背景技術】

## 【0002】

近年、視野角特性や表示品質が改善された液晶表示装置として、垂直配向 ( V A : V e r t i c a l l y A l i g n e d ) 型の液晶表示装置が提供されている。また、 V A 型液晶表示装置において、一画素に複数の画素電極と、それぞれの画素電極に接続し、画素電極の電位を制御する薄膜トランジスタを有するマルチドメイン構造の液晶表示装置が提供されている。一画素に複数の画素電極を設けることで、各画素電極によって液晶の配向を異ならせることが可能であるため、従来の V A 型液晶表示装置と比較して、更に視野角を広げることが可能である ( 特許文献 1 参照 ) 。

40

## 【0003】

また、液晶表示装置は、画面サイズが対角 60 インチ以上と大型化する傾向にあり、さらには、対角 120 インチ以上の画面サイズも視野に入れた開発が行われている。加えて、画面の解像度も、ハイビジョン画質 ( H D 、 1366 × 768 ) 、フルハイビジョン画質 ( F H D 、 1920 × 1080 ) と高精細化の傾向にあり、解像度が 3840 × 2048 または 4096 × 2180 といった、いわゆる 4 K デジタルシネマ用の液晶表示装置の開発も急がれている。

50

**【0004】**

また、残像を低減し、表示品位を向上するために駆動速度を2倍（倍速駆動とも呼ばれる）の高速駆動とすることが行われており、さらには4倍速以上の高速駆動が検討されている。また、3次元（3D）表示の液晶表示装置を実現するには、右目用と左目用の画像を交互に表示する必要があるため、2倍速駆動以上の高速動作で液晶表示装置を動作させることが求められる。

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2006-317867号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、液晶表示装置の大型化と高精細化に伴い、必要とされる画素数が著しく増加し、一画素当たりの書き込み時間が短くなる。このため、画素電極の電位を制御する薄膜トランジスタには、高速動作及び高いオン電流等が求められている。

**【0007】**

また、配線抵抗及び配線間に生じる寄生容量の増大は、信号線の終端への信号伝達の遅れを引き起す。この結果、表示ムラや階調不良などの表示品質の低下や、消費電力の増加が生じてしまう。

20

**【0008】**

そこで、本発明の一態様は、配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供することを課題とする。また、本発明の一態様は、表示品質を向上させた表示装置を提供することを課題とする。また、本発明の一態様は、消費電力を低減できる表示装置を提供することを課題とする。

**【課題を解決するための手段】****【0009】**

本発明の一態様は、液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状で開口部を有しており、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

30

**【0010】**

また、本発明の一態様は、マルチドメイン構造の液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する複数の第2の電極と、該複数の第2の電極と接続する複数の画素電極とを有する。また、走査線の一部はループ形状で開口部を有する。また、走査線、第1の電極、ゲート絶縁膜、半導体膜、及び複数の第2の電極の一により第1の薄膜トランジスタを構成し、走査線の開口部と第1の電極とが重畳する。また、走査線、第1の電極、ゲート絶縁膜、半導体膜、及び複数の第2の電極の二により第2の薄膜トランジスタを構成し、走査線の開口部と第1の電極とが重畳する。

40

**【0011】**

上記走査線において、走査線の一部はループ形状で開口部を有する領域であり、走査線の他部は信号線と交差する方向に延伸する領域であり、走査線の一部において、開口部を挟んだ走査線の幅の合計は、走査線の他部の幅以上であることが好ましい。また、走査線の一部の端部は、走査線の他部の端部より外側に位置することが好ましい。更には、当該走査線の一部の端部が、走査線の他部の端部より外側に位置する領域において、走査線は上記ループ形状を有する。

**【0012】**

なお、第1の電極は、第1の薄膜トランジスタ及び第2の薄膜トランジスタのソース電極

50

及びドレイン電極の一方として機能する。また、複数の第2の電極の一は、第1の薄膜トランジスタのソース電極及びドレイン電極の他方として機能し、複数の第2の電極の二は、第2の薄膜トランジスタのソース電極及びドレイン電極の他方として機能する。

#### 【0013】

また、第1の電極は、上面形状において、複数の第2の電極それぞれの間に設けられてもよい。または、第2の電極及び第3の電極は、上面形状において、前記第1の電極の一方の辺側に設けられてもよい。

#### 【0014】

複数の薄膜トランジスタにおいて、ソース電極及びドレイン電極の一方として機能する第1の電極が共通している。このため、ソース電極及びドレイン電極の一方並びに走査線の重畠面積を低減することが可能であり、画素の開口率を維持しつつ、且つ走査線及び第1の電極の間に生じる寄生容量を低減することができる。

10

#### 【0015】

また、走査線の一部はループ形状で開口部を有しており、当該開口部と重畠する領域に、薄膜トランジスタにおいてソース電極及びドレイン電極の一方として機能する第1の電極が位置する。このため、ループ形状の走査線と、第1の電極との重畠面積を低減することができる、走査線と第1の電極の寄生容量を低減することができる。

#### 【発明の効果】

#### 【0016】

本発明の一態様を適用することで、配線抵抗の上昇を防ぎつつ、画素の開口率を維持しつつ、且つ配線間の寄生容量を低減することができる。また、本発明の一態様を適用することで、表示装置の表示品質を向上させることができる。また、本発明の一態様を適用することで、表示装置の消費電力を低減することができる。

20

#### 【図面の簡単な説明】

#### 【0017】

【図1】本発明の一実施の形態に係る表示装置の画素の構成を説明する上面図である。

【図2】マルチドメイン構造の画素の構成を説明する回路図である。

【図3】本発明の一実施の形態に係る表示装置の薄膜トランジスタ及び容量素子を説明する断面図である。

【図4】本発明の一実施の形態に係る表示装置の画素の構成を説明する上面図である。

30

【図5】本発明の一実施の形態に係る表示装置の薄膜トランジスタを説明する断面図である。

【図6】本発明の一実施の形態に係る表示装置の薄膜トランジスタの作製方法を説明する断面図である。

【図7】本発明の一実施の形態に係る表示装置の薄膜トランジスタの作製方法を説明する断面図である。

【図8】本発明の一実施の形態に係る表示装置の画素の構成を説明する上面図である。

#### 【発明を実施するための形態】

#### 【0018】

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

40

#### 【0019】

なお本明細書にて用いる第1、第2、第3、乃至第n（nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【0020】

50

## (実施の形態 1 )

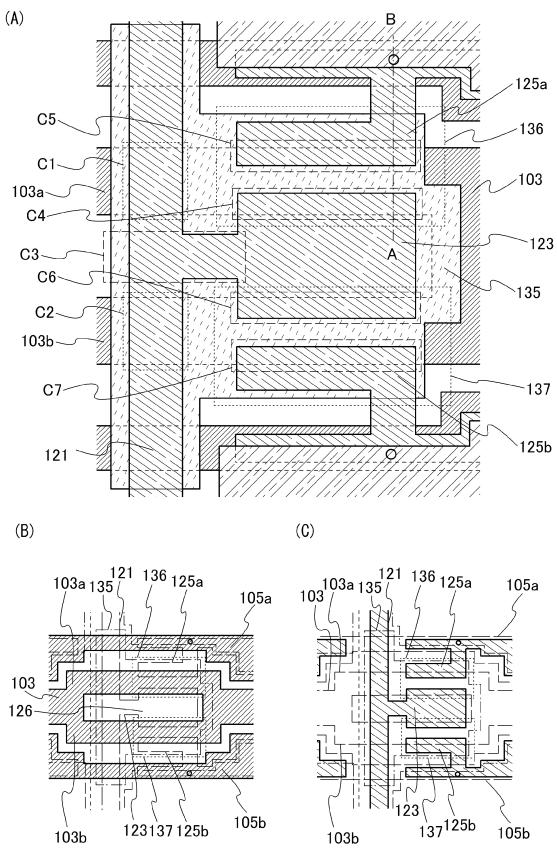

本実施の形態では、配線容量を低減した液晶表示装置の一画素の構成について、図 1 ~ 図 3、及び図 8 を用いて説明する。なお、本実施の形態では、1 画素に複数のサブ画素を設けた画素を、画素 1 0 0 として説明するがこれに限定されるものではない。

## 【 0 0 2 1 】

図 1 は、本実施の形態に示すマルチドメイン構造の液晶表示装置の一画素 1 0 0 の上面図を示し、図 2 ( A ) は、図 1 に示す画素 1 0 0 の回路図を示し、図 2 ( B ) は従来の画素の回路図を示し、図 3 ( A ) は、図 1 に示す一点鎖線 A - B の断面図を示し、図 3 ( B ) は、図 1 に示す一点鎖線 C - D の断面図を示す。図 8 ( A ) は、図 1 における薄膜トランジスタ 1 3 6 及び薄膜トランジスタ 1 3 7 の近傍の拡大上面図である。図 8 ( B ) は、図 8 ( A ) の走査線 1 0 3 、走査線 1 0 3 a 、及び走査線 1 0 3 b の形状を見やすくするため、走査線 1 0 3 、走査線 1 0 3 a 、走査線 1 0 3 b 、容量配線 1 0 5 a 、及び容量配線 1 0 5 b のみハッチングを用いて示した上面図である。図 8 ( C ) は、図 8 ( A ) の第 1 の電極 1 2 3 の形状を見やすくするため、信号線 1 2 1 、第 1 の電極 1 2 3 、第 2 の電極 1 2 5 a 、及び第 3 の電極 1 2 5 b のみハッチングを用いて示した上面図である。なお、図 8 ( B ) 及び図 8 ( C ) は、図 1 の一部を縮小して表示している。

## 【 0 0 2 2 】

図 1 及び図 2 ( A ) に示すように、画素 1 0 0 には、走査線 1 0 3 と、走査線 1 0 3 と交差する信号線 1 2 1 を有する。また、走査線 1 0 3 と同じ方向に延びる容量配線 1 0 5 a 及び容量配線 1 0 5 b を有する。なお、容量配線 1 0 5 a と、容量配線 1 0 5 b との間に、走査線 1 0 3 を有する。

## 【 0 0 2 3 】

また、走査線 1 0 3 及び信号線 1 2 1 の交差部近傍に薄膜トランジスタ 1 3 6 及び薄膜トランジスタ 1 3 7 を有する。薄膜トランジスタ 1 3 6 は、走査線 1 0 3 に重畠する半導体膜 1 3 5 と、半導体膜 1 3 5 と重畠する第 1 の電極 1 2 3 及び第 2 の電極 1 2 5 a を有する。第 1 の電極 1 2 3 は、信号線 1 2 1 から突出した領域である。第 1 の電極 1 2 3 及び第 2 の電極 1 2 5 a は、薄膜トランジスタ 1 3 6 においてソース電極及びドレイン電極として機能する。

## 【 0 0 2 4 】

薄膜トランジスタ 1 3 7 は、走査線 1 0 3 に重畠する半導体膜 1 3 5 と、半導体膜 1 3 5 と重畠する第 1 の電極 1 2 3 及び第 3 の電極 1 2 5 b を有する。第 1 の電極 1 2 3 及び第 3 の電極 1 2 5 b は、薄膜トランジスタ 1 3 7 においてソース電極及びドレイン電極として機能する。

## 【 0 0 2 5 】

薄膜トランジスタ 1 3 6 に含まれる第 2 の電極 1 2 5 a は、画素電極 1 3 9 a と接続される。即ち、薄膜トランジスタ 1 3 6 は、第 2 の電極 1 2 5 a により画素電極 1 3 9 a を含む液晶素子 1 4 2 と接続する。また、容量素子 1 4 0 の一方の電極は画素電極 1 3 9 a 及び薄膜トランジスタ 1 3 6 の第 2 の電極 1 2 5 a と接続し、他方の電極は容量配線 1 0 5 a と接続する(図 2 ( A ) 参照。)。

## 【 0 0 2 6 】

薄膜トランジスタ 1 3 7 に含まれる第 3 の電極 1 2 5 b は、画素電極 1 3 9 b と接続される。即ち、薄膜トランジスタ 1 3 7 は、第 3 の電極 1 2 5 b により画素電極 1 3 9 b を含む液晶素子 1 4 3 と接続する。また、容量素子 1 4 1 の一方の電極は画素電極 1 3 9 b 及び薄膜トランジスタ 1 3 7 の第 3 の電極 1 2 5 b と接続し、他方の電極は容量配線 1 0 5 b と接続する(図 2 ( A ) 参照。)。即ち、薄膜トランジスタ 1 3 6 及び薄膜トランジスタ 1 3 7 は、上面形状において画素 1 0 0 の略中央に位置し、画素 1 0 0 における各サブ画素の画素電極 1 3 9 a 及び画素電極 1 3 9 b の間に形成される。薄膜トランジスタ 1 3 6 及び薄膜トランジスタ 1 3 7 を画素電極 1 3 9 a 及び画素電極 1 3 9 b の間に設けることにより、第 2 の電極 1 2 5 a 及び画素電極 1 3 9 a 、並びに第 3 の電極 1 2 5 b 及び画素電極 1 3 9 b の接続距離を短くすることが可能であるため、第 2 の電極 1 2 5 a 及び画

10

20

30

40

50

素電極 139a、並びに第3の電極 125b 及び画素電極 139b の間に発生する寄生容量を低減すると共に、画素 100 における開口率の低減を防ぐことができる。

【0027】

薄膜トランジスタ 136 及び薄膜トランジスタ 137 は、ソース電極及びドレイン電極の一方である第1の電極 123 が共通している。即ち、各画素において、信号線から突出する電極が第1の電極 123 一つであり、且つ薄膜トランジスタ 136 及び薄膜トランジスタ 137 において共通であるため、走査線 103 と信号線 121 から突出された第1の電極 123 との間に発生する寄生容量を低減することができる。

【0028】

また、走査線 103 は、薄膜トランジスタ 136 及び薄膜トランジスタ 137 が形成される領域近傍においてループ形状であり、走査線 103a 及び走査線 103b となっており、開口部 126 を有する。即ち、走査線は、信号線 121 と交差する方向に延伸する領域である走査線 103 と、間に開口部 126 を挟むことでループ形状を形成する走査線 103a 及び走査線 103b とで構成される。このとき、開口部 126 を挟む走査線 103a 及び走査線 103b の幅の合計は、走査線 103 の幅以上である。また、ループ形状となっている走査線 103a 及び走査線 103b においては、走査線 103 の端部より走査線 103a 及び走査線 103b の端部が外側に突出している（図 8 (B) 参照。）。また、ループ形状を形成する走査線 103a 及び走査線 103b の間に設けられる開口部において、第1の電極 123 の一部が配置される（図 8 (C) 参照。）。走査線 103a 及び走査線 103b の幅の合計は、走査線 103 の幅以上であるため、走査線 103 から分岐した走査線 103a 及び走査線 103b において、配線抵抗の増加を防ぐことができると共に、発熱、静電破壊等による半導体装置の不良の発生を低減することができる。

【0029】

なお、図 2 (A) 及び図 8 (A) に示すように、薄膜トランジスタ 136 においては、走査線 103a 及び第1の電極 123 の重畠部において寄生容量 C4 が発生する。また、走査線 103a 及び第2の電極 125a の重畠部において寄生容量 C5 が発生する。薄膜トランジスタ 137 においては、走査線 103b 及び第1の電極 123 の重畠部において寄生容量 C6 が発生する。また、走査線 103b 及び第3の電極 125b の重畠部において寄生容量 C7 が発生する。

【0030】

ここで、比較例として、薄膜トランジスタと重畠する領域においてループ形状を有せず、直線状である走査線 203 を有し、薄膜トランジスタ 236 及び薄膜トランジスタ 237 それぞれにおいて、信号線 121 と接続する電極が異なる画素 200 の回路図を図 2 (B) に示す。図 2 (A) と同様の構成においては、同じ符号を用いて示し、構成の説明を省略する。

【0031】

図 2 (B) に示すように、画素 200 には、走査線 203 と、走査線 203 と交差する信号線 121 を有する。また、走査線 203 と同じ方向に延びる容量配線 105a 及び容量配線 105b を有する。なお、容量配線 105a と、容量配線 105b との間に、走査線 203 を有する。

【0032】

また、走査線 203 及び信号線 121 の交差部近傍に薄膜トランジスタ 236 及び薄膜トランジスタ 237 を有する。薄膜トランジスタ 236 は、走査線 203 に接続するゲート電極と、信号線 121 から突出する第1の電極と、液晶素子 142 と接続する第2の電極とを有する。また、容量素子 140 の一方の電極は、液晶素子 142 に含まれる画素電極及び薄膜トランジスタ 236 の第2の電極に接続し、容量素子 140 の他方の電極は、容量配線 105a に接続する。

【0033】

薄膜トランジスタ 237 は、走査線 203 に接続するゲート電極と、信号線 121 から突出する第3の電極と、液晶素子 143 と接続する第4の電極とを有する。また、容量素子

10

20

30

40

50

141の一方の電極は、液晶素子143に含まれる画素電極及び薄膜トランジスタ237の第4の電極に接続し、容量素子141の他方の電極は、容量配線105bに接続する。

【0034】

なお、薄膜トランジスタ236においては、走査線203及び第1の電極の重畠部において寄生容量C14が発生する。また、走査線203及び第2の電極の重畠部において寄生容量C15が発生する。薄膜トランジスタ237においては、走査線203及び第3の電極の重畠部において寄生容量C16が発生する。また、走査線203及び第4の電極の重畠部において寄生容量C17が発生する。

【0035】

薄膜トランジスタ136及び薄膜トランジスタ236のそれぞれにおいて、走査線103a、203、及び第1の電極の重畠部の面積が略同一であれば、寄生容量C4及び寄生容量C14は略同一である。また、走査線103a、203、及び第2の電極の重畠部の面積が略同一であれば、寄生容量C5及び寄生容量C15は略同一である。薄膜トランジスタ137及び薄膜トランジスタ237において、走査線103b及び第1の電極の重畠部の面積と、走査線203及び第3の電極の重畠部の面積とが略同一であれば、寄生容量C6及び寄生容量C16は略同一である。また、走査線103b及び第3の電極の重畠部の面積と、走査線203及び第4の電極の重畠部の面積とが略同一であれば、寄生容量C7及び寄生容量C17は略同一である。

【0036】

比較例である、薄膜トランジスタと重畠する領域において、ループ形状を有せず、直線状である走査線203を有する画素200は、図2(B)に示すように、走査線203及び信号線121の間ににおいて、寄生容量C11が発生している。また、薄膜トランジスタ236及び薄膜トランジスタ237において、ソース電極及びドレイン電極の一方となる電極が異なる電極(薄膜トランジスタ236においては第1の電極、薄膜トランジスタ237においては第3の電極)の場合、即ち、薄膜トランジスタ236の第1の電極及び薄膜トランジスタ237の第3の電極のそれぞれと、信号線121とが接続する場合、走査線203及び第1の電極の間に寄生容量C12が発生し、走査線203及び第3の電極の間に寄生容量C13が発生する。

【0037】

しかしながら、本実施の形態に示す走査線103は、薄膜トランジスタ136及び薄膜トランジスタ137が形成される領域近傍においてループ形状であり、図1及び図8(B)に示すように、走査線103a及び走査線103bとなっており、開口部126を有する。また、ループ形状である走査線103a及び走査線103bの間に設けられる開口部126において、第1の電極123が配置している(図8(C)参照。)。このため、当該領域における第1の電極123において、走査線との寄生容量は生じていない。即ち、図8(A)における寄生容量C3はゼロである。なお、走査線103a及び信号線121の間、並びに走査線103b及び信号線121の間ににおいては、それぞれ寄生容量C1及び寄生容量C2が生じている。

【0038】

また、走査線103a及び走査線103bの幅の合計を走査線203の幅と、概略同一とすると、画素200における寄生容量C11と、画素100における寄生容量C1及び寄生容量C2の合計とは、略同一とすることが可能であるため、画素100と比較して、画素200においては、寄生容量C12及び寄生容量C13が多い。

【0039】

また、図1及び図2(A)に示す画素100において、薄膜トランジスタ136及び薄膜トランジスタ137は、ソース電極及びドレイン電極の一方である第1の電極123が共通している(図8(C)参照)。このため、第1の電極123において、抵抗が生じる。

【0040】

しかしながら、図2(B)に示すような、薄膜トランジスタ236及び薄膜トランジスタ237において、ソース電極及びドレイン電極の一方となる電極が異なる電極の場合、即

10

20

30

40

50

ち、薄膜トランジスタ 236 の第 1 の電極及び薄膜トランジスタ 237 の第 3 の電極のそれぞれと、信号線 121 とが接続する場合、薄膜トランジスタ 236 の第 1 の電極及び薄膜トランジスタ 237 の第 3 の電極のそれぞれにおいて、抵抗が生じる。

【0041】

これらのことから、図 1 及び図 2 (A) に示すように、信号線 121 から突出した第 1 の電極 123 を、薄膜トランジスタ 136 及び薄膜トランジスタ 137 それぞれのソース電極及びドレイン電極の一方とすることで、走査線 103 及び第 1 の電極 123 の重畠面積を低減することが可能であり、配線幅を広げることなく、即ち、開口率を維持しつつ、走査線 103 及び第 1 の電極 123 の間に生じる寄生容量を低減することができる。なお、ここでは、走査線 103a 及び走査線 103b の幅の合計を走査線 203 の幅と、概略同一としたが、走査線 103a 及び走査線 103b の幅の合計は、走査線 103 の幅以上であればよい。この結果、画素における走査線の抵抗の増加を防ぐことができる。

10

【0042】

また、図 1 に示す画素 100 において、信号線 121、第 1 の電極 123、第 2 の電極 125a、及び第 3 の電極 125b と、走査線 103a、走査線 103b、容量配線 105a、及び容量配線 105b とが交差する領域近傍において、信号線 121、第 1 の電極 123、第 2 の電極 125a、及び第 3 の電極 125b と、走査線 103a、走査線 103b、容量配線 105a、及び容量配線 105b との交差部の外側に、半導体膜 135 の端部が位置する。即ち、走査線 103a 及び信号線 121、走査線 103b 及び信号線 121、容量配線 105a 及び信号線 121、容量配線 105b 及び信号線 121、走査線 103a 及び第 1 の電極 123、走査線 103a 及び第 2 の電極 125a、走査線 103b 及び第 3 の電極 125b の間ににおいて、ゲート絶縁膜のみでなく、半導体膜 135 が形成されるため、配線間の寄生容量を低減できる。

20

【0043】

なお、本実施の形態に示す薄膜トランジスタは、第 1 の電極 123 を間として、第 2 の電極 125a 及び第 3 の電極 125b が設けられている。このため、第 1 の電極 123 から第 2 の電極 125a に流れる電流の方向と、第 1 の電極 123 から第 3 の電極 125b に流れる電流の方向が反対である。画素を 2 分割し、それぞれにチャネル方向（電流の流れる方向）の異なる薄膜トランジスタを設けることにより、半導体膜 135 の結晶性のばらつきを原因とする、画素ごとの薄膜トランジスタの電気特性のばらつきを低減することができる。また、薄膜トランジスタ 136 及び薄膜トランジスタ 137 において、共通の半導体膜を有するため、薄膜トランジスタ 136 及び薄膜トランジスタ 137 において、第 1 の電極 123 及び半導体膜が接する領域を共有することができる。この結果、画素 100 における薄膜トランジスタ 136 及び薄膜トランジスタ 137 の専有面積を低減することができる。

30

【0044】

なお、本実施の形態においては、一画素に 2 つの薄膜トランジスタを設けた構造を示したが、これに限定されない。一画素に 3 つ以上の複数の薄膜トランジスタ及び当該薄膜トランジスタに接続する複数の画素電極を有してもよい。

40

【0045】

次に、薄膜トランジスタ及び容量素子の構造について、図 3 を用いて説明する。

【0046】

図 3 (A) は、図 1 に示す一点鎖線 A - B における薄膜トランジスタ 136 の断面構造である。

【0047】

薄膜トランジスタ 136 は、基板 101 上に、走査線 103 と、半導体膜 135 と、走査線 103 及び半導体膜 135 の間に設けられるゲート絶縁膜 107 と、半導体膜 135 に接するソース領域及びドレイン領域として機能する不純物半導体膜 127 及び不純物半導体膜 129 と、不純物半導体膜 127 に接する第 1 の電極 123 と、不純物半導体膜 129 に接する第 2 の電極 125a とを有する。また、ゲート絶縁膜 107、半導体膜 135

50

、不純物半導体膜 127、不純物半導体膜 129、第1の電極 123、及び第2の電極 125aを覆う絶縁膜 138が形成される。また、絶縁膜 138の開口部において第2の電極 125aと接続する画素電極 139aが形成される。

【0048】

基板 101としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス等の金属の基板の表面に絶縁膜を設けたものを用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス若しくはアルミニケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、基板 101のサイズに限定はなく、例えば液晶表示装置でよく使われる第3世代乃至第10世代のガラス基板を用いることができる。

10

【0049】

走査線 103の一部は薄膜トランジスタ 136のゲート電極として機能する。走査線 103は、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム、ニッケル等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、Ag-Pd-Cu合金、Al-Nd合金、Al-Ni合金などを用いてもよい。

【0050】

例えば、走査線 103の二層の積層構造としては、アルミニウム膜上にモリブデン膜を積層した二層の積層構造、または銅膜上にモリブデン膜を積層した二層構造、または銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、窒化チタン膜とモリブデン膜とを積層した二層構造、酸素を含む銅-マグネシウム合金膜と銅膜とを積層した二層構造、酸素を含む銅-マンガン合金膜と銅膜とを積層した二層構造、銅-マンガン合金膜と銅膜とを積層した二層構造などとすることが好ましい。三層の積層構造としては、タンゲステン膜または窒化タンゲステン膜と、アルミニウムとシリコンの合金膜またはアルミニウムとチタンの合金膜と、窒化チタン膜またはチタン膜とを積層した三層構造とすることが好ましい。電気的抵抗が低い膜上にバリア膜として機能する金属膜が積層されることで、電気的抵抗を低くでき、且つ金属膜から半導体膜への金属元素の拡散を防止することができる。

20

【0051】

なお、走査線 103と同時に、容量配線 105a及び容量配線 105bが形成される。このため、容量配線 105a及び容量配線 105bは、走査線 103と同様の材料及び積層構造を有する。

【0052】

ゲート絶縁膜 107は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、または窒化酸化アルミニウム膜を、単層でまたは積層して形成することができる。なお、ゲート絶縁膜 107において、半導体膜 135が微結晶シリコン膜の場合、半導体膜 135と接する層を、酸化シリコン膜、酸化アルミニウム膜等の酸化物膜で形成することで、半導体膜 135との界面の窒素濃度を低減できるため、薄膜トランジスタの電気特性の信頼性を高めることができる。

30

【0053】

なお、ここでは、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法 (RBS: Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS: Hydrogen Forward Scattering Spectrometry) を用いて測定した場合に、組成範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、シリコンが 25 ~ 35 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有

40

50

量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、組成範囲として酸素が5～30原子%、窒素が20～55原子%、シリコンが25～35原子%、水素が10～30原子%の範囲で含まれるものという。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0054】

半導体膜135は、シリコンまたはシリコングルマニウムを用いて形成する。または、酸化物半導体を用いて形成する。酸化物半導体の代表例としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O膜や、三元系金属酸化物であるIn-Ga-Zn-O膜、In-Sn-Zn-O膜、In-Al-Zn-O膜、Sn-Ga-Zn-O膜、Al-Ga-Zn-O膜、Sn-Al-Zn-O膜や、二元系金属酸化物であるIn-Zn-O膜、Sn-Zn-O膜、Al-Zn-O膜、In-Ga-O膜などを用いることができる。10

【0055】

また、半導体膜135は、上記半導体材料のいずれかを用いた、非晶質半導体、微結晶半導体、または結晶性半導体を、単層または積層して形成することができる。

【0056】

なお、微結晶半導体とは、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体である。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、混相粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状または針状の混相粒が基板表面に対して法線方向に成長している。このため、柱状または針状の混相粒の界面には、粒界が形成される場合もある。20

【0057】

微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520cm<sup>-1</sup>より低波数側に、シフトしている。即ち、単結晶シリコンを示す520cm<sup>-1</sup>とアモルファスシリコンを示す480cm<sup>-1</sup>の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダングリングボンド）を終端するため水素またはハロゲンを少なくとも1原子%含んでいる。さらに、ヘリウム、アルゴン、ネオン、クリプトン、キセノンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。30

【0058】

ここでは、半導体膜135として、微結晶半導体領域131及び非晶質半導体領域133の積層構造を適用する。

【0059】

微結晶半導体領域131は表面が鋭角な凹凸状であり、凸部はゲート絶縁膜107から非晶質半導体領域133に向かって、先端が狭まる（凸部の先端が鋭角である）凸状（錐形状）である。なお、微結晶半導体領域131の凹凸の形状は、ゲート絶縁膜107から非晶質半導体領域133に向かって幅が広がる凸状（逆錐形状）であってもよい。

【0060】

微結晶半導体領域131において、少なくとも凸部の領域は、窒素濃度の高い領域である。また、微結晶半導体領域131に含まれる結晶粒界に、NH基またはNH<sub>2</sub>基を有してもよい。二次イオン質量分析法によって計測される微結晶半導体領域131の凸部の領域に含まれる窒素の濃度を、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{20}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$  atoms/cm<sup>3</sup>以下とすることで、錐形状または逆錐形状を含む凹凸を形成することが可能である。40

【0061】

非晶質半導体領域133は、窒素を有する非晶質半導体で形成される。窒素を有する非晶質半導体に含まれる窒素は、例えばNH基またはNH<sub>2</sub>基として存在していてよい。非50

晶質半導体としては、アモルファスシリコンを用いて形成する。

【0062】

窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、CPM (Constant photocurrent method) やフォトルミネッセンス分光測定で測定される Urbach 端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体である。即ち、窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体である。窒素を含む非晶質半導体は、価電子帯のバンド端における準位のテール(裾)の傾きが急峻であるため、バンドギャップが広くなり、トンネル電流が流れにくく。このため、窒素を含む非晶質半導体を、微結晶半導体領域 131 と不純物半導体膜 127 及び不純物半導体膜 129 との間に設けることで、薄膜トランジスタのオフ電流を低減することができる。また、窒素を含む非晶質半導体を設けることで、オン電流と電界効果移動度を高めることが可能である。

【0063】

さらに、窒素を含む非晶質半導体は、低温フォトルミネッセンス分光によるスペクトルのピーク領域が、1.31 eV 以上 1.39 eV 以下である。なお、微結晶半導体、代表的には微結晶シリコンを低温フォトルミネッセンス分光により測定したスペクトルのピーク領域は、0.98 eV 以上 1.02 eV 以下であり、窒素を含む非晶質半導体は、微結晶半導体とは異なるものである。

【0064】

また、非晶質半導体領域 133 に、粒径が 1 nm 以上 10 nm 以下、好ましくは 1 nm 以上 5 nm 以下の半導体結晶粒を含ませることで、更に薄膜トランジスタのオン電流と電界効果移動度を高めることができる。

【0065】

不純物半導体膜 127 及び不純物半導体膜 129 は、必要に応じて設ければよい。例えば、半導体膜をシリコン膜またはシリコンゲルマニウム膜で形成する場合であって、且つ n チャネル型薄膜トランジスタの場合は、リンが添加されたアモルファスシリコン、リンが添加された微結晶シリコン等を用いて形成する。また、リンが添加されたアモルファスシリコン及びリンが添加された微結晶シリコンの積層構造とすることもできる。なお、p チャネル型薄膜トランジスタの場合は、不純物半導体膜 127 及び不純物半導体膜 129 は、ホウ素が添加された微結晶シリコン、ホウ素が添加されたアモルファスシリコン等を用いて形成する。

【0066】

第 1 の電極 123 及び第 2 の電極 125a は、アルミニウム、銅、チタン、ネオジム、スカンジウム、モリブデン、クロム、タンタル若しくはタンゲステン等により単層で、または積層して形成することができる。または、ヒロック防止元素が添加されたアルミニウム合金（走査線 103 に用いることができる Al - Nd 合金等）により形成してもよい。ドナーとなる不純物元素を添加した結晶性シリコンを用いてもよい。ドナーとなる不純物元素が添加された結晶性シリコンと接する側の膜を、チタン、タンタル、モリブデン、タンゲステンまたはこれらの元素の窒化物により形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としてもよい。更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タンゲステンまたはこれらの元素の窒化物で挟んだ積層構造としてもよい。

【0067】

なお、第 1 の電極 123 及び第 2 の電極 125a と同時に、第 3 の電極 125b が形成される。このため、第 3 の電極 125b は、第 1 の電極 123 及び第 2 の電極 125a と同様の材料及び積層構造を有する。また、第 1 の電極 123 は、信号線 121 の一部が突出した領域である。このため、信号線 121 は、第 1 の電極 123 と同様の材料及び積層構造を有する。

【0068】

10

20

30

40

50

絶縁膜 138 は、ゲート絶縁膜 107 と同様の材料を適宜用いることができる。なお、絶縁膜 138 を積層構造とする場合は、半導体膜 135 に接する層を、酸化シリコン膜、酸化アルミニウム膜等の酸化物膜で形成することが好ましい。これは、絶縁膜 138 上にバックゲート電極を設ける場合、半導体膜 135 において絶縁膜 138 に接する領域はチャネル領域として機能する。チャネル領域における窒素濃度を低減させることで、薄膜トランジスタの信頼性を高めることができるためである。

【0069】

画素電極 139a は、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料や、グラフェンを用いて形成することができる。

10

【0070】

画素電極 139a と同時に、画素電極 139b が形成される。このため、画素電極 139b は、画素電極 139a と同様の材料及び積層構造を有する。

【0071】

図 3 (B) は、図 1 に示す一点鎖線 C - D における容量素子の断面構造である。

【0072】

容量素子 140 は、基板 101 上に、容量配線 105a と、第 2 の電極 125a と、容量配線 105a 及び第 2 の電極 125a の間に設けられるゲート絶縁膜 107 とで構成される。また、ゲート絶縁膜 107 及び第 2 の電極 125a を覆う絶縁膜 138 が形成される。また、絶縁膜 138 上に第 2 の電極 125a と接続する画素電極 139a が形成される。

20

【0073】

なお、図示しないが、薄膜トランジスタ 137 は、薄膜トランジスタ 136 と同様の構造で構成される。また、薄膜トランジスタ 137 に接続する容量素子 141 は、容量素子 140 と同様の構造で構成される。

【0074】

本実施の形態により、マルチドメイン構造の液晶表示装置において、走査線及び信号線の間、薄膜トランジスタの走査線と、ソース電極及びドレイン電極の一方との寄生容量を低減することができる。このため、大型である液晶表示装置、高速駆動が可能な液晶表示装置、解像度の高い液晶表示装置において、表示品質を向上させることができる。また、液晶表示装置の消費電力を低減することができる。

30

【0075】

なお、本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【0076】

(実施の形態 2)

本実施の形態では、配線容量を低減した液晶表示装置において、実施の形態 1 と異なる構造を有する一画素の構成について、図 4 及び図 5 を用いて説明する。なお、本実施の形態では、1 画素に複数のサブ画素を設けた画素を、画素 150 として説明するがこれに限定されるものではない。

40

【0077】

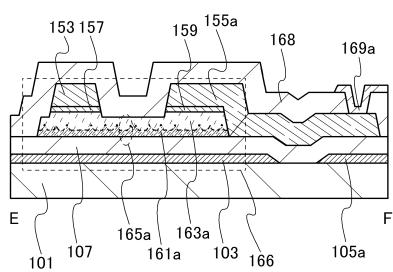

図 4 は、本実施の形態に示すマルチドメイン構造の液晶表示装置の一画素 150 の上面図であり、図 5 は、図 4 に示す一点鎖線 E - F の断面図を示す。

【0078】

図 4 に示すように、画素 150 には、走査線 103 と、走査線 103 と交差する信号線 151 とを有する。また、走査線 103 と同じ方向に延びる容量配線 105a 及び容量配線 105b を有する。なお、容量配線 105a と、容量配線 105b との間に、走査線 103 を有する。

50

## 【0079】

また、走査線 103 及び信号線 151 の交差部近傍に薄膜トランジスタ 166 及び薄膜トランジスタ 167 を有する。薄膜トランジスタ 166 は、走査線 103 に重畳する半導体膜 165a と、半導体膜 165a と重畳する第 1 の電極 153 及び第 2 の電極 155a とを有する。第 1 の電極 153 は、信号線 151 から突出した領域である。第 1 の電極 153 及び第 2 の電極 155a は、薄膜トランジスタ 166 においてソース電極及びドレイン電極として機能する。

## 【0080】

薄膜トランジスタ 167 は、走査線 103 に重畳する半導体膜 165b と、半導体膜 165b と重畳する第 1 の電極 153 及び第 3 の電極 155b とを有する。第 1 の電極 153 及び第 3 の電極 155b は、薄膜トランジスタ 167 においてソース電極及びドレイン電極として機能する。

10

## 【0081】

薄膜トランジスタ 166 に含まれる第 2 の電極 155a は、画素電極 169a と接続される。また、容量配線 105a と、第 2 の電極 155a 及び画素電極 169a のそれぞれ一部とが重畳している。容量配線 105a、ゲート絶縁膜、及び第 2 の電極 155a により容量素子を構成する。

## 【0082】

薄膜トランジスタ 167 に含まれる第 3 の電極 155b は、画素電極 169b と接続される。また、容量配線 105b と、第 3 の電極 155b 及び画素電極 169b のそれぞれ一部とが重畳している。容量配線 105b、ゲート絶縁膜、及び第 3 の電極 155b により容量素子を構成する。即ち、薄膜トランジスタ 166 及び薄膜トランジスタ 167 は、薄膜トランジスタ 136 及び薄膜トランジスタ 137 と同様に、上面形状において画素 150 の略中央に位置し、画素 150 における各サブ画素の画素電極 169a 及び画素電極 169b の間に形成される。このため、第 2 の電極 155a 及び画素電極 169a、並びに第 3 の電極 155b 及び画素電極 169b の間に発生する寄生容量を低減すると共に、画素 150 における開口率の低減を防ぐことができる。

20

## 【0083】

薄膜トランジスタ 166 及び薄膜トランジスタ 167 は、ソース電極及びドレイン電極の一方である第 1 の電極 153 が共通している。即ち、各画素において、信号線から突出する電極が第 1 の電極 153 一つであり、且つ薄膜トランジスタ 166 及び薄膜トランジスタ 167 において共通であるため、走査線 103 と信号線 151 から突出された第 1 の電極 153 との間に発生する寄生容量を低減することができる。

30

## 【0084】

また、走査線 103 は、薄膜トランジスタ 166 及び薄膜トランジスタ 167 が形成される領域近傍においてループ形状であり、走査線 103a 及び走査線 103b となっている。また、ループ形状である走査線 103a 及び走査線 103b との間に設けられる開口部において、第 1 の電極 153 の一部が配置される。このため、薄膜トランジスタ 166 及び薄膜トランジスタ 167 それぞれに、ソース電極及びドレイン電極の一方が設けられる場合と比較して、走査線 103 及び第 1 の電極 153 の重畳面積を低減することが可能であり、走査線 103 及び第 1 の電極 153 の間に生じる寄生容量を低減することができる。また、走査線 103a 及び走査線 103b の幅の合計は、走査線 103 の幅以上であるため、走査線 103 から分岐した走査線 103a 及び走査線 103b において、配線抵抗の増加を防ぐことができると共に、発熱、静電破壊等による半導体装置の不良の発生を低減することができる。

40

## 【0085】

これらのことから、走査線 103 及び第 1 の電極 153 の重畳面積を低減することが可能であり、配線幅を広げることなく、即ち、開口率を維持しつつ、走査線 103 及び第 1 の電極 153 の間に生じる寄生容量を低減することができる。また、画素における抵抗を低減することができる。

50

## 【0086】

また、図4に示す画素150において、走査線103a及び信号線151、走査線103b及び信号線151、容量配線105a及び信号線151、並びに容量配線105b及び信号線151の間ににおいて、半導体膜165cが設けられている。また、走査線103a及び信号線151、走査線103b及び信号線151、容量配線105a及び信号線151、並びに容量配線105b及び信号線151それぞれの交差部より外側に、半導体膜165cの端部が位置する。このため、上記配線間には、ゲート絶縁膜のみでなく、半導体膜165cが形成されるため、配線間の寄生容量を低減できる。なお、半導体膜165cの端部は、走査線103の一端部と重畳しているため、走査線103の一端部及び第1の電極153の一部における寄生容量を低減している。

10

## 【0087】

また、薄膜トランジスタ166及び薄膜トランジスタ167のそれぞれにおいて、半導体膜165a及び半導体膜165bの端部は、走査線103の内側に位置する。このため、半導体膜165a及び半導体膜165bへのバックライトや外光の照射を低減することができる、薄膜トランジスタ166及び薄膜トランジスタ167の光リーク電流を低下することができる。

## 【0088】

なお、本実施の形態に示す薄膜トランジスタは、上面形状において、第1の電極153の一方の辺側に、第2の電極155a及び第3の電極155bが設けられている。即ち、第2の電極155a及び第3の電極155bと、信号線151との間に、信号線から突出する第1の電極153が設けられる。このため、第1の電極153及び第2の電極155aの間に流れる電流の方向と、第1の電極153及び第3の電極155bの間に流れる電流の方向とが略一致する。半導体膜が微結晶半導体膜または結晶性半導体膜の場合、結晶の配向方向と、上記電流の流れる方向を略一致させることで、薄膜トランジスタの電気特性を向上させることができる。また、薄膜トランジスタ166及び薄膜トランジスタ167が有する半導体膜がそれぞれ異なるため、薄膜トランジスタ同士におけるリーク電流が少なく、更には、一方の薄膜トランジスタの電気特性が悪くとも、一方の薄膜トランジスタの電気特性が他方の薄膜トランジスタの電気特性に影響しないため、画素間の電気特性のムラを低減することができる。

20

## 【0089】

30

なお、本実施の形態においては、一画素に2つの薄膜トランジスタを設けた構造を示したが、これに限定されない。一画素に3つ以上の複数の薄膜トランジスタ及び当該薄膜トランジスタに接続する複数の画素電極を有してもよい。

## 【0090】

次に、薄膜トランジスタの構造について、図5を用いて説明する。

## 【0091】

図5は、図4に示す一点鎖線E-Fにおける薄膜トランジスタ166の断面構造である。

## 【0092】

薄膜トランジスタ166は、基板101上に、走査線103と、半導体膜165aと、走査線103及び半導体膜165aの間に設けられるゲート絶縁膜107と、半導体膜165aに接するソース領域及びドレイン領域として機能する不純物半導体膜157及び不純物半導体膜159と、不純物半導体膜157に接する第1の電極153と、不純物半導体膜159に接する第2の電極155aとを有する。また、ゲート絶縁膜107、半導体膜165a、不純物半導体膜157、不純物半導体膜159、第1の電極153、及び第2の電極155aを覆う絶縁膜168が形成される。また、絶縁膜168の開口部において第2の電極155aと接続する画素電極169aが形成される。

40

## 【0093】

半導体膜165aは、実施の形態1に示す半導体膜135と同様の材料及び構造を適宜用いることができる。

## 【0094】

50

なお、半導体膜 165a と同時に、半導体膜 165b が形成される。このため、半導体膜 165b は、半導体膜 165a と同様の材料及び積層構造を有する。

【0095】

不純物半導体膜 157 及び不純物半導体膜 159 は、必要に応じて設ければよい。また、不純物半導体膜 157 及び不純物半導体膜 159 を設ける場合は、実施の形態 1 に示す不純物半導体膜 127 及び不純物半導体膜 129 と同様の材料及び構造を適宜用いることができる。

【0096】

第 1 の電極 153 及び第 2 の電極 155a は、実施の形態 1 に示す第 1 の電極 123 及び第 2 の電極 125a と同様の材料及び構造を適宜用いることができる。

10

【0097】

なお、第 1 の電極 153 及び第 2 の電極 155a と同時に、第 3 の電極 155b が形成される。このため、第 3 の電極 155b は、第 1 の電極 153 及び第 2 の電極 155a と同様の材料及び積層構造を有する。また、第 1 の電極 153 は、信号線 151 の一部が突出した領域である。このため、信号線 151 は、第 1 の電極 153 と同様の材料及び積層構造を有する。

【0098】

絶縁膜 168 は、実施の形態 1 に示す絶縁膜 138 と同様の材料及び構造を適宜用いることができる。

20

【0099】

画素電極 169a は、実施の形態 1 に示す画素電極 139a と同様の材料及び構造を適宜用いることができる。

【0100】

なお、画素電極 169a と同時に、画素電極 169b が形成される。このため、画素電極 169b は、画素電極 169a と同様の材料及び積層構造を有する。

【0101】

本実施の形態により、マルチドメイン構造の液晶表示装置において、走査線及び信号線の間、薄膜トランジスタの走査線と、ソース電極及びドレイン電極の一方との寄生容量を低減することができる。このため、大型である液晶表示装置、高速駆動が可能な液晶表示装置、解像度の高い液晶表示装置において、表示品質を向上させることができる。また、液晶表示装置の消費電力を低減することができる。

30

【0102】

なお、本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【0103】

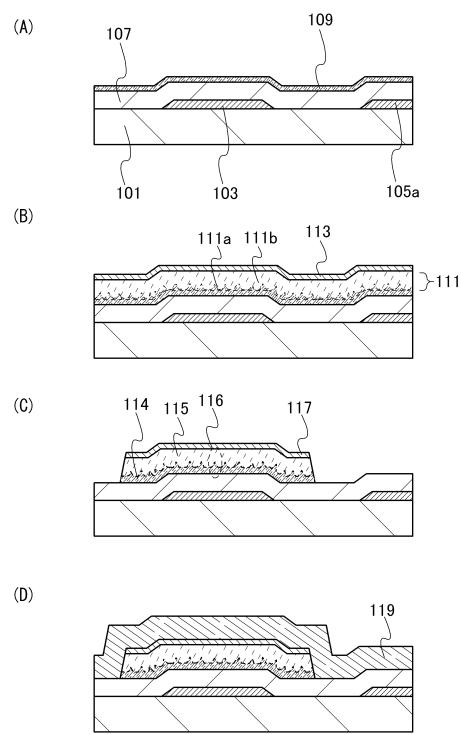

(実施の形態 3)

本実施の形態では、実施の形態 1 及び実施の形態 2 に示す薄膜トランジスタの作製方法について、図 6 及び図 7 を用いて説明する。なお、ここでは、実施の形態 1 に示す薄膜トランジスタ 136 の作製方法を説明するが、適宜実施の形態 1 に示す薄膜トランジスタ 137、実施の形態 2 に示す薄膜トランジスタ 166 及び薄膜トランジスタ 167 に適用することができる。なお、薄膜トランジスタは、p 型よりも n 型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができ、好ましい。そのため、本実施の形態では、n 型の薄膜トランジスタの作製方法について説明する。

40

【0104】

図 6 (A) に示すように、基板 101 上に走査線 103 を形成する。次に、走査線 103 を覆うゲート絶縁膜 107 を形成し、ゲート絶縁膜 107 上に微結晶半導体膜 109 を形成する。

【0105】

走査線 103 は、基板 101 上に、スパッタリング法または真空蒸着法を用いて、上記し

50

た材料により導電膜を形成し、該導電膜上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電膜をエッチングして形成することができる。また、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、走査線 103 及び基板 101 の密着性向上を目的として、上記の金属材料の窒化物膜を、基板 101 と、走査線 103 との間に設けてもよい。ここでは、基板 101 上に導電膜を形成し、フォトリソグラフィ工程により形成したレジストで形成されるマスクを用いて、当該導電膜をエッチングする。

#### 【0106】

なお、走査線 103 の側面は、テーパー形状とすることが好ましい。これは、後の工程で、走査線 103 上に形成される絶縁膜、半導体膜及び配線が、走査線 103 の段差箇所において切断されないようにするためである。走査線 103 の側面をテーパー形状にするためには、レジストで形成されるマスクを後退させつつエッチングを行えばよい。

10

#### 【0107】

また、走査線 103 を形成する工程により、容量配線 105a 及び容量配線 105b を同時に形成することができる。

#### 【0108】

ゲート絶縁膜 107 は、CVD 法またはスパッタリング法等を用いて形成することができる。ゲート絶縁膜 107 を形成する際のグロー放電プラズマの生成は、3 MHz から 30 MHz、代表的には 13.56 MHz、27.12 MHz の HF 帯の高周波電力、または 30 MHz より大きく 300 MHz 程度までの VHF 帯の高周波電力、代表的には、60 MHz を印加することで行われる。また、1 GHz 以上のマイクロ波の高周波電力を印加することで行われる。なお、高周波電力がパルス状に印加されるパルス発振や、連続的に印加される連続発振とすることができます。また、HF 帯の高周波電力と、VHF 帯の高周波電力とを重畠させることで、大面積基板においてもプラズマのムラを低減し、均一性を高めることができると共に、堆積速度を高めることができる。高周波数が 1 GHz 以上であるマイクロ波プラズマ CVD 装置を用いてゲート絶縁膜 107 を形成すると、ゲート電極と、ドレイン電極及びソース電極との間の耐圧を向上させることができると、信頼性の高い薄膜トランジスタを得ることができる。

20

#### 【0109】

また、ゲート絶縁膜 107 として、有機シランガスを用いた CVD 法により酸化シリコン膜を形成することで、後に形成する半導体膜の結晶性を高めることができると共に、薄膜トランジスタのオン電流及び電界効果移動度を高めることができる。有機シランガスとしては、テトラメチルシラン (TMS : 化学式 Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン (TMC TS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン (SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン (SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>) 等のシリコン含有化合物を用いることができる。

30

#### 【0110】

微結晶半導体膜 109 は、プラズマ CVD 装置の反応室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合し、グロー放電プラズマにより形成する。または、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスとを混合し、グロー放電プラズマにより形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を 50 倍以上 1000 倍以下にして堆積性気体を希釈する条件により、微結晶シリコン、微結晶シリコンゲルマニウム等を形成する。このときの堆積温度は、室温～350 とすることが好ましく、より好ましくは 150～280 とする。なお、上部電極及び下部電極の間隔は、プラズマが発生しうる間隔とすればよい。

40

#### 【0111】

シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、GeH<sub>4</sub>、Ge<sub>2</sub>H<sub>6</sub> 等がある。

50

## 【0112】

なお、微結晶半導体膜109の原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを添加することで、微結晶半導体膜109の成膜速度が高まる。この結果、成膜速度が高まることで、微結晶半導体膜109に混入される不純物量が低減する。また、高いパワーを供給せずとも安定したプラズマを発生させることが可能である。これらの結果、微結晶半導体膜109のプラズマダメージを低減することが可能であり、微結晶半導体膜109の結晶性を高めることができる。

## 【0113】

微結晶半導体膜109のCVD法による形成工程において、グロー放電プラズマの生成は、ゲート絶縁膜107形成の際のグロー放電プラズマの生成条件を適宜用いることができる。

10

## 【0114】

次に、図6(B)に示すように、微結晶半導体膜109上に半導体膜111を形成する。半導体膜111は、微結晶半導体領域111a及び非晶質半導体領域111bで構成される。次に、半導体膜111上に、不純物半導体膜113を形成する。次に、不純物半導体膜113上にマスクを形成する。

## 【0115】

微結晶半導体膜109を種結晶として、部分的に結晶成長させる条件(結晶成長を低減する条件)で、微結晶半導体領域111a及び非晶質半導体領域111bを有する半導体膜111を形成することができる。

20

## 【0116】

半導体膜111は、プラズマCVD装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを混合し、グロー放電プラズマにより形成する。窒素を含む気体としては、アンモニア、窒素、フッ化窒素、塩化窒素、クロロアミン、フルオロアミン等がある。グロー放電プラズマの生成は、ゲート絶縁膜107と同様にすることができる。

## 【0117】

このとき、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比は、微結晶半導体膜109と同様に微結晶半導体膜を形成する流量比を用い、さらに原料ガスに窒素を含む気体を用いる条件とすることで、微結晶半導体膜109の堆積条件よりも、結晶成長を低減することができる。具体的には、半導体膜111の堆積初期においては、原料ガスに窒素を含む気体が含まれるため、部分的に結晶成長が抑制され、錐形状の微結晶半導体領域が成長すると共に、非晶質半導体領域が形成される。さらに、堆積中期または後期では、錐形状の微結晶半導体領域の結晶成長が停止し、非晶質半導体領域のみが堆積される。この結果、半導体膜111において、微結晶半導体領域111a、及び欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体膜で形成される非晶質半導体領域111bを形成することができる。

30

## 【0118】

ここでは、半導体膜111を形成するガス流量条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量が10~2000倍、好ましくは10~200倍である。なお、通常の非晶質半導体膜を形成するガス流量条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量は0~5倍である。

40

## 【0119】

また、半導体膜111の原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを導入することで、成膜速度を高めることができる。

## 【0120】

半導体膜111の厚さは、厚さ50~350nmとすることが好ましく、さらに好ましくは120~250nmとする。

## 【0121】

ここでは、半導体膜111の原料ガスに窒素を含む気体を含ませて、微結晶半導体領域1

50

11a 及び非晶質半導体領域 111b を有する半導体膜 111 を形成したが、他の半導体膜 111 の形成方法として、微結晶半導体膜 109 の表面を窒素を含む気体に曝して、微結晶半導体膜 109 の表面に窒素を吸着させた後、シリコンまたはゲルマニウムを含む堆積性気体及び水素を原料ガスとして、微結晶半導体領域 111a 及び非晶質半導体領域 111b を有する半導体膜 111 を形成することができる。

【0122】

不純物半導体膜 113 は、プラズマ CVD 装置の反応室内において、シリコンを含む堆積性気体と、水素と、ホスフィン（水素希釈またはシラン希釈）とを混合したグロー放電プラズマにより、リンが添加されたアモルファスシリコン、またはリンが添加された微結晶シリコンを形成する。なお、p 型の薄膜トランジスタを作製する場合は、不純物半導体膜 113 として、ホスフィンの代わりに、ジボランを用いて、グロー放電プラズマにより、ボロンが添加されたアモルファスシリコン、またはボロンが添加された微結晶シリコンを形成すればよい。

10

【0123】

また、不純物半導体膜 113 を、リンが添加された微結晶シリコン、またはホウ素が添加された微結晶シリコンで形成する場合は、半導体膜 111 と、不純物半導体膜 113 との間に、微結晶半導体膜、代表的には微結晶シリコン膜を形成することで、界面の特性を向上させることができる。この結果、不純物半導体膜 113 と、半導体膜 111 との界面に生じる抵抗を低減することができる。この結果、薄膜トランジスタのソース領域、半導体膜、及びドレイン領域を流れる電流量を増加させ、オン電流及び電界効果移動度の増加が可能となる。

20

【0124】

マスクはフォトリソグラフィ工程により形成することができる。

【0125】

次に、マスクを用いて、微結晶半導体膜 109、半導体膜 111、及び不純物半導体膜 113 をエッティングする。この工程により、微結晶半導体膜 109、半導体膜 111、及び不純物半導体膜 113 を素子毎に分離し、半導体膜 116 及び不純物半導体膜 117 を形成する。なお、半導体膜 116 は、微結晶半導体膜 109 及び半導体膜 111 の微結晶半導体領域 111a それぞれ一部を含む微結晶半導体領域 114 と、半導体膜 111 の非晶質半導体領域 111b の一部を含む非晶質半導体領域 115 とを有する。この後、マスクを除去する（図 6 (C) 参照。）。

30

【0126】

次に、不純物半導体膜 117 上に導電膜 119 を形成する（図 6 (D) 参照。）。導電膜 119 は、CVD 法、スパッタリング法または真空蒸着法を用いて形成する。

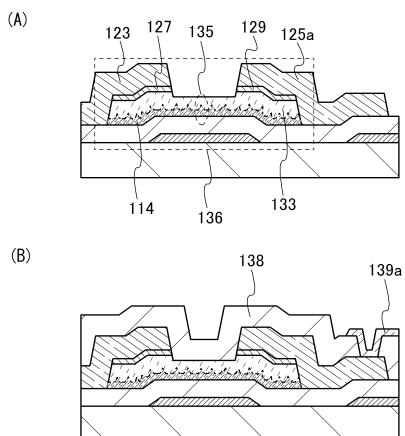

【0127】

次に、フォトリソグラフィ工程によりレジストで形成されるマスクを形成し、当該レジストで形成されるマスクを用いて導電膜 119 をエッティングして、ソース電極及びドレイン電極として機能する第 1 の電極 123 及び第 2 の電極 125a を形成する。導電膜 119 のエッティングはドライエッティングまたはウェットエッティングを用いることができる。または、第 1 の電極 123 及び第 2 の電極 125a は、銀、金または銅等の導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法等を用いて吐出し、焼成することで形成しても良い。なお、当該工程において、第 3 の電極 125b 及び信号線 121 を形成する。

40

【0128】

次に、不純物半導体膜 117 及び半導体膜 116 の一部をエッティングして、ソース領域及びドレイン領域として機能する不純物半導体膜 127 及び不純物半導体膜 129 を形成する。また、微結晶半導体領域 114 及び凹部を有する非晶質半導体領域 133 を有する半導体膜 135 を形成する。

【0129】

ここでは、第 1 の電極 123 及び第 2 の電極 125a の端部と、不純物半導体膜 127 及

50

び不純物半導体膜129の端部とが揃っているが、第1の電極123及び第2の電極125aの端部と、不純物半導体膜127及び不純物半導体膜129の端部とがずれ、断面において、第1の電極123及び第2の電極125aの端部が、不純物半導体膜127及び不純物半導体膜129の端部より内側に位置してもよい。

【0130】

次に、ドライエッチングを行ってもよい。ドライエッチングの条件は、非晶質半導体領域133にダメージが入らず、且つ非晶質半導体領域133に対するエッチング速度が低い条件を用いる。エッチングガスとしては、代表的にはCl<sub>2</sub>、CF<sub>4</sub>、またはN<sub>2</sub>等を用いる。また、エッチング方法については特に限定はなく、誘導結合型プラズマ( ICP : Inductively Coupled Plasma )方式、容量結合型プラズマ( CCP : Capacitively Coupled Plasma )方式、電子サイクロン共鳴プラズマ( ECR : Electron Cyclotron Resonance )方式、反応性イオンエッチング( RIE : Reactive Ion Etching )方式等を用いることができる。

【0131】

次に、非晶質半導体領域133の表面にプラズマ処理、代表的には水プラズマ処理、酸素プラズマ処理、オゾンプラズマ処理、N<sub>2</sub>Oプラズマ処理、酸素及び水素の混合ガスによるプラズマ処理等の酸化ガス雰囲気によるプラズマ処理を行う。この後、マスクを除去する。なお、当該マスクの除去は、不純物半導体膜117及び半導体膜116のドライエッチング前に行ってもよい。

【0132】

上記したように、非晶質半導体領域133にダメージを与えない条件で更なるドライエッチングを行うことで、露出した非晶質半導体領域133上に存在する残渣などの不純物を除去することができる。また、ドライエッチングに続けて、水プラズマ、または水素及び酸素の混合ガスによるプラズマ処理を行うことで、非晶質半導体領域133の欠陥を低減することができる。このため、後に完成する薄膜トランジスタのオフ電流を低減し、電気的特性のばらつきを低減することができる。

【0133】

なお、フォトリソグラフィ工程により形成されるマスクを導電膜119上に形成し、当該レジストで形成されるマスクを用いて導電膜119をエッチングして、ソース電極及びドレイン電極として機能する第1の電極123及び第2の電極125aを形成する。次に、不純物半導体膜117をエッチングして、ソース領域及びドレイン領域として機能する不純物半導体膜127及び不純物半導体膜129を形成する。この際、半導体膜116の一部がエッチングされる場合もある。次に、マスクを除去した後、半導体膜116の一部をエッチングして、非晶質半導体領域133を形成してもよい。当該エッチング工程のエッチングガスとして、HBrと、CF<sub>4</sub>、NF<sub>3</sub>、及びSF<sub>6</sub>の一以上と、酸素との混合ガスを用いることで、エッチングの残渣物を低減することができるため、薄膜トランジスタの特性のバラツキを低減することができる。

【0134】

また、マスクを除去した後、第1の電極123及び第2の電極125aを用いて、非晶質半導体領域115の一部をエッチングして、凹部を有する非晶質半導体領域133を形成する。このため、剥離液及びレジストの残渣物に触れた非晶質半導体領域はエッチングにより除去されるため、バックチャネルには残存しない。この結果、バックチャネルに残存した剥離液及びレジストの残渣物によるリーク電流が発生しないため、薄膜トランジスタのオフ電流をより低減することができる。

【0135】

以上の工程によりシングルゲート型の薄膜トランジスタを作製することができる(図7( A )参照。)。また、本実施の形態に示す薄膜トランジスタは、逆スタガ型の薄膜トランジスタであるため、オン電流及び電界効果移動度が高く、オフ電流が低く、且つ電気特性の変動が少ないシングルゲート型の薄膜トランジスタを生産性高く作製することができる

10

20

30

40

50

。

## 【0136】

次に、図7(B)に示すように、半導体膜135、不純物半導体膜127、不純物半導体膜129、第1の電極123、及び第2の電極125aの上に絶縁膜138を形成する。絶縁膜138は、ゲート絶縁膜107と同様に形成することができる。

## 【0137】

次に、フォトリソグラフィ工程により形成したレジストで形成されるマスクを用いて絶縁膜138に開口部を形成する。次に、絶縁膜138上に画素電極139aを形成する。

## 【0138】

以上の工程により、薄膜トランジスタと、当該薄膜トランジスタに接続する画素電極を作製することができる。 10

## 【0139】

なお、本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができるものとする。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 国際公開第2008/096483 (WO, A1)

特開2007-164172 (JP, A)

特開2003-297850 (JP, A)

特開2001-042361 (JP, A)

特開2009-180981 (JP, A)

特開2008-159643 (JP, A)

特開昭61-243487 (JP, A)

国際公開第2009/001578 (WO, A1)

特開平01-166020 (JP, A)

特開2010-161358 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343

H 01 L 29 / 786