(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4935486号

(P4935486)

(45) 発行日 平成24年5月23日(2012.5.23)

(24) 登録日 平成24年3月2日(2012.3.2)

(51) Int.Cl.

F 1

|                   |                  |            |     |

|-------------------|------------------|------------|-----|

| <b>HO4N 5/341</b> | <b>(2011.01)</b> | HO4N 5/335 | 41O |

| <b>HO4N 5/355</b> | <b>(2011.01)</b> | HO4N 5/335 | 55O |

| <b>HO4N 5/357</b> | <b>(2011.01)</b> | HO4N 5/335 | 57O |

| <b>HO4N 5/374</b> | <b>(2011.01)</b> | HO4N 5/335 | 74O |

請求項の数 10 (全 19 頁)

(21) 出願番号

特願2007-112652 (P2007-112652)

(22) 出願日

平成19年4月23日 (2007.4.23)

(65) 公開番号

特開2008-271280 (P2008-271280A)

(43) 公開日

平成20年11月6日 (2008.11.6)

審査請求日

平成22年3月15日 (2010.3.15)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 楠原 雅樹

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 大池 祐輔

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】 固体撮像装置、固体撮像装置の駆動方法、固体撮像装置の信号処理方法および撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたりセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる画素アレイ部と、

前記画素アレイ部の画素列ごとに設けられ、前記単位画素と同等の特性を有するダミー画素と、

前記単位画素と前記ダミー画素によって形成される差動回路と、

前記リセットトランジスタに対して前記出力ノードを通してリセット電圧を供給するとともに、当該リセット電圧の電圧値が調整可能なりセット電圧供給手段と、

前記リセットトランジスタによるリセット動作が終了した後、前記差動回路の差動出力の差分の中心が、外部の電圧源で調整された制御電圧になるように前記差動回路の電流源の制御を行なう同相帰還回路と

を備えたことを特徴とする固体撮像装置。

## 【請求項 2】

前記同相帰還回路は、前記リセット電圧供給手段の機能を持っている

ことを特徴とする請求項1記載の固体撮像装置。

## 【請求項 3】

10

20

前記ダミー画素は、前記単位画素に比べてサイズが大きく設計されていることを特徴とする請求項1記載の固体撮像装置。

**【請求項4】**

光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたリセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる画素アレイ部と、

前記画素アレイ部の画素列ごとに設けられ、前記単位画素と同等の特性を有するダミー画素と、

前記単位画素と前記ダミー画素によって形成される差動回路とを備えた固体撮像装置の駆動方法であって、

前記リセットトランジスタに対して前記出力ノードを通して供給するリセット電圧の電圧値を可変とし、

前記リセットトランジスタによるリセット動作の終了後、前記差動回路の差動出力の差分の中心が、外部の電圧源で調整された制御電圧になるように前記差動回路の電流源の制御を行なう

ことを特徴とする固体撮像装置の駆動方法。

**【請求項5】**

光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたリセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる画素アレイ部と、

前記画素アレイ部の画素列ごとに設けられ、前記単位画素と同等の特性を有するダミー画素と、

前記単位画素と前記ダミー画素によって形成される差動回路とを備えた固体撮像装置の信号処理方法であって、

前記画素アレイ部の各単位画素に同じ入力を与えたときの前記単位画素の各々の出力の逆数を補正係数として求め、

前記補正係数を用いて画素間の感度ばらつきを補正する

ことを特徴とする固体撮像装置の信号処理方法。

**【請求項6】**

前記補正係数を求めるに当たって、前記画素アレイ部の各単位画素に対して均一に光を照射し、このときの前記単位画素の各々の出力の逆数を前記補正係数とする

ことを特徴とする請求項5記載の固体撮像装置の信号処理方法。

**【請求項7】**

前記補正係数を求めるに当たって、前記転送トランジスタを駆動する転送制御信号の電圧値を徐々に高くして前記光電変換素子で発生した信号電荷を複数回に分けて転送し、初回以外の電荷転送での前記単位画素の各々の出力の逆数を前記補正係数とする

ことを特徴とする請求項5記載の固体撮像装置の信号処理方法。

**【請求項8】**

前記初回以外の電荷転送での前記単位画素の各々の出力の平均値の逆数を前記補正係数とする

ことを特徴とする請求項7記載の固体撮像装置の信号処理方法。

**【請求項9】**

光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたリセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる画素アレイ部と、

10

20

30

40

50

ンジスタとを含む単位画素が配置されてなる画素アレイ部と、

前記画素アレイ部の画素列ごとに設けられ、前記単位画素と同等の特性を有するダミー画素と、

前記単位画素と前記ダミー画素によって形成される差動回路とを備えた固体撮像装置の信号処理方法であって、

前記転送トランジスタを駆動する転送制御信号の電圧値を徐々に高くして一単位の蓄積期間に前記光電変換素子で発生した信号電荷を複数回に分けて転送し、

前記複数回の転送によって前記単位画素から出力される各信号を加算処理することを特徴とする固体撮像装置の信号処理方法。

#### 【請求項 10】

10

光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたリセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる固体撮像装置と、

入射光を前記固体撮像装置の撮像面上に結像する光学系とを具備し、

前記固体撮像装置は、

前記画素アレイ部の画素列ごとに設けられ、前記単位画素と同等の特性を有するダミー画素と、

前記単位画素と前記ダミー画素によって形成される差動回路と、

20

前記リセットトランジスタに対して前記出力ノードを通してリセット電圧を供給するとともに、当該リセット電圧の電圧値が調整可能なりセット電圧供給手段と、

前記リセットトランジスタによるリセット動作が終了した後、前記差動回路の差動出力の差分の中心が、外部の電圧源で調整された制御電圧になるように前記差動回路の電流源の制御を行なう同相帰還回路とを備えた

ことを特徴とする撮像装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、固体撮像装置、固体撮像装置の駆動方法、固体撮像装置の信号処理方法および撮像装置に関する。

30

##### 【背景技術】

##### 【0002】

固体撮像装置において、光電変換部（受光部）で発生した信号電荷は浮遊拡散容量に転送され、当該浮遊拡散容量で電圧に変換されて外部へと読み出される。しかし、近年の画素の微細化に伴い、十分な信号電荷を確保することが困難になっている。このため、画素個々から十分な大きさの出力電圧を得るのが難しくなってきている。

##### 【0003】

画素の出力電圧  $V$  は、信号検出容量を  $C$ 、受光信号に応じた信号電荷量を  $Q$  とすると、 $V = Q / C$  で与えられる。したがって、信号検出容量  $C$  が小さければ、出力電圧  $V$  を大きくする、即ち感度を高くすることができる。

40

##### 【0004】

このため、従来は、一端が接地された光電変換素子と、当該光電変換素子の他端にゲート電極が接続され、ソース電極が接地され、ドレイン電極が負荷回路に接続されたソース接地型の増幅トランジスタと、当該増幅トランジスタのドレイン電極とゲート電極の間に接続された微小容量の容量素子と、当該容量素子に並列に接続されたリセットトランジスタとで画素を構成し、高感度信号出力を実現していた（例えば、特許文献 1 参照）。

##### 【0005】

【特許文献 1】特開平 5 - 207375 号公報

##### 【発明の開示】

50

**【発明が解決しようとする課題】****【0006】**

特許文献1記載の従来技術では、画素内部に信号電荷の転送路を持たない構成を採っていることから、出力電圧は受光した信号レベルとその後にリセットをして読み出されるリセットレベルとなるため、増幅トランジスタの閾値ばらつきに起因する固定パターンノイズを除去することは可能であるが、リセット時に発生するリセットノイズを抑制することができない。このリセットノイズは、高感度信号出力を行なう上記従来技術に係る画素では、大きなノイズとして見えてしまう。

**【0007】**

これに対して、画素内部に信号電荷を転送する転送トランジスタを設けることで、上記従来技術の問題を解決することができる。すなわち、画素内部に転送トランジスタを設けることで、先に画素をリセットし、その後に画素で発生した信号電荷を転送することができるため、後段の回路において相関二重サンプリング動作が可能になる。そして、この相関二重サンプリング動作により、リセットノイズと画素の固定パターンノイズの両方を抑制することが可能になる。

10

**【0008】**

ここで、画素内部に転送トランジスタを設けた場合、転送トランジスタによって信号電荷を浮遊拡散容量に転送することになるので、光電変換素子のポテンシャルは浮遊拡散容量のポテンシャルよりも高くないと、光電変換素子から浮遊拡散容量への信号電荷の転送が行えないことになる。

20

**【0009】**

浮遊拡散容量のポテンシャルは、リセットトランジスタがON状態になるリセット動作により浮遊拡散容量に印加されるリセット電圧で決まる。しかし、ソース接地型の増幅トランジスタを用いた画素では、浮遊拡散容量のノード電位が増幅トランジスタの閾値電圧付近となって低い（ポテンシャルは高い）状態になり、しかもリセット電圧が回路の動作点付近で固定するために浮遊拡散容量のポテンシャルの調整が不可能であり、この理由により、本質的に受光部から浮遊拡散層容量への信号電荷の完全転送が不可能になってしまう。

**【0010】**

そこで、本発明は、ソース接地型の増幅トランジスタと微小容量の容量素子を用いて高感度信号出力を実現した単位画素において、受光部から浮遊拡散層容量への信号電荷の完全転送の実現を容易にする固体撮像装置、固体撮像装置の駆動方法、固体撮像装置の信号処理方法および撮像装置を提供することを目的とする。

30

**【課題を解決するための手段】****【0011】**

上記目的を達成するために、本発明は、光電変換素子と、この光電変換素子で光電変換された信号電荷を浮遊拡散容量に転送する転送トランジスタと、前記浮遊拡散容量と出力ノードの間に接続されたりセットトランジスタと、前記浮遊拡散容量と前記出力ノードの間に接続され、前記浮遊拡散容量と比較して微小な容量の容量素子と、前記容量素子で電圧に変換された信号を読み出す増幅トランジスタとを含む単位画素が配置されてなる画素アレイ部を有する固体撮像装置において、前記単位画素と同等の特性を有するダミー画素を前記画素アレイ部の画素列ごとに設け、このダミー画素と前記単位画素によって差動回路を形成するとともに、前記リセットトランジスタに対して前記出力ノードを通して供給するリセット電圧の電圧値を可変とし、前記リセットトランジスタによるリセット動作の終了後、前記差動回路の差動出力の差分の中心が、外部の電圧源で調整された制御電圧になるように前記差動回路の電流源の制御を行なうことを特徴とする。

40

**【0012】**

上記構成の固体撮像装置において、リセット電圧の電圧値を調整することにより、浮遊拡散容量のポテンシャルを自由に設定可能になるため、単位画素のポテンシャル設計が容易になり、受光部から浮遊拡散層への信号電荷の完全転送が可能となる。また、リセット

50

動作の終了後、差動回路の差動出力の差分の中心が、外部の電圧源で調整された制御電圧になるように差動回路の電流源の制御を行なうことにより、増幅トランジスタのゲート部分の動作点を出力振幅が最大になるように設定することが可能になるため、ダイナミックレンジを拡大できる。

【発明の効果】

【0013】

本発明によれば、ソース接地型の増幅トランジスタと微小容量の容量素子を用いて高感度信号出力を実現した単位画素において、浮遊拡散容量のポテンシャルを自由に設定可能になるため、受光部から浮遊拡散層への信号電荷の完全転送を実現できるようになる。

【発明を実施するための最良の形態】

10

【0014】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0015】

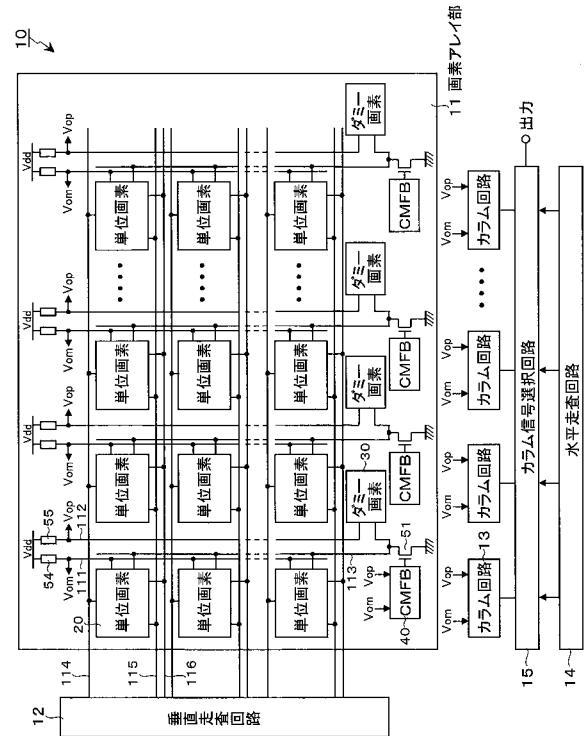

図1は、本発明の一実施形態に係る固体撮像装置、例えばCMOSイメージセンサの構成を示すシステム構成図である。

【0016】

図1に示すように、本実施形態に係るCMOSイメージセンサ10は、光電変換素子を含む単位画素（以下、単に「画素」と記述する場合もある）20が行列状に2次元配置されてなる画素アレイ部11と、その周辺回路とを有する構成となっている。画素アレイ部11の周辺回路としては、例えば、垂直走査回路12、複数のカラム回路13、水平走査回路14およびカラム信号選択回路15などが設けられている。

20

【0017】

画素アレイ部11の単位画素20の行列状配列に対して、2本の信号線111, 112とソース線113が画素列毎に配線されるとともに、単位画素20と同じ特性を持つダミー画素30と同相帰還回路（CMB; Common Mode Feedback Circuit）40が画素列毎に設けられている。単位画素20とダミー画素30は差動回路を形成している。その詳細については後述する。画素アレイ部11にはさらに、画素行毎に駆動制御線、例えば転送制御線114、リセット制御線115および選択制御線116が配線されている。

【0018】

垂直走査回路12は、シフトレジスタあるいはアドレスデコーダ等によって構成され、画素アレイ部11の各画素20を電子シャッタ行と読み出し行それぞれについて行単位で垂直方向（上下方向）に走査しつつ、電子シャッタ行に対してはその行の画素20の信号掃き捨てを行うための電子シャッタ動作を行うとともに、読み出し行に対してはその行の画素20の信号読み出しを行うための読み出し動作を行う。

30

【0019】

ここでは、図示を省略するが、垂直走査回路12は、画素20を行単位で順に選択しつつ、読み出し行の各画素20の信号を読み出す読み出し動作を行うための読み出し走査系と、当該読み出し走査系による読み出し走査よりもシャッタ速度に対応した時間分だけ前に同じ行（電子シャッタ行）に対して電子シャッタ動作を行うための電子シャッタ走査系とを有する構成となっている。

40

【0020】

そして、電子シャッタ走査系によるシャッタ走査によって光電変換部の不要な電荷がリセットされたタイミングから、読み出し走査系による読み出し走査によって画素20の信号が読み出されるタイミングまでの期間が、画素20における信号電荷の一単位の蓄積期間（露光期間）となる。すなわち、電子シャッタ動作とは、光電変換部に蓄積された信号電荷のリセット（掃き捨て）を行い、そのリセット後から新たに信号電荷の蓄積を開始する動作である。

【0021】

複数のカラム回路13は、画素アレイ部11の例えは画素列ごとに、即ち画素列に対して1対1の対応関係をもって配置され、垂直走査回路12による垂直走査によって選択さ

50

れた読み出し行の各画素 20 から出力される画素信号に対して所定の信号処理を行うとともに、信号処理後の画素信号を一時的に保持する。

#### 【0022】

カラム回路 13 としては、画素信号をサンプルホールドするサンプルホールド回路からなる回路構成のものや、サンプルホールド回路を含み、CDS(Correlated Double Sampling; 相関二重サンプリング)処理により、リセットノイズや増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズを除去するノイズ除去回路からなる回路構成のものなどが用いられる。

#### 【0023】

ただし、これらは一例に過ぎず、これに限定されるものではない。例えば、カラム回路 13 に A/D (アナログ - デジタル) 変換機能を持たせ、画素信号レベルをデジタル信号で出力する構成を探ることも可能である。10

#### 【0024】

水平走査回路 14 は、シフトレジスタあるいはアドレスデコーダ等によって構成され、画素アレイ部 11 の各画素列毎に信号処理後の画素信号を保持するカラム回路 13 を順に水平走査する。

#### 【0025】

カラム信号選択回路 15 は、水平選択スイッチや水平信号線等によって構成され、画素アレイ部 11 から画素行毎にカラム回路 13 に保持された画素信号を、水平走査回路 14 による水平走査に同期して順次出力する。20

#### 【0026】

なお、垂直走査回路 12、カラム回路 13 および水平走査回路 14 等の動作の基準となるタイミング信号や制御信号は、図示せぬタイミング制御回路で生成される。

#### 【0027】

上記構成の CMOS イメージセンサ 10 では、単位画素 20 から出力される画素信号に対する CDS 等の種々の信号処理をカラム回路 13 で行なう構成としたが、カラム信号選択回路 15 の後段側に配置される信号処理回路(図示せず)で行なう構成を探ることも可能である。この場合、信号処理回路については、画素アレイ部 11 と同じ半導体基板上に搭載するようにしてもよく、また当該半導体基板外に配置するようにしてもよい。

#### 【0028】

( 単位画素およびダミー画素 )

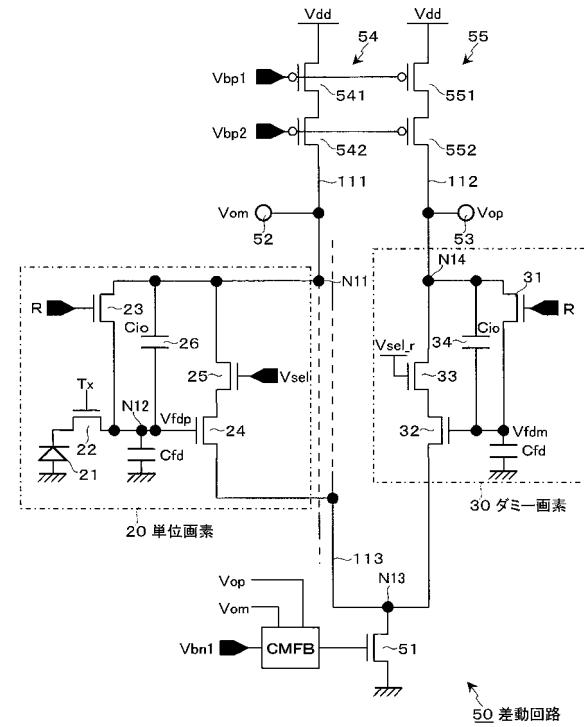

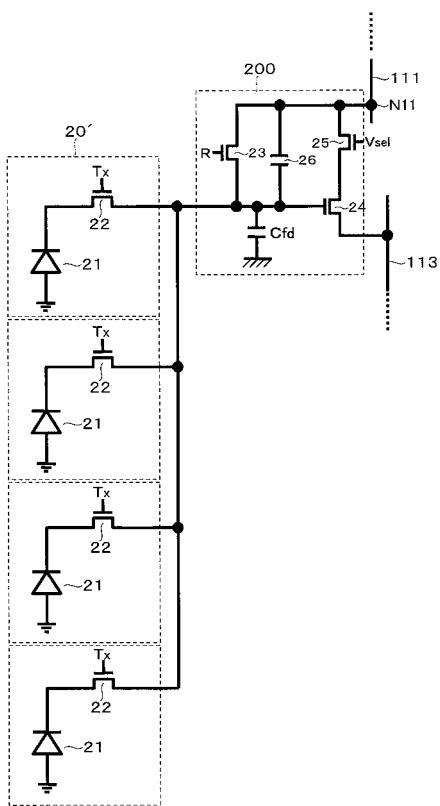

図 2 は、単位画素 20 およびダミー画素 30 の構成の一例を示す回路図である。

#### 【0029】

本例に係る単位画素 20 は、フォトダイオード等の光電変換素子 21 に加えて、例えば転送トランジスタ(転送ゲート) 22、リセットトランジスタ 23、増幅トランジスタ 24 および選択トランジスタ 25 の 4 つのトランジスタと、容量素子 26 を有する画素回路となっている。ここでは、これらトランジスタ 22 ~ 25 として、例えば N チャネルの MOS トランジスタを用いているが、これに限られるものではない。

#### 【0030】

光電変換素子 21 は、一端(アノード電極)が接地されている。転送トランジスタ 22 は、光電変換素子 21 の他端(カソード電極)と浮遊拡散容量 Cfd の間に接続され、光電変換素子 21 で光電変換され、ここに蓄積された信号電荷(ここでは、電子)を、ゲート電極(制御電極)に転送制御信号 Tx が与えられることによって電荷電圧変換部である浮遊拡散容量 Cfd に転送する。40

#### 【0031】

リセットトランジスタ 23 は、画素の出力ノード N11 にドレイン電極が、浮遊拡散容量 Cfd にソース電極がそれぞれ接続され、光電変換素子 21 から浮遊拡散容量 Cfd への信号電荷の転送に先立って、ゲート電極にリセット制御信号 R が与えられることによって浮遊拡散容量 Cfd のノード N12 の電位(ノード電位)をリセットする。

#### 【0032】

50

20

30

40

50

増幅トランジスタ 2 4 は、浮遊拡散容量  $C_{f\ d}$  にゲート電極が、ソース線 1 1 3 にソース電極がそれぞれ接続されたソース接地型となっており、リセットトランジスタ 2 3 によってリセットされた後の浮遊拡散容量  $C_{f\ d}$  の電位をリセットレベルとして読み出し、さらに転送トランジスタ 2 2 によって信号電荷が転送された後の浮遊拡散容量  $C_{f\ d}$  の電位を信号レベルとして読み出す。

#### 【0033】

選択トランジスタ 2 5 は、例えば、出力ノード N 1 1 にドレイン電極が、増幅トランジスタ 2 4 のドレイン電極にソース電極がそれぞれ接続され、ゲート電極に選択制御信号  $V_{s\ e\ l}$  が与えられることによって導通状態になることで、垂直走査回路 1 2 による垂直走査に同期して単位画素 2 0 を選択する。選択トランジスタ 2 5 については、増幅トランジスタ 2 4 のソース電極とソース線 1 1 3 の間に接続する構成を探ることも可能である。10

#### 【0034】

容量素子 2 6 は、浮遊拡散容量  $C_{f\ d}$  と比較して微小な容量  $C_{i\ o}$  を持ち、出力ノード N 1 1 に一端が、増幅トランジスタ 2 4 のゲート電極に他端がそれぞれ接続されている。この容量素子 2 6 としては、増幅トランジスタ 2 4 のゲート電極（浮遊拡散容量  $C_{f\ d}$  のノード N 1 2 ）と出力ノード N 1 1 の間の寄生容量であってもよい。

#### 【0035】

ダミー画素 3 0 は、例えばリセットトランジスタ 3 1、増幅トランジスタ 3 2、選択トランジスタ 3 3 および容量素子 3 4 を有する構成となっている。これら構成素子は、単位画素 2 0 のリセットトランジスタ 2 3、増幅トランジスタ 2 4、選択トランジスタ 2 5 および容量素子 2 6 にそれぞれ相当する。20

#### 【0036】

このダミー画素 3 0 を画素アレイ部 1 1 内に、単位画素 2 0 と同じプロセスで形成することにより、ダミー画素 3 0 の特性を単位画素 2 0 の特性と同等にすることができる。ここで、選択トランジスタ 3 3 のゲート電位（選択制御信号  $V_{s\ e\ l\_r}$  ）は、単位画素 2 0 と同一の波形が入力されるように制御される。

#### 【0037】

本例に係るダミー画素 3 0 は、単位画素 2 0 の転送トランジスタ 2 2 に相当するトランジスタを持たないが、図 3 に示すように、単位画素 2 0 の転送トランジスタ 2 2 に相当する転送トランジスタ 3 5 を持つ構成を探ることも可能である。この場合は、転送トランジスタ 3 5 のゲート電位を“ Low ” レベル（例えば、接地レベル）に固定すればよい。30

#### 【0038】

上記構成の単位画素 2 0 およびダミー画素 3 0 において、選択制御信号  $V_{s\ e\ l}$  ,  $V_{s\ e\ l\_r}$  については、デジタル的にグランドレベルと  $V_{d\ d}$  レベルの電圧で制御するようにもよいが、その電圧値を調整するようにすることで、画素回路の利得を向上させることができある。この選択制御信号  $V_{s\ e\ l}$  ,  $V_{s\ e\ l\_r}$  は、同一の波形が入力されるように制御される。

#### 【0039】

##### (差動回路)

単位画素 2 0 とダミー画素 3 0 は差動回路 5 0 を形成している。この差動回路 5 0 の具体的な構成について以下に説明する。40

#### 【0040】

単位画素 2 0 の増幅トランジスタ 2 4 のソース電極とダミー画素 3 0 の増幅トランジスタ 3 2 のソース電極は、ソース線 1 1 3 を介して共通に接続され、その共通接続ノード N 1 3 が電流源トランジスタ 5 1 を介して接地されている。

#### 【0041】

単位画素 2 0 の出力ノード N 1 1 およびダミー画素 3 0 の出力ノード N 1 4 からそれぞれ信号を導出する信号線 1 1 1 , 1 1 2 は出力端子 5 2 , 5 3 にそれぞれ接続されている。これら信号線 1 1 1 , 1 1 2 と電源  $V_{d\ d}$  の間、即ち出力端子 5 2 , 5 3 を挟んで単位画素 2 0 およびダミー画素 3 0 と反対側には負荷回路 5 4 , 5 5 がそれぞれ接続されてい50

る。

#### 【0042】

負荷回路54は、例えば縦積み2段の構成(カスコード)のPチャネルMOSトランジスタ541, 542によって構成されている。負荷回路55も同様に、縦積み2段の構成のPチャネルMOSトランジスタ551, 552によって構成されている。そして、MOSトランジスタ541, 551の各ゲート電極がバイアス電圧V<sub>b p 1</sub>によってバイアスされ、MOSトランジスタ542, 552の各ゲート電極がバイアス電圧V<sub>b p 2</sub>によってバイアスされている。

#### 【0043】

ここでは、負荷回路54, 55をPチャネルMOSトランジスタの縦積み2段の構成としたが、これに限られるものではなく、図4に示すように、それぞれ1個のPチャネルMOSトランジスタ541, 551によって構成するようにしてもよい。10

#### 【0044】

上述したようにして、単位画素20の増幅トランジスタ24、ダミー画素30の増幅トランジスタ32、電流源トランジスタ51および負荷回路54, 55によって差動回路50が形成されている。

#### 【0045】

この差動回路50では、増幅トランジスタ32のゲート電圧V<sub>f dm</sub>を基準として、増幅トランジスタ24のゲート電圧V<sub>f pd</sub>に応じた差動出力V<sub>o m</sub>, V<sub>o p</sub>が出力端子52, 53から導出される。この差動出力V<sub>o m</sub>, V<sub>o p</sub>は、単位画素20の画素信号としてカラム回路13に供給される。20

#### 【0046】

##### (同相帰還回路)

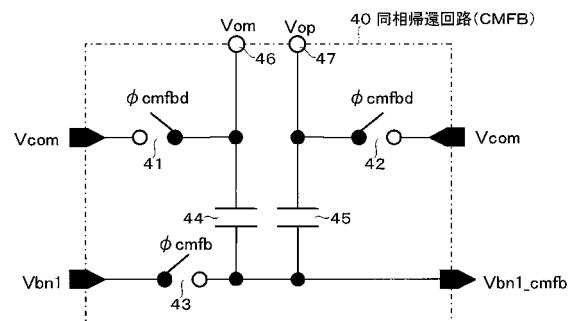

図5は、同相帰還回路40の構成の一例を示す回路図である。同相帰還回路40は、その出力端が電流源トランジスタ51のゲート電極に接続されており、差動回路50の差動出力V<sub>o m</sub>, V<sub>o p</sub>と外部の電圧源でコントロールされた制御電圧V<sub>c om</sub>に基づいて電流源トランジスタ51のゲートバイアスを制御することにより、差動出力V<sub>o m</sub>, V<sub>o p</sub>の差分の中心(振幅の中心)が制御電圧V<sub>c om</sub>になるように制御を行なう。

#### 【0047】

図5に示すように、同相帰還回路40は、3つのスイッチ素子41～43と2つの容量素子44, 45によって構成され、2つの入出力端子46, 47が差動回路50の出力端子52, 53にそれぞれ接続されている。30

#### 【0048】

スイッチ素子41, 42は、スイッチ制御信号c m f b dに応答してON(閉)状態になることで、外部の電圧源から制御電圧V<sub>c om</sub>を選択的に取り込んで差動回路50の出力端子52, 53に与える。制御電圧V<sub>c om</sub>は、単位画素20をリセットしているときはリセットに適した電圧値に、単位画素20のリセットが終了した時点で差動回路50の出力振幅が最大となる電圧値(CMF B電圧)にそれぞれ設定されている。

#### 【0049】

ここに、リセットに適した電圧値とは、光電変換素子21のポテンシャルと浮遊拡散容量C<sub>f d</sub>のポテンシャルの関係から、光電変換素子21から浮遊拡散容量C<sub>f d</sub>へ信号電荷を完全に転送することができるような電圧値を言う。このリセット電圧の電圧値を調整することにより、増幅トランジスタ24のゲート部分の動作点を自由に設定することができる。40

#### 【0050】

また、差動回路50の出力振幅が最大となる電圧値(CMF B電圧)とは、差動回路50の同相信号レベル(同相電圧)、即ち差動出力V<sub>o m</sub>, V<sub>o p</sub>の差分の中心電圧を規定する電圧値、差動出力V<sub>o m</sub>, V<sub>o p</sub>の差分の中心電圧が例えば差動回路50の出力振幅の中心になるように制御する電圧値である。

#### 【0051】

スイッチ素子 4 3 は、スイッチ制御信号  $c m f b$  に応答して ON (閉) 状態になることで、バイアス電圧  $V_{b n 1}$  を取り込んで差動回路 5 0 の電流源トランジスタ 5 1 にそのゲートバイアスとして供給する。

#### 【0052】

スイッチ素子 4 3 が OFF (開) 状態のときはバイアス電圧  $V_{b n 1}$  に代えて、本同相帰還回路 4 0 の作用により、差動回路 5 0 の差動出力  $V_{o m}, V_{o p}$  の振幅の中心が、単位画素 2 0 のリセット終了後の制御電圧  $V_{c o m}$  (CMFB 電圧) になるように差動回路 5 0 を制御するためのバイアス電圧  $V_{b n 1\_cmfb}$  が電流源トランジスタ 5 1 にそのゲートバイアスとして供給される。

#### 【0053】

なお、上記構成の CMOS イメージセンサ 1 0 では、画素アレイ部 1 1 の同相帰還回路 4 0 側 (図 1 の上側) に負荷回路 5 4, 5 5 を配置するとともに、差動出力  $V_{o m}, V_{o p}$  を導出する配置構成としたが、この配置構成に限られるものではない。

#### 【0054】

このような配置構成を採ることにより、画素列毎に配線する信号線を 1 本、具体的にはダミー画素 3 0 側の信号線 1 1 2 を削減できるとともに、差動回路 5 0 の出力端子 5 2, 5 3 (図 2 参照) と同相帰還回路 4 0 の入出力端子 4 6, 4 7 (図 5 参照) との間の配線長を短くできるため、画素アレイ部 1 1 全体のレイアウト面積の縮小化を図ることができる利点がある。

#### 【0055】

##### (画素アレイ部の動作)

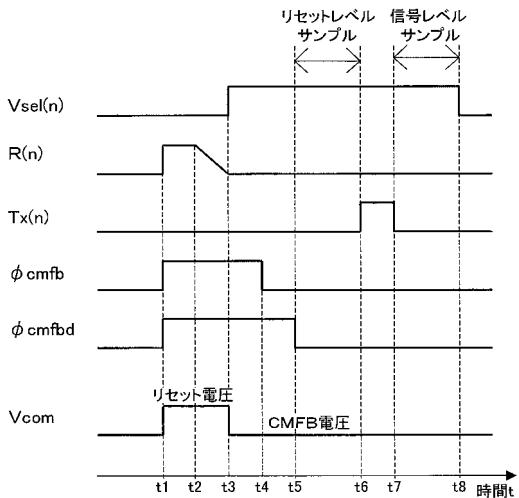

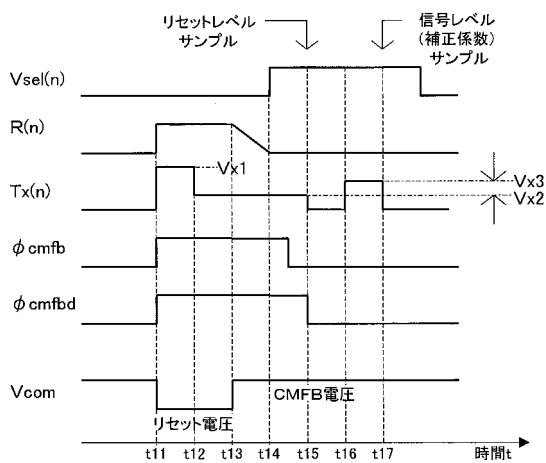

続いて、画素アレイ部 1 1 における単位画素 2 0、ダミー画素 3 0 および同相帰還回路 4 0 の動作について、図 6 のタイミング波形図を用いて説明する。

#### 【0056】

先ず、時刻  $t_1$  で、特定の画素行  $n$  の単位画素 2 0 とダミー画素 3 0 に “High” レベルのリセット制御信号  $R(n)$  を入力し、同時に、同相帰還回路 4 0 のスイッチ素子 4 1 ~ 4 3 をスイッチ制御信号  $c m f b, c m f b d$  によって全て ON (閉) 状態にする。

#### 【0057】

これと同時に、外部の電圧源から同相帰還回路 4 0 に対して、差動回路 5 0 の同相信号レベルを規定する制御電圧  $V_{c o m}$  を、単位画素 2 0 のリセット電圧として入力する。すなわち、外部の電圧源と同相帰還回路 4 0 は、リセットトランジスタ 2 3 に対して出力ノード N 1 1 を通してリセット電圧を供給するリセット電圧供給手段を構成している。

#### 【0058】

ここでは、制御電圧  $V_{c o m}$  を単位画素 2 0 のリセット電圧として用いるようにしているが、リセット専用の信号線とスイッチ素子からなるリセット電圧供給手段を別途用意して、当該リセット電圧供給手段から適宜リセット電圧を制御電圧  $V_{c o m}$  と並列的に入力する構成を探ることも可能である。

#### 【0059】

ただし、同相帰還回路 4 0 をリセット電圧供給手段として兼用する構成を探った方が、リセット電圧供給手段を別途用意する必要がなくなるため、その分だけ回路構成を簡略化できる利点がある。

#### 【0060】

リセット制御信号  $R(n)$  によるリセット動作により、単位画素 2 0 の信号検出部である浮遊拡散容量  $C_{f d}$  のノード電位が、制御電圧  $V_{c o m}$  のリセット電圧に設定された時点  $t_2$  で、リセット制御信号  $R(n)$  を “High” レベルから “Low” レベルに徐々に遷移させる。この動作については、ダミー画素 3 0 についても同じである。

#### 【0061】

リセット制御信号  $R(n)$  が “Low” レベルになった後時刻  $t_3$  で、“High” レベルの選択制御信号  $V_{sel}(n)$  を入力し、画素行  $n$  の各単位画素 2 0 の選択トランジ

10

20

30

40

50

スタ 2 5 を O N 状態にすることによって各単位画素 2 0 を選択状態にする。

**【 0 0 6 2 】**

ここで、選択制御信号  $V_{sel}(n)$  については、リセット制御信号  $R(n)$  と同時に入力するようにしてもよい。ただし、同時に入力しない方が、時刻  $t_1$  ~ 時刻  $t_3$  の期間で選択トランジスタ 2 5 が O N することに伴って消費する電力分だけ低減できるため、単位画素 2 0 での消費電力を小さく抑える上で有利である。

**【 0 0 6 3 】**

選択制御信号  $V_{sel}(n)$  の入力と同時に、またはそれ以降に、制御電圧  $V_{com}$  を差動回路 5 0 の出力振幅を最大限にとれる電圧値に設定する。その後、時刻  $t_4$  でスイッチ制御信号  $c_{mfb}$  を、次いで時刻  $t_5$  でスイッチ制御信号  $c_{mfbd}$  を順に非アクティブ（“ Low ” レベル）状態にする。10

**【 0 0 6 4 】**

このとき、単位画素 2 0 では、制御電圧  $V_{com}$  のリセット電圧に設定された浮遊拡散容量  $C_{fd}$  の電圧をリセットレベルとして読み出し、後段のカラム回路 1 3 に供給する動作が行われる。

**【 0 0 6 5 】**

次に、時刻  $t_6$  で、転送制御信号  $T(n)$  を入力し、転送トランジスタ 2 3 を O N 状態にすることで、それまでに光電変換素子 2 1 で光電変換されて蓄積された信号電荷を浮遊拡散容量  $C_{fd}$  に転送する。そして、転送制御信号  $T(n)$  が消滅した時刻  $t_6$  で、転送された信号電荷に応じた電圧を信号レベルとして読み出し、後段のカラム回路 1 3 に供給する。20

**【 0 0 6 6 】**

単位画素 2 0 におけるリセットレベルおよび信号レベルの読み出しあは、浮遊拡散容量  $C_{fd}$  と信号線 1 1 1 の間に接続された容量素子 2 6 とソース接地型の増幅トランジスタ 2 4 が担う。容量素子 2 6 は、浮遊拡散容量  $C_{fd}$  と比較して微小な容量である。したがって、微小容量の容量素子 2 6 とソース接地型の増幅トランジスタ 2 4 を用いて信号の読み出しを行なう単位画素 2 0 においては、出力する電圧レベルが大きい、即ち信号検出感度が高い。

**【 0 0 6 7 】**

**[ 本実施形態の作用効果 ]**

このように、ソース接地型の増幅トランジスタ 2 4 と微小容量の容量素子 2 6 を用いて信号の読み出しを行うことによって信号検出感度を高めた単位画素 2 0 において、光電変換素子 2 1 で光電変換された信号電荷を浮遊拡散容量  $C_{fd}$  に転送する転送トランジスタ 2 2 を設けたことにより、先に画素 2 0 をリセットしてそのリセットレベルを読み出し、その後に光電変換素子 2 1 から信号電荷を転送して信号レベルとして読み出すことで、例えばカラム回路 1 3 において相関二重サンプリングによるノイズ除去を実行することができるため、リセットノイズと画素の固定パターンノイズの両方を抑制することができる。30

**【 0 0 6 8 】**

加えて、単位画素 2 0 とダミー画素 3 0 で差動回路 5 0 を形成し、単位画素 2 0 からリセットレベルおよび信号レベルを読み出す読み出し回路を差動回路構成にし、リセットトランジスタ 2 3 に対して画素 2 0 の出力ノード N 1 1 を通してリセット電圧を供給するとともに、当該リセット電圧の電圧値が可変なりリセット電圧供給手段（本例では、外部の電圧源と同相帰還回路 4 0 ）を設けたことにより、リセット電圧の電圧値を調整によって浮遊拡散容量  $C_{fd}$  のポテンシャルを自由に設定可能になるため、単位画素 2 0 のポテンシャル設計が容易になり、光電変換素子 2 1 から拡散浮遊容量  $C_{fd}$  への信号電荷の完全転送が可能となる。40

**【 0 0 6 9 】**

ただし、単位画素 2 0 側（正相側）のリセット電圧の電圧値を調整すると、差動出力  $V_{om}$  ,  $V_{op}$  の差分の中心電圧が差動回路 5 0 の出力振幅から外れてしまう。そこで、差動回路 5 0 の電流源トランジスタ 5 1 のゲートバイアスを制御する同相帰還回路 4 0 を設50

け、単位画素 2 0 の浮遊拡散容量  $C_{fd}$  のノード電位をリセット電圧でリセットした後、同相帰還回路 4 0 の作用によって差動出力  $V_{om}$ ,  $V_{op}$  の差分の中心電圧が差動回路 5 0 の出力振幅の中心になるように制御電圧  $V_{com}$  の電圧値（CMFB 電圧）を設定して帰還制御を行なう構成を探っている。これにより、増幅トランジスタ 2 4 のゲート部分の動作点を出力振幅（出力範囲）が最大になるように設定することができるため、ダイナミックレンジを拡大できる。

#### 【0070】

（差動回路の特性ばらつき）

ここで、本実施形態に係る単位画素 2 0 では、信号の読み出しに微小容量の容量素子 2 6 を用いていることで、差動回路 5 0 の単位画素 2 0 側とダミー画素 3 0 側に、サイズのミスマッチなどによって特性ばらつきがあると、当該特性ばらつきによって出力信号の出力特性に影響が及ぶ懸念がある。10

#### 【0071】

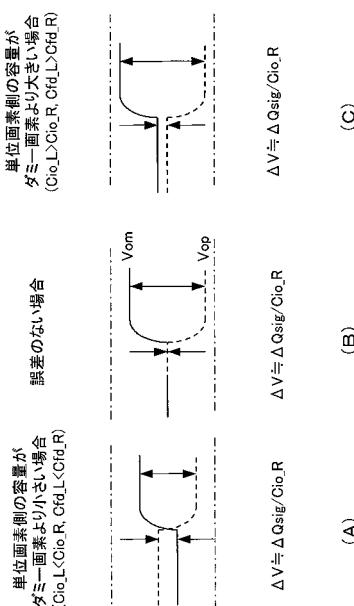

単位画素 2 0 側とダミー画素 3 0 側に特性ばらつき（誤差）があった場合の出力波形を図 7 に示す。ここでは、単位画素 2 0 側の浮遊拡散容量を  $C_{fd\_L}$ 、容量素子 2 6 の容量を  $C_{io\_L}$ 、ダミー画素 3 0 側の遊拡散容量を  $C_{fd\_R}$ 、容量素子 3 4 の容量を  $C_{io\_R}$  としている。

#### 【0072】

単位画素 2 0 側の容量  $C_{fd\_L}$ ,  $C_{io\_L}$  がダミー画素 3 0 側の容量  $C_{fd\_R}$ ,  $C_{io\_R}$  よりも小さい場合には、単位画素 2 0 とダミー画素 3 0 のリセットレベルは同じではなく、図 7 (A) に示すようにずれる。因みに、単位画素 2 0 側とダミー画素 3 0 側に誤差が無い場合は、図 7 (B) に示すように、単位画素 2 0 とダミー画素 3 0 のリセットレベルは一致する。20

#### 【0073】

そこで、単位画素 2 0 側の容量  $C_{fd\_L}$ ,  $C_{io\_L}$  とダミー画素 3 0 側の容量  $C_{fd\_R}$ ,  $C_{io\_R}$  の違いによってリセットレベルが変化する特性を逆に利用して、意図的に、ダミー画素 3 0 側の容量  $C_{fd\_R}$ ,  $C_{io\_R}$  が単位画素 2 0 側の容量  $C_{fd\_L}$ ,  $C_{io\_L}$  よりも小さくなるように、ダミー画素 3 0 側を単位画素 2 0 側よりもサイズを大きく設計することにより、図 7 (C) に示すように、差動出力  $V_{om}$ ,  $V_{op}$  の振幅範囲を広くすることができる。30

#### 【0074】

（感度ばらつき）

また、同様に、信号を検出する容量素子 2 6 の容量  $C_{io}$  が微小であるために単位画素 2 0 ごとに感度のばらつきが生じる。この感度ばらつきを補正する補正係数は、各画素 2 0 に同じ入力を与えたときの各出力の逆数で求めることができる。

#### 【0075】

単位画素 2 0 に同じ入力を与えて補正係数を求める第 1 の方法としては、すべての単位画素 2 0 に対して均一に光を照射し、そのときの各画素 2 0 の出力の逆数を求めることで画素ごとの補正係数を求めることができる。第 2 の方法として、転送制御信号  $T_x$  の電圧値を徐々に高く設定し、光電変換素子 2 1 で発生した信号電荷を複数回に分けて転送（部分転送）を行うことで補正係数を求めることができる。40

#### 【0076】

<補正係数の算出>

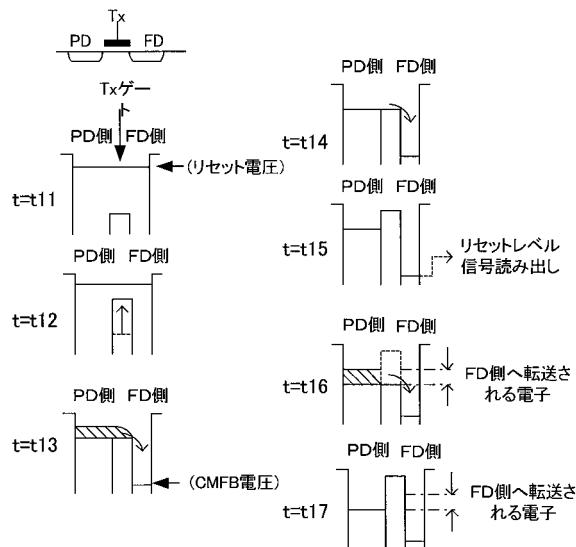

ここで、感度ばらつきの補正係数を求めるための第 2 の方法について、図 8 のタイミング波形図および図 9 のポテンシャル図を用いて具体的に説明する。

#### 【0077】

先ず、例えば光電変換素子 (PD) 2 1 に外部より電圧を与えることにより、光電変換素子 2 1 を電荷（本例では、電子）で満たす。その後、時刻  $t_{11}$  で、特定の画素行  $n$  の単位画素 2 0 とダミー画素 3 0 に “High” レベルのリセット制御信号  $R(n)$  を入力し、同時に、転送制御信号  $T_x(n)$  を光電変換素子 2 1 の電荷を完全に転送できる電圧50

値  $V \times 1$  に設定する。

**【0078】**

これと同時に、同相帰還回路 40 のスイッチ素子 41 ~ 43 をスイッチ制御信号  $c m f b$ ,  $c m f b d$  によって全て ON 状態にするとともに、同相帰還回路 40 に入力される制御電圧  $V c o m$  をリセット電圧にする。

**【0079】**

次に、時刻  $t_{12}$  で、転送制御信号  $T_x(n)$  を光電変換素子 21 の電荷を完全に転送できないが、画素アレイ部 11 のすべての画素 20 の光電変換素子 21 から電荷をわずかに転送できる電圧値  $V \times 2$  に設定する。

**【0080】**

次に、時刻  $t_{13}$  で、浮遊容量 (FD) Cf d 側の電圧、即ち制御電圧  $V c o m$  を高い電圧 (CMFB 電圧) にし、浮遊容量 Cf d のポテンシャルを低くする。これにより、転送トランジスタ 22 のゲート直下のチャネルのポテンシャルで設定される、いわゆるすりきりの電圧以上の電荷が光電変換素子 21 から浮遊拡散容量 Cf d へ転送される。

**【0081】**

次に、リセット制御信号  $R(n)$  が “Low” レベルになった後時刻  $t_{14}$  で、“High” レベルの選択制御信号  $V_{sel}(n)$  を入力し、画素行  $n$  の各単位画素 20 の選択トランジスタ 25 を ON 状態にすることによって各単位画素 20 を選択状態にし、読み出しの設定を行なう。

**【0082】**

そして、時刻  $t_{15}$  で、転送制御信号  $T_x(n)$  を “Low” レベルにし、転送制御信号  $T_x(n)$  の電圧  $V \times 2$  で転送された電荷に応じた浮遊拡散容量 Cf d の電圧をリセットレベル (信号基準レベル) として外部に読み出す。

**【0083】**

次に、時刻  $t_{16}$  で、転送制御信号  $T_x(n)$  を完全転送ではないある一定の電圧値  $V \times 3$  (最初のすりきりの電圧値  $V \times 2$  よりも高い) に設定する。そして、時刻  $t_{17}$  で、転送制御信号  $T_x(n)$  を “Low” レベルにし、転送制御信号  $T_x(n)$  の電圧値  $V \times 3$  で転送された電荷に応じた浮遊拡散容量 Cf d の電圧を信号レベルとして外部に読み出す。

**【0084】**

この信号レベルは、理想的には各画素同じ電荷量に基づくものなので、感度ばらつきがなければ、読み出した信号レベルとリセットレベルで相關 2 重サンプリングを行うことにより、すべての画素から同じ画素信号が出力される。しかし、単位画素 20 の感度ばらつきの影響を受けて画素信号に画素間でばらつきが発生する。

**【0085】**

そこで、転送制御信号  $T_x$  の電圧値を徐々に高く設定し、光電変換素子 21 で発生した信号電荷を複数回に分けて転送し、初回以外の電荷転送での単位画素 20 の各々の出力信号の逆数を補正係数補正係数とし、この補正係数を用いて出力信号に対して補正処理を行なうことで画素の感度ばらつきを補正することができる。なお、1 度の読み出しではノイズが含まれるため、初回以外の電荷転送での単位画素 20 の各々の出力信号の平均値を求めて補正係数とするのが好ましい。

**【0086】**

(出力信号の飽和)

本実施形態に係る単位画素 20、即ち微小容量の容量素子 26 とソース接地型の増幅トランジスタ 24 を用いて信号の読み出しを行なう単位画素 20 は、従来のソースフォロワ読み出しの場合に比べて感度が 1 衍程度高くなる。そのため、わずかな電荷で画素 20 からの出力信号が飽和してしまう懸念がある。

**【0087】**

この出力信号が飽和する問題については、例えば、上述した感度ばらつきの補正で用了いた単位画素 20 の駆動法、即ち光電変換素子 21 で光電変換された信号電荷を、任意の電

10

20

30

40

50

荷量で複数に分割して転送し、各分割転送による電荷に応じた信号を読み出す駆動法を用い、この駆動法によって読み出された各信号を加算して1つの画素信号とすることで解決できる。

#### 【0088】

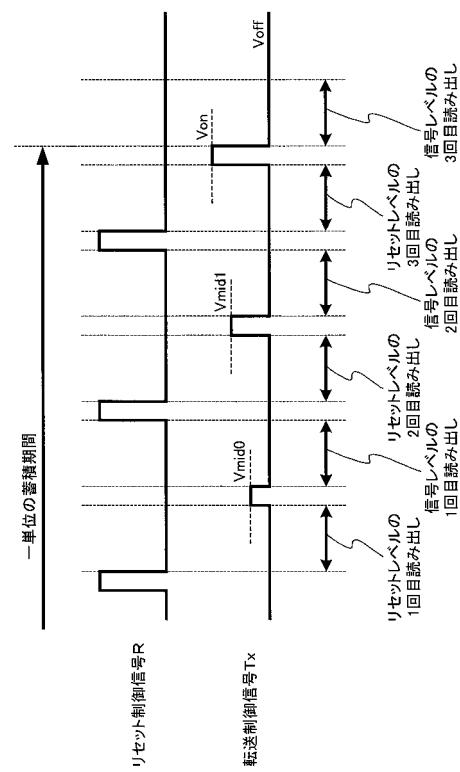

任意の電荷量で複数に分割して転送し、各分割転送による電荷に応じた信号を読み出す駆動法について、一単位の蓄積期間中に光電変換素子21に蓄積された信号電荷を例えれば3分割転送にて浮遊拡散容量 $C_{fd}$ へ転送する場合を例に挙げて以下により具体的に説明する。

#### 【0089】

3分割転送の場合、転送トランジスタ22のゲート電極に印加する転送制御信号 $T_x$ として、光電変換素子21の電荷を完全に転送できるオン電圧 $V_{on}$ と、“Low”レベルのオフ電圧 $V_{off}$ と、オフ電圧 $V_{off}$ よりも大きく、オン電圧 $V_{on}$ よりも小さい2つの中間電圧 $V_{mid0}$ ,  $V_{mid1}$ を設定する。10

#### 【0090】

そして、中間電圧 $V_{mid0}$ ,  $V_{mid1}$ およびオン電圧 $V_{on}$ をその順番で順次転送トランジスタ22のゲート電極に転送制御信号 $T_x$ として印加し、一単位の蓄積期間中に光電変換素子21に蓄積された信号電荷を3分割転送にて浮遊拡散容量 $C_{fd}$ へ転送し、この分割転送に対応して単位画素20から出力される各信号を例えればカラム回路13あるいは後段の信号処理回路（図示せず）で加算処理するようとする。

#### 【0091】

このように、分割転送による駆動法を用いて単位画素20を駆動し、分割転送によって単位画素20から出力される信号を加算して1つの画素信号とすることにより、飽和レベルを損なうことなく、高い信号検出感度にて単位画素20から信号を読み出すことができるため、高感度なイメージセンサを実現できる。20

#### 【0092】

##### (画素共有化)

以上説明した本実施形態に係る単位画素20については、感度低下が少ないとから、図11に示すように、単位画素20を光電変換素子21と転送トランジスタ22で構成し、当該単位画素20を並列に複数配置するとともに、リセットトランジスタ23、増幅トランジスタ24、選択トランジスタ25および容量素子26からなる信号検出回路200を複数の単位画素20で共有する構成を探ることができる。画素共有化により、読み出し線の寄生容量が減るため、信号の読み出し速度を高速化できる。30

#### 【0093】

特に、読み出し回路を差動構成にしたことにより、差動回路50の増幅率が理想的な場合は、浮遊拡散容量 $C_{fd}$ に依存せずに信号検出を行なうことができるため、図11に示すように、画素回路の中に光電変換素子21と転送トランジスタ22を並列に設けた場合に、電圧感度を落とすことなく信号の読み出しが可能になる。

#### 【0094】

因みに、通常の画素構成での読み出しでは、浮遊拡散容量 $C_{fd}$ に依存し、光電変換素子21と転送トランジスタ22を画素内に複数設けた場合に浮遊拡散容量 $C_{fd}$ が増すために感度の低下が生じる。40

#### 【0095】

本実施形態に係る単位画素20でも、同様に浮遊拡散容量 $C_{fd}$ が増加するものの、信号電圧の検出感度はあくまで浮遊拡散容量 $C_{fd}$ のノードN12と出力ノードN11の容量で決まるため、画素の並列度を増しても感度に影響しにくい。また、並列度が増すことにより、増幅トランジスタ24の拡散層の数が減少するため、読み出し線に付く寄生容量を低減することが可能になり、結果として、信号の読み出し速度の高速化に寄与することになる。

#### 【0096】

##### [変形例]

10

20

30

40

50

なお、上記実施形態では、可視光の光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されてなるC M O Sイメージセンサに適用した場合を例に挙げて説明したが、本発明はC M O Sイメージセンサへの適用に限られるものではなく、画素アレイ部の画素列ごとにカラム回路を配置してなるカラム方式の固体撮像装置全般に対して適用可能である。

#### 【 0 0 9 7 】

また、本発明は、可視光の入射光量の分布を検知して画像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像装置や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像装置（物理量分布検知装置）全般に対して適用可能である。

10

#### 【 0 0 9 8 】

さらに、本発明は、画素アレイ部の各単位画素を行単位で順に走査して各単位画素から画素信号を読み出す固体撮像装置に限らず、画素単位で任意の画素を選択して、当該選択画素から画素単位で信号を読み出すX-Yアドレス型の固体撮像装置に対しても適用可能である。

#### 【 0 0 9 9 】

なお、固体撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

20

#### 【 0 1 0 0 】

また、本発明は、固体撮像装置への適用に限られるものではなく、撮像装置にも適用可能である。ここで、撮像装置とは、デジタルスチルカメラやビデオカメラ等のカメラシステムや、携帯電話機などの撮像機能を有する電子機器のことを言う。なお、電子機器に搭載される上記モジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

#### 【 0 1 0 1 】

##### [ 撮像装置 ]

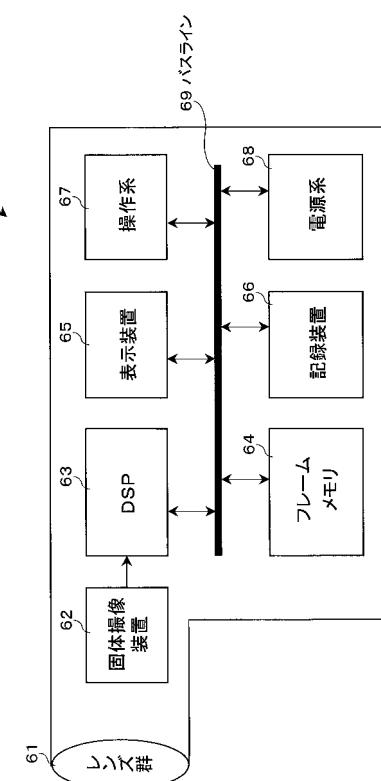

図12は、本発明に係る撮像装置の構成の一例を示すブロック図である。図12に示すように、本発明に係る撮像装置60は、レンズ群61を含む光学系、固体撮像装置62、カメラ信号処理回路であるD S P回路63、フレームメモリ64、表示装置65、記録装置66、操作系67および電源系68等を有し、D S P回路63、フレームメモリ64、表示装置65、記録装置66、操作系67および電源系68がバスライン69を介して相互に接続された構成となっている。

30

#### 【 0 1 0 2 】

レンズ群61は、被写体からの入射光（像光）を取り込んで固体撮像装置62の撮像面上に結像する。固体撮像装置62は、レンズ群61によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像装置62として、先述した実施形態に係るC M O Sイメージセンサ10が用いられる。

#### 【 0 1 0 3 】

表示装置65は、液晶表示装置や有機E L (electro luminescence)表示装置等のパネル型表示装置からなり、固体撮像装置62で撮像された動画または静止画を表示する。記録装置66は、固体撮像装置62で撮像された動画または静止画を、ビデオテープやD V D (Digital Versatile Disk)等の記録媒体に記録する。

40

#### 【 0 1 0 4 】

操作系67は、ユーザによる操作の下に、本撮像装置が持つ様々な機能について操作指令を発する。電源系68は、D S P回路63、フレームメモリ64、表示装置65、記録装置66および操作系67の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

#### 【 0 1 0 5 】

上述したように、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバ

50

イル機器向けカメラモジュールなどの撮像装置において、その固体撮像装置 62 として先述した実施形態に係る C M O S イメージセンサ 10 を用いることで、当該 C M O S イメージセンサ 10 では、少ない信号電荷量でも十分な大きさの画素信号を得ることができたため、高感度な撮像装置を実現できる。

【図面の簡単な説明】

【0106】

【図 1】本発明の一実施形態に係る C M O S イメージセンサの構成を示すシステム構成図である。

【図 2】単位画素およびダミー画素の構成の一例を示す回路図である。

【図 3】ダミー画素の他の構成例を示す回路図である。 10

【図 4】負荷回路の他の構成例を示す回路図である。

【図 5】同相帰還回路の構成の一例を示す回路図である。

【図 6】単位画素、ダミー画素および同相帰還回路の動作説明に供するタイミング波形図である。

【図 7】単位画素側とダミー画素側に特性ばらつきがあった場合の出力波形を示す波形図である。

【図 8】感度ばらつきの補正係数を求める方法についての説明に供するタイミング波形図である。

【図 9】感度ばらつきの補正係数を求める方法についての説明に供するポテンシャル図である。 20

【図 10】3分割転送の場合の駆動タイミング例を示すタイミングチャートである。

【図 11】画素共有化の例を示す回路図である。

【図 12】本発明に係る撮像装置の構成の一例を示すブロック図である。

【符号の説明】

【0107】

10 ... C M O S イメージセンサ、 11 ... 画素アレイ部、 12 ... 垂直走査回路、 13 ... ラム回路、 14 ... 水平走査回路、 15 ... カラム信号選択回路、 20 , 20 ... 単位画素、 21 ... 光電変換素子、 22 ... 転送トランジスタ、 23 ... リセットトランジスタ、 24 ... 増幅トランジスタ、 25 ... 選択トランジスタ、 26 ... 容量素子、 30 ... ダミー画素、 40 ... 同相帰還回路、 50 ... 差動回路 30

【図1】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【図 1 1】

【図12】

---

フロントページの続き

(56)参考文献 特開2006-148284(JP,A)

特開2007-068099(JP,A)

特開2006-148461(JP,A)

特開2006-017933(JP,A)

特開2001-177775(JP,A)

特開2008-263395(JP,A)

特開2004-037382(JP,A)

特開2000-165754(JP,A)

特開平05-207375(JP,A)

特開平03-163971(JP,A)

特表2007-516654(JP,A)

特開2006-101394(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762