**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

*HO1L 51/30 (2006.01)*

(45) 공고일자

2007년03월12일

(11) 등록번호

10-0694364

(24) 등록일자

2007년03월06일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2005-7003713   | (65) 공개번호   | 10-2005-0059166 |

| (22) 출원일자   | 2005년03월03일       | (43) 공개일자   | 2005년06월17일     |

| 심사청구일자      | 2005년03월04일       |             |                 |

| 번역문 제출일자    | 2005년03월03일       |             |                 |

| (86) 국제출원번호 | PCT/GB2003/003960 | (87) 국제공개번호 | WO 2004/023573  |

| 국제출원일자      | 2003년09월03일       | 국제공개일자      | 2004년03월18일     |

|            |                         |                            |                  |

|------------|-------------------------|----------------------------|------------------|

| (30) 우선권주장 | 0220404.8<br>60/480,502 | 2002년09월03일<br>2003년06월20일 | 영국(GB)<br>미국(US) |

|------------|-------------------------|----------------------------|------------------|

(73) 특허권자

캠브리지 디스플레이 테크놀로지 리미티드

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그린위치 하우스 아이피

디파트먼트

제너럴 일렉트릭 캄파니

미국 뉴욕주 12309 니스케이야우나 씨알디 패튼트 도킷 룸 케이-1/4에이 59

(72) 발명자

아처 로버트

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

베이네스 니콜라스

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

버틀러 티모씨

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

치나 살바토레

프랑스 에프-38000 그레노블르 뤼 카시미르 브레니어 12

포텐 클레어

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

포시트 다니엘

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

리드-비터 마크

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

머피 크레이그

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

파텔 날린쿠마

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

필립스 나탄

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

로버츠 매튜

영국 캠브리지셔 씨비3 0티엑스 캠브리지 매딩리 로드 매딩리 라이즈 그

린위치 하우스 캠브리지 디스플레이 테크놀로지 리미티드내

두갈 아닐 레이즈

미국 뉴욕주 12309 니스카유나 알콘퀸 로드 2322

리우 지

미국 뉴욕주 12309 니스카유나 세이즈몬트 코트 1265

(74) 대리인

김창세

장성구

**심사관 : 구본재**

전체 청구항 수 : 총 29 항

#### (54) 광학 디바이스

#### (57) 요약

본 발명은,

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

가교결합가능한 바이닐 또는 에티닐 기가 없고 증착시 용매에 가용성인 제 1 반도체 물질을 증착시킴으로써, 용매에 적어도 부분적으로 불용성인 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

용매 중의 용액으로부터 제 2 반도체 물질을 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 물질을 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하되,

상기 제 1 층은 상기 제 1 반도체 물질의 증착 후에 가열, 진공 및 주변 건조 처리 중 하나 이상에 의해 적어도 부분적으로 불용성이 되는 광학 디바이스의 제조방법에 관한 것이다.

## 대표도

**특허청구의 범위**

### 청구항 1.

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

가교결합가능한 바이닐 또는 에티닐 기가 없고 증착시 용매에 가용성인 제 1 반도체 물질을 증착시킴으로써, 용매에 완전히 또는 부분적으로 불용성인 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 물질을 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 물질을 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하되,

상기 제 1 층은 상기 제 1 반도체 물질의 증착 후에 가열 처리, 진공 처리 및 대기중 견조 처리 중 하나 이상에 의해 완전히 또는 부분적으로 불용성이 되는 광학 디바이스의 제조방법.

### 청구항 2.

제 1 항에 있어서,

제 1 반도체 물질 및 제 2 반도체 물질 중 하나 이상이 중합체인 광학 디바이스의 제조방법.

### 청구항 3.

제 1 항에 있어서,

제 2 층의 증착 전에 제 1 층을 가열하는 단계를 포함하는 광학 디바이스의 제조방법.

### 청구항 4.

제 1 항에 있어서,

제 2 층을 형성하기 전에, 제 1 반도체 물질이 가용성인 세척 용매로 제 1 층을 세정하는 단계를 포함하는 광학 디바이스의 제조방법.

### 청구항 5.

제 1 항에 있어서,

제 1 층을 용매 중의 용액으로부터 증착시키는 광학 디바이스의 제조방법.

### 청구항 6.

제 1 항에 있어서,

용매가 방향족 탄화수소인 광학 디바이스의 제조방법.

### 청구항 7.

제 6 항에 있어서,

용매가 알킬화 벤젠인 광학 디바이스의 제조방법.

### 청구항 8.

제 7 항에 있어서,

용매가 톨루엔 또는 자일렌인 광학 디바이스의 제조방법.

### 청구항 9.

제 2 항에 있어서,

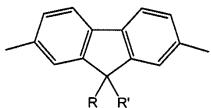

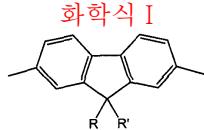

중합체가 하기 화학식 I의 선택적으로 치환된 반복 단위를 포함하는 폴리플루오렌인 광학 디바이스의 제조방법.

화학식 I

상기 식에서,

R 및 R'는 수소 및 선택적으로 치환된 알킬, 알콕시, 아릴, 아릴알킬, 헤테로아릴 및 헤�테로아릴알킬로부터 독립적으로 선택되되, R과 R' 중 하나 이상은 수소가 아니다.

### 청구항 10.

제 9 항에 있어서,

R과 R' 중 하나 이상이 선택적으로 치환된 C<sub>4</sub>-C<sub>20</sub> 알킬 기를 포함하는 광학 디바이스의 제조방법.

### 청구항 11.

제 1 항에 있어서,

제 1 전극이 정공을 주입할 수 있고, 제 2 전극이 전자를 주입할 수 있는 광학 디바이스의 제조방법.

### 청구항 12.

제 11 항에 있어서,

제 1 반도체 중합체가 트라이아릴아민 반복 단위를 포함하는 광학 디바이스의 제조방법.

### 청구항 13.

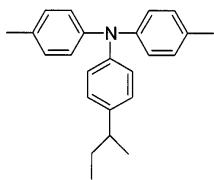

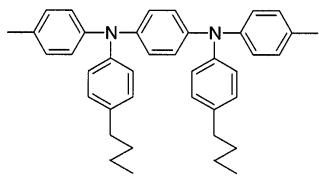

제 12 항에 있어서,

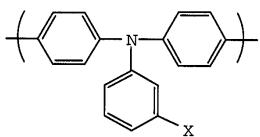

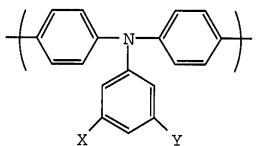

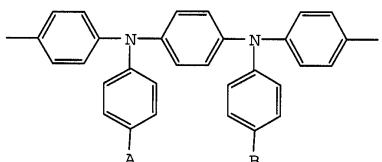

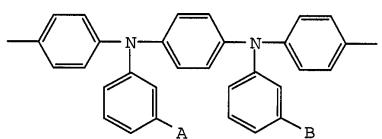

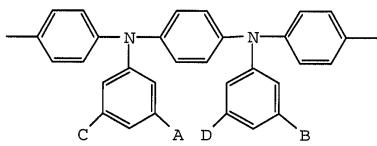

트라이아릴아민 반복 단위가 하기 화학식 1 내지 6의 선택적으로 치환된 반복 단위로부터 선택되는 광학 디바이스의 제조방법.

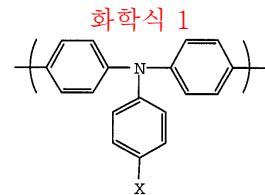

화학식 1

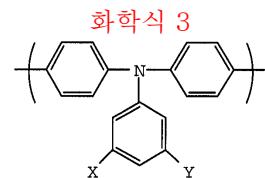

화학식 2

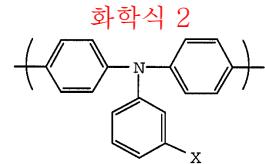

화학식 3

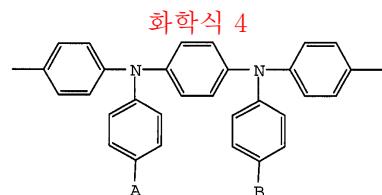

화학식 4

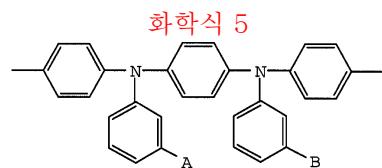

화학식 5

화학식 6

상기 식에서,

X, Y, A, B, C 및 D는 독립적으로 H 및 치환기로부터 선택된다.

청구항 14.

제 13 항에 있어서,

X, Y, A, B, C 및 D 중 하나 이상이 알킬, 아릴, 퍼플루오로알킬, 싸이오알킬, 사이아노, 알콕시, 헤테로아릴, 알킬아릴 및 아릴알킬 기로 이루어진 군으로부터 독립적으로 선택되는 광학 디바이스의 제조방법.

청구항 15.

제 12 항에 있어서,

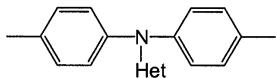

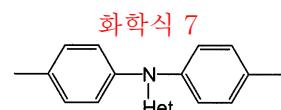

트라이아릴아민 반복 단위가 하기 화학식 7의 선택적으로 치환된 반복 단위인 광학 디바이스의 제조방법.

화학식 7

상기 식에서,

Het는 헤테로아릴이다.

청구항 16.

제 15 항에 있어서,

Het가 4-페리딜인 광학 디바이스의 제조방법.

청구항 17.

제 1 항에 있어서,

제 1 반도체 중합체가, 제 9 항 또는 제 10 항에 정의된 플루오렌 반복 단위와 제 12 항 내지 제 16 항 중 어느 한 항에 정의된 트라이아릴아민 반복 단위의 1:1 규칙적 교호 공중합체를 포함하는 광학 디바이스의 제조방법.

청구항 18.

제 11 항에 있어서,

도전성 유기 물질의 층을 제 1 전극과 제 1 층 사이에 제공하는 광학 디바이스의 제조방법.

### 청구항 19.

제 18 항에 있어서,

도전성 유기 물질의 층이 폴리(에틸렌 디아이옥시 싸이오펜)/폴리스타이렌 셀포네이트(PEDT/PSS)인 광학 디바이스의 제조방법.

### 청구항 20.

제 1 항에 있어서,

제 1 층이 3 내지 20nm의 두께를 갖는 광학 디바이스의 제조방법.

### 청구항 21.

제 20 항에 있어서,

제 1 층이 3 내지 10nm의 두께를 갖는 광학 디바이스의 제조방법.

### 청구항 22.

제 1 항에 있어서,

제 2 반도체 중합체가 다수의 영역을 포함하되, 정공 수송 영역, 전자 수송 영역 및 발광 영역 중 2개 이상을 포함하는 광학 디바이스의 제조방법.

### 청구항 23.

제 22 항에 있어서,

제 2 반도체 중합체가 정공 수송 영역, 전자 수송 영역 및 발광 영역을 포함하는 광학 디바이스의 제조방법.

### 청구항 24.

제 1 항 내지 제 23 항 중 어느 한 항의 방법에 따라 제조가능한 광학 디바이스.

### 청구항 25.

제 1 항 내지 제 23 항 중 어느 한 항의 방법에 따라 제조가능한 유기 전자발광 디스플레이.

### 청구항 26.

제 1 항 내지 제 23 항 중 어느 한 항의 방법에 따라 제조가능한 청색 발광의 전자발광 디스플레이.

### 청구항 27.

제 1 항 내지 제 23 항 중 어느 한 항의 방법에 따라 제조가능한 백색 발광의 유기 전자발광 디스플레이.

### 청구항 28.

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

가교결합가능한 바이닐 또는 에티닐 기가 없는 제 1 반도체 물질을 증착시킴으로써, 용매에 완전히 또는 부분적으로 불용성인 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 제 1 층에 가열 처리를 실시하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 물질을 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 중합체를 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하는 광학 디바이스의 제조방법.

### 청구항 29.

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

플루오렌 반복 단위를 포함하고 가교결합가능한 바이닐 또는 에티닐 기가 없으며 증착시 용매에 가용성인 제 1 반도체 중합체를 증착시킴으로써 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 제 1 층에 가열 처리, 진공 처리 또는 대기중 진조 처리 중 하나 이상을 실시하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 중합체를 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 중합체를 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하는 광학 디바이스의 제조방법.

### 청구항 30.

삭제

### 청구항 31.

삭제

### 청구항 32.

삭제

**청구항 33.**

삭제

**청구항 34.**

삭제

**청구항 35.**

삭제

**청구항 36.**

삭제

**청구항 37.**

삭제

**청구항 38.**

삭제

**청구항 39.**

삭제

**청구항 40.**

삭제

**명세서****기술분야**

본 발명은 불용성 유기 물질 층을 포함하는 유기 광학 디바이스 및 그의 제조방법에 관한 것이다.

**배경기술**

현재, 국제특허공개 제 WO 90/13148 호에 개시된 중합체 발광 다이오드("PLED"), 국제특허공개 제 WO 96/16449 호에 개시된 광전압 디바이스, 및 미국특허 제 5,523,555 호에 개시된 광검출기와 같은 다수의 광학 디바이스에서 전자활성 중합체가 빈번하게 사용되고 있다.

전형적인 PLED는 기판, 그 위에 지지되는 애노드, 캐쓰드, 및 상기 애노드와 상기 캐쓰드 사이에 위치하는 하나 이상의 중합체 전자발광 물질을 포함하는 유기 전자발광 층으로 구성된다. 작동시, 정공은 애노드를 통해 디바이스 내에 주입되고, 전자는 캐쓰드를 통해 디바이스 내에 주입된다. 정공 및 전자는 유기 전자발광 층에서 합쳐져서 엑시톤(exciton)을 형성한 후, 그 다음 방사 감쇠(radiative decay)가 진행되어 광을 생성한다. PLED에는 다른 층들이 존재할 수 있다. 예를 들면, 폴리(에틸렌 디이옥시 싸이오펜)/폴리스타이렌 설포네이트(PEDT/PSS)와 같은 유기 정공 주입 물질 층은 애노드와 유기 전자발광 층 사이에 제공되어 정공이 상기 애노드로부터 상기 유기 전자발광 층으로 주입되는 것을 돋는다.

전형적인 PLED에서, 전자발광 물질은, 예를 들어 국제특허공개 제 WO 99/48160 호에 기재된 바와 같이 정공 수송 중합체, 전자 수송 중합체 및 발광 중합체(emissive polymer)의 블렌드를 포함하는 단층으로서 제공된다. 다르게는, 단일 중합체는 정공 수송, 전자 수송 및 발광의 기능 중 둘 이상을 제공할 수 있다. 전자발광 중합체 또는 중합체들은 바람직하게는 통상의 유기 용매에 대해 가용성이어서 이들의 증착을 촉진시킨다. 이러한 부류의 가용성 중합체 중 하나는, 우수한 제막 특성을 갖는 것으로, 생성된 중합체의 위치규칙성(regioregularity)에 대해 높은 제어도를 부여할 수 있는 스즈키(Suzuki) 또는 야마모토(Yamamoto) 중합에 의해 용이하게 제조될 수 있는 폴리플루오렌이다.

그러나, 개별 기능들, 예컨대 전자 또는 정공 전하 수송, 발광, 광-유도 전하 생성 및 전하 차단 또는 저장의 최적화를 달성 할 수 있도록, 상이한 중합체로 이루어진 다층, 즉 적층물을 단일 기판 표면에 캐스팅하는 것이 바람직할 수 있다. 또한, PEDT/PSS는 양성자 또는 설포네이트 기가 PSS로부터 전자 발광 층(즉, 정공 및 전자가 결합하여 엑시톤을 형성하는 층) 내로 침투하여 발광을 소광시킴으로써 전자발광 층에 대해 악영향을 미칠 수 있는 것으로 생각된다. 따라서, PEDT/PSS와 전자발광 층 사이에 보호 층을 제공하는 것이 바람직할 수 있다. 그러나, 중합체 적층물의 제조는 연속 층에 사용되는 용매 중에서의 초기 캐스트 또는 증착된 층의 가용성 때문에 문제가 될 수 있다.

전자발광 중합체의 층들은 이후에 불용성 전자발광 형태로 화학적으로 전환되는 가용성 중합체 전구물질을 증착시킴으로써 형성될 수 있다. 예를 들어, 국제특허공개 제 WO 94/03030 호에는, 가용성 전구물질로부터 불용성 전자발광 폴리(페닐렌 바이닐렌)을 형성시킨 후, 이 불용성 층에 추가의 층을 용액으로부터 증착시키는 방법이 개시되어 있다. 그러나, 화학적 전환 공정은 극도의 가공 조건과, 마무리처리된 디바이스의 성능에 해를 미칠 수 있는 반응성 부산물을 포함한다. 따라서, 통상의 유기 용매에 가용성인 전자발광 중합체가 바람직하다. 이러한 물질의 예는 예컨대 문헌 [Adv. Mater. 2000 12 (23) 1737-1750]에 개시되어 있으며, 가용화 기를 갖는 폴리플루오렌, 폴리페닐렌 및 폴리(아릴렌 바이닐렌)과 같은 전체 또는 적어도 부분적으로 공액된 주체를 갖는 중합체, 및 폴리(바이닐 카바졸)과 같은 비공액된 주체를 갖는 중합체를 들 수 있다.

국제특허공개 제 WO 98/05187 호에는 폴리(바이닐 피리딘) 층을 PEDT/PSS에 증착시키는 단계 및 PPV 전구물질을 폴리(바이닐 피리딘) 층에 증착시키는 단계를 포함하는 다층 디바이스의 제조방법이 개시되어 있다. 상기에서와 같이, 이 전구물질로 반도체 물질을 전환시키기 위해 가혹한 가공 조건이 요구된다.

미국특허 제 6,107,452 호에는, 말단 바이닐 기를 포함하는 플루오렌-함유 올리고머를 용액으로부터 증착시키고 가교결합시켜 불용성 중합체(그 위에 추가의 층이 증착될 수도 있음)를 형성하는 다층 디바이스의 제조방법이 개시되어 있다. 유사하게, 김(Kim) 등의 문헌 [Synthetic Metals 122 (2001), 363-368]에는 가교결합되어 중합체가 증착될 수 있는, 트라이아릴아민 기 및 에티닐 기를 포함하는 중합체가 개시되어 있다. 양자의 경우에 중합체의 선택은 복수의 바이닐 또는 에티닐 잔기가 존재해야 하는 요구조건에 의해 제한된다.

문헌 [IEEE Transactions on Electron Devices, 44(8), 1263-1268, 1997]에는 폴리(바이닐 카바졸) (PVK) 및 피리딘-함유 공액된 중합체의 2중층의 형성이 개시되어 있다. 이는 피리딘-함유 공액된 중합체를 증착시키는데 사용되는 용매가 PVK의 하부 층을 용해시키지 않기 때문에 가능하다.

리우(J. Liu), 구오(Z.F. Guo) 및 양(Y. Yang)의 문헌 [J. Appl Phys. 91, 1595-1600, 2002]에는 반도체 중합체를 증착 및 가열한 후, 동일한 중합체의 다른 층을 증착시킴으로써 다층 디바이스를 제조하는 것이 개시되어 있다.

국제특허공개 제 WO 99/48160 호에는 정공 수송 물질 층을 PEDT/PSS 층과 전자발광 물질 층 사이에 제공한 PLED가 개시되어 있다.

PLED를 비롯한 다층 중합체 광학 디바이스를 제작하기 위해 많은 노력을 기울여 왔지만, 개선된 성능을 갖는 다층 중합체 광학 디바이스, 및 이러한 디바이스를 제조하는 방법에 대한 지속적인 필요성은 여전히 존재한다.

### 발명의 요약

제 1 양태에서, 본 발명은

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

가교결합가능한 바이닐 또는 에티닐 기가 없고 증착시 용매에 가용성인 제 1 반도체 물질을 증착시킴으로써, 용매에 적어도 부분적으로 불용성인 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 물질을 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 물질을 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하되,

상기 제 1 층은 상기 제 1 반도체 물질의 증착 후에 가열 처리, 진공 처리 및 대기중(ambient) 건조 처리 중 하나 이상에 의해 적어도 부분적으로 불용성이 되는 광학 디바이스의 제조방법을 제공한다.

바람직하게는, 제 1 반도체 물질 및 제 2 반도체 물질 중 하나 이상은 중합체이다. 보다 바람직하게는, 제 1 반도체 물질 및 제 2 반도체 물질은 둘다 중합체이다.

바람직하게는, 상기 방법은 제 2 층을 형성하기 전에 제 1 층을 가열하는 단계를 포함한다. 보다 바람직하게는, 제 1 층은 제 1 반도체 물질의 유리전이온도를 초과하는 온도에서 가열된다.

본원에서 사용된 "대기중 건조 처리"는 가열 또는 진공을 포함하지 않고 용매를 제 1 층으로부터 증발시키는 처리를 의미한다. 특히, 대기중 건조 처리는 대기 조건 하에서 선택적으로는 불활성 기체 스트림의 존재 하에 제 1 층으로부터 용매를 증발시키는 것을 수반할 수 있다.

바람직하게는, 상기 방법은 제 2 층의 형성 이전에 제 1 반도체 물질이 용해될 수 있는 세척 용매로 제 1 층을 세척하는 단계를 포함한다.

바람직하게는, 제 1 층은 용매 중의 용액으로부터 증착된다.

바람직하게는, 용매는 방향족 탄화수소이고, 보다 바람직하게는 알킬화된 벤젠이고, 가장 바람직하게는 툴루엔 또는 자일렌이다.

바람직하게는, 제 1 반도체 물질은 바이닐 또는 에티닐 기 이외에 가교결합가능한 기가 존재하지 않는다.

제 1 및 제 2 반도체 물질 중 하나 또는 이들 모두가 중합체인 경우, 제 1 및 제 2 반도체 중합체의 반복 단위는 인접 반복 단위와 공액되어 적어도 부분적으로 공액된 중합체 주쇄를 형성하는 것이 바람직하다.

바람직하게는 이러한 중합체는 9-치환된 또는 9,9-이치환된 플루오렌-2,7-다이일 반복 단위, 가장 바람직하게는 화학식 I의 선택적으로 치환된 단위를 포함한다:

상기 식에서,

R 및 R'는 독립적으로 수소이거나, 또는 선택적으로 치환된 알킬, 알콕시, 아릴, 아릴알킬, 헤테로아릴 및 헤테로아릴알킬에서 선택되되, R과 R' 중 하나 이상은 수소가 아니다. 보다 바람직하게는, R과 R' 중 하나 이상은 선택적으로 치환된 C<sub>4</sub>–C<sub>20</sub> 알킬 기를 포함한다.

본 발명의 방법에 의해 제조된 디바이스의 바람직한 제 1 실시양태에서, 제 1 전극은 정공을 주입 또는 수용할 수 있고, 제 2 전극은 전자를 주입 또는 수용할 수 있다. 이 실시양태에서, 도전성 유기 물질의 층은 바람직하게는 제 1 전극 및 제 1 층 사이에 제공된다. 도전성 유기 물질은 전하 균형(charge balancing) 도판트를 갖는 대전된 종(특히 대전된 중합체)을 전형적으로 포함한다. 도전성 중합체의 예는 전하 균형 폴리산 또는 도전성 형태의 폴리아닐린을 갖는 PEDT이다. 바람직하게는, 도전성 유기 물질의 층은 PEDT/PSS이다.

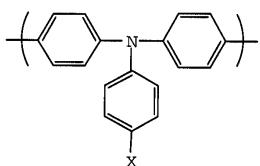

이 실시양태에서, 바람직하게는 제 1 반도체 물질은 정공 수송 물질, 보다 바람직하게는 트라이아릴아민 반복 단위를 포함하는 중합체를 포함한다. 특히 바람직한 트라이아릴아민 반복 단위는 하기 화학식 1 내지 6의 선택적으로 치환된 반복 단위로부터 선택된다.

상기 식에서,

X, Y, A, B, C 및 D는 수소이거나, 또는 치환기로부터 선택된다. 보다 바람직하게는, X, Y, A, B, C 및 D중 하나 이상은 독립적으로 알킬, 아릴, 퍼플루오로알킬, 싸이오알킬, 사이아노, 알콕시, 헤테로아릴, 알킬아릴 및 아릴알킬 기로 구성된 군에서 선택된다.

또한, 트라이아릴아민 반복 단위로서 특히 바람직한 것은 화학식 7의 선택적으로 치환된 반복 단위이다.

상기 식에서,

Het는 헤테로아릴이다. 가장 바람직하게는, Het는 4-페리딜이다.

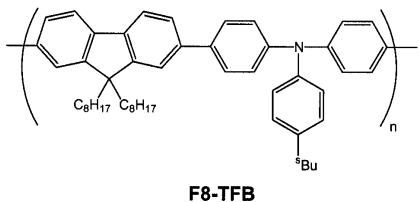

바람직하게는, 제 1 반도체 물질은 플루오렌 반복 단위와 트라이아릴아민 반복 단위의 1:1 규칙적 교호 공중합체를 포함한다.

본 발명의 방법에 의해 제조된 디바이스의 바람직한 제 2 실시양태에서, 제 1 전극은 전자를 주입 또는 수용할 수 있고, 제 2 전극은 정공을 주입 또는 수용할 수 있다. 이 실시양태에서, 제 1 반도체 물질은 바람직하게는 전자 수송 물질, 바람직하게는 선택적으로 치환된 9,9-다이알킬플루오렌-2,7-다이일의 단독중합체를 포함한다.

바람직하게는, 제 1 층은 20nm 미만, 보다 바람직하게는 10nm 미만, 가장 바람직하게는 3 내지 10nm 범위의 두께를 갖는다.

바람직하게는, 제 2 반도체 중합체는 정공 수송 영역, 전자 수송 영역 및 발광 영역 중 둘 이상, 보다 바람직하게는 이들 영역 모두를 포함하는 복수의 영역을 포함한다.

제 2 양태에서, 본 발명은 바람직하게는 본 발명의 방법에 따라 제조될 수 있는 광학 디바이스를 제공한다. 바람직하게는, 광학 디바이스는 전자발광 디바이스, 특히 청색 발광 전자발광 디바이스이다. 청색 발광 디바이스의 발광부는 상기 청색 광을 다운컨버팅(downconverting)시켜 적색 및 녹색 광을 생성할 수 있는 인광체(phosphor)를 사용하여 다운컨버팅되어 백색 발광 전자발광 디바이스를 제공할 수 있다.

본 발명의 방법은 제 1 층이 특히 얇은 중합체 적층물을 형성할 수 있다. 따라서, 제 3 양태에서, 본 발명은 기판;

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극;

용매에 불용성인 제 1 반도체 중합체를 포함하는 두께 20nm 미만의 제 1 층;

용매에 가용성인 제 2 반도체 중합체를 포함하는, 상기 제 1 층과 접촉하는 제 2 층; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 순차적으로 포함하는 광학 디바이스를 제공한다.

제 4 양태에서, 본 발명은

정공을 주입 또는 수용할 수 있고 양성자를 공여할 수 있는 도전성 유기 물질을 포함하는 기판을 제공하는 단계;

양성자를 수용할 수 있고 증착시 용매에 가용성인 제 1 반도체 중합체를 증착시킴으로써 상기 도전성 유기 물질과 접촉하여 그 위에 제 1 층을 형성하는 단계;

상기 제 1 층에 가열 처리, 진공 처리 및 대기중 건조 처리 중 하나 이상을 실시하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 중합체를 상기 제 1 층과 접촉하여 그 위에 증착시킴으로써, 제 2 층을 형성하는 단계; 및

전자를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하는 광학 디바이스의 제조방법을 제공한다.

바람직하게는, 제 1 반도체 중합체는 트라이아릴아민 반복 단위를 포함한다. 보다 바람직하게는, 트라이아릴아민 반복 단위는 전술한 화학식 1 내지 7의 반복 단위 중에서 선택된다.

바람직하게는, 제 1 반도체 중합체는 플루오렌 반복 단위와 트라이아릴아민 반복 단위의 1:1 규칙적 교호 공중합체를 포함한다.

바람직하게는, 정공을 주입 또는 수용할 수 있는 무기 물질 층이 기판과 도전성 유기 물질 사이에 제공된다. 보다 바람직하게는, 정공을 주입 또는 수용할 수 있는 무기 물질이 인듐 주석 산화물이다.

바람직하게는, 도전성 유기 물질이 PEDT/PSS이다.

#### 제 5 양태에서, 본 발명은

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

가교결합가능한 바이닐 또는 에티닐 기가 없는 제 1 반도체 물질을 증착시킴으로써, 용매에 적어도 부분적으로 불용성인 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 제 1 층에 가열 처리를 실시하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 물질을 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 중합체를 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하는 광학 디바이스의 제조방법을 제공한다.

바람직하게는, 본 발명의 제 5 양태에 따른 제 1 반도체 물질과 제 2 반도체 물질 중 하나 이상, 보다 바람직하게는 둘다가 중합체이다.

이러한 본 발명의 제 5 양태에 따른 제 1 반도체 물질은 제 2 반도체 중합체의 증착을 위해 사용된 용매에 가용성이거나 불용성일 수 있다.

#### 제 6 양태에서, 본 발명은,

제 1 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 1 전극을 포함하는 기판을 제공하는 단계;

플루오렌 반복 단위를 포함하고 가교결합가능한 바이닐 또는 에티닐 기가 없으며 증착시 용매에 가용성인 제 1 반도체 중합체를 증착시킴으로써 제 1 층을 상기 제 1 전극 상에 형성하는 단계;

상기 제 1 층에 가열 처리, 진공 처리 또는 대기중 건조 처리 중 하나 이상을 실시하는 단계;

상기 용매 중의 용액으로부터 제 2 반도체 중합체를 증착시킴으로써, 상기 제 1 층과 접촉하고 제 2 반도체 중합체를 포함하는 제 2 층을 형성하는 단계; 및

제 2 유형의 전하 캐리어를 주입 또는 수용할 수 있는 제 2 전극을 상기 제 2 층에 형성하는 단계를 포함하는 광학 디바이스의 제조방법을 제공한다.

본 발명의 임의의 양태에 따른 제 1 반도체 중합체와 제 2 반도체 중합체가 상이하다. 예를 들어, 제 1 중합체 및 제 2 중합체는 2개의 중합체의 분자량이 상이할 수도 있다. 선택적으로 또는 부가적으로, 제 1 중합체 및 제 2 중합체는 중합체내에서 반복 단위의 위치규칙성 측면에서 상이할 수도 있다. 가장 바람직하게는, 제 1 중합체 및 제 2 중합체는, 제 1 중합체 및 제 2 중합체 중 하나가 다른 중합체 내에 존재하지 않은 하나 이상의 형태의 반복 단위를 포함한다는 점에서 상이하다. 따라서, 예를 들면, 반복 단위의 위치규칙성 및/또는 화학적 동질성의 측면에서 제 1 중합체와 제 2 중합체 사이의 차이점으로 인하여, 제 1 중합체는 증착되는 경우 정공 수송 층을 형성하고, 제 2 중합체는 증착되는 경우 전자발광 층을 형성할 수 있다. 제 2 층은 제 2 반도체 중합체 단독으로 구성될 수 있거나 제 2 반도체 중합체를 포함하는 블렌드일 수 있다.

"적색 광"이란 용어는, 600 내지 750nm의 파장을 갖는 방사선, 바람직하게는 600 내지 700nm의 파장을 갖는 방사선, 보다 바람직하게는 610 내지 650nm의 파장을 갖는 방사선, 가장 바람직하게는 650 내지 660nm 사이에 발광 피크를 갖는 방사선을 의미한다.

"녹색 광"이란 용어는, 510 내지 580nm, 바람직하게는 510 내지 570nm의 파장을 갖는 방사선을 의미한다.

"청색 유기광"이란 용어는, 400 내지 500nm, 보다 바람직하게는 430 내지 500nm의 파장을 갖는 방사선을 의미한다.

본원에서 사용되는 바와 같이 "정공 수송", "전자 수송" 및 "발광성"이란 의미는, 예를 들어 국제특허공개 제 WO 00/55927 호 및 국제특허공개 제 WO 00/46321 호에 설명되어 있고 당업계의 숙련자들에게 공지되어 있다.

### 발명의 상세한 설명

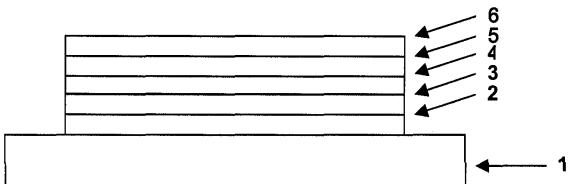

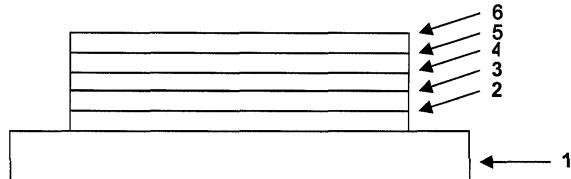

도 1을 참조하면, 본 발명의 방법에 따라 제조된 PLED 또는 광전압 디바이스는 기판(1), 인듐 주석 산화물의 애노드(2), 유기 정공 수송 물질 층(3), 제 1 가용성 반도체 중합체의 증착에 의해 제조된 불용성 물질 층(4), 제 2 반도체 중합체의 증착에 의해 제조된 층(5) 및 캐쏘드(6)를 포함한다.

광학 디바이스는 수분과 산소에 민감한 경향이 있다. 따라서, 기판은 수분 및 산소의 디바이스 내로의 침투를 방지하는 우수한 차단 특성을 갖는 것이 바람직하다. 상기 기판은 통상 유리이지만, 특히 디바이스의 유연성이 요구되는 경우 다른 기판이 사용될 수 있다. 예컨대, 기판은 플라스틱과 차단층이 교호하는 기판을 개시하고 있는 미국특허 제 6268695 호에서와 같이 플라스틱, 또는 유럽특허 제 0949850 호에 개시된 얇은 유리와 플라스틱의 적층물을 포함할 수 있다.

본질적이지는 않지만, 애노드로부터 반도체 중합체 층 또는 층들 내로의 정공 주입을 보조하기 때문에, 유기 정공 주입 물질 층(3)이 존재하는 것이 바람직하다. 유기 정공 주입 물질의 예로는 유럽특허 제 0901176 호 및 유럽특허 제 0947123 호에 개시된 PEDT/PSS, 또는 미국특허 제 5723873 호 및 미국특허 제 5798170 호에 개시된 폴리아닐린을 들 수 있다.

캐쏘드(6)는 전자가 디바이스 내로 효율적으로 주입될 수 있도록 선택되며 이는 알루미늄 층 등의 단일 도전성 물질로 이루어질 수 있다. 또한, 다수의 금속, 예컨대 국제특허공개 제 WO 98/10621 호에 개시된 칼슘과 알루미늄의 이중층, 또는 국제특허공개 제 WO 00/48258 호에 개시된 전자 주입을 보조하는 불화리튬 등의 유전물질 박층을 포함할 수 있다.

디바이스는 밀봉제(도시되지 않음)로 밀봉되어 수분과 산소의 침입을 방지하는 것이 바람직하다. 적합한 밀봉제는 예컨대 국제특허공개 제 WO 01/81649 호에 개시된 중합체와 유전재의 교호적 스택 등과 같이 적합한 차단 특성을 갖는 유리, 필름 시이트 또는 예컨대 국제특허공개 제 WO 01/19142 호에 개시된 기밀 용기를 들 수 있다.

실제 디바이스에서, 전극 중 하나 이상은 반투명성이어서 광을 흡수하거나(감광성 디바이스의 경우) 방출할 수 있다 (PLED의 경우). 애노드가 투명한 경우, 이는 인듐 주석 산화물을 포함하는 것이 전형적이다. 투명한 캐쏘드의 예는 예컨대 영국특허 제 2348316 호에 개시되어 있다.

불용성 층(4)은 바람직하게는 플루오렌 반복 단위를 포함하는 중합체를 포함한다. 불용성 층이 애노드와 층(5) 사이에 위치하는 경우, 도 1의 실시양태에서 따라, 정공을 수송할 수 있는 반도체 중합체, 예컨대 국제특허공개 제 WO 99/54385 호에 개시된 플루오렌 반복 단위와 트라이아릴아민 반복 단위의 공중합체로 형성되는 것이 바람직하다. 다르게는, 불용성 층은 캐쏘드 상에 증착될 수 있다. 이 경우, 불용성 층은 전자를 수송할 수 있는 반도체 중합체, 예컨대 유럽특허 제 0842208 호에 개시된 바와 같은 플루오렌의 단독중합체로 형성되는 것이 바람직하다.

불용성 층(4)은 제 1 반도체 중합체의 증착에 의해 형성된다. 증착되는 층은 전체가 불용성이거나 부분적으로 불용성일 수 있다. 제 1 층이 부분적으로만 불용성인 경우, 층 내에서 불용성 부분은 증착시 층의 가열에 의해 증가될 수 있다. 임의의 가용성 제 1 반도체 중합체는 적절한 용매 중에서 린싱에 의해 층으로부터 제거되어 전체가 불용성인 층으로 만들 수 있다.

층(5)을 형성하는데 사용된 본 발명에 따른 제 2 반도체 중합체는 불용성 층(4)을 형성하는데 사용된 제 1 반도체 중합체와 동일한 용매 중에서 가용성인 임의의 반도체 중합체일 수 있다. 적합한 제 2 반도체 중합체의 예로는 문헌 [Adv. Mater. 2000 12(23) 1737-1750] 및 그의 참조문헌에 개시된 가용성 폴리(p-페닐렌 바이닐렌), 폴리페닐렌 및 폴리플루오렌을 들 수 있다. 단일 중합체 또는 다수의 중합체를 용액으로부터 증착시켜 층(5)을 형성할 수 있다. 다수의 중합체가 증착되는 경우, 이들은 바람직하게는 국제특허공개 제 WO 99/48160 호에 개시된 바와 같이 정공 수송 중합체, 전자 수송 중합체, 및 디바이스가 PLED인 경우 발광 중합체 중 2종 이상의 블렌드를 포함한다. 다르게는, 층(5)은 예컨대 국제특허 공개 제 WO 00/55927 호 및 미국특허 제 6353083 호에 개시된 바와 같이 정공 수송 영역, 전자 수송 영역 및 발광 영역 중 2개 이상으로부터 선택된 영역을 포함하는 단일 제 2 반도체 중합체로부터 형성될 수 있다. 각각의 정공 수송, 전자 수송 및 발광 기능은 단일 중합체의 개별 영역 또는 개별 중합체로 제공될 수 있다. 다르게는, 하나 이상의 기능이 단일 영역 또는 중합체에 의해 수행될 수 있다. 특히, 단일 중합체 또는 영역은 전하 수송과 발광이 모두 가능할 수 있다. 각 영역은 단일 반복 단위로 이루어질 수 있으며, 예컨대 트라이아릴아민 반복 단위는 정공 수송 영역일 수 있다. 다르게는, 각 영역은

전자 수송 영역으로서의 폴리플루오렌 단위의 쇄와 같은 반복 단위의 쇄일 수 있다. 이와 같은 중합체 내의 서로 다른 영역은 미국특허 제 6353083 호에서와 같이 중합체 주쇄를 따라 제공되거나, 또는 국제특허공개 제 WO 01/62869 호에서와 같이 중합체 주쇄로부터의 팬던트 기로서 제공될 수 있다. 불용성 층(4)이 정공 또는 전자 수송 특성을 보유하는 경우, 이러한 특성을 갖는 중합체 또는 중합체 영역은 선택적으로 층(5)을 이루는 중합체 또는 중합체들로부터 배제될 수 있다.

본 발명에 따른 제 1 중합체 및 제 2 중합체는 모두 반도체이다. 어느 하나의 중합체의 주쇄는 적어도 부분적으로 공액되거나 그렇지 않을 수 있다. 적어도 부분적으로 공액된 주쇄를 갖는 반도체 중합체의 예는 상기한 바와 같이 폴리아릴렌, 예컨대 폴리플루오렌 및 폴리페닐렌, 및 폴리(아릴렌 바이닐렌)을 포함한다. 또한, 본 발명은 예컨대 폴리(바이닐카바졸) 등의 공액된 주쇄를 갖지 않는 제 1 반도체 중합체 및 제 2 반도체 중합체를 포함한다.

본 발명의 방법에 따라 제조된 광학 디바이스는 제 1 전극 및 제 2 전극이 전하 캐리어를 주입하는 경우 바람직하게는 PLED이다. 이 경우, 층(5)은 발광 층이다.

광학 디바이스는 바람직하게는 제 1 및 제 2 전극이 전하 캐리어를 수용하는 경우 광전압 디바이스 또는 광검출기이다. 이 경우, 제 2 층은 바람직하게는 정공 및 전자 수송이 가능한 중합체 또는 중합체들을 포함한다.

본 발명자들은 반도체 중합체의 다중 층을 제공하여 제조하는 경우 중합체 광학 디바이스의 성능이 개선될 수 있음을 놀랍게도 발견하였다. 제 1 층과 제 2 층의 임의의 실질적인 혼합을 방지하기 위해, 본 발명자들은 제 1 층의 적합한 처리, 특히 가열 처리가 제 1 층이 불용성이 되게 하는 것을 놀랍게도 발견하였다.

본 발명자들은 가교결합(예컨대, 바이닐 또는 에티닐) 잔기 없이 플루오렌 반복 단위를 포함하는 반도체 중합체가 불용성 층(4)을 형성하도록 증착되는 경우 부분적으로 불용성이 되는 것을 놀랍게도 발견하였다. 본 발명자들은 (a) PEDT/PSS 층이 사용되거나 사용되지 않는 것에 상관없이 및 (b) 공기 중 또는 질소 만의 환경에서 이 불용성 층을 형성함을 발견하였다. 그러나, 본 발명자들은 플루오렌의 증착에 이어 이 불용성 층을 가열 처리, 진공 처리 또는 대기중 건조 처리를 실시하여 디바이스 성능을 최대화하고 특히 제 1 층의 불용성을 증가시킴으로써 제 2 층과 제 1 층의 혼합을 최소화할 필요가 있음을 발견하였다. 어떠한 이론에 속박되지 않기를 바라면서, 제 1 층의 형성시 용해성의 소실에 대한 가능한 메카니즘으로는, 중합체로부터 용매의 제거 후, 제 1 반도체 중합체 내의 플루오렌 반복 단위의 9-위치에 부착된 가용성 기의 소실 또는 제 1 반도체 중합체가 증착되는 표면에의 부착을 포함한다.

본 발명자들은 또한 다른 반도체 중합체, 예컨대 폴리(바이닐 카바졸)(PVK)이 본 발명에 따른 조건 하에서 불용성 층을 형성할 수 있음을 발견하였다.

앞서 개략적으로 설명한 바와 같이, 층(4)은 본 발명의 방법에 사용되는 중합체 증착 및 용매 증발에 전형적으로 사용되는 조건 하에서 층(5)의 증착에 사용되는 용매에서의 용해에 저항성이 있다. 또한, 층(4)은 상기 용매로 린싱 처리하는 경우에도 용해에 저항성이 있는 것으로 알려져 있다. 강제 조건 하에 상기 용매 중에서 층(4)의 용해가 가능할 수 있지만, 상기 용매 중의 반도체 중합체의 증착에 전형적으로 사용되는 조건 하에서 본 발명에 따른 다수의 전기활성 유기 층의 형성을 가능하게 할 정도로 충분히 층(4)이 불용성임을 이해할 수 있을 것이다. 따라서, "불용성"이란 용어는 이와 같이 해석되어야 한다.

기재한 처리는 PLED의 효율 및 수명을 개선시키는 것으로 알려져 있다. 어떠한 이론에 속박되지 않기를 바라면서, 하기 요소들이 이러한 관찰되는 증가에 원인이 될 수 있다.

- 제 1 층은 애노드와 제 2 층 사이에 배치되는 경우 정공 수송, 전자 차단층으로 작용할 수 있다.

- PEDT/PSS 층이 사용되는 경우, 불용성 층은 산성 PSS 물질로부터 제 2 층으로의 양성자의 침입을 방지할 수 있다. 이는 중합체가 양성자를 수용할 수 있는 염기성 단위, 예컨대 화학식 1 내지 6의 아민 또는 화학식 7의 범위 내의 Het 그룹, 예컨대 피리딜 등을 포함하는 경우 특히 적용할 수 있다.

- 특히 스판 린싱 단계가 이용되는 경우 달성되는 층의 얇기 정도는 보다 두꺼운 층으로부터 기인하는 디바이스 성능, 예컨대 더욱 높은 구동 전압에 해를 미치는 일 없이 전하 차단을 가능하게 할 수 있다.

## 실시예

### 일반 절차

제 1 반도체 중합체로서 하기 예시되며 국제특허공개 제 WO 99/54385 호에 개시되어 있는 중합체 "F8-TFB"를 이용하여 본 발명을 예시하였다.

F8-TFB

일반적인 절차는 하기 예시된 단계를 따른다:

- 1) 바이엘(Bayer, 등록상표)에서 베이트론(Baytron) P(등록상표)서 구입가능한 PEDT/PSS를 유리 기판(미국 콜로라도 소재의 어플라이드 필름즈(Applied Films)에서 구입가능)상에 지지된 인듐 주석 산화물 상에 스핀 코팅에 의해 증착시키는 단계.

- 2) 2% w/v의 농도를 갖는 자일렌 용액으로부터의 스핀 코팅에 의해 정공 수송 중합체 층을 증착시키는 단계.

- 3) 불활성(질소) 환경에서 정공 수송 물질 층을 가열하는 단계.

- 4) 선택적으로 상기 기판을 자일렌중에서 스핀-린싱 처리하여 임의의 잔여 가용성 정공 수송 물질을 제거하는 단계.

- 5) 제 2 반도체 중합체를 자일렌 용액으로부터 스핀-코팅에 의해 증착시키는 단계.

- 6) 국제특허공개 제 WO 03/012891 호에 기술된 공정에 따라 NaF/Al 캐쏘드를 제 2 반도체 중합체 위에 증착시키고 사에스 게터스 에스피에이(Saes Getters SpA)에서 구입가능한 기밀 금속 엔클로저(enclosure)를 사용하여 디바이스를 봉입하는 단계.

상기 일반 절차에서 파라미터는 변화할 수 있다. 특히, F8-TFB의 농도는 약 3% w/v 이하일 수 있고 0.5% w/v의 농도를 사용하여 특히 얇은 필름을 제공할 수 있으며; 선택적인 가열 단계는 약 2시간 이하의 임의의 시간 동안 지속될 수 있고; 선택적인 가열 단계는 약 220°C 이하의 임의의 온도, 바람직하게는 증착된 중합체의 유리전이온도를 초과하는 온도에서 이루어질 수 있다. 당업자에게 명백한 바와 같이, 제 1 및/또는 제 2 중합체, 및 PEDT/PSS와 같은 다른 디바이스 성분은 가열 온도가 너무 높으면 열 분해될 수 있으므로, 가열 온도는 그에 따라 선택되어야 한다. 최종적으로, 본 발명자들은 제 1 층의 두께가 제 1 반도체 중합체의 분자량(Mw)을 적절히 선택함에 의해 조정될 수 있다는 것을 발견했다. 따라서, 50,000의 Mw를 갖는 F8-TFB는 약 2nm 정도의 두께를 가지지만, 약 250,000 내지 300,000의 Mw에 대해서는 약 15nm 이하의 두께를 갖는다.

#### 실시예 1

F8-TFB를 제 1 반도체 중합체로서 사용하고, 70% 9,9-다이옥틸플루오렌-2,7-다이일, 10% 9,9-다이페닐플루오렌-2,7-다이일, 10% "TFB" 반복 단위 및 10% "PFB" 반복 단위를 포함하는 청색 전자발광 중합체를 제 2 반도체 중합체 (F8-TFB 중합체, TFB 및 PFB 반복 단위는 하기 예시되며 예를 들어 국제특허공개 제 WO 99/54385 호에 기술되어 있다)로서 사용함으로써 상기 일반적 절차를 따랐다. 제 1 반도체 중합체 및 제 2 반도체 중합체는 예를 들어 국제특허공개 제 WO 00/53656 호에 개시된 바와 같은 스즈키 중합에 의해 제조되었다.

F8-TFB의 제 1 반도체 층을 180°C에서 1시간 동안 가열 처리한 후 제 2 반도체 중합체를 증착시켰다.

“TFB”

“PFB”

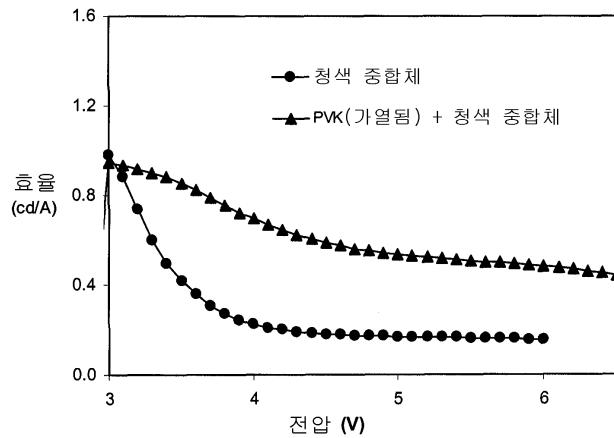

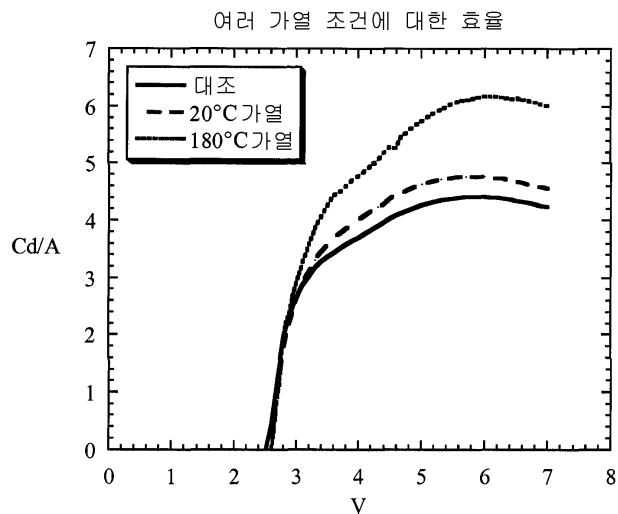

도 2는 본 발명에 따른 가열 처리의 효율에 대한 효과를 나타낸다. 3개의 디바이스를 비교하였다: 실시예 1의 디바이스(F8-TFB 제 1 층을 180°C로 가열함); F8-TFB의 제 1 층이 제공되지 않은 제 1 대조 디바이스(즉, 단계 2 내지 4가 제외됨); 및 가열 단계 3을 거치지 않은 F8-TFB의 제 1 층을 갖는 제 2 대조 디바이스. 제 1 대조 디바이스와 제 2 대조 디바이스에 대한 결과를 비교하여 알 수 있는 바와 같이, F8-TFB의 층을 포함시킴으로써 효율이 개선되지만(국제특허공개 제 WO 99/48160 호에 보고된 바와 같이), 가장 유의적인 개선은 본 발명에 따른 디바이스, 즉 F8-TFB 층이 가열된 디바이스에서 유도된다.

### 실시예 2

3% 4,7-비스(2-싸이오펜-5-일)-2,1,3-벤조싸이아다이아졸 반복 단위(국제특허공개 제 WO 01/49768에 개시됨), 80% 9,9-다이옥틸플루오렌-2,7-다이일, 30% 2,1,3-벤조싸이아다이아졸-4,7-다이일 반복 단위 및 17% TFB 반복 단위를 포함하는 적색 전자발광 중합체가 제 2 반도체 중합체(이후 "적색 중합체"라 지칭함)로서 사용되는 점을 제외하고는 실시예 1의 절차를 따랐다.

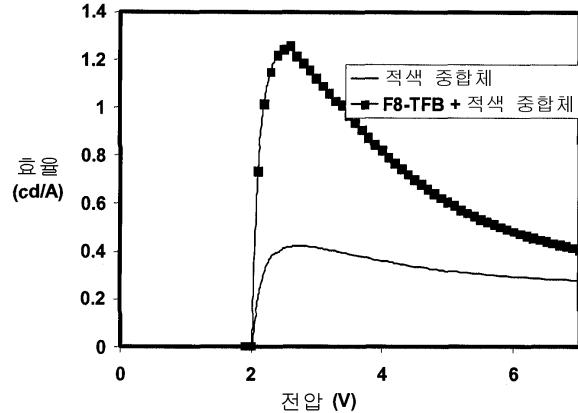

도 3은 본 디바이스에 대한 효율 대 바이어스의 플롯 및 F8-TFB의 불용성 층이 제공되지 않은 적색 중합체를 포함하는 대조 디바이스(즉, 단계 2 내지 4가 생략됨)와의 비교를 도시한다.

### 실시예 3

폴리(9-바이닐카바졸)(PVK)을 제 1 반도체 중합체(알드리치(Aldrich) 카탈로그 넘버 18260-5; 평균 Mw 약 1,100,000)로서 사용하고 아메리칸 다이 소스 인코포레이티드(American Dye Source, Inc)에서 구입한 청색 발광 중합체 폴리(9,9-다이헥실플루오렌일-2,7-다이일)(PFO)(카탈로그 넘버 ADS130BE; 평균 Mw 약 300,000)을 사용하여 상기 일반 절차를 따랐다.

PVK의 층을 200°C에서 1시간 동안 가열한 후 PFO의 층을 증착시켰다.

도 5는 중간 PVK 층이 가열 처리되거나 대기중 건조 처리될 경우, PVK의 층을 갖지 않는 대조 디바이스에 비해 효율이 개선된다는 것을 보여준다.

참조된 도면으로부터 알 수 있듯이, 본 발명에 따른 불용성 층을 포함함으로써 디바이스 성능이 상당히 증진된다. 게다가, 불용성 층을 포함함으로써 수명(즉, 고정된 전류에서 디바이스의 명도가 원 명도의 반으로 쇠퇴하는데 소요되는 시간) 및 디바이스의 명도는 적어도 손상되지 않으며, 일부 경우 개선된다.

불용성 층은 F8-TFB 층을 가열하거나 가열하지 않고 형성되지만, 불용성 층의 두께는 F8-TFB 층이 가열되는 경우 더욱 두껍다.

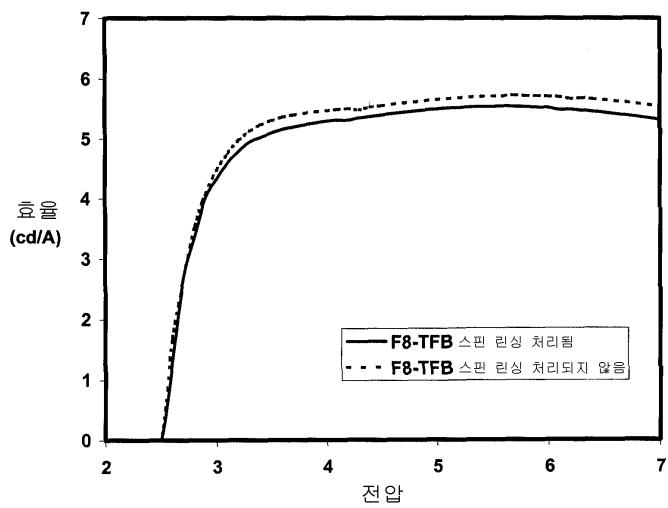

제 2 반도체 중합체는 제 1 층을 스핀-린싱 처리하지 않고 증착될 수 있다. 이는 제 1 반도체 중합체가 묽은 용액으로부터의 스핀-코팅에 의해 증착되어 전체적으로 불용성으로 되기에 충분히 얇은 제 1 층을 형성하는 경우에 바람직하게 수행되지만, 본 발명은 또한 제 1 층이 단지 부분적으로 불용성으로 되고 가용성 부분이 제거되지 않은 경우의 제 2 반도체 중합체의 증착도 포괄한다. 이러한 경우 제 1 및 제 2 반도체 중합체의 제 2 층에 일부 블렌딩이 있을 것이다. 도 4는 한 디바이스는 스핀-린싱 처리되고 다른 하나는 처리되지 않은, 청색 중합체를 사용하는 본 발명의 방법에 따라 제조된 2개의 디바이스에 대한 효율 대 바이어스를 도시한다. 상기 도면은 스핀 린싱 단계를 생략해도 디바이스 성능에는 거의 영향을 미치지 않는다는 것을 보여 준다.

상기 실시예는 제 1 및 제 2 층을 스핀-코팅에 의해 증착하는 것을 기술하지만, 본 발명에 따른 제 1 및 제 2 층은 다른 기술, 특히 유럽특허 제 0880303 호에 개시된 바와 같은 잉크젯 인쇄, 유럽특허 제 0851714 호에 기술된 바와 같은 레이저 전사, 플렉소그래프 인쇄, 스크린 인쇄 및 닥터 블레이드 코팅과 같은 풀 컬러 디스플레이의 제조에 적합한 기술에 의해 증착될 수 있다. 제 2 반도체 물질이 잉크젯 인쇄에 의해 증착되는 경우, 스핀-린싱 단계를 이용하는 것은 잉크젯 인쇄에 더 적은 부피의 용매 및 반도체 물질이 요구되기 때문에 상응하는 스핀-코팅 증착보다 더 유리할 수 있다.

### 적용예

다운컨버터(downconverter) 입자를 실시예 1(청색 중합체)의 디바이스의 기판의 외부 표면에 문현 [Applied Physics Letters 80(19), 3470-3472, 2002]에 기술된 바와 같이 부착하여 백색 광을 방출할 수 있는 디바이스를 수득했다.

본 발명이 특정 예시적 실시양태를 통해 기술되었으나, 당업자에게는 청구의 범위에 제시된 본 발명의 의의 및 범위를 벗어나지 않고 개시된 특징의 다양한 개량, 변경 및/또는 조합이 명백하다는 것을 알 것이다.

### 도면의 간단한 설명

본 발명은 예를 들어 하기의 첨부된 도면을 참고하여 이후에 상세하게 설명할 것이다.

도 1은 본 발명의 방법에 따라 제조된 PLED 또는 광전압 디바이스를 나타낸다.

도 2는 제 1 청색 전자발광 디바이스 및 2개의 대조 디바이스에 대한 효율 대 비아이어스의 비교 플롯을 나타낸다.

도 3은 적색 전자발광 디바이스에 관한 효율 대 비아이어스의 플롯을 도시한 것이다.

도 4는 스픈 런싱(spin rinsing)을 행한 경우와 그렇지 않은 경우의 제 1 청색 전자발광 디바이스에 관한 효율 대 비아이어스의 플롯을 도시한 것이다.

도 5는 제 2 청색 전자발광 디바이스 및 대조 디바이스에 대한 효율 대 비아이어스의 비교 플롯을 도시한 것이다.

### 도면

도면1

도면2

도면3

도면4

도면5