## (12) 发明专利

(10) 授权公告号 CN 106887449 B

(45) 授权公告日 2021.11.05

(21) 申请号 201610835745.9

(74) 专利代理机构 北京派特恩知识产权代理有限公司 11270

(22) 申请日 2011.12.07

代理人 康艳青 姚开丽

(65) 同一申请的已公布的文献号

申请公布号 CN 106887449 A

(51) Int.CI.

H01L 27/32 (2006.01)

(43) 申请公布日 2017.06.23

H01L 29/16 (2006.01)

(30) 优先权数据

H01L 29/78 (2006.01)

61/420,512 2010.12.07 US

H01L 51/00 (2006.01)

(62) 分案原申请数据

H01L 51/05 (2006.01)

201180064181.9 2011.12.07

H01L 51/10 (2006.01)

(73) 专利权人 佛罗里达大学研究基金会

H01L 51/52 (2006.01)

地址 美国佛罗里达

审查员 陈树华

(72) 发明人 安德鲁·加布里埃尔·林兹勒

米歇尔·奥斯汀·麦卡锡 刘波

权利要求书2页 说明书17页 附图25页

## (54) 发明名称

一种显示面板

## (57) 摘要

本发明提供了关于稀释源极实现垂直有机发光晶体管的各个实施例。在各个实施例中，显示面板包括像素阵列。在一个实施例中，其中，至少一个像素包括开关晶体管以及耦接至所述开关晶体管的驱动晶体管，其中所述驱动晶体管经配置以响应于所述开关晶体管的启动而发光。所述驱动晶体管可以是稀释源极实现垂直有机发光晶体管(DS-VOLET)。所述开关晶体管可以包括稀释源极实现垂直场效应晶体管(DS-VFET)。在另一个实施例中，双稀释源极实现垂直场效应晶体管(DS-VFET)包括第一DS-VFET，所述第一DS-VFET耦接至第二DS-VFET。

1. 一种显示面板,包括:

一个像素阵列,其特征在于,所述像素阵列中的至少一个像素包括:

开关晶体管(106a);以及

耦接至所述开关晶体管的驱动晶体管(103d),所述驱动晶体管经配置以响应于所述开关晶体管的启动而发光,其中所述驱动晶体管包括:

栅电极(201a);

漏极层(209);

源极层(113a),所述源极层包括稀释源极材料;

介电双层(109a),所述介电双层包括具有无机氧化物的第一层和具有聚合物的第二层,其中所述介电双层插入于所述栅电极与所述源极层之间,并且所述驱动晶体管具有基于所述源极层的电阻和由所述介电双层提供的栅极电容的频率响应,无需独立于所述栅极电容外的储能电容器;以及

有源层(116);

源极导电线(123b),所述源极导电线(123b)耦接至所述源极层(113a);以及

层间介电层,所述层间介电层位于所述漏极层(209)和所述源极导电线(123b)之间的重叠区域中。

2. 如权利要求1所述的显示面板,其中所述介电双层的所述第一层包括氧化铝。

3. 如权利要求1所述的显示面板,其中所述介电双层的所述第二层包括苯并环丁烯(BCB)。

4. 如权利要求1所述的显示面板,其中所述有源层包括一个半导体层和一个发光层。

5. 如权利要求1所述的显示面板,其中所述稀释源极材料包括碳纳米管稀释网络。

6. 一种显示面板,包括:

一个像素阵列,其特征在于,所述像素阵列中的至少一个像素包括:

开关晶体管(106a);以及

耦接至所述开关晶体管的驱动晶体管(103d),所述驱动晶体管经配置以响应于所述开关晶体管的启动而发光,其中所述驱动晶体管包括:

栅电极(201a);

源极层(113a),所述源极层包括稀释源极材料,其中所述驱动晶体管经配置具有基于所述源极层的电阻和位于所述源极层和所述栅电极之间的栅极电容的频率响应,无需独立于所述栅极电容外的储能电容器;

半导体层(203);

漏极层(209);

发光层(206),所述发光层位于所述半导体层和所述漏极层之间,其中所述漏极层经配置以允许传输由所述发光层产生的光;

过渡导电层(220),所述过渡导电层位于所述发光层和所述半导体层之间,其中所述过渡导电层对由所述发光层产生的光不透明。

7. 如权利要求6所述的显示面板,其中所述过渡导电层为不透明导体。

8. 如权利要求6所述的显示面板,其中所述过渡导电层包括金属。

9. 如权利要求6所述的显示面板,其中所述稀释源极材料包括碳纳米管稀释网络。

10. 一种显示面板,包括:

包含多个像素的像素阵列,其特征在于,所述多个像素中的至少一个像素包括:

开关晶体管(106a);以及

耦接至所述开关晶体管的驱动晶体管(103d),所述驱动晶体管经配置以响应于所述开关晶体管的启动而发光,其中所述驱动晶体管包括:

栅电极(201a);

源极层(113a),所述源极层包括稀释源极材料;

漏极层(209);

有源层,所述有源层位于所述源极层和所述漏极层之间,其中所述有源层包括半导体层(203),发光层(206),以及位于所述半导体层和所述发光层之间的过渡导电层(220)。

11. 如权利要求10所述的显示面板,其中所述漏极层包括用于注入电荷的导体,所述电荷与由所述源极层注入的另一种电荷互补,所述电荷经组合以在所述有源层生成光子,并且所述栅电极经配置以提供栅极场来调制在所述源极层与所述有源层之间的电荷注入。

12. 如权利要求10所述的显示面板,其中所述驱动晶体管进一步包括位于所述栅电极和所述源极层之间的介电层。

13. 如权利要求10所述的显示面板,其中所述稀释源极材料包括碳纳米管稀释网络。

14. 如权利要求10所述的显示面板,其中所述开关晶体管包括:

位于基板上的栅电极;

位于所述栅电极上的栅极介电层;

位于所述栅极介电层上的源极层,所述源极层包括稀释源极材料;

半导体层;以及

漏极层,其中所述半导体层位于所述源极层和所述漏极层之间。

## 一种显示面板

[0001] 本申请是申请日为2011年12月7日的PCT国际专利申请PCT/US2011/063745进入中国国家阶段的中国专利申请号201180064181.9、发明名称为“有源矩阵稀释源极实现垂直有机发光晶体管”的分案申请。

[0002] 相关申请案的交叉参考

[0003] 本发明主张于2010年12月7日提交的序列号为61/420,512的标题为“有源矩阵纳米管实现垂直有机发光晶体管阵列(ACTIVE MATRIX NANOTUBE ENABLED VERTICAL ORGANIC LIGHT EMITTING TRANSISTOR ARRAY)”的同时待审的美国临时申请案的在先申请优先权，该临时申请案的全部内容以引用的方式并入本文中。

[0004] 关于由联邦资助的研发的声明

[0005] 本发明得到了美国政府支持且遵守协议ECCS-0824157/00069937，并受到美国国家自然基金会的资助。美国政府享有本发明的某些权利。

### 技术领域

[0006] 无

### 背景技术

[0007] 为了满足不同的市场需求，显示技术不断地进步。改进的对比度、对观看角度的不敏感性、省电，以及制造成本的降低，成为许多研发活动的推动力。但是，现有显示技术在降低功耗方面的转变常常会与在显示对比度和显示强度方面的改善相冲突。

### 发明内容

[0008] 无

### 附图说明

[0009] 本发明的许多方面通过参考以下附图可以得到更好地理解。附图中的组件不一定按比例绘制，而是将重点放在清晰地说明本发明的原理上。此外，在附图中，贯穿若干视图，相同的参考数字表示对应的部分。

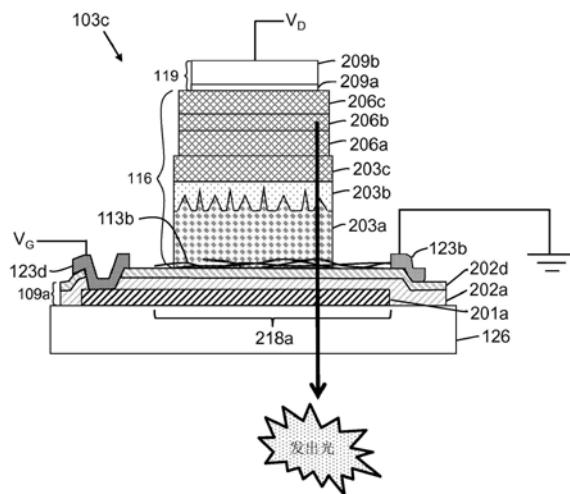

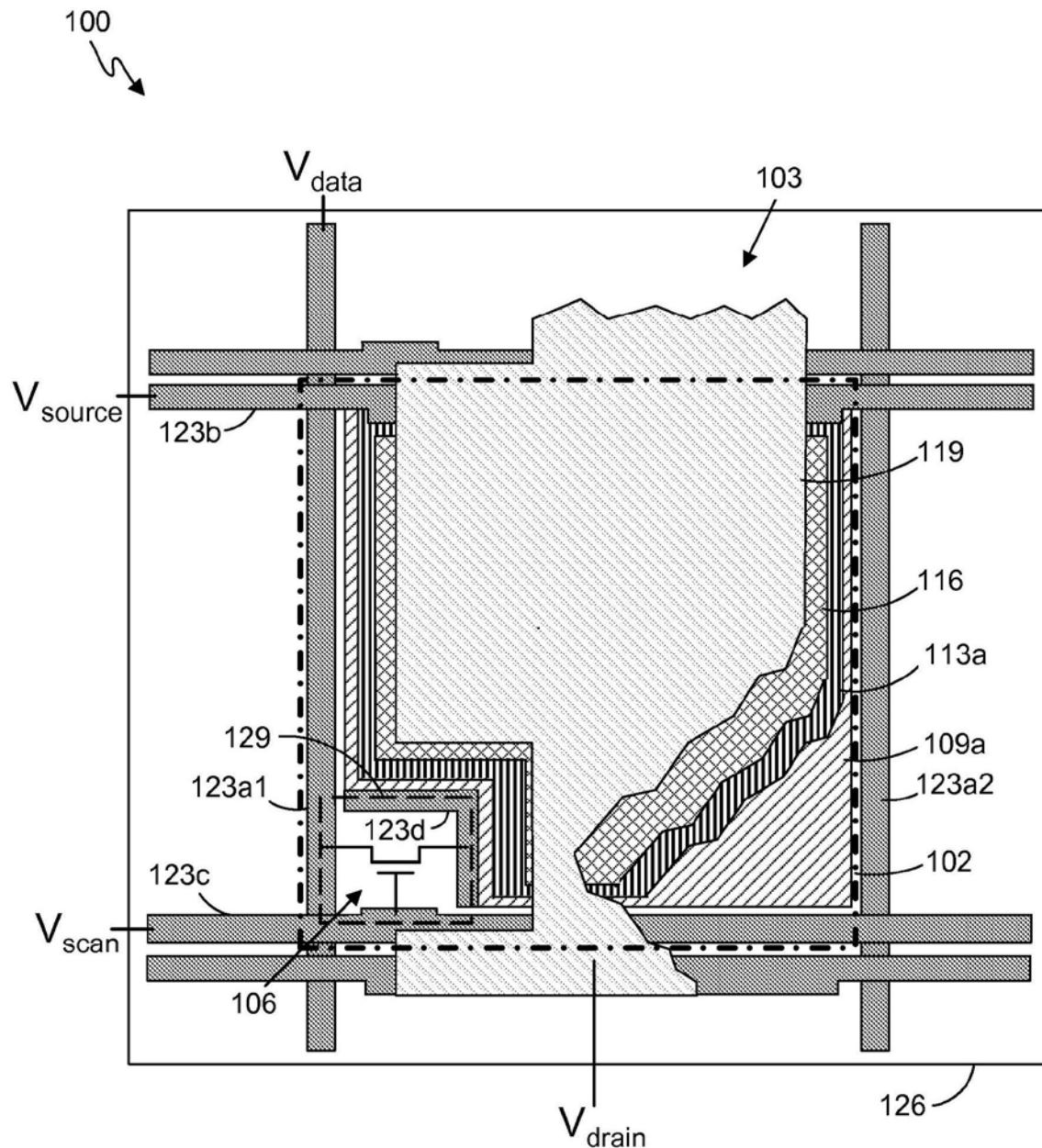

[0010] 图1A所示为根据本发明各个实施例的有源矩阵稀释源极实现垂直有机发光晶体管(AMDS-VOLET)像素的实例的平面图。

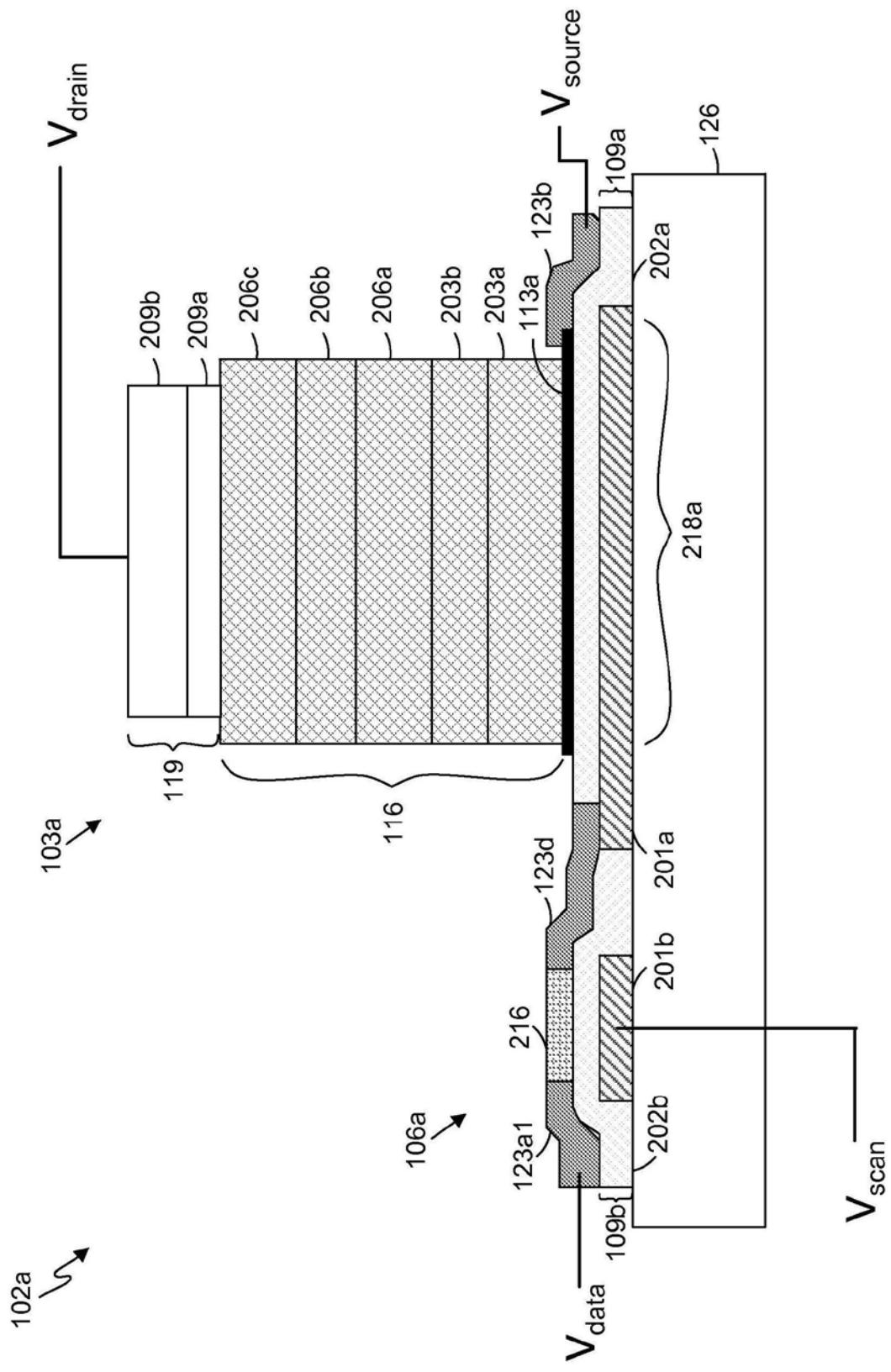

[0011] 图1B和图1C所示为根据本发明各个实施例的图1A中的AMDS-VOLET像素的有源单元的实例的截面图。

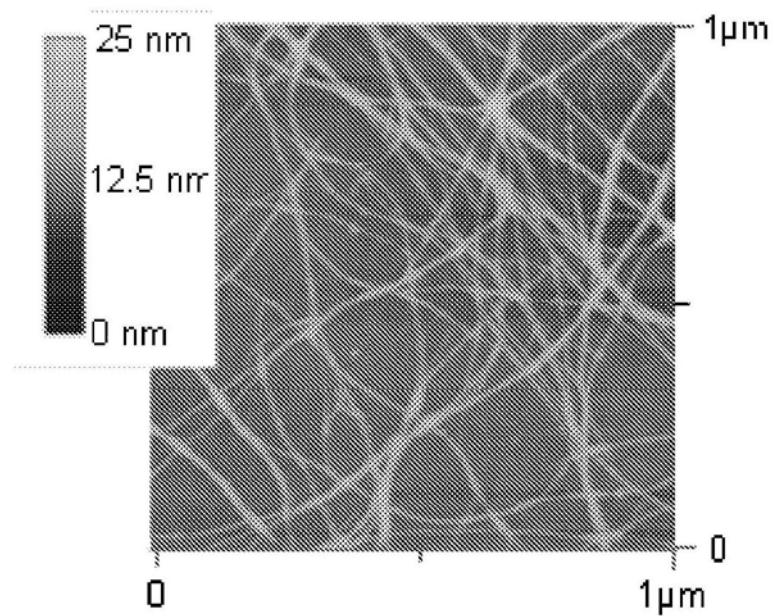

[0012] 图2A所示为根据本发明各个实施例的可能被包括在AMDS-VOLET中的稀释碳纳米管(CNT)网络的实例的原子力显微镜(AFM)图像。

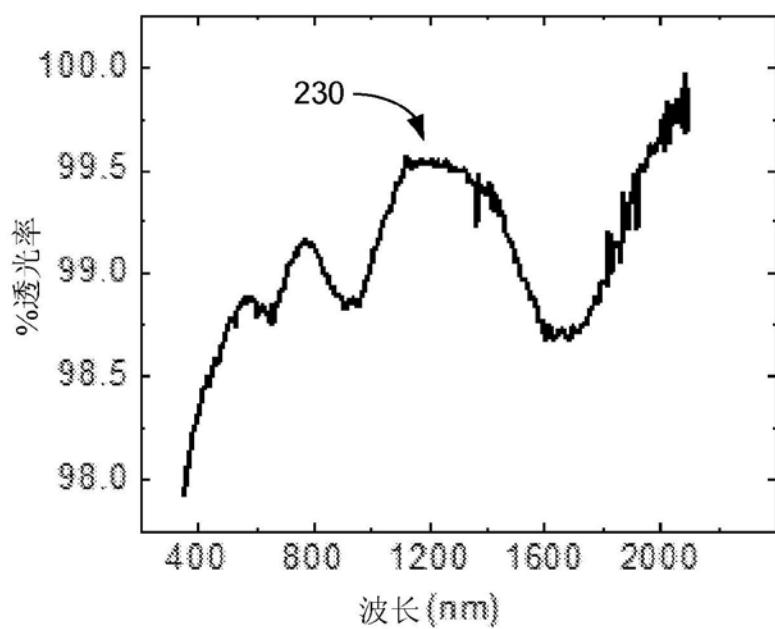

[0013] 图2B所示为根据本发明各个实施例的图2A中的CNT网络的透射率与波长关系的图表。

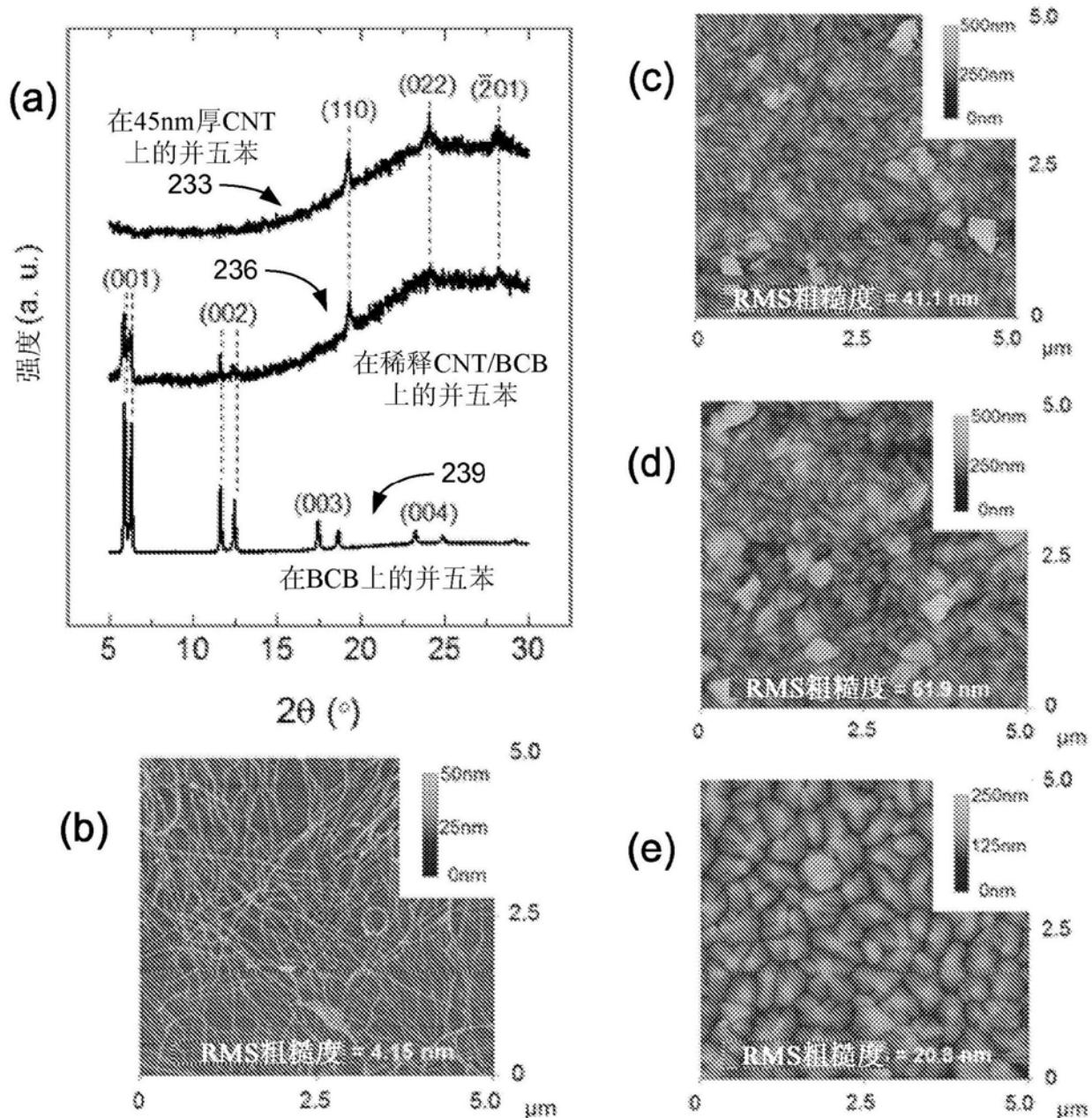

[0014] 图3所示为根据本发明各个实施例的在图2A中的稀释CNT网络上生长的并五苯多

晶体晶粒的重取向的X射线衍射(XRD)以及原子力显微镜(AFM)证据。

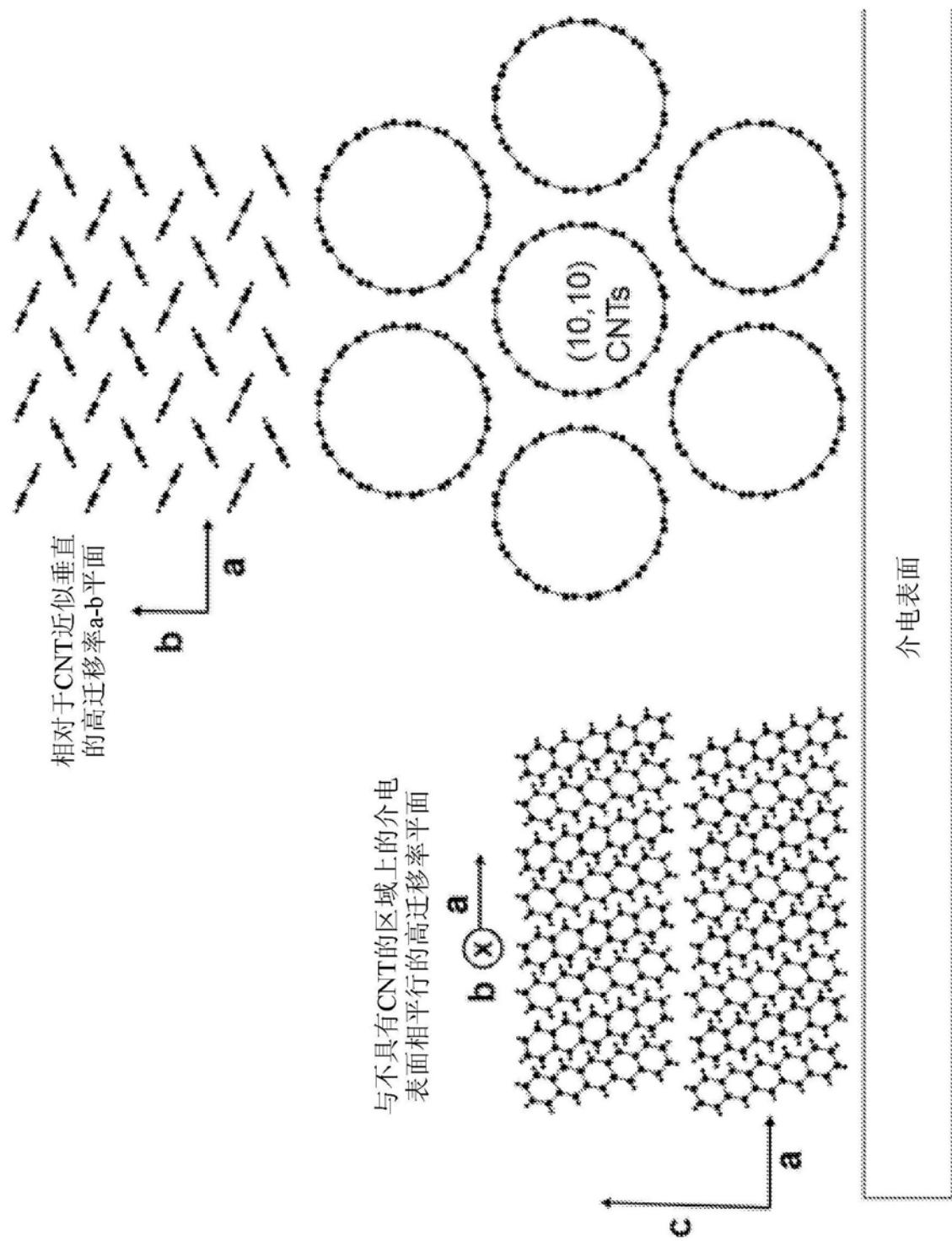

[0015] 图4所示为根据本发明各个实施例的在一个表面上的并五苯平面取向。

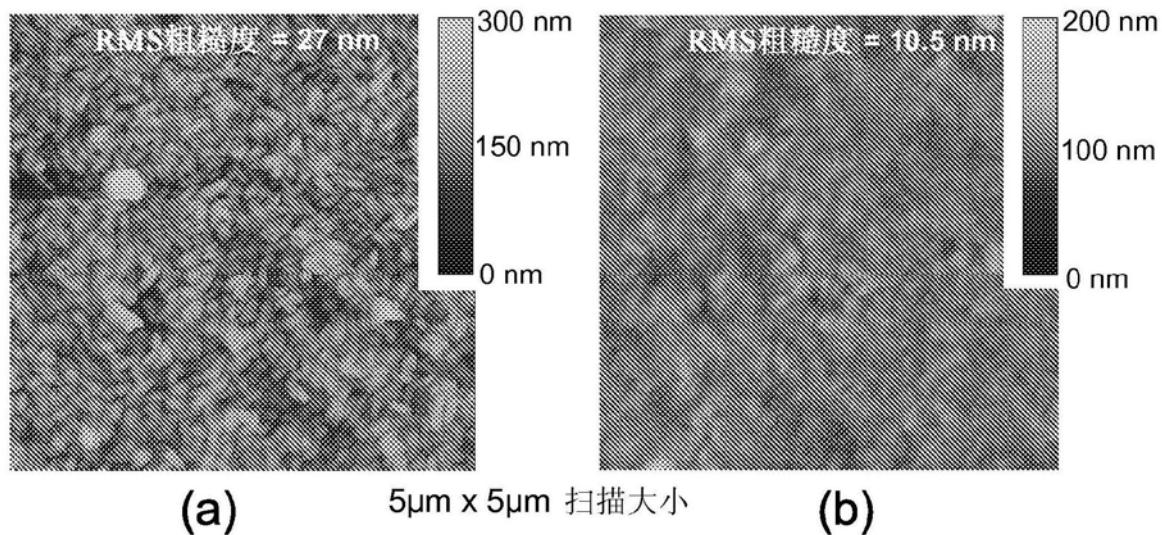

[0016] 图5所示为根据本发明各个实施例的由聚[9,9-二辛基-笏-共-N-(4-丁基苯基)-二苯胺](TFB)对粗糙多晶表面进行的平坦化的图像。

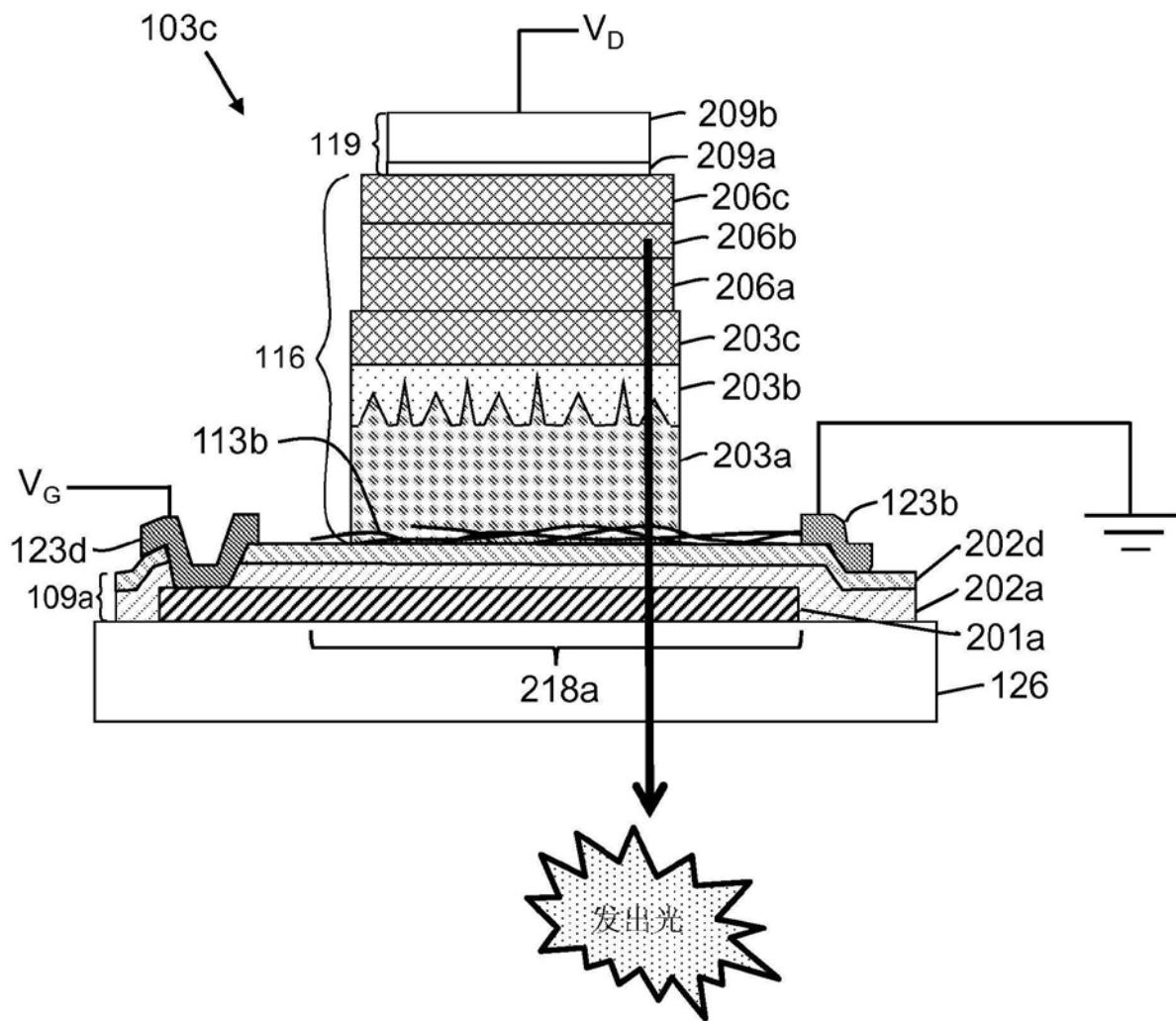

[0017] 图6所示为根据本发明各个实施例的图1A中的AMDS-VOLET的有源单元的实例的截面图,其中包括图5中的TFB平坦化层。

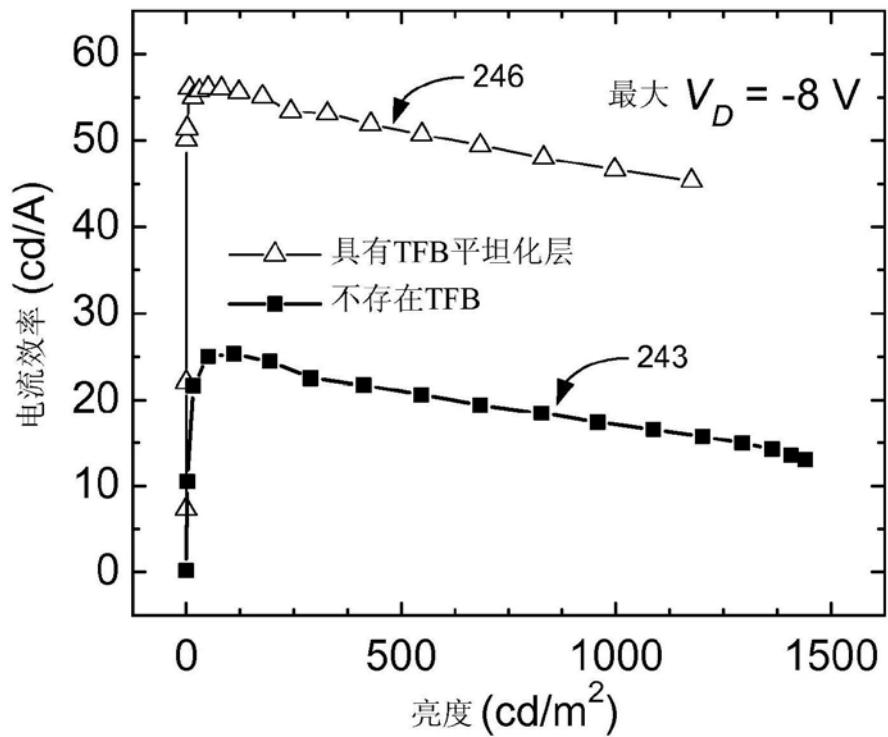

[0018] 图7所示为根据本发明各个实施例的通过在图6中有源单元中的图5中TFB平坦化层在电流效率上的改善的图表。

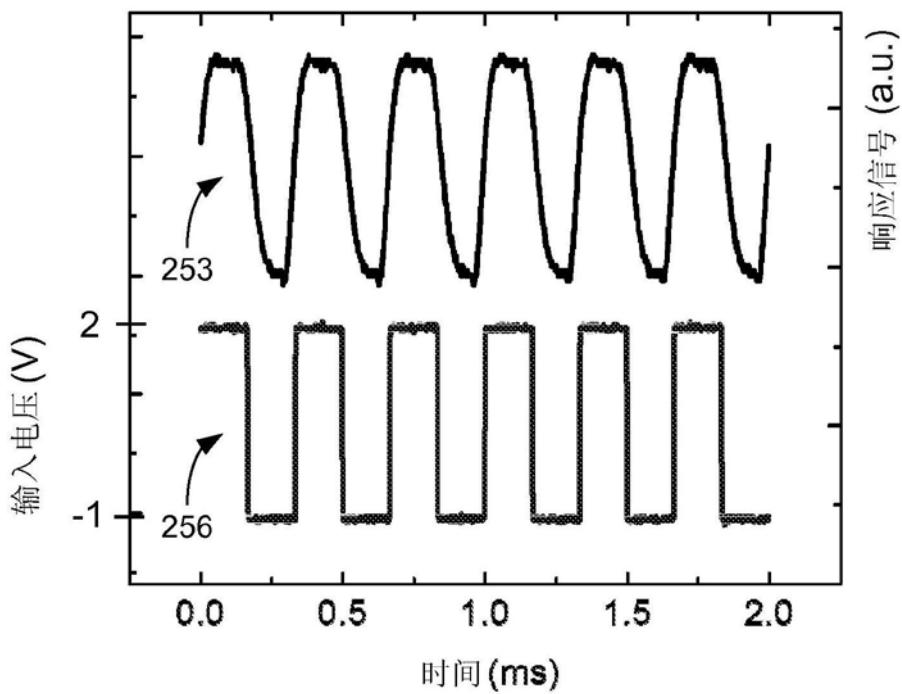

[0019] 图8所示为根据本发明各个实施例的图6中的有源单元的光电二极管响应的图表。

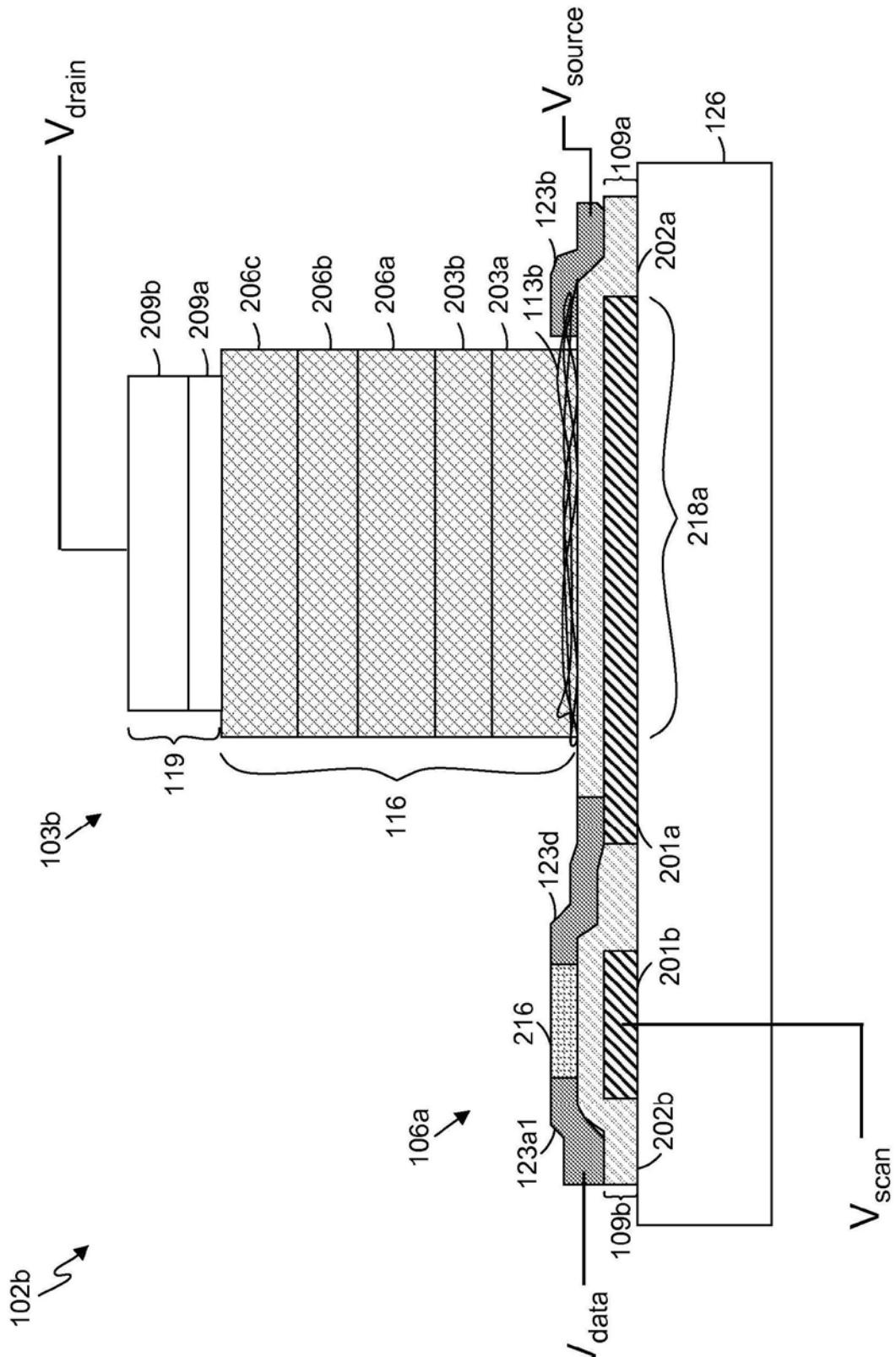

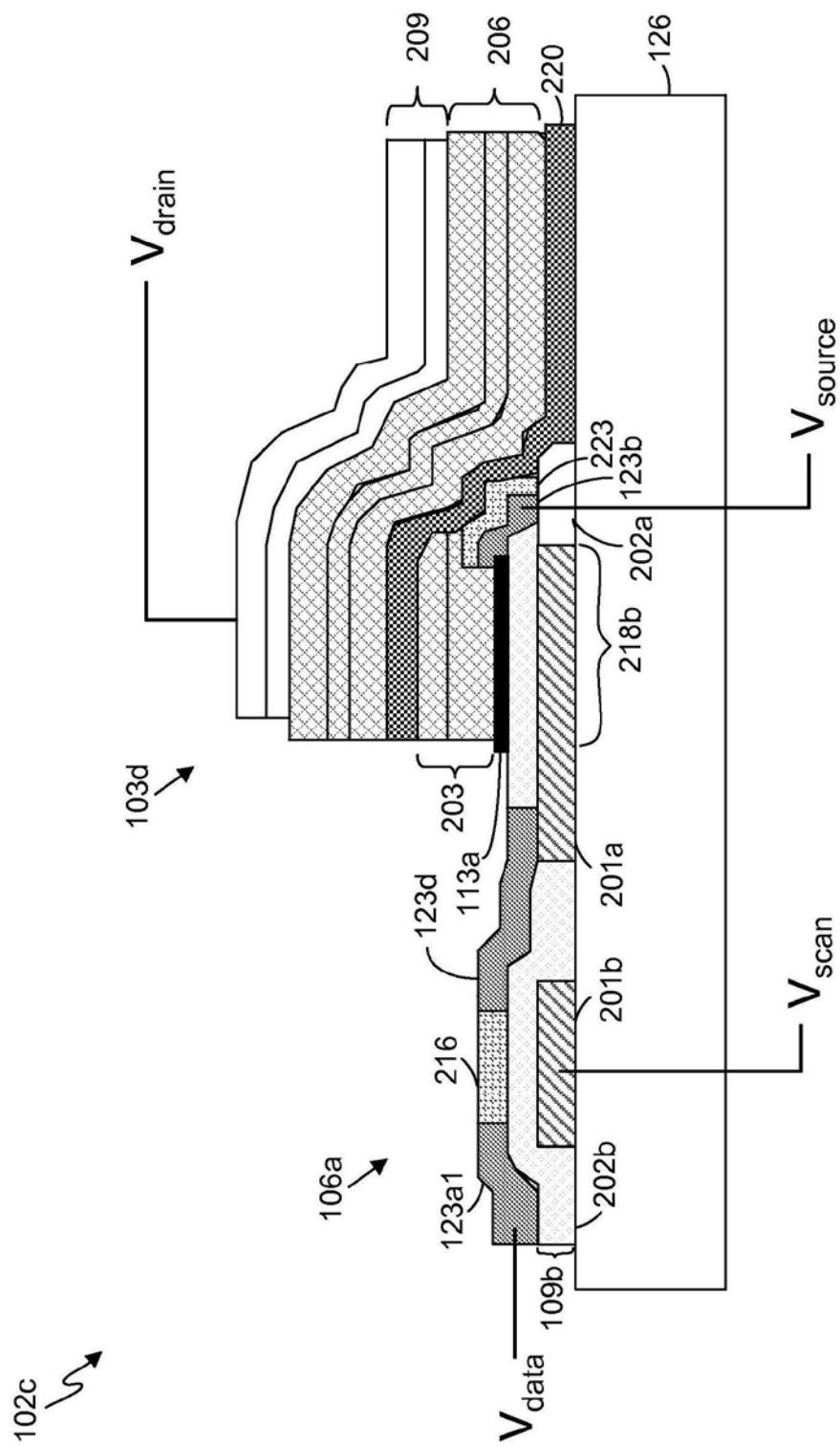

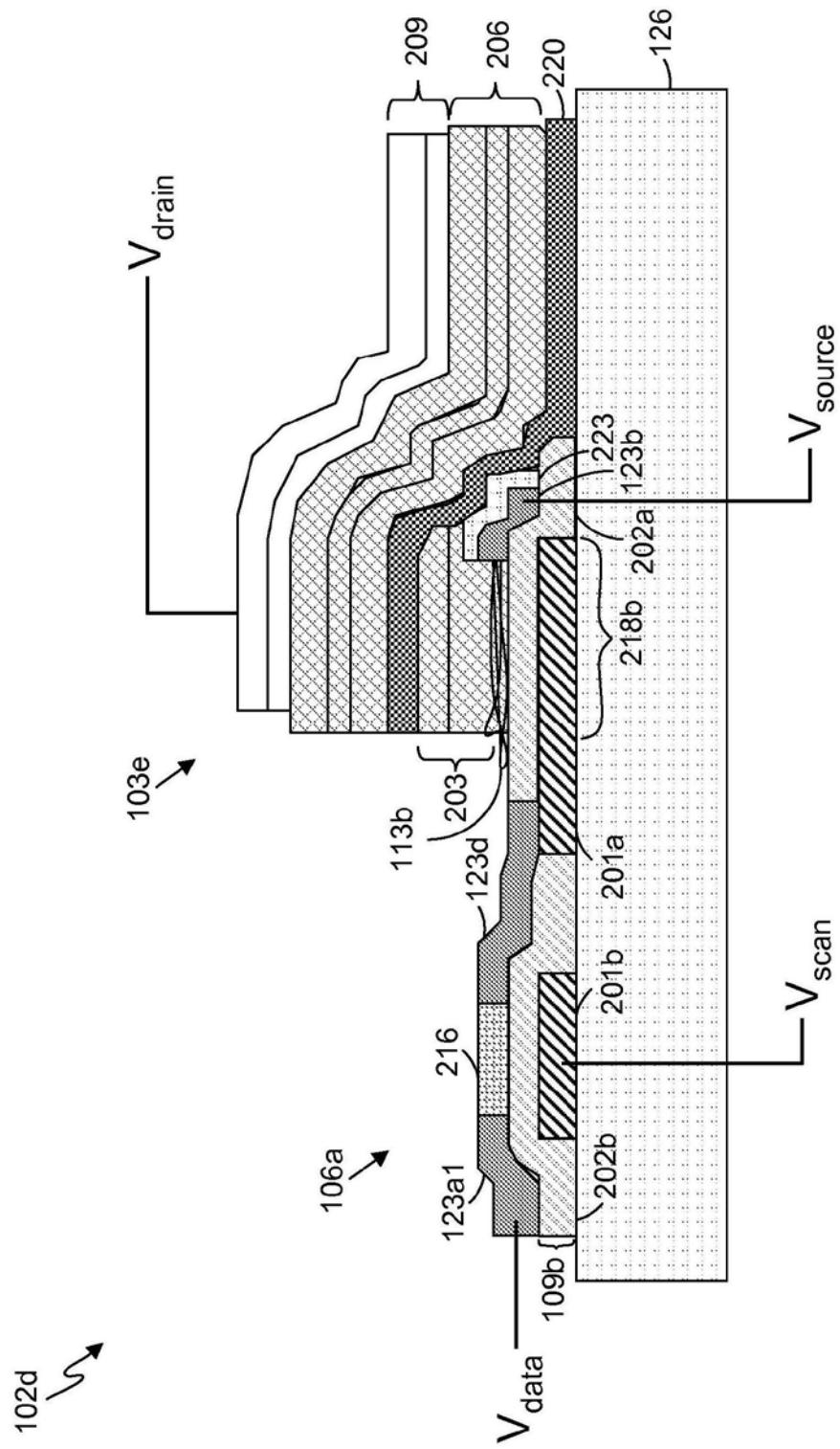

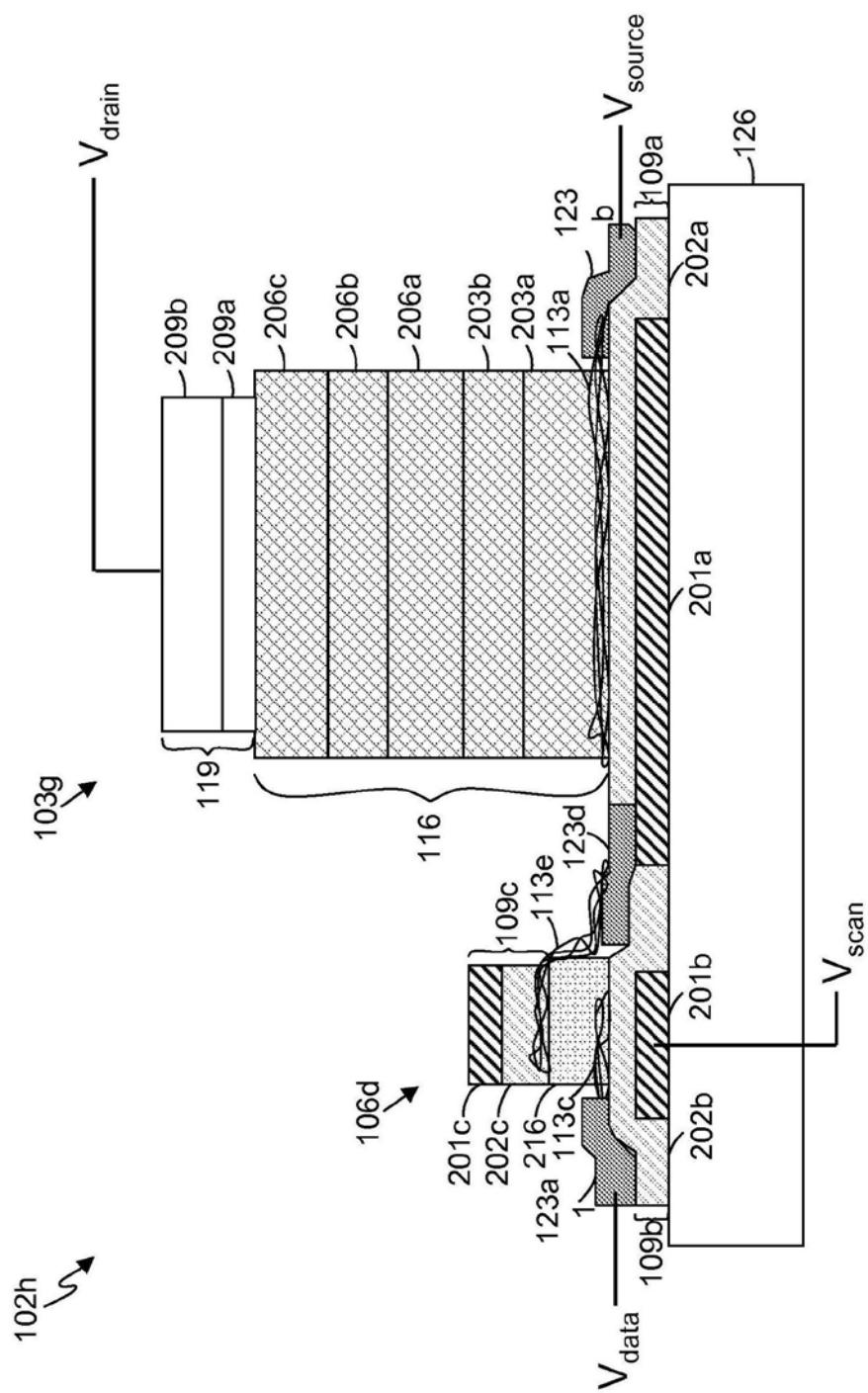

[0020] 图9A和图9B所示为根据本发明各个实施例的图1A中的AMDS-VOLET像素的有源单元的实例的截面图。

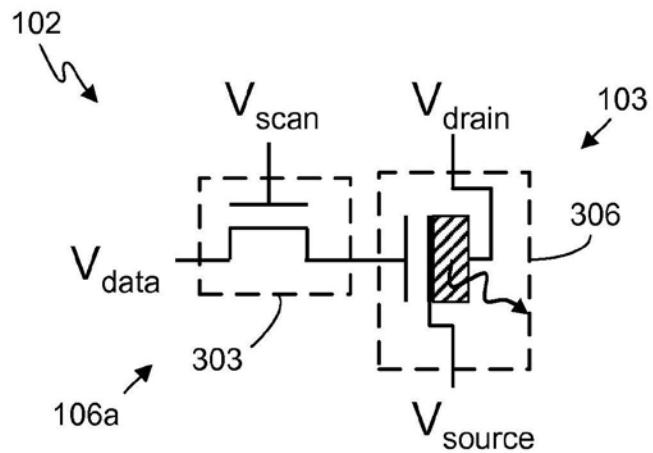

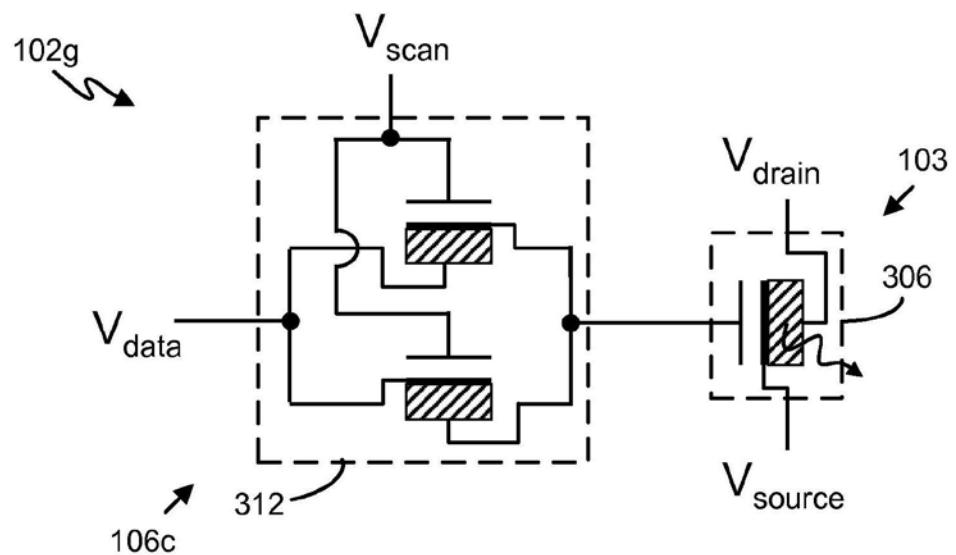

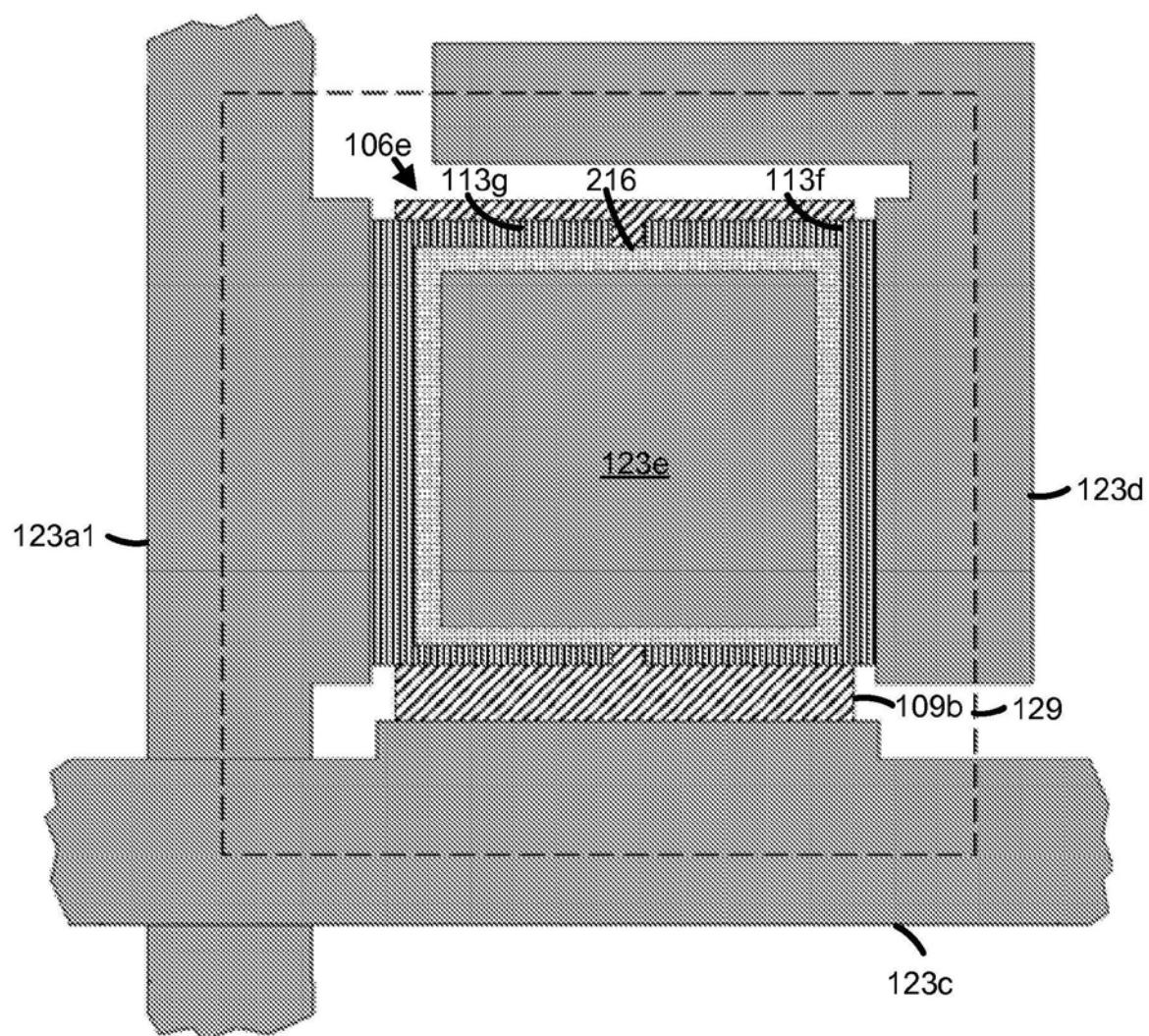

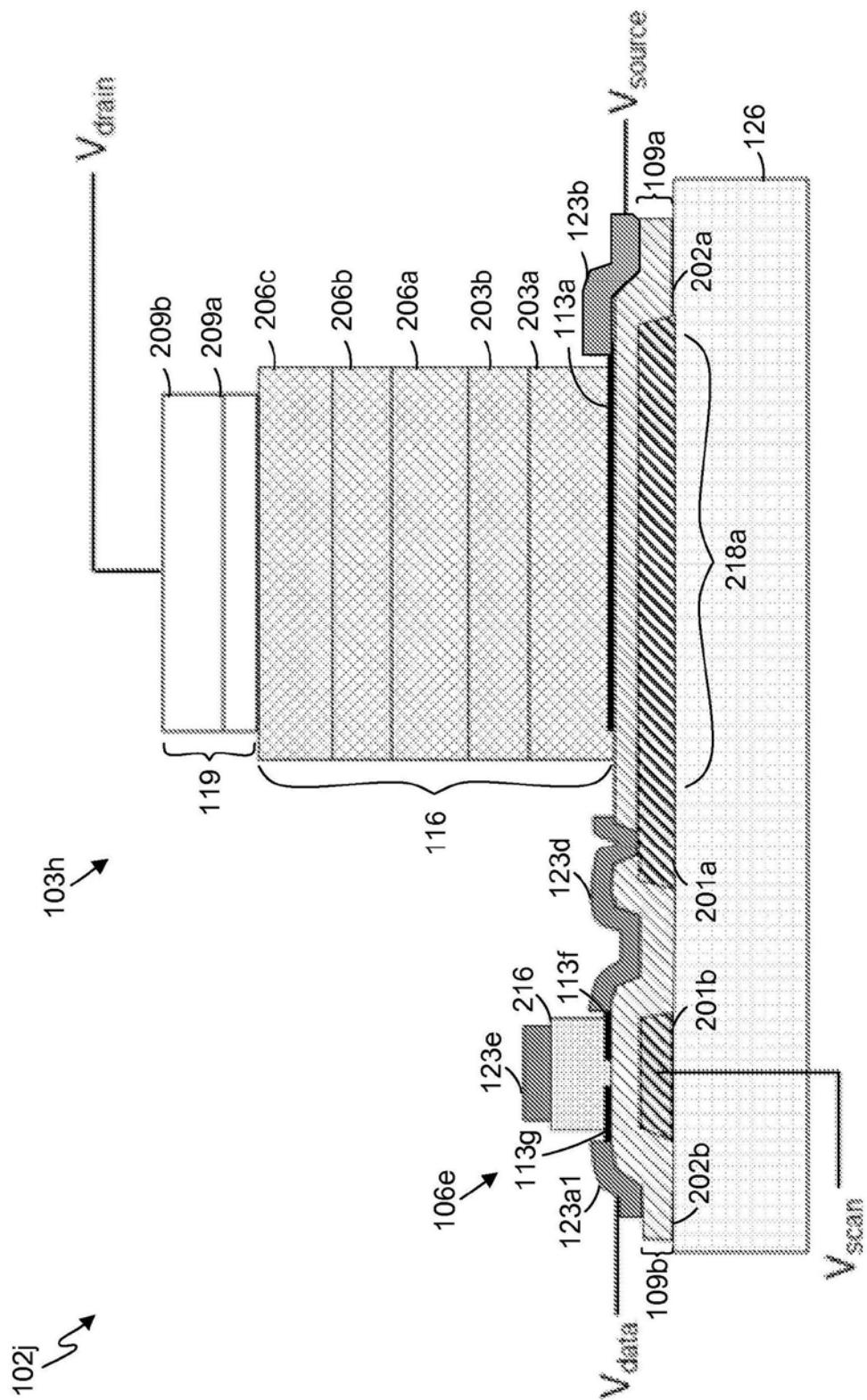

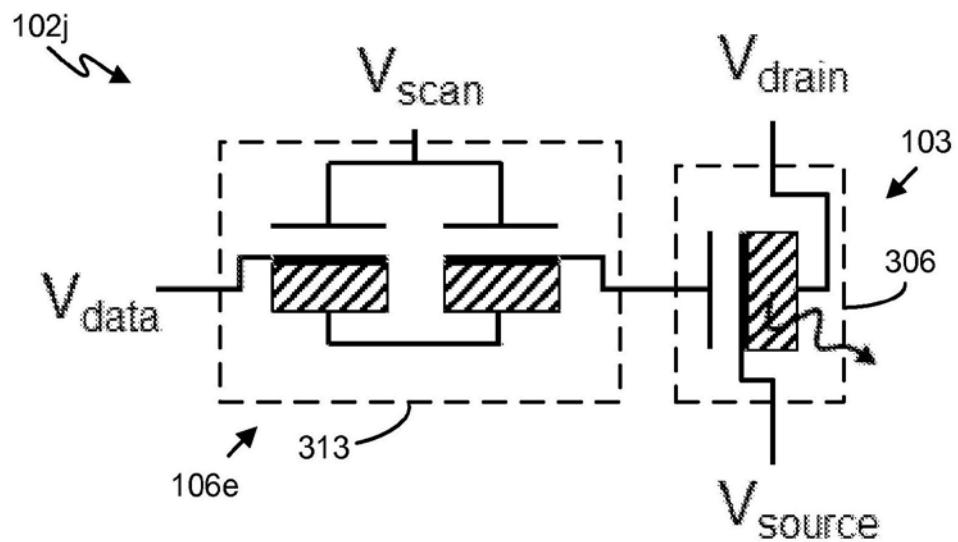

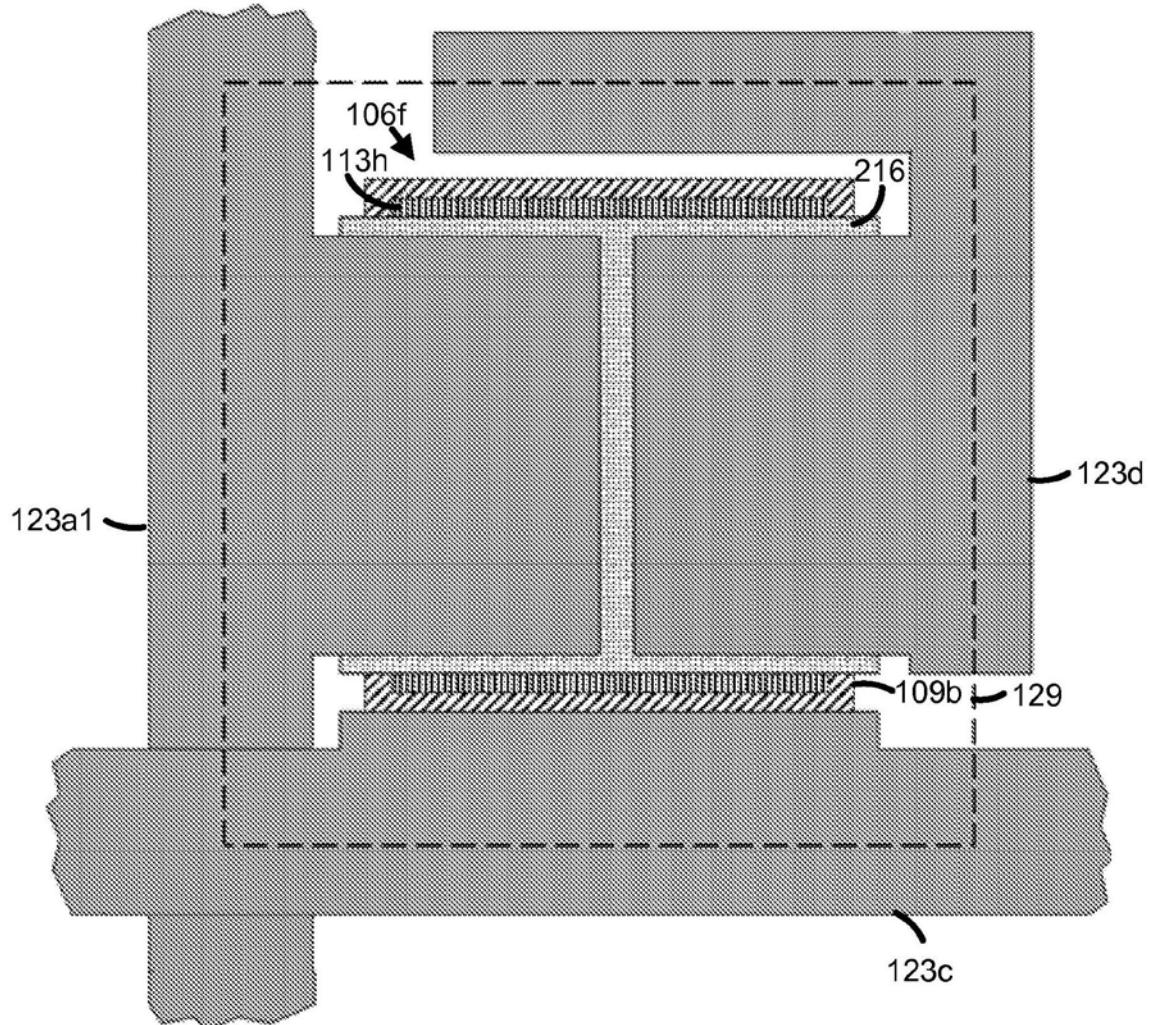

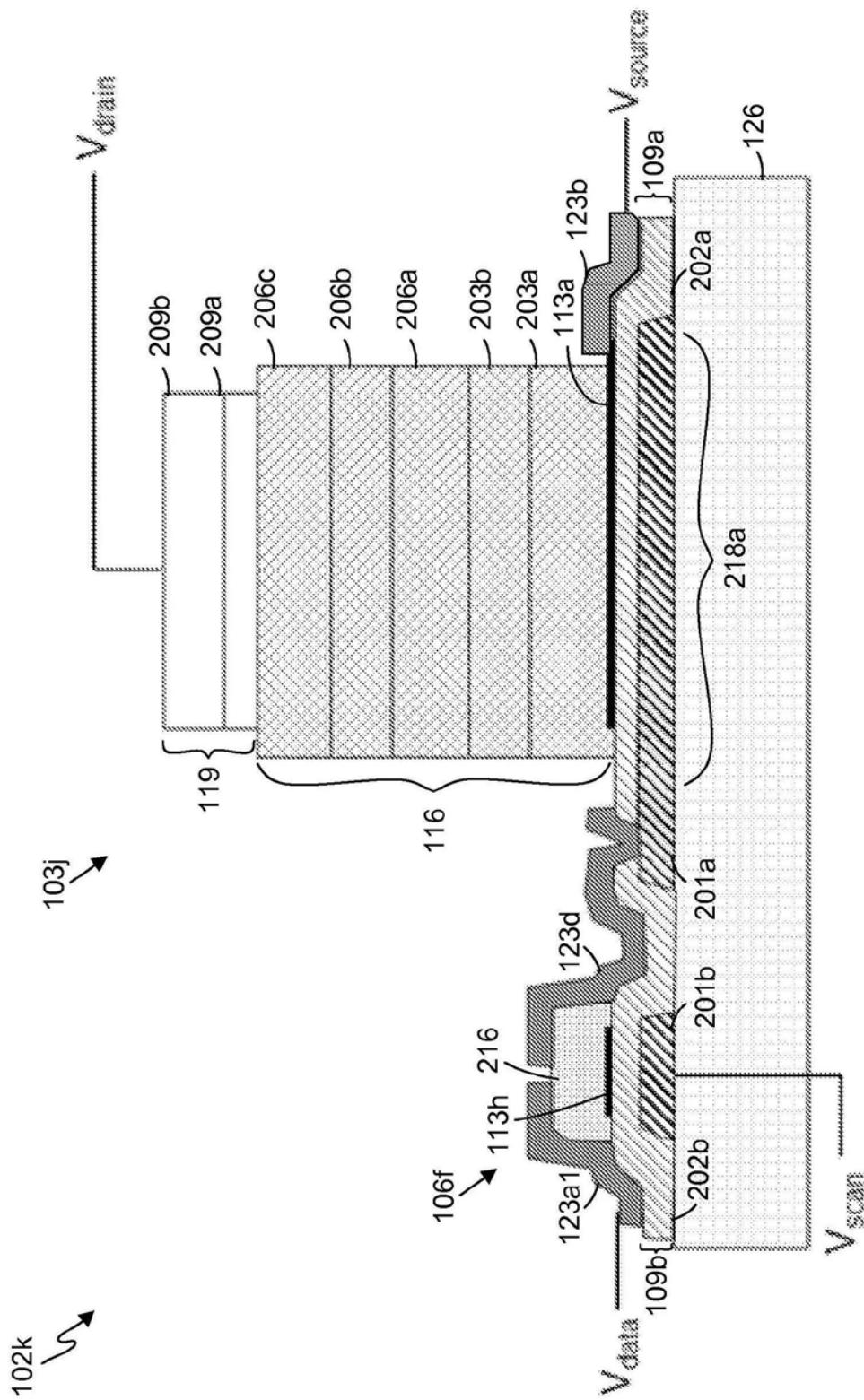

[0021] 图10所示为根据本发明各个实施例的图1B、图1C、图9A和图9B中的有源单元的电路图。

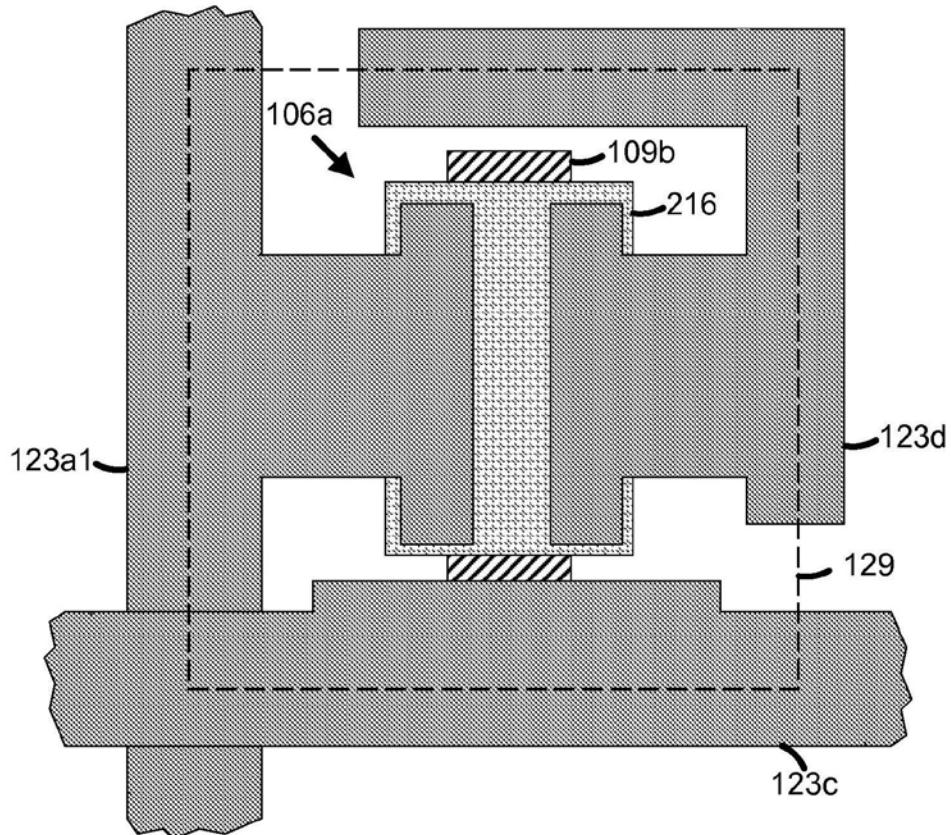

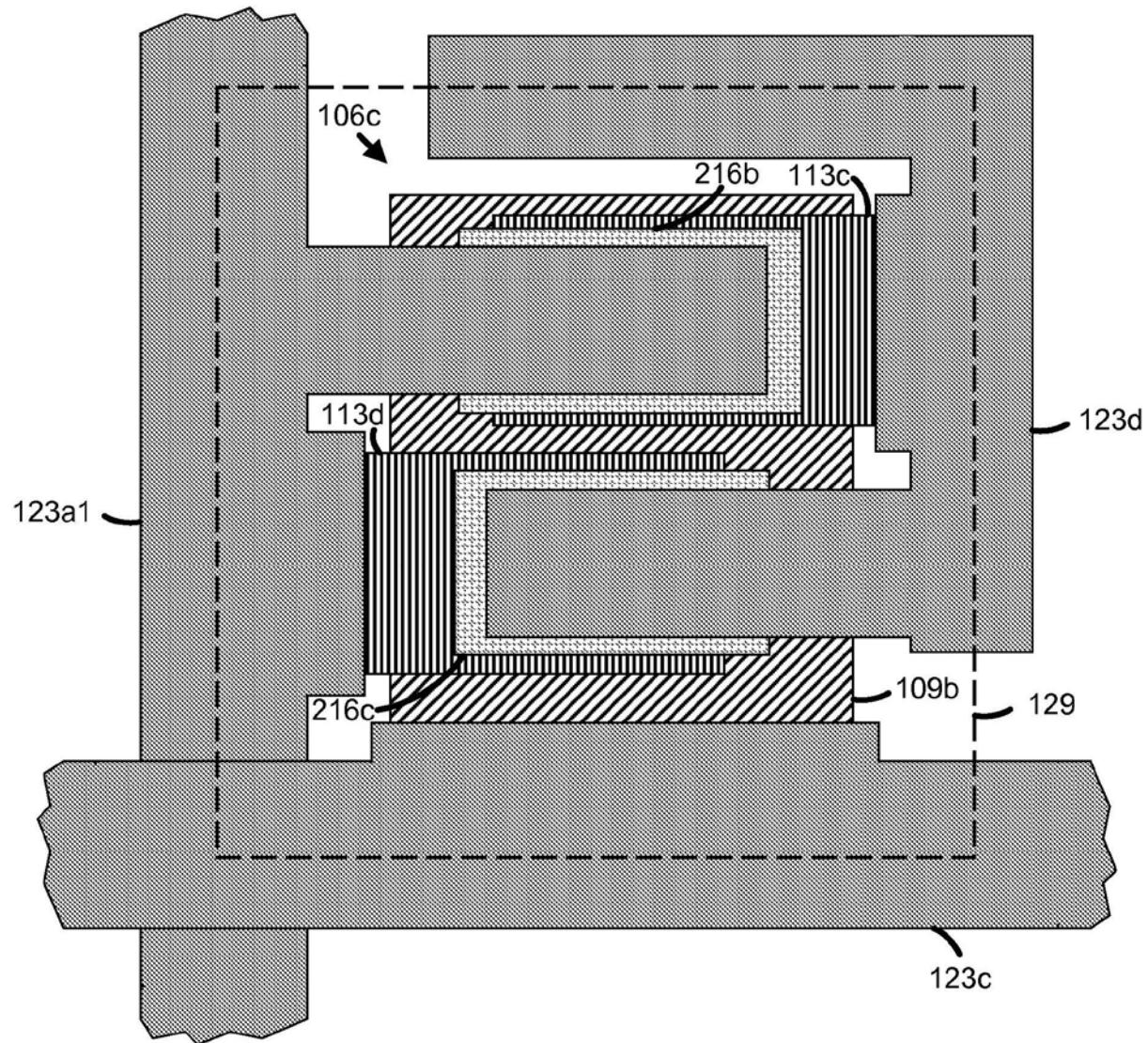

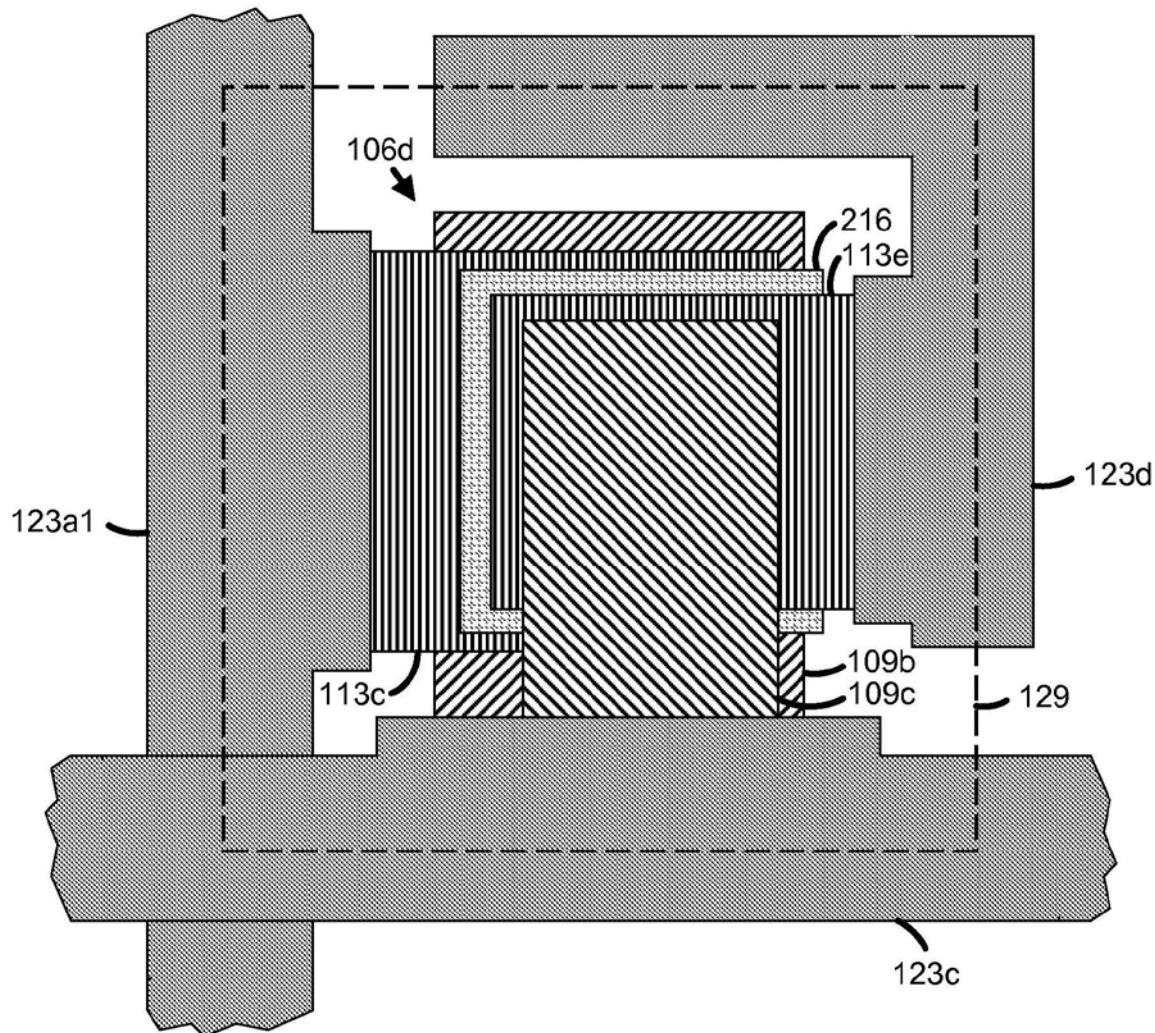

[0022] 图11、图12、图15、图17、图19和图22所示为根据本发明各个实施例的图1A中的开关晶体管(Sw-Ts)的布局实例的平面图。

[0023] 图13、图18、图20和图23所示为根据本发明各个实施例的图1A中的有源单元的实例的截面图,其中包括图12、图17、图19和图22中的Sw-Ts。

[0024] 图14A、图14B、图16、图21和图24所示为根据本发明各个实施例的图13、图15、图20和图23中的有源单元的实例的电路图。

[0025] 图25和图26所示为根据本发明各个实施例的图1A中的AMDS-VOLET像素的阵列的布局的实例的平面图。

## 具体实施方式

[0026] 本文所揭示的各个实施例涉及有源矩阵稀释源极实现垂直有机发光晶体管(AMDS-VOLET)。现在起将详细参考对于附图中所示的实施例的描述,其中在若干视图中相同参考数字表示相同部分。

[0027] 由于省电、改善的对比度以及对观看角度的不敏感性等方面原因,现有显示技术在技术方面正逐渐转变为有源矩阵有机发光二极管(AMOLED)显示器。该转变在以下方面存在障碍:通过底板中的薄膜晶体管(TFT)来供应有机发光二极管(OLED)所需要的高驱动电流。把多晶硅(poly-Si)用作通道材料是达成高驱动电流的一种选项,但是poly-Si会带来高的制造成本,并且具有不均匀性问题。用作TFT通道材料的有机半导体材料可能不会那么昂贵,但是有机半导体材料在输出电流方面赶不上Poly-Si。

[0028] 使用有机半导体材料达成高输出电流的一种方法,是将TFT的通道长度变短。在常规的横向通道TFT设计中,使通道长度变短会涉及到将TFT的源极端子和漏极端子安置成彼此非常接近。但是,由于需要高分辨率图案化,这种设计会很昂贵。稀释源极实现垂直场效应晶体管(DS-VFET)巧妙地解决了这个问题。DS-VFET的通道长度由半导体薄膜通道层的厚度来界定,从而无需使用高分辨率图案化也能获得亚微米通道长度。这样就可以在与poly-Si TFT相当的功耗下获得适用于操作OLED的高驱动电流。DS-VFET还可以转化成自身发光的装置,进而减少在像素底板中所需要的组件数目。DS-VFET发光组合装置也被称为稀释源

极实现垂直有机发光晶体管 (DS-VOLET)。

[0029] 本申请案描述了显示面板、像素以及有源单元的各个实施例，包括DS-VOLET。在常规AMOLED像素中，驱动晶体管和电荷储能电容器靠近占据像素面积的OLED装置，因此降低了孔径比 (OLED发光面积与总像素面积之比)。在所描述的各个实施例中，DS-VOLET包括驱动晶体管和储能电容器来作为其结构中的一部分，从而允许DS-VOLET可以更大并且因此增大了发光面积。由于所需的离散电路组件更少，这样还简化了制造工艺。另外，在每个像素中，DS-VOLET耦接至开关晶体管 (Sw-T)，并且下文也会描述Sw-T的各个实施例。

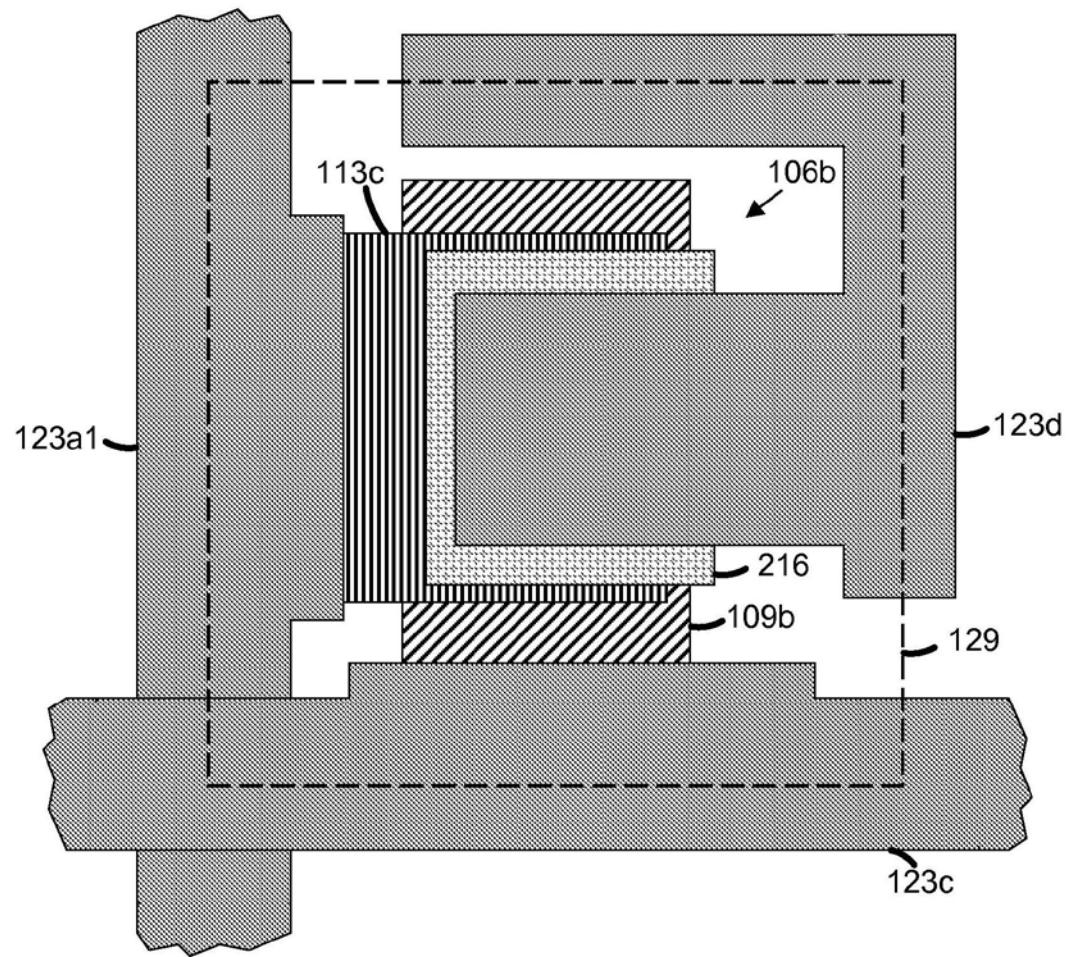

[0030] 图1A所示为有源矩阵稀释源极实现垂直有机发光晶体管 (AMDS-VOLET) 像素100的实施例的实例布局的平面图。AMDS-VOLET像素100包括有源单元102的实施例，有源单元102居于由导电线123环绕的区域中，如图1A所示。图1B所提供的图1A中所示的有源单元102的实施例的截面图，本文中标注为102a。图1A和图1B所示的有源单元102包括DS-VOLET 103的实施例的实例布局。开关晶体管 (Sw-T) 106 (由晶体管电路元件表示) 耦接至DS-VOLET 103和导电线123，导电线123在本文中被标注为123a1、123a2、123b、123c和123d。下文将详细论述Sw-T 106的各个实施例的布局。

[0031] 在图1A和图1B中所示的AMDS-VOLET像素100的实施例中所包括的导电线123，包括两根数据导电线123a，该两根数据导电线在本文中被标注为123a1和123a2，它们分别提供相应的 $V_{data}$ 电压信号。导电线123还包括源极导电线123b (即，提供 $V_{source}$ 电压信号) 以及扫描导电线123c (即，提供 $V_{scan}$ 电压信号)。此外，导电线123d将Sw-T 106耦接至DS-VOLET 103。

[0032] DS-VOLET 103为AMDS-VOLET像素100的发光组件。不同于在AMDS-VOLET像素100中包括独立的驱动晶体管和电荷储能电容器，DS-VOLET 103将该驱动晶体管和储能电容器并入到DS-VOLET 103的堆叠内。通过将该驱动晶体管和储能电容器添加在DS-VOLET 103的堆叠内，也就不需要独立于DS-VOLET 103的驱动晶体管和储能电容器。此外，由于该驱动晶体管和储能电容器被添加在DS-VOLET 103内，所以AMDS-VOLET像素100的发光部分大于常规像素的发光部分。发光部分的增加，增加了AMDS-VOLET像素100的孔径比。发光部分的这种增加使得AMDS-VOLET像素100能够输出与常规像素相同的光强，但是AMDS-VOLET像素100使用了较低的电流密度，这样可以增加AMDS-VOLET像素100的寿命。而且，在一些实施例中，Sw-T 106被设计得比较小，以减少由Sw-T 106所占用的像素面积，并增加由DS-VOLET 103所使用的像素面积。

[0033] 使用薄膜晶体管 (TFT) 架构驱动晶体管的有源矩阵阵列中的储能电容器，为该驱动晶体管的现有栅极电容提供了额外的电荷储能能力。总电容，即栅极电容和储能电容器电容的总和，应足够大，以在该阵列的操作循环中的刷新事件之间保留绝大部分的数据电荷。DS-VOLET 103的架构使得其具有大的门控面积，并且因此具有更大的栅极电容，该栅极电容比在刷新事件之间保留绝大部分数据电荷所需的栅极电容更大，并且无需独立的储能电容器。这是因为该门控面积可以同AMDS-VOLET像素100的发光面积一样大，该发光面积可以是AMDS-VOLET像素100面积的大部分 (即，大于50%)。DS-VOLET 103既具有大的门控面积，也具有大的孔径比，这是因为栅极层和基板可以是透明的，如下文所描述。但是，如果栅极电容变得过大，那么会存在DS-VOLET 103的切换速度不够的问题。栅极电容越大，切换速度越低。下文提供了切换速度测量值，表明因切换速度足够快而无法限制通常的显示应用

中的AMDS-VOLET像素100的切换速度。

[0034] 如图1A所示,DS-VOLET 103包括栅极层109(本文中标注为109a)、源极层113(本文中标注为113a)、有源层116,以及漏极层119。下文将结合图1B的描述进一步论述这些层。Sw-T 106耦接至传输 $V_{data}$ 信号的数据导电线123a1,而Sw-T 106也通过导电线123d耦接至DS-VOLET 103的栅极层109a。Sw-T 106被扫描导电线123c以规则的间隔启动,扫描导电线123c耦接至Sw-T 106的栅极109,扫描导电线123c提供 $V_{scan}$ 电压信号。Sw-T 106的启动使得 $V_{data}$ 信号被传输到DS-VOLET 103的栅极层109a。以此方式,Sw-T 106选择性地将电压(例如, $V_{data}$ )提供给DS-VOLET 103的栅极层109a,来控制DS-VOLET 103的灰度。 $V_{source}$ 和 $V_{drain}$ 信号分别提供穿过DS-VOLET 103的源极层113a和漏极层119的电压。

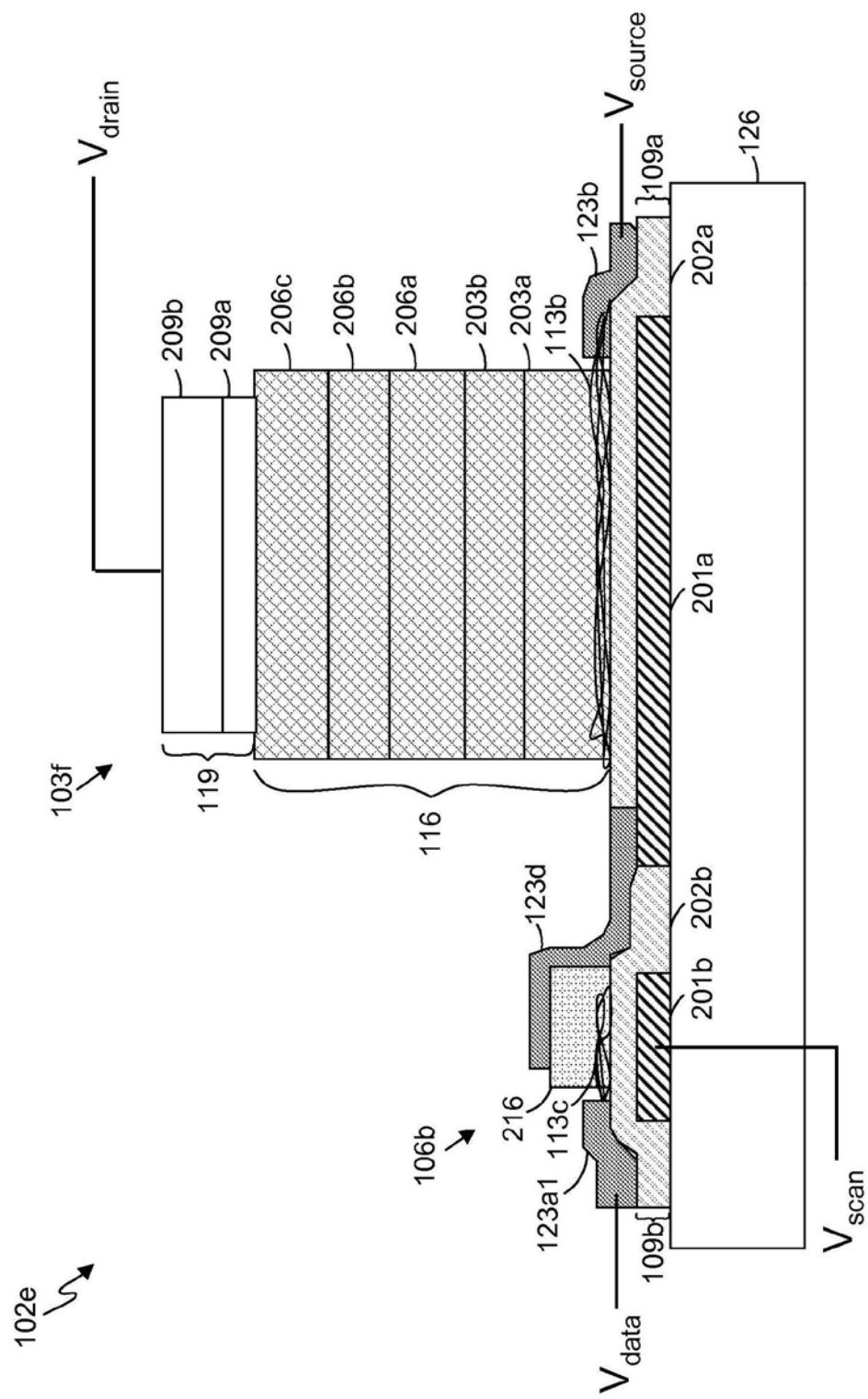

[0035] 现在参看图1B,图中所示为图1A中所示的有源单元102的实施例的截面图,本文中标注为102a。有源单元102a包括Sw-T 106的实施例,本文中标注为106a。Sw-T 106a为TFT。有源单元102a还包括DS-VOLET 103的实施例(本文中标注为103a)。DS-VOLET 103a和Sw-T 106a各自包括栅极层109,本文中分别标注为109a和109b。栅极层109a、109b可以根据相同工艺来形成,或者彼此独立地形成。栅极层109a、109b与基板层126直接接触,基板层126可以包括能透过可见光的材料。举例来说,基板层126可以包括玻璃、石英、塑料基板,和/或另一种透明材料。基板层126在性质上可以是刚性或柔性的。用于基板层126的可用塑料材料包括但不限于,聚酰亚胺、聚对苯二甲酸乙二醇酯(PET),以及聚萘二甲酸乙二醇酯(PEN)。在一些实施例中,基板层126可以是不透明的,并且基板层126可以包括绝缘材料并且对该绝缘材料的光学性质没有任何限制。举例来说,在一些实施例中,AMDS-VOLET像素100可以用于顶部发光显示器中,而AMDS-VOLET像素100中所包括的基板层126是不透明的。基板层126还可以包括诸如不锈钢等金属。该金属可以具有一定厚度来实现机械柔性。在基板层126包括金属的实施例中,绝缘基础层在沉积所有其他层之前先沉积,以防止AMDS-VOLET像素100与金属基板层126之间发生电通信。该绝缘基础层可以包括氧化硅、氮化硅或者是可溶液制备的绝缘聚合物,诸如聚酰亚胺。可以通过等离子体增强化学气相沉积(PECVD)、原子层沉积(ALD)、旋涂或下文提及的另一沉积方法来沉积该绝缘基础层。

[0036] 栅极层109a、109b中的每一者包括栅电极201和栅极介电层202。在图1A中,为了简明,将栅极层109a图示为单层。栅电极201经图案化以分别对应于DS-VOLET 103a和Sw-T 106a,并且这里标记为DS-VOLET栅电极201a和Sw-T栅电极201b。栅电极201中的至少一部分被栅极介电层202电绝缘。栅极介电层202经图案化以分别对应于DS-VOLET 103a和Sw-T 106a,并且在这里标记为DS-VOLET栅极介电202a和Sw-T栅极介电202b。

[0037] 在一些实施例中,栅电极201包括透明导电层,而栅极介电层202包括透明介电涂层。在其他实施例中,栅电极201是不透明的。栅电极201可以包括单层或多层的导电材料,例如,有机或无机导电材料、透明或不透明金属、半金属和/或半导体(经掺杂或未掺杂的,优选为掺杂的)。术语“导体”可以用于指代一种半导电材料或半金属,该半导体材料或半金属经掺杂以提高其载流子密度,使得其可以被看做是导体。栅电极201中所包括的材料的一些实例有:单层或多层石墨烯、碳纳米管(CNT)的稀释网络或非稀释层、掺杂有锡的氧化铟(ITO)、聚(3,4-乙烯二氧噻吩)聚(磺化苯乙烯)(PEDOT:PSS)、ZnO和/或氧化铟纳米颗粒。在一些实施例中,栅极介电层202还可以包括由诸如氧化铝等无机材料以及诸如苯并环丁烯(BCB)等聚合物组成的双层。该无机材料提供了大的电容,并且该聚合物充当了疏水层。这

些层可以通过PECVD、ALD、旋涂或其他已知方法来沉积。

[0038] 在DS-VOLET 103a中，栅极介电202a被定位在栅电极201a上，以将栅电极201a与DS-VOLET 103a中所包括的其他层电隔离。DS-VOLET栅电极201a和Sw-T栅电极201b可以同时进行沉积和图案化。相似地，对于栅极介电层202，也可以同时进行关于DS-VOLET栅极介电202a和Sw-T栅极介电202b的沉积和图案化。这些层也可以分开来沉积。

[0039] 在一些实施例中，源极层113a可以包括稀释源极材料，该稀释源极材料包含逾渗性稀释网络。逾渗性稀释网络可以是任何稀释且电逾渗的材料，例如任何低态密度导体；纳米结构化导体或半导体；纳米图案化导体或半导体；低态密度半导体，无机的或有机的；或低态密度半金属，无机的或有机的。低态密度半金属的实例为石墨烯。石墨烯可以是单层或多层的，并且可以经图案化以包括穿孔，或者不加图案化。低态密度导体的另一实例包括金属单壁和多壁碳纳米管，其具有本有的低态密度，并且可以进一步以低密度沉积到所谓的稀释网络中。低态密度半导体的其他实例包括半导碳纳米管以及几乎所有的有机半导体。纳米结构化半导体的实例包括Si纳米线、氧化锌纳米线、磷化铟纳米线、氮化镓纳米线。纳米结构化导体的实例包括银纳米线、金纳米线以及镍纳米线。术语有机半导体指代任何基于有机小分子、低聚物或者是已知具有半导体性质的聚合物。

[0040] 如本文中所使用，“稀释网络”指代在源极层113a中所包括的薄膜或网络，该薄膜或网络具有穿孔，其中介电层202a的大部分区域未被该薄膜或网络所覆盖。源极层113a可以是足够稀的，以便能暴露出例如约0.1%至约99.9%、约30%至约90%，以及约50%至约80%范围的底层表面。另外，“逾渗性”指代：(i) 纳米管或纳米线源极层113a所含有的纳米管或纳米线密度(即，每单元面积内的纳米管数目)足够提供从源极层113a的一端到另一端的电气连续性；或者(ii) 导体、半导体或半金属薄膜包括频繁的穿孔(例如，以纳米范围、皮米范围和/或微米范围发生)，但是仍保持了从源极层113a的一端到另一端的电气连续性。稀释的还可以指代石墨烯，它被看做是稀释源极材料，因为其具有低态密度，并且因此可以结合穿孔或不结合穿孔来使用。

[0041] 在一些实施例中，碳纳米管稀释网络被用作DS-VOLET 103a的源电极。参看图1C，图中所示为有源单元102b的实施例，其中包括用作源极层113b的单壁碳纳米管稀释网络，可以将其称作碳纳米管实现垂直有机发光晶体管(CN-VOLET) 103b。稀释纳米管网络源极层113b被定位在CN-VOLET栅电极201a上的CN-VOLET栅极介电202a上。CN-VOLET 103b的各个实施例以及DS-VFET和DS-VOLET 103的其他实施例见述于以下文献中：于2008年9月10日提交的标题为“纳米管实现栅极电压控制发光二极管(Nanotube Enabled, Gate-Voltage Controlled Light Emitting Diodes)”的序列号为No.12/677,457的美国专利申请公开案US 2010/0237336；于2011年3月4日提交的标题为“包括电逾渗源极层的半导体装置及其制造方法(Semiconductor Devices Including an Electrically Percolating Source Layer and Methods of Fabricating the Same)”的国际申请号为No.PCT/US2011/027155的国际公开案WO 2011/109693A2；以及于2010年3月4日提交且序列号为No.61/310,342的标题为“包括纳米管层和存储器层的半导体装置及其制造方法(Semiconductor Devices Including a Nanotube Layer and a Memory Layer and Methods of Fabricating the Same)”的美国临时申请案，以上所有文献均以全文引用的方式并入本文中。

[0042] 再次参看图1B，栅电极201a和源极层113a界定出基板126的重叠区域218a。有源层

116被定位在源极层113a上，并且有源层116包括可能被掺杂的至少一个有机半导体层203。在图1B所示的实施例中，有源层116包括两个有机半导体层203，这里标记为203a、203b。该稀释纳米管网络可以使用见述于《科学》[Science (2004) 305, pp. 1273-1276]杂志中的真空过滤转移方法(vacuum filtration transfer method)来进行沉积，或者通过以下方法中的至少一者来进行沉积：旋涂、浸涂、落模铸造、丝网印刷、喷涂、蒸汽喷印、刮刀涂布、化学气相沉积、凹版印刷、柔性版印刷以及喷墨印刷。

[0043] 有源层116进一步包括至少一个发光层206。在图1B所示的实施例中，有源层116包括三个实例发光层206，这里标记为206a、206b以及206c。这些发光层206被定位在至少一个有机半导体层203上。在图1B所示的实施例中，发光层206a被定位在该至少一个有机半导体层203上。发光层206a为空穴传输层(HTL)，而发光层206b为电致发光层(EL)并且被定位在发光层206a上。发光层206c为电子传输层(ETL)并且被定位在发光层206b上。这些发光层206可以是经掺杂或未掺杂的。可以添加额外层(未在图1B中示出)并且可以将这些额外层定位在至少一个有机半导体层203上，位于HTL 206a下方，诸如经掺杂或未掺杂的一个或多个空穴注入层的下方。有源层116可以包括任何有机(小分子或聚合物)或无机半导体。在一些实施例中，发光层206b为荧光或磷光发光的经掺杂或未掺杂的有机或无机半导体材料。发光层206b中所包括的材料的实例为面式三(2-苯基吡啶)合铱(III)(Ir(ppy)3)，该材料被掺杂到4,4'-N,N-二咔唑-联苯(CBP)中。在一些实施例中，发光层206a包括1,1'-双[(2-4-甲苯基氨基)苯基]环己烷(TAPC)，或者是N,N'-二(1-萘基)-N,N'-二苯基-1,1'-二苯基-1,4'-二胺(NPD)。在一些实施例中，发光层206c包括三[3-(3-吡啶基)-米基]硼烷(3TPYMB)。

[0044] 漏极层119被定位在有源层116上。确切地说，漏极层119被定位在有源层116中所包括的至少一个发光层206上。在一些实施例中，诸如在图1B中所示的那样，漏极层119包括两个导电层209，这里标记为209a、209b。导电层209a可以充当发光层206c的电子注入层(EIL)。导电层209b可以包括铝、另一种金属，和/或透明导电材料。在一些实施例中，漏极层119还可以是单层、双层或者是包含各种导电材料的多层，诸如有机或无机导电材料、透明或非透明金属、半金属或半导体(经掺杂或未掺杂的，优选为经掺杂的)。漏极层119中所包括的材料的一些实例有：单层或多层石墨烯、碳纳米管的稀释网络或非稀释层、铝、氟化锂、掺杂有锡的氧化铟(ITO)、氧化钼、聚(3,4-乙烯二氧噻吩)聚(磺化苯乙烯)(PEDOT:PSS)、ZnO或氧化铟纳米颗粒或金属纳米颗粒。在一些实施例中，DS-VOLET 103a的有源层116进一步包括定位在发光层206a与发光层206b之间的电子阻挡层。

[0045] 在DS-VOLET 103发光透过漏极层119的情况下(也可以称作顶部发射DS-VOLET 103)，可以使用ITO，因为它是透明导体。但是，因为ITO通常是通过溅射法来沉积，这样一般会对下面的有机发光层造成损伤。为了保护下面的发光层，可以在沉积ITO之前热蒸镀氧化钼或另一种金属氧化物，因为这些无机金属氧化物提供了保护势垒，用于阻挡在ITO溅射沉积期间对材料的高能撞击，ITO溅射沉积可以在金属氧化物沉积之后再进行。此外，其他实施例可以包括对上述各层及额外层的组合，或修改，或者省略它们。

[0046] 参看图2A，图中所示为CNT网络的原子力显微镜(AFM)图像，其中的CNT表面数密度为用于CN-VOLET 103b的实施例的源极层113b的典型表面数密度。如图2B所示，具有大约这种表面数密度的稀释CNT网络具有极高的透射比230，因此有利于允许在CN-VOLET 103b的一些实施例中的电致发光发光层206b中所产生的光逸出，使得就由CNT源极层113b所导致

的透射比损失来说,CN-VOLET 103b的能量效率所受的影响被最小化(大约为1%)。图2A中所示稀释网络透过可见近红外光谱的透射比在图2B中示出,并且大于98%的可见波长透射比。

[0047] 如图1B和图1C所示,在一些实施例中,有源层116包括两个有机半导体层203,这里标记为203a和203b。有机半导体层203a可以包括多晶有机半导体材料,并且有机半导体层203a涂覆到DS-VOLET 103的源极层113中的至少一部分上。举例来说,图1C中的源极层113b的涂层形成了有机半导体层203a的极粗糙的顶部表面形态,这至少部分是因为源极层113b中包括纳米管。

[0048] 举例而言,直接生长于碳纳米管源极层113b上的并五苯,使多晶体晶粒成核,所述多晶体晶粒相对于纳米管以及暴露的CN-VOLET栅极介电202a的取向不同,其中所述栅极介电与源极层113b的纳米管相邻。在纳米管上成核的晶粒的特定取向,将有机半导体层203a的高迁移率平面取向为与利于CN-VOLET 103b操作的电流流向相一致。因此,高迁移率平面的方向高度有利于CN-VOLET 103b的性能。在纳米管上的高迁移率晶粒也是生长最快的晶粒,因此,在沉积完有机半导体层203a之后,快速生长的晶粒会形成最终表面拓扑结构中的高点。

[0049] 图3所示为生长于稀释CNT网络上的并五苯多晶体晶粒的重新取向的X射线衍射(XRD)和原子力显微镜(AFM)证据。在真空热蒸镀腔室中,并五苯在以下三种基板类型上以1 Å/s的速率生长到560nm的厚度,所述三种基板类型为:1) 在涂有BCB的玻璃上的稀释CNT网络;2) 在玻璃上的45nm厚的CNT膜;以及,3) 涂有BCB但不存在CNT的玻璃基板。45nm厚的膜允许进行在不存在任何BCB区域的表面上生长并五苯的实验,就像在CN-VOLET中所用的稀释CNT网络的情况那样,这是因为45nm厚的CNT膜中的CNT能有效地涂覆了整个基板表面。图3(a)中的XRD数据233、236以及239与具有如下特点的并五苯晶粒相一致:并五苯晶粒的a-b平面在基板中存在CNT的区域上被取向为近似垂直方向,而并五苯晶粒的a-b平面在CNT之间的光裸介电区域上被取向为平行于区域中的基板。图3(b)所示为在涂有BCB的玻璃基板上的稀释CNT网络的AFM图像。对于CN-VOLET 103b的一些实施例来说,图3(b)中的CNT表面数密度与源电极中所用的CNT表面数密度相似。图3(a)中针对45nm CNT样本的XRD数据233中的缺少较低阶峰值,这表明,当不存在暴露的BCB区域时,不存在被取向为其a-b平面平行于表面的晶粒。在图3(a)中,BCB样本上的稀释CNT上的并五苯的XRD数据236表明XRD峰值来自以下晶粒取向:a-b平面平行于基板表面的晶粒,a-b平面近似垂直于基板表面的晶粒。XRD数据239中的光裸BCB的XRD峰值仅指示出a-b平面平行于表面的并五苯晶粒的存在。这指示出CNT将并五苯晶粒的重新取向成核为近似垂直方向,这是有利于在CN-VOLET 103b中输送电荷的方向,从而增强其性能。在BCB上的45nm CNT膜和稀释CNT网络上生长的并五苯的表面在图3(c)和图3(d)中的AFM图像示出分别为41.1nm和51.9nm的较大根均方(RMS)表面粗糙度值。这些RMS粗糙度值显著大于针对光裸BCB样本上的并五苯在图3(e)中的AFM图像中所测得的20.8nm RMS粗糙度。AFM数据233、236以及239表明,在基板表面上的CNT的存在(并五苯随后生长于顶部)显著增加了并五苯的表面RMS粗糙度。当并五苯a-b平面被取向为近似垂直方向时,并五苯分子是平着的,其长轴平行于CNT长轴,如在图4中的图式所描绘。

[0050] 参看图1C中所示的实施例,>30nm的RMS表面粗糙度(例如,如图3(d)中的AFM图像

所测得)产生了高于有机半导体层203a达120nm以及低于有机半导体层203a达120nm的离群值(膜中极高或极低的区域)。这些相对于有机半导体层203a的平均厚度突起或凹陷的表面区域所跨越的范围大于所有发光层206(即,206a、206b以及206c)的总厚度。这种表面粗糙度可能导致发光层206上的直接短路,从而使得AMDS-VOLET像素100的电流效率为不工作的或会降低亮度的。

[0051] 为了克服这种直接短路的问题,可以沉积无定形的、可溶液制备的有机半导体层203b来作为平坦化层。在一些实施例中,可溶液制备的无定形的有机半导体,聚[9,9-二辛基-笏-共-N-(4-丁基苯基)-二苯胺](TFB),可以用于平坦化层并充当有机半导体层203b。可以从甲苯或其他溶剂中将TFB旋涂到粗糙多晶体小分子有机表面上。图5所示为由粗糙多晶体表面中的TFB所进行的此类平坦化的一个实例。图5(a)所示为在平坦化之前的粗糙光裸多晶体有机表面,其中RMS表面粗糙度为27nm。通过改变生长条件,图5(a)中的表面变得比图3(d)中的51.9nm RMS表面粗糙度更加平滑。图5(b)所示为在通过TFB平坦化之后的图5(a)中的同一表面,从而形成了减小后的10.5nm的RMS粗糙度。

[0052] 作为此平坦化的有效性的一个实验,将具有图6中所示结构的CN-VOLET装置103c制造为具有以及不具有TFB平坦化层,并对装置性能进行比较。在图6的制造实例中,基板126为玻璃;栅电极201a为掺杂有锡的氧化铟(ITO);介电层109a为双层,其中第一层为所沉积氧化铝的原子层202a,第二层为BCB层202d;源极层113b为这样的稀释CNT网络,其中CNT表面数密度相似于图3B的AFM图像中所示的CNT表面数密度;第一有机半导体层203a为小分子多晶体有机物质;第二有机半导体层203b为TFB;第三有机半导体层203c(空穴注入层)为共掺杂有氧化钼的NPD;空穴传输发光层206a为NPD;电致发光发光层206b为共掺杂有Ir(ppy)3的CBP;电子输送发光层206c为3TPYMB;电子注入导体层209a为氟化锂;而金属导电层209b为铝。在图6的图示中,多晶体有机半导体层203a被示有尖峰,用来表示其粗糙表面。

[0053] 图7所示为由TFB平坦化层所实现的电流效率的改善,电流效率以坎德拉/安培(Cd/A)为单位来测量并且被绘制成被测试的CN-VOLET 103c(图6)的亮度的函数,其中亮度以坎德拉每平方米(Cd/m<sup>2</sup>)为单位。漏极电压(V<sub>D</sub>)被从0V扫描至-9V,而栅极电压(V<sub>G</sub>)被保持恒定于-3V。在没有TFB平坦化层的情况下,电流效率243会减少两倍以上。电流效率上的这种减少归因于在不存在TFB的CN-VOLET装置103c中的第一有机半导体层203a与导电层209a和209b之间会发生直接短路,这是由粗糙多晶体有机半导体层表面所造成的。存在TFB的CN-VOLET装置103c所具有的电流效率246为不存在TFB情况下的两倍以上,这是因为有机半导体层203a和203b一起来说足够平滑,从而能实现随后沉积的空穴注入层203c和发光层206a、206b以及206c的充分覆盖,从而驱动电流通过发光层206a、206b和206c,因此具有较高的电流效率。

[0054] 但是,应注意,无定形的可溶液制备的有机半导体材料无法匹配多晶体半导体材料的迁移率。多晶体半导体材料的高迁移率取向晶粒为有机半导体层203a的拓扑结构中的最高特征,这一事实允许使用厚度被限制的有机半导体层203b,有机半导体层203b可以填充在这些最高特征周围并且轻轻地涂覆在这些最高特征上,进而减少由于此类层所造成的任何性能损失。有机半导体层203b可以进一步掺杂有可共溶的掺杂剂和界面掺杂剂,这些掺杂剂可以在沉积此平坦化层之前和/或之后进行沉积。可能的掺杂剂包括SbCl<sub>5</sub>、W<sub>0</sub><sub>3</sub>、氧化钼、ReO<sub>3</sub>、氯化铁、铁氧化物、2,3,5,6-四氟-7,7,8,8-四氰醌二甲烷(F4TCNQ)、1,3,4,5,7,

8-六氟四氰基萘醌二甲烷(F6-TNAP)以及3,6-二氟-2,5,7,7,8,8-六氟醌二甲烷(F2-HCNQ)。有机半导体层203a可以包括经掺杂或未掺杂的聚合物,诸如TFB或聚[N,N'-二(4-丁基苯基)-N,N'-二(苯基)-联苯胺](聚-TPD)。在替代实施方案中,有机半导体层203a可以包括高度导电的聚合物,诸如聚(3,4-乙烯二氧噻吩)聚(磺化苯乙烯)(PEDOT:PSS),或者可溶液沉积的纳米颗粒层。

[0055] 图5(b)中所示的平坦化表面的粗糙度为10.5nm。在一些应用中,此粗糙度可能是过大的,进而防止了在随后沉积完发光层和漏极层之后获得高性能装置。通过将第二平坦化层旋涂到第一平坦化层的顶部上,可以减小该粗糙度。在旋涂之前,第一层被制成与第二层不可溶。达成此目标的一种方法是使第一平坦化层交联化,并使得其与其原始溶剂不可溶,进而允许再次使用相同的聚合物和溶剂溶液。已知在持续恰当时段的退火过程(annealing process)中,TFB可以在某一温度以上交联化,这意味着TFB可以用作可交联化的第一和第二平坦化层,只要其在沉积第二TFB层之前通过恰当处理来交联化即可。如先前提及,TFB的载流子迁移率低于多晶体半导体层,并且因此,使用多个聚合物平坦化层可能会增加该装置的串联电阻,进而会将其功耗增加到超过其可承受的程度。对聚合物平坦化层进行掺杂是减轻此问题的一种方法。但是,在存在两个聚合物平坦化层的情况下,第二层可以比第一层掺杂得更浓。对于可以将第一平坦化层掺杂到何种程度存在一个上限,因为一旦跨过了某个点,DS-VOLET的开关比会受损,因为载流子密度过高会导致断开状态(off-state)电流增高。第一聚合物平坦化层的交联化会保护掺杂较浓的第二聚合物平坦化层以免污染DS-VOLET的下部层。使第二聚合物层掺杂较浓可以将其对DS-VOLET功耗的负面影响最小化。

[0056] 另外,在一些实施例中,有机半导体层203a和发光层206a、206b以及206c可以通过热蒸镀来沉积。而且,有机半导体层203b可以通过旋涂来沉积。在其他实施例中,可以将可溶解的高迁移率宽带隙有机小分子添加到溶液中,以便通过下文提及方法中的任一者来用作有机半导体层203a。高迁移率指代约 $0.01\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ 的场效应载流子迁移率。由于宽带隙的存在,该有机小分子的薄膜固相不会吸收可见光。在该溶剂干燥期间和之后,该有机小分子可以形成局域多晶体晶粒,这种多晶体晶粒使得该有机小分子能获得高迁移率。但是,应注意,包括经溶解的有机小分子材料的此类溶液的粘度可以是很低的,低到使得在下文提及的旋涂或其他技术中无法达成该材料的充分厚度,即使将该有机小分子的浓度增加到饱和点之后也不行。为了增加该粘度,可以将诸如TFB或聚TPD的可溶解无定形聚合物以控制量进行添加,以增加该可溶解有机小分子溶剂溶液的粘度,使得其允许所选用的沉积方法能够达成恰当的膜厚度和形态。使用或不使用聚合物增稠剂的溶液沉积型的小分子有机半导体层203a,可以同聚合物平坦化的热蒸镀型的小分子有机半导体层203a至少一样平滑,并且可能比后者更平滑。在其他实施例中,有机半导体层203a可以由宽带隙、高迁移率的低聚或聚合材料组成,这些材料可以在溶剂干燥期间及之后通过下文提及的沉积方法中的一者来形成局域多晶体晶粒。这些局域多晶体晶粒可以允许所沉积的薄膜获得高迁移率。溶液沉积的低聚或聚合有机半导体层203a,可以同聚合物平坦化的热蒸镀的小分子有机半导体层203a至少一样平滑,并且可能比后者更平滑。在一些实施例中,可以使用以下可溶液制备以及不可溶液制备的方法中的任一者来沉积有机半导体层203和发光层206中的至少一者:旋涂、浸涂、落模铸造、丝网印刷、喷涂、蒸汽喷印、物理气相沉积、热梯度升华(thermal

gradient sublimation)、刮刀涂布、凹版印刷、柔性版印刷、热蒸镀以及喷墨印刷。

[0057] 导电线123,包括数据导电线123a(即提供 $V_{\text{data}}$ 电压信号)(这里标记为123a1和123a2)、源极导电线123b(即提供 $V_{\text{source}}$ 电压信号)以及扫描导电线123c(即提供 $V_{\text{scan}}$ 电压信号),可以使用以下物质中的至少一者来加以制造:金属;并入或未并入导电纳米颗粒的碳膏;可溶液制备的导电聚合物,诸如聚(3,4-乙烯二氧噻吩)聚(磺化苯乙烯)(PEDOT:PSS);溶液沉积的导电纳米颗粒;以及并入导电纳米颗粒的膏。沉积导电线123的方法包括:溅射法、热蒸镀、电子束蒸镀、电镀、旋涂、浸涂、落模铸造、刮刀涂布、丝网印刷、喷涂、凹版印刷、柔性板印刷、通过喷嘴进行的膏沉积,以及喷墨印刷。数据导电线123a在其自身与源极导电线123b和扫描导电线123c之间的重叠区域中具有层间介电(ILD)以防止其间的电通信。源极导电线123b与DS-VOLET 103的源极层113a电接触。数据导电线123a提供到达Sw-T 106的一侧的连接。Sw-T 106的另一侧连接到DS-VOLET栅电极201a。在一些实施例中,漏极层119为沿一整列中的多个有源单元102的一个连续层(下文会更详细描述)。ILD被沉积在漏极层119与源极导电线123b和扫描导电线123c之间的重叠区域中。该ILD层可以包括一种或多种不同的有机或无机绝缘材料。举例而言,该ILD层可以包括氧化硅、氮化硅、氧化铝、氧化铪、BCB,或聚酰亚胺。该ILD层可以通过PECVD、ALD、旋涂或上文提及的另一种沉积方法来沉积。

[0058] 图6中的CN-VOLET 103c的实施例的切换速度经测量,以确定CN-VOLET 103c的截止频率对于典型的显示应用是否足够。该像素大小为 $1\text{mm} \times 1\text{mm}$ ,正如 $1\text{mm}$ 宽CNT源极113b与 $1\text{mm}$ 宽铝导电层209b的重叠所界定。寄生重叠电容据估计有像素中的栅极电容的两倍大,这是因为CNT源极层113b与ITO栅电极201a的重叠区域为 $1\text{mm}$ (CNT宽度) $\times 3\text{mm}$ (ITO宽度),此栅电极的宽度为所需宽度的3倍宽,这有助于有利的装置制造,且无需过度关注层对准问题,但是,也可以将该宽度减小以减小寄生电容。该装置在CNT源极113b与铝导电层209b之间被给予恒定电压。ITO栅电极201a被连接到供应方波电压信号的函数发生器,使得CN-VOLET 103c在其导通状态与断开状态之间振荡。由CN-VOLET 103c发射的闪光被Si光电二极管测量,该Si光电二极管连接到高速放大器,该高速放大器的信号由示波器读取。图8所示为在 $3\text{kHz}$ 频率下的CN-VOLET的光电二极管响应253和输入信号256。截止频率是在光电二极管响应衰减 $3\text{db}$ 时取得的,并且测得为约 $9.1\text{kHz}$ 。考虑到寄生电容两倍于像素栅极电容的大小,不具有此寄生电容且经恰当设计成 $1\text{mm} \times 1\text{mm}$ 的像素的切换速度会有可能为这个量的三倍,约为 $27\text{kHz}$ 。用于手持式装置及电视的典型显示像素的典型边尺寸处于约 $100\mu\text{m}$ 到约 $400\mu\text{m}$ 的范围内。随着 $1\text{mm} \times 1\text{mm}$ 像素大小变小,切换速度反而增加。如果将CN-VOLET 103c(图6)的尺寸减小到典型的手持式显示像素大小和电视显示像素大小,其切换速度的对应增加会分别形成约 $2.7\text{MHz}$ 和约 $200\text{kHz}$ 的值。考虑到后一种情况,由于其切换速度较低, $1920 \times 1200$ 像素WUXGA大屏幕高分辨率电视显示器需要约 $72\text{kHz}$ 来达到 $60\text{Hz}$ 的屏幕刷新率。因此,预期有,对于包括大型高分辨率电视显示器的大多数显示应用来说,CN-VOLET 103c具有的切换速度是足够的。

[0059] DS-VOLET 103的架构具有关于其切换速度的本有益处。由于DS-VOLET与常规TFT之间的架构存在差异,DS-VOLET不会受到限制常规TFT切换速度的相同物理过程的影响。典型TFT的架构使得栅极电荷的充电与放电的速率会受到其通道的电阻的限制,当该TFT处于断开状态时,该电阻极高。但是DS-VOLET不会受其信道电阻的限制,它主要受源极层113a的电阻的限制,源极层113a的电阻相对较低并且不论该装置处于导通或断开状态均近似恒

定。如本领域技术人员所熟知,在TFT中,计算得的截止频率 $f_{Tc} = g_m / (2\pi C_g)$ ,其中 $g_m$ 为跨导而 $C_g$ 为栅极电容。在尝试使用用于常规TFT的已知 $f_{Tc}$ 方程式来计算DS-VOLET的切换速度时,发现,当稀释CNT网络用作包含CN-VOLET 103c的源电极113b时,计算得的 $f_{Tc}$ 大大低估了针对DS-VOLET 103的示例性实施例所测得的实际截止频率。使用 $f_{Tc} = g_m / (2\pi C_g)$ 并插入独立测量的CN-VOLET 103c参数 $g_m = 32\mu A/V$ 和 $C_g = 3.7nF$ 进行计算,计算得的 $f_T = 1.3kHz$ ,比测得的截止频率 $f_{Tm} = 9.1kHz$ 几乎要低一个数量级。但是,更接近所测得的截止频率的模型为:对于包括电阻R和电容C的典型并联RC电路来说,为RC截止频率 $f_{RC} = 1 / (2\pi RC)$ ,对于 $R = 5$ 千欧且 $C = 3.7nF$ 的装置所测得的CNT串联电阻来说, $f_{RC}$ 计算值为8.6kHz,这更加接近于所测得的值9.1kHz。预期会看到与RC模型更相符,因为CN-VOLET栅极的充电和放电受到该源极层的串联电阻的限制,该源极层示意性地与栅电极和有源区域的重叠区域218a所界定的电容器串联连接(即,在CNT间的开放区域中由源极层113b和有机半导体层203a组成的区域,在源极层113a包含CNT的实施例中,在该区域中层203a可以与介电层202a直接接触),从而给出其栅极电容。因为该CN-VOLET有可能拟合该并联RC电路模型,所以简单地通过增加介电层202a的厚度或者是降低介电层202a的介电常数来降低该CN-VOLET的栅极电容,从而有可能增加其速度,但这样做则需要较大的操作栅极电压。但是,减少栅极电容以试图增大常规TFT截止平率是行不通的,如本领域技术人员所了解的,这是因为针对TFT的控制模型中所涉及到的物理过程所致。

[0060] 如上文所论述,AMDS-VOLET像素100布局使得AMDS-VOLET像素100孔径比较大,这至少是由于与发光层206相同的堆叠结构中包括了驱动晶体管,这样就能使AMDS-VOLET像素100中更多的区域用于发光。但是,连同AMDS-VOLET像素100中由DS-VOLET 103所实现的发光层206覆盖的较大面积来看,源极层113a与栅电极201a之间的电容,此处称作栅极电容,在一些实施例中大于必需值。大于必需值的栅极电容可能会限制AMDS-VOLET像素100的切换速度,并且在一些应用中有可能限制AMDS-VOLET像素100的有用性。

[0061] 为了提高切换速度,可以通过使用具有较低介电常数的介电层202a以及/或者增加介电层202a的厚度,来降低DS-VOLET 103的栅极电容。但是,通过这些方法中的任一方法来提高切换速度的代价是栅极电压会成比例增加。在一些应用中,栅极电压成比例增加有可能会限制AMDS-VOLET像素100的有用性。在替代实施方案中,可以通过减少在栅电极201a与源极层113a之间的重叠区域218a中的基板126上的面积覆盖,来降低DS-VOLET 103的栅极电容,进而使得DS-VOLET 103的栅极电容的减少方式不会引起栅极电压成比例增加。以此种方式减少栅极电容,能够使AMDS-VOLET像素100的切换速度增加,但不会出现较大栅极电压的限制性缺点。但是,为了在减少重叠区域218a的同时维持较大的孔径比,可以添加一个过渡导电层。

[0062] 接下来参看图9A,图中所示为图1A中所示的有源单元102(这里标记为102c)的另一实施例的截面图,其包括实例DS-VOLET 103,这里标记为103d。在几个方面上,图9A所示的DS-VOLET 103d不同于图1B所示的DS-VOLET 103a。举例来说,栅电极201a和源极层113a界定出一个重叠区域218b,重叠区域218b具有的面积小于图1B中所示的重叠区域218a的面积。此外,DS-VOLET 103d进一步包括定位于发光层206与有机半导体层203之间的过渡导电层220。ILD层223定位于过渡导电层220与源极导电线123b之间。参看图9B,图中所示为有源单元(标记为102d)的实施例,其包括实例CN-VOLET 103,这里标记为103e。CN-VOLET 103e

包括单壁碳纳米管的稀释网络来作为源极层113b,源极层113b定位于CN-VOLET栅电极201a上方的CN-VOLET栅极介电202a上。如同图9A中的DS-VOLET 103d,CN-VOLET 103e包括定位于发光层206与有机半导体层203之间的过渡导电层220。

[0063] 过渡导电层220将电流从有机半导体层203传递到发光层206,有机半导体层203定位于源极层113a、栅极介电层202a以及栅电极201a之上,发光层206在较大面积上进行沉积,这种电流传递进而使发光区域占据AMDS-VOLET像素100中基本上所有的可用面积。ILD层223防止源极导电线123b与过渡导电层220之间出现电短路。过渡导电层220可以包括一层或多层的任何导电材料,诸如有机或无机材料、透明或不透明金属、半金属或半导体(经掺杂或未掺杂的,优选为掺杂的)。用于过渡导电层220的材料的一些实例包括:单层或多层石墨烯、碳纳米管的稀释网络或非稀释层、掺杂有锡的氧化铟、聚(3,4-乙烯二氧噻吩)聚(磺化苯乙烯)(PEDOT:PSS)、ZnO或氧化铟纳米颗粒。

[0064] 在一些实施例中,过渡导电层220能够透过由发光层206所发射的光。在一些实施例中,过渡导电层220为不透明导体,诸如金属。在那些不透明实施例中,漏极层209可以包括透明材料,而AMDS-VOLET像素100可以被包括在顶部发光显示器中,其中发光层206中所生成的光会传输通过透明漏极层209。此外,在金属过渡导电层220上的光反射减少了AMDS-VOLET像素100的出光(light out-coupling)损失。在替代实施方案中,过渡导电层220的顶部表面被制成为非反射性的,并且可以是黑色的,从而能在环境光辐射到AMDS-VOLET像素100上时改善AMDS-VOLET的对比度;这可以通过双层来完成,其中第一层是金属,然后是黑色导电涂层,诸如:无定形碳、碳纳米管、石墨烯、石墨、PEDOT:PSS或C<sub>60</sub>。

[0065] 另外,当DS-VOLET 103的驱动晶体管层(即,201a、202a、113a、203a以及203b)对从发光层206发出的光敏感,或者是在环境中使用的AMDS-VOLET像素100所遇到的外部光敏感时,包括过渡导电层220的此类实施例可以变得尤其有用。在那些实施例中,过渡导电层220还提供了针对光的势垒,从而改善了AMDS-VOLET像素100的稳定性。在此类实施例中,DS-VOLET 103的驱动晶体管层(即,201a、202a、113a、203a以及203b)的面积覆盖可以小于、等于或大于发光层206的面积覆盖。此外,可以将光吸收或反射层添加在基板层126的底部上,或者是栅电极201a与基板层126之间,或者该基板层自身可以是不透明的,或者栅电极201a自身可以包括不透明的和/或反射材料,诸如金属,以到达为DS-VOLET 103的驱动晶体管层(即,201a、202a、113a、203a以及203b)遮光的目的。

[0066] 连同本文所描述的DS-VOLET 103的说明来看,其中正电荷从源极层113a注入并由栅电极201a控制而电子从漏极层119注入并且电子和空穴在发光层206b(例如,EL层)中重组合来发光,可以在不显著偏离本发明精神的情况下实施此布置的倒置版本。在倒置AMDS-VOLET像素100的情况下,一个实施例可以包括源极层113,源极层113将电子注入到有机半导体层203中,在实施例中这些电子的注入可以由施加给栅电极201a的电压来控制。类似地,空穴可以由漏极层119来注入。然后在发光层206b中,这些空穴可以与注入的电子重组合来发光。额外的变体包括顶部发射倒置设计、完全透明非倒置以及完全透明倒置设计。

[0067] 现在来看Sw-T 106a的论述,在图1B、图1C、图9A以及图9B中所示的有源单元102的实施例中,Sw-T 106a为薄膜晶体管(TFT)。Sw-T 106a中所包括的栅极层109b包括Sw-T栅电极201b和Sw-T栅极介电202b。Sw-T栅电极201b与基板126直接接触,而Sw-T栅电极201b与扫描导电线123c电接触。Sw-T栅极介电202b覆盖了Sw-T栅电极201b的表面,如图1B、图1C、图

9A和图9B中的截面图所示。Sw-T栅极介电202b可以是透明或不透明的，并且可以包括由无机材料(如，氧化铝)和自装置单分子层(SAM)(如，正十八烷基磷酸(ODPA))组成的双层。该无机材料提供了大的电容，并且该SAM充当了疏水层。Sw-T 106a另外包括定位在Sw-T栅极介电202b上的半导体层216。半导体层216可以包括透明或不透明的有机或无机半导体材料(例如，分别为并五苯或无定形Si)。

[0068] 在图6、图13以及图18中所示的有源单元102的各个实施例的截面图中，(相应地)仅示出了CN-VOLET 103c、103f以及103g实施例。但是，如本领域技术人员所了解，在图6、图13和图18中所示的有源单元102的各个实施例中，可以使用DS-VOLET 103来替换CN-VOLET 103c、103f以及103g。

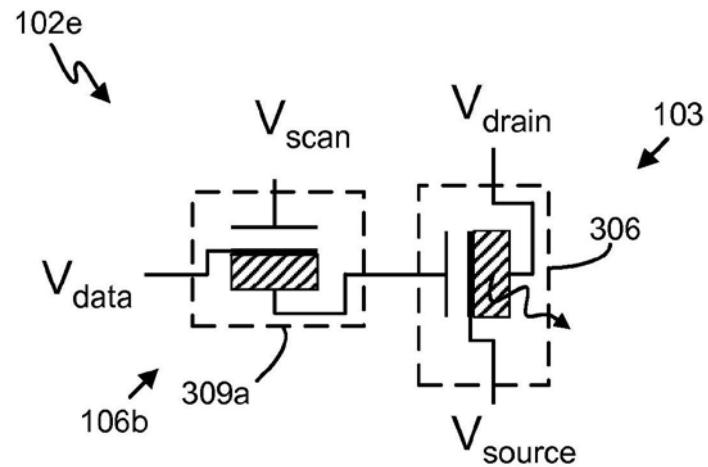

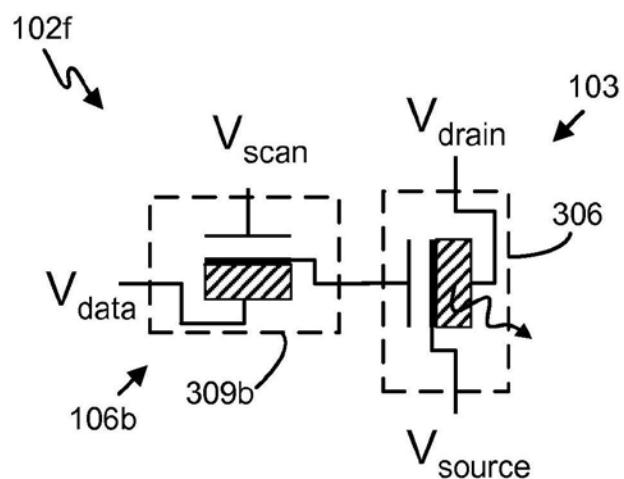

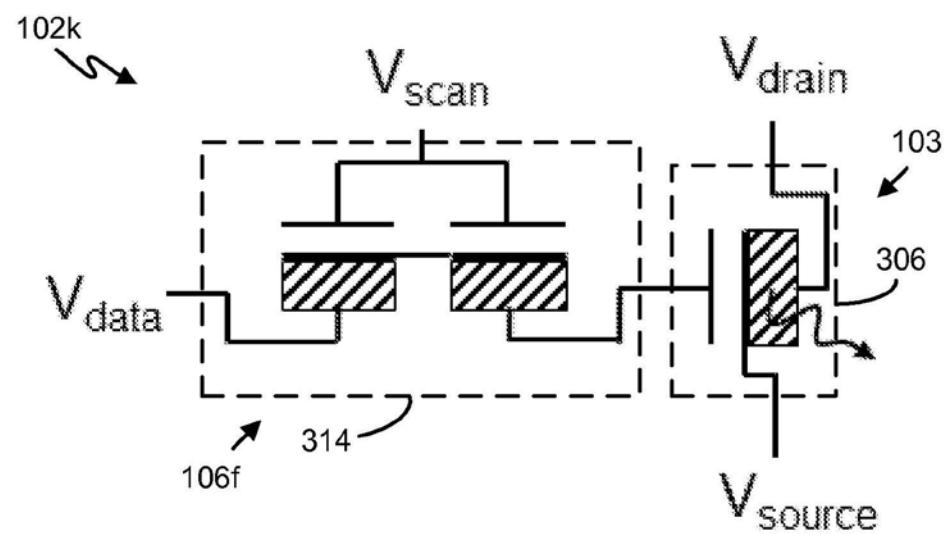

[0069] 图10为图示了图1B、图1C、图9A以及图9B中的截面图所示的有源单元102a的电路图。Sw-T 106a包括薄膜晶体管，该薄膜晶体管用晶体管电路元件303来表示，而DS-VOLET 103用DS-VOLET电路元件306来表示。如该图所示， $V_{\text{scan}}$ 信号耦接至晶体管电路元件303的栅极。另外， $V_{\text{data}}$ 信号耦接至晶体管电路元件303的源极/漏极，而晶体管电路元件303的漏极/源极耦接至DS-VOLET 103的栅极。

[0070] 图11为图示了图1B、图1C、图9A、图9B以及图3所示的Sw-T 106a的实例布局的平面图。图11中所示的布局对应于图1A中用虚线界定的Sw-T区域129。图11中所示的Sw-T 106a包括栅极层109b(包括图1B、图1C、图9A以及图9B中所示的Sw-T栅电极201b以及Sw-T栅极介电202b)，并且Sw-T 106a还包括定位在栅极层109b上的半导体层216。导电线123d耦接至半导体层216，尽管未在图11中示出，导电线123d耦接至DS-VOLET 103的DS-VOLET栅电极201a。扫描导电线123c耦接至栅极层109b，而数据导电线123a耦接至半导体层216中与耦接至导电线123d的半导体层216末端相反的末端。

[0071] 接下来，Sw-T设计被描述成包括以各种方式连接的单个或多个DS-VFET来代替在Sw-T 106a中所描述的实施例中的TFT。包括DS-VFET的这些版本具有以下优势，其具有的DS-VFET和DS-VOLET设计优于传统TFT设计。简言之，通道长度较短并且面积电流容量较大的DS-VFET架构使得，相对于相同的电流输出容量来说，Sw-T可以被制作得更小，并且因此相对于由包括TFT的Sw-T制造成的架构来说，占据的面积更小。这使得AMDS-VOLET像素100的孔径比进一步增大。

[0072] 图12为图示Sw-T 106(这里标记为106b)的实施例的实例布局的平面图，而图13为包括Sw-T 106b的有源单元102e的实施例的截面图。图12中所示的布局对应于图1A中用虚线界定的Sw-T区域129。Sw-T 106b包括单个碳纳米管实现垂直场效应晶体管(CN-VFET)，它也可以替换为DS-VFET。CN-VOLET 103b的各个实施例以及DS-VFET和DS-VOLET 103的其他实施例见述于以下文献中：于2008年9月10日提交的标题为“纳米管实现栅极电压控制发光二极管(Nanotube Enabled, Gate-Voltage Controlled Light Emitting Diodes)”的序列为No.12/677,457的美国专利申请公开案US 2010/0237336；于2011年3月4日提交的标题为“包括电逾渗源极层的半导体装置及其制造方法(Semiconductor Devices Including an Electrically Percolating Source Layer and Methods of Fabricating the Same)”的国际申请号为No.PCT/US2011/027155的国际公开案WO 2011/109693 A2；以及于2010年3月4日提交且序列为No.61/310,342的标题为“包括纳米管层和存储器层的半导体装置及其制造方法(Semiconductor Devices Including a Nanotube Layer and a

Memory Layer and Methods of Fabricating the Same) 的美国临时申请案,以上所有文献均以全文引用的方式并入本文中。”不同于图11中的包括TFT的Sw-T 106a,图12的Sw-T 106b为包括具有稀释碳纳米管层的源极层113c的CN-VFET。在包括CN-VOLET 103f的情况下,可以同时沉积源极层113b和113c(图13)。类似地,在包括DS-VOLET 103的情况下,可以同时沉积源极层113a(图1B)和113c。而且,图12和图13中的Sw-T 106b可以包括DS-VFET,在该DS-VFET中,源极层113c可以包括其他源电极,包括先前针对DS-VOLET 103列出的逾渗稀释网络中的任一者。源极层113c可以包括任何低态密度金属,包括无机或有机的;低态密度半导体,包括无机或有机的;或低态密度半金属,包括无机或有机的。低态密度有机半金属的实例包括石墨烯。石墨烯可以是单层或多层的,并且可以经图案化以包括穿孔,或者不加图案化。参看图13,CN-VOLET 103f的结构与图1C中所示实施例中所示的结构相同,并且它可以任选地替换为图1B、图9A或图9B中所示的结构。

[0073] 与图1B、图1C、图9A以及图9B中所示的Sw-T 106a相似,图13中所示的Sw-T 106b包括栅极层109b,该栅极层109b包括Sw-T栅电极201b以及Sw-T栅极介电202b。Sw-T栅电极201b耦接至扫描导电线123c(图12)。Sw-T栅极介电202b覆盖了Sw-T栅电极201b的表面。Sw-T栅电极201b可以是透明或不透明的,并且可以包括由诸如氧化铝(例如,Al<sub>2</sub>O<sub>3</sub>)的无机材料和诸如BCB的聚合物组成的双层。该无机材料提供了大的电容,并且该聚合物充当了疏水层。

[0074] 接下来,Sw-T 106b包括耦接至数据导电线123a的源极层113c。如上文所提及,源极层113c包括稀释碳纳米管层。定位在源极层113c上的是半导体层216。半导体层216包括单层或多层,或者是经掺杂的单层或多层。这些层可以包括诸如并五苯的有机半导体材料或者是诸如硅(无定形的纳米晶体/微晶体或多晶体)的无机半导体材料。硅可以使用PECVD来沉积。在一些实施例中,半导体层116中可能的有机p型掺杂剂包括SbCl<sub>5</sub>、W<sub>0</sub><sub>3</sub>、氧化钼、ReO<sub>3</sub>、氯化铁、铁氧化物、F4-TCNQ、F2-HCNQ或F6-TNAP。在半导体层116包括硅的其他实施例中,可能的掺杂剂包括硼(p型)以及磷或砷(均为n型)。

[0075] 图14A为图示图13中所示的有源单元102e的实例的电路图。如图13所示,在Sw-T 106b中,导电线123d定位于半导体层216上,从而形成耦接至DS-VOLET 103或耦接至CN-VOLET 103f的漏电极。如上文所论述,Sw-T 106b包括CN-VFET,该CN-VFET在图14A中用CN-VFET或DS-VFET电路元件309a来表示。图14B为图示有源单元102的另一实例的电路图,这里标记为102f。与图14A中所示的有源单元102e相似,有源单元102f包括DS-VOLET 103。有源单元102f还包括Sw-T 106b。另外,Sw-T 106b包括CN-VFET,该CN-VFET在图14B中用CN-VFET或DS-VFET电路元件309b来表示。但是,在CN-VFET电路元件309b中,Sw-T 106b的源极-漏极连接是反向的。Sw-T 106b的源电极(即源极层113c)(而不是Sw-T 106b的漏电极)耦接至导电线123d,从而实现到CN-VOLET 103的栅电极201a的电连接。因此,在有源单元102f中,漏电极由数据导电线123a1形成。

[0076] 图15为图示Sw-T 106(这里标记为106c)的实施例的实例布局的平面图,而图16为包括图15所示的平面图中所示Sw-T 106c的有源单元102g的实施例的电路图。图15中所示的布局对应于图1A中用虚线界定的Sw-T区域129。参看图15和图16,所示的Sw-T 106c包括双横向CN-VFET或双横向DS-VFET。在图16中,Sw-T 106c中所包括的双横向CN-VFET或双横向DS-VFET用双横向CN-VFET或双横向DS-VFET电路元件312来表示。双横向CN-VFET包括两

个CN-VFET,这两个CN-VFET并联耦接并且与反向的源极层113c、113d和漏电极并排布置,并且这两个CN-VFET共用一个共同的栅极层109b。类似地,双横向DS-VFET包括两个DS-VFET,这两个DS-VFET并联耦接并且与反向的源极层113c、113d和漏电极并排布置,并且这两个DS-VFET共用一个共同的栅极层109b。

[0077] 与Sw-T 106b相比,Sw-T 106c(即包括双横向CN-VFET或双横向DS-VFET)在通过数据导电线123a向DS-VOLET栅电极201a和从该栅电极处供应和移除电荷方面,能实现更好的电流控制。相比之下,当图12、图13、图14A以及图14B中的Sw-T 106b(即包括单个CN-VFET或DS-VFET)被正向偏置时,电流从源极层113c流到导电线123d(即从源极到漏极),并且该电流得到充分的控制以添加足够量的电荷来以指定的灰度操作DS-VOLET 103。但是,当Sw-T 106b被反向偏置时,从导电线123d流到源极层113c(即从漏极到源极)的电流没有得到充分的控制,从而在有源单元102的刷新事件之间的时间内会导致DS-VOLET栅电极201a上所储存的电荷发生损失。刷新事件包括有源单元102的定址,方式是对指定行中的扫描导电线123c的电压施以脉冲,进而使用来自指定列的数据导电线123a的电荷来对DS-VOLET 103的DS-VOLET栅电极201a进行充电。对进入和离开DS-VOLET 103的栅极的电荷转移进行同等良好的控制实现了对AMDS-VOLET像素100的成功操作。

[0078] 可以使用与上文提及的Sw-T 106b相同的制造过程来制造Sw-T 106c中所包括的双横向CN-VFET或双横向DS-VFET的栅极层109b、源极层113c、113d、半导体层216b、216c,不同之处在于如图15中所示的实例布局所示,Sw-T 106c中的各层均被图案化。此外,可以同时沉积源极层113c、113d来作为相同图案化层的一部分。类似地,也可以同时沉积半导体层216b、216c来作为相同图案化层的一部分。在图15中所示的实例中图示了这些层的布置。在Sw-T 106c的一些实施例中,导电线123d形成图15中的下部单个CN-VFET或DS-VFET的漏电极,而导电线123a形成图15中的上部单个CN-VFET或DS-VFET的漏电极,这两种导电线可以包括一种材料,该材料在与该双横向CN-VFET或双横向DS-VFET的半导体层216b、216c相接触时形成电子或空穴的肖特基势垒(>0.1eV)。

[0079] 图17为图示Sw-T 106(这里标记为106d)的另一实施例的实例布局的平面图,而图18为包括Sw-T 106d的有源单元102h的实施例的截面图。图17中所示的布局对应于图1A中用虚线界定的Sw-T区域129。在此实施例中,Sw-T 106d包括双倒置CN-VFET或双倒置DS-VFET。图18所示为包括双倒置CN-VFET的Sw-T 106d的实施例。双倒置CN-VFET和双倒置DS-VFET的设计分别类似于单个CN-VFET和DS-VFET,其至少一个差异在于添加了充当漏极层的另一源极层113e。在Sw-T 106d包括双倒置CN-VFET的情况下,源极层113e包括稀释碳纳米管网络,而源极层113e耦接至导电线123d。栅极层109c定位在包括Sw-T栅极介电202c和Sw-T栅电极201c的源极层113e上,如图17和图18所示。

[0080] 可以使用与上文所提及的Sw-T 106b相同的方式和相同的材料来制造双倒置CN-VFET或双倒置DS-VFET的栅极层109b、源极层113c、半导体层216,不同之处在于如图17中的实例布局所示,Sw-T 106d中的各个层均被图案化。在图17和图18中所示的实例中图示了这些层的覆盖。举例来说,源极层113e沉积于半导体层216上,而第二栅极层109c沉积于源极层113e上。如图18所示,第二栅极层109c包括沉积于源极层113e上的Sw-T栅极介电202c以及沉积于Sw-T栅极介电202c上的Sw-T栅电极201c。Sw-T栅极介电202c可以是单个绝缘层或多个绝缘层。Sw-T栅电极201c可以是金属(例如,铝(A1))、TCO(例如,ITO),以及/或者该两

种或其他导电材料的混合物,该其他导电材料包括碳纳米管、石墨烯、PEDOT:PSS以及导电纳米颗粒。图17和图18中所示的Sw-T 106d的实施例,尽管不同于Sw-T 106c(即包括双横向CN-VFET以及双横向DS-VFET),仍能够实现对Sw-T 106b(即包括单个CN-VFET以及单个DS-VFET)的相似的电流控制益处。

[0081] 图19为图示Sw-T 106(这里标记为106e)的另一实施例的实例布局的平面图,而图20为包括Sw-T 106e的有源单元102j的实施例的截面图。图19中所示的布局对应于图1A中用虚线界定的Sw-T区域129。在此实施例中,Sw-T 106e包括反向串联双CN-VFET或反向串联双DS-VFET。图19和图20所示为包括反向串联双DS-VFET的Sw-T 106e的实施例。该反向串联双DS-VFET设计类似于单个DS-VFET,至少一个差异在于添加了另一源极层113f,该源极层充当第二串联连接但极性相反的DS-VFET的源极层。源极层113f包括用于包含稀释纳米管网络的DS-VFET或DS-VOLET中的所有先前提及的材料。源极层113f耦接至导电线123d。如图19和图20所示,Sw-T 106e的漏电极123e在各个DS-VFET之间共用。图21所示为包括反向串联双DS-VFET Sw-T 106e(标记为电路元件313)的有源单元102j的电路图。

[0082] 可以使用与上文所提及的Sw-T 106b相同的方式和相同的材料来制造反向串联双DS-VFET的栅极层109b、源极层113f和113g、半导体层216,不同之处在于如图19和图20中的实例布局所示,Sw-T 106e中的各个层均被图案化。在Sw-T 106e的一些实施例中,漏电极123e可以包括一种材料,该材料在与反向串联双DS-VFET的半导体层216b接触时形成电子和空穴的欧姆接触势垒(<0.2eV)。图19和图20中所示的Sw-T 106e的实施例,尽管不同于Sw-T 106c(即包括双横向CN-VFET以及双横向DS-VFET),仍能够实现对Sw-T 106b(即包括单个CN-VFET以及单个DS-VFET)的相似的电流控制益处。

[0083] Sw-T 106的另一实施例包括在反向串联双DS-VFET实施例中使每一DS-VFET的极性变反,并且示于图22、图23以及图24,且这里标记为Sw-T 106f。图23为包括Sw-T 106f的有源单元102k的实施例的截面图。Sw-T 106f中的DS-VFET共用一个共同的源电极113h,并且具有独立图案化的漏电极,如图22和图23所示。图24所示为反向串联双DS-VFET Sw-T 106f的电路图,其电路元件标记为314。

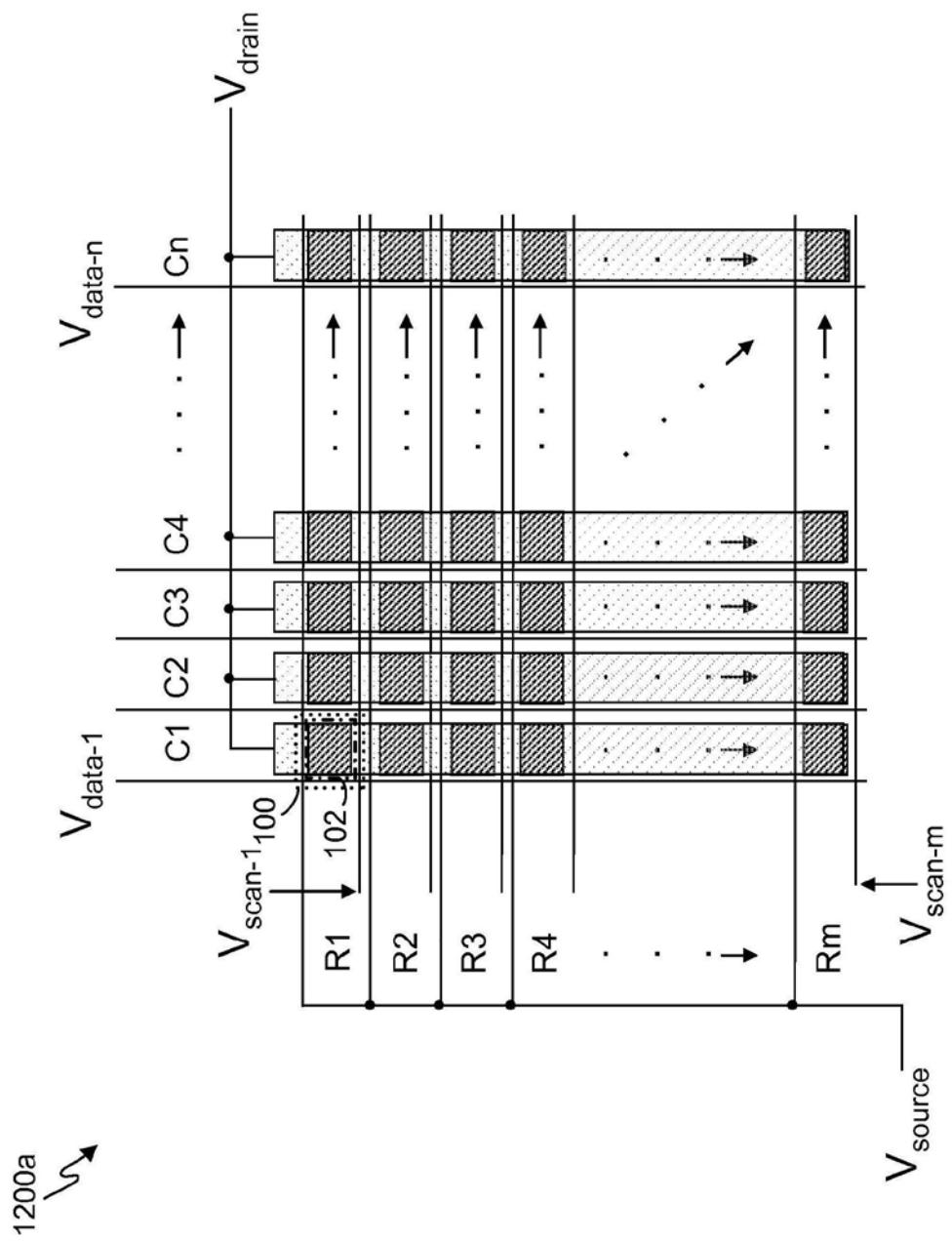

[0084] 图25为图示AMDS-VOLET像素100的阵列1200(这里标记为1200a)的实施例的实例布局的平面图。每一AMDS-VOLET像素100各自发出具有相同颜色的光,并且每一AMDS-VOLET像素100包括根据上文所述实施例中的任一者的有源单元102。有源单元102排布于n列×m行的阵列1200a中,每一有源单元102的位置用坐标(n,m)表示,其中n为列数目,而m为行数目。每一有源单元102可以由 $V_{\text{scan}-n}$ 和 $V_{\text{data}-m}$ 信号来定址,该两个信号由外部控制电路提供,该外部控制电路可以在显示面板的外围安装到显示面板。所有 $V_{\text{drain}-m}$ 电压信号均可以连接到单个电压供应器来提供指定电压。所有 $V_{\text{source}}$ 电压信号均可以连接到单个电压供应器来提供指定电压。

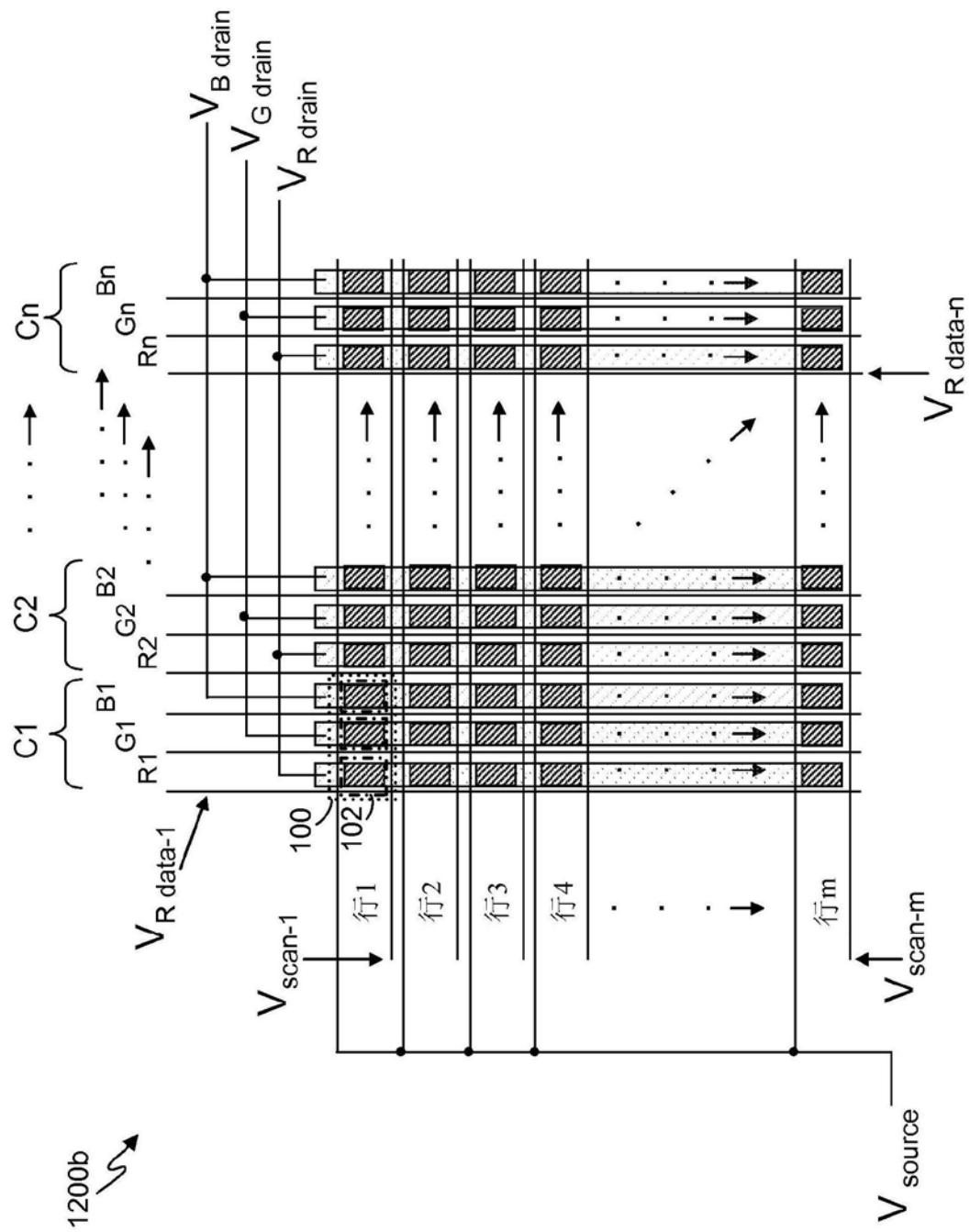

[0085] 图26为图示AMDS-VOLET像素100的阵列1200(这里标记为1200b)的另一实施例的实例布局的平面图。每一AMDS-VOLET像素100包括三个有源单元102,根据上文所述的实施例中的任一者,每一有源单元各自发出不同的色光(例如,红色、蓝色、绿色)。在一个实施例中,AMDS-VOLET像素100包括并排的三个有源单元102,其中一个有源单元102为红色(R),一者为绿色(G),另一者为蓝色(B)。重复的有源单元102排布于n列×m行的矩阵中,每一重复单元的位置用坐标(n,m)表示,其中n为列数目,而m为行数目。如图26所示,每一列Cn被划分

成三种颜色。列Cn根据列颜色(例如,Rn(红)、Gn(绿)、Bn(蓝))划分成单独的列。

[0086] 根据各种颜色获得方法,可以达成有源单元102的各种颜色。在第一颜色获得方法中,确定颜色的方式为,在相应的有源单元102中的DS-VOLET 103的发光层206b(即EL层)中对所用的材料进行选择。换言之,发光层206b中所包括的材料会发出所要的颜色,R、G或B。在第二颜色获得方法中,发光层206b中所包括的材料经选择以发出白光,并且使用恰当的色光过滤层来使指定的R、G或B色光传输透过该色光过滤层。该色光过滤层可以放置在基板层126的另一侧上,或者是在基板层126与栅极层109a之间的需要指定色光的区域中(例如,在底部发射显示器中,其中来自发光层206b的光发射通过基板层126)。在顶部发射显示器(来自发光层206b的光发射通过DS-VOLET 103的漏极层119)的情况下,该色光过滤层可以放置在漏极层119的顶部上。在第三颜色获得方法中,发光层206b发出蓝光,并且使用恰当的颜色改变层来分别在R和G有源单元上获得R光和G光。颜色改变层的位置可以类似于第二颜色获得方法中的色光过滤层所用的位置。

[0087] 所有的先前提及的实施例均假定使用了本领域技术人员所熟知的常规图案化方法。常规光刻为用于在随后的工艺步骤中界定图案的一种广泛使用的方法,所述工艺步骤例如,在沉积光阻之前对曾沉积在整个基板上的感兴趣材料进行消减蚀刻(湿式或干式)。光阻为用于通过通常用紫外(UV)光暴露所要区域来制造图案的聚合物材料。在UV曝光之后,正/负光阻的暴露/未暴露区域变得可溶于显影液中。该光阻还覆盖着整个基板,并且通常通过旋涂来沉积。还可以利用除消减蚀刻以外的其他方法。对于其他金属类型,还可以使用诸如剥离工艺(lift-off process)的方法,该方法通常用于界定金属。在剥离方法中,在沉积感兴趣材料(例如可以是金属)之前,敷加光阻。光阻通常专用于此目的,它通常被称作剥离光阻,然后,该光阻会经历UV曝光的常规光刻工艺步骤,并在显影液中进行图案显影。在将图案传递给该剥离光阻之后,可以通过诸如溅射的常规方法来沉积该金属。在沉积该金属之后,仍存在剥离光阻的区域可以被溶解于溶剂中,并且可以将在该区域中的金属剥离,从而留下具有所要布局的图案化金属层。而且,对于自身图案化的方法来说,诸如凹版印刷、柔性板印刷、喷墨印刷以及蒸汽喷印,常规光刻可能并不是必需。

[0088] 本申请案中所含有的所有附图并非按比例绘制。有机半导体层无需限制为有机物质。在其他实施例中,有机半导体层可以是无机物质,在这种情况下它们仅是半导体层。可能的无机半导体包括硅(无定形的单晶体、微/纳米晶体以及多晶体)以及纳米颗粒。

[0089] 应强调,上文所述的实施例仅仅是为便于清晰理解本发明原理而阐述的实施方案的可能实例。可以在不实质偏离本发明精神和原理的前提下对上文所描述的实施例作出许多变化和修改。所有这些修改和变化在此希望被包括在本发明和本申请案的范围内。

[0090] 应注意,在本文中,比率、浓度、量以及其他数值数据可能通过范围形式来表达。应理解,此类范围形式的使用是为了方便和简捷,因此,应该以灵活方式来理解,它不仅包括所明确提到的作为范围界限的数值,而且还包括在该范围内所涵盖的所有单个数值或子范围,就像明确引用了每一数值和子范围一样。为便于说明,应将“约0.1%至约5%”的浓度范围理解为不仅包括约0.1wt%至约5wt%的明确引用的浓度,而且还包括所指示范围内的单个浓度(例如,1%、2%、3%以及4%)和子范围(例如,0.5%、1.1%、2.2%、3.3%以及4.4%)。术语“约”可以包括根据数值的有效数字进行传统四舍五入后的整数值。此外,词组“约‘x’至‘y’”包括“约‘x’至约‘y’”。

图1A

图1B

图1C

图2A

图2B

图3

图4

图5

图6

图7

图8

图9A

图9B

图10

图11

图12

图13

图14A

图14B

图15

图16

图17

图18

图19

图20

图21

图22

图23

图24

图25

图26