(19) 日本国特許庁(JP)

(12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-503029

(P2008-503029A)

(43) 公表日 平成20年1月31日(2008.1.31)

(51) Int.Cl.

G 1 1 C 11/41 (2006.01)

G 1 1 C 11/417 (2006.01)

F |

G 1 1 C 11/34

5

### テーマコード（参考）

5 B 0 1 5

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2007-527283 (P2007-527283) |

| (86) (22) 出願日 | 平成17年5月5日 (2005. 5. 5)       |

| (85) 翻訳文提出日   | 平成18年12月25日 (2006. 12. 25)   |

| (86) 國際出願番号   | PCT/US2005/015858            |

| (87) 國際公開番号   | W02006/001910                |

| (87) 國際公開日    | 平成18年1月5日 (2006. 1. 5)       |

| (31) 優先権主張番号  | 10/865, 274                  |

| (32) 優先日      | 平成16年6月10日 (2004. 6. 10)     |

| (33) 優先権主張國   | 米国 (US)                      |

(71) 出願人 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 健

(72) 発明者 ラマラジュ、ラビンドララジ

アメリカ合衆国 78681 テキサス州

ラウンド ロック エバンス ドライブ

7014

最終頁に続く

(54) 【発明の名称】データ保持ラッチを含むメモリ素子

(57) 【要約】

複数の対の相補ビット線（200, 202）および複数のラッチ回路を含むメモリ素子。複数の対の相補ビット線の各対はメモリ・セル（31, 37）の列と結合している。各ラッチ回路は、データ線と結合している入力と、データ線の値により相補ラッチ値を供給するための第1の出力および第2の出力を含む。複数の各ラッチの場合、第1の出力は、第1のビット線の値が、メモリ素子の動作中、第1の出力により連続的に決まるように複数のうちの一対の第1のビット線と結合し、第2の出力は、第2のビット線の値が、メモリ素子の動作中、第2の出力により連続的に決まるように一対の第2のビット線と結合している。

**【特許請求の範囲】****【請求項 1】**

メモリ素子であって、

ビット線と、

同ビット線と結合しているメモリ・セルの列と、

データ線と結合している入力および同データ線の値によりラッチされた値を供給する出力を有するラッチ回路と、を備え、

前記出力は前記ビット線と結合して、メモリ素子の動作中、前記ビット線の値が前記出力により連続的に決まる、メモリ素子。

**【請求項 2】**

前記ビット線が書き込みビット線である請求項 1 に記載のメモリ素子。

**【請求項 3】**

読み出しビット線をさらに備え、前記メモリ・セルの列が前記読み出しビット線と結合している請求項 2 に記載のメモリ素子。

**【請求項 4】**

第 2 のビット線をさらに備え、同第 2 のビット線が前記ビット線に対する相補ビット線であり、前記メモリ・セルの列が前記第 2 のビット線と結合している請求項 1 に記載のメモリ素子。

**【請求項 5】**

前記ラッチ回路が第 2 の出力を含み、メモリ素子の動作中、同第 2 の出力が前記第 2 のビット線と結合して、同第 2 のビット線の値が前記第 2 の出力により連続的に決まる、請求項 4 に記載のメモリ素子。

**【請求項 6】**

前記ラッチ回路が、一対のクロス結合しているインバータを含み、

前記ラッチ回路の出力が、前記一対のインバータの第 1 のインバータの入力および前記一対のインバータの第 2 のインバータの出力と結合している請求項 1 に記載のメモリ素子。

**【請求項 7】**

前記ラッチ回路が第 3 のインバータを含み、同第 3 のインバータは前記ラッチ回路の出力と接続している出力と、前記一対のインバータの第 1 のインバータの入力および前記一対のインバータの第 2 のインバータの出力と接続している入力と、を有する請求項 6 に記載のメモリ素子。

**【請求項 8】**

前記ラッチ回路が、クロック信号を受信するための第 2 の入力を含み、前記ラッチ回路の出力でのラッチ値が、前記クロック信号の状態の変化により決まる時点のデータ線の値により値を変化する請求項 1 に記載のメモリ素子。

**【請求項 9】**

前記ビット線の値が、前記クロック信号の状態の変化により決まる時点のデータ線上の値に応じてだけ変化する請求項 8 に記載のメモリ素子。

**【請求項 10】**

メモリ・セルに書き込み信号を送るために、前記メモリ・セルの列のメモリ・セルと結合しているワード線と、

前記書き込み信号を供給するために前記ワード線と結合している出力を有し、クロック信号を受信するための入力を含むワード線生成回路とをさらに備え、前記書き込み信号が、前記ワード線生成回路の前記入力のところで受信する前記クロック信号の状態の変化により決まる時点で状態を変化させ、

前記ワード線生成回路が受信するクロック信号および前記ラッチの第 2 の入力のところで受信するクロック信号が、共通のクロック信号により生成される請求項 8 に記載のメモリ素子。

**【請求項 11】**

10

20

30

40

50

前記ラッチ回路の出力のところの値が、第1の状態から第2の状態への共通のクロック信号の状態の変化により決まる時点のデータ線の値により値を変化させ、

前記書き込み信号が、前記第1の状態から前記第2の状態への共通のクロック信号の状態の変化により決まる時点で非書き込み状態から書き込み状態に変化する請求項10に記載のメモリ素子。

**【請求項12】**

前記書き込み信号が、前記第2の状態から前記第1の状態への共通のクロック信号の状態の変化により決まる時点で書き込み状態から非書き込み状態に変化する請求項11に記載のメモリ素子。

**【請求項13】**

第2のビット線と、

前記第2のビット線と結合しているメモリ・セルの第2の列と、

第2のデータ線と結合している第2の入力と、前記第2のデータ線の値によりラッチされた値を供給する第2の出力とを有する第2のラッチ回路とをさらに備え、

前記第2のラッチ回路の第2の出力が前記第2のビット線と結合して、メモリ素子の動作中に、前記第2のビット線の値が前記第2の出力により連続的に決まる請求項1に記載のメモリ素子。

**【請求項14】**

前記メモリ・セルの列が、前記メモリ・セルの第2の列のメモリ・セルと同じ行に位置するメモリ・セルを含む請求項13に記載のメモリ素子。

**【請求項15】**

前記ビット線の値が、前記データ線の値に応じてだけ変化する請求項1に記載のメモリ素子。

**【請求項16】**

前記メモリ素子が、多ポート・レジスタ・ファイルとしての特徴を有する請求項1に記載のメモリ素子。

**【請求項17】**

前記ビット線の値が、前記列のメモリ・セルへのすべてのメモリ読み出しを含む、メモリ素子の動作中の出力により連続的に決まるように、前記出力が前記ビット線と結合している請求項1に記載のメモリ素子。

**【請求項18】**

前記集積回路がプロセッサ・コアをさらに含む請求項1に記載のメモリ素子を含む集積回路。

**【請求項19】**

前記メモリ・セルの列のメモリ・セルへの読み出しあり書き込みが、メモリ素子の動作中に行われる請求項1に記載のメモリ素子。

**【請求項20】**

メモリ・セルの列のメモリ・セルへの複数の読み出しあり複数の書き込みを行うステップを含むメモリ素子を動作させるステップと、

前記動作中、ラッチ出力により、前記メモリ・セルの列と結合しているビット線の値を連続的に制御するステップと、を含むメモリ素子を動作するための方法。

**【請求項21】**

第1の状態から第2の状態へのクロック信号の状態の変化により決まる時点で、ラッチ入力の値に応じて前記ラッチ出力の値を変化させるステップをさらに含む請求項20に記載の方法。

**【請求項22】**

前記メモリ・セルの列のメモリ・セルにある値を書き込むステップをさらに含み、該書き込みステップが前記ビット線の状態を変化させるステップを含む請求項20に記載の方法。

**【請求項23】**

10

20

30

40

50

前記書き込みステップが、前記メモリ・セルと結合している書込み線の前記状態を、非書き込み状態から書き込み状態へ変化させるステップを含む請求項 2 2 に記載の方法。

**【請求項 2 4】**

前記ビット線の状態を変化させる前記ステップが、第 1 の状態から第 2 の状態へのクロック信号の状態の変化により決まる時点で、前記状態を変化させるステップを含み、

前記書き込み線の前記状態を変化させる前記ステップが、前記第 1 の状態から前記第 2 の状態へのクロック信号の状態の変化により決まる時点で、前記状態を変化させるステップをさらに含む請求項 2 3 に記載の方法。

**【請求項 2 5】**

前記書き込みステップが、前記第 2 の状態から前記第 1 の状態へのクロック信号の状態の変化により決まる時点で、前記書き込み線の状態を前記書き込み状態から前記非書き込み状態に変化させるステップをさらに含む請求項 2 4 に記載の方法。 10

**【請求項 2 6】**

前記書き込みステップが、前記第 1 の状態から前記第 2 の状態へのクロック信号の状態の変化により決まる時点で、前記書き込み線の状態を前記書き込み状態から前記非書き込み状態に変化させるステップをさらに含む請求項 2 2 に記載の方法。

**【請求項 2 7】**

前記書き込みステップが、前記ビット線の状態を第 1 の状態から第 2 の状態に変化させるステップを含み、

前記書き込みステップの後で、前記メモリ・セルの列のメモリ・セルにもう 1 つの値を書き込むステップをさらに含み、もう 1 つの値を書き込む同ステップが、前記ビット線の状態を変化させるステップを含み、前記書き込みおよびもう 1 つの値の書き込みの状態の変化の間に前記列のメモリ・セルへ他の書き込みが行われず、 20

前記ビット線が、前記書き込みの状態の変化の時点からもう 1 つの値の書き込みの状態の変化まで、前記第 2 の状態のままである請求項 2 2 に記載の方法。

**【請求項 2 8】**

前記書き込みステップの後であって、前記もう 1 つの値の書き込みステップの前に前記列のメモリ・セルの値を読み出すステップをさらに含み、前記ビット線が、読み出し中の前記メモリ・セルの値が何である、前記第 2 の状態を維持する請求項 2 7 に記載の方法。 30

**【請求項 2 9】**

動作中、前記ラッチ出力により前記メモリ・セルの列と結合している第 2 のビット線の値を連続的に制御するステップをさらに含み、前記第 2 のビット線が前記ビット線に対する相補ビット線である請求項 2 0 に記載の方法。

**【請求項 3 0】**

前記メモリ素子を動作する前記ステップが、メモリ・セルの第 2 の列のメモリ・セルへの複数の読み出しおよび複数の書き込みを行うステップをさらに含み、

動作中、第 2 のラッチ出力によりメモリ・セルの第 2 の列と結合している第 2 のビット線の値を連続的に制御するステップをさらに含む請求項 2 0 に記載の方法。

**【請求項 3 1】**

メモリ素子であって、

ビット線と、

前記ビット線と結合しているメモリ・セルの列と、

データ線と結合している入力と、前記データ線の値によりラッチされた値を供給する出力とを有するラッチ回路とを備え、前記出力が前記ビット線に接続しているメモリ素子。 40

**【請求項 3 2】**

第 2 のビット線と、

前記第 2 のビット線と結合しているメモリ・セルの第 2 の列と、

第 2 のデータ線と結合している第 2 の入力と、前記第 2 のデータ線の値によりラッチされた値を供給する第 2 の出力とを有する第 2 のラッチ回路とをさらに備え、前記第 2 の出力が、前記第 2 のビット線に接続している請求項 3 1 に記載のメモリ素子。 50

**【請求項 3 3】**

メモリ素子であって、

複数の対の相補ビット線であって、各対がメモリ・セルの列と結合している複数の対の相補ビット線と、

複数のラッチ回路であって、各ラッチ回路がデータ線と結合している入力と、前記データ線の値により相補ラッチ値を供給するための第1の出力および第2の出力とを含む複数のラッチ回路とを備え、

前記複数の各ラッチに対して、前記第1の出力が、前記第1のビット線の値が、メモリ素子の動作中、前記第1の出力により連続的に決まるように前記複数の対の一対の第1のビット線と結合し、前記第2の出力が、前記第2のビット線の値が、メモリ素子の動作中、前記第2の出力により連続的に決まるように前記対の第2のビット線と結合しているメモリ素子。

**【請求項 3 4】**

メモリ素子であって、

ビット線と、

前記ビット線と結合しているメモリ・セルの列と、

データ線と結合している入力と、前記データ線の値によりラッチされた値を供給する出力とを有するラッチ回路とを備え、前記出力が、メモリ素子の動作中、前記出力のところの値が変化した場合だけ、前記ビット線の前記値が変化するように前記ビット線と結合しているメモリ素子。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、集積回路に関し、特にメモリ素子に関する。

**【背景技術】****【0 0 0 2】**

多ポート・メモリ素子の場合には、メモリ読み出し動作およびメモリ書き込み動作は、このような動作を行うために必要な時間の長さにより重大な影響を受ける。書き込み動作中、入力データ・アサート時間は、メモリ素子の属性に関連する復号遅延により異なる場合がある。例えば、アサート時間が不十分な場合には、入力データの依存性に関連する不確実性により、メモリ内に書き込み中の偽値データによりプロセッサが障害を起こす場合がある。

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 3】**

それ故、メモリの性能を改善するメモリ設計が求められている。

**【課題を解決するための手段】****【0 0 0 4】**

以下に本発明について説明するが、これは例示としてのものであって、本発明は添付の図面に限定されない。図面中、類似の参照番号は類似の要素を示す。

当業者であれば、図面中の要素は、簡単に明確に表示するためのものであって、必ずしも正確な縮尺でないことを理解することができるだろう。例えば、本発明の実施形態を容易に理解できるように、図面中の要素のうちのあるものの寸法は他の要素より誇張してある。

**【発明を実施するための最良の形態】****【0 0 0 5】**

一実施形態の場合には、メモリ素子は、ビット線と、メモリ・セルの列と、ラッチ回路とを含む。メモリ・セルの列はビット線と結合している。ラッチ回路は、データ線と結合している入力と、データ線の値によりラッチした値を供給する出力とを有する。出力は、ビット線の値が、メモリ素子の動作中出力により連続的に決まるようにビット線と結合し

10

20

30

40

50

ている。

**【0006】**

一実施形態は、メモリ素子を動作するための方法に関する。メモリ・セルの列のメモリ・セルに対して、複数の読み出しあり複数の書き込みが行われる。ビット線の値はメモリ・セルの列と結合していて、ビット線の値は、メモリ素子の動作中、ラッチ出力により連続的に制御される。一実施形態の場合には、ラッチ出力の値は、第1の状態から第2の状態へのクロック信号の状態の変化により決まる時点で、ラッチ入力の値に応じて変化することができる。一実施形態の場合には、値はメモリ・セルの列のメモリ・セルに書き込むことができる。この場合、書き込みは、例えば、ビット線の状態の変化を含む。一実施形態の場合には、値をメモリ・セルの列のメモリ・セルに書き込むことができる。この場合、書き込みは、例えば、非書き込み状態から書き込み状態への書き込み線の状態の変化を含む。

10

**【0007】**

一実施形態の場合には、メモリ素子は、ビット線と、メモリ・セルの列と、ラッチ回路とを含む。メモリ・セルの列はビット線と結合している。ラッチ回路は、データ線と結合している入力と、データ線の値によりラッチした値を供給するための出力とを有する。出力は、ビット線に接続している。

**【0008】**

一実施形態の場合には、メモリ素子は、複数の対の相補ビット線と、複数のラッチ回路とを含む。複数の対の相補ビット線の各対は、メモリ・セルの列と結合している。各ラッチ回路は、データ線と結合している入力と、データ線の値により相補ラッチ値を供給するための第1の出力および第2の出力とを有する。複数のラッチ回路の各ラッチの場合、第1の出力は、第1のビット線の値が、メモリ素子の動作中、第1の出力により連続的に決まるように複数の対の第1のビット線と結合していて、第2の出力は、第2のビット線の値が、メモリ素子の動作中、第2の出力により連続的に決まるように対の第2のビット線と結合している。

20

**【0009】**

一実施形態の場合には、メモリ素子は、ビット線と、メモリ・セルの列と、ラッチ回路とを含む。メモリ・セルの列はビット線と結合している。ラッチ回路は、データ線と結合している入力と、データ線の値によりラッチした値を供給するための出力とを有する。出力は、メモリ素子の動作中、出力のところの値が変化した場合だけ、ビット線の値が変化するようにビット線と結合している。

30

**【0010】**

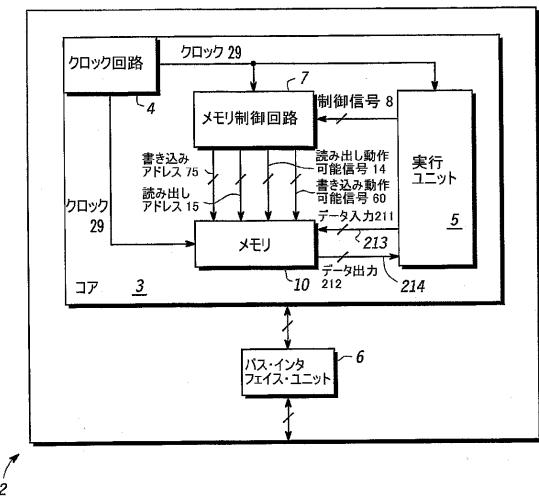

図1は、本発明の一実施形態による集積回路2である。集積回路2は、コア3と、バス・インターフェース・ユニット(BIU)6とを含む。コア3は、クロック回路4と、実行ユニット5と、メモリ制御装置7と、メモリ10とを含む。一実施形態の場合には、コア3は、例えば、プロセッサ・コアであってもよいし、メモリ10は、例えば、多ポート・レジスタ・ファイルにより特徴づけることができる。

**【0011】**

一実施形態の場合には、集積回路2の正常な動作中、メモリ10に対して、実行ユニット5からメモリ制御装置7に供給される制御信号8に基づいて、書き込みアクセスまたは読み出しアクセスが行われる。制御信号8は、メモリ読み出し動作またはメモリ書き込み動作をスタートするために使用することができる。実行ユニット5は、例えば、メモリ10内にデータを格納し、メモリ10からデータを読み出すために、制御信号8を発行する中央処理装置(CPU)であっても、またはデジタル信号処理装置であってもよい。一実施形態の場合には、メモリ10にいつデータを書き込むことができるか、またはメモリ10からいつデータを読み出すことができるかを決定するためのタイミング機構として使用されているクロック信号29(CLK29)は、クロック回路4からメモリ制御装置7、実行ユニット5およびメモリ10に供給される。メモリ制御装置7は、実行ユニット5からクロック信号29および制御信号8を受信し、実行ユニット5により読み出し動作が要

40

50

求されたのかまたは書き込み動作が要求されたのかに基づいて、書き込み動作可能信号 60 (WR EN60) または読み出し動作可能信号 14 (READ EN14) をアサートする。

#### 【0012】

読み出し動作中、RD ADDRESS15 および READ EN14 が、メモリ制御装置 7 からメモリ 10 に供給される。メモリ 10 は、READ EN14 を受信し、RD ADDRESS15 が指定するメモリ・アドレス位置を動作可能にする。RD ADDRESS15 が指定するメモリ・アドレス位置内のデータはメモリ 10 から読み出され、データ線 214 を介して DATA-OUT212 として実行ユニット 5 に供給される。

#### 【0013】

書き込み動作中、WR ADDRESS75 および WR EN60 はメモリ制御装置 7 からメモリ 10 に供給される。メモリ 10 は、WR EN60 を受信し、書き込み動作に対する WR ADDRESS75 が指定するメモリ 10 内のメモリ・アドレス位置を動作可能にする。実行ユニット 5 からのデータ (DATA-IN211) は、データ線 213 を介してメモリ 10 に供給され、WR ADDRESS75 が指定するメモリ 10 のメモリ・アドレス位置に書き込まれる。集積回路 2 は、他の実施形態の場合には他の構成を有することができる。

#### 【0014】

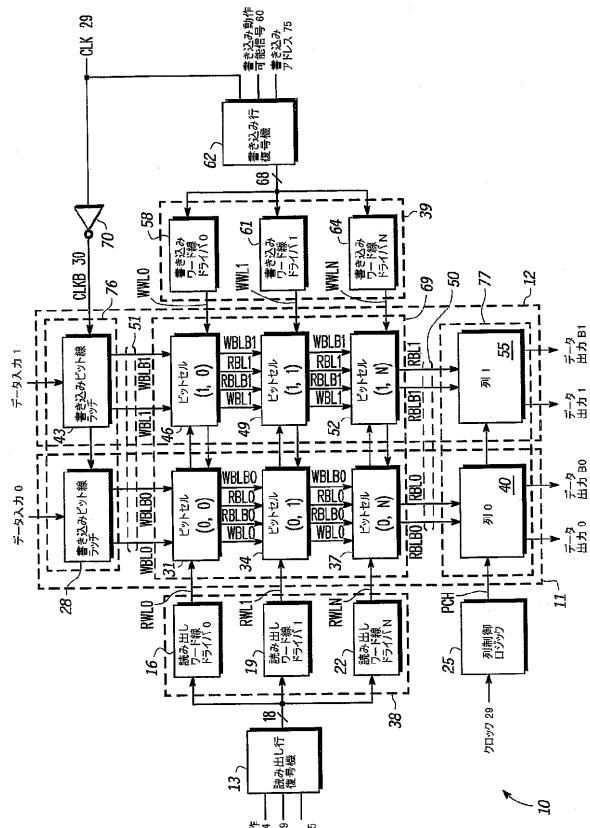

図 2 は、本発明の一実施形態によるメモリ 10 である。メモリ 10 は、読み出し行デコーダ 13 と、読み出しワード線ドライバ 38 と、書き込みワード線ドライバ 39 と、書き込みビット線ラッチ 76 と、列制御ロジック 25 と、列アレイ回路 11 と、列アレイ回路 12 と、インバータ 70 と、書き込み行デコーダ 62 と、列回路 77 を含む。読み出しワード線ドライバ 38 は、読み出しワード線ドライバ 16 と、読み出しワード線ドライバ 19 と、読み出しワード線ドライバ 22 を含む。書き込みワード線ドライバ 39 は、書き込みワード線ドライバ 58 と、書き込みワード線ドライバ 61 と、書き込みワード線ドライバ 64 を含む。列アレイ回路 11 は、書き込みビット線ラッチ 28 と、ビットセル (メモリ・セル) 31 と、ビットセル 34 と、ビットセル 37 と、列回路 40 を含む。列アレイ回路 12 は、書き込みビット線ラッチ 43 と、ビットセル 46 と、ビットセル 49 と、ビットセル 52 と、列回路 55 を含む。説明を分かり易くするために、ビットセル 46、ビットセル 49、ビットセル 52、ビットセル 31、ビットセル 34 およびビットセル 37 をビットセル・アレイ 69 と呼ぶことにし、書き込みワード線ドライバ 39 および書き込み行デコーダ 62 をワード線発生回路と呼ぶことにする。図の実施形態の場合には、ビットセル 31 はビットセル 46 と同じ行に位置する。

#### 【0015】

一実施形態の場合には、読み出し動作中、メモリ 10 の読み出し行デコーダ 13 は、メモリ制御装置 7 (図 1) から読み出し動作可能信号 14 および読み出しアドレス 15 を受信し、クロック回路 4 (図 1) からクロック信号 29 を受信する。読み出し行デコーダ 13 は、読み出しアドレス 15 を復号し、読み出しアクセスができるようにビットセル・アレイ 69 のビット・セルの行を決定する。ビットセル・アレイ 69 は、ビット・セルの 1 つまたは複数の行または列を含むことができる。読み出し行デコーダ 13 は、行動作可能信号 18 を復号した行アドレスに対応する読み出しワード線ドライバ 38 のうちの少なくとも 1 つに出力する。復号した行アドレスに対応する読み出しワード線ドライバ 38 の読み出しワード線ドライバは、ビット・セルの選択した 1 つまたは複数の行に供給される読み出しワード線信号をアサートする。図の実施形態の場合には、読み出しワード線ドライバ 16、読み出しワード線ドライバ 19、または読み出しワード線ドライバ 22 が、読み出しワード線信号 RWL0、RWL1、RWLN のいずれかをそれぞれアサートする。ビット・セルの選択した行は、読み出しビット線信号 (RBL0 および RBLB0) を列回路 40 への入力として供給し、読み出しビット線信号 (RBL1 および RBLB1) を列回路 55 への入力として供給する。ビット・セル・アレイ 69 が複数の行のビット・セルを有している場合には、読み出しビット線信号 RBL0 および RBLB0 および読み出し

10

20

30

40

50

ビット線信号RBL1およびRBLB1を列回路40および列回路55に入力として供給する前に、ビット・セルの1つまたは複数の追加行に供給することができる。同様に、ビット・セル・アレイ69がビット・セルの複数の列を有している場合に、読み出しワード線信号RWL0、RWL1およびRWLNをビット・セルの1つまたは複数の追加列に供給することができる。

#### 【0016】

列回路40および列回路55は、それぞれ読み出しビット線信号RBL0およびRBLB0および読み出しビット線信号RBL1およびRBLB1を受信する。列回路40は、出力データ(DATA-OUT0およびDATA-OUTB0)を生成するために、読み出し線ビット信号RBL0およびRBLB0を使用し、列回路55は、出力データ(DATA-OUT1およびDATA-OUTB1)を生成するために、読み出しビット線信号を使用する。次に、出力データは、さらに処理を行うために図1の実行ユニット5のような実行ユニットに供給することができる。メモリ10の他の実施形態は、図2に示すものに限定されない1つの列アレイ回路11または複数の列アレイ回路を含むことができることに留意されたい。

10

#### 【0017】

一実施形態の場合には、書き込み動作中、書き込み行デコーダ62は、書き込み動作可能信号60、クロック信号29および書き込みアドレス75を受信する。書き込み行デコーダ62は書き込みアドレス75を復号し、ビット・セルのどの行を書き込みアクセスのために動作可能にするのかを決定する。書き込み行デコーダ62は、行動作可能信号68を復号した行アドレスに対応する書き込みワード線ドライバ39のうちの少なくとも1つに出力する。復号した行アドレスに対応する書き込みワード線ドライバ39の書き込みワード線ドライバは、ビット・セルの選択した1つまたは複数の行に供給される書き込みワード線信号をアサートする。図の実施形態の場合には、書き込みワード線ドライバ58、書き込みワード線ドライバ61、および書き込みワード線ドライバ64が、書き込みワード線ドライバ39をビットセル・アレイ69に結合する書き込みワード線を介して、書き込みワード線信号WWL0、WWL1およびWWLNのいずれかをそれぞれアサートする。一実施形態の場合には、書き込みワード線信号は、例えば、クロック信号29の状態の変化により決まる時点で、非書き込み状態から書き込み状態に変化することができる。例えば、実行ユニット5(図示せず)から供給することができる入力データ(DATA-IN0およびDATA-IN1)は、書き込みビット線ラッチ76(書き込みビット線ラッチ28および書き込みビット線ラッチ43)に転送される。書き込みビット線ラッチ76は、入力データおよびインバータ70により反転される反転クロック信号29(CLK\_B30)を受信する。書き込みビット線ラッチ76は、入力データを書き込みビット線信号WBL0、WBL1として、および書き込みビット線信号WBLB0、WBLBの補足を、書き込みビット線ラッチ76をビットセル・アレイ69と結合する書き込みビット線上に駆動するためにCLK\_B30を使用する。次に、書き込みビット線信号が、ビットセル・アレイ69のビットセルの選択した行上に書き込まれる。ビット・セル・アレイ69がビット・セルの複数の行を有している場合には、書き込みビット線信号WBL0およびWBLB0および書き込みビット線信号WBL1およびWBLB1を、ビット・セルの1つまたは複数の追加行に供給することができる。同様に、ビット・セル・アレイ69がビット・セルの複数の列を有している場合には、書き込みワード線信号WWL0、WWL1およびWWLNをビット・セルの1つまたは複数の追加列に供給することができる。メモリ10は、他の実施形態の場合には他の構成を有することができる。

20

30

40

#### 【0018】

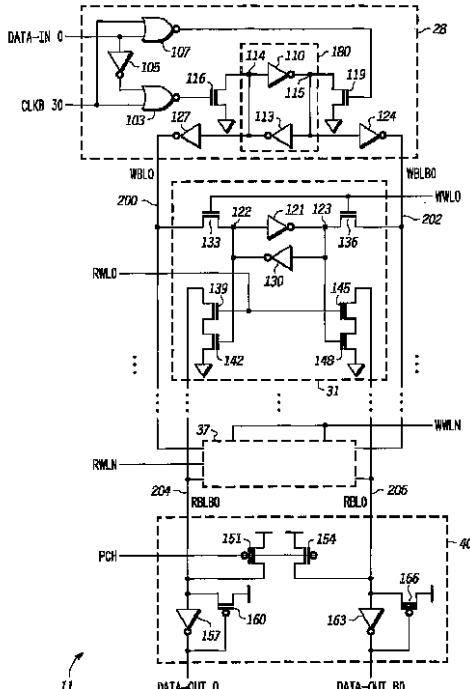

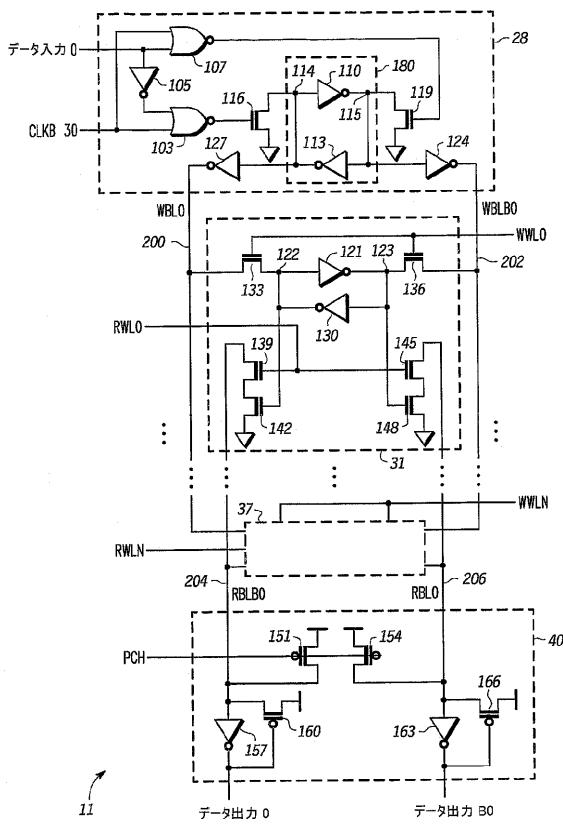

図3は、列アレイ回路11の一実施形態である。図に示すように、列アレイ回路11は、書き込みビット線ラッチ28と、ビットセル31と、ビットセル37と、列回路40とを含む。書き込みビット線ラッチ28は、書き込みビット線200および書き込みビット線202を介してビットセル31およびビットセル37と結合している。一実施形態の場合には、書き込みビット線202は、書き込みビット線200の相補ビット線である。ビ

50

ットセル31およびビットセル37は、読み出しビット線204および読み出しビット線206を介して列回路40と結合している。他の実施形態の場合には、追加のビット・セルを列アレイ回路11に追加することができる。ビットセル34は図3には図示していない。

#### 【0019】

書き込み動作中、列アレイ回路11の書き込みビット線ラッチ28は、インバータ70(図2)からクロックバー信号30(CLK\_B30)を、実行ユニット5(図1)から入力データ(DATA-IN0)を受信する。NORゲート107は、DATA-IN0およびクロックバー信号30を否定論理和(NOR)し、その出力をNMOSトランジスタ119に供給する。NORゲート103は、クロックバー信号30および入力データDATA-IN0の逆数を否定論理和し、その出力をNMOSトランジスタ116に供給する。

10

#### 【0020】

通常、DATA-IN0およびクロックバー信号30は、アサート値または非アサート値をとることができる。一実施形態の場合には、クロックバー信号30が高レベルの場合には、NORゲート107の出力およびNORゲート103の出力は低レベルである。その結果、NMOSトランジスタ119およびNMOSトランジスタ116はオフになり、インバータ113とクロス結合しているインバータ110を含むラッチ180は、もしあった場合には、ラッチ180に前に書き込んだデータ値を能動的に保持する。

#### 【0021】

一実施形態の場合には、クロックバー信号30が低レベルであり、DATA-IN0が高レベルである場合には、NORゲート107の出力は低レベルであり、NORゲート103の出力は高レベルである。その結果、NMOSトランジスタ119はオフになり、NMOSトランジスタ116はオンになり、ノード114は低レベルであり、インバータ110の出力は高レベルである。インバータ110の出力は、インバータ113およびインバータ124により反転される。インバータ113は、インバータ110の出力を反転し、その出力をインバータ127に供給する。書き込みビット線信号WBL0としての書き込みビット線200上で転移するインバータ127の出力は高レベルである。書き込みビット線バー信号WBLB0としての書き込みビット線202上で転移するインバータ124の出力は低レベルである。両方の書き込みビット線信号WBL0および書き込みビット線バー信号WBLB0はビットセル31に供給される。

20

#### 【0022】

一実施形態の場合には、クロックバー信号30が低レベルであり、DATA-IN0が低レベルである場合には、NORゲート107の出力は高レベルであり、NORゲート103の出力は低レベルである。その結果、NMOSトランジスタ119がオンになり、NMOSトランジスタ116がオフになる。NMOSトランジスタ119がオンになるので、ノード115が低レベルになり、インバータ113の出力は高レベルになる。書き込みビット線バー信号WBLB0として書き込みビット線202上で転移するインバータ124の出力は高レベルであり、書き込みビット線バー信号WBL0として書き込みビット線204に転移するインバータ127の出力は低レベルである。それ故、書き込みビット線ラッチ28の出力のところの書き込みビット線信号WBL0および書き込みビット線バー信号WBLB0の値は、クロックバー信号30の状態の変化により決まる時点での入力データ線のところのDATA-IN0の値による値をえる。同様に、書き込みビット線200および書き込みビット線202の書き込みビット線信号WBL0および書き込みビット線バー信号WBLB0の値は、クロック信号の状態の変化により決まる時点での入力データ線上のDATA-IN0の値に応じて変化することができる。書き込みビット線信号WBL0および書き込みビット線バー信号WBLB0は、ビットセル31に供給される。

30

#### 【0023】

ビットセル31は、NMOSトランジスタ133の電流端子のところでインバータ127の出力から書き込みビット信号WBL0を受信し、NMOSトランジスタ136の電流

端子のところでインバータ 124 の出力から書き込みビット線バー - 信号 WBLB0 を受信する。NMOSトランジスタ 133 および NMOSトランジスタ 136 の制御端子に供給される書き込みワード線信号 WWL0 が高レベルである場合には、NMOSトランジスタ 133 および NMOSトランジスタ 136 がオンになる。ノード 122 は書き込みビット線 200 に転移された値になり、ノード 123 は、書き込みビット線 202 に転移された値になる。それ故、WWL0 が高レベルである場合には、ビットセル 31 は、列アレイ回路 11 内へ入力として供給される入力データ DATA-IN0 を格納する。WWL0 が低レベルである場合には、NMOSトランジスタ 133 および NMOSトランジスタ 136 がオフなり、書き込みビット線 200 および書き込みビット線 202 から書き込まれたデータ値が、インバータ 121 およびインバータ 130 により格納される。

10

#### 【0024】

読み出し動作中、読み出しワード線 208 上の読み出しワード線信号 RWL0 が高レベルである場合には、NMOSトランジスタ 139 および NMOSトランジスタ 145 がオンになる。ノード 122 のところに格納している値の逆数およびノード 123 のところに格納している値の逆数が、それぞれ NMOSトランジスタ 142 および NMOSトランジスタ 148 により、読み出しビット線バー信号 RBLB0 として読み出しビット線 204 に転送され、読み出しビット線信号 RBL0 として読み出しビット線 206 に転送される。列回路 40 へ入力として供給される予備充電信号 (PCH) が高レベルである場合には、PMOSトランジスタ 151 および PMOSトランジスタ 154 がオフになり、読み出しビット線 204 上の読み出しビット線信号 RBLB0 の値がインバータ 157 に供給され、読み出しビット線 206 上の読み出しビット線信号 RBL0 の値がインバータ 163 に供給される。インバータ 157 の出力は、出力データ DATA-OUT0 として実行ユニット (図示せず) および PMOSトランジスタ 160 の制御端子に供給される。同様に、インバータ 163 の出力は、出力データ (DATA-OUTB0) として実行ユニット (図示せず) および PMOSトランジスタ 166 の制御端子に供給される。読み出しビット線信号 RBL0 および 読み出しビット線信号 RBLB0 の値により、PMOSトランジスタ 160 または PMOSトランジスタ 166 をオフにすることができる。他の実施形態の場合には、書き込みビット線ラッチ 28、ビットセル 31、ビットセル 37、および / または列回路 40 は、他の構成を有することができる。図の実施形態の場合には、DATA-IN0 信号は、シングル・エンド信号であるが、他の実施形態の場合には、この信号は差動信号のような他の形の信号であってもよい。

20

30

40

#### 【0025】

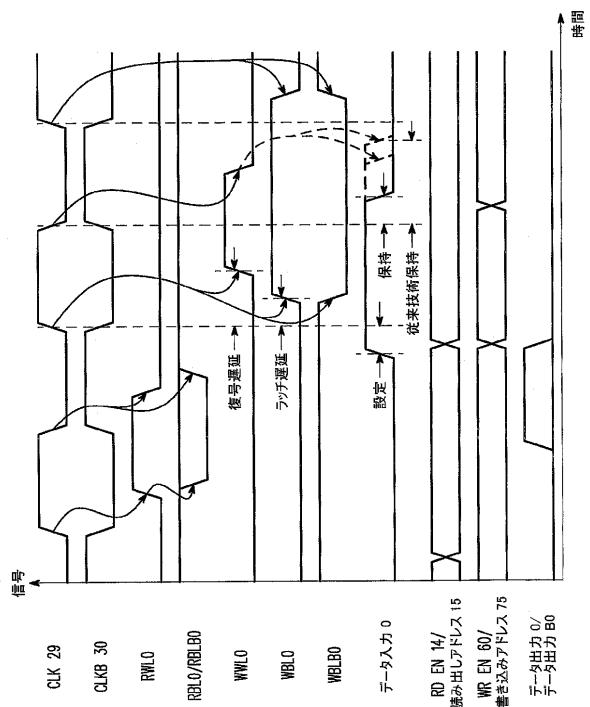

図 4 は、本発明の一実施形態によるビットセル 31 に対して読み出しおよび書き込みを行うための種々の信号を示すタイミング図である。一実施形態に示すように、読み出し動作中、読み出し動作可能信号 14 およびクロック信号 29 が高レベルである場合には、読み出しワード線信号 RWL0 は高レベルである。読み出しワード線信号 RWL0 は、例えば、読み出し行デコーダ 13 および読み出しワード線ドライバ 38 により遅延が生じた場合には、高レベルであるとアサートすることができる。読み出しワード線信号 RWL0 が高レベルになると、読み出しビット線信号 RBL0 が低レベルになり、読み出しビット線バー信号 RBLB0 が高レベルになるか、または読み出しビット線信号 RBL0 が高レベルになり、読み出しビット線バー信号 RBLB0 が低レベルになる。読み出しビット線信号 RBL0 または読み出しビット線バー信号 RBLB0 が低レベルになると、DATA-OUT0 または DATA-OUTB0 が高レベルになる。クロック信号 29 が低レベルである場合には、読み出しワード線信号 RWL0 が低レベルであり、読み出しビット線信号 RBL0 および読み出しビット線バー信号 RBLB0 が高レベルであり、DATA-OUT0 および DATA-OUTB0 が低レベルである。

#### 【0026】

図 4 に示すように、DATA-IN0 およびクロック信号 29 が高レベル (クロックバー信号 30 が低レベル) である場合には、書き込みビット線信号 WBL0 が高レベルであり、書き込みビット線バー信号 WBLB0 が低レベルである。書き込み動作中、書き込み

50

動作可能信号 60 およびクロック信号 29 が高レベルである場合には、書き込みワード線信号 W WL 0 は高レベルである。書き込みワード線信号 W WL 0 は、例えば、書き込み行デコーダ 62 および書き込みワード線ドライバ 39 により遅延が生じた場合には、高レベルであるとアサートすることができる。クロック信号 29 が低レベルである場合には、書き込みワード線信号 W WL 0 は低レベルになる。

#### 【0027】

図 4 のタイミング図を見れば分かるように、復号遅延は、書き込みワード線信号 W WL 0 のアサートへのクロック信号 29 のアサートに関連する。ラッチ遅延は、書き込みビット線信号 W BL 0 のアサートへのクロック信号 29 のアサートに関連する。一実施形態の場合には、書き込み動作中、書き込みビット線信号 W BL 0 は、書き込みワード線信号 W WL 0 が低レベルになるまで高い値に保持される。同様に、書き込みビット線バー信号 W BLB 0 は、書き込みワード線信号 W WL 0 が低レベルになるまで低い値に保持される。DATA-IN 0 は、クロック信号 29 が低レベルになるまで高レベルに保持される。図に示すように、DATA-IN 0 アサート時間は、書き込みワード線信号 W WL 0 に関連する復号遅延の影響を受けない。

10

#### 【0028】

今まで特定の実施形態を参照しながら本発明を説明してきたが、通常の当業者であれば、下記の特許請求の範囲に記載する本発明の範囲から逸脱することなしに種々の修正および変更を行うことができるこを理解することができるだろう。それ故、上記明細書および図面は本発明を制限するものではなく、例示としてのものと見なすべきであり、このようなすべての修正は本発明の範囲内に含まれる。

20

#### 【0029】

特定の実施形態を参照しながら種々の利益、種々の他の利点および問題の解決方法を説明してきたが、このような種々の利益、種々の他の利点、問題の解決方法および任意の利益、利点または問題の解決方法を実行し、より優れたものにすることができる任意の要素は、請求項のいずれかまたはすべての重要で、必要なまたは不可欠な機能または要素であると解釈すべきではない。

#### 【図面の簡単な説明】

#### 【0030】

【図 1】本発明の一実施形態による集積回路のブロック図。

30

【図 2】本発明の一実施形態によるメモリ。

【図 3】本発明の一実施形態による列アレイ回路。

【図 4】本発明の一実施形態による種々の信号を表すタイミング図。

【 図 1 】

【 図 2 】

【 义 3 】

【 四 4 】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | International application No.<br>PCT/US05/15858   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------|------------|------------------------------------------------------------------------------------|-----------------------|------|-----------------------------------------------------------------|----------------------|---|-------------------------------------------------------------------------|-------|---|-----------------------------------------|--|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC: E06C 7/10( 2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| USPC: 182/217<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 182/217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Please See Continuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category *</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="padding: 2px;">Y, P</td> <td style="padding: 2px;">US 6,859,400 B2 (ARAKAW) 22 February 2005, see entire document.</td> <td style="padding: 2px;">1-3,6,15-20-22,31,34</td> </tr> <tr> <td style="padding: 2px;">Y</td> <td style="padding: 2px;">US 6,470,467 B2 (TOMISHIMA et al) 22 October 2002, see entire document.</td> <td style="padding: 2px;">20-22</td> </tr> <tr> <td style="padding: 2px;">A</td> <td style="padding: 2px;">US 5,517,461 A (UNNO et al) 14 May 1996</td> <td style="padding: 2px;"></td> </tr> </tbody> </table> |                                                                                    |                                                   | Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | Y, P | US 6,859,400 B2 (ARAKAW) 22 February 2005, see entire document. | 1-3,6,15-20-22,31,34 | Y | US 6,470,467 B2 (TOMISHIMA et al) 22 October 2002, see entire document. | 20-22 | A | US 5,517,461 A (UNNO et al) 14 May 1996 |  |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                             |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Y, P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 6,859,400 B2 (ARAKAW) 22 February 2005, see entire document.                    | 1-3,6,15-20-22,31,34                              |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 6,470,467 B2 (TOMISHIMA et al) 22 October 2002, see entire document.            | 20-22                                             |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 5,517,461 A (UNNO et al) 14 May 1996                                            |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    | <input type="checkbox"/> See patent family annex. |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"B" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Date of the actual completion of the international search<br>26 June 2006 (26.06.2006)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Date of mailing of the international search report<br>13 JUL 2006                  |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (571) 273-3201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

| <br>Authorized officer<br>RANDOLPH A. REESE<br>Telephone No. 571-272-3600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                   |            |                                                                                    |                       |      |                                                                 |                      |   |                                                                         |       |   |                                         |  |

**INTERNATIONAL SEARCH REPORT**

|                                                 |

|-------------------------------------------------|

| International application No.<br>PCT/US05/15858 |

|-------------------------------------------------|

Continuation of B. FIELDS SEARCHED Item 3:

EPAB, JPAB, PGPB, USPT

write, cell, memory, bit line, latch, address\$, clock, signal, invertor, word, line, clock\$, row\$, data

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 フーケストラ、ジョージ ピー.

アメリカ合衆国 78750 テキサス州 オースティン フラワー セント コート 1170

5

(72)発明者 ケンケア、プラシャント ユー.

アメリカ合衆国 78736 テキサス州 オースティン コニファー コープ 6501

F ターム(参考) 5B015 HH01 HH03 JJ12 JJ16 KA09 KA38 KB08 KB35 NN01