(12)

## Offenlegungsschrift

(21) Aktenzeichen: **10 2015 114 371.2**

(22) Anmeldetag: 28.08.2015

(43) Offenlegungstag: 03.03.2016

(51) Int Cl.:

H03K 17/10 (2006.01)

H03K 17/567 (2006.01)

**H02M 1/08 (2006.01)**

---

### (30) Unionspriorität:

14/473.207

29.08.2014 US

(74) Vertreter:

Westphal, Mussgnug & Partner Patentanwälte mit

beschränkter Berufshaftung, 80331 München, DE

(71) Anmelder:

Infineon Technologies Austria AG, Villach, AT

(72) Erfinder:

Zojer, Bernhard, Villach, AT

Prüfungsantrag gemäß § 44 PatG ist gestellt.

**Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen**

(54) Bezeichnung: SYSTEM UND VERFAHREN FÜR EINEN SCHALTER MIT EINEM SELBSTLEITENDEN TRANSISTOR UND EINEM SELBSTSPERRENDEN TRANSISTOR

(57) Zusammenfassung: Gemäß einem Ausführungsbeispiel weist eine Schaltung einen ersten Treiber auf, der einen ersten Ausgang aufweist, der zum Koppeln mit einem Steuernoden eines selbstsperrenden Transistors gekoppelt ist. Der erste Treiber ist zum Betreiben eines ersten Schaltsignals am ersten Ausgang in einem Kaskodenmodus und zum Betreiben einer ersten konstanten Spannung am ersten Ausgang in einem Direktansteuermodus konfiguriert. Die Schaltung weist ferner einen zweiten Treiber auf, der einen zweiten Ausgang aufweist, der zum Koppeln mit einem Steuernoden eines selbstleitenden Transistors konfiguriert ist, der einen zweiten Laststreckenanschluss aufweist, der mit einem ersten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist. Der zweite Treiber ist zum Betreiben eines zweiten Schaltsignals am zweiten Ausgang im Direktansteuermodus konfiguriert.

**Beschreibung**

**[0001]** Die vorliegende Erfindung betrifft allgemein eine elektronische Vorrichtung und insbesondere ein System und ein Verfahren für einen Schalter, der einen selbstleitenden Transistor und einen selbstsperrenden Transistor aufweist.

**[0002]** Leistungsversorgungssysteme sind in vielen elektronischen Anwendungen von Computern und Automobilen weit verbreitet. Allgemein werden Spannungen in einem Leistungsversorgungssystem durch Durchführen einer DC-DC-, DC-AC- und/oder AC-DC-Wandlung durch Betreiben eines Schalters durchgeführt der mit einer Spule oder einem Transformator belastet ist. Eine Klasse solcher Systeme schließt getaktete Leistungsversorgungen (Switched Mode Power Supplies, SMPS) ein. Ein SMPS ist normalerweise effizienter als andere Arten von Leistungswandlungssystemen, da eine Leistungswandlung durch gesteuertes Laden und Entladen der Spule oder Transformators erfolgt und die Energie reduziert, die aufgrund der Verlustleistung aufgrund eines inneren Spannungsabfalls verloren geht.

**[0003]** Spezifische Topologien für SMPS umfassen u. a. Hochsetz-Tiefsetz-Wandler und Sperrwandler. Ein Hochsetz-Tiefsetz-Wandler verwendet typischerweise eine Spule, während ein Sperrwandler eine Last isoliert und das Spannungsumrichtverhältnis durch die Verwendung eines Transformators vervielfachen kann. Zusätzlich zu dem Energiespeicher- element (entweder Spule oder Transformator) kann der Betrieb des Schalters von besonderer Wichtigkeit sein, insbesondere bei Hochspannungsanwendungen.

**[0004]** Gemäß einem Ausführungsbeispiel weist eine Schaltung einen ersten Treiber auf, der einen ersten Ausgang aufweist, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstsperrenden Transistors gekoppelt zu werden. Der erste Treiber ist dazu ausgebildet, in einem Kaskodemodus am ersten Ausgang ein erstes Schaltsignal auszugeben und in einem Direktansteuermodus eine erste konstante Spannung am ersten Ausgang auszugeben. Die Schaltung weist ferner einen zweiten Treiber auf, der einen zweiten Ausgang aufweist, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstleitenden Transistors gekoppelt zu werden, der einen zweiten Laststreckenanschluss aufweist, der mit einem ersten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist. Der zweite Treiber ist dazu ausgebildet, im Direktansteuermodus ein zweites Schaltsignal am zweiten Ausgang auszugeben.

**[0005]** Für ein umfassenderes Verständnis der vorliegenden Erfindung und deren Vorteile wird nun Bezug genommen auf die folgende Beschreibung zusammen mit den angefügten Zeichnungen, in denen:

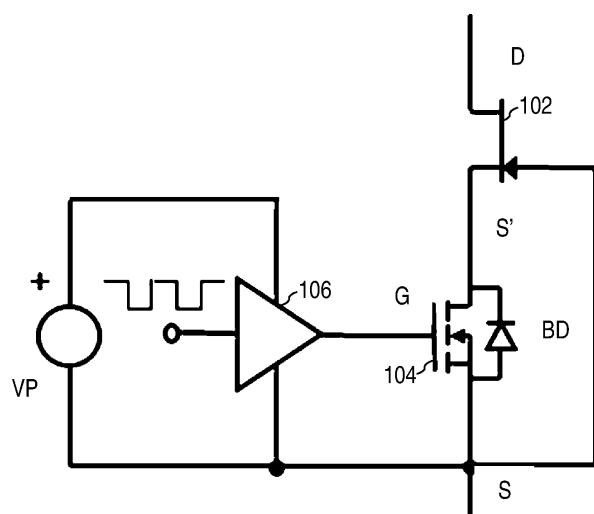

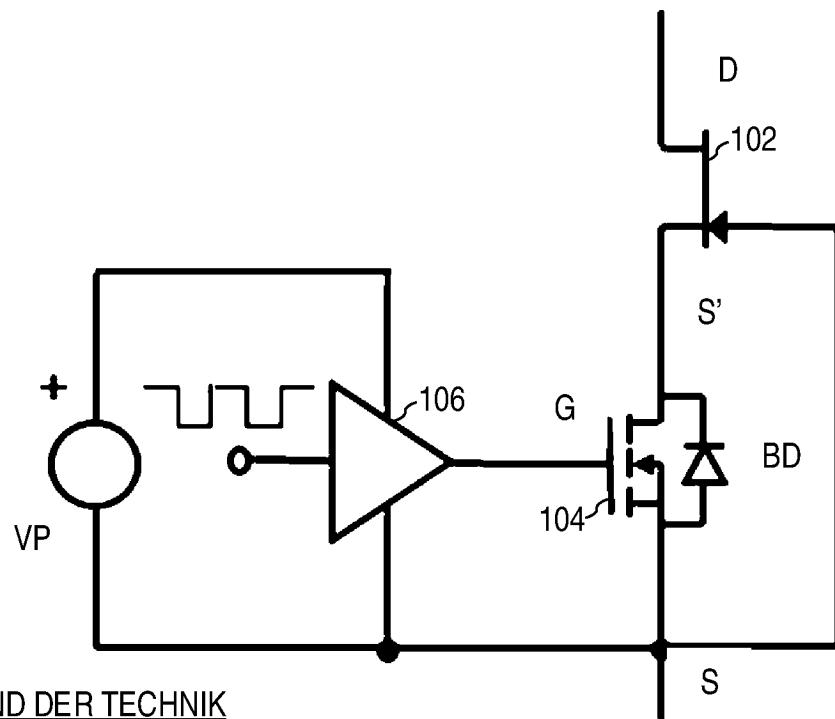

**[0006]** **Fig. 1a–Fig. 1b** herkömmliche zusammengesetzte Schalt-Schaltungen veranschaulichen;

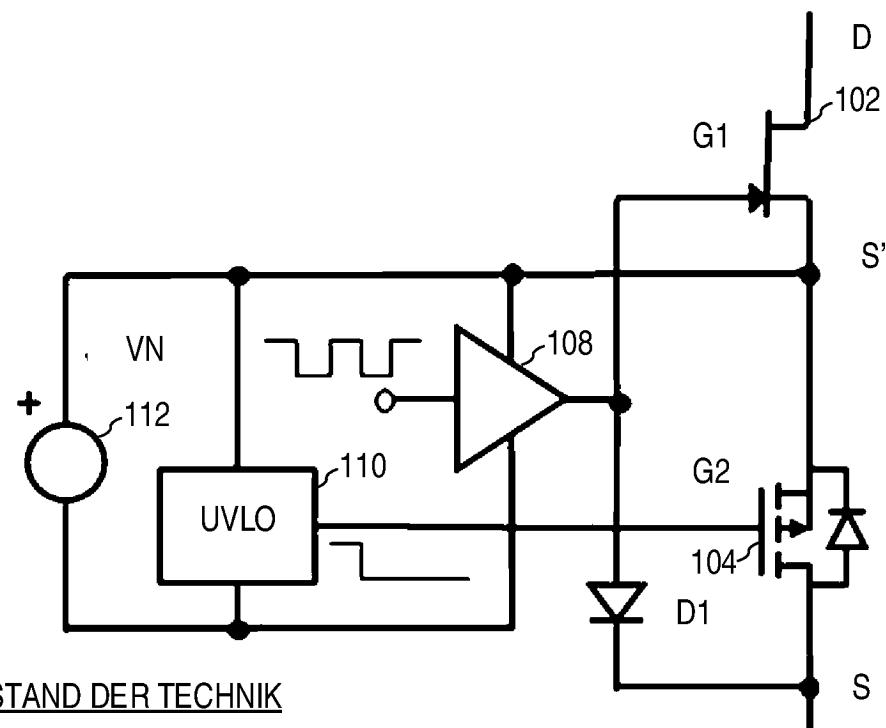

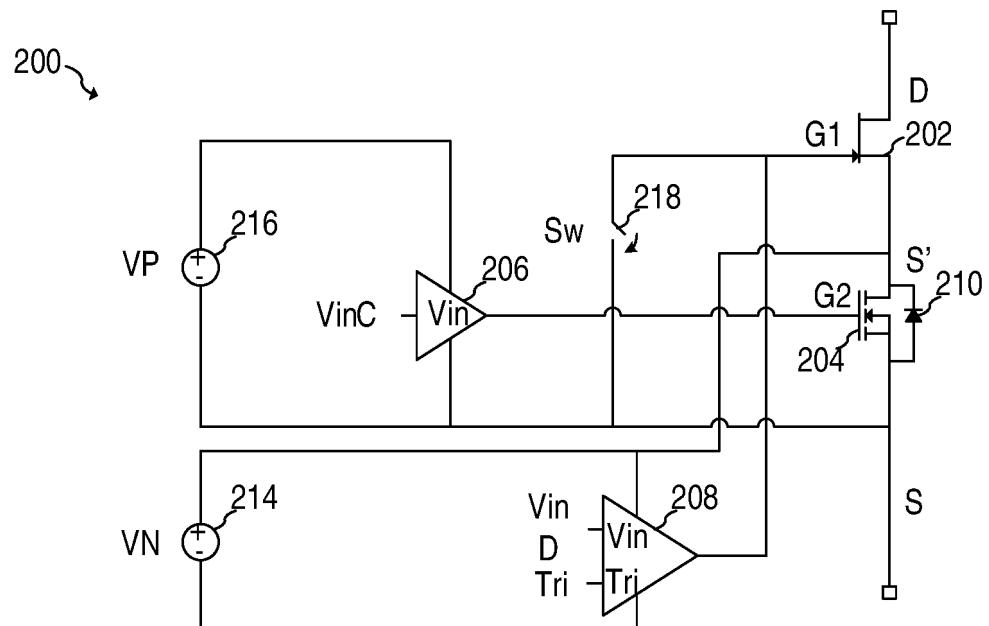

**[0007]** **Fig. 2a–Fig. 2c** Schalt-Schaltungen gemäß einem Ausführungsbeispiel der vorliegenden Erfindung veranschaulichen;

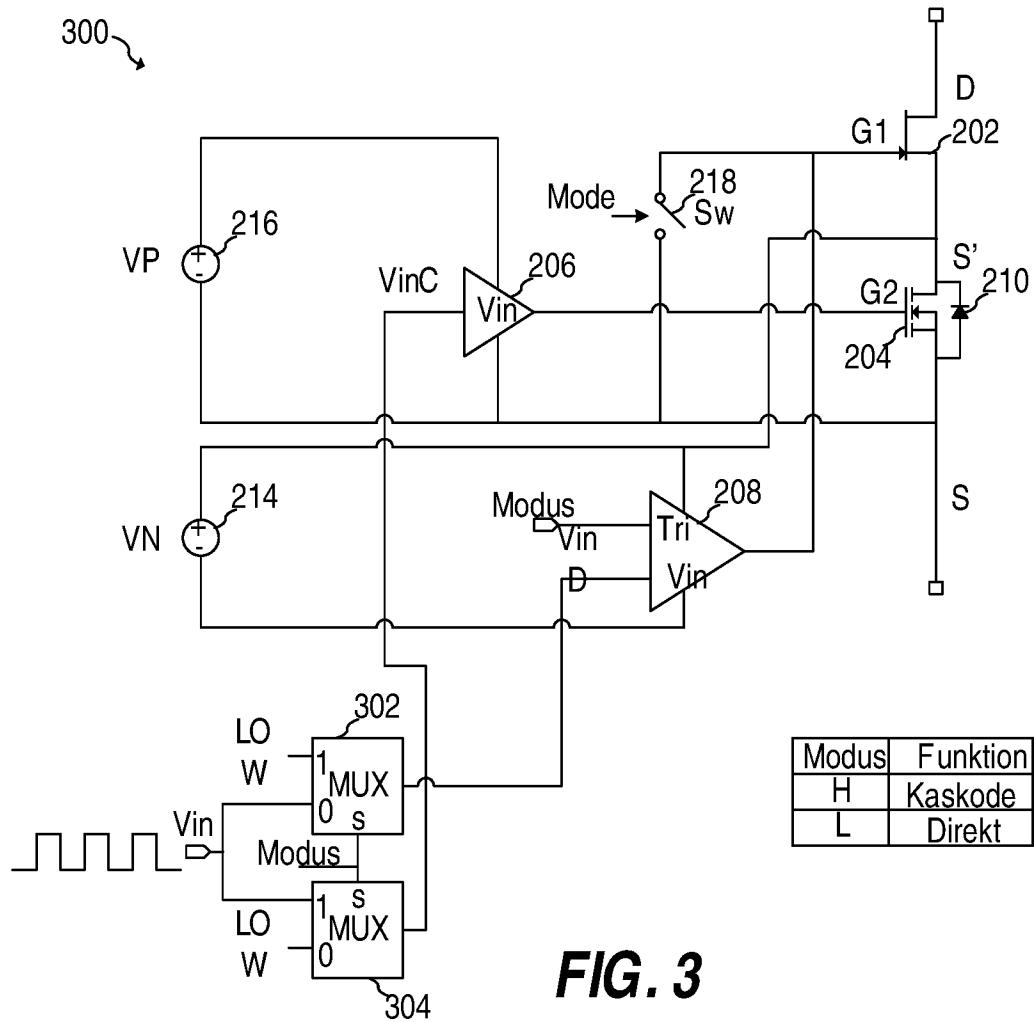

**[0008]** **Fig. 3** eine zusammengesetzte Schalt-Schaltung gemäß einem anderen Ausführungsbeispiel veranschaulicht;

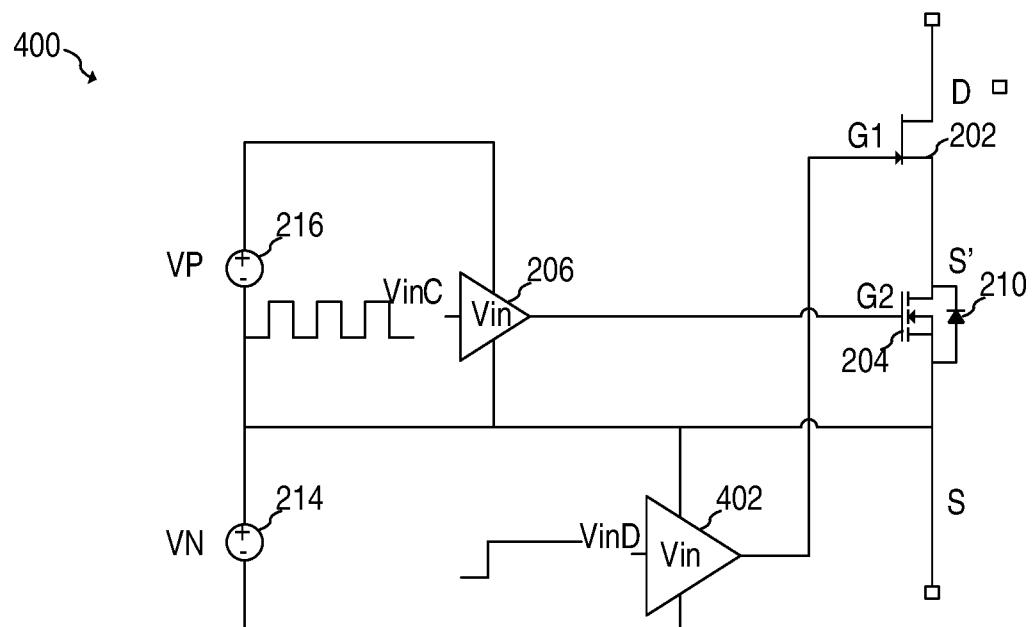

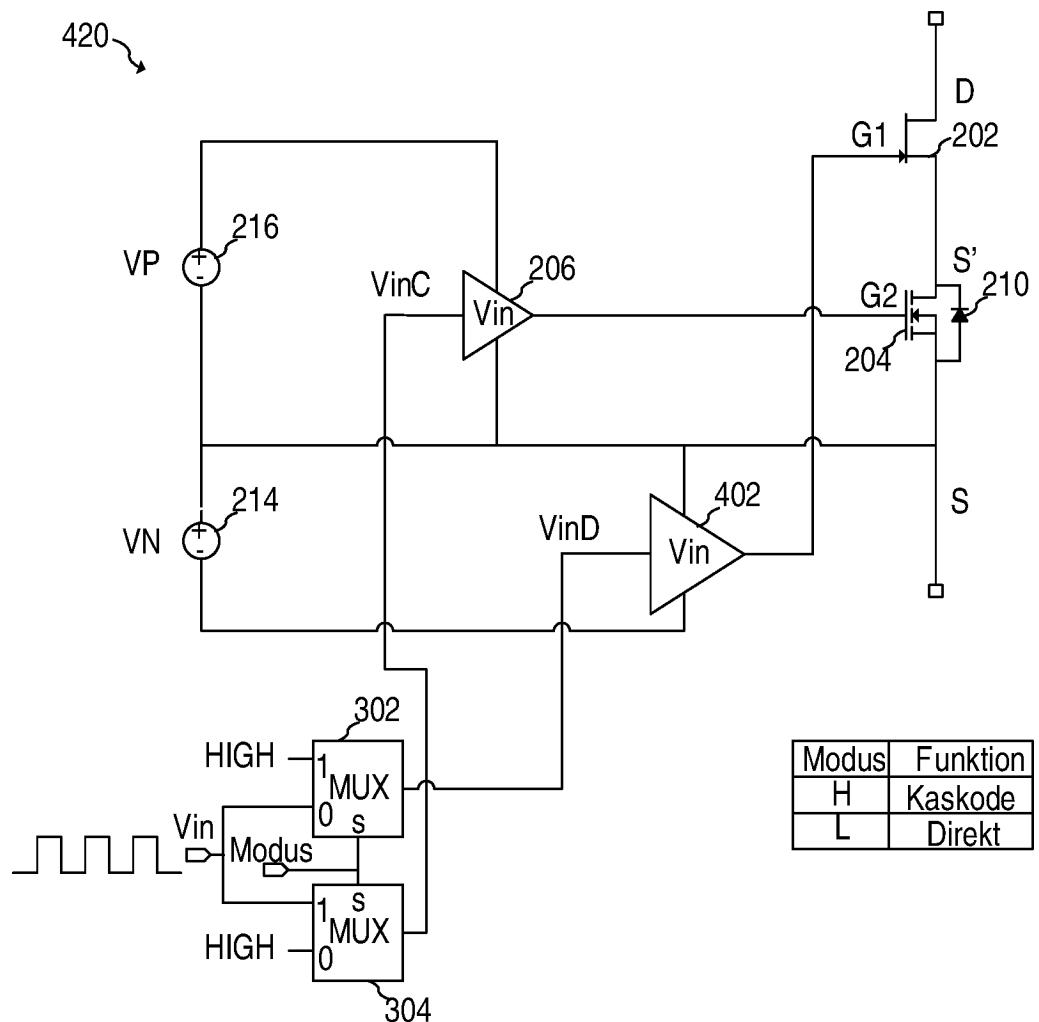

**[0009]** **Fig. 4a–Fig. 4c** zusammengesetzte Schalt-Schaltungen gemäß einer weiteren Ausführungsform veranschaulichen;

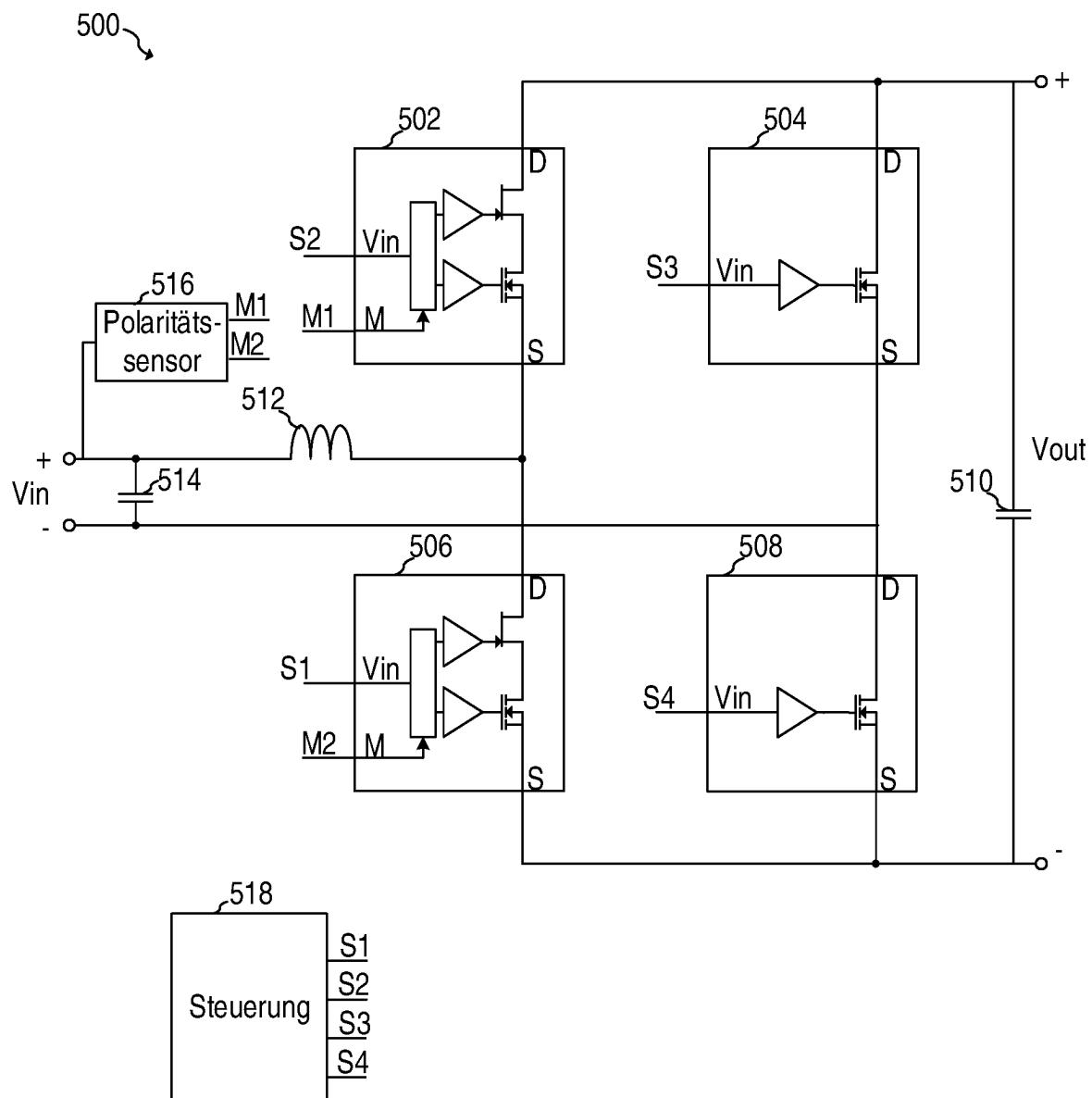

**[0010]** **Fig. 5** ein Ausführungsbeispiel einer getakteten Leistungsversorgung, die Ausführungsbeispiele der zusammengesetzten Schalt-Schaltungen benutzt;

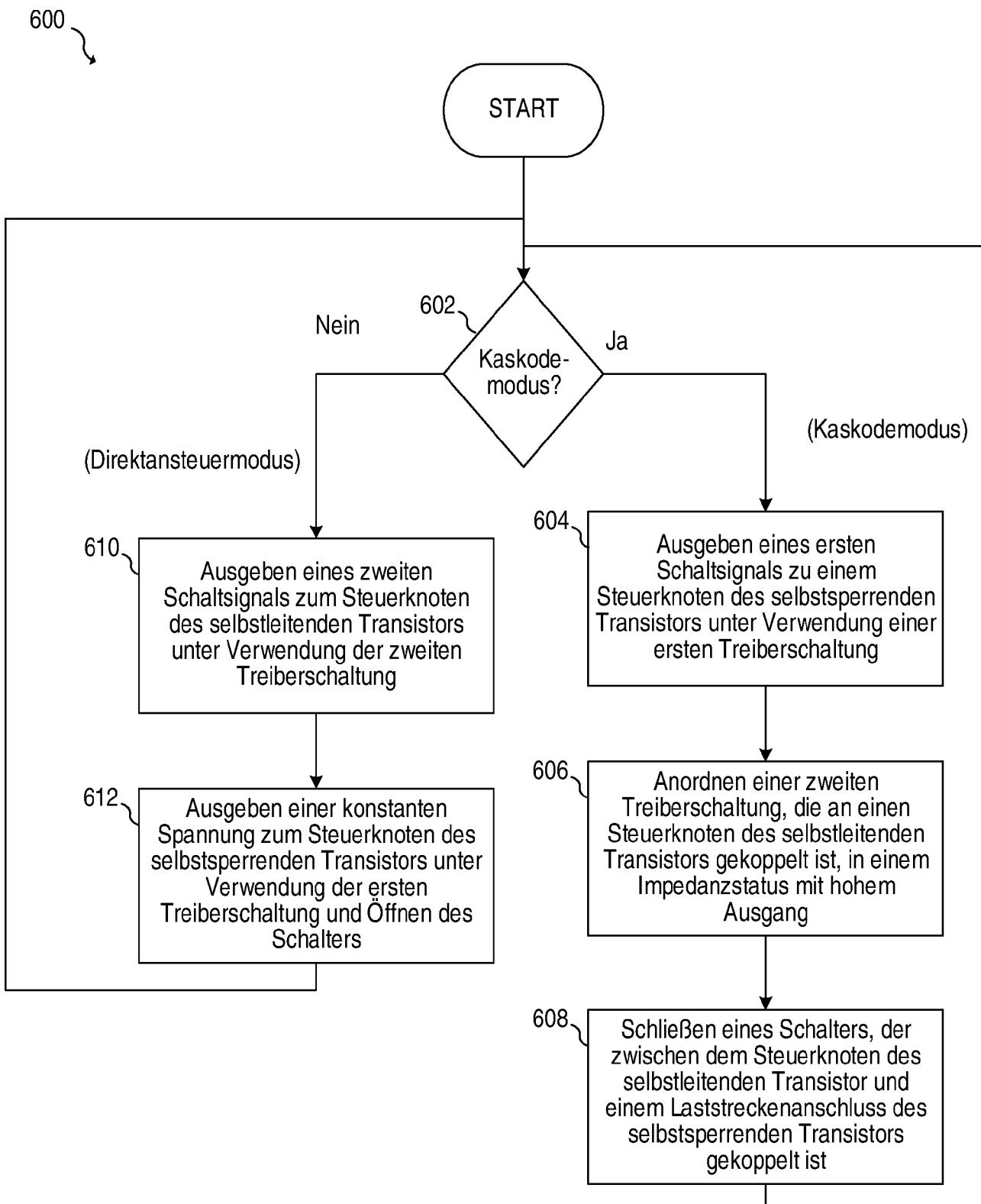

**[0011]** **Fig. 6** ein Flussdiagramm eines Verfahrens gemäß einem Ausführungsbeispiel; und

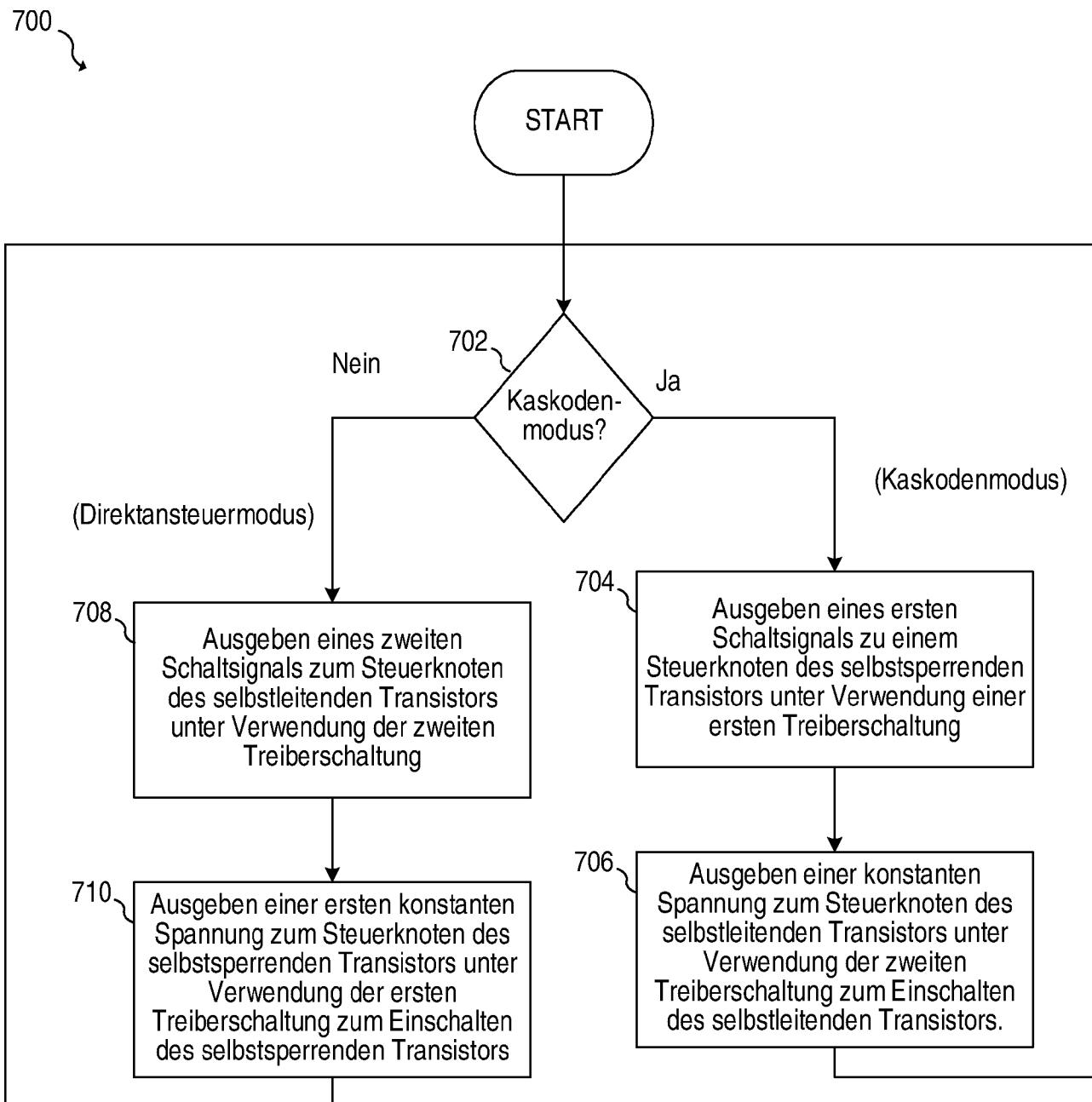

**[0012]** **Fig. 7** ein Flussdiagramm eines Verfahrens gemäß einem weiteren Ausführungsbeispiel.

**[0013]** Zugehörige Nummernbezeichnungen und Symbole in den unterschiedlichen Figuren beziehen sich im Allgemeinen auf entsprechende Teile, wenn nichts anderes angegeben ist. Die Figuren sollen die relevanten Aspekte von bevorzugten Ausführungsbeispielen verdeutlichen und sind nicht unbedingt maßstabsgetreu.

**[0014]** Die Herstellung und Verwendung der vorliegenden bevorzugten Ausführungsbeispiele werden unten ausführlich erläutert. Man wird jedoch zu schätzen wissen, dass die vorliegende Erfindung viele anwendbare erfinderische Konzepte bereitstellt, die in vielen verschiedenen spezifischen Kontexten ausgeführt werden können. Die erläuterten spezifischen Ausführungsbeispiele sind rein veranschaulichend für spezifische Arten, wie die Erfindung hergestellt und verwendet werden kann, und schränken den Umfang der Erfindung nicht ein.

**[0015]** Die vorliegende Erfindung wird in Bezug auf bevorzugte Ausführungsbeispiele in einem spezifischen Kontext beschrieben, einem System und Verfahren für einen Schalter mit einem selbstleitenden Transistor, der mit einem selbstsperrenden Transistor in Reihe gekoppelt ist. Ausführungsbeispiele der vorliegenden Erfindung können auch auf verschiedene Systeme angewandt werden, die eine solche Schaltstruktur benutzen, z. B. getaktete Leistungsversorgungen.

**[0016]** In einem Ausführungsbeispiel der vorliegenden Erfindung umfasst ein Schalter-Controller zum Ansteuern eines zusammengesetzten Schalters, der

einen in Reihe zu einem selbstsperrenden Transistor gekoppelten selbstleitenden Transistor aufweist, eine erste Treiberschaltung, die dazu ausgebildet ist, das Gate eines selbstsperrenden Transistors, wie beispielsweise eines Anreicherungs-MOSFET, anzusteuern, und eine zweite Treiberschaltung, die die dazu ausgebildet das Gate eines selbstleitenden Transistors, wie beispielsweise eines JFET oder eines Galliumnitrid-(GaN)-HEMT anzusteuern. In einem Betriebsmodus stellt die erste Treiberschaltung eine Vorspannung bereit, welche das selbstsperrende Bauelement einschaltet, und der zweite Treiber stellt eine Reihe von Impulsen bereit, welche das selbstleitende Bauelement ein- und ausschalten. In diesem Betriebsmodus betreibt die zweite Treiberschaltung das selbstleitende Bauelement direkt und effektiv. In einem anderen Betriebsmodus arbeitet das selbstleitende Bauelement als Kaskodebauelement und die Reihe von Impulsen wird dem Gate des selbstsperrenden Bauelements über die erste Treiberschaltung zugeführt. In einem Beispiel wird das selbstleitende Bauelement als Kaskodebauelement durch Koppeln des Gates des selbstleitenden Bauelements mit Source des selbstsperrenden Bauelements und durch Versetzen des Ausgangs der zweiten Treiberschaltung in einen Hochimpedanzzustand vorgespannt.

**[0017]** In einigen Ausführungsbeispiele weist die Steuerung einen Schalter auf, der zwischen das Gate des selbstleitenden Bauelements und Source des selbstsperrenden Bauelements gekoppelt ist. Wenn der zusammengesetzte Schalter als Kaskodebauelement betrieben wird, wird der Schalter geschlossen, um das Gate des selbstleitenden Bauelements mit Source des selbstsperrenden Bauelements zu koppeln. Andererseits ist der Schalter, wenn der zusammengesetzte Schalter als direkt angesteuertes Bauelement betrieben wird, offen, um dem zweiten Treiber zu ermöglichen, das Gate des selbstleitenden Bauelements anzusteuern.

**[0018]** Bestimmte Arten von Leistungstransistoren, wie der Sperrsicht-Feldeffekt-Transistor (JFET) und Galliumnitrid-High Electron Mobility-Transistor (GaN HEMT) verhalten sich wie „selbstleitende“ Bauelemente, weil sie sich bei Anlegen von null Volt zwischen Gate und Source des Transistors in einem leitenden Zustand befinden. Zum Abschalten dieser Transistoren wird eine ausreichend hohe negative Gatespannung zwischen Gate und Source des Transistors angelegt. Im Fall eines GaN HEMT kann diese Sperrspannung z. B. zwischen etwa  $-5\text{ V}$  und etwa  $-8\text{ V}$  betragen; Abschaltspannungen außerhalb dieses Bereichs können jedoch in einigen Bauelementen ebenfalls auftreten. Entsprechend besteht bei einigen Systemen, wie solchen, die Ladungspumpen zum Erzeugen von negativen Vorspannungen benutzen, die Gefahr, dass das selbstleitende Bauelement einen Kurzschluss zwischen den Leistungsver-

sorgungsschienen der Anordnung verursacht, bevor die Ladungspumpe ausreichend Zeit hat, um eine ausreichend hohe negative Spannung zum Abschalten des selbstleitenden Bauelements zu erzeugen. Des Weiteren besteht die Gefahr von Kurzschlüssen während verschiedener Fehlerzustände.

**[0019]** Eine Art, wie dieses Problem angegangen wurde, war – wie in **Fig. 1a** dargestellt – das Koppeln des selbstleitenden Bauelements in Reihe mit einem selbstsperrenden Bauelement, wie beispielsweise eines Anreicherungs-MOSFET-Bauelements. Wie dargestellt ist die Source des selbstleitenden Bauelements **102** mit dem Drain des selbstsperrenden Bauelements **104** am Knoten  $S'$  gekoppelt und das Gate  $G$  des selbstsperrenden Bauelements **104** wird von der Treiberschaltung **106** angesteuert.

**[0020]** Hier dient das Gate  $G$  des selbstsperrenden Bauelements **104** als Steueranschluss, der von der Treiberschaltung **106** angesteuert wird, während das Gate des selbstleitenden Bauelements **102** mit der Source  $S$  des selbstsperrenden Bauelements **104** verbunden ist. Während des Hochfahrens ist die Reihenkombination aus selbstleitendem Bauelement und selbstsperrenden Bauelement nicht leitend. Sobald die erforderliche Versorgungsspannung verfügbar ist, kann das selbstsperrende Bauelement mit einem Eingangssignal angesteuert werden, sodass das selbstleitende Bauelement als Kaskodebauelement dient. Wenn der Strom durch den Schalter in Gegenrichtung getrieben wird, wird die Bodydiode  $BD$  des selbstsperrenden Bauelements **104** vorwärts vorgespannt. Aufgrund der Schaltkreistopologie (d. h. Verbinden des Sourceknotens  $S'$  des selbstleitenden Transistors **102** mit dem Sourceknoten  $S$  des selbstsperrenden Transistors **104**) bleibt das selbstleitende Bauelement in seinem An-Zustand, d. h.  $V_{GD} > 0$ .

**[0021]** Es treten jedoch eine Reihe von Problemen bei dem zusammengesetzten Bauelement auf, wenn dieses als eine Kaskode betrieben wird. Erstens können Schaltverluste auftreten, weil die Gate-Source-Kapazität des selbstleitenden Bauelements **102** von dem Hochspannungsnetzteil betrieben wird und nicht von der Gatetreiber-Versorgungsspannung. Des Weiteren können weitere Schaltverluste aufgrund der Drain-Kapazität des selbstsperrenden Bauelements **104** auftreten, das eine sehr große Bauelement zum Handhaben niedriger Ströme sein kann und eine geringe Impedanz besitzt. Da die parasitäre Drain-Kapazität des selbstsperrenden Bauelements **104** während des Betriebs aufgeladen und entladen wird, geht Leistung verloren.

**[0022]** Ein weiteres Problem mit der Kaskodenkonfiguration ist, dass eine mögliche Spannungsbeanspruchung für das selbstsperrende Bauelement **104** auftritt. Zum Beispiel kann während des Betriebs die Spannung bei Knoten  $S'$  aufgrund der kapaziti-

ven Kopplung vom Drain des selbstleitenden Bauelements **102** sehr große Spannungssprünge aufweisen. Mit anderen Worten, die Spannung bei Knoten S geht über den negativen Schwellenwert des selbstleitenden Bauelements **102** hinaus und kann 20V oder mehr bei einigen Schnellschaltbedingungen erreichen.

**[0023]** Fig. 1b stellt eine andere Art dar, in der eine zusammengesetzte Anordnung mit einem selbstleitenden Transistor und einem selbstsperrenden Transistor betrieben werden kann. Hier wird das Gate G1 des selbstleitenden Bauelements **102** direkt mithilfe des Treibers **108** angesteuert und das Gate G2 des selbstsperrenden Bauelements **104** wird gemäß dem Ausgang der Unterspannungsabschaltung **110** eingeschaltet, welche das selbstsperrende Bauelement **104** einschaltet, wenn die Leistungsversorgung **112** eine Spannung erreicht hat, die ausreicht, um das selbstleitende Bauelement **102** auszuschalten. Während des Normalbetriebs bleibt das selbstsperrende Bauelement **104** im EIN-Zustand. Während des Hochfahrens und bei Störungen kann sich das selbstsperrende Bauelement **104** ausschalten und die Diode D1 verhindert, dass die Drain-Spannung des selbstsperrenden Bauelements hohe Spannungen erreicht, indem das Gate G1 des selbstleitenden Bauelements **102** an die Sourcespannung des selbstsperrenden Bauelements **104** geklemmt wird. In einer solchen direkt angesteuerten Konfiguration müssen die zugeordneten Treiber ggf. beide Gates G1 und G2 des selbstleitenden Bauelements **102** und selbstsperrenden Bauelements **104** ansteuern. Ein weiteres Problem des Direktansteuer-Ansatzes ist, dass ein hoher Sperrstrom über die in Reihe geschalteten Bauelemente zu einem hohen Spannungsverlust in des selbstleitenden Bauelements **102** führt.

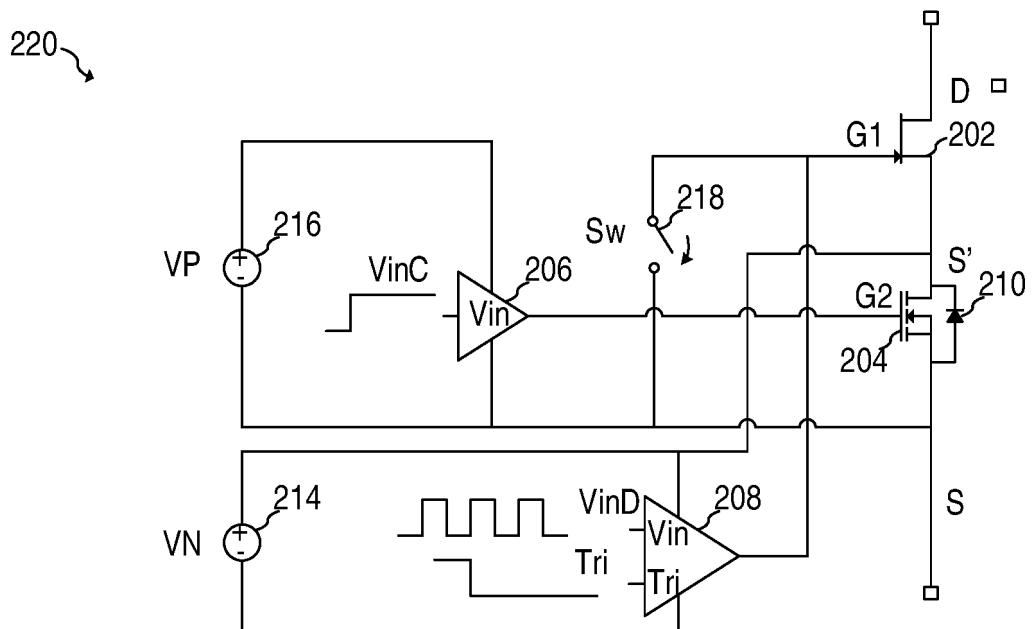

**[0024]** In einem Ausführungsbeispiel gemäß der vorliegenden Erfindung kann ein selbstleitendes Bauelement, das in Reihe mit einem selbstsperrenden Bauelement gekoppelt ist, selektiv konfiguriert werden, um entweder als Kaskodebauelement, wobei das selbstsperrende Bauelement gemäß einem Eingangssignals ein- und ausgeschaltet wird und das selbstleitende Bauelement als Kaskodetransistor funktioniert, oder als direkt angesteuertes Bauelement betrieben zu werden, wobei das selbstleitende Bauelement gemäß dem Eingangssignal ein- und ausgeschaltet wird und das selbstsperrende Bauelement während des Direktansteuerbetriebs eingeschaltet wird. Ein solches Ausführungsbeispiel ist in Fig. 2a dargestellt, die das beispielhafte zusammengesetzte Schalter- und Treibersystem **200** mit einem selbstleitenden Bauelement **202** darstellt, das in Reihe mit dem selbstsperrenden Bauelement **204** gekoppelt ist. Die Bodydiode des selbstsperrenden Bauelements **204** wird durch die Diode **210** repräsentiert. Wie dargestellt wird das selbstsperrende Bauelement **204** von der Treiberschaltung **206** ange-

steuert und das selbstleitende Bauelement **202** von der Tri-State-Treiberschaltung **208** angesteuert. Der Schalter **218** ist dazu ausgebildet, das Gate G1 des selbstleitenden Bauelements **202** mit Source S des selbstsperrenden Bauelements **204** zu koppeln.

**[0025]** Die Treiberschaltung **206** erhält ihre Leistung aus der Leistungsversorgung **216**. Entsprechend kann die Ausgangsspannung der Treiberschaltung **206** zwischen der Sourcespannung des selbstsperrenden Bauelements **204** bei Knoten S und einer Spannung umschalten, welche die Summe der Sourcespannung des selbstsperrenden Bauelements **204** und der Spannung der Leistungsversorgung **216** ist. In einigen Ausführungsbeispielen reicht die Spannung VP der Leistungsversorgung **216** aus, um das selbstsperrende Bauelement **204** auszuschalten, wird aber niedrig genug erzeugt, um eine Überbeanspruchung des Gates des selbstsperrenden Bauelements **204** zu vermeiden. Zum Beispiel kann die Spannung VP in dem Bereich zwischen 5V und etwa 12V liegen, in anderen Ausführungsbeispielen können die Spannungen, die außerhalb dieses Bereichs liegen, jedoch ebenfalls verwendet werden.

**[0026]** Die Treiberschaltung **206** kann mithilfe der Treiberschaltungen aus dem Stand der Technik implementiert werden. Zum Beispiel kann in einigen Ausführungsbeispielen eine Texas Instruments UCC 275x zum Implementieren der Treiberschaltung **206** verwendet werden. Die Leistungsversorgung **216** kann mithilfe von DC-Leistungsversorgungssystemen und -Verfahren implementiert werden, die aus dem Stand der Technik bekannt sind. Zum Beispiel kann die Leistungsversorgung **216** mithilfe der sekundären oder Hilfswicklung eines Transformatoren in einer getakteten Leistungsversorgung zusammen mit einer Diode und/oder einem Gleichrichter implementiert werden. In einigen Ausführungsbeispielen kann die Spannung VP weiter geregelt werden, z. B. mithilfe eines linearen Spannungsreglers. Alternativ können andere bekannte Leistungsversorgungsprinzipien verwendet werden.

**[0027]** Die Tri-State-Treiberschaltung **208** erhält ihre Leistung aus der Leistungsversorgung VN, die einen Pluspol aufweist, der mit dem Sourceknoten S des selbstleitenden Bauelements **202** verbunden ist. Entsprechend kann die Ausgangsspannung der Tri-State-Treiberschaltung **208** zwischen der Spannung am Minuspol der Leistungsversorgung **214** und der Spannung am Pluspol der Leistungsversorgung **214** in einem Spannungsbereich von VN umschalten. In einigen Ausführungsbeispielen reicht die Spannung VN der Leistungsversorgung **214** aus, um eine adäquate negative Abschaltspannung an Gate G1 des selbstleitenden Bauelements **202** zum Bereitstellen einer Betriebsspanne bei verschiedenen Betriebsbedingungen bereitzustellen. In einem Ausführungsbeispiel beträgt die Spannung VN zwischen etwa -10V

und etwa –15V für selbstsperrende Bauelemente mit einer Einsatzspannung zwischen etwa –5V und etwa –8V. Spannungen außerhalb dieses Bereichs können jedoch von der besonderen Ausführungsform und dem Typ des verwendeten Bauelements abhängig sein. Zum Beispiel kann die Einsatzspannung eines GaN HEMT-Bauelements aufgrund ihrer Temperaturempfindlichkeit und Drifteffekte deutlich über Temperatur- und Betriebsbedingungen variieren.

**[0028]** In einem Ausführungsbeispiel wird die Tri-State-Treiberschaltung **208** als Treiberschaltung betrieben, wenn ein logisches LOW am Pin Tri anliegt, und besitzt einen hochimpedanten Ausgang, wenn ein logisches HIGH am Pin Tri anliegt. Alternativ können die logischen Steuersignale am Pin Tri umgekehrt werden. Zum Beispiel kann eine Tri-State-Treiberschaltung **208** als Treiberschaltung betrieben werden, wenn ein logisches LOW am Pin Tri anliegt, und kann einen hochimpedanten Ausgang besitzen, wenn ein logisches HIGH am Pin Tri anliegt. Gemäß verschiedenen Ausführungsbeispielen kann die Tri-State-Treiberschaltung **208** mithilfe der Tri-State-Treiberschaltungen aus dem Stand der Technik implementiert werden. Zum Beispiel kann der IXYS 609 Low Side MOSFET-Treiber von IXYS zum Implementieren der Tri-State-Treiberschaltung **208** verwendet werden. Ähnlich wie die Leistungsversorgung **216** kann die Leistungsversorgung **214** mithilfe von DC-Leistungsversorgungssystemen und -Verfahren implementiert werden, die aus dem Stand der Technik bekannt sind. Zum Beispiel kann die Leistungsversorgung **214** mithilfe der sekundären oder Hilfswicklung eines Transformators in einer getakteten Leistungsversorgung zusammen mit einer Diode und/oder einem Gleichrichter implementiert werden. In einigen Ausführungsbeispielen kann die Spannung VN weiter geregelt werden, z. B. mithilfe eines linearen Spannungsreglers. Alternativ können andere bekannte Leistungsversorgungsprinzipien verwendet werden.

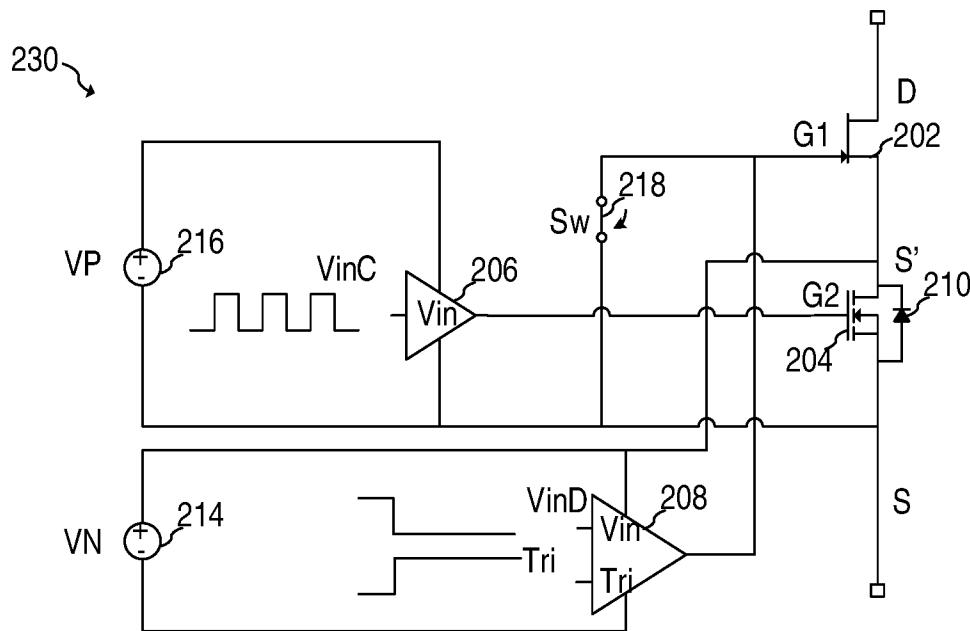

**[0029]** In einem Ausführungsbeispiel wird der Betriebsmodus des zusammengesetzten Schalter- und Treibersystems **200** durch den Status des Schalters **218** bestimmt, ob eine Tri-State-Schaltung **208** eine hohe Ausgangsimpedanz besitzt oder nicht, wobei die Treiberschaltung **206** oder **208** das Schaltignal liefert. **Fig. 2b** veranschaulicht den Betrieb des zusammengesetzten Schalter- und Treibersystems im Direktansteuermodus und **Fig. 2c** veranschaulicht den Betrieb des zusammengesetzten Schalter- und Treibersystems im Kaskodenmodus dar.

**[0030]** In einem Ausführungsbeispiel wird das zusammengesetzte Schalter- und Treibersystem **220** in einem Direktansteuermodus betrieben durch Öffnen des Schalters **218**, Zuführen einer Einschaltspannung für das selbstsperrende Bauelement **204** über die Treiberschaltung **206** und das Zuführen

eines Schaltsignals an das selbstleitende Bauelement **202** über die Tri-State-Treiberschaltung **208**. In einigen Ausführungsbeispielen wird die Einschaltspannung des selbstsperrenden Bauelements **204** erzeugt durch Zuführen eines logischen HIGH am Eingangsknoten VinC der Treiberschaltung **206**. Das Schaltignal wird dem selbstleitenden Bauelement **202** durch Zuführen eines Schaltsignals am Eingang VinD der Tri-State-Treiberschaltung **208** und eines logischen LOW an den Tri-State-Modus-Eingang Pin Tri der Tri-State-Treiberschaltung **208** zugeführt. Während des Betriebs wird der Schalter **218** geöffnet, um zu verhindern, dass der Ausgang der Tri-State-Treiberschaltung **208** mit dem Sourceknoten S des selbstsperrenden Bauelements **204** kurzgeschlossen wird.

**[0031]** In einem Ausführungsbeispiel wird das zusammengesetzte Schalter- und Treibersystem **230** in einem Kaskodenmodus durch Schließen des Schalters **218** betrieben, wobei ein Schaltignal des selbstsperrenden Bauelements **204** über die Treiberschaltung **206** zugeführt wird, die das Gate G1 des selbstleitenden Bauelements **202** mit dem Sourceknoten S des selbstsperrenden Bauelements **204** koppelt. Der Ausgang der Tri-State-Treiberschaltung **208** ist auf eine hohe Impedanz eingestellt, um das Umschalten der Vorspannung des Sourceknotens S des selbstsperrenden Bauelements **204** zu vermeiden. In einigen Ausführungsbeispielen wird die Tri-State-Treiberschaltung **208** durch Zuführen eines logischen LOW am Tri-State-Modus-Eingangspin Tri der Tri-State-Treiberschaltung **208** in den Tri-State-Modus versetzt, und das Schaltignal wird der Treiberschaltung **206** über den Eingangspin VinC zugeführt.

**[0032]** **Fig. 3** zeigt ein Ausführungsbeispiel eines zusammengesetzten Schalter- und Treibersystems **300** gemäß einem anderen Ausführungsbeispiel, das eine zusätzliche Modussteuerschaltung aufweist. Wie dargestellt, steuert das Eingangssignal Mode den Modus des zusammengesetzten Schalter- und Treibersystems **300**, sodass, wenn ein logisches HIGH an den Eingang Mode angelegt wird, das System in einem Kaskodenmodus arbeitet, und, wenn ein logisches LOW an den Eingang Mode angelegt wird, das System in einem Direktansteuermodus arbeitet. Wie dargestellt, wird das Eingangssignal Mode an den Schalter **218**, an den Tri-State-Eingang Pin Tri und an die Multiplexer **302** und **304** angelegt. Daraus wird bei Anlegen einer Logik HIGH an das Eingangssignal Mode der Schalter **218** geschlossen und der Ausgang der Tri-State-Treiberschaltung **208** auf eine hohe Impedanz gesetzt, wodurch der Sourceknoten S des selbstsperrenden Bauelements **204** mit dem Gate G1 des selbstleitenden Bauelements **202** gekoppelt wird. Das Eingangssignal Mode leitet auch das Eingangsschaltignal Vin zum Eingang VinC der Treiberschaltung **206** über Multiplexer **304** und ein Logik LOW-Signal zum Eingang VinD der Tri-State-

Treiberschaltung **208** über Multiplexer **302**, wodurch das Eingangsschaltignal zur Treiberschaltung **206** geleitet wird. In einigen Ausführungsbeispielen kann ein Logik HIGH-Signal dem Eingang VinD der Tri-State-Treiberschaltung **208** bereitgestellt werden, weil die Tri-State-Treiberschaltung **208** in einem hohen Hochimpedanzausgang-Modus arbeitet.

**[0033]** Andererseits wird, wenn ein logisches LOW an das Eingangssignal Mode angelegt wird, der Schalter **218** geöffnet und eine Tri-State-Treiberschaltung **208** konfiguriert, das das Gate G1 des selbstleitenden Bauelements **202** anzusteuern, wodurch das selbstleitende Bauelement **202** direkt angesteuert wird. Das Eingangssignal Mode leitet auch das Eingangsschaltignal Vin zum Eingang VinD der Tri-State-Treiberschaltung **208** über den Multiplexer **302** und ein logisches HIGH-Signal zum Eingang VinC der Treiberschaltung **206** über den Multiplexer **304**, wodurch das Eingangsschaltignal zur Treiberschaltung **208** geleitet wird und das selbstsperrende Bauelement **204** eingeschaltet wird.

**[0034]** Das zusammengesetzte Schalter- und Treibersystem **300** aus **Fig. 3** ist nur ein spezifisches Ausführungsbeispiel eines zusammengesetzten Schalter- und Treibersystems ist. In alternativen Ausführungsbeispielen können andere funktionell ähnliche Schaltungen und Topologien verwendet werden. Zum Beispiel kann in einigen Ausführungsbeispielen die Polarität des Eingangssignal Modes umgekehrt werden, sodass ein HIGH-Eingangssignal Mode den Direktansteuermodus auswählt und ein LOW-Eingangssignal Mode den Kaskodenmodus auswählt. In einigen Ausführungsbeispielen kann eine Multi-Bit-Auswahllogik verwendet werden.

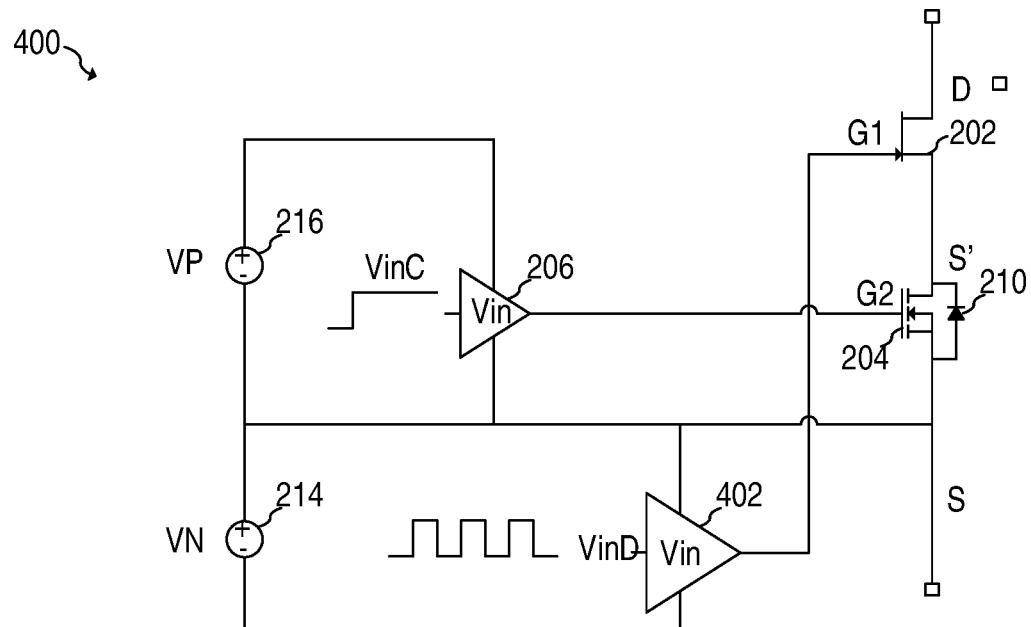

**[0035]** **Fig. 4a-c** zeigen zusammengesetzte Schalter- und Treibersysteme gemäß einem weiteren Ausführungsbeispiel der vorliegenden Erfindung. Hier wird anstelle der Verwendung einer Schalter- und Tri-State-Treiberschaltung zum Konfigurieren der Verbindung zu dem selbstleitenden Bauelement **202** das Modus-Umschalten zwischen dem Direktansteuerbetrieb und dem Kaskodenbetrieb durch selektives Betreiben der Verstärker aktiviert, die mit den Gates des selbstleitenden Bauelements **202** und selbstsperrenden Bauelements **204** gekoppelt sind.

**[0036]** **Fig. 4a** zeigt das Treibersystem **400**, das dazu ausgebildet ist, im Direktansteuerbetrieb zu arbeiten. Wie dargestellt, weist das Treibersystem **400** eine Treiberschaltung **206** mit einem Ausgang auf, der mit dem Gateanschluss G2 des selbstsperrenden Bauelements **204** gekoppelt ist, und Treiberschaltung **402** weist einen Ausgang auf, der mit dem Gateanschluss G1 des selbstleitenden Bauelements **202** gekoppelt ist. Die positive Versorgung der Leistungsversorgung **214**, die negative Versorgung der Leistungsversorgung **216**, die negative Versorgung der

Treiberschaltung **206** und die positive Versorgung der Treiberschaltung **402** sind mit der Source S des selbstsperrenden Bauelements **204** gekoppelt.

**[0037]** Während des Direktansteuerbetriebs ist der Gateanschluss G2 des selbstsperrenden Bauelements **210** vorgespannt, z. B. über die Treiberschaltung **206** zur positiven Spannung VP der Leistungsversorgung **216**, wodurch das selbstsperrende Bauelement **204** eingeschaltet wird. In einem Ausführungsbeispiel kann das selbstsperrende Bauelement **204** durch Anlegen eines logischen HIGH an Eingang VinC der Treiberschaltung **206** eingeschaltet werden. Ein Schaltignal wird dann an Eingang VinD der Treiberschaltung **402** angelegt. In einem Ausführungsbeispiel schaltet der Ausgang der Treiberschaltung **402** den Eingang G1 am Gate des selbstleitenden Bauelements **202** zwischen der Spannung am Sourceknoten S des selbstsperrenden Bauelements **204** und der Spannung am Minuspol der Leistungsversorgung **214** um. Wenn der Gateknoten G1 des selbstleitenden Bauelements **202** bei einer negativen Versorgungsspannung des Gatetreibers **402** vorgespannt ist, wird das selbstleitende Bauelement **202** abgeschaltet. Wenn der Gateknoten **202** an der Sourcespannung S des selbstsperrenden Bauelements **204** vorgespannt ist (positive Versorgung des Gatetreibers), wird das selbstleitende Bauelement **202** eingeschaltet. In einem Ausführungsbeispiel werden die Spannungen VP und VN der Leistungsversorgungen **216** und **214** gemäß den Einsatzspannungen des selbstsperrenden Bauelements **204** bzw. selbstleitenden Bauelements **202** gesetzt. In einem Beispiel liegt für das Treibersystem **400** die Spannung VP der Leistungsversorgung **216** zwischen etwa 5 V und etwa 12 V und die Spannung VN der Leistungsversorgung **402** zwischen etwa 10 V und etwa 15 V. In alternativen Ausführungsbeispielen können unterschiedliche Spannungen verwendet werden.

**[0038]** **Fig. 4b** zeigt das Treibersystem **400**, das dazu ausgebildet ist, im Kaskodenmodus zu arbeiten. Hier ist der Eingang VinD der Treiberschaltung **402** auf ein logisches HIGH gesetzt, um die Spannung des Sourceknotens S des selbstsperrenden Bauelements **204** an Gate G1 des selbstleitenden Bauelements **202** anzulegen. Die Schaltspannung wird an den Eingang VinC der Treiberschaltung **206** angelegt, die wiederum das Schaltignal an den Gateanschluss G2 des selbstsperrenden Bauelements **204** anlegt.

**[0039]** **Fig. 4c** zeigt ein Ausführungsbeispiel eines zusammengesetzten Schalter- und Treibersystems **420** gemäß einem weiteren Ausführungsbeispiel, die eine zusätzliche Modussteuerschaltung besitzt. In diesem Fall wird ein Schaltignal an die Eingänge der Multiplexer **302** und **304** angelegt, die das Schaltignal selektiv zum Gateanschluss G1 des selbstleitenden Bauelements **202** im Direktansteuermodus und

zum Gateanschluss G2 des selbstsperrenden Baulements **204** im Kaskodenmodus leiten.

**[0040]** In einem Ausführungsbeispiel arbeitet das zusammengesetzte Schalt- und Treibersystem **420** im Kaskodenmodus, wenn der Eingang Modehoch (high) ist. Hier wählt der Multiplexer **302**, wenn der Eingang ModeHIGH ist, einen Logik-HIGH-Eingang aus und legt den Logik-HIGH-Eingang an den Eingang VinD der Treiberschaltung **402** an, wodurch das selbstleitende Bauelement **202** eingeschaltet wird. Der Multiplexer **302** legt das Schaltsignal an Eingang VinC der Treiberschaltung **206** an, die wiederum das Schaltsignal an das selbstsperrende Bauelement **204** anlegt.

**[0041]** Das Ausführungsbeispiel des zusammengesetzten Schalt- und Treibersystem **420** wird im Direktansteuermodus betrieben, wenn der Eingang ModeLOW ist. Hier wählt der Multiplexer **302**, wenn der Eingang ModeLOW ist, das Schaltsignal aus und legt das Schaltsignal an den Eingang VinD der Treiberschaltung **402** an, wodurch das Schaltsignal an das selbstleitende Bauelement **202** angelegt wird. Der Multiplexer **304** legt ein logisches HIGH-Signal an den Eingang VinC der Treiberschaltung **206** an, die wiederum das selbstsperrende Bauelement **204** einschaltet. Es versteht sich, dass das zusammengesetzte Schalter- und Treibersystem **420** aus **Fig. 4c** nur eine spezifische Ausführungsform eines zusammengesetzten Schalter- und Treibersystems ist. In alternativen Ausführungsbeispielen können andere funktionell ähnliche Schaltungen und Topologien verwendet werden.

**[0042]** **Fig. 5** zeigt einen getakteten Leistungswandler **500** gemäß einem Ausführungsbeispiel der vorliegenden Erfindung, der dazu ausgebildet ist, ein AC-Eingangssignal, wie z. B. eine Netzspannung mit 50 Hz bis 60Hz, am Eingang Vin in eine DC-Ausgangsspannung am Ausgang Vout zu wandeln. Zum Beispiel ist bei einem Ausführungsbeispiel der getaktete Leistungswandler **500** dazu ausgebildet, eine Netzeingangsspannung mit 120 VAC oder 240 VAC und 50 Hz bis 60 Hz in eine DC-Ausgangsspannung von etwa 400V zu wandeln. Alternativ können andere Eingangsspannungen verwendet werden, die im gleichen oder in anderen Frequenzbereichen arbeiten.

**[0043]** Der Schaltstromrichter **500** weist eine H-Bridge auf, die mithilfe zusammengesetzter Schalter und Treiber **502** und **506** gemäß den hierin beschriebenen Ausführungsbeispielen implementiert ist. Diese H-Bridge ist mit dem Ausgang Vin über eine Spule **512** gekoppelt. Während des Betriebs des getakteten Leistungswandlers **500** magnetisieren und entmagnetisieren der zusammengesetzte Schalter und Treiber **502** und **506** die Spule **512**, sodass die Leistung vom Eingang Vin zum Ausgang Vout übertragen wird. Die Schalt-Schaltungen **504** und **508**,

die MOSFET-Schalttransistoren einschließen, werden als synchrone Gleichrichter betrieben, die einen Rückstrompfad bereitstellen und in einigen Ausführungsbeispielen auch mithilfe von Dioden implementiert werden können. Der Kondensator **514** repräsentiert die Eingangskapazität des Schaltstromrichters **500** und der Kondensator **510** repräsentiert die Lastkapazität des Schaltstromrichters **500**. Jeder zusammengesetzte Schalter und Treiber **502** und **506** der Ausführungsform weist ein selbstleitendes Bauelement auf, das in Reihe mit einem selbstsperrenden Bauelement gekoppelt ist, und ist dazu ausgebildet, ein Schaltsignal am Eingangspin Vin und eine Modusauswahlsignals am Eingangspin M zu erhalten. In einem Ausführungsbeispiel stellt die Steuerung **518** Schaltsignale an den zusammengesetzten Schalter und Treiber **502** und **506** und die Schalt-Schaltungen **504** und **508** bereit, deren zeitlicher Verlauf (engl.: timing) dazu ausgebildet ist, ein AC-Eingangssignal am Eingang Vin in ein DC-Ausgangssignal am Ausgang Vout zu wandeln. Die Steuerung **518** kann mithilfe eines H-Bridge-Schaltstromrichters implementiert sein, der im Stand der Technik bekannt ist. In einigen Ausführungsbeispielen kann die Steuerung **518** Strom und/oder eine Spannungsrückkopplung aus verschiedenen Knoten und Zweigströmen des Schaltstromrichters **500** benutzen, um eine Regelung der Ausgangsspannung, des Ausgangstroms und/oder der Eingangsströme zu ermöglichen. Zum Beispiel kann das Schalten der Signale S1, S2, die mit den zusammengesetzten Schaltern und Treibern **506** und **502** gekoppelt sind, und der Signale S3 und S4, die mit den Schalt-Schaltungen **504** und **508** gekoppelt sind, dazu ausgebildet sein, eine geregelte Ausgangsspannung und einen geregelten Eingangstrom zu erzeugen, sodass eine Leistungsfaktorkorrektur erreicht wird.

**[0044]** In einem Ausführungsbeispiel ist jeder zusammengesetzte Schalter und Treiber **502** und **506** gemäß einem Ausführungsbeispiel dazu ausgebildet, in einem Kaskodenmodus zu arbeiten, wenn einer Logik HIGH ein Eingang Pin M zugeordnet wird und in einem Direktansteuermodus betrieben, wenn ein logisches LOW am Eingangspin M angelegt wird. In alternativen Ausführungsbeispielen kann die Polarität des Modusauswahlsignals umgekehrt werden. Der Polaritätssensor **516** ist zum Messen der Polarität der Spannung an der Eingangsleitung Vin und zum Erzeugen der Modussignale M1 und M2 gemäß der gemessenen Spannung an der Leitung ausgebildet konfiguriert.

**[0045]** In einem Ausführungsbeispiel werden die Betriebsmodi der zusammengesetzten Schalter und Treiber **502** und **506** derart ausgewählt, dass Schaltverluste reduziert werden und hohe Rückwärts-Vorspannungsbedingungen an den selbstleitenden Baulementen vermieden werden. Wenn zum Beispiel die Spannung am Eingang Vin eine positive Polari-

tät besitzt, dient der zusammengesetzte Schalter und Treiber **506**, der mit den Steuersignalen S1 gekoppelt ist, im Wesentlichen als ein Schalter und, der zusammengesetzte Schalter und Treiber **502** dient, wenn er mit den Steuersignalen S2 gekoppelt ist, im Wesentlichen als Diode. Entsprechend kann, wenn die Spannung am Eingang Vin eine positive Polarität besitzt, der zusammengesetzte Schalter und Treiber **502** als Kaskodebauelement konfiguriert sein, und der zusammengesetzte Schalter und Treiber **506** kann als direkt angesteuertes Bauelement konfiguriert sein. Durch das Betreiben des zusammengesetzten Schalters und Treibers **502** als Kaskodebauelement, wenn dieser als Diode arbeitet, kann eine große Sperrspannung des selbstleitenden Bauelements vermieden werden. Obgleich die Schaltverluste leicht höher sind, können die Verluste in bestimmten Anwendungen insgesamt reduziert werden (insbesondere bei hoher Schaltfrequenz bei mittlerer Spannung). In anderen Anwendungen und unter unterschiedlichen Bedingungen kann jede beliebige der anderen möglichen Kombinationen (im Kaskodemodus, im Direktansteuer-Diodenmodus oder sowohl im Kaskodemodus als auch Direktansteuermodus betriebener Schalter) je nach dem bestimmten System und seinen Anforderungen verwendet werden.

**[0046]** Wenn Vin die Polarität wechselt, wechseln die Bauelemente **502** und **506** ihre Funktion. Nun arbeitet **502** als Schalter und **506** als Diode. Die den zusammengesetzten Schaltern und Treibern **502**, **506** zugewiesenen Modi werden umgekehrt. Zum Beispiel werden der zusammengesetzte Schalter und Treiber **506** als direkt angesteuerte Bauelemente und der zusammengesetzte Schalter und Treiber **502** als Kaskodebauelement betrieben. Durch das dynamische Wechseln der Betriebsmodi der zusammengesetzten Schalter und Treiber **502** und **506** und während verschiedener Betriebsphasen des Schaltstromrichters **500** kann eine erhöhte Effizienz erreicht werden, weil weniger Schaltverluste von den parasitären Kapazitäten der selbstsperrenden Bauelemente verursacht werden.

**[0047]** **Fig. 6** zeigt ein Flussdiagramm eines beispielhaften Verfahrens **600** zum Betreiben eines zusammengesetzten Schalters, der einen selbstleitenden Transistor aufweist, der mit einem selbstsperrenden Transistor in Reihe gekoppelt ist. Dieses Verfahren kann z. B. zusammen mit den Ausführungsbeispielen aus **Fig. 2a-c** und **Fig. 3** verwendet werden. In einem Ausführungsbeispiel wird bei Schritt **602** bestimmt, ob der zusammengesetzte Schalter im Kaskodemodus oder im Direktansteuermodus betrieben werden muss. Diese Bestimmung erfolgt z. B. basierend auf einer Polarität eines AC-Eingangssignals, wie in dem Ausführungsbeispiel gemäß **Fig. 4** beschrieben. Wenn der Kaskodemodus ausgewählt wird, wird ein erstes Schaltsignal an einen Steuerknoten eines selbstsperrenden Transistors gekoppelt,

der eine erste Treiberschaltung bei Schritt **604** verwendet. Gleichzeitig wird bei Schritt **606** eine zweite Treiberschaltung mit einem Steuerknoten eines selbstleitenden Transistors gekoppelt, während sein Ausgang in einem hohen Hochimpedanz-Zustand ist. Ein Schalter, der zwischen dem Steuerknoten des selbstleitenden Transistors und dem Sourceanschluss des selbstsperrenden Transistors gekoppelt ist, wird bei Schritt **608** geschlossen.

**[0048]** Wenn der Direktansteuermodus im Schritt **602** ausgewählt wird, wird im Schritt **610** ein zweites Schaltsignal mit dem Steuerknoten des selbstleitenden Transistors unter Verwendung der zweiten Treiberschaltung gekoppelt. Bei Schritt **612** ist eine konstante Spannung, die höher als die Schwellenspannung ist, mit dem Steuerknoten des selbstsperrenden Transistors unter Verwendung der ersten Treiberschaltung gekoppelt. Der Schalter, der zwischen den Steuerknoten des selbstleitenden Transistors und dem Sourceanschluss des selbstsperrenden Transistors gekoppelt ist, wird geöffnet.

**[0049]** **Fig. 7** zeigt ein Flussdiagramm eines beispielhaften Verfahrens **700** zum Betreiben eines zusammengesetzten Schalters, der einen selbstleitenden Transistor aufweist, der mit einem selbstsperrenden Transistor in Reihe gekoppelt ist. Dieses Verfahren kann z. B. zusammen mit den Ausführungsbeispielen aus **Fig. 4a-c** verwendet werden. In einem Ausführungsbeispiel wird bei Schritt **702** bestimmt, ob der zusammengesetzte Schalter im Kaskodemodus oder im Direktansteuermodus betrieben werden muss. Diese Bestimmung erfolgt z. B. basierend auf einer Polarität eines AC-Eingangssignals, wie in dem Ausführungsbeispiel gemäß **Fig. 4** beschrieben. Wenn der Kaskodemodus ausgewählt wird, wird ein erstes Schaltsignal mit einem Steuerknoten eines selbstsperrenden Transistors gekoppelt, der eine erste Treiberschaltung bei Schritt **704** verwendet. Gleichzeitig wird bei Schritt **706** eine zweite Treiberschaltung verwendet, um den Steuerknoten des selbstleitenden Transistors mit dem Sourceknoten des selbstsperrenden Transistors zu verbinden.

**[0050]** Wenn bei Schritt **702** der Direktansteuermodus ausgewählt wird, wird im Schritt **708** ein zweites Schaltsignal mit dem Steuerknoten des selbstleitenden Transistors unter Verwendung der zweiten Treiberschaltung gekoppelt. Bei Schritt **710** ist eine konstante Spannung mit dem Steuerknoten des selbstsperrenden Transistors unter Verwendung der ersten Treiberschaltung gekoppelt.

**[0051]** Gemäß einem Ausführungsbeispiel weist eine Schaltung einen ersten Treiber auf, der einen ersten Ausgang aufweist, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstsperrenden Transistors gekoppelt zu werden. Der erste Treiber ist dazu ausgebildet, in einem Kaskodemodus ein erstes

Schaltsignals am ersten Ausgang auszugeben und in einem Direktansteuermodus eine erste konstante Spannung am ersten Ausgang auszugeben. Die Schaltung weist ferner einen zweiten Treiber auf, der einen zweiten Ausgang aufweist, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstleitenden Transistors gekoppelt zu werden, der einen zweiten Laststreckenanschluss aufweist, der mit einem ersten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist. Der zweite Treiber ist dazu ausgebildet, im Direktansteuermodus ein zweites Schaltsignals am zweiten Ausgang auszugeben.

**[0052]** In einem Ausführungsbeispiel ist der zweite Treiber ferner dazu ausgebildet im Kaskodenmodus eine hohe Impedanz am zweiten Ausgang zu haben, und die Schaltung weist ferner einen Schalter auf, der zwischen den Steuerknoten des selbstleitenden Transistors und einem zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, wobei der Schalter dazu ausgebildet ist, im Direktansteuermodus geöffnet und im Kaskodenmodus geschlossen zu sein. Der erste Treiber weist einen ersten Netzanschluss auf, der zwischen einem ersten Referenzspannungsknoten und den zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, und der zweite Treiber umfasst einen zweiten Netzanschluss, der zwischen den zweiten Laststreckenanschluss des selbstleitenden Transistors und einen zweiten Referenzspannungsknoten gekoppelt ist.

**[0053]** In einem Ausführungsbeispiel weist das erste Schaltignal eine Spannung auf, die von einer Spannung des ersten Referenzspannungsknotens auf eine Spannung des zweiten Laststreckenanschlusses des selbstsperrenden Transistors übergeht, und das zweite Schaltignal umfasst eine Spannung, die von einer Spannung des zweiten Laststreckenanschlusses des selbstleitenden Transistors auf die des zweiten Referenzspannungsknotens übergeht.

**[0054]** Die Schaltung kann ferner eine erste Leistungsversorgung, die zwischen den ersten Referenzspannungsknoten und den zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, und eine zweite Leistungsversorgung, die zwischen den zweiten Laststreckenanschluss des selbstleitenden Transistors und den zweiten Referenzspannungsknoten gekoppelt ist. Die Schaltung kann ferner eine Steuerung umfassen, die dazu ausgebildet ist, ein Eingangsschaltignal mit einem Eingang des ersten Treibers zu koppeln, ein Steuerignal auszugeben, das den zweiten Treiber dazu konfiguriert, eine hohe Impedanz am zweiten Ausgang zu haben, den Schalter im Kaskodenmodus zu schließen, das Eingangsschaltignal mit einem Eingang des zweiten Treibers zu koppeln, eine konstante Spannung an einen Eingang des ersten Treibers anzulegen und den Schalter im Direktansteuermodus

zu öffnen. In einigen Ausführungsbeispielen besitzt die konstante Spannung eine Einschaltspannung des selbstsperrenden Transistors.

**[0055]** Gemäß einigen Ausführungsbeispielen weist die Schaltung ferner den selbstleitenden Transistor und den selbstsperrenden Transistor auf. Der selbstleitende Transistor kann z. B. ein GaN HEMT-Bauelement aufweisen und der zweite Laststreckenanschluss des selbstleitenden Transistors umfasst eine Source des GaN HEMT. In einem Ausführungsbeispiel ist der selbstsperrende Transistor ein Anreicherungs-MOSFET-Transistor, der erste Laststreckenanschluss des Anreicherungs-MOSFET-Transistors ist ein Drain des Anreicherungs-MOSFET-Transistors und der zweite Laststreckenanschluss des Anreicherungs-MOSFET-Transistors ist ein Source des Anreicherungs-MOSFET-Transistors.

**[0056]** In einem Ausführungsbeispiel weist der erste Treiber erste Leistungsversorgungsanschlüsse auf, die zwischen einem ersten Referenzspannungsknoten und dem zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt sind, und der zweite Treiber weist zweite Leistungsversorgungsanschlüsse auf, die zwischen dem zweiten Laststreckenanschluss des selbstleitenden Transistors und einem zweiten Referenzspannungsknoten gekoppelt sind.

**[0057]** Ein Verfahren zum Betreiben eines Schalters mit einem selbstleitenden Transistor, der mit einem selbstsperrenden Transistor gekoppelt ist, umfasst in einem Kaskodenmodus das Ausgeben eines ersten Schaltsignals an einen Steuerknoten des selbstsperrenden Transistors unter Verwendung einer ersten Treiberschaltung und Einschalten des selbstleitenden Transistors, der einen Steuerknoten aufweist, der mit einem Ausgang einer zweiten Treiberschaltung gekoppelt ist. Das Verfahren beinhaltet ferner in einem Direktansteuermodus das Ausgeben eines zweiten Schaltsignals an den Steuerknoten des selbstleitenden Transistors unter Verwendung der zweiten Treiberschaltung, und Ausgeben einer ersten konstanten Spannung am Steuerknoten des selbstsperrenden Transistors unter Verwendung der ersten Treiberschaltung und Öffnen des Schalters.

**[0058]** Das Verfahren beinhaltet ferner im Kaskodenmodus das Versetzen einer zweiten Treiberschaltung, die mit dem Steuerknoten des selbstleitenden Transistors gekoppelt ist, in einen Zustand mit hoher Ausgangsimpedanz und Schließen eines Schalters, der zwischen den Steuerknoten des selbstleitenden Transistors und einen Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist. Der selbstsperrende Transistor kann mithilfe eines FET-Transistors implementiert werden und der Laststreckenanschluss des selbstsperrenden Tran-

sistors kann eine Source des selbstsperrenden Transistors aufweisen.

**[0059]** Im Kaskodemodus kann der Schalter den Steuerknoten des selbstleitenden Transistors mit einem Sourceanschluss des selbstsperrenden Transistors koppeln. Der selbstsperrende Transistor kann mithilfe eines Anreicherungs-MOSFET implementiert werden und der selbstleitende Transistor kann mithilfe eines GaN HEMT implementiert werden.

**[0060]** In einem Ausführungsbeispiel beinhaltet das Verfahren ferner das Anlegen einer ersten Versorgungsspannung zwischen den Netzanschlüssen der ersten Treiberschaltung und das Anlegen einer zweiten Versorgungsspannung zwischen den Netzanschlüssen der zweiten Treiberschaltung. Das Anlegen der ersten Versorgungsspannung kann das Anlegen eines ersten Leistungsversorgungsreferenzknotens an einen Pluspol der ersten Treiberschaltung und das Koppeln eines Lastanschlusses des selbstsperrenden Transistors mit einem Minuspol der ersten Treiberschaltung beinhalten. Das Anlegen der zweiten Versorgungsspannung kann das Anlegen eines zweiten Leistungsversorgungsreferenzknotens an einen Minuspol der zweiten Treiberschaltung und das Koppeln eines Lastanschlusses des selbstleitenden Transistors mit einem Pluspol der zweiten Treiberschaltung beinhalten.

**[0061]** Gemäß einer weiteren Ausführungsform weist eine getaktete Leistungsversorgung mehrere zusammengesetzte Schalt-Schaltungen auf, wobei eine erste zusammengesetzte Schalt-Schaltung in Reihe mit einer zweiten zusammengesetzten Schalt-Schaltung zum Bilden einer ersten Reihenkombination gekoppelt ist. Jeder der mehreren zusammengesetzten Schalt-Schaltungen weist einen selbstleitenden Transistor, einen selbstsperrenden Transistor mit einem ersten Laststreckenanschluss, der mit einem zweiten Laststreckenanschluss des selbstleitenden Transistors gekoppelt ist, und einen ersten Treiber auf, der einen ersten Ausgang umfasst, der mit einem Steuerknoten des selbstsperrenden Transistors gekoppelt ist. Der erste Treiber ist dazu ausgebildet, in einem Kaskodemodus ein erstes Schaltsignals an dem ersten Ausgang auszugeben und in einem Direktansteuermodus eine erste konstante Spannung am ersten Ausgang auszugeben. Jede der mehreren zusammengesetzten Schalt-Schaltungen weist ferner einen zweiten Treiber mit einem zweiten Ausgang auf, der mit einem Steuerknoten des selbstleitenden Transistors gekoppelt ist. Der zweite Treiber ist dazu ausgebildet, im Direktansteuermodus ein zweites Schaltsignals am zweiten Ausgang auszugeben, und jede der mehreren zusammengesetzten Schalt-Schaltungen ist dazu ausgebildet, im Kaskodemodus den Steuerknoten des selbstleitenden Transistors mit einer Source des selbstsperrenden Transistors zu verbinden.

**[0062]** In einem Ausführungsbeispiel ist der zweite Treiber ferner dazu ausgebildet, im Kaskodemodus eine hohe Impedanz am zweiten Ausgang zu haben, und jeder der mehreren Schalt-Schaltungen umfasst ferner einen Schalter, der zwischen den Steuerknoten des selbstleitenden Transistors und einem zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist. Der Schalter ist dazu ausgebildet, im Direktansteuermodus geöffnet und im Kaskodenmodus geschlossen zu sein.

**[0063]** Vorteile der Ausführungsbeispielen schließen die Reduktion von Schaltverlusten und Verlusten aufgrund des Spannungsabfalls in Sperrrichtung gepolter selbstleitender Transistoren ein. Ein weiterer Vorteil der Ausführungsbeispielen schließt die Möglichkeit ein, ein selbstleitendes Bauelement, das in Reihe mit einem selbstsperrenden Bauelement gekoppelt ist, anzusteuern, ohne das selbstsperrende Bauelement übermäßig zu beanspruchen. Entsprechend kann das selbstsperrende Bauelement auf eine Weise bemessen und konfiguriert sein, um die Schaltverluste zu reduzieren.

**[0064]** Weitere Vorteile von Ausführungsbeispielen sind die Optimierungsmöglichkeiten für unterschiedlichen Anwendungen durch Auswählen der am besten geeigneten Betriebsmodus-Kombination.

**[0065]** Zum Beispiel können die beispielhaften Leistungsversorgungssysteme und andere beispielhafte Treibersysteme, die hierin offenbart sind, mithilfe einer gestapelten Treiberschaltung implementiert werden, die in der anhängigen Anmeldung mit der US-Seriennummer 14/473,101 offenbart ist.

## Patentansprüche

1. Schaltung, die aufweist:

einen ersten Treiber, der aufweist: einen ersten Ausgang, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstsperrenden Transistors gekoppelt zu werden, wobei der erste Treiber dazu ausgebildet ist, in einem Kaskodemodus ein erstes Schaltsignals am ersten Ausgang auszugeben ist und in einem Direktansteuermodus eine erste konstanten Spannung am ersten Ausgang auszugeben ist; und

einen zweiten Treiber, der einen zweiten Ausgang aufweist, der dazu ausgebildet ist, mit einem Steuerknoten eines selbstleitenden Transistors gekoppelt zu werden, der einen zweiten Laststreckenanschluss aufweist, der mit einem ersten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, wobei der zweite Treiber dazu ausgebildet ist, im Direktansteuermodus ein zweites Schaltsignals am zweiten Ausgang auszugeben.

2. Schaltung nach Anspruch 1, bei der:

der zweite Treiber ferner dazu ausgebildet ist, im Kaskodemodus eine hohen Impedanz am zweiten Ausgang zu haben; und die Schaltung ferner einen Schalter aufweist, der zwischen den Steuerknoten des selbstleitenden Transistors und einen zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, wobei der Schalter dazu ausgebildet ist, im Direktansteuermodus geöffnet und im Kaskodemodus geschlossen zu sein.

3. Schaltung nach Anspruch 1 oder 2, bei der: der erste Treiber einen ersten Netzanschluss aufweist, der zwischen einen ersten Referenzspannungsknoten und den zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist; und der zweite Treiber einen zweiten Netzanschluss aufweist, der zwischen den zweiten Laststreckenanschluss des selbstleitenden Transistors und einen zweiten Referenzspannungsknoten gekoppelt ist.

4. Schaltung nach Anspruch 3, bei der: das erste Schaltsignal eine Spannung aufweist, die von einer Spannung des ersten Referenzspannungsknotens auf eine Spannung des zweiten Laststreckenanschlusses des selbstsperrenden Transistors übergeht; und das zweite Schaltsignal eine Spannung umfasst, die von einer Spannung des zweiten Laststreckenanschlusses des selbstleitenden Transistors auf die des zweiten Referenzspannungsknotens übergeht.

5. Schaltung nach Anspruch 3, die weiterhin aufweist: eine erste Leistungsversorgung, die zwischen den ersten Referenzspannungsknoten und den zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist; und eine zweite Leistungsversorgung, die zwischen den zweiten Laststreckenanschluss des selbstleitenden Transistors und den zweiten Referenzspannungsknoten gekoppelt ist.

6. Schaltung nach einem der Ansprüche 1 bis 5, die weiterhin eine Steuerung aufweist, die dazu ausgebildet ist, im Kaskodenmodus ein Eingangsschaltsignal mit einem Eingang des ersten Treibers zu koppeln, ein Steuersignal auszugeben, das den zweiten Treiber dazu konfiguriert, eine hohe Impedanz am zweiten Ausgang zu haben, und den Schalter zu schließen; und im Direktansteuermodus das Eingangsschaltsignal mit einem Eingang des zweiten Treibers zu koppeln, eine konstante Spannung an einen Eingang des ersten Treibers anzulegen und den Schalter zu öffnen.

7. Schaltung nach Anspruch 6, wobei die konstante Spannung eine Einschaltspannung des selbstsperrenden Transistors umfasst.

8. Schaltung nach einem der Ansprüche 1 bis 7, die weiterhin den selbstleitenden Transistor und den selbstsperrenden Transistor aufweist.

9. Schaltung nach Anspruch 8, bei der der selbstleitende Transistor ein GaN HEMT-Bauelement aufweist und der zweite Laststreckenanschluss des selbstleitenden Transistors ein Source des GaN HEMT aufweist.

10. Schaltung nach Anspruch 9, bei der der selbstsperrende Transistor einen Anreicherungs-MOSFET-Transistor aufweist, wobei der erste Laststreckenanschluss des Anreicherungs-MOSFET-Transistors ein Drain des Anreicherungs-MOSFET-Transistors und der zweite Laststreckenanschluss des Anreicherungs-MOSFET-Transistors ein Source des Anreicherungs-MOSFET-Transistors aufweist.

11. Schaltung nach einem der Ansprüche 1 bis 10, bei der: der erste Treiber erste Netzanschlüsse umfasst, die zwischen einen ersten Referenzspannungsknoten und den zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt sind; und der zweite Treiber zweite Netzanschlüsse umfasst, die zwischen den zweiten Laststreckenanschluss des selbstsperrenden Transistors und einem zweiten Referenzspannungsknoten gekoppelt sind.

12. Verfahren zum Betreiben eines Schalters, der einen in Reihe zu einem selbstsperrenden Transistor geschalteten selbstleitenden Transistor aufweist, wobei das Verfahren aufweist: in einem Kaskodemodus, Ausgeben eines ersten Schaltsignals an einen Steuerknoten des selbstsperrenden Transistors unter Verwendung einer ersten Treiberschaltung und Einschalten des selbstleitenden Transistors, der einen Steuerknoten aufweist, der mit einem Ausgang einer zweiten Treiberschaltung gekoppelt ist; und in einem Direktansteuermodus, Ausgeben eines zweiten Schaltsignals an den Steuerknoten des selbstleitenden Transistors unter Verwendung der zweiten Treiberschaltung, und Ausgeben einer ersten konstanten Spannung an den Steuerknoten des selbstsperrenden Transistors unter Verwendung der ersten Treiberschaltung und Öffnen des Schalters.

13. Verfahren nach Anspruch 12, das weiterhin aufweist: im Kaskodemodus, Versetzen einer zweiten Treiberschaltung, die mit dem Steuerknoten des selbstleitenden Transistors gekoppelt ist, in einen Zustand mit hoher Ausgangsimpedanz, und Schließen eines Schalters, der zwischen den Steuerknoten des

selbstleitenden Transistors und einem Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist.

14. Verfahren nach Anspruch 13, bei der der selbstsperrende Transistor jeweils FET-Transistoren umfasst und der Laststreckenanschluss des selbstsperrenden Transistors eine Source des selbstsperrenden Transistors umfasst.

15. Verfahren nach einem der Ansprüche 12 bis 14, bei dem im Kaskodemodus der Schalter den Steuerknoten des selbstleitenden Transistors mit einem Sourceanschluss des selbstsperrenden Transistors koppelt.

16. Verfahren nach einem der Ansprüche 12 bis 15, bei dem der selbstsperrende Transistor einen Anreicherungs-MOSFET und der selbstleitende Transistor einen GaN HEMT umfasst.

17. Verfahren nach einem der Ansprüche 12 bis 16, das weiterhin das Anlegen einer ersten Versorgungsspannung zwischen den Netzanschlüssen der ersten Treiberschaltung und das Anlegen einer zweiten Versorgungsspannung zwischen den Netzanschlüssen der zweiten Treiberschaltung aufweist.

18. Verfahren nach Anspruch 17, bei dem das Anlegen der ersten Versorgungsspannung das Anlegen eines ersten Leistungsversorgungsreferenzknotens an einen Pluspol der ersten Treiberschaltung und das Koppeln eines Lastanschlusses des selbstsperrenden Transistors mit einem Minuspol der ersten Treiberschaltung aufweist.

19. Verfahren nach Anspruch 17, bei dem das Anlegen der zweiten Versorgungsspannung das Anlegen eines zweiten Leistungsversorgungsreferenzknotens an einen Minuspol der zweiten Treiberschaltung und das Koppeln eines Lastanschlusses des selbstleitenden Transistors mit einem Pluspol der zweiten Treiberschaltung aufweist.

20. Getaktete Leistungsversorgung, die aufweist: mehrere zusammengesetzte Schalt-Schaltungen, wobei die mehreren zusammengesetzten Schalt-Schaltungen eine erste zusammengesetzte Schalt-Schaltung umfassen, die in Reihe mit einer zweiten zusammengesetzten Schalt-Schaltung gekoppelt ist, um eine erste Reihenkombination zu bilden, wobei jeder der mehreren zusammengesetzten Schalt-Schaltungen aufweist:

einen selbstleitenden Transistor;

einen selbstsperrenden Transistor mit einem ersten Laststreckenanschluss, der mit einem zweiten Laststreckenanschluss des selbstleitenden Transistors gekoppelt ist,

einen ersten Treiber, der einen ersten Ausgang aufweist, der mit einem Steuerknoten des selbstsperren-

den Transistors gekoppelt ist, wobei der erste Treiber dazu ausgebildet ist, in einem Kaskodemodus ein erstes Schaltsignals am ersten Ausgang auszugeben und in einem Direktansteuermodus eine erste konstante Spannung am ersten Ausgang auszugeben; und

einen zweiten Treiber, der einen zweiten Ausgang aufweist, der mit einem Steuerknoten des selbstleitenden Transistors gekoppelt ist, wobei der zweite Treiber dazu ausgebildet ist, im Direktansteuermodus ein zweites Schaltsignals am zweiten Ausgang auszugeben, wobei jeder der mehreren zusammengesetzten Schalt-Schaltungen dazu ausgebildet ist im Kaskodenmodus den Steuerknoten des selbstleitenden Transistors mit einer Source des selbstsperrenden Transistors zu verbinden.

21. Schaltmodus-Leistungsversorgung nach Anspruch 20, bei der:

der zweite Treiber weiterhin dazu ausgebildet ist, im Kaskodemodus eine hohe Impedanz am zweiten Ausgang zu haben; und

jeder der mehreren zusammengesetzten Schalt-Schaltungen ferner einen Schalter umfasst, der zwischen den Steuerknoten des selbstleitenden Transistors und einem zweiten Laststreckenanschluss des selbstsperrenden Transistors gekoppelt ist, wobei der Schalter dazu ausgebildet ist, im Direktansteuermodus geöffnet und im Kaskodemodus geschlossen zu sein.

Es folgen 8 Seiten Zeichnungen

## Anhängende Zeichnungen

**FIG. 1a****FIG. 1b**

**FIG. 2a**

**FIG. 2b**

**FIG. 2c****FIG. 3**

**FIG. 4a****FIG. 4b**

**FIG. 4c**

**FIG. 5**

FIG. 6

FIG. 7