(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-283269

(P2010-283269A)

(43) 公開日 平成22年12月16日(2010.12.16)

(51) Int.Cl.

|                    |                  |

|--------------------|------------------|

| <b>H01L 27/04</b>  | <b>(2006.01)</b> |

| <b>H01L 21/822</b> | <b>(2006.01)</b> |

| <b>H01L 21/82</b>  | <b>(2006.01)</b> |

F 1

|            |

|------------|

| H01L 27/04 |

| H01L 21/82 |

| H01L 21/82 |

| H01L 27/04 |

テーマコード(参考)

|   |           |

|---|-----------|

| A | 5 F 0 3 8 |

| L | 5 F 0 6 4 |

| B |           |

| D |           |

審査請求 未請求 請求項の数 10 O L (全 18 頁)

(21) 出願番号

特願2009-137210 (P2009-137210)

(22) 出願日

平成21年6月8日(2009.6.8)

(71) 出願人

302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人

100102864

弁理士 工藤 実

(72) 発明者

桜林 太郎

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

F ターム(参考) 5F038 BH18 CA02 CA05 CA09 CA17

CD02 CD03 CD04 CD16 DF08

EZ20

5F064 AA05 BB07 BB37 CC12 DD02

DD07 DD13 DD19 DD24 DD34

EE12 EE22 EE25 EE27 EE52

FF07 FF08 FF24 FF36 HH06

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】半導体装置のレイアウトの自由度を向上させる。

【解決手段】本発明による半導体装置は、第1行において、行方向に連続的に配置される第1電源供給セル20及び複数の第1セル10と、第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セル10とを具備する。第1電源供給セル20は、行方向に直交する第1電源配線62に接続され、第1電源配線62から供給される電圧に応じた電源電圧を、複数の第1セル10及び複数の第2セル10に供給する。第2行において、第1行に配置された第1電源供給セル20に隣接する第2セルと第1電源配線62とは、直接接続されず第1行に配置された第1電源供給セル20を介して接続される。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

第1行において、行方向に連続的に配置される第1電源供給セル及び複数の第1セルと、前記第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セルと

を具備し、

前記第1電源供給セルは、行方向に直交する第1電源配線に接続され、前記第1電源配線から供給される電圧に応じた電源電圧を、前記複数の第1セル及び前記複数の第2セルに供給し、

前記第2行において、前記第1電源供給セルに隣接する第2セルと前記第1電源配線とは、直接接続されず前記第1電源供給セルを介して接続される

半導体装置。

**【請求項 2】**

請求項1に記載の半導体装置において、

前記第2行において、前記第1電源供給セルに隣接する第2セルは、プリミティブセルである

半導体装置。

**【請求項 3】**

請求項1に記載の半導体装置において、

前記第2行において、前記第1電源供給セルに隣接する第2セルは、スタンダードセルである。

半導体装置。

**【請求項 4】**

請求項1から3のいずれか1項に記載の半導体装置において、

前記複数の第1セルと前記複数の第2セルは共通する第1ウェルを介して隣接し、

前記第1電源供給セルは、前記第1電源配線と前記第1ウェルとの間を電気的に接続する拡散層を備える

半導体装置。

**【請求項 5】**

請求項4に記載の半導体装置において、

前記第1電源供給セルは、

セルハイト方向に対し上部領域と下部領域のそれぞれに形成され、前記第1ウェルに隣接する第2ウェルを更に備え、

前記拡散層は、前記前記第2ウェル上に設けられる

半導体装置。

**【請求項 6】**

請求項1から5のいずれか1項に記載の半導体装置において、

前記第1電源配線に直交する第2電源配線を更に具備し、

前記第1電源供給セルは、前記第1電源配線から供給される電圧に応じた電源電圧を、前記第2配線を介して前記複数の第1セル及び前記複数の第2セルに供給する電源スイッチを備え、

前記電源スイッチは、制御信号に応じて前記電源電圧の供給及び供給停止を制御する半導体装置。

**【請求項 7】**

請求項5に記載の半導体装置において、

前記第1電源配線に直交する第2電源配線を更に具備し、

前記第1電源供給セルは、前記第1電源配線から供給される電圧に応じた電源電圧を、前記第2配線を介して前記複数の第1セル及び前記複数の第2セルに供給する電源スイッチを備え、

前記第1電源供給セルにおいて、セルハイト方向に対し上部領域と下部領域に形成され

10

20

30

40

50

た第1導電型のウェルは相互にブリッジ構造によって接続され、

前記電源スイッチは、前記ブリッジ構造上に形成される

半導体装置。

**【請求項8】**

請求項1から7のいずれか1項に記載の半導体装置において、

前記第2行には、第2電源供給セルが配置され、

前記第2電源供給セルは、前記第1電源配線に平行して設けられた第3電源配線に接続され、前記第3電源配線から供給される電圧に応じた電源電圧を、前記複数の第1セル及び前記複数の第2セルに供給し、

前記第1行において、前記第2電源供給セルに隣接する第1セルと前記第3電源配線とは、直接接続されず前記第2電源供給セルを介して接続される

半導体装置。 10

**【請求項9】**

請求項1から8のいずれか1項に記載の半導体装置において、

前記第2行に隣接する第3行において、行方向に連続的に配置される第3電源供給セルと複数の第3セルと、

前記第2行において、行方向に連続的に配置され、前記第3行に隣接する複数の第4セルと

を更に具備し、

前記第3電源供給セルは、前記第1電源配線に接続され、前記第1電源配線から供給される電圧に応じた電源電圧を、前記複数の第4セル及び前記複数の第3セルに供給し、

前記第2行において、前記第1電源供給セル及び前記第3電源供給セルに隣接する第2セル及び第4セルと前記第1電源配線とは、直接接続されず前記第1電源供給セルを介して接続される

半導体装置。 20

**【請求項10】**

請求項9に記載の半導体装置において、

前記複数の第4セルと前記複数の第3セルは共通する第3ウェルを介して隣接し、

前記第3電源供給セルは、前記第1電源配線と前記第3ウェルとの間を電気的に接続する拡散層を備える

半導体装置。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置に関し、特に行(row)内のセルに対して電源電圧を供給する電源供給セルを有する半導体装置に関する。 40

**【背景技術】**

**【0002】**

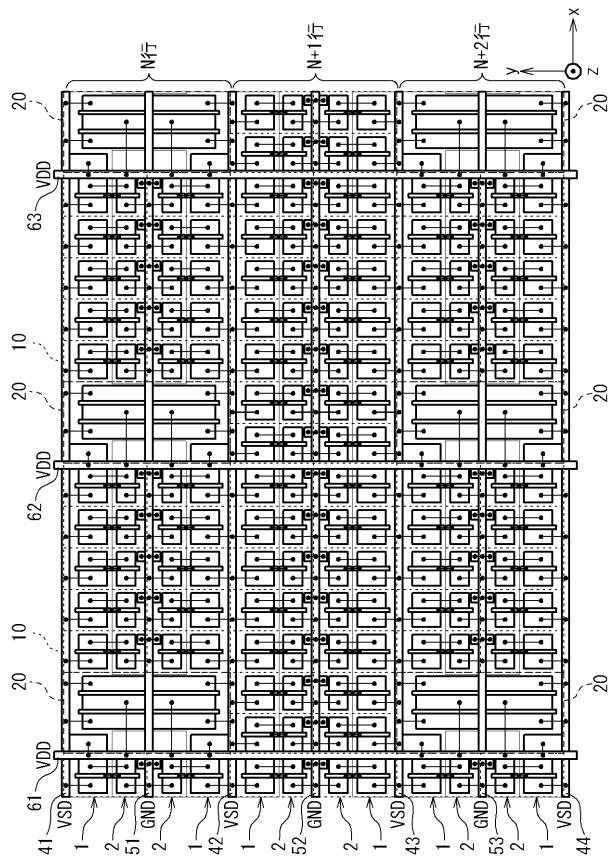

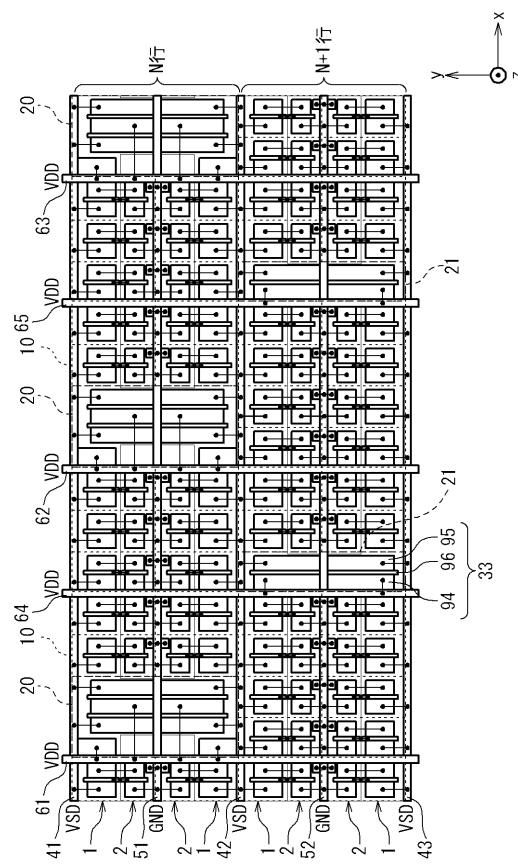

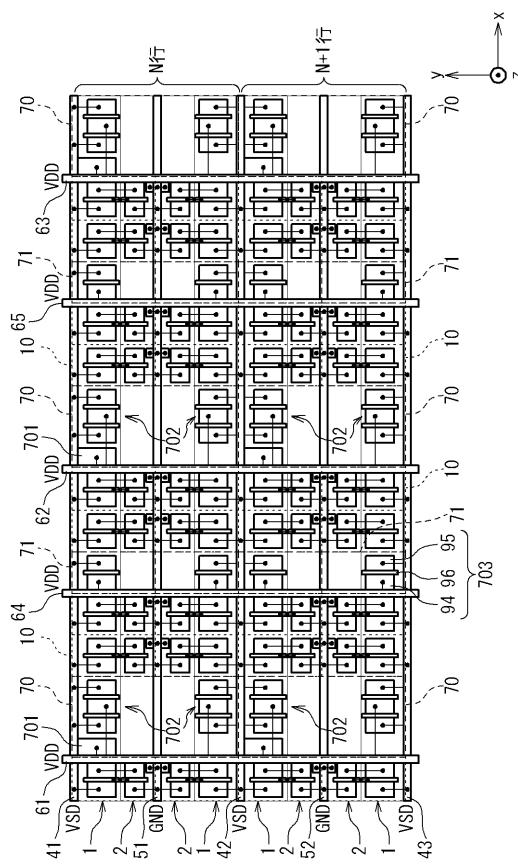

図1に示す半導体装置には、同一行に配置された複数のセル10に対して電源電圧を供給するセル70が設けられている。複数のセル10に対して必要な電源電圧を確保するため、セル70は、同一行において所定の間隔(ここでは距離B1、B2)で配置されることが必要である。 40

**【0003】**

ここで、図1に示す従来技術による半導体装置のレイアウト構造を説明する。図1を参照して、従来技術による半導体装置は、行方向(X方向)に延設される電源配線41～43、51、52と、電源配線41～43、51、52に沿って配置される複数のセル10(例えばプリミティブセルやスタンダードセル)と、電源配線41～43、51、52に垂直な方向(Y方向)に延設される電源配線61～63と、電源配線61～63のそれぞれに沿って配置される複数のセル70を具備する。 50

**【0004】**

セル70は、同一行において所定の間隔（距離B1）で配置され、同一行に配置されたセル10に対して電源電圧を供給する電源供給素子80を備える。通常、セル70は、電源配線61～63のそれぞれの近傍に配置される。電源供給素子80は、例えば、同一行内のセル10の基板（N型ウェル1）に対し電源配線61～63からの電源電圧VDDを供給するコンタクト（以下、ウェルコンと称す）を有する。あるいは、電源供給素子80は、電源配線61～63からの電源電圧VDDに応じた電源電圧VSDを電源配線41～43介してセル10に供給する電源スイッチを有する。電源スイッチは、図示しない制御信号に応じてセル10に対する電源電圧VSDの供給及び供給停止を制御する。

#### 【0005】

電源配線41～43には電源電圧VSDが供給され、電源配線51、52はGNDに接続される。複数のセル10は、それに設けられたコンタクトを介して、電源配線41～43のうち近接する電源配線から電源電圧VSDが供給される。又、複数のセル10、70は、電源配線51、52のうち近接する電源配線を介して接地される。尚、電源供給素子80は、ウェルコンと電源スイッチの両方を有していても構わない。

#### 【0006】

セル10は、電源配線41～43及び電源配線51、52のそれぞれから供給される電源電圧VSD及び接地電圧GNDに応じて動作する論理回路を有する。

#### 【0007】

セル10、セル70のそれぞれはN型ウェル1及びP型ウェル2を有する。セル10内のN型ウェル1は、同一行において当該セル10に隣接するセル10又はセル70内のN型ウェル1に接続される。同様に、セル10内のP型ウェル1は、同一行において当該セル10に隣接するセル10又はセル70内のP型ウェル1に接続される。これにより、同一行内でN型ウェル1及びP型ウェル2は連続して形成されることとなる。

#### 【0008】

上述のような電源供給を行なうセル70を有する半導体装置が、例えば、特開2008-103569に記載されている（特許文献1参照）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

【特許文献1】特開2008-103569

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

同一行におけるセル70同士の間隔（距離B1）は、半導体装置のプロセスの世代に応じて設定される電源供給素子80間の距離によって決定する。例えば、電源供給素子80がN型ウェル1に電源電圧VDDを供給するウェルコンである場合、電源供給素子80間の距離C1、C2は、プロセスに応じたラッチアップ基準に基づいて設定される。

#### 【0011】

セル10を配置可能な領域は、同一行におけるセル70間の距離B1、B2によって決まる。この距離B1、B2は上述のようにプロセスによって制約を受けるため、配置可能なセル10の数や大きさも同様に、プロセスに応じた制約を受けることになる。

#### 【0012】

一方、半導体装置の高集積化を目的として、チップ面積を増大せずに配置可能なセル10の数を増大したいという要求が高まっている。このため、プロセスに応じた制約を満足しながら、電源供給セル（セル70）間に配置可能なセル10の数を増加させることが求められている。又、同一行におけるセルの配置可能な領域が狭い場合、サイズの大きなセル10を配置できない場合がある。このため、同一行においてセルの配置可能な領域を拡大し、配置可能なセル10のサイズの自由度を向上させることが求められている。

#### 【課題を解決するための手段】

#### 【0013】

40

50

以下に、[発明を実施するための形態]で使用される番号・符号を括弧付きで用いて、[課題を解決するための手段]を説明する。この番号・符号は、[特許請求の範囲]の記載と[発明を実施するための形態]の記載との対応関係を明らかにするために付加されたものであるが、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

#### 【0014】

本発明による半導体装置は、第1行において、行方向に連続的に配置される第1電源供給セル(20)及び複数の第1セル(10)と、第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セル(10)とを具備する。第1電源供給セル(20)は、行方向に直交する第1電源配線(例えば62)に接続され、第1電源配線(例えば62)から供給される電圧に応じた電源電圧を、複数の第1セル(10)及び複数の第2セル(10)に供給する。第2行において、第1行に配置された第1電源供給セル(20)に隣接する第2セルと第1電源配線(例えば62)とは、直接接続されず第1行に配置された第1電源供給セル(20)を介して接続される。

10

#### 【発明の効果】

#### 【0015】

本発明によれば、半導体装置のレイアウトの自由度を向上させることができる。

#### 【図面の簡単な説明】

#### 【0016】

【図1】図1は、従来技術による半導体装置のレイアウト構造を示す平面図である。

20

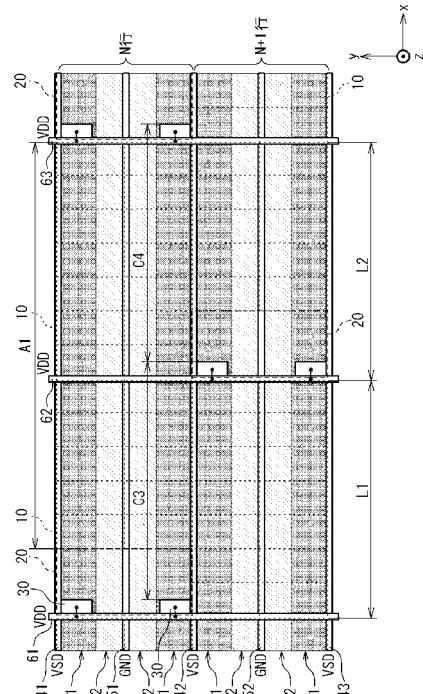

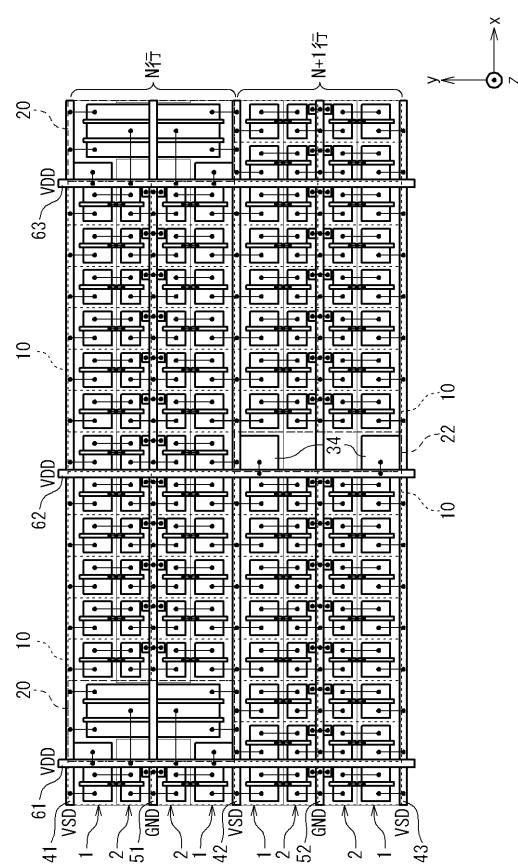

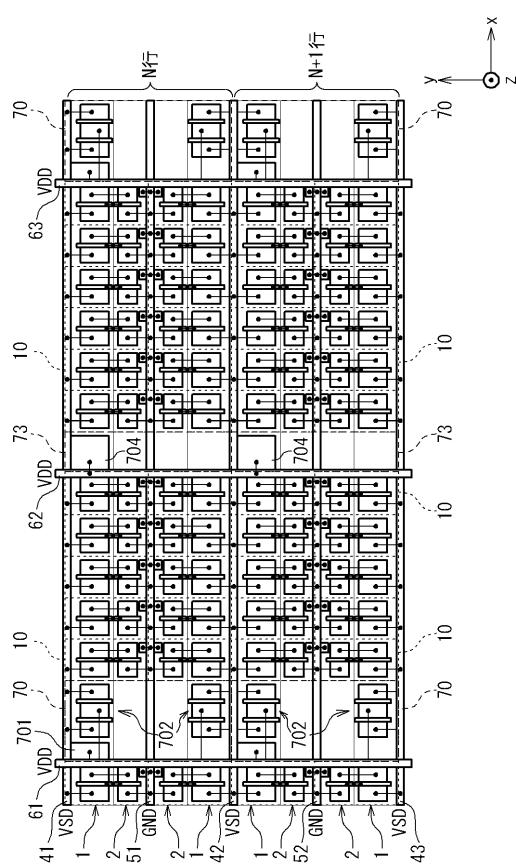

【図2】図2は、本発明による半導体装置の第1の実施の形態におけるレイアウト構造を示す平面図である。

【図3】図3は、本発明による半導体装置のレイアウト構造の第1実施例を示す平面図である。

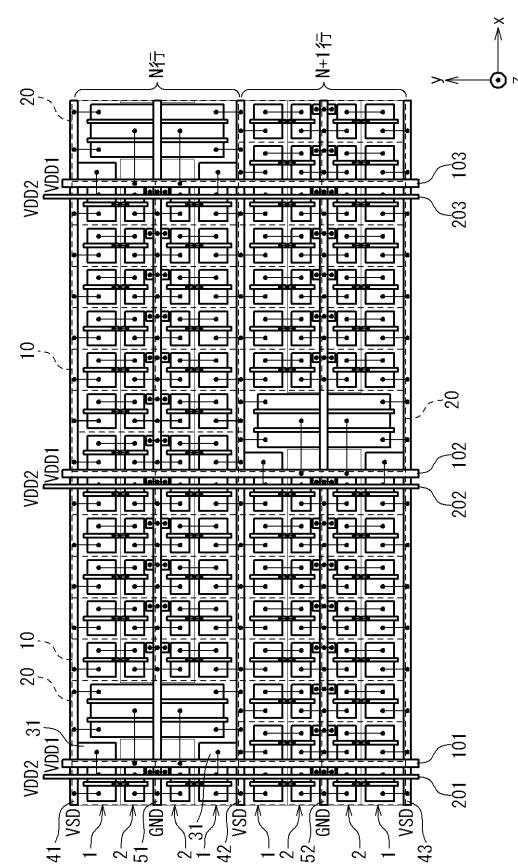

【図4】図4は、本発明による半導体装置のレイアウト構造の第2実施例を示す平面図である。

【図5】図5は、本発明による半導体装置のレイアウト構造の第3実施例を示す平面図である。

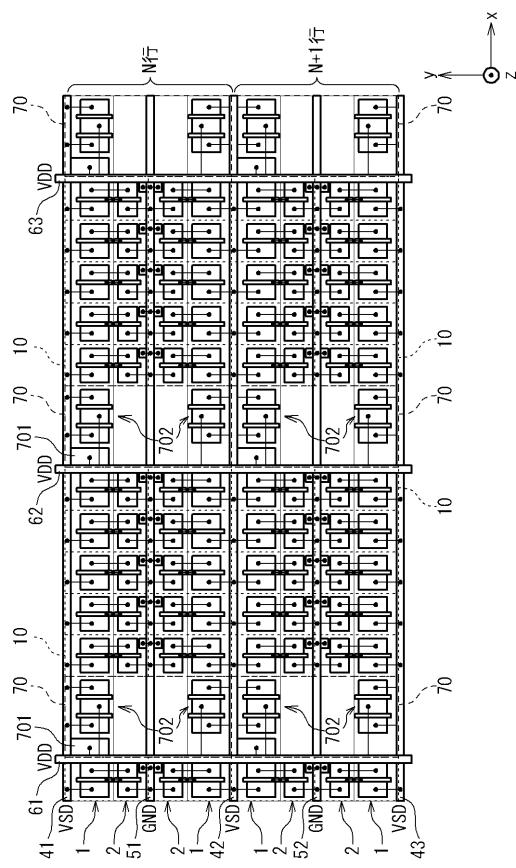

【図6】図6は、本発明による半導体装置のレイアウト構造の第4実施例を示す平面図である。

30

【図7】図7は、本発明による半導体装置の第1実施例に対する比較例を示す平面図である。

【図8】図8は、本発明による半導体装置の第2実施例に対する比較例を示す平面図である。

【図9】図9は、本発明による半導体装置の第3実施例に対する比較例を示す平面図である。

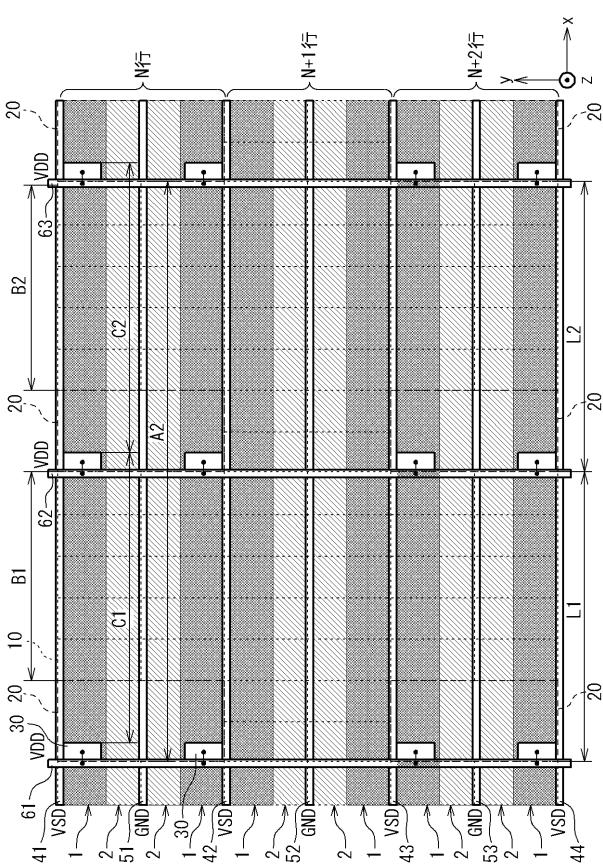

【図10】図10は、本発明による半導体装置の第2の実施の形態におけるレイアウト構造を示す平面図である。

【図11】図11は、本発明による半導体装置のレイアウト構造の第5実施例を示す平面図である。

40

#### 【発明を実施するための形態】

#### 【0017】

以下、添付図面を参照して、本発明による半導体装置、及びそのレイアウト方法の実施の形態を説明する。

#### 【0018】

##### 概要

電源配線(電源電圧VDD)を必要とする電源スイッチ素子とウェルコン(N型拡散層)は同じ位置に配置すると配線効率が良い。このため、従来からウェルコン及び電源スイッチを有するセル(セル70)をラッチアップ耐性に必要な間隔で配置していた。しかし、セル70のサイズは大きいため(例えばセル幅がプリミティブセルの約2倍)、サイズ

50

の大きいスタンダードセルの配置を阻害する原因となっていた。

【0019】

しかし、本発明では、行の境界でウェルが共有されていることに着目し、1つのウェルコンによって2つの行に共通のウェルに対して電源電圧を供給することで、行に配置する電源供給セルの数を減じることができる。すなわち、ウェルコン及び電源スイッチを有するセル（電源供給セル：セル20）を2つの行にわたり千鳥に配置することで、電源供給セルの間隔をウェルコンの間隔の2倍程度まで広げることができる。これにより、サイズの大きいスタンダードセルを配置する際の自由度が高まる。

【0020】

1. 第1の実施の形態

図2から図9を参照して、本発明による半導体装置の第1の実施の形態を説明する。図2は、本発明による半導体装置の第1の実施の形態におけるレイアウトを示す平面図である。図2を参照して、本実施の形態における半導体装置は、行方向（X方向）に延設される電源配線41～43、51、52と、電源配線41～43、51、52に沿って配置される複数のセル10（例えばプリミティブセルやスタンダードセル）と、電源配線41～43、51、52に垂直な方向（Y方向）に延設される電源配線61～63と、複数のセル10に電源電圧VDDを供給する複数のセル20（電源供給セル）を具備する。

10

【0021】

セル20は、電源配線61～63から供給される電源電圧VDDに応じた電源電圧を、セル10に対して供給する電源供給素子30を備える。電源供給素子30は、例えば、セル10、20の基板（N型ウェル1）に対し電源配線61～63からの電源電圧VDDを供給するコントラクト（以下、ウェルコンと称す）を有する。あるいは、電源供給素子30は、電源配線61～63からの電源電圧VDDに応じた電源電圧VSDを、電源配線41～43介してセル10に供給する電源スイッチを有する。電源スイッチは、図示しない制御信号に応じてセル10に対する電源電圧VSDの供給及び供給停止を制御する。尚、電源供給素子30は、ウェルコンと電源スイッチの両方を有していても構わない。

20

【0022】

セル10は、電源配線41～43及び電源配線51、52のそれぞれから供給される電源電圧VSD及び接地電圧GNDに応じて動作する論理回路（図示なし）を有する。

30

【0023】

セル20には、セルハイト方向（Y方向）に対して上部及び下部の領域、すなわち、他の行と隣接する領域にN型ウェル1が形成される。以下、上部領域に形成されるN型ウェル1をN型ウェル1（上段）と称し、下部領域に形成されるN型ウェル1をN型ウェル1（下段）と称す。又、セル20には、N型ウェル1（上段）とN型ウェル1（下段）に挟まれる領域にP型ウェル2が形成される。後述するが、N型ウェル1（上段）とN型ウェル1（下段）は、P型ウェル2を分断して相互に接続され、ブリッジ構造を形成しても良い。N型ウェル1（上段）及びN型ウェル1（下段）のそれぞれには、電源供給素子30が設けられる。

【0024】

セル10には、セルハイト方向（Y方向）に対して上部又は下部の領域にN型ウェル1が形成され、他方の領域にP型ウェル2が形成される。セル10は、隣接する他の行と、自身のN型ウェル1が接続するように配置される。本一例では、セル20のセルハイトの半分のセル10が、同行において2つのセル20の間に配置される。この際、N型ウェル1が行の境に位置し、P型ウェル2同士が接続されるように、2つのセル10がセルハイト方向（Y方向）に連結されて配置される。

40

【0025】

以上のようなセル10、20を配置することで、セル10内のN型ウェル1は、同一行において当該セル10に隣接するセル10又はセル20内のN型ウェル1に接続される。同様に、セル10内のP型ウェル1は、同一行において当該セル10に隣接するセル10又はセル20内のP型ウェル1に接続される。これにより、同一行内でN型ウェル1及び

50

P型ウェル2は、それぞれ連続して形成されることとなる。又、行と他の行との境（例えば、N行とN+1行の境、Nは自然数）付近の領域には、両行ともN型ウェル1が形成されている。このため、隣接する行との他の行との間（N行とN+1行との間）においてN型ウェル1は連続して形成されることとなる。

【0026】

電源配線41～43、51、52は、列方向（Y方向）上から、電源配線41、51、42、52、43の順で配置される。電源配線41～43には電源電圧VSDが供給され、電源配線51、52はGNDに接続される。複数のセル10、20には、それぞれに設けられたコンタクト（図示なし）を介して、電源配線41～43のうち近接する電源配線から電源電圧VSDが供給される。又、複数のセル10、20は、それぞれに設けられたコンタクト（図示なし）を介して、電源配線51、52のうち近接する電源配線を介して接地される。

10

【0027】

このような構成により、行の境界を介して接する2つのセル10は、行方向に延びる同じ電源配線に接続される。例えば、N行においてN+1行に隣接するセル10と、N+1行においてN行に隣接するセル10は、同じ電源配線42に接続される。

【0028】

本発明によるセル20には、セル20内のN型ウェル1（上段）とN型ウェル1（下段）のそれぞれに電源供給素子30が形成されている。以下、N型ウェル1（上段）に設けられた電源供給素子30を電源供給素子30（上段）と称し、N型ウェル1（下段）に設けられた電源供給素子30を電源供給素子30（下段）と称す。

20

【0029】

例えば、電源供給素子がN型ウェル1に電源電圧VDDを供給するウェルコンである場合、N行に設けられた電源供給素子30（下段）によって、N行におけるN型ウェル1（下段）のみならずN+1行のN型ウェル1（上段）にも電源電圧VDDを供給することができる。同様に、N+1行に設けられた電源供給素子30（上段）によって、N+1行のN型ウェル1（上段）のみならずN行のN型ウェル1（下段）にも電源電圧VDDを供給することができる。従って、本発明では、N行又はN+1行のどちらか一方にセル20を配置することで、N行とN+1行との境界領域に形成されたN型ウェル1に電源電圧VDDを供給することができる。

30

【0030】

あるいは、電源供給素子30が電源配線41～43に電源電圧VSDを供給する電源スイッチである場合、N行に配置されたセル20内の電源スイッチ（P型MOSトランジスタ32）と、N+1行に配置されたセル20内の電源スイッチ（P型MOSトランジスタ32）のどちらからでも、行の境界にある電源配線42に電源電圧VSDを供給することができる。

【0031】

以上のことから、本発明では、N行とN+1行のどちらか一方にセル20を配置することで行の境界付近のセル10に電源電圧を供給することができる。図2に示す一例では、電源配線61、63に接続するセル20は、隣接する2つの行（N行とN+1行）のうち、N行のみに配置され、電源配線62に接続するセル20は、隣接する2つの行（N行とN+1行）のうち、N+1行のみに配置される。この場合、電源配線61、63に接続するセル20に隣接する他の行のセルは、当該セル20を介して電源配線61、63に接続され、電源配線62に接続するセル20に隣接する他の行のセルは、当該セル20を介して電源配線62に接続されることとなる。このため、本発明ではセル20に隣接する位置にセル20を配置する必要がない。ここで、電源配線61～63は、行方向（Y方向）左から電源配線61、62、63の順で配置される。従って、本発明では、隣接する2つの行（N行とN+1行）において、セル20が千鳥配置となるようにレイアウトされる。

40

【0032】

N行に配置される2つのセル20は、それぞれ電源配線61、63から供給される電源

50

電圧 V D D に応じた電源電圧を複数のセル 1 0 に供給する。一方、N + 1 行に配置されるセル 2 0 は、電源配線 6 2 から供給される電源電圧 V D D に応じた電源電圧を複数のセル 1 0 に供給する。N 行において電源配線 6 1 と電源配線 6 3 との間に配置されたセル 1 0 は、N + 1 行におけるセル 2 0 から電源電圧が供給される。このため、プロセス等によって制約を受ける電源供給素子 3 0 間の距離は、N 行形成された電源供給素子 3 0 (下段) と N + 1 行に形成された電源供給素子 3 0 (上段) との間の距離 C 3 、C 4 となる。又、距離 C 3 、C 4 と距離 C 1 、C 2 は、ほぼ同じ長さである。すなわち、本発明のようなレイアウト構造に変更しても、制約条件を満足する距離が保持される。

#### 【 0 0 3 3 】

従って、本実施の形態における半導体装置では、N 行において電源配線 6 1 ~ 6 3 に対し 1 つおきにセル 2 0 を配置することができる。すなわち、電源配線 6 1 近傍のセル 2 0 から電源配線 6 3 近傍のセル 2 0 までの間 ( 距離 A 1 ) の領域に、セル 1 0 を配置することができる。この領域は、電源配線 6 3 近傍に電源供給セルを配置しない分だけ、図 1 に示すセル 1 0 の配置可能な領域よりも大きくなる。詳細には、電源配線 6 1 から電源配線 6 3 間での距離が、図 1 に示す半導体装置と同じ L 1 + L 2 である場合、N 行においてセル 1 0 の配置可能な領域の幅は、距離 L 1 + L 2 から 1 つのセル 1 0 のセル幅を減じた距離 A 1 となる。一方、図 1 に示す N 行におけるセル 1 0 の配置可能な領域の幅は、L 1 からセル 7 0 のセル幅を減じた距離 B 1 と、L 2 からセル 7 0 のセル幅を減じた距離 B 2 と和となる。すなわち、L 1 + L 2 から 2 つのセル 7 0 のセル幅を減じた距離 B 1 + B 2 < A 1 となる。

#### 【 0 0 3 4 】

以上のことから、本発明による半導体装置は、プロセスに応じた制約を満足する電源供給素子の間隔を保持したまま、電源供給セル ( セル 2 0 ) 間におけるセル 1 0 の配置可能領域を広げることができる。これにより、セル 1 0 の配置数を増加させることができるとなる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、T A T や面積効率が改善される。

#### 【 0 0 3 5 】

次に、図 3 から図 9 を参照して、第 1 の実施の形態における半導体装置の具体例を示す。以下では、通常モードと待機モードの切り替えに応じて電源の供給が制御される機能セルを有する半導体装置について説明する。ここで、通常モードとは、通常動作を実施している状態であり、待機モードとは、一部の機能セルを動作させない状態である。

#### 【 0 0 3 6 】

通常モードと待機モードの切り替えは、電源スイッチによって行なわれる。電源スイッチは、電源電圧 V D D に応じた電圧を電源電圧 V S D としてスタンダードセルに供給する。スタンダードセルは、電源電圧 V S D に応じて動作する。電源スイッチを用いる場合、電源スイッチが形成されたセル ( 電源スイッチセル ) の N 型ウェルに固定電圧 ( 電源電圧 V D D ) を供給する必要がある。又、電源電圧 V S D によって動作するスタンダードセルの N 型ウェルには、電源電圧 V S D を供給する場合と電源電圧 V D D を供給する場合がある。前者の場合、電源スイッチセルの N 型ウェルとスタンダードセルの N 型ウェルとの間に電位差が生じるため、電源スイッチセルとスタンダードセルとの間の距離を広げる必要がある。この場合、チップ面積は増大してしまう。後者の場合、N 型ウェルのラッチアップを回避するため、所定の間隔以内にウェルコンを配置する必要がある。この場合、ウェルコンを含むセルの間隔を狭くすると、当該セル間に配置可能なスタンダードセルの大きさや数が制限される。しかし、面積デメリットは後者の方が少ないため、本発明では後者が選択される。

#### 【 0 0 3 7 】

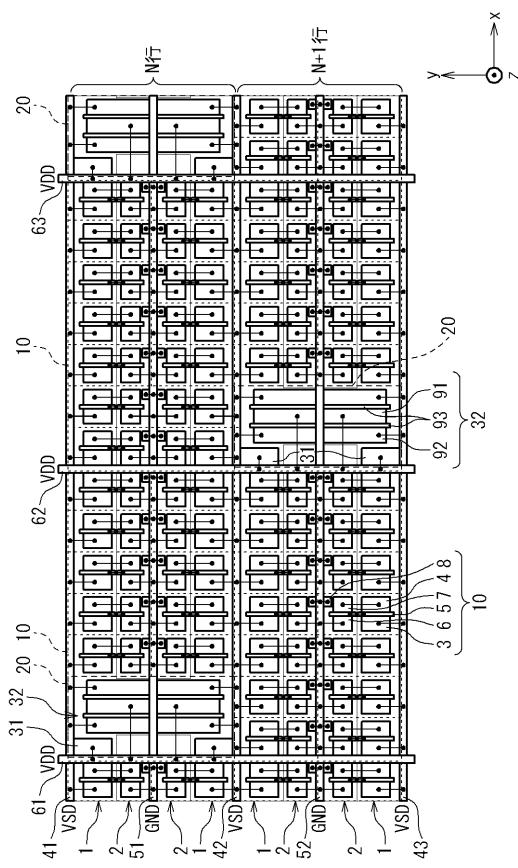

##### ( 第 1 実施例 )

図 3 は、第 1 の実施の形態における半導体装置のレイアウト構造の一例 ( 第 1 実施例 ) を示す平面図である。第 1 実施例におけるセル 2 0 は、電源供給素子 3 0 として、上述のウェルコンと電源スイッチとを有する。図 7 は、図 3 に示す半導体装置に対応する比較例

10

20

30

40

50

を示す平面図である。

【0038】

第1実施例では、行方向における電源スイッチの間隔とウェルコンの間隔の比が1対1である。又、本実施例(図3)における半導体装置の基本構造は、図2に示すレイアウトと同様である。例えば、電源配線41～43、51、52、61～63の配置やセル10、20の配置(配線間の距離等)は、同様であるので、その説明は省略する。

【0039】

図3を参照して、セル10は、N型ウェル1上に設けられたP型MOSトランジスタ11と、P型ウェル2上に設けられたN型MOSトランジスタ12とを備える。P型MOSトランジスタ11は、N型ウェル1上に設けられたP型拡散層3、4、及びゲート絶縁膜5によって形成される。N型MOSトランジスタ12はP型ウェル2上に設けられたN型拡散層6、7、及びゲート絶縁膜9によって形成される。

10

【0040】

セル10は、同一行においてセルハイト方向(Y方向)に対し上段と下段の2段に配置される。N行においてセルハイト方向(Y方向)上段に設置されたセル10の構造を説明する。上段に配置されたセル10のP型MOSトランジスタ11は、ソースとして機能するP型拡散層3が配線41に接続され、ドレインとして機能するP型拡散層4がN型拡散層7に接続される。又、N型MOSトランジスタ12は、ソースとして機能するN型拡散層6が配線51に接続され、ドレインとして機能するN型拡散層7がP型拡散層4に接続される。これにより、電源電圧VSDで駆動するインバータが形成される。N行においてセルハイト方向(Y方向)下段に設置されたセル10も同様に、ソースが電源配線42に接続されたP型MOSトランジスタ11とソースが電源配線51に接続されたN型MOSトランジスタ12とを有するインバータが形成される。

20

【0041】

セル20は、ウェルコンとして機能する2つのN型拡散層31と、電源スイッチとして機能するP型MOSトランジスタ32を有する。セル20におけるセルハイト方向(Y方向)に対する上部及び下部の領域には、N型ウェル1が形成される。以下、セル20の上部領域に形成されるN型ウェル1をN型ウェル1(上段)と称し、下部領域に形成されるN型ウェル1をN型ウェル1(下段)と称す。又、N型ウェル1(上段)とN型ウェル1(下段)に挟まれ、セル幅方向(X方向)の他のセルと隣接する領域に、P型ウェル2が形成される。更にN型ウェル1(上段)とN型ウェル1(下段)は、P型ウェル2を分断するように相互に接続され、ブリッジ構造を形成する。

30

【0042】

2つのN型拡散層31は、N型ウェル1(上段)とN型ウェル1(下段)のそれぞれに設けられる。又、2つのN型拡散層31は、図示しない上部配線を介して電源配線61に接続され、電源電圧VDDを自身が設けられたN型ウェル1に供給する。以下、N型ウェル1(上段)に設けられたN型拡散層31をN型拡散層31(上段)と称し、N型ウェル1(下段)に設けられたN型拡散層31をN型拡散層31(下段)と称す。

【0043】

N型ウェル1及びP型ウェル2は、上述のように行方向(X方向)に連続して形成され、行の境界においてN型ウェル1は列方向(Y方向)に連続して形成されている。又、本発明によるセル20には、上段と下段の両方にウェルコンとなるN型拡散層31が形成されている。このため、N行に設けられたN型拡散層31(下段)によって、N行におけるN型ウェル1(下段)のみならずN+1行のN型ウェル1(上段)にも電源電圧VDDを供給することができる。同様に、N+1行に設けられたN型拡散層31(上段)によって、N+1行のN型ウェル1(上段)のみならずN行のN型ウェル1(下段)にも電源電圧VDDを供給することができる。従って、本発明では、N行又はN+1行のどちらか一方にセル20を配置することで、N行とN+1行との境界領域に形成されたN型ウェル1に電源電圧VDDを供給することができる。例えば、電源配線61～63のそれぞれに接続されるセル20は、N行又はN+1行のどちらか一方に配置すればよい。

40

50

## 【0044】

次に、P型MOSトランジスタ32の構成の詳細を説明する。ここでは、N行において電源配線61に接続されたP型MOSトランジスタ32を一例に説明する。P型MOSトランジスタ32は、N型ウェル1によるブリッジ構造上に形成されるP型拡散層91、92及びゲート絶縁膜93を有する。P型拡散層91は、電源電圧VDDが供給される電源配線61に接続されソースとして機能する。P型拡散層92は、電源配線41、42に接続されドレインとして機能する。P型MOSトランジスタ32は、ゲート絶縁膜93に入力された制御信号(図示なし)に応じて電源電圧VDDに応じた電源電圧VSDを電源配線41、42に供給する。

## 【0045】

行の境界を介して接する2つのセル10は、行方向に延びる同じ電源配線に接続される。例えば、N行においてN+1行に隣接するセル10と、N+1行においてN行に隣接するセル10は、同じ電源配線42に接続される。電源配線42には、N行に配置されたセル20内の電源スイッチ(P型MOSトランジスタ32)と、N+1行に配置されたセル20内の電源スイッチ(P型MOSトランジスタ32)のどちらからでも電源電圧VSDを供給することができる。すなわち、本発明では、N行又はN+1行のどちらか一方にセル20を配置することで、N行とN+1行との境界領域に形成されたセル10に電源電圧VSDを供給することができる。例えば、電源配線61～63のそれぞれに接続されるセル20は、N行又はN+1行のどちらか一方に配置すればよい。

10

## 【0046】

以上のことから、本実施例では、N行に配置されたセル20のN型拡散層31(下段)と、N+1行に配置されたセル20のN型拡散層31(上段)との距離が、ラッチアップ耐性を確保するために必要なウェルコンの間隔以内となるように、N行及びN+1行にわたり、セル20が千鳥に配置される。図3に示す一例では、電源配線61、63に接続するセル20は、隣接する2つの行(N行とN+1行)のうち、N行のみに配置され、電源配線62に接続するセル20は、隣接する2つの行(N行とN+1行)のうち、N+1行のみに配置される。

20

## 【0047】

一方、図7に示す比較例では、ウェルコンとして機能するN型拡散層701が、セル70の上段のみに設けられている。この場合、N行におけるN型ウェル1(下段)には、N+1行に配置されたセル70によって電源電圧VDDが供給される。すなわち、ラッチアップ耐性を確保するために必要な間隔でN型ウェル1に電源電圧VDDを供給するためには、N行及びN+1行に当該間隔でセル70を配置する必要がある。

30

## 【0048】

本実施例では、セル20を千鳥に配置できるため、例えば、N行に配置されるセル20の間隔を比較例よりも長くすることができる。これにより、図7に示す比較例に比べてセル10の配置数を増加させることができるとなる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、TATや面積効率が改善される。

40

## 【0049】

又、図7に示す比較例では、セル70の上部及び下部の領域に分離したN型ウェル1のそれぞれに電源スイッチとして機能するP型MOSトランジスタ702が形成されている。一方、本発明によるセル20内のN型ウェル1(上段)及びN型ウェル1(下段)は、ブリッジ構造によって接続されているため、ラッチアップ耐性を高めることができる。

## 【0050】

(第2実施例)

図4は、第1の実施の形態における半導体装置のレイアウト構造の一例(第2実施例)を示す平面図である。第2実施例におけるセル20は、第1実施例と同じ構造である。図8は、図4に示す半導体装置に対応する比較例を示す平面図である。

## 【0051】

50

第1実施例の行方向における電源スイッチの間隔を1とした場合、第2実施例では、行方向における電源スイッチの間隔とウェルコンの間隔の比は0.5対1である。すなわち、第2実施例は、第1実施例に対して、電源強度を倍増させた半導体装置である。以下では、第1実施例と同様な構成は省略し、異なる構成を説明する。

#### 【0052】

図4を参照して、電源配線61～63の間隔は、第1実施例と同じであり、電源配線61と電源配線62の間に電源配線64が設けられ、電源配線62と電源配線63の間に電源配線65が設けられる。電源配線61～63には、N行に配置されたセル20が接続され、電源配線64、65には、N+1行に配置されたセル21が接続される。セル20、21以外の領域にはセル10が配置される。

10

#### 【0053】

セル20の構造は、第1実施例と同様である。すなわち、セル20は、上部及び下部の領域にウェルコンとして機能するN型拡散層31を有している。このため、ウェルコンの間隔を図8に示す比較例と同様な間隔としながら、隣接する2つの行の一方のみにセル20を配置することが可能となる。

#### 【0054】

セル21は、セルハイトがセル20と同じ大きさで、セル幅がセル10より小さい。セル21は、電源スイッチとして機能するP型MOSトランジスタ33を有する。以下、電源配線64に接続されたP型MOSトランジスタ33を一例に、その構造の詳細を説明する。P型MOSトランジスタ33は、N型ウェル1上に形成されるP型拡散層94、95及びゲート絶縁膜96を有する。P型拡散層94は、電源電圧VDDが供給される電源配線64に接続されソースとして機能する。P型拡散層95は、電源配線42、43に接続されドレインとして機能する。P型MOSトランジスタ33は、ゲート絶縁膜96に入力された制御信号(図示なし)に応じて電源電圧VDDに応じた電源電圧VSDを電源配線42、43に供給する。

20

#### 【0055】

ウェルコン及び電源スイッチを有するセル20を、電源配線61～63に接続する位置に配置し、電源スイッチのみを有するセル21を、追加された電源配線64、65に接続する位置に配置することで、電源スイッチの間隔をウェルコンの間隔の1/2倍とすることができる。又、セル21は、セル20と同様に、セルハイト方向(Y方向)上部及び下部の電源配線に対する電源電圧VSDを制御する。例えば、電源配線64に接続するセル21は、N行又はN+1行のどちらか一方に配置すればよい。従って、本実施例では、図4に示すようにN行及びN+1行においてセル20とセル21とを千鳥に配置することができる。

30

#### 【0056】

一方、図8に示す比較例では、ウェルコンとして機能するN型拡散層701が、セル70の上段のみに設けられている。この場合、N行におけるN型ウェル1(下段)には、N+1行に配置されたセル70によって電源電圧VDDが供給される必要がある。このため、ラッチアップ耐性を確保するために必要な間隔でN型ウェル1に電源電圧VDDを供給するためには、N行及びN+1行に当該間隔でセル70を配置する必要がある。

40

#### 【0057】

又、図8に示す比較例では、電源スイッチとして機能するP型MOSトランジスタ703のみを有するセル71が設けられているが、列方向(Y方向)に連続的に配置されている。例えば、電源配線64に接続されるセル71は隣接するN行及びN+1行に配置される。

#### 【0058】

本実施例では、セル20、21を千鳥に配置できるため、N行に配置されるセル20の間隔や、N+1行におけるセル21の間隔を比較例よりも長くすることができる。これにより、図8に示す比較例に比べてセル10の配置数を増加させることが可能となる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができる

50

ことから、設計が容易となり、TATや面積効率が改善される。

#### 【0059】

(第3実施例)

図5は、第1の実施の形態における半導体装置のレイアウト構造の一例(第3実施例)を示す平面図である。第3実施例におけるセル20は、第1実施例と同じ構造である。図9は、図5に示す半導体装置に対応する比較例を示す平面図である。

#### 【0060】

第1実施例の行方向における電源スイッチの間隔を1とした場合、第3実施例では、行方向における電源スイッチの間隔とウェルコンの間隔の比は2.1対1である。すなわち、第3実施例は、第1実施例に対して、電源強度を半減させた半導体装置である。以下では、第1実施例と同様な構成は省略し、異なる構成を説明する。

10

#### 【0061】

図5を参照して、電源配線61、63には、N行に配置されたセル20が接続され、電源配線63には、N+1行に配置されたセル22が接続される。セル20、22以外の領域にはセル10が配置される。

#### 【0062】

セル20の構造は、第1実施例と同様である。すなわち、セル20は、上部及び下部の領域にウェルコンとして機能するN型拡散層31を有している。このため、ウェルコンの間隔を図9に示す比較例と同様な間隔としながら、隣接する2つの行の一方のみにセル20を配置することが可能となる。

20

#### 【0063】

セル22は、セルハイトがセル20と同じ大きさで、セル幅がセル10より小さい。セル22は、ウェルコンとして機能する2つのN型拡散層34を有する。詳細には、セル22は、セルハイト方向(Y方向)に対して上部と下部の領域のそれぞれにN型ウェル1を有し、N型ウェル間にP型ウェル2を有する。2つのN型拡散層34は、上部及び下部のN型ウェル1上に設けられ、それぞれ電源配線62に接続される。

#### 【0064】

電源スイッチを有するセル20を電源配線61、63に接続する位置に配置し、ウェルコンのみを有するセル22を電源配線62に接続する位置に配置することで、電源スイッチの間隔を、ウェルコンの間隔の約2倍にすることができます。又、セル22は、セル20と同様に、セルハイト方向(Y方向)上部及び下部にウェルコンとなるN型拡散層34を有している。このため、セル22は、N行又はN+1行のどちらか一方に配置すればよい。従って、本実施例では、図5に示すようにN行及びN+1行においてセル20とセル22とを千鳥に配置することができる。

30

#### 【0065】

一方、図9に示す比較例では、ウェルコンとして機能するN型拡散層701、704がそれぞれセル70、73の上段のみに設けられている。この場合、N行におけるN型ウェル1(下段)には、N+1行に配置されたセル70、又はセル73によって電源電圧VDDが供給される必要がある。このため、ラッチアップ耐性を確保するために必要な間隔でN型ウェル1に電源電圧VDDを供給するためには、N行及びN+1行に当該間隔でセル70を配置する必要がある。

40

#### 【0066】

本実施例では、セル20、22を千鳥に配置できるため、N行に配置されるセル20の間隔や、N+1行におけるセル22の間隔を比較例よりも長くすることができる。これにより、図9に示す比較例に比べてセル10の配置数を増加させることが可能となる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、TATや面積効率が改善される。

#### 【0067】

(第4実施例)

図6は、第1の実施の形態における半導体装置のレイアウト構造の一例(第4実施例)

50

を示す平面図である。第4実施例におけるセル20は、第1実施例と同じ構造である。

【0068】

第1から第3実施例では、電源スイッチセル20の基板電位とソース電位として共通の電源電位VDDが供給されたが、第4実施例では、ソース電位（電源電圧VDD1）とは異なる固定電位（電源電圧VDD2）が基板電位として供給される。その他の構成は、第1実施例と同様である。

【0069】

第4実施例における半導体装置は、第1実施例における電源配線61に替えて、電源配線101、201を備える。同様に電源配線62に替えて電源配線102、202を、電源配線63に替えて電源配線103、203を備える。電源配線101～103には電源電圧VDD1が供給され、セル20内のP型MOSトランジスタ32のソースに接続される。P型MOSトランジスタ32は、電源電圧VDD1に応じた電源電圧VSDをセル10に供給する。電源配線201～203には電源電圧VDD2が供給され、セル20のN型拡散層31に接続される。N型ウェル1の電位は、N型拡散層31を介して供給される電源電圧VDD2に固定される。

10

【0070】

セル20の配置は、第1実施例と同様に千鳥に配置されているため、N行に配置されるセル20の間隔や、N+1行におけるセル22の間隔を比較例よりも長くすることができる。これにより、図7に示す比較例に比べてセル10の配置数を増加させることができる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、TATや面積効率が改善される。

20

【0071】

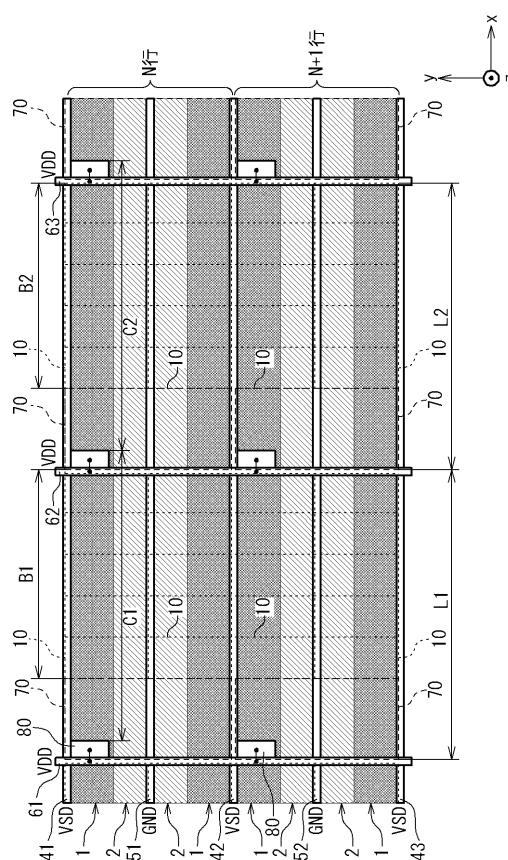

## 2. 第2の実施の形態

図10及び図11を参照して、本発明による半導体装置の第2の実施の形態を説明する。図10は、本発明による半導体装置の第2の実施の形態におけるレイアウトを示す平面図である。第1の実施の形態では、セル20がN行及びN+1行にわたり千鳥に配置されていたが、第2の実施の形態では、隣接する2行（N行、N+1行、Nは自然数）のうち、セル20を配置する行（N行）と配置しない行（N+1）とが交互に配置される。すなわち、隔行毎にセル20を配置する。

30

【0072】

図10を参照して、本実施の形態における半導体装置は、行方向（X方向）に延設される電源配線41～44、51～53と、電源配線41～44、51～53に沿って配置される複数のセル10（例えばプリミティブセルやスタンダードセル）と、電源配線41～44、51～53に垂直な方向（Y方向）に延設される電源配線61～63と、複数のセル10に電源電圧VDDを供給する複数のセル20を具備する。

【0073】

セル20、セル10の構成は、第1の実施の形態と同様である。セル20のセルハイト方向（Y方向）に対して上部及び下部の領域に電源供給素子30が配置されているため、セル20が配置された行の列方向（Y方向）に対して上段及び下段の行のN型ウェル1に対して電源電圧を供給することができる。このため、N行及びN+2行に配置されたセル20によって、N+1行に形成されたN型ウェル1に電源電圧が供給されることとなる。

40

【0074】

N行に配置される3つのセル20は、それぞれ電源配線61～63から供給される電源電圧VDDに応じた電源電圧を複数のセル10に供給する。同様に、N+2行に配置される3つのセル20は、それぞれ電源配線61～63から供給される電源電圧VDDに応じた電源電圧を複数のセル10に供給する。N+1行に配置されたセル10は、N行及びN+2行におけるセル20から電源電圧が供給される。このため、プロセス等によって制約を受ける電源供給素子30間の距離は、N行又はN+2行における2つのセル20内の電源供給素子30間の距離C1、C2となる。この距離C1、C2がラッチアップ耐性を維持できる距離内であるように、セル20が配置される。

50

## 【0075】

本実施の形態における半導体装置では、セル20が配置されるN行、N+2行では、セル10を配置する領域が、プロセスに応じた距離内（ここでは距離B1、B2内）に制約されるが、N+1行では、電源を供給するためのセル20が配置されないため、セル10の配置可能な領域が、距離A2の範囲に大きく広がる。詳細には、電源配線61から電源配線63間での距離が、図1に示す半導体装置と同じL1+L2である場合、N行においてセル10の配置可能な領域の幅は、距離L1+L2から1つのセル10のセル幅を減じた距離C3となる。一方、図10に示すN+1行におけるセル10の配置可能な領域の幅は、L1+L2=A2となる。すなわち、N+1行の全ての領域にセル10を配置することができる。

10

## 【0076】

以上のことから、本実施の形態による半導体装置は、プロセスに応じた制約を満足する電源供給素子の間隔を保持したまま、セル10の配置可能領域を広げることができる。これにより、セル10の配置数を増加させることが可能となる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、TATや面積効率が改善される。

20

## 【0077】

次に、図11を参照して、第2の実施の形態における半導体装置の具体例を示す。以下では、第1～第4実施例と同様に通常モードと待機モードの切り替えに応じて電源の供給が制御される機能セルを有する半導体装置について説明する。

30

## 【0078】

## (第5実施例)

図11は、第2の実施の形態における半導体装置のレイアウト構造の一例（第5実施例）を示す平面図である。第5実施例におけるセル20は、第1実施例と同じ構造である。

## 【0079】

第5実施例では、行方向における電源スイッチの間隔とウェルコンの間隔の比が1対1である。又、本実施例（図11）における半導体装置の基本構造は、図10に示すレイアウトと同様である。例えば、電源配線41～43、51～53、61～63の配置やセル10、20の配置（配線間の距離等）は、同様である。すなわち、電源配線61～63には、N行及びN+2行に配置されるセル20が接続される。

30

## 【0080】

N+1行におけるN型ウェル1（上段）には、N行におけるN型拡散層31を介して電源電圧VDDが供給され、N+1行におけるN型ウェル1（下段）には、N+1行におけるN型拡散層31を介して電源電圧VDDが供給される。又、N行とN+1行の境に配置された電源配線42には、N行に配置されたセル20内のP型MOSトランジスタ32によって電源電圧VSDが供給され、N+1行とN+2行の境に配置された電源配線43には、N+2行に配置されたセル20内のP型MOSトランジスタ32によって電源電圧VSDが供給される。

40

## 【0081】

本実施例では、セル20が配置された行（N行及びN+2行）は挟まれた行（N+1行）にセル20を配置する必要がないため、当該行（N+1行）では、セル10を自由に配置することができる。これにより、従来の電源スイッチを有する半導体装置に比べて、セル10の配置数を増加させることができるとなる。又、配置可能な領域が広がるため、様々な大きさのスタンダードセルを配置することができることから、設計が容易となり、TATや面積効率が改善される。

## 【0082】

本発明によれば、リーク電流を抑制するため電源の供給の制御が可能な電源スイッチを有する半導体装置の製造に際し、セル10の配置数又は配置の自由度を向上させるようにレイアウトすることができる。尚、上述の半導体装置のレイアウトは、コンピュータを用いてレイアウトプログラムを実行することで実現される。

50

## 【0083】

以上、本発明の実施の形態を詳述してきたが、具体的な構成は上記実施の形態に限られるものではなく、本発明の要旨を逸脱しない範囲の変更があっても本発明に含まれる。第1及び第2の実施の形態では、N行～N+1行又はN行～N+2行のレイアウトのみを示したがこれに限らず、通常、図面に示されたパターンが列方向繰り返されてレイアウトされる。又、第1～第5実施例は、技術的に矛盾がない範囲内で組み合せて適用され得る。

## 【0084】

又、上述の実施例では、電源電圧VDDに応じた電源電圧の供給を制御するセル20について説明したが、GND電位の供給を制御するセルにも適用できる。この場合、N型ウェル1、N型拡散層31、P型MOSトランジスタ32をそれぞれP型ウェル、P型拡散層、N型MOSトランジスタに読み替えることで実現できる。

10

20

## 【符号の説明】

## 【0085】

1 : N型ウェル

2 : P型ウェル

3、4、91、92、94、95 : P型拡散層

5、93、96 : ゲート絶縁膜

6、7、31、34 : N型拡散層

10 : セル

11、32、33 : Pチャネル型MOSトランジスタ

12 : Nチャネル型MOSトランジスタ

20 : セル

41～44、51～53、61～65、101～103、201～203 : 電源配線

【図1】

【図3】

【 図 4 】

【図5】

【 四 6 】

【図7】

【 図 8 】

【図9】

【 図 1 0 】

【図 11】