(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6224150号

(P6224150)

(45) 発行日 平成29年11月1日(2017.11.1)

(24) 登録日 平成29年10月13日(2017.10.13)

(51) Int.Cl.

F 1

G09G 3/3233 (2016.01)

G09G 3/3233

G09G 3/20 (2006.01)

G09G 3/20 624 B

H01L 51/50 (2006.01)

G09G 3/20 642 A

G09G 3/20 641 D

G09G 3/20 611 A

請求項の数 5 (全 54 頁) 最終頁に続く

(21) 出願番号

特願2016-59929 (P2016-59929)

(22) 出願日

平成28年3月24日 (2016.3.24)

(62) 分割の表示

特願2015-85898 (P2015-85898)

の分割

原出願日

平成22年2月22日 (2010.2.22)

(65) 公開番号

特開2016-153903 (P2016-153903A)

(43) 公開日

平成28年8月25日 (2016.8.25)

審査請求日

平成28年4月15日 (2016.4.15)

(31) 優先権主張番号

特願2009-45603 (P2009-45603)

(32) 優先日

平成21年2月27日 (2009.2.27)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】半導体装置、表示モジュール、電子機器

(57) 【特許請求の範囲】

【請求項 1】

トランジスタの移動度およびしきい値電圧のばらつきの影響を低減することができる機能を有する半導体装置であって、

発光素子と、

前記トランジスタと、

第1の容量素子と、

第2の容量素子と、

第3の容量素子と、

第1の配線と、

第2の配線と、

第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、

を有し、

前記第1の配線は、前記トランジスタを介して、前記発光素子に電流を供給することができる機能を有し、

前記第2の配線は、前記第2の容量素子および前記第3の容量素子に電圧を供給することができる機能を有し、

10

20

前記第3の配線は、映像信号を前記第1のスイッチに供給することができる機能を有し

前記トランジスタのゲートは、前記第1の容量素子の第1の端子と直接接続され、

前記第1のスイッチの第1の端子は、前記第3の配線と直接接続され、

前記第1のスイッチの第2の端子は、前記第1の容量素子の第2の端子と直接接続され

前記トランジスタのソースまたはドレインの一方は、前記第2のスイッチの第1の端子

と直接接続され、

前記第2のスイッチの第2の端子は、前記発光素子と直接接続され、

前記トランジスタのソースまたはドレインの一方は、前記第2の容量素子の第1の端子

と直接接続され、

前記トランジスタのソースまたはドレインの他方は、前記第1の配線と直接接続され、

前記第3のスイッチの第1の端子は、前記トランジスタのソースまたはドレインの他方

と直接接続され、

前記第3のスイッチの第2の端子は、前記第1の容量素子の第2の端子と直接接続され

前記第2の容量素子の第2の端子は、前記第2の配線と直接接続され、

前記第3の容量素子の第1の端子は、前記第1の容量素子の第2の端子と直接接続され

前記第3の容量素子の第2の端子は、前記第2の配線と直接接続されていることを特徴

とする半導体装置。

**【請求項2】**

請求項1において、

前記トランジスタは、Pチャネル型であることを特徴とする半導体装置。

**【請求項3】**

請求項1において、

前記トランジスタは、Nチャネル型であることを特徴とする半導体装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一に記載の半導体装置と、

FPCと、を有することを特徴とする表示モジュール。

30

**【請求項5】**

請求項1乃至請求項3のいずれか一に記載の半導体装置と、

アンテナ、操作スイッチ、スピーカ、マイクロフォン、または、受像部と、を有することを特徴とする電子機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置、表示装置、若しくは発光装置、又はそれらの駆動方法に関する。

**【背景技術】**

**【0002】**

近年、液晶ディスプレイ(LCD)などのフラットパネルディスプレイが広く普及してきている。しかしながら、LCDには、視野角が狭い、色度範囲が狭い、応答速度が遅い、などの様々な欠点を有している。そこで、それらの欠点を克服したディスプレイとして、有機EL(エレクトロルミネッセンス、有機発光ダイオード、オーレッドなどとも言う)ディスプレイの研究が活発に行われている(特許文献1)。

**【0003】**

しかしながら、有機ELディスプレイには、有機EL素子に流れる電流を制御するためのトランジスタの電流特性が、画素毎にばらついてしまう、という問題点があった。有機EL素子に流れる電流(すなわち、トランジスタを流れる電流)がばらつけば、有機EL素子の輝度もばらつき、ムラのある表示画面となってしまう。そこで、トランジスタのしき

40

50

い値電圧のバラツキを補正する方法が検討されている（特許文献 2 乃至 6 ）。

【 0 0 0 4 】

しかし、トランジスタのしきい値電圧のバラツキを補正しても、トランジスタの移動度がばらつければ、有機 E L 素子に流れる電流もばらついてしまい、画像ムラを生じてしまう。そこで、トランジスタのしきい値電圧だけでなく、移動度のバラツキも補正する方法が検討されている（特許文献 7 乃至 8 ）。

【先行技術文献】

【特許文献】

【 0 0 0 5 】

【特許文献 1 】特開 2 0 0 3 - 2 1 6 1 1 0 号公報

10

【特許文献 2 】特開 2 0 0 3 - 2 0 2 8 3 3 号公報

【特許文献 3 】特開 2 0 0 5 - 3 1 6 3 0 号公報

【特許文献 4 】特開 2 0 0 5 - 3 4 5 7 2 2 号公報

【特許文献 5 】特開 2 0 0 7 - 1 4 8 1 2 9 号公報

【特許文献 6 】国際公開第 2 0 0 6 / 0 6 0 9 0 2 号パンフレット

【特許文献 7 】特開 2 0 0 7 - 1 4 8 1 2 8 号公報（ [ 0 0 9 8 ] 段落 ）

【特許文献 8 】特開 2 0 0 7 - 3 1 0 3 1 1 号公報（ [ 0 0 2 6 ] 段落 ）

【発明の概要】

【発明が解決しようとする課題】

【 0 0 0 6 】

20

特許文献 7 乃至 8 で開示された技術においては、映像信号（ビデオ信号）を画素に入力しながら、トランジスタの移動度のばらつきの補正を行っており、問題が生じる。

【 0 0 0 7 】

例えば、映像信号を入力しながら移動度のばらつきの補正を行うため、その間は、別の画素に映像信号を入力することが出来ない。通常、画素数、フレーム周波数または画面サイズなどが決まれば、各画素に映像信号を入力する期間（いわゆる、1 ゲート選択期間または 1 水平期間）の最大値も決まる。よって、1 ゲート選択期間中に、移動度のバラツキの補正を行う期間が増えることにより、他の処理（映像信号の入力やしきい値電圧の取得など）の期間が減ってしまう。そのため画素では、1 ゲート選択期間中に、様々な処理を行わなければならないこととなる。結果として、処理期間が足りず、正確な処理を行えない、または、移動度のバラツキの補正の期間を十分に確保することができないために移動度の補正が不十分となってしまう。

30

【 0 0 0 8 】

さらに、画素数やフレーム周波数が高くなる、または画面サイズが大きくなると、1 画素当たりの 1 ゲート選択期間がますます短くなる。そのため、画素への映像信号の入力や、移動度のばらつきの補正などが十分に確保できなくなってしまう。

【 0 0 0 9 】

あるいは、映像信号を入力しながら移動度のばらつきの補正を行う場合、移動度のばらつきの補正は、映像信号の波形のなまりの影響を受けやすい。そのため、映像信号の波形のなまりが大きい場合と小さい場合とでは、移動度の補正の程度にばらつきが生じてしまい、正確な補正が出来ない。

40

【 0 0 1 0 】

あるいは、画素に映像信号を入力しながら移動度のばらつきの補正を行う場合、点順次駆動を行うことが困難である場合が多い。点順次駆動では、ある行の画素に映像信号を入力する場合、その行の全ての画素に同時に映像信号を入力するのではなく、1 画素ずつ順に映像信号を入力していく。したがって、映像信号を入力している期間の長さは、画素毎に異なってくる。よって、映像信号を入力しながら移動度のばらつきの補正を行う場合、画素毎に移動度のばらつきの補正期間が異なってしまうため、補正量も画素毎に異なってしまい、正常に補正を行うことが出来ない。したがって、映像信号を入力しながら移動度のばらつきの補正を行う場合は、点順次駆動ではなく、その行の全ての画素に同時に信

50

号を入力する線順次駆動を行う必要がある。

#### 【0011】

さらに、線順次駆動を行う場合、点順次駆動を行う場合と比べて、ソース信号線駆動回路（ビデオ信号線駆動回路、ソースドライバー、データドライバーとも言う）の構成が複雑になる。例えば、線順次駆動でのソース信号線駆動回路は、D A コンバータ、アナログバッファ、ラッチ回路などの回路が必要となる場合が多い。しかし、アナログバッファは、オペアンプやソースフォロワ回路などで構成される場合が多く、トランジスタの電流特性のばらつきの影響を受けやすい。したがって、TFT（薄膜トランジスタ）を用いて回路を構成する場合、トランジスタの電流特性のばらつきを補正する回路が必要となり、回路の規模が大きくなったり、消費電力が大きくなったりする。そのため、画素部分のトランジスタとしてTFTが用いられている場合には、画素部分と信号線駆動回路とを同一基板上に形成することが困難となる可能性がある。そのため、信号線駆動回路を画素部分とは別の手段を用いて作成する必要があり、コストが高くなってしまう可能性がある。さらに、画素部分と信号線駆動回路とを、COG（チップ・オン・グラス）またはTAB（テープ・オートメイテド・ボンディング）などを用いて接続する必要があり、接触不良などを起こしてしまったり、信頼性を損ねてしまったりする。10

#### 【0012】

そこで、本発明の一態様は、トランジスタのしきい値電圧のばらつきの影響を低減することを課題とする。または、本発明の一態様は、トランジスタの移動度のばらつきの影響を低減することを課題とする。または、本発明の一態様は、トランジスタの電流特性のばらつきの影響を低減することを課題とする。または、本発明の一態様は、映像信号の入力期間を長く確保することを課題とする。または、本発明の一態様は、しきい値電圧のばらつきの影響を低減するための補正期間を長く確保することを課題とする。または、本発明の一態様は、移動度のばらつきの影響を低減するための補正期間を長く確保することを課題とする。または、本発明の一態様は、移動度のばらつきの補正が映像信号の波形のなまりの影響を受けにくくすることを課題とする。または、本発明の一態様は、線順次駆動だけでなく、点順次駆動を用いることも出来ることを課題とする。または、本発明の一態様は、画素と駆動回路とを同じ基板上に形成することを課題とする。または、本発明の一態様は、消費電力を低くすることを課題とする。または、本発明の一態様は、製造コストを低くすることを課題とする。または、本発明の一態様は、配線の接続部分の接触不良を起こす可能性を低減することを課題とする。なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、上記の課題の全てを解決する必要はないものとする。2030

#### 【課題を解決するための手段】

#### 【0013】

本発明の一態様は、トランジスタと、トランジスタのゲートに電気的に接続された容量素子と、を有する半導体装置の駆動方法であって、容量素子に、トランジスタのしきい値電圧に応じた電圧を保持する第1の期間と、しきい値電圧が保持された容量素子に映像信号電圧及びしきい値電圧の和を保持する第2の期間と、第2の期間に、映像信号電圧及びしきい値電圧の和に応じて容量素子に保持された電荷を、トランジスタを介して放電する第3の期間と、を有する半導体装置の駆動方法である。40

#### 【0014】

本発明の一態様は、トランジスタと、トランジスタのゲートに電気的に接続された容量素子と、を有する半導体装置の駆動方法であって、容量素子に保持される電荷を初期化するための第1の期間と、容量素子に、トランジスタのしきい値電圧に応じた電圧を保持する第2の期間と、しきい値電圧が保持された容量素子に映像信号電圧及びしきい値電圧の和を保持する第3の期間と、第3の期間に、映像信号電圧及びしきい値電圧の和に応じて容量素子に保持された電荷を、トランジスタを介して放電する第4の期間と、を有する半導体装置の駆動方法。

#### 【0015】

本発明の一態様は、トランジスタと、トランジスタのゲートに電気的に接続された容量素子と、表示素子と、を有する半導体装置の駆動方法であって、容量素子に、トランジスタのしきい値電圧に応じた電圧を保持する第1の期間と、しきい値電圧が保持された容量素子に映像信号電圧及びしきい値電圧の和を保持する第2の期間と、第2の期間に、映像信号電圧及びしきい値電圧の和に応じて容量素子に保持された電荷を、トランジスタを介して放電する第3の期間と、第3の期間の後に、トランジスタを介して、表示素子に電流を供給する第4の期間と、を有する半導体装置の駆動方法。

【0016】

本発明の一態様は、トランジスタと、トランジスタのゲートに電気的に接続された容量素子と、表示素子と、を有する半導体装置の駆動方法であって、容量素子に保持される電荷を初期化するための第1の期間と、容量素子に、トランジスタのしきい値電圧に応じた電圧を保持する第2の期間と、しきい値電圧が保持された容量素子に映像信号電圧及びしきい値電圧の和を保持する第3の期間と、第3の期間に、映像信号電圧及びしきい値電圧の和に応じて容量素子に保持された電荷を、トランジスタを介して放電する第4の期間と、第3の期間の後に、トランジスタを介して、表示素子に電流が供給する第5の期間と、を有する半導体装置の駆動方法。

10

【0017】

なお、スイッチは、様々な形態のものを用いることができる。例としては、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されない。例えば、スイッチとして、トランジスタ（例えば、バイポーラトランジスタ、MOSトランジスタなど）、ダイオード（例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM（Metal Insulator Metal）ダイオード、MIS（Metal Insulator Semiconductor）ダイオード、ダイオード接続のトランジスタなど）などを用いることが出来る。または、これらを組み合わせた論理回路をスイッチとして用いることが出来る。

20

【0018】

機械的なスイッチの例としては、デジタルマイクロミラーデバイス（DMD）のように、MEMS（マイクロ・エレクトロ・メカニカル・システム）技術を用いたスイッチがある。そのスイッチは、機械的に動かすことが出来る電極を有し、その電極が動くことによって、導通と非導通とを制御して動作する。

30

【0019】

なお、Nチャネル型トランジスタとPチャネル型トランジスタの両方を用いて、CMOS型のスイッチをスイッチとして用いてもよい。

【0020】

なお、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

40

【0021】

例えば、AとBとが電気的に接続されている場合として、AとBとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど）が、AとBとの間に1個以上接続されていてもよい。あるいは、AとBとが機能的に接続されている場合として、AとBとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制

50

御回路など)が、AとBとの間に1個以上接続されていてもよい。例えば、AとBとの間に別の回路を挟んでいても、Aから出力された信号がBへ伝達される場合は、AとBとは機能的に接続されているものとする。

#### 【0022】

なお、AとBとが電気的に接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合(つまり、AとBとの間に別の素子や別の回路を挟んで接続されている場合)と、AとBとが機能的に接続されている場合(つまり、AとBとの間に別の回路を挟んで機能的に接続されている場合)と、AとBとが直接接続されている場合(つまり、AとBとの間に別の素子や別の回路を挟まずに接続されている場合)とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

10

#### 【0023】

なお、表示素子、表示素子を有する装置である表示装置、発光素子、発光素子を有する装置である発光装置は、様々な形態を用いたり、様々な素子を有することが出来る。例えば、表示素子、表示装置、発光素子または発光装置としては、EL(エレクトロルミネッセンス)素子(有機物及び無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LED、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、デジタルマイクロミラーデバイス(DMD)、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショニングディスプレイ(FED)やSED方式平面型ディスプレイ(SED: Surface-conduction Electron-emitter Display)など、液晶素子を用いた表示装置としては液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)、電子インクや電気泳動素子を用いた表示装置としては電子ペーパーがある。

20

#### 【0024】

なお、液晶素子とは、液晶の光学的変調作用によって光の透過または非透過を制御する素子であり、一対の電極、及び液晶により構成される。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御される。なお、液晶素子としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC)、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶(PALC)、バナナ型液晶などを挙げることができる。また、液晶の駆動方式としては、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、IPS(In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi-domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、ゲストホストモード、ブルー相(Blue Phase)モードなどを用いることができる。ただし、これに限定されず、液晶素子及びその駆動方法と

30

40

50

して様々なものを用いることができる。

【0025】

なお、トランジスタとして、様々な形態のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを用いることが出来る。

【0026】

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。ただし、触媒（ニッケルなど）を用いずに、多結晶シリコンや微結晶シリコンを製造することは可能である。

【0027】

なお、シリコンの結晶性を、多結晶または微結晶などへと向上させることは、パネル全体で行なうことが望ましいが、それに限定されない。パネルの一部の領域のみにおいて、シリコンの結晶性を向上させてもよい。

【0028】

または、半導体基板やSOI基板などを用いてトランジスタを形成することが出来る。

【0029】

または、ZnO、a-InGaZnO、SiGe、GaAs、IZO、ITO、SnO、TiO、AlZnSnO（AZTO）などの化合物半導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。なお、これらの化合物半導体または酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体または酸化物半導体を抵抗素子、画素電極、透光性を有する電極として用いることができる。さらに、それらをトランジスタと同時に成膜又は形成できるため、コストを低減できる。

【0030】

または、インクジェットや印刷法を用いて形成したトランジスタなどを用いることが出来る。

【0031】

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。このような基板を用いた半導体装置は、衝撃に強くすることができる。

【0032】

さらに、様々な構造のトランジスタを用いることができる。例えば、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどをトランジスタとして用いることが出来る。

【0033】

なお、MOS型トランジスタ、バイポーラトランジスタなどを1つの基板に混在させて形成してもよい。

【0034】

その他、様々なトランジスタを用いることができる。

【0035】

なお、トランジスタは、様々な基板を用いて形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板としては、例えば、単結晶基板（例えばシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タン

10

20

30

40

50

グステン・ホイルを有する基板、可撓性基板などを用いることが出来る。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルフォン（P E S）に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。他にも、貼り合わせフィルム（ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなど）、纖維状な材料を含む紙、基材フィルム（ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、紙類等）などがある。または、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板としては、単結晶基板、S O I 基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、ゴム基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。あるいは、人などの動物の皮膚（表皮、真皮）又は皮下組織を基板として用いてもよい。または、ある基板を用いてトランジスタを形成し、その基板を研磨して薄くしてもよい。研磨される基板としては、単結晶基板、S O I 基板、ガラス基板、石英基板、プラスチック基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。10

#### 【0036】

なお、トランジスタの構成は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。

#### 【0037】

別の例として、チャネルの上下にゲート電極が配置されている構造を適用することができる。なお、チャネルの上下にゲート電極が配置される構成にすることにより、複数のトランジスタが並列に接続されたような構成となる。

#### 【0038】

チャネル領域の上にゲート電極が配置されている構造、チャネル領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、またはチャネル領域が直列に接続する構成も適用できる。さらに、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造も適用できる。30

#### 【0039】

なお、トランジスタは、様々なタイプを用いることができ、様々な基板を用いて形成させることができる。したがって、所定の機能を実現させるために必要な回路の全てが、同一の基板に形成することも可能である。例えば、所定の機能を実現させるために必要な回路の全てが、ガラス基板、プラスチック基板、単結晶基板、またはS O I 基板などの様々な基板を用いて形成することも可能である。あるいは、所定の機能を実現させるために必要な回路の一部が、ある基板に形成され、所定の機能を実現させるために必要な回路の別の一部が、別の基板に形成されていることも可能である。つまり、所定の機能を実現させるために必要な回路の全てが同じ基板を用いて形成されていなくてもよい。例えば、所定の機能を実現させるために必要な回路の一部は、ガラス基板上にトランジスタにより形成され、所定の機能を実現させるために必要な回路の別の一部は、単結晶基板に形成され、単結晶基板を用いて形成されたトランジスタで構成されたI C チップをC O G ( C h i p On G l a s s ) でガラス基板に接続して、ガラス基板上にそのI C チップを配置することも可能である。あるいは、そのI C チップをT A B ( T a p e A u t o m a t e d B o n d i n g ) やプリント基板を用いてガラス基板と接続することも可能である。40

#### 【0040】

50

なお、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれを第1電極、第2電極と表記する場合がある。

【0041】

10

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子などと表記する場合がある。

【0042】

なお、Aの上にBが形成されている、あるいは、A上にBが形成されている、と明示的に記載する場合は、Aの上にBが直接接して形成されていることに限定されない。直接接してはいない場合、つまり、AとBと間に別の対象物が介在する場合も含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

【0043】

20

従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、と明示的に記載されている場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

【0044】

さらに、Aの上方にBが形成されている、と明示的に記載されている場合についても同様であり、Aの上にBが直接接していることに限定されず、AとBとの間に別の対象物が介在する場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

30

【0045】

なお、Aの上にBが形成されている、A上にBが形成されている、又はAの上方にBが形成されている、と明示的に記載する場合、斜め上にBが形成される場合も含むこととする。

【0046】

なお、Aの下にBが、あるいは、Aの下方にBが、の場合についても、同様である。

【0047】

40

なお、明示的に単数として記載されているものについては、単数であることが望ましい。ただし、これに限定されず、複数であることも可能である。同様に、明示的に複数として記載されているものについては、複数であることが望ましい。ただし、これに限定されず、単数であることも可能である。

【0048】

なお、図において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0049】

なお、図は、理想的な例を模式的に示したものであり、図に示す形状又は値などに限定されない。例えば、製造技術による形状のばらつき、誤差による形状のばらつき、ノイズに

50

よる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

【0050】

なお、専門用語は、特定の実施の形態などを述べる目的で用いられる場合が多い。ただし、発明の一態様は、専門用語によって、限定して解釈されるものではない。

【0051】

なお、定義されていない文言（専門用語又は学術用語などの科学技術文言を含む）は、通常の当業者が理解する一般的な意味と同等の意味として用いることが可能である。辞書等により定義されている文言は、関連技術の背景と矛盾がないような意味に解釈されることが好ましい。

10

【0052】

なお、第1、第2、第3などの語句は、様々な要素、部材、領域、層、区域を他のものと区別して記述するために用いられる。よって、第1、第2、第3などの語句は、要素、部材、領域、層、区域などの数を限定するものではない。さらに、例えば、「第1の」を「第2の」又は「第3の」などと置き換えることが可能である。

【0053】

なお、「上に」、「上方に」、「下に」、「下方に」、「横に」、「右に」、「左に」、「斜めに」、「奥に」、「手前に」、「内に」、「外に」、又は「中に」などの空間的配置を示す語句は、ある要素又は特徴と、他の要素又は特徴との関連を、図によって簡単に示すために用いられる場合が多い。ただし、これに限定されず、これらの空間的配置を示す語句は、図に描く方向に加えて、他の方向を含むことが可能である。例えば、Aの上にB、と明示的に示される場合は、BがAの上にあることに限定されない。図中のデバイスは反転、又は180°回転することが可能なので、BがAの下にあることを含むことが可能である。このように、「上に」という語句は、「上に」の方向に加え、「下に」の方向を含むことが可能である。ただし、これに限定されず、図中のデバイスは様々な方向に回転することが可能なので、「上に」という語句は、「上に」、及び「下に」の方向に加え、「横に」、「右に」、「左に」、「斜めに」、「奥に」、「手前に」、「内に」、「外に」、又は「中に」などの他の方向を含むことが可能である。つまり、状況に応じて適切に解釈することが可能である。

20

【発明の効果】

30

【0054】

本発明の一態様は、トランジスタのしきい値電圧のばらつきの影響を低減することができる。または、本発明の一態様は、トランジスタの移動度のばらつきの影響を低減することができる。または、本発明の一態様は、トランジスタの電流特性のばらつきの影響を低減することができる。または、本発明の一態様は、映像信号の入力期間を長く確保することができる。または、本発明の一態様は、しきい値電圧のばらつきの影響を低減するための補正期間を長く確保することができる。または、本発明の一態様は、移動度のばらつきの影響を低減するための補正期間を長く確保することができる。または、本発明の一態様は、移動度のばらつきの補正が映像信号の波形のなまりの影響を受けにくくすることができる。または、本発明の一態様は、線順次駆動だけでなく、点順次駆動を用いることができる。または、本発明の一態様は、画素と駆動回路とを同じ基板上に形成することができる。または、本発明の一態様は、消費電力を低くすることができる。または、本発明の一態様は、コストを低くすることができます。または、本発明の一態様は、配線の接続部分の接触不良を低減することができます。

40

【図面の簡単な説明】

【0055】

【図1】実施の形態で示す回路または駆動方法を説明する図。

【図2】実施の形態で示す回路または駆動方法を説明する図。

【図3】実施の形態で示す動作を説明する図。

【図4】実施の形態で示す回路または駆動方法を説明する図。

50

- 【図 5】実施の形態で示す回路または駆動方法を説明する図。

- 【図 6】実施の形態で示す回路または駆動方法を説明する図。

- 【図 7】実施の形態で示す回路または駆動方法を説明する図。

- 【図 8】実施の形態で示す回路または駆動方法を説明する図。

- 【図 9】実施の形態で示す回路または駆動方法を説明する図。

- 【図 10】実施の形態で示す回路または駆動方法を説明する図。

- 【図 11】実施の形態で示す回路または駆動方法を説明する図。

- 【図 12】実施の形態で示す回路または駆動方法を説明する図。

- 【図 13】実施の形態で示す駆動方法を説明する断面図。

- 【図 14】実施の形態で示すブロック図を説明する断面図。

- 【図 15】実施の形態で示すブロック図を説明する断面図。

- 【図 16】実施の形態で示すトランジスタを説明する断面図。

- 【図 17】実施の形態で示すトランジスタを説明する断面図。

- 【図 18】実施の形態で示す電子機器を説明する図。

- 【図 19】実施の形態で示す電子機器を説明する図。

【発明を実施するための形態】

【0056】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0057】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、及び／又は、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。

【0058】

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

【0059】

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、及び／又は、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

【0060】

なお、ある一つの実施の形態において述べる図または文章において、その一部分を取り出して、発明の一態様を構成することは可能である。したがって、ある部分を述べる図または文章が記載されている場合、その一部分の図または文章を取り出した内容も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能であるものとする。そのため、例えば、能動素子（トランジスタ、ダイオードなど）、配線、受動素子（容量素子、抵抗素子など）、導電層、絶縁層、半導体層、有機材料、無機材料、部品、基板、モジュール、装置、固体、液体、気体、動作方法、製造方法などが単数又は複数記載された図面（断面図、平面図、回路図、ブロック図、フローチャート、工程図、斜視図、立面図、配置図、タイミングチャート、構造図、模式図、グラフ、表、光路図、ベクトル図、状態図、波形図、写真、化学式など）または文章において、その一部分を取り出して、発明の一態様を構成することが可能であるものとする。一例としては、N個（Nは整数）の回路素子（トランジスタ、容量素子等）を有して構成される回路図から、M個（Mは整数で、M < N）の回路素子（トランジスタ、容量素子等）を抜き出して、発明の一態

10

20

30

40

50

様を構成することは可能である。別の一例としては、N個（Nは整数）の層を有して構成される断面図から、M個（Mは整数で、M < N）の層を抜き出して、発明の一態様を構成することは可能である。別の一例としては、N個（Nは整数）の要素を有して構成されるフローチャートから、M個（Mは整数で、M < N）の要素を抜き出して、発明の一態様を構成することは可能である。

#### 【0061】

##### （実施の形態1）

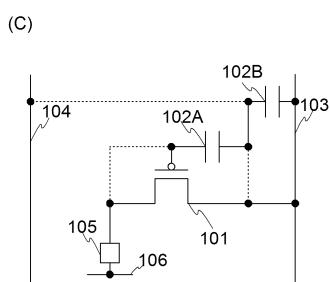

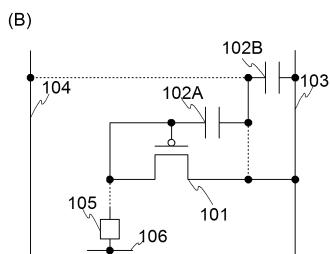

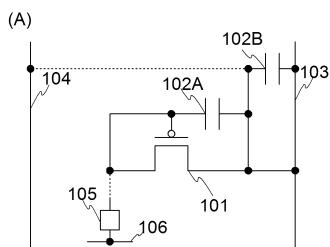

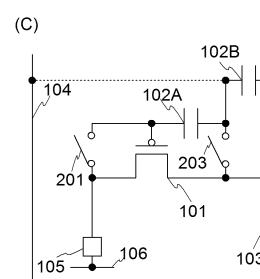

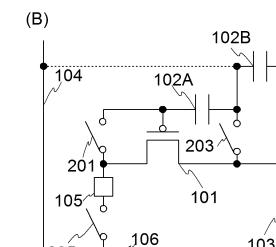

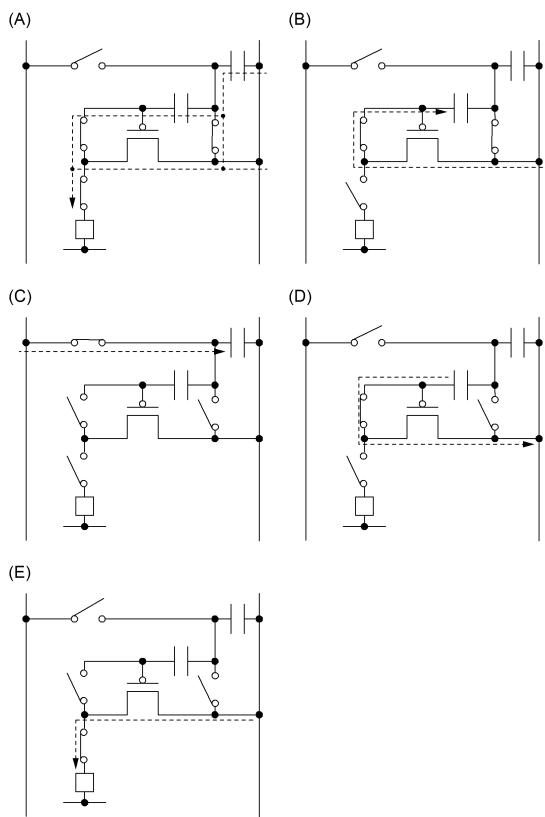

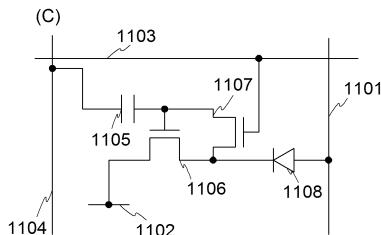

図1（A）乃至（C）に、トランジスタのしきい値電圧、移動度などの電流特性のばらつきを補正する場合の駆動方法、駆動タイミングおよび、その時の回路構成について、その一例を示す。なお、本実施の形態においては、トランジスタの導電型がpチャネル型の例について説明を行う。

10

#### 【0062】

図1（A）に、トランジスタ101のしきい値電圧のばらつきを補正している期間における回路構成を示す。すなわち、トランジスタ101に接続された容量素子に、トランジスタ101のしきい値電圧に応じた電荷を保持させるための期間における回路構成について示す。なお図1（A）に示す回路構成は、トランジスタ101のしきい値電圧の電流特性のばらつきを補正するために、トランジスタのゲートに保持されている電荷を放電するための回路構成であり、実際には配線間に設けられる複数のスイッチのオンまたはオフを制御することで当該回路構成の接続関係を実現するものである。なお図中、実線は素子間の導通状態をあらわし、点線は、素子間の非導通状態をあらわすものとする。なお導通状態、非導通状態は、スイッチ、トランジスタ、抵抗素子、容量素子等の素子で接続を切り替えることにより、制御することが可能である。

20

#### 【0063】

図1（A）において、トランジスタ101のソースまたはドレインの一方（以下、第1の端子という）は、配線103と導通状態にある。トランジスタ101のソースまたはドレインの他方（以下、第2の端子という）は、トランジスタ101のゲートと導通状態にある。容量素子102Aの第1の端子（または第1の電極）は、トランジスタ101のゲートと導通状態にある。容量素子102Aの第2の端子（または第2の電極）は、容量素子102Bの第1の端子（または第1の電極）、トランジスタ101の第1の端子、及び配線103と導通状態にある。容量素子102Bの第2の端子（または第2の電極）は、配線103と導通状態にある。

30

#### 【0064】

図1（A）において、表示素子105の第1の端子（または第1の電極）は、トランジスタ101の第2の端子と、非導通状態にある。トランジスタ101の第2の端子以外の端子、配線または電極と、表示素子105の第1の端子（または第1の電極）とは、非導通状態にあることが望ましい。表示素子105の第2の端子（または第2の電極）は、配線106と導通状態にあることが望ましい。

40

#### 【0065】

配線104は、トランジスタ101の第2の端子と、非導通状態にある。さらに、配線104は、容量素子102Aの第2の端子、容量素子102Bの第1の端子と、非導通状態にある。なお、配線104は、図1（A）に示すように、トランジスタ101の第2の端子と容量素子102Aの第2の端子、容量素子102Bの第1の端子以外の端子、配線または電極とも、非導通状態にあることが望ましい。

40

#### 【0066】

なお、配線104を介して、トランジスタ101、容量素子102A、または容量素子102Bに、映像信号または所定の電圧などを供給される場合がある。よって、配線104は、ソース信号線、映像信号線、または、ビデオ信号線などと呼ばれる場合がある。

#### 【0067】

図1（B）に、トランジスタ101の移動度などの電流特性のばらつきを補正している期間における回路構成を示す。なお図1（B）に示す回路構成は、トランジスタ101の移

50

動度などの電流特性のばらつきを補正するために、トランジスタのゲートに保持されている電荷を放電するための回路構成であり、実際には配線間に設けられる複数のスイッチのオンまたはオフを制御することで当該回路構成の接続関係を実現するものである。

【0068】

図1(B)において、トランジスタ101の第1の端子は、配線103と導通状態にある。トランジスタ101の第2の端子は、トランジスタ101のゲートと導通状態にある。容量素子102Aの第1の端子は、トランジスタ101のゲートと導通状態にある。容量素子102Aの第2の端子は、容量素子102Bの第1の端子と導通状態にある。容量素子102Bの第2の端子は、配線103と導通状態にある。

【0069】

図1(B)において、表示素子105の第1の端子は、トランジスタ101の第2の端子と、非導通状態にある。トランジスタ101の第2の端子以外の端子、配線または電極と、表示素子105の第1の端子とは、非導通状態にあることが望ましい。表示素子105の第2の端子は、配線106と導通状態にあることが望ましい。

【0070】

配線104は、トランジスタ101の第2の端子と、非導通状態にある。さらに、配線104は、容量素子102Aの第2の端子、容量素子102Bの第1の端子と、非導通状態にある。なお、配線104は、図1(B)に示すように、トランジスタ101の第2の端子と容量素子102Aの第2の端子、容量素子102Bの第1の端子以外の端子、配線または電極とも、非導通状態にあることが望ましい。

10

【0071】

なお、図1(B)の様な接続構成になる前に、つまり、トランジスタ101の移動度などの電流特性のばらつきの補正を行う前に、容量素子102Aには、トランジスタ101のしきい値電圧に応じた電圧が保持され、その上で映像信号(ビデオ信号)が配線104を介して容量素子102Bに入力されていることが望ましい。したがって、容量素子102Aにはしきい値電圧に応じた電圧、容量素子102Bには映像信号電圧が保持されていることが望ましい。その結果、トランジスタ101のゲートとソースの間の電圧は、容量素子102Aと容量素子102Bとの和になるので、容量素子102A及び容量素子102Bには、しきい値電圧に応じた電圧と映像信号電圧との和の電圧が保持されていることとなる。よって、図1(A)と図1(B)との間の状態においては、つまり、図1(B)のトランジスタ101の移動度のばらつきの補正を行う前には、配線104は、トランジスタ101のドレイン、ソース、ゲート、容量素子102Aの第2の端子、容量素子102Bの第1の端子、などのうちの少なくとも一つと導通状態にあり、既に映像信号の入力動作が行われていることが望ましい。

20

【0072】

なお、容量素子102A及び容量素子102Bによってトランジスタ101のしきい値電圧に応じた電圧および映像信号電圧の和の電圧が保持されている場合、スイッチングノイズなどにより、わずかに電圧が変動する可能性がある。ただし、実動作に影響を与えない範囲であれば、多少ずれっていても問題はない。したがって、例えば、トランジスタ101のしきい値電圧に応じた電圧および映像信号電圧の和の電圧が容量素子102A及び容量素子102Bに入力された場合、実際に容量素子102A及び容量素子102Bに保持されている電圧は、その入力された電圧とは、完全には一致せず、ノイズなどの影響により、わずかに、異なっている場合がある。ただし、実動作に影響を与えない範囲であれば、多少ずれっていても問題はない。

30

【0073】

次に、図1(C)に、トランジスタ101を介して、表示素子105に電流が供給されている期間における回路構成について示す。なお図1(C)に示す回路構成は、トランジスタ101より表示素子105に電流を供給するための回路構成であり、実際には配線間に設けられる複数のスイッチのオンまたはオフを制御することで当該回路構成の接続関係を実現するものである。

40

50

## 【0074】

図1(C)において、トランジスタ101の第1の端子は、配線103と導通状態にある。トランジスタ101の第2の端子は、表示素子105の第1の端子と導通状態にある。トランジスタ101の第2の端子は、トランジスタ101のゲートと非導通状態にある。容量素子102Aの第1の端子は、トランジスタ101のゲートと導通状態にある。容量素子102Aの第2の端子は、容量素子102Bの第1の端子と導通状態にある。容量素子102Bの第2の端子は、配線103と導通状態にある。表示素子105の第2の端子は、配線106と導通状態にある。

## 【0075】

図1(C)において、配線104は、トランジスタ101の第2の端子と、非導通状態にある。さらに、配線104は、容量素子102Aの第2の端子と、容量素子102Bの第1の端子と、非導通状態にある。なお、配線104は、図1(C)に示すように、トランジスタ101の第2の端子と、容量素子102Aの第2の端子と、容量素子102Bの第1の端子以外の端子、配線または電極とも、非導通状態にあることが望ましい。

10

## 【0076】

つまり、トランジスタ101の移動度などの電流特性のばらつきを補正している期間(図1(B))から、トランジスタ101を介して、表示素子105に電流が供給されている期間(図1(C))へ移行するときには、少なくとも、トランジスタ101の第2の端子とトランジスタ101のゲートとの導通状態と、トランジスタ101の第2の端子と表示素子105の第1の端子(または第1の電極)との導通状態とが変化することとなるが、これに限定されず、他の部分の導通状態が変化することもできる。そして、上述のように導通状態を制御できるように、スイッチ、トランジスタまたはダイオードなど素子を配置することが望ましい。そして、当該素子を用いて導通状態を制御し、図1(A)乃至図1(C)の接続状況を実現するような回路構成を実現することが出来る。よって、図1(A)乃至図1(C)のような接続状況を実現できるならば、スイッチ、トランジスタまたはダイオードなどの素子を自由に配置することができ、その個数または接続構造も限定されない。

20

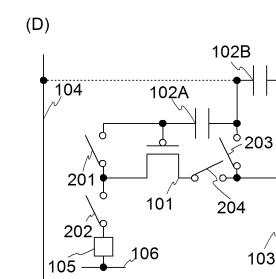

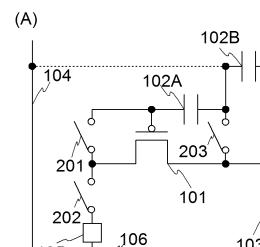

## 【0077】

一例としては、図2(A)に示すように、スイッチ201の第1の端子をトランジスタ101のゲートと電気的に接続し、スイッチ201の第2の端子をトランジスタ101の第2の端子と電気的に接続する。そして、スイッチ202の第1の端子をトランジスタ101の第2の端子と電気的に接続し、スイッチ202の第2の端子を表示素子105と電気的に接続する。そして、スイッチ203の第1の端子を容量素子102Aの第2の端子及び容量素子102Bの第1の端子と電気的に接続し、スイッチ203の第2の端子をトランジスタ101の第1の端子及び配線103と電気的に接続する。このように、3つのスイッチを配置することにより、図1(A)乃至図1(C)の接続状況を実現するような回路構成を実現することが出来る。

30

## 【0078】

図2(A)とは別の例を、図2(B)、図2(C)に示す。図2(B)では、図2(A)の表示素子105の上にあるスイッチ202を削除し、表示素子の下にスイッチ205を追加する。図2(C)では、図2(A)におけるスイッチ202を削除したものである。その代わり、例えば、配線106の電位を変化させることにより、表示素子105が非導通状態となり、図1(A)と同様な動作を実現することが出来る。そして、さらにスイッチやトランジスタなどが必要な場合は、適宜、配置される。

40

## 【0079】

なお、AはBと導通状態にある、と記載しているが、その場合、AとBとの間には、様々な素子が接続されていることは可能である。例えば、抵抗素子、容量素子、トランジスタ、ダイオードなどがAとBとの間に、直列接続、または並列接続で接続されていることは可能である。同様に、AはBと非導通状態にある、と記載しているが、その場合、AとBとの間には、様々な素子が接続されていることは可能である。AとBとが、非導通になつ

50

てさえすればよいため、それ以外の部分では、様々な素子が接続されていることは可能である。例えば、抵抗素子、容量素子、トランジスタ、ダイオードなどの素子が直列接続、または並列接続で接続されていることは可能である。

#### 【0080】

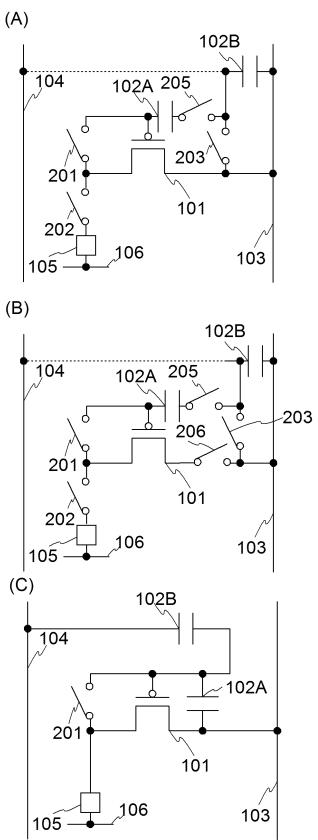

したがって、例えば、図2(A)の回路において、スイッチ204を追加した場合の回路を図2(D)に、スイッチ205を追加した場合の回路を図10(A)に、図10(A)にスイッチ206を追加した場合の回路を図10(B)に示す。

#### 【0081】

また、各配線及び素子の接続において、導通状態または非導通状態とするためのスイッチを省略することも可能である。スイッチを省略した場合の回路を図10(C)に示す。図10(C)に示す回路は、例えば、容量素子102Bの第2の端子の接続を配線104を行い、配線103の電位、配線104の電位、配線106の電位、及び各スイッチのオン又はオフの制御を行うことにより、上記図1(A)乃至(C)と同様の動作を行うことができる。なお容量素子102Bは、トランジスタ101の寄生容量を利用して省略することも可能である。

10

#### 【0082】

このように、トランジスタ101の移動度などの電流特性のばらつきを補正している期間(図1(B))において、トランジスタ101の移動度などの電流特性のばらつきが低減されるため、表示素子105に電流が供給されている期間(図1(B))において、表示素子105に供給される電流のばらつきも低減される。その結果、表示素子105の表示状態のばらつきも低減され、表示品位の高い表示を行うことが出来る。

20

#### 【0083】

以上説明した図2(A)乃至図2(D)、図10(A)乃至図10(C)に示す回路構成は、上記図1(A)乃至図1(C)で示した回路構成を実現する一例として示したものである。なお、実際には図2(A)乃至図2(D)、図10(A)乃至図10(C)に示した複数のスイッチ以外に、配線間に設けられる複数のスイッチのオンまたはオフを制御することで、当該回路構成の接続関係を実現するものである。

#### 【0084】

なお、表示素子105に電流が供給されている期間(図1(C))は、トランジスタ101の移動度などの電流特性のばらつきを補正している期間(図1(B))の直後に出現させることが望ましい。なぜなら、表示素子105に電流が供給されている期間(図1(C))において取得したトランジスタ101のゲート電位(容量素子102A及び容量素子102Bに保持された電荷)を利用して、表示素子105に電流が供給されている期間(図1(C))において、処理を行うからである。しかしながら、トランジスタ101の移動度などの電流特性のばらつきを補正している期間(図1(B))の直後に表示素子105に電流が供給されている期間(図1(C))を出現させることに限定されない。トランジスタ101の移動度などの電流特性のばらつきを補正している期間において、容量素子102A及び容量素子102Bの電荷量が変化し、そして、期間終了時に決定した容量素子102A及び容量素子102Bの電荷量が、表示素子105に電流が供給されている期間(図1(C))において、大きく変化していない場合などは、トランジスタ101の移動度などの電流特性のばらつきを補正している期間(図1(B))と、表示素子105に電流が供給されている期間(図1(C))との間に、別の処理が行われる期間が設けられても良い。

30

#### 【0085】

したがって、トランジスタ101の移動度などの電流特性のばらつきを補正している期間が終了した時点での容量素子102A及び容量素子102Bに保持された電荷と、表示素子105に電流が供給されている期間が開始した時点での容量素子102A及び容量素子102Bに保持された電荷とは、概ね同じ量であることが望ましい。ただし、ノイズなどの影響により、わずかに双方の電荷量が異なっている場合もある。具体的には、双方の電荷量の差は、10%以内が望ましく、より望ましくは、3%以内が望ましい。電荷量の差

40

50

が3%以内であれば、その差が反映される表示素子を人間の眼で見たときに、その差を視認できないため、より望ましい。

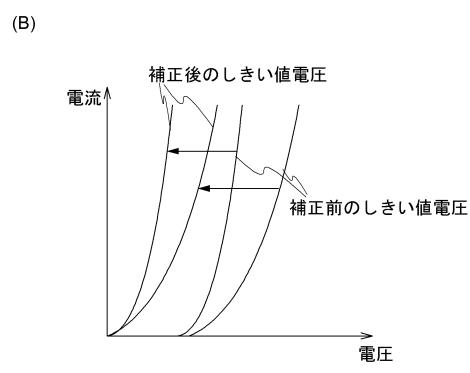

#### 【0086】

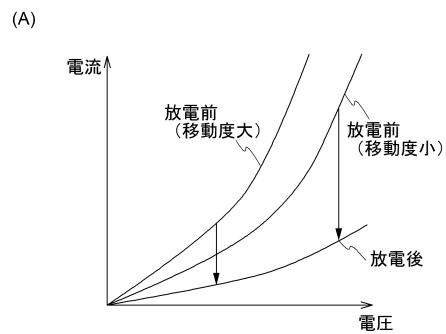

そこで、トランジスタ101の移動度などの電流特性のばらつきを補正している期間（図1（B））において、電圧電流特性がどのような状態に変化するかを図3（A）に示す。容量素子102A及び容量素子102Bに保存されていた電荷が、トランジスタ101の移動度などの電流特性のばらつきを補正している期間（図1（B））において、トランジスタ101のソース（第1の端子）とドレイン（第2の端子）との間を介して、放電していく。その結果、容量素子102A及び容量素子102Bに保持されていた電荷量が減少していく、容量素子102A及び容量素子102Bに保持された電圧も減少していく。

したがって、トランジスタ101のゲートとソースの間の電圧の絶対値も減少していく。容量素子102A及び容量素子102Bに保存されている電荷は、トランジスタ101を介して放電されていくため、電荷の放電量は、トランジスタ101の電流特性に依存する。つまり、トランジスタ101の移動度が高ければ、より多くの電荷が放電される。または、トランジスタ101のチャネル幅Wとチャネル長Lの比（W/L）が大きければ、より多くの電荷が放電される。または、トランジスタ101のゲートとソースの間の電圧の絶対値が大きければ（つまり、容量素子102A及び容量素子102Bで保持される電圧の絶対値が大きければ）、より多くの電荷が放電される。または、トランジスタ101のソース領域、ドレイン領域での寄生抵抗が小さければ、より多くの電荷が放電される。または、トランジスタ101のLDD領域での抵抗が小さければ、より多くの電荷が放電される。または、トランジスタ101と電気的に接続されているコンタクトホールでのコンタクト抵抗が小さければ、より多くの電荷が放電される。

10

20

30

40

#### 【0087】

そのため、放電前、つまり、トランジスタ101の移動度などの電流特性のばらつきを補正している期間（図1（B））に入る前の期間における電圧電流特性のグラフは、トランジスタ101の移動度などの電流特性のばらつきを補正している期間（図1（B））において、容量素子102A及び容量素子102Bに保存されている電荷の一部が放電された結果、傾きが小さな曲線のグラフに変化する。そして、例えば、放電前と放電後の電圧電流特性のグラフの差は、トランジスタ101の移動度が大きい方が大きくなる。したがって、トランジスタ101の移動度が高い場合（つまり、グラフの傾きが大きい場合）は、放電後には、傾きの変化量が大きくなり、トランジスタ101の移動度が低い場合（つまり、グラフの傾きが小さい場合）は、放電後には、傾きの変化量が小さくなる。その結果、放電後では、トランジスタ101の移動度が高い場合と低い場合とで、電圧電流特性のグラフの差が小さくなり、移動度のばらつきの影響が低減することができる。さらに、トランジスタ101のゲートとソースの間の電圧の絶対値が大きければ（つまり、容量素子102A及び容量素子102Bで保持される電圧の絶対値が大きければ）、より多くの電荷が放電され、トランジスタ101のゲートとソースの間の電圧の絶対値が小さければ（つまり、容量素子102A及び容量素子102Bで保持される電圧の絶対値が小さければ）、放電される電荷量が少なくなるため、より適切に、移動度のばらつきを低減することが出来る。

30

40

#### 【0088】

なお、図3（A）のグラフは、トランジスタ101のしきい値電圧のばらつきを補正している期間（図1（A））の後のグラフである。したがって、図3（B）に示すように、トランジスタ101の移動度のばらつきを補正している期間（図1（B））に入る前には、図1（A）で示す期間によって、しきい値電圧のばらつきの影響が低減されている。しきい値電圧のばらつきは、図1（A）で示す期間で、電圧電流特性のグラフをしきい値電圧の分だけ平行移動させることで達成される。つまり図1（B）の期間では、トランジスタのゲートとソースの間の電圧には、映像信号電圧としきい値電圧との和が供給されている。その結果、しきい値電圧のばらつきの影響は低減されていることとなる。しきい値電圧のばらつきを低減したあと、図3（A）のグラフに示すように、移動度のばらつきを低減

50

することにより、トランジスタ 101 の電流特性のばらつきを大幅に低減させることが出来る。

【0089】

なお、ばらつきを補正できるトランジスタ 101 の電流特性は、トランジスタ 101 の移動度だけでなく、しきい値電圧、ソース部分（ドレイン部分）での寄生抵抗、低濃度不純物領域（LDD 領域）での抵抗、トランジスタ 101 と電気的に接続されているコンタクトホールでのコンタクト抵抗などもあげられる。これらの電流特性も、トランジスタ 101 を介して電荷が放電されることから、移動度の場合と同様、ばらつきを低減することが出来る。

【0090】

従って、放電前、つまり、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））に入る前の期間における容量素子 102A 及び容量素子 102B の電荷量は、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））の終了時点における容量素子 102A 及び容量素子 102B の電荷量よりも多い。なぜなら、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））では、容量素子 102A 及び容量素子 102B の電荷が放電されるため、容量素子 102A 及び容量素子 102B に保存されている電荷が少なくなっているからである。

【0091】

なお、容量素子 102A 及び容量素子 102B に保持されている電荷は、一部が放電されれば、すぐに放電を停止することが望ましい。仮に、完全に放電してしまったら、つまり、電流が流れなくなるまで放電させてしまうと、映像信号の情報がほとんど無くなってしまう。したがって、完全に放電される前に、放電を停止することが望ましい。つまり、トランジスタ 101 に電流が流れている間に、放電を停止することが望ましい。

【0092】

したがって、1 ゲート選択期間（または 1 水平期間、1 フレーム期間を画素の行数で割り算した値など）と、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））との長さを比較すると、1 ゲート選択期間（または 1 水平期間、1 フレーム期間を画素の行数で割り算した値など）の方が長いことが望ましい。なぜなら、1 ゲート選択期間よりも長く放電を行うと、放電しすぎてしまう可能性があるからである。ただし、これに限定されない。

【0093】

または、画素に映像信号を入力している期間と、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））との長さを比較すると、画素に映像信号を入力している期間の方が長いことが望ましい。なぜなら、画素に映像信号を入力している期間よりも長く放電を行うと、放電しすぎてしまう可能性があるからである。ただし、これに限定されない。

【0094】

または、トランジスタのしきい値電圧を取得している期間（図 1（A））と、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））との長さを比較すると、トランジスタのしきい値電圧を取得している期間の方が長いことが望ましい。なぜなら、トランジスタのしきい値電圧を取得している期間よりも長く放電を行うと、放電しすぎてしまう可能性があるからである。ただし、これに限定されない。

【0095】

なお、トランジスタ 101 の移動度などの電流特性のばらつきを補正している期間（図 1（B））において、容量素子 102A 及び容量素子 102B に保持されている電荷を放電する期間の長さは、例えば、トランジスタ 101 の移動度のばらつき量、容量素子 102A 及び容量素子 102B の大きさ、トランジスタ 101 の W/L などに応じて、決定することが望ましい。

【0096】

10

20

30

40

50

例えば、図1(A)乃至(C)、図2(A)乃至(D)に示す回路が複数ある場合について考える。例としては、第1の色を表示するための第1の画素と、第2の色を表示するための第2の画素とを有しており、各々の画素はトランジスタ101に相当するトランジスタとして、第1の画素は、トランジスタ101Aを、第2の画素はトランジスタ101Bとを有しているとする。同様に、容量素子102Aに相当する容量素子として、第1の画素は、容量素子102A\_1を、第2の画素は容量素子102A\_2とを有しているとする。また容量素子102Bに相当する容量素子として、第1の画素は、容量素子102B\_1を、第2の画素は容量素子102B\_2とを有しているとする。

#### 【0097】

そして、トランジスタ101AのW/Lが、トランジスタ101BのW/Lよりも大きい場合は、容量素子102A\_1と容量素子102B\_1の合計の容量値の方が、容量素子102A\_2と容量素子102B\_2の合計の容量値よりも大きいことが望ましい。なぜなら、トランジスタ101Aの方が多くの電荷を放電するため、容量素子102A\_2と容量素子102B\_2の合計の電圧も、より大きく変化してしまう。そこで、それを調整するために、容量素子102A\_1と容量素子102B\_1の合計の容量値が大きいことが望ましい。または、トランジスタ101Aのチャネル幅Wが、トランジスタ101Bのチャネル幅Wよりも大きい場合は、容量素子102A\_1と容量素子102B\_1の合計の容量値の方が、容量素子102A\_2と容量素子102B\_2の合計の容量値よりも大きいことが望ましい。または、トランジスタ101Aのチャネル長Lが、トランジスタ101Bのチャネル長Lよりも小さい場合は、容量素子102A\_1と容量素子102B\_1の合計の容量値の方が、容量素子102A\_2と容量素子102B\_2の合計の容量値よりも大きいことが望ましい。

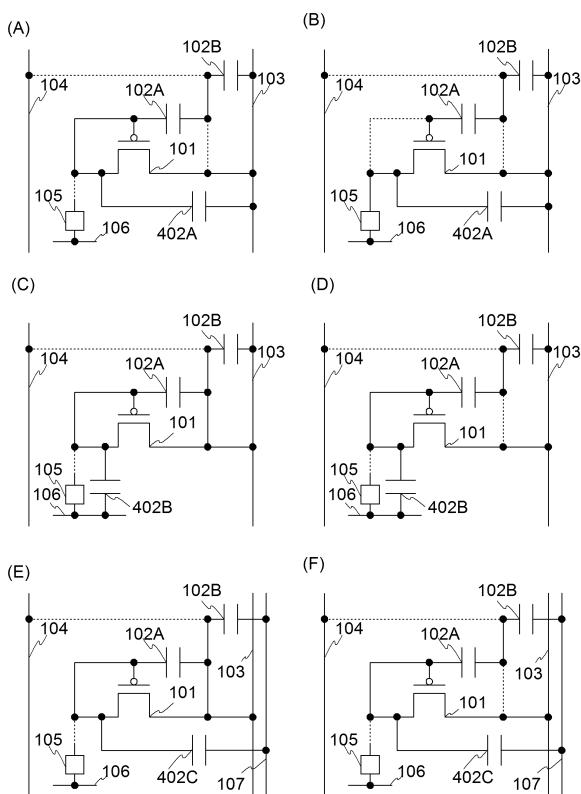

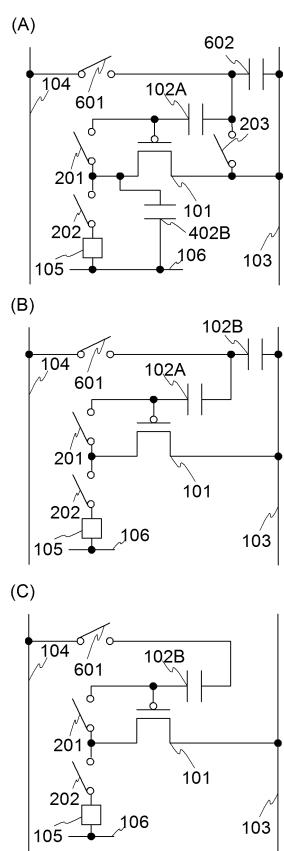

#### 【0098】

なお、容量素子102Aと容量素子102Bの合計に保持されている電荷の放電量を制御するために、追加して容量素子を配置することが可能である。例えば、図1(B)、図1(C)に対して、容量素子を追加した場合の一例を図4(A)、図4(B)に示す。なお図4(A)乃至図4(F)で説明する回路構成は、上記図1(B)、図1(C)で示した回路構成を実現する一例として示したものである。なお、実際には図4(A)乃至図4(F)に示した複数のスイッチ及び容量素子以外に、配線間に設けられる複数のスイッチのオンまたはオフを制御することで、当該回路構成の接続関係を実現するものである。

#### 【0099】

図4(A)、図4(B)において、容量素子402Aの第1の端子は、トランジスタ101の第2の端子と導通状態にあり、容量素子402Aの第2の端子は、配線103と導通状態にある。なお、図4(B)では、容量素子402Aの各端子の導通状態は、図4(A)と同じであることが望ましい。一部が非導通状態にあってもよい。なお、ここでは図示しないが、図4(A)の前の期間に、トランジスタ101のしきい値電圧を補正するための期間が、図1(A)と同様にある。

#### 【0100】

同様に、図1(B)、図1(C)に対して容量素子を追加した場合の別の例を図4(C)、図4(D)に示す。容量素子402Bの第1の端子は、トランジスタ101の第2の端子と導通状態にあり、容量素子402Bの第2の端子(または第2の電極)は、配線106と導通状態にある。なお、図4(D)では、容量素子402Bの各端子の導通状態は、図4(C)と同じであることが望ましい。なお、一部が非導通状態にあってもよい。

#### 【0101】

例えば、図4などに示す回路が複数ある場合について考える。例としては、第1の色を表示するための第1の画素と、第2の色を表示するための第2の画素とを有しており、各々の画素はトランジスタ101に相当するトランジスタとして、第1の画素は、トランジスタ101Aを、第2の画素はトランジスタ101Bとを有しているとする。同様に、容量素子102Aに相当する容量素子として、第1の画素は、容量素子102A\_1を、第2の画素は容量素子102A\_2とを有しているとする。また、容量素子102Bに相当す

10

20

30

40

50

る容量素子として、第1の画素は、容量素子102B\_1を、第2の画素は容量素子102B\_2とを有しているとする。さらに、容量素子402A乃至容量素子402Cの少なくともいずれか一つに相当する容量素子として、第1の画素は、容量素子402A\_1を、第2の画素は容量素子402A\_2とを有しているとする。

#### 【0102】

そして、トランジスタ101AのW/Lが、トランジスタ101BのW/Lよりも大きい場合は、容量素子102A\_1と容量素子102B\_1の合計の容量値の方が、容量素子102A\_2と容量素子102B\_2の合計の容量値よりも大きいことが望ましい。または、容量素子402A\_1と容量素子402B\_1の合計の容量値の方が、容量素子402A\_2と容量素子402B\_2の合計の容量値よりも大きいことが望ましい。

容量素子102A\_1、容量素子102B\_1、容量素子402A\_1、及び容量素子402B\_1の合計の容量値の方が、容量素子102A\_2、容量素子102B\_2、容量素子402A\_2、及び容量素子402B\_2の合計の容量値よりも大きいことが望ましい。トランジスタ101Aから放電される電荷量が、トランジスタ101Bから放電される電荷量より大きくなることによって、電位が調整される。または、トランジスタ101Aのチャネル幅Wが、トランジスタ101Bのチャネル幅Wよりも大きい場合は、容量素子102A\_1の容量値の方が、容量素子102A\_2の容量値よりも大きいことが望ましい。または、容量素子402A\_1と容量素子402B\_1の合計の容量値の方が、容量素子402A\_2と容量素子402B\_2の合計の容量値よりも大きいことが望ましい。または、容量素子102A\_1、容量素子102B\_1、容量素子402A\_1、及び容量素子402B\_1の合計の容量値の方が、容量素子102A\_2、容量素子102B\_2、容量素子402A\_2、及び容量素子402B\_2の合計の容量値よりも大きいことが望ましい。または、トランジスタ101Aのチャネル長Lが、トランジスタ101Bのチャネル長Lよりも小さい場合は、容量素子102A\_1と容量素子102B\_1の合計の容量値の方が、容量素子102A\_2と容量素子102B\_2の合計の容量値よりも大きいことが望ましい。または、容量素子402A\_1と容量素子402B\_1の合計の容量値の方が、容量素子402A\_2と容量素子402B\_2の合計の容量値よりも大きいことが望ましい。または、容量素子102A\_1、容量素子102B\_1、容量素子402A\_1、及び容量素子402B\_1の合計の容量値の方が、容量素子102A\_2、容量素子102B\_2、容量素子402A\_2、容量素子402B\_2の合計の容量値よりも大きいことが望ましい。

#### 【0103】

なお、容量素子402A\_1と容量素子402B\_1の合計の容量値と、容量素子402A\_2と容量素子402B\_2の合計の容量値は異なっていて、容量素子102A\_1と容量素子102B\_1の合計と、容量素子102A\_2と容量素子102B\_2の合計の容量値は、概ね等しい、という状態になっていることも可能である。つまり、容量値の調整を、容量素子102A\_1と容量素子102B\_1の合計と容量素子102A\_2と容量素子102B\_2の合計ではなく、容量素子402A\_1と容量素子402A\_2の方を用いて行う、ということも可能である。容量素子102A\_1と容量素子102B\_1の合計と容量素子102A\_2と容量素子102B\_2の合計の大きさが異なる場合、映像信号の大きさに差が出てきてしまう可能性があるなど、他への影響が大きい場合がある。そのため、容量素子402A\_1と容量素子402A\_2の方を用いて容量値の調整を行うことが望ましい。

#### 【0104】

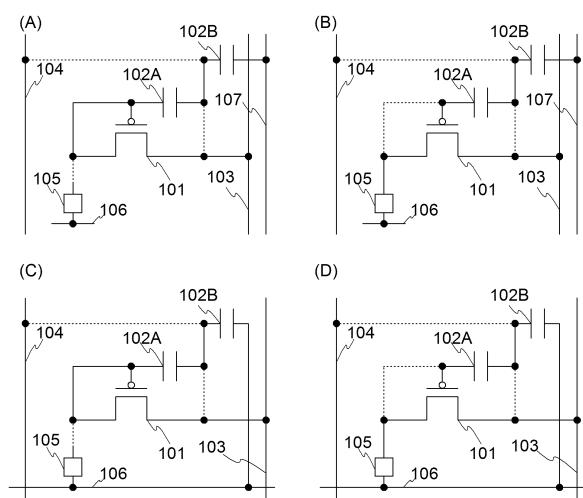

なお、回路の接続構造は、図1(A)乃至図1(C)に限定されない。例えば、図1(A)乃至図1(C)では、容量素子102Bの第2の端子が、配線103と導通状態にある。なお、少なくとも所定の期間において、一定の電位を供給する機能を有している配線と導通状態にあればよい。例えば、容量素子102Bの第2の端子が配線107に接続されている場合の例を、図5(A)、図1(B)に示す。同様に、容量素子102Bの第2の端子が配線106に接続されている場合の例を、図5(C)、図5(D)に示す。

10

20

30

40

50

## 【0105】

なお、図5(A)乃至図5(D)においても、図4(A)乃至図4(D)と同様に、追加で容量素子を配置することができる。一例として、図5(A)、図1(B)に対して、追加の容量素子402Cを配置した場合を図4(E)、図4(F)に示す。

## 【0106】

なお、図5(A)乃至図5(D)においても、図2(A)乃至図2(D)、図10(A)乃至図10(C)と同様に、スイッチを配置することができる。

## 【0107】

なお、図1(A)乃至図1(C)、図2(A)乃至図2(D)、図4(A)乃至図4(F)、図5(A)乃至図5(D)、図10(A)乃至図10(C)などにおいて、容量素子を複数配置し、直列接続、または、並列接続によって、複数の容量素子が配置する構成としてもよい。

10

## 【0108】

なお、図1(A)乃至図1(C)、図2(A)乃至図2(D)、図4(A)乃至図4(F)、図5(A)乃至図5(D)、図10(A)乃至図10(C)などにおいて、トランジスタ101がpチャネル型の場合について述べている。なお図6に示すように、Nチャネル型を用いることが可能である。例として、図1(A)乃至図1(C)に対して、nチャネル型を用いた場合を図6(A)乃至図6(C)に示す。これら以外の場合においても、同様に行うことが出来る。また図6(D)に示す回路構成は、図6(C)での表示素子105がEL素子で有る際の一例である。なお図6(A)乃至図6(D)で説明する回路構成は、上記図1(A)乃至図1(C)で示した回路構成を実現する一例として示したものである。なお、実際には図6(A)乃至図6(C)に示した複数のスイッチ及び容量素子以外に、配線間に設けられる複数のスイッチのオンまたはオフを制御することで、当該回路構成の接続関係を実現するものである。

20

## 【0109】

なお、トランジスタ101は、表示素子105に流れる電流の大きさを制御し、表示素子105を駆動する能力を有している場合が多い。

## 【0110】

なお、配線103は、表示素子105に電力を供給する能力を有している場合が多い。あるいは、配線103は、トランジスタ101に流れる電流を供給する能力を有している場合が多い。

30

## 【0111】

なお、配線107は、容量素子102A若しくは容量素子102Bに電圧を供給する能力を有している場合が多い。あるいは、トランジスタ101のゲート電位がノイズなどにより変動しにくくなるようにする機能を有している場合が多い。

## 【0112】

なお、トランジスタ101のしきい値電圧に応じた電圧とは、トランジスタ101のしきい値電圧と同じ大きさの電圧、または、トランジスタ101のしきい値電圧に近い大きさを有する電圧のことを言う。例えば、トランジスタ101のしきい値電圧が大きい場合は、しきい値電圧に応じた電圧も大きく、トランジスタ101のしきい値電圧が小さい場合は、しきい値電圧に応じた電圧も小さい。このように、しきい値電圧に応じて大きさが決まっているような電圧のことを、しきい値電圧に応じた電圧と呼ぶ。したがって、ノイズなどの影響により、僅かに異なっているような電圧も、しきい値電圧に応じた電圧と呼ぶ事が出来る。

40

## 【0113】

なお、表示素子105は、輝度、明るさ、反射率、透過率などを変化させるような機能を有する素子のことを言う。したがって、表示素子105の例としては、液晶素子、発光素子、有機EL素子、電気泳動素子などを用いることが出来る。

## 【0114】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に

50

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0115】

(実施の形態2)

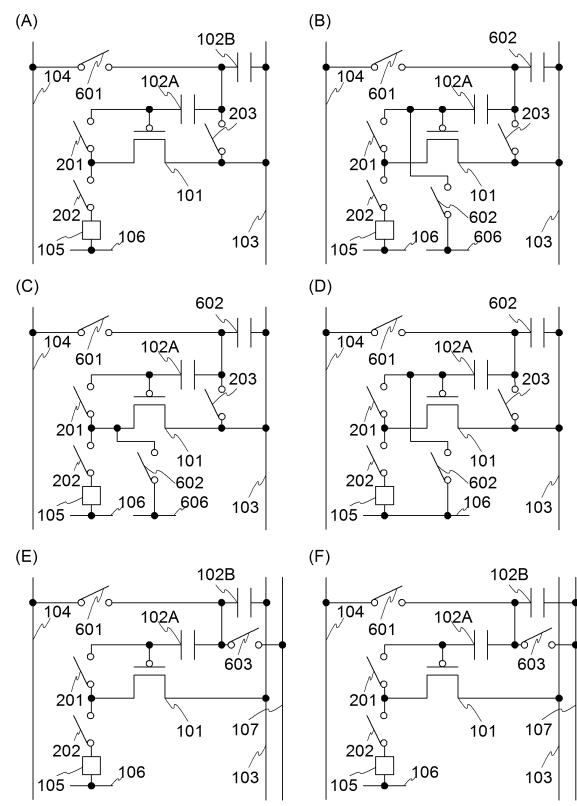

本実施の形態では、実施の形態1で述べた回路および駆動方法の具体例について示す。

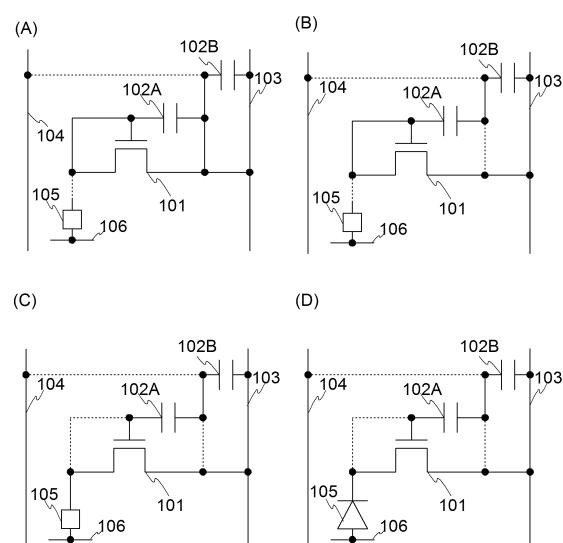

【0116】

図8(A)乃至図8(F)に、上記実施の形態1で述べた回路構成の具体例について示す。スイッチ601の第1の端子は、配線104に接続され、スイッチ601の第2の端子は、容量素子102Aの第2の端子、容量素子102Bの第1の端子、及びスイッチ203の第1の端子と接続されている。スイッチ203の第2の端子は、配線103、及びトランジスタ101の第1の端子と接続されている。容量素子102Aの第1の端子は、トランジスタ101のゲート、スイッチ201の第1の端子と接続されている。トランジスタ101の第2端子は、スイッチ201の第2の端子、及びスイッチ202の第1の端子と接続されている。スイッチ202の第2の端子は、表示素子105の第1の端子と接続されている。表示素子105の第2の端子は、配線106と接続されている。

【0117】

なお、トランジスタ101のゲートの電位、または第2の端子の電位を制御するために、スイッチを追加することが望ましい。ただし、これに限定されない。スイッチを追加した例を図8(B)、図8(C)に示す。図8(B)では、スイッチ602が追加され、その第1の端子はトランジスタ101のゲートに接続され、第2の端子は、配線606に接続されている。図8(C)では、スイッチ602が追加され、スイッチ603の第1の端子はトランジスタ101の第2の端子に接続され、スイッチ603の第2の端子は、配線606に接続されている。このような構成にすることにより、初期化のときなどにおいて、表示素子105に余分な電流が流れてしまうことを低減することができる。そのため、黒を表示する際の輝度をより低減することができるため、コントラストを向上することができる。

【0118】

なお、配線606は、別の配線と共有して、配線数を削減することができる。例えば、配線106と配線606とを共有して、配線106のみで構成した場合の例を図8(D)に示す。スイッチ602の第1の端子はトランジスタ101のゲートに接続され、第2の端子は、配線106に接続されている。このように、スイッチ602の第2の端子の接続先は、限定されず、様々な配線に接続させることができる。そして、別の配線と共有することにより、配線数を低減することができる。なお、容量素子102Bの第2の端子及びトランジスタ101の第1の端子は配線103と接続されているが、それぞれ別の配線に接続されていることが可能である。

【0119】

なお、回路の接続構成は、これに限定されない。所望の動作を行うように配置されていれば、様々な場所に、スイッチやトランジスタなどを配置することによって、様々な構成の回路を実現することができる。

【0120】

このように、実施の形態1で述べた構成についての例は、様々な構成をとることが出来る。さらに、他の構成においても、同様に、具体例を構成することができる。

【0121】

例として、図5(A)についての例を図8(E)、図8(F)に示す。なお、図8(E)では、スイッチ603の第2の端子は、配線107に接続されている。なお、図8(F)では、容量素子102Bの第2の端子は、配線107に接続されている。ただし、これに限定されない。

【0122】

さらに、図4(C)、図4(D)についての例を図9(A)に示す。容量素子402Bの第1の端子は、トランジスタ101の第2の端子に接続され、容量素子402Bの第2の端子は、配線106に接続されている。

10

20

30

40

50

## 【0123】

なお、配線 104 に供給する電位と、スイッチ 601 の導通または非導通とするタイミングとを制御することによって、スイッチ 203 を削減することが可能である。例えば、スイッチ 203 を削減した場合の例を図 9 (B) に示す。このように、スイッチ 203 の有無は特に限定されず、削減することが可能である。そして、スイッチ 203 を削減することにより、画素を構成する素子数を削減することが出来る。

## 【0124】

なお、容量素子 102A は、配線などとの交差容量による寄生容量を利用することにより、削減することが可能である。例えば、容量素子 102B 及びスイッチ 203 を削減した場合の例を図 9 (C) に示す。このように、容量素子 102B 及びスイッチ 203 の有無は特に限定されず、削除することが可能である。そして、容量素子 102A 及びスイッチ 203 を削減することにより、画素を構成する素子数を削減することが出来る。

10

## 【0125】

このように、図 8、図 9 では、実施の形態 1 で述べた構成についての例の一部を示したが、それ以外の例についても、同様に構成することが出来る。

## 【0126】

次に、動作方法について述べる。ここでは、図 8 (A) の回路を用いて述べるが、それ以外の回路についても、同様な動作方法を用いることが出来る。なお図 7 (A) 乃至図 7 (E) 中での各素子の符号については、図 8 (A) と同様であり、ここでは省略している。また、図 7 (A) 乃至図 7 (E) 中に示す点線矢印は、それぞれの期間における電流の流れを、可視化するために示したものである。

20

## 【0127】

まず、図 7 (A) に示す期間では、各ノードの電位の初期化を行う。これは、トランジスタ 101 のゲート、第 1 端子、及び第 2 端子の電位を、所定の電位に設定する動作である。これにより、トランジスタ 101 を導通状態とすることが出来る。または、容量素子 102A に、所定の電圧が供給される。または、容量素子 102A に保持される電荷の初期化がなされる。そのため、容量素子 102A は、電荷が保持されることとなる。スイッチ 201、スイッチ 202、スイッチ 203 は導通状態になっている。スイッチ 601 については、非導通状態になっていることが望ましい。ただし、これに限定されない。

## 【0128】

30

なお、配線 106 の電位は、配線 103 より低いことが望ましい。なお、電位は、これに限定されない。また、これらの電位は、トランジスタ 101 が p チャネル型の場合である。よって、トランジスタ 101 の極性が n チャネル型の場合は、電位の上下関係は逆であることが望ましい。

## 【0129】

次に、図 7 (B) に示す期間では、トランジスタ 101 のしきい値電圧のばらつきを補正するための動作を行う。なお当該期間は、図 1 (A) の期間に相当する期間である。これは、トランジスタ 101 のしきい値電圧に応じた電圧を、容量素子で保持することとなる。スイッチ 201、スイッチ 203 は、導通状態になっている。スイッチ 202、スイッチ 601 は、非導通状態になっていることが望ましい。このとき、容量素子 102A は、図 7 (A) の期間において蓄積された電荷があるため、その電荷が放電していく。そのため、トランジスタ 101 のゲートの電位は上昇していく、トランジスタ 101 のゲートとソースの間にトランジスタ 101 のしきい値電圧 (負の値) を保持するための電位に近づいていく。つまり、配線 103 より供給される電位よりも、トランジスタ 101 のしきい値電圧の絶対値の分だけ低い電位に近づいていく。そして、このとき、トランジスタ 101 のゲートとソースの間の電圧は、トランジスタ 101 のしきい値電圧に近づいていく。これらの動作により、しきい値電圧の取得を行うことが出来る。

40

## 【0130】

なお、容量素子 102A の電荷を放電する場合、ほぼ完全に放電することは可能である。その場合、トランジスタ 101 は、ほとんど電流が流れなくなっているため、トランジス

50

タ101のゲートとソースの間の電圧は、トランジスタ101のしきい値電圧に非常に近い大きさになっている。ただし、完全に放電する前に、放電を止めることも可能である。

#### 【0131】

なお、この期間において、容量素子102Aの電荷を放電する場合、その期間に違いがでても、大きな問題はない。なぜなら、ある程度の時間が経過すれば、ほぼ完全に放電されてしまうため、期間に長さが違っても、動作に与える影響は小さいからである。したがって、この動作は、線順次ではなく、点順次を用いて駆動させることが出来る。したがって、駆動回路の構成が簡単な構成で実現できる。そのため、図8に示すような回路を1つの画素としたとき、その画素がマトリクス状に配置された画素部と、画素部に信号を供給する駆動回路部とについて、両者を同じ種類のトランジスタを用いて構成すること、または同じ基板上に形成することが可能となる。ただしこれに限定されず、線順次駆動を用いたり、画素部と駆動回路部とを別々の基板上に形成することも可能である。

10

#### 【0132】

次に、図7(C)に示す期間では、映像信号(映像信号電圧)の入力を行う。スイッチ601は、導通状態になっている。スイッチ201、スイッチ202、スイッチ203は、非導通状態になっている。そして、配線104より容量素子102Bに映像信号が供給される。このとき、容量素子102Aの第2の端子と容量素子102Bの第1の端子が接続されるノードでは、映像信号に応じた電位の下降が行われる。つまり容量素子102Bに映像信号電圧が入力されることとなる。そして容量素子102Aの第1の端子側の電位は容量結合により、容量素子102Aに保持された電圧分だけ下降することとなる。そのため、トランジスタ101のゲートの電位は、配線104より供給される映像信号と、トランジスタ101のしきい値電圧(負の値)を足し合わせた電位に近づいていく。これらの動作により、映像信号の入力(映像信号電圧の取得)と、しきい値電圧の取得とを行うことが出来る。

20

#### 【0133】

このような動作により、容量素子102Aには、しきい値電圧に応じた電圧と映像信号電圧とを足し合わせた電圧が供給され、その電圧に応じた電荷が蓄積されることとなる。

#### 【0134】

次に、図7(D)に示す期間では、トランジスタ101の移動度などの電流特性のばらつきの補正を行う。なお当該期間は、図1(B)の期間に相当する期間である。スイッチ201は、導通状態になっている。スイッチ202、スイッチ203、及びスイッチ601は、非導通状態になっている。このような状態にすることにより、容量素子102A及び容量素子102Bに蓄積された電荷が、トランジスタ101を介して放電されていく。このようにして、トランジスタ101を介してわずかに放電されることにより、トランジスタ101の電流のばらつきの影響を低減することが出来る。

30

#### 【0135】

次に、図7(E)に示す期間では、トランジスタ101を介して、表示素子105に電流を供給する。なお当該期間は、図1(C)の期間に相当する期間である。スイッチ203は、導通状態になっている。スイッチ201、スイッチ202、及びスイッチ601は、非導通状態になっている。このとき、トランジスタ101のゲートとソースの間の電圧は、しきい値電圧に応じた電圧と映像信号電圧との和の電圧から、トランジスタ101の電流特性に応じた電圧が差し引かれた電圧となっている。したがって、トランジスタ101の電流特性のばらつきの影響を低減することができ、表示素子105には、適切な大きさの電流を供給することが出来る。

40

#### 【0136】

なお、図8(C)、(D)の回路構成の場合、図7(A)に示す初期化の期間においては、スイッチ602を介して、トランジスタ101の第2の端子の電位を制御することが可能である。そして、スイッチ202については、非導通状態とすることが望ましい。スイッチ602を介して初期化を行うことにより、表示素子側に流れる電流をなくすことが出来る。なお、図7(B)以降については、同様に動作させればよい。

50

## 【0137】

なお、図7において、各動作への切り替わり時において、その動作の間に、別の動作や別の期間が設けられていることも可能である。例えば、図7(D)に示すような状態を、図7(A)と図7(B)の間に設けても良い。このような期間を設けても、支障がないため、問題はない。

## 【0138】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

## 【0139】

(実施の形態3)

10

本実施の形態では、実施の形態1で述べた回路および駆動方法の別の具体例または変形例について示す。

## 【0140】

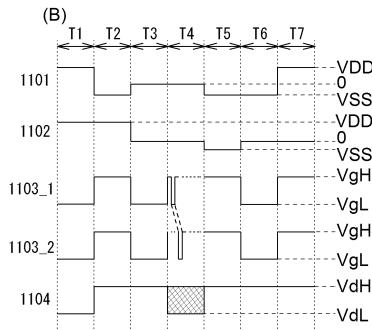

図11(A)に、図1、図9(C)、図10(C)の具体例について示す。図11(A)では、配線1101、配線1102、配線1103、配線1104、容量素子1105、トランジスタ1106、トランジスタ1107、表示素子1108について示している。なお、配線1101は、図9(C)での配線103に対応する。なお、配線1102は、図9(C)での配線106に対応する。なお、配線1104は、図9(C)での配線104に対応する。なお、容量素子1105は、図9(C)での容量素子102Bに対応する。なお、トランジスタ1106は、図9(C)でのトランジスタ101に対応する。なお、トランジスタ1107は、図9(C)での表示素子105に対応する。なおトランジスタ1106及びトランジスタ1107は共にpチャネル型であるとして説明する。なお表示素子としてEL素子を一例としてあげて説明を行うものとする。

20

## 【0141】

図11(A)に示す回路について、図11(B)に示すタイミングチャートに基づいて、動作の説明を行う。次に、図11(B)では、第1の期間T1、第2の期間T2、第3の期間T3、第4の期間T4、第5の期間T5、第6の期間T6、第7の期間T7に分けて、各配線の電位について説明する。なお配線1101、配線1102の電位は、「VDD」(高電源電位に基づく信号、H信号)、「0」(グラウンド電位に基づく信号、GND)、「VSS」(低電源電位に基づく信号、L信号)の3段階として説明するものとする。また、配線1103は、表示部の走査線として機能しうる配線であり、表示部は実際には走査線の数に対応して、1103\_1乃至1103\_N(Nは自然数)を有する。図11(B)では、配線1103\_1、及び配線1103\_2の電位は、「VgH」、「VgL」の2段階として説明するものとする。なお、以下の説明では、配線1103\_1に着目して説明することとする。また配線1104は、表示部の信号線として機能しうる配線であり、配線1104の電位は、「VdH」から「VdL」の範囲の値を取るものとして説明する。なお、各配線が取り得る電位は、これに限定されず、特に動作に支障がなければ、他の電位であってもよい。

30

## 【0142】

第1の期間T1について、説明する。第1の期間T1では、配線1101がVDD、配線1102がVDD、配線1103\_1がVgL、配線1104がVdLとなる。その結果、容量素子1105に蓄えられた電荷が放電され、各ノードの電位が初期化されることとなる。次に第2の期間T2について説明する。第2の期間T2では、配線1101がVSS、配線1102がVDD、配線1103\_1がVgH、配線1104がVdHとなる。その結果、容量素子1105への電荷の充電がなされることとなる。次に第3の期間T3について説明する。第3の期間T3では、配線1101が「0」、配線1102が「0」、配線1103\_1がVgL、配線1104がVdHとなる。その結果、容量素子1105からの電荷の放電が行われ、トランジスタ1106のゲート-ソース間の寄生容量に、トランジスタ1106のしきい値電圧が保持されることとなる。すなわち、第3の期間T3では、トランジスタのしきい値電圧を取得している期間(図1(A))に相当するもの

40

50

となる。次に第4の期間T4について説明する。第4の期間T4では、配線1101が「0」、配線1102が「0」となる。このとき、配線1103\_2は、配線1103\_1と引き続いて、走査が行われる。そして、配線1104では各画素に入力される電位が切り替わっていき、各画素へのデータの書き込みが行われることとなる。次に第5の期間T5について説明する。第5の期間T5では、配線1101がVSS、配線1102がVSS、配線1103\_1がVgH、配線1104がVdHとなる。その結果、表示素子1108に蓄積された電荷の初期化を行うこととなる。次に第6の期間T6について説明する。第6の期間T6では、配線1101がVSS、配線1102が「0」、配線1103\_1がVgL、配線1104がVdHとなる。その結果、容量素子1105から、トランジスタの移動度などの電流特性のばらつきに応じて、電荷の放電を行い、トランジスタ1106の移動度などの電流特性のばらつきを補正することとなる。すなわち、第6の期間T6では、トランジスタの移動度などの電流特性のばらつきを補正する期間(図1(B))に相当するものとなる。次に第7の期間T7について説明する。第7の期間T7では、配線1101がVDD、配線1102が「0」、配線1103\_1がVgH、配線1104がVdHとなる。その結果、表示素子1108に電流を流すこととなる。すなわち、第7の期間T7では、表示を行う期間(図1(C))に相当するものとなる。

#### 【0143】

なお、回路の接続構成は、これに限定されない。所望の動作を行うことができるように配置されれば、様々な場所に、スイッチやトランジスタなどを配置することによって、様々な構成の回路を実現することができる。

10

20

#### 【0144】

例えば、図11(C)には、トランジスタ1106及びトランジスタ1107の極性をnチャネル型とした際の回路を示している。トランジスタ1106及びトランジスタ1107の極性を反転させた際には、スイッチとなるトランジスタ1107の導通または非導通を制御するために、配線1103に入力される信号の電位を反転させて用い、表示素子1108を配線1101に接続されるように設けることが好ましい。

#### 【0145】

このように、実施の形態3で述べた構成についての例は、様々な構成をとることが出来る。さらに、図1、図9(C)、図10(C)の具体例について示したが、他の図においても、同様に、具体例を構成することが出来る。

30

#### 【0146】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0147】

##### (実施の形態4)

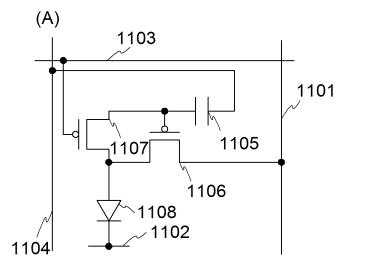

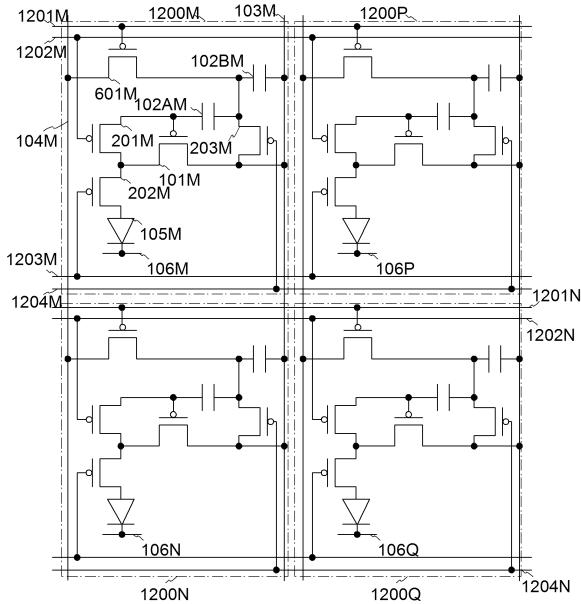

本実施の形態では、実施の形態1乃至実施の形態3で述べた回路について、具体例を示す。

#### 【0148】

例として、図8(A)に示す回路が1つの画素を構成し、その画素がマトリクス状に配置されている場合の例について、図12に示す。なお、図12では、スイッチは、pチャネル型のトランジスタを用いて実現している。ただし、これに限定されず、別の極性のトランジスタを用いたり、両方の極性のトランジスタを用いたり、ダイオードまたはダイオード接続されたトランジスタなどを用いたりすることも可能である。

40

#### 【0149】

図8(A)に示す回路は、1つ分の画素である画素1200Mを構成している。画素1200Mと同様な構成の画素が、画素1200N、画素1200P、画素1200Qとして、マトリクス状に配置されている。各画素では、上下、左右の配置に応じて、同じ配線に接続されている場合がある。

#### 【0150】

次に、図8(A)の各要素と、画素1200Mにおける各要素との対応を、以下に示す。

50

配線 104 は、配線 104M に対応し、配線 103 は、配線 103M に対応し、スイッチ 601 は、トランジスタ 601M に対応し、スイッチ 201 は、トランジスタ 201M に対応し、トランジスタ 101 は、トランジスタ 101M に対応し、スイッチ 202 は、トランジスタ 202M に対応し、スイッチ 203 は、トランジスタ 203M に対応し、容量素子 102A は容量素子 102AM に対応し、容量素子 102B は容量素子 102BM に対応し、表示素子 105 は、発光素子 105M に対応し、配線 106 は、配線 106M に対応する。

【0151】

トランジスタ 601M のゲートは、配線 1201M と接続されている。トランジスタ 201M のゲートは、配線 1202M と接続されている。トランジスタ 202M のゲートは、配線 1203M と接続されている。トランジスタ 203M のゲートは、配線 1204M と接続されている。

【0152】

なお、各々のトランジスタのゲートに接続されている配線は、別の画素の配線または同じ画素の別の配線に接続されていることが可能である。

【0153】

なお、配線 106M は、配線 106P、配線 106N、配線 106Q と接続されることが可能である。

【0154】

図 12 と同様に、様々な回路を構成することが可能である。

【0155】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0156】

(実施の形態 5)

次に、表示装置の別の構成例およびその駆動方法について説明する。本実施の形態においては、表示装置の外部から入力される画像（入力画像）の動きを補間する画像を、複数の入力画像を基にして表示装置の内部で生成し、当該生成された画像（生成画像）と、入力画像とを順次表示させる方法について説明する。なお、生成画像を、入力画像の動きを補間するような画像とすることで、動画の動きを滑らかにすることができる、さらに、ホールド駆動による残像等によって動画の品質が低下する問題を改善できる。ここで、動画の補間について、以下に説明する。動画の表示は、理想的には、個々の画素の輝度をリアルタイムに制御することで実現されるものであるが、画素のリアルタイム個別制御は、制御回路の数が膨大なものとなる問題、配線スペースの問題、および入力画像のデータ量が膨大なものとなる問題等が存在し、実現が困難である。したがって、表示装置による動画の表示は、複数の静止画を一定の周期で順次表示することで、表示が動画に見えるようにして行なわれている。この周期（本実施の形態においては入力画像信号周期と呼び、 $T_{in}$  と表す）は規格化されており、例として、NTSC 規格では 1/60 秒、PAL 規格では 1/50 秒である。この程度の周期でも、インパルス型表示装置である CRT においては動画表示に問題は起こらなかった。しかし、ホールド型表示装置においては、これらの規格に準じた動画をそのまま表示すると、ホールド型であることに起因する残像等により表示が不鮮明となる不具合（ホールドぼけ：hold blur）が発生してしまう。ホールドぼけは、人間の目の追従による無意識的な動きの補間と、ホールド型の表示との不一致（discrepancy）で認識されるものであるので、従来の規格よりも入力画像信号周期を短くする（画素のリアルタイム個別制御に近づける）ことで低減させることができるが、入力画像信号周期を短くすることは規格の変更を伴い、さらに、データ量も増大することになるので、困難である。しかしながら、規格化された入力画像信号を基にして、入力画像の動きを補間するような画像を表示装置内部で生成し、当該生成画像によって入力画像を補間して表示することで、規格の変更またはデータ量の増大なしに、ホールドぼけを低減できる。このように、入力画像信号を基にして表示装置内部で画像信号を生成

10

20

30

40

50

し、入力画像の動きを補間することを、動画の補間と呼ぶこととする。

【0157】

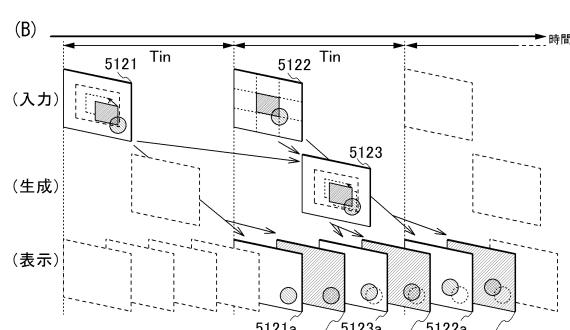

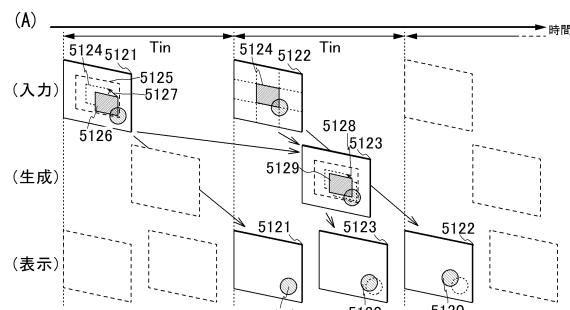

本実施の形態における動画の補間方法によって、動画ぼけを低減させることができる。本実施の形態における動画の補間方法は、画像生成方法と画像表示方法に分けることができる。そして、特定のパターンの動きについては別の画像生成方法および／または画像表示方法を用いることで、効果的に動画ぼけを低減させることができる。図13(A)および(B)は、本実施の形態における動画の補間方法の一例を説明するための模式図である。図13(A)および(B)において、横軸は時間であり、横方向の位置によって、それぞれの画像が扱われるタイミングを表している。「入力」と記された部分は、入力画像信号が入力されるタイミングを表している。ここでは、時間的に隣接する2つの画像として、画像5121および画像5122に着目している。入力画像は、周期 $T_{in}$ の間隔で入力される。なお、周期 $T_{in}$ 1つ分の長さを、1フレームもしくは1フレーム期間と記すことがある。「生成」と記された部分は、入力画像信号から新しく画像が生成されるタイミングを表している。ここでは、画像5121および画像5122を基にして生成される生成画像である、画像5123に着目している。「表示」と記された部分は、表示装置に画像が表示されるタイミングを表している。なお、着目している画像以外の画像については破線で記しているのみであるが、着目している画像と同様に扱うことによって、本実施の形態における動画の補間方法の一例を実現できる。

【0158】

本実施の形態における動画の補間方法の一例は、図13(A)に示されるように、時間的に隣接した2つの入力画像を基にして生成された生成画像を、当該2つの入力画像が表示されるタイミングの間隙に表示させることで、動画の補間を行うことができる。このとき、表示画像の表示周期は、入力画像の入力周期の1/2とされることが好ましい。ただし、これに限定されず、様々な表示周期とすることができます。例えば、表示周期を入力周期の1/2より短くすることで、動画をより滑らかに表示できる。または、表示周期を入力周期の1/2より長くすることで、消費電力を低減できる。なお、ここでは、時間的に隣接した2つの入力画像を基にして画像を生成しているが、基にする入力画像は2つに限定されず、様々な数を用いることができる。例えば、時間的に隣接した3つ(3つ以上でも良い)の入力画像を基にして画像を生成すれば、2つの入力画像を基にする場合よりも、精度の良い生成画像を得ることができる。なお、画像5121の表示タイミングを、画像5122の入力タイミングと同時刻、すなわち入力タイミングに対する表示タイミングを1フレーム遅れとしているが、本実施の形態における動画の補間方法における表示タイミングはこれに限定されず、様々な表示タイミングを用いることができる。例えば、入力タイミングに対する表示タイミングを1フレーム以上遅らせることができる。こうすることで、生成画像である画像5123の表示タイミングを遅くすることができるので、画像5123の生成にかかる時間に余裕を持たせることができ、消費電力および製造コストの低減につながる。なお、入力タイミングに対する表示タイミングをあまりに遅くすると、入力画像を保持しておく期間が長くなり、保持にかかるメモリ容量が増大してしまうので、入力タイミングに対する表示タイミングは、1フレーム遅れから2フレーム遅れ程度が好ましい。

【0159】

ここで、画像5121および画像5122を基にして生成される画像5123の、具体的な生成方法の一例について説明する。動画を補間するためには入力画像の動きを検出する必要があるが、本実施の形態においては、入力画像の動きの検出のために、ブロックマッチング法と呼ばれる方法を用いることができる。ただし、これに限定されず、様々な方法(画像データの差分をとる方法、フーリエ変換を利用する方法等)を用いることができる。ブロックマッチング法においては、まず、入力画像1枚分の画像データ(ここでは画像5121の画像データ)を、データ記憶手段(半導体メモリ、RAM等の記憶回路等)に記憶させる。そして、次のフレームにおける画像(ここでは画像5122)を、複数の領域に分割する。なお、分割された領域は、図13(A)のように、同じ形状の矩形とする

10

20

30

40

50

ことができるが、これに限定されず、様々なもの（画像によって形状または大きさを変える等）とすることができる。その後、分割された領域毎に、データ記憶手段に記憶させた前のフレームの画像データ（ここでは画像 5121 の画像データ）とデータの比較を行い、画像データが似ている領域を探索する。図 13 (A) の例においては、画像 5122 における領域 5124 とデータが似ている領域を画像 5121 の中から探索し、領域 5126 が探索されたものとしている。なお、画像 5121 の中を探索するとき、探索範囲は限定されることが好ましい。図 13 (A) の例においては、探索範囲として、領域 5124 の面積の 4 倍程度の大きさである、領域 5125 を設定している。なお、探索範囲をこれより大きくすることで、動きの速い動画においても検出精度を高くすることができる。ただし、あまりに広く探索を行なうと探索時間が膨大なものとなってしまい、動きの検出の実現が困難となるため、領域 5125 は、領域 5124 の面積の 2 倍から 6 倍程度の大きさであることが好ましい。その後、探索された領域 5126 と、画像 5122 における領域 5124 との位置の違いを、動きベクトル 5127 として求める。動きベクトル 5127 は領域 5124 における画像データの 1 フレーム期間の動きを表すものである。そして、動きの中間状態を表す画像を生成するため、動きベクトルの向きはそのまま大きさを変えた画像生成用ベクトル 5128 を作り、画像 5121 における領域 5126 に含まれる画像データを、画像生成用ベクトル 5128 に従って移動させることで、画像 5123 における領域 5129 内の画像データを形成させる。これらの一連の処理を、画像 5122 における全ての領域について行なうことで、画像 5123 が生成されることができる。そして、入力画像 5121、生成画像 5123、入力画像 5122 を順次表示することで、動画を補間することができる。なお、画像中の物体 5130 は、画像 5121 および画像 5123 において位置が異なっている（つまり動いている）が、生成された画像 5123 は、画像 5121 および画像 5122 における物体の中間点となっている。このような画像を表示することで、動画の動きを滑らかにすることができる、残像等による動画の不鮮明さを改善できる。

10 20 30 40 50

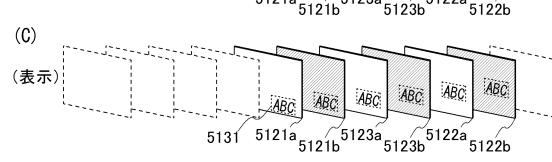

#### 【0160】

なお、画像生成用ベクトル 5128 の大きさは、画像 5123 の表示タイミングに従って決められることができる。図 13 (A) の例においては、画像 5123 の表示タイミングは画像 5121 および画像 5122 の表示タイミングの中間点（1/2）としているため、画像生成用ベクトル 5128 の大きさは動きベクトル 5127 の 1/2 としているが、他にも、例えば、表示タイミングが 1/3 の時点であれば、大きさを 1/3 とし、表示タイミングが 2/3 の時点であれば、大きさを 2/3 とすることができる。

#### 【0161】

なお、このように、様々な動きベクトルを持った複数の領域をそれぞれ動かして新しい画像を作る場合は、移動先の領域内に他の領域が既に移動している部分（重複）や、どこの領域からも移動されてこない部分（空白）が生じることもある。これらの部分については、データを補正することができる。重複部分の補正方法としては、例えば、重複データの平均をとる方法、動きベクトルの方向等で優先度をつけておき、優先度の高いデータを生成画像内のデータとする方法、色（または明るさ）はどちらかを優先させるが明るさ（または色）は平均をとる方法、等を用いることができる。空白部分の補正方法としては、画像 5121 または画像 5122 の当該位置における画像データをそのまま生成画像内のデータとする方法、画像 5121 または画像 5122 の当該位置における画像データの平均をとる方法、等を用いることができる。そして、生成された画像 5123 を、画像生成用ベクトル 5128 の大きさに従ったタイミングで表示することで、動画の動きを滑らかにすることができる、さらに、ホールド駆動による残像等によって動画の品質が低下する問題を改善できる。

#### 【0162】

本実施の形態における動画の補間方法の他の例は、図 13 (B) に示されるように、時間的に隣接した 2 つの入力画像を基にして生成された生成画像を、当該 2 つの入力画像が表示されるタイミングの間隙に表示させる際に、それぞれの表示画像をさらに複数のサブ画

像に分割して表示することで、動画の補間を行なうことができる。この場合、画像表示周期が短くなることによる利点だけでなく、暗い画像が定期的に表示される（表示方法がインパルス型に近づく）ことによる利点も得ることができる。つまり、画像表示周期が画像入力周期に比べて $1/2$ の長さにするだけの場合よりも、残像等による動画の不鮮明さをさらに改善できる。図13（B）の例においては、「入力」および「生成」については図13（A）の例と同様な処理を行なうことができるので、説明を省略する。図13（B）の例における「表示」は、1つの入力画像または/および生成画像を複数のサブ画像に分割して表示を行うことができる。具体的には、図13（B）に示すように、画像5121をサブ画像5121aおよび5121bに分割して順次表示することで、人間の目には画像5121が表示されたように知覚させ、画像5123をサブ画像5123aおよび5123bに分割して順次表示することで、人間の目には画像5123が表示されたように知覚させ、画像5122をサブ画像5122aおよび5122bに分割して順次表示することで、人間の目には画像5122が表示されたように知覚させる。すなわち、人間の目に知覚される画像としては図13（A）の例と同様なものとしつつ、表示方法をインパルス型に近づけることができるので、残像等による動画の不鮮明さをさらに改善できる。なお、サブ画像の分割数は、図13（B）においては2つとしているが、これに限定されず様々な分割数を用いることができる。なお、サブ画像が表示されるタイミングは、図13（B）においては等間隔（ $1/2$ ）としているが、これに限定されず様々な表示タイミングを用いることができる。例えば、暗いサブ画像（5121b、5122b、5123b）の表示タイミングを早くする（具体的には、 $1/4$ から $1/2$ のタイミング）ことで、表示方法をよりインパルス型に近づけることができるため、残像等による動画の不鮮明さをさらに改善できる。または、暗いサブ画像の表示タイミングを遅くする（具体的には、 $1/2$ から $3/4$ のタイミング）ことで、明るい画像の表示期間を長くすることができるので、表示効率を高めることができ、消費電力を低減できる。

#### 【0163】

本実施の形態における動画の補間方法の他の例は、画像内で動いている物体の形状を検出し、動いている物体の形状によって異なる処理を行なう例である。図13（C）に示す例は、図13（B）の例と同様に表示のタイミングを表しているが、表示されている内容が、動く文字（スクロールテキスト、字幕、テロップ等とも呼ばれる）である場合を示している。なお、「入力」および「生成」については、図13（B）と同様としても良いため、図示していない。ホールド駆動における動画の不鮮明さは、動いているものの性質によって程度が異なることがある。特に、文字が動いている場合に顕著に認識されることが多い。なぜならば、動く文字を読む際にはどうしても視線を文字に追従させてしまうので、ホールドぼけが発生しやすくなるためである。さらに、文字は輪郭がはっきりしていることが多いため、ホールドぼけによる不鮮明さがさらに強調されてしまうこともある。すなわち、画像内を動く物体が文字かどうかを判別し、文字である場合はさらに特別な処理を行なうことは、ホールドぼけの低減のためには有効である。具体的には、画像内を動いている物体に対し、輪郭検出または/およびパターン検出等を行なって、当該物体が文字であると判断された場合は、同じ画像から分割されたサブ画像同士であっても動き補間を行い、動きの中間状態を表示するようにして、動きを滑らかにことができる。当該物体が文字ではないと判断された場合は、図13（B）に示すように、同じ画像から分割されたサブ画像であれば動いている物体の位置は変えずに表示することができる。図13（C）の例では、文字であると判断された領域5131が、上方向に動いている場合を示しているが、画像5121aと画像5121bとで、領域5131の位置を異ならせている。画像5123aと画像5123b、画像5122aと画像5122bについても同様である。こうすることで、ホールドぼけが特に認識されやすい動く文字については、通常の動き補償倍速駆動よりもさらに動きを滑らかにすることができるので、残像等による動画の不鮮明さをさらに改善できる。

#### 【0164】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

**【0165】**

(実施の形態6)

本実施の形態では、表示装置の一例について説明する。

**【0166】**

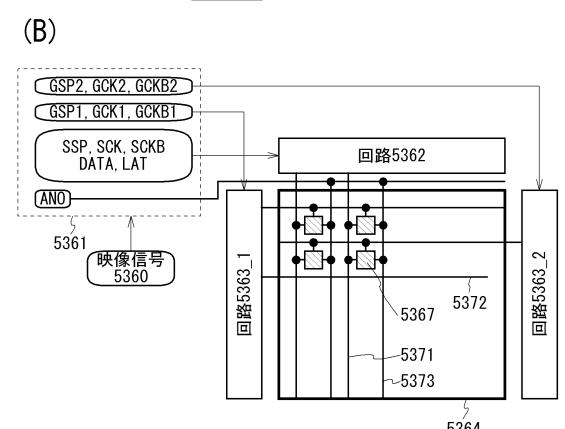

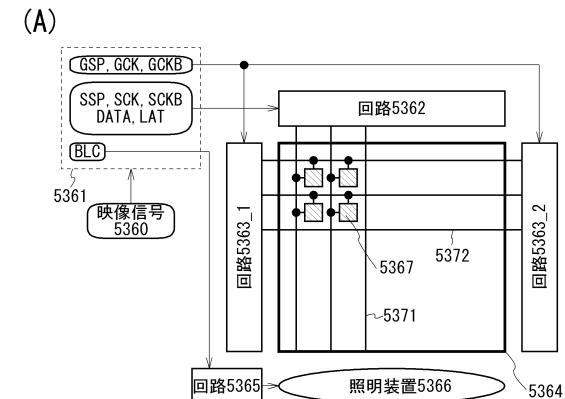

まず、図14(A)を参照して、液晶表示装置のシステムブロックの一例について説明する。液晶表示装置は、回路5361、回路5362、回路5363\_1、回路5363\_2、画素部5364、回路5365、及び照明装置5366を有する。画素部5364には、複数の配線5371が回路5362から延伸して配置され、複数の配線5372が回路5363\_1、及び回路5363\_2から延伸して配置されている。そして、複数の配線5371と複数の配線5372との交差領域には、各々、液晶素子などの表示素子を有する画素5367がマトリクス状に配置されている。10

**【0167】**

回路5361は、映像信号5360に応じて、回路5362、回路5363\_1、回路5363\_2、及び回路5365に、信号、電圧、又は電流などを供給する機能を有し、コントローラ、制御回路、タイミングジェネレータ、電源回路、又はレギュレータなどとして機能することが可能である。本実施の形態では、一例として、回路5361は、回路5362に、信号線駆動回路用スタート信号(SSP)、信号線駆動回路用クロック信号(SCK)、信号線駆動回路用反転クロック信号(SCKB)、ビデオ信号用データ(DATA)、ラッチ信号(LAT)を供給するものとする。または、回路5361は、一例として、回路5363\_1、及び回路5363\_2に、走査線駆動回路用スタート信号(GSP)、走査線駆動回路用クロック信号(GCK)、及び走査線駆動回路用反転クロック信号(GCKB)を供給するものとする。または、回路5361は、回路5365に、バックライト制御信号(BLC)を供給するものとする。ただし、これに限定されず、回路5361は、他にも様々な信号、様々な電圧、又は様々な電流などを、回路5362、回路5363\_1、回路5363\_2、及び回路5365に供給することが可能である。20

**【0168】**

回路5362は、回路5361から供給される信号(例えば、SSP、SCK、SCKB、DATA、LAT)に応じて、ビデオ信号を複数の配線5371に出力する機能を有し、信号線駆動回路として機能することが可能である。回路5363\_1、及び回路5363\_2は、回路5361から供給される信号(GSP、GCK、GCKB)に応じて、走査信号を複数の配線5372に出力する機能を有し、走査線駆動回路として機能することが可能である。回路5365は、回路5361から供給される信号(BLC)に応じて、照明装置5366に供給する電力の量、又は時間などを制御することによって、照明装置5366の輝度(又は平均輝度)を制御する機能を有し、電源回路として機能することが可能である。30

**【0169】**

なお、複数の配線5371にビデオ信号が入力される場合、複数の配線5371は、信号線、ビデオ信号線、又はソース線などとして機能することが可能である。複数の配線5372に走査信号が入力される場合、複数の配線5372は、信号線、走査線、又はゲート線などとして機能することが可能である。ただし、これに限定されない。40

**【0170】**

なお、回路5363\_1、及び回路5363\_2に、同じ信号が回路5361から入力される場合、回路5363\_1が複数の配線5372に出力する走査信号と、回路5363\_2が複数の配線5372に出力する走査信号とは、おおむね等しいタイミングとなる場合が多い。したがって、回路5363\_1、及び回路5363\_2が駆動する負荷を小さくすることができる。よって、表示装置を大きくすることができる。または、表示装置を高精細にすることができます。または、回路5363\_1、及び回路5363\_2が有するトランジスタのチャネル幅を小さくすることができるので、狭額縁な表示装置を得ることができます。ただし、これに限定されず、回路5361は、回路5363\_1と回路53650

3\_2 とに別々の信号を供給することが可能である。

【0171】

なお、回路 5363\_1 と回路 5363\_2 の一方を省略することが可能である。

【0172】

なお、画素部 5364 には、容量線、電源線、走査線などの配線を新たに配置することが可能である。そして、回路 5361 は、これらの配線に信号又は電圧などを出力することが可能である。または、回路 5363\_1 又は回路 5363\_2 と同様の回路を新たに追加し、この新たに追加した回路は、新たに追加した配線に走査信号などの信号を出力することが可能である。

【0173】

なお、画素 5367 が表示素子として E L 素子などの発光素子を有することが可能である。この場合、図 14 (B) に示すように、表示素子が発光することが可能なので、回路 5365、及び照明装置 5366 は省略されることが可能である。そして、表示素子に電力を供給するために、電源線として機能することが可能な複数の配線 5373 を画素部 5364 に配置することが可能である。回路 5361 は、電圧 (A N O) という電源電圧を配線 5373 に供給することが可能である。この配線 5373 は、画素の色要素別に接続されることが可能であるし、全ての画素に共通して接続されることが可能である。

【0174】

なお、図 14 (B) では、一例として、回路 5361 は、回路 5363\_1 と回路 5363\_2 とに別々の信号を供給する場合の一例を示す。回路 5361 は、走査線駆動回路用スタート信号 (G S P 1)、走査線駆動回路用クロック信号 (G C K 1)、及び走査線駆動回路用反転クロック信号 (G C K B 1) などの信号を回路 5363\_1 に供給する。そして、回路 5361 は、走査線駆動回路用スタート信号 (G S P 2)、走査線駆動回路用クロック信号 (G C K 2)、及び走査線駆動回路用反転クロック信号 (G C K B 2) などの信号を回路 5363\_2 に供給する。この場合、回路 5363\_1 は、複数の配線 5372 のうち奇数行目の配線のみを走査し、回路 5363\_2 は、複数の配線 5372 のうち偶数行目の配線のみを走査することが可能になる。よって、回路 5363\_1、及び回路 5363\_2 の駆動周波数を小さくできるので、消費電力の低減を図ることができる。または、1 段分のフリップフロップをレイアウトすることが可能な面積を大きくすることができます。よって、表示装置を高精細にすることができる。または、表示装置を大型にすることができる。ただし、これに限定されず、図 14 (A) と同様に、回路 5361 は、回路 5363\_1 と回路 5363\_2 と同じ信号を出力することが可能である。

【0175】

なお、図 14 (B) と同様に、図 14 (A) においても、回路 5361 は、回路 5363\_1 と回路 5363\_2 とに別々の信号を供給することが可能である。

【0176】

以上、表示装置のシステムブロックの一例について説明した。

【0177】

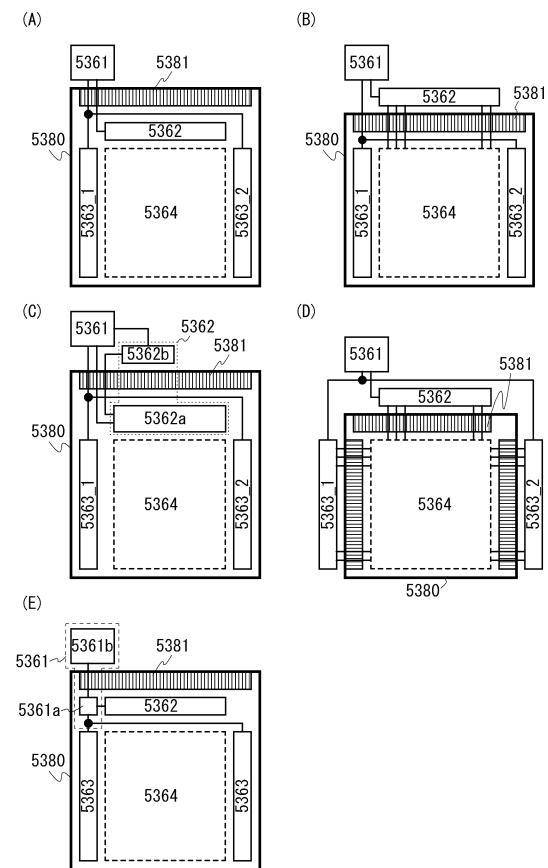

次に、表示装置の構成の一例について、図 15 (A)、(B)、(C)、(D)、及び (E) を参照して説明する。

【0178】

図 15 (A) では、画素部 5364 に信号を出力する機能を有する回路 (例えば、回路 5362、回路 5363\_1、及び回路 5363\_2 など) は、画素部 5364 と同じ基板 5380 に形成される。そして、回路 5361 は、画素部 5364 とは別の基板に形成される。こうして、外部部品の数が減るので、コストの低減を図ることができる。または、基板 5380 に入力される信号又は電圧の数が減るので、基板 5380 と、外部部品との接続数を減らすことができる。よって、信頼性の向上、又は歩留まりの向上を図ることができる。

【0179】

なお、回路が画素部 5364 とは別の基板に形成される場合、当該基板は、T A B (T a

10

20

30

40

50

pe Automated Bonding) 方式によって FPC (Flexible Printed Circuit) に実装されることが可能である。または、当該基板は、COG (Chip on Glass) 方式によって画素部 5364 と同じ基板 5380 に実装することが可能である。

【0180】

なお、回路が画素部 5364 とは別の基板に形成される場合、当該基板には、単結晶半導体を用いたトランジスタを形成することが可能である。したがって、当該基板に形成される回路は、駆動周波数の向上、駆動電圧の向上、出力信号のばらつきの低減などのメリットを得ることができる。

【0181】

なお、外部回路からは、入力端子 5381 を介して信号、電圧、又は電流などが入力される場合が多い。

【0182】

図 15 (B) では、駆動周波数が低い回路 (例えば、回路 5363\_1、回路 5363\_2) は、画素部 5364 と同じ基板 5380 に形成される。そして、回路 5361、及び回路 5362 は、画素部 5364 とは別の基板に形成される。こうして、移動度が小さいトランジスタによって、基板 5380 に形成される回路を構成することが可能になる。よって、トランジスタの半導体層として、非単結晶半導体、微結晶半導体、有機半導体、又は酸化物半導体などを用いることが可能になる。したがって、表示装置の大型化、工程数の削減、コストの低減、又は歩留まりの向上などを図ることができる。

【0183】

なお、図 15 (C) に示すように、回路 5362 の一部 (回路 5362a) が画素部 5364 と同じ基板 5380 に形成され、残りの回路 5362 (回路 5362b) が画素部 5364 とは別の基板に形成されることが可能である。回路 5362a は、移動度が低いトランジスタによって構成することが可能な回路 (例えば、シフトレジスタ、セレクタ、スイッチなど) を有する場合が多い。そして、回路 5362b は、移動度が高く、特性ばらつきが小さいトランジスタによって構成することが好ましい回路 (例えば、シフトレジスタ、ラッチ回路、バッファ回路、DA 変換回路、AD 変換回路など) を有する場合が多い。こうすることによって、図 15 (B) と同様に、トランジスタの半導体層として、非単結晶半導体、微結晶半導体、有機半導体、又は酸化物半導体などを用いることが可能となり、さらに外部部品の削減を図ることができる。

【0184】

図 15 (D) では、画素部 5364 に信号を出力する機能を有する回路 (例えば、回路 5362、回路 5363\_1、及び回路 5363\_2 など)、及びこれらの回路を制御する機能を有する回路 (例えば、回路 5361) は、画素部 5364 とは別の基板に形成される。こうして、画素部と、その周辺回路とを別々の基板に形成することが可能になるので、歩留まりの向上を図ることができる。

【0185】

なお、図 15 (D) と同様に、図 15 (A) ~ (C) においても、回路 5363\_1、及び回路 5363\_2 を画素部 5364 とは別の基板に形成することが可能である。

【0186】

図 15 (E) では、回路 5361 の一部 (回路 5361a) が画素部 5364 と同じ基板 5380 に形成され、残りの回路 5361 (回路 5361b) が画素部 5364 とは別の基板に形成される。回路 5361a は、移動度が小さいトランジスタによって構成することが可能な回路 (例えば、スイッチ、セレクタ、レベルシフト回路など) を有する場合が多い。そして、回路 5361b は、移動度が高く、ばらつきが小さいトランジスタを用いて構成することが好ましい回路 (例えば、シフトレジスタ、タイミングジェネレータ、オシレータ、レギュレータ、又はアナログバッファなど) を有する場合が多い。

【0187】

なお、図 15 (A) ~ (D) においても、回路 5361a を画素部 5364 と同じ基板に

10

20

30

40

50

形成し、回路 5 3 6 1 b を画素部 5 3 6 4 とは別の基板に形成することが可能である。

【0188】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0189】

(実施の形態 7)

本実施の形態では、トランジスタ、及び容量素子の作製工程の一例を示す。特に、半導体層として、酸化物半導体を用いる場合の作製工程について説明する。酸化物半導体層としては、 $InMO_3$  ( $ZnO$ )<sub>m</sub> ( $m > 0$ ) で表記される層を用いることが可能である。なお、Mとしては、Ga、Fe、Ni、Mn及びCoから選ばれた一の金属元素又は複数の金属元素などがある。例えば、Mとして、Gaの場合があることの他、GaとNi又はGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。なお、酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。このような薄膜をIn-Ga-Zn-O系非単結晶膜と示すことが可能である。なお、酸化物半導体としては、ZnOを用いることが可能である。なお、酸化物半導体層の可動イオン、代表的にはナトリウムの濃度は、 $5 \times 10^{18} / cm^3$  以下、更には $1 \times 10^{18} / cm^3$  以下であると、トランジスタの電気特性が変化することを抑制することができるため好ましい。ただし、これに限定されず、半導体層としては、他に様々な材料の酸化物半導体を用いることが可能である。または、半導体層としては、単結晶半導体、多結晶半導体、微結晶（マイクロクリスタル、又はナノクリスタル）半導体、非晶質（アモルファス）半導体、又は、様々な非単結晶半導体などを用いることが可能である。

10

【0190】

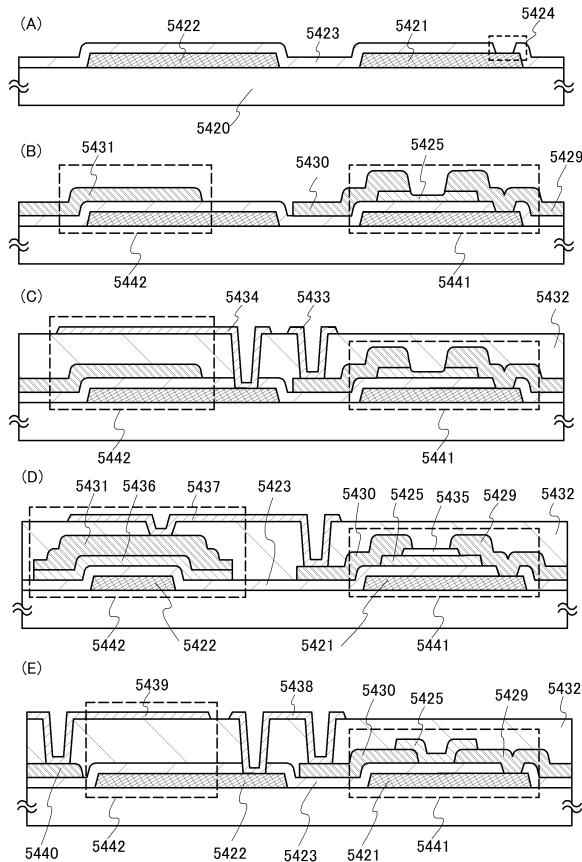

図16(A)～(C)を参照して、トランジスタ、及び容量素子の作製工程の一例について説明する。図16(A)～(C)には、トランジスタ5441、及び容量素子5442の作製工程の一例である。トランジスタ5441は、逆スタガ型薄膜トランジスタの一例であり、酸化物半導体層上にソース電極またはドレイン電極を介して配線が設けられているトランジスタの例である。

20

【0191】

まず、基板5420上に、スパッタリング法により第1導電層を全面に形成する。次に、第1フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて、選択的に第1導電層のエッチングを行い、導電層5421、及び導電層5422を形成する。導電層5421は、ゲート電極として機能することが可能であり、導電層5422は、容量素子の一方の電極として機能することが可能である。ただし、これに限定されず、導電層5421、及び導電層5422は、配線、ゲート電極、又は容量素子の電極として機能する部分を有することが可能である。この後、レジストマスクを除去する。

30

【0192】

次に、絶縁層5423をプラズマCVD法またはスパッタリング法を用いて全面に形成する。絶縁層5423は、ゲート絶縁層として機能することが可能であり、導電層5421、及び導電層5422を覆うように形成される。なお、絶縁層5423の膜厚は、 $50 nm \sim 250 nm$  である場合が多い。

40

【0193】

なお、絶縁層5423として、酸化シリコン層が用いられる場合、有機シランガスを用いたCVD法により、酸化シリコン層を形成することが可能である。有機シランガスとしては、珪酸エチル（TEOS：化学式 $Si(OCH_3)_4$ ）、テトラメチルシラン（TMS：化学式 $Si(CH_3)_4$ ）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（ $SiH(OCH_3)_3$ ）、トリスジメチルアミノシラン（ $SiH(N(CH_3)_2)_3$ ）等のシリコン含有化合物、又は、酸化イットリウム（ $Y_2O_3$ ）を用いることが可能である。

50

## 【0194】

次に、第2フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて、絶縁層5423を選択的にエッチングして導電層5421に達するコンタクトホール5424を形成する。この後、レジストマスクを除去する。ただし、これに限定されず、コンタクトホール5424を省略することが可能である。または、酸化物半導体層の形成後に、コンタクトホール5424を形成することが可能である。ここまで段階での断面図が図16(A)に相当する。

## 【0195】

次に、酸化物半導体層をスパッタリング法により全面に形成する。ただし、これに限定されず、酸化物半導体層をスパッタリング法により形成し、さらにその上に $n^+$ 層を形成することが可能である。なお、酸化物半導体の膜厚は、5nm~200nmである場合が多い。

10

## 【0196】

なお、酸化物半導体層をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことが好ましい。この逆スパッタリングにより、絶縁層5423の表面及びコンタクトホール5424の底面に付着しているゴミを除去することができる。逆スパッタリングとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。ただし、これに限定されず、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いることが可能である。または、アルゴン雰囲気に酸素、水素、N<sub>2</sub>Oなどを加えた雰囲気で行うことが可能である。または、アルゴン雰囲気にC<sub>1</sub><sub>2</sub>、CF<sub>4</sub>などを加えた雰囲気で行うことが可能である。なお、逆スパッタリングを行うと、絶縁層5423の表面が好ましくは2~10nm程度削られる。このようなプラズマ処理後に、大気に曝すことなく酸化物半導体を形成することによって、ゲート絶縁層と半導体層との界面にゴミ又は水分を付着させない点で有用である。

20

## 【0197】

次に、第3フォトマスクを用いて選択的に、酸化物半導体層のエッチングを行う。この後、レジストマスクを除去する。

## 【0198】

次に、スパッタリング法により第2導電層を全面に形成する。次に、第4フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて選択的に第2導電層のエッチングを行い、導電層5429、導電層5430、及び導電層5431を形成する。導電層5429は、コンタクトホール5424を介して導電層5421と接続される。導電層5429、及び導電層5430は、ソース電極又はドレイン電極として機能することが可能であり、導電層5431は、容量素子の他方の電極として機能することが可能である。ただし、これに限定されず、導電層5429、導電層5430、及び導電層5431は、配線、ソース若しくはドレイン電極、又は容量素子の電極として機能する部分を含むことが可能である。

30

## 【0199】

なお、この後、熱処理(例えば200~600の)を行う場合、この熱処理に耐える耐熱性を第2導電層に持たせることが好ましい。よって、第2導電層としては、Alと、耐熱性導電性材料(例えば、Ti、Ta、W、Mo、Cr、Nd、Sc、Zr、Ceなどの元素、これらの元素を組み合わせた合金、又は、これらの元素を成分とする窒化物など)とを組み合わせた材料であることが好ましい。ただし、これに限定されず、第2導電膜を積層構造にすることによって、第2導電膜に耐熱性を持たせることができる。例えば、Alの上下に、Ti、又はMoなどの耐熱性導電性材料を設けることが可能である。

40

## 【0200】

なお、第2導電層をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行い、絶縁層5423の表面、酸化物半導体層の表面、及びコンタクトホール5424の底面に付着しているゴミを除去することが好ましい

50

。ただし、これに限定されず、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いることが可能である。または、アルゴン雰囲気に酸素、水素、N<sub>2</sub>Oなどを加えた雰囲気で行うことが可能である。または、アルゴン雰囲気にCl<sub>2</sub>、CF<sub>4</sub>などを加えた雰囲気で行うことが可能である

【0201】

なお、第2導電層のエッティングの際に、さらに、酸化物半導体層の一部をエッティングして、酸化物半導体層5425を形成する。このエッティングによって、導電層5421と重なる部分の酸化物半導体層5425、又は、上方に第2の導電層が形成されていない部分の酸化物半導体層5425は、削れられるので、薄くなる場合が多い。ただし、これに限定されず、酸化物半導体層は、エッティングされないことが可能である。ただし、酸化物半導体層の上にn<sup>+</sup>層が形成される場合は、酸化物半導体はエッティングされる場合が多い。この後、レジストマスクを除去する。このエッティングが終了した段階でトランジスタ5441と容量素子5442とが完成する。ここまで段階での断面図が図16(B)に相当する。

10

【0202】

ここで、第2導電層をスパッタリング法により形成する前に逆スパッタリングを行うと、絶縁層5423の露出部が好ましくは2~10nm程度削られことがある。よって、絶縁層5423に凹部が形成される場合がある。または、第2導電層のエッティングを行い、導電層5429、導電層5430、及び導電層5431を形成した後、逆スパッタリングすることによって、図16(B)に示すように、導電層5429、導電層5430、及び導電層5431の端部が湾曲する場合がある。

20

【0203】

次に、大気雰囲気下または窒素雰囲気下で200~600の加熱処理を行う。この熱処理によりIn-Ga-Zn-O系非単結晶層の原子レベルの再配列が行われる。この熱処理によりキャリアの移動を阻害する歪が解放されるため、ここで熱処理(光アニールも含む)は重要である。なお、この加熱処理を行うタイミングは限定されず、酸化物半導体の形成後であれば、様々なタイミングで行うことが可能である。

20

【0204】

次に、絶縁層5432を全面に形成する。絶縁層5432としては、単層構造であることが可能であるし、積層構造であることが可能である。例えば、絶縁層5432として有機絶縁層を用いる場合、有機絶縁層の材料である組成物を塗布し、大気雰囲気下または窒素雰囲気下で200~600の加熱処理を行って、有機絶縁層を形成する。このように、酸化物半導体層に接する有機絶縁層を形成することにより、電気特性の信頼性の高い薄膜トランジスタを作製することができる。なお、絶縁層5432として有機絶縁層を用いる場合、有機絶縁層の下に、窒化珪素膜、又は酸化珪素膜を設けることが可能である。

30

【0205】

なお、図16(C)においては、非感光性樹脂を用いて絶縁層5432を形成した形態を示すため、コンタクトホールが形成される領域の断面において、絶縁層5432の端部が角張っている。しかしながら、感光性樹脂を用いて絶縁層5432を形成すると、コンタクトホールが形成される領域の断面において、絶縁層5432の端部を湾曲させることが可能になる。この結果、後に形成される第3導電層又は画素電極の被覆率が向上する。

40

【0206】

なお、組成物を塗布する代わりに、その材料に応じて、ディップ、スプレー塗布、インクジェット法、印刷法、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることが可能である。

【0207】

なお、酸化物半導体層を形成した後の加熱処理をせず、有機絶縁層の材料である組成物の加熱処理時に、酸化物半導体層の加熱処理を兼ねることが可能である。

【0208】

なお、絶縁層5432は、200nm~5μm、好ましくは300nm~1μmで形成す

50

ることが可能である。

【0209】

次に、第3導電層を全面に形成する。次に、第5フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて第3導電層を選択的にエッチングして、導電層5433、及び導電層5434を形成する。ここまで段階での断面図が図16(C)に相当する。導電層5433、及び導電層5434は、配線、画素電極、反射電極、透明電極、又は容量素子の電極として機能することが可能である。特に、導電層5434は、導電層5422と接続されるので、容量素子5442の電極として機能することが可能である。ただし、これに限定されず、第1導電層と第2導電層とを接続する機能を有することが可能である。例えば、導電層5433と導電層5434とを接続することによって、導電層5422と導電層5430とを第3導電層(導電層5433及び導電層5434)を介して接続されることが可能になる。10

【0210】

なお、容量素子5442は、導電層5422と導電層5434とによって、導電層5431が挟まれる構造になるので、容量素子5442の容量値を大きくすることができる。ただし、これに限定されず、導電層5422と導電層5434との一方を省略することが可能である。

【0211】

なお、レジストマスクをウェットエッチングで除去した後、大気雰囲気下または窒素雰囲気下で200～600の加熱処理を行うことができる。20

【0212】

以上の工程により、トランジスタ5441と容量素子5442とを作製することができる。20

【0213】

なお、図16(D)に示すように、酸化物半導体層5425の上に絶縁層5435を形成することが可能である。絶縁層5435は、第2導電層がパターニングされる場合に、酸化物半導体層が削られることを防止する機能を有し、チャネルストップ膜として機能する。よって、酸化物半導体層の膜厚を薄くすることができるので、トランジスタの駆動電圧の低減、オフ電流の低減、ドレイン電流のオンオフ比の向上、又はS値の改善などを図ることができる。なお、絶縁層5435は、酸化物半導体層と絶縁層とを連続して全面に形成し、その後、フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて選択的に当該絶縁層をパターニングすることによって、形成されることがある。その後、第2導電層を全面に形成し、第2導電層と同時に酸化物半導体層をパターニングする。つまり、同じマスク(レチクル)を用いて、酸化物半導体層と第2導電層とをパターニングすることが可能になる。この場合、第2導電層の下には、必ず酸化物半導体層が形成されることになる。こうして、工程数を増やすことなく、絶縁層5435を形成することができる。このような製造プロセスでは、第2導電層の下に酸化物半導体層が形成される場合が多い。ただし、これに限定されず、酸化物半導体層をパターニングした後に、絶縁層を全面に形成し、当該絶縁層をパターニングすることによって、絶縁層5435を形成することが可能である。30

【0214】

なお、図16(D)において、容量素子5442は、導電層5422と導電層5431とによって、絶縁層5423と酸化物半導体層5436とが挟まれる構造である。ただし、酸化物半導体層5436を省略することが可能である。そして、導電層5430と導電層5431とは、第3導電層をパターニングして形成される導電層5437を介して接続されている。このような構造は、一例として、液晶表示装置の画素に用いられることが可能である。例えば、トランジスタ5441はスイッチングトランジスタとして機能し、容量素子5442は保持容量として機能することが可能である。そして、導電層5421、導電層5422、導電層5429、導電層5437は、各々、ゲート線、容量線、ソース線、画素電極として機能することが可能である。ただし、これに限定されない。なお、図140

6 (D) と同様に、図 16 (C) においても、導電層 5430 と導電層 5431 とを第 3 導電層を介して接続することが可能である。

【0215】

なお、図 16 (E) に示すように、第 2 導電層をパターニングした後に、酸化物半導体層 5425 を形成することが可能である。こうすることによって、第 2 導電層がパターニングされる場合、酸化物半導体は形成されていないので、酸化物半導体層が削られることがない。よって、酸化物半導体層の膜厚を薄くすることができるので、トランジスタの駆動電圧の低減、オフ電流の低減、ドレイン電流のオンオフ比の向上、又は S 値の改善などを図ることができる。なお、酸化物半導体層 5425 は、第 2 導電層がパターニングされる後に、酸化物半導体層が全面に形成され、その後フォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて選択的に酸化物半導体層パターニングすることによって形成されることがある。

【0216】

なお、図 16 (E) において、容量素子は、導電層 5422 と、第 3 導電層をパターニングして形成される導電層 5439 とによって、絶縁層 5423 と絶縁層 5432 とが挟まれる構造である。そして、導電層 5422 と導電層 5430 とは、第 3 導電層をパターニングして形成される導電層 5438 を介して接続される。さらに、導電層 5439 は、第 2 導電層をパターニングして形成される導電層 5440 と接続される。なお、図 16 (E) と同様に、図 16 (C) 及び (D) においても、導電層 5430 と導電層 5422 とは、導電層 5438 を介して接続されることが可能である。

【0217】

なお、酸化物半導体層（又はチャネル層）の膜厚を、トランジスタがオフの場合の空乏層よりも薄くすることによって、完全空乏化状態を作り出すことが可能になる。こうして、オフ電流を低減することができる。これを実現するために、酸化物半導体層の膜厚は、20 nm 以下であることが好ましい。より好ましくは 10 nm 以下である。さらに好ましくは 6 nm 以下であることが好ましい。

【0218】

なお、トランジスタの動作電圧の低減、オフ電流の低減、ドレイン電流のオンオフ比の向上、S 値の改善などを図るために、酸化物半導体層の膜厚は、トランジスタを構成する層の中で、一番薄いことが好ましい。例えば、酸化物半導体層の膜厚は、絶縁層 5423 よりも薄いことが好ましい。より好ましくは、酸化物半導体層の膜厚は、絶縁層 5423 の 1/2 以下であることが好ましい。より好ましくは、1/5 以下であることが好ましい。さらに好ましくは、1/10 以下であることが好ましい。ただし、これに限定されず、信頼性を向上させるために、酸化物半導体層の膜厚は、絶縁層 5423 よりも厚いことが可能である。特に、図 16 (C) のように、酸化物半導体層が削られる場合には、酸化物半導体層の膜厚は厚いほうが好ましいので、酸化物半導体層の膜厚は、絶縁層 5423 よりも厚いことが可能である。

【0219】

なお、トランジスタの耐圧を高くするために、絶縁層 5423 の膜厚は、第 1 導電層よりも厚いことが好ましい。より好ましくは、絶縁層 5423 の膜厚は、第 1 導電層の 5/4 以上であることが好ましい。さらに好ましくは、4/3 以上であることが好ましい。ただし、これに限定されず、トランジスタの移動度を高くするために、絶縁層 5423 の膜厚は、第 1 導電層よりも薄いことが可能である。

【0220】

なお、本実施の形態の基板、絶縁膜、導電膜、及び半導体層としては、他の実施の形態に述べる材料、又は本明細書において述べる材料と同様なものを用いることが可能である。

【0221】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0222】

10

20

30

40

50

## (実施の形態 8 )

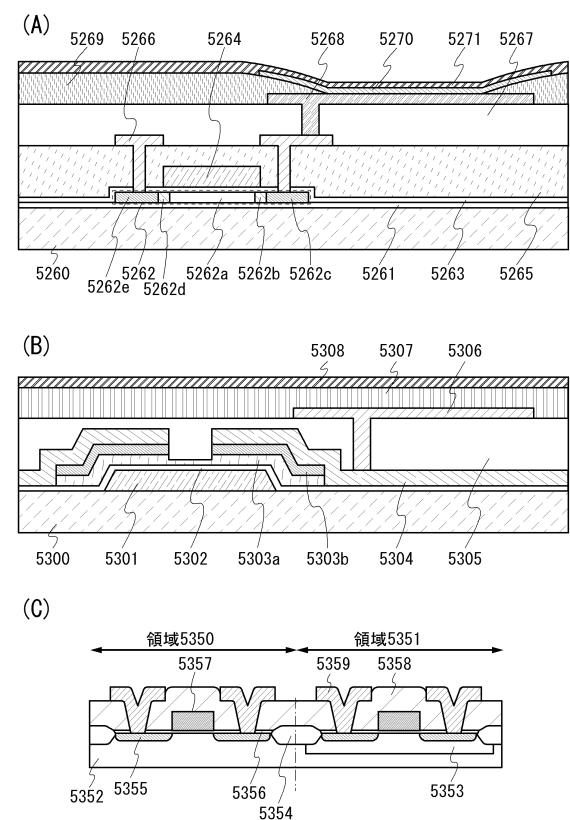

本実施の形態では、トランジスタの構造の一例について図 17 ( A )、( B )、及び( C )を参照して説明する。

## 【 0 2 2 3 】

図 17 ( A ) は、トップゲート型のトランジスタの構成の一例である。図 17 ( B ) は、ボトムゲート型のトランジスタの構成の一例である。図 17 ( C ) は、半導体基板を用いて作製されるトランジスタの構造の一例である。

## 【 0 2 2 4 】

図 17 ( A ) には、基板 5260 と、基板 5260 の上に形成される絶縁層 5261 と、絶縁層 5261 の上に形成され、領域 5262a、領域 5262b、領域 5262c、領域 5262d、及び 5262e を有する半導体層 5262 と、半導体層 5262 を覆うように形成される絶縁層 5263 と、半導体層 5262 及び絶縁層 5263 の上に形成される導電層 5264 と、絶縁層 5263 及び導電層 5264 の上に形成され、開口部を有する絶縁層 5265 と、絶縁層 5265 の上及び絶縁層 5265 の開口部に形成される導電層 5266 と、導電層 5266 の上及び絶縁層 5265 の上に形成され、開口部を有する絶縁層 5267 と、絶縁層 5267 の上及び絶縁層 5267 の開口部に形成される導電層 5268 と、絶縁層 5267 の上及び導電層 5268 の上に形成され、開口部を有する絶縁層 5269 と、絶縁層 5269 の上及び絶縁層 5269 の開口部に形成される発光層 5270 と、絶縁層 5269 の上及び発光層 5270 の上に形成される導電層 5271 とを示す。

10

## 【 0 2 2 5 】

図 17 ( B ) には、基板 5300 と、基板 5300 の上に形成される導電層 5301 と、導電層 5301 を覆うように形成される絶縁層 5302 と、導電層 5301 及び絶縁層 5302 の上に形成される半導体層 5303a と、半導体層 5303a の上に形成される半導体層 5303b と、半導体層 5303b の上及び絶縁層 5302 の上に形成される導電層 5304 と、絶縁層 5302 の上及び導電層 5304 の上に形成され、開口部を有する絶縁層 5305 と、絶縁層 5305 の上及び絶縁層 5305 の開口部に形成される導電層 5306 と、絶縁層 5305 の上及び導電層 5306 の上に配置される液晶層 5307 と、液晶層 5307 の上に形成される導電層 5308 とを示す。

20

## 【 0 2 2 6 】

30

図 17 ( C ) には、領域 5353 及び領域 5355 を有する半導体基板 5352 と、半導体基板 5352 の上に形成される絶縁層 5356 と、半導体基板 5352 の上に形成される絶縁層 5354 と、絶縁層 5356 の上に形成される導電層 5357 と、絶縁層 5354、絶縁層 5356、及び導電層 5357 の上に形成され、開口部を有する絶縁層 5358 と、絶縁層 5358 の上及び絶縁層 5358 の開口部に形成される導電層 5359 とを示す。こうして、領域 5350 と領域 5351 とに、各々、トランジスタが作製される。

## 【 0 2 2 7 】

40

絶縁層 5261 は、下地膜として機能することが可能である。絶縁層 5354 は、素子間分離層 ( 例えばフィールド酸化膜 ) として機能する。絶縁層 5263、絶縁層 5302、絶縁層 5356 は、ゲート絶縁膜として機能することが可能である。導電層 5264、導電層 5301、導電層 5357 は、ゲート電極として機能することが可能である。絶縁層 5265、絶縁層 5267、絶縁層 5305、及び絶縁層 5358 は、層間膜、又は平坦化膜として機能することが可能である。導電層 5266、導電層 5304、及び導電層 5359 は、配線、トランジスタの電極、又は容量素子の電極などとして機能することが可能である。導電層 5268、及び導電層 5306 は、画素電極、又は反射電極などとして機能することが可能である。絶縁層 5269 は、隔壁として機能することが可能である。導電層 5271、及び導電層 5308 は、対向電極、又は共通電極などとして機能することが可能である。

## 【 0 2 2 8 】

基板 5260、及び基板 5300 の一例としては、ガラス基板、石英基板、単結晶基板 (

50

例えばシリコン基板)、SOI基板、プラスチック基板、金属基板、ステンレス基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板又は可撓性基板などがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニオホウケイ酸ガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。他にも、貼り合わせフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなど)、纖維状な材料を含む紙、基材フィルム(ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、紙類等)などがある。

## 【0229】

10

半導体基板5352としては、一例として、n型又はp型の導電型を有する単結晶Si基板を用いることが可能である。ただし、これに限定されず、基板5260と同様なものを用いることが可能である。領域5353は、一例として、半導体基板5352に不純物が添加された領域であり、ウェルとして機能する。例えば、半導体基板5352がp型の導電型を有する場合、領域5353は、n型の導電型を有し、nウェルとして機能する。一方で、半導体基板5352がn型の導電型を有する場合、領域5353は、p型の導電型を有し、pウェルとして機能する。領域5355は、一例として、不純物が半導体基板5352に添加された領域であり、ソース領域又はドレイン領域として機能する。なお、半導体基板5352に、LDD領域を形成することが可能である。

## 【0230】

20

絶縁層5261の一例としては、酸化珪素(SiO<sub>x</sub>)膜、窒化珪素(SiN<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜などの酸素若しくは窒素を有する膜、又はこれらの積層構造などがある。絶縁層5261が2層構造で設けられる場合の一例としては、1層目の絶縁層として窒化珪素膜を設け、2層目の絶縁層として酸化珪素膜を設けることが可能である。絶縁層5261が3層構造で設けられる場合の一例としては、1層目の絶縁層として酸化珪素膜を設け、2層目の絶縁層として窒化珪素膜を設け、3層目の絶縁層として酸化珪素膜を設けることが可能である。

## 【0231】

30

半導体層5262、半導体層5303a、及び半導体層5303bの一例としては、非単結晶半導体(非晶質(アモルファス)シリコン、多結晶シリコン、微結晶シリコンなど)、単結晶半導体、化合物半導体若しくは酸化物半導体(ZnO、InGaZnO、SiGe、GaAs、IZO、ITO、SnO、TiO、AlZnSnO(AZTO))、有機半導体、又はカーボンナノチューブなどがある。

## 【0232】

40

なお、例えば、領域5262aは、不純物が半導体層5262に添加されていない真性の状態であり、チャネル領域として機能する。ただし、領域5262aに微少な不純物を添加することが可能であり、領域5262aに添加される不純物は、領域5262b、領域5262c、領域5262d、又は領域5262eに添加される不純物の濃度よりも低いことが好ましい。領域5262b、及び領域5262dは、低濃度に不純物が添加された領域であり、LDD(Lightly Doped Drain:LDD)領域として機能する。ただし、領域5262b、及び領域5262dを省略することが可能である。領域5262c、及び領域5262eは、高濃度に不純物が半導体層5262に添加された領域であり、ソース領域又はドレイン領域として機能する。

## 【0233】

なお、半導体層5303bは、不純物元素としてリンなどが添加された半導体層であり、n型の導電型を有する。

## 【0234】

なお、半導体層5303aとして、酸化物半導体、又は化合物半導体が用いられる場合、半導体層5303bを省略することが可能である。

50

## 【0235】

絶縁層5263、絶縁層5273、及び絶縁層5356の一例としては、酸化珪素(SiO<sub>x</sub>)膜、窒化珪素(SiNx)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜などの酸素若しくは窒素を有する膜、又はこれらの積層構造などがある。

## 【0236】

導電層5264、導電層5266、導電層5268、導電層5271、導電層5301、導電層5304、導電層5306、導電層5308、導電層5357、及び導電層5359の一例としては、単層構造の導電膜、又はこれらの積層構造などがある。当該導電膜の一例としては、アルミニウム(A1)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンクスチタン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マンガン(Mn)、コバルト(Co)、ニオブ(Nb)、シリコン(Si)、鉄(Fe)、パラジウム(Pd)、炭素(C)、スカンジウム(Sc)、亜鉛(Zn)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)、酸素(O)、ジルコニウム(Zr)、セリウム(Ce)によって構成される群から選ばれた一つの元素の単体膜、又は、前記群から選ばれた一つ又は複数の元素を含む化合物などがある。当該化合物の一例としては、前記群から選ばれた一つ若しくは複数の元素を含む合金(インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、酸化錫(SnO)、酸化錫カドミウム(CTO)、アルミニオジム(A1-Nd)、アルミタンクスチタン(A1-W)、アルミジルコニウム(A1-Zr)、アルミチタン(A1-Ti)、アルミセリウム(A1-Ce)、マグネシウム銀(Mg-Ag)、モリブデンニオブ(Mo-Nb)、モリブデンタンクスチタン(Mo-W)、モリブデンタンタル(Mo-Ta)などの合金材料)、前記群から選ばれた一つ若しくは複数の元素と窒素との化合物(窒化チタン、窒化タンタル、窒化モリブデンなどの窒化膜)、又は、前記群から選ばれた一つ若しくは複数の元素とシリコンとの化合物(タンクスチタンシリサイド、チタンシリサイド、ニッケルシリサイド、アルミシリコン、モリブデンシリコンなどのシリサイド膜)などがある。他にも、カーボンナノチューブ、有機ナノチューブ、無機ナノチューブ、又は金属ナノチューブなどのナノチューブ材料がある。

## 【0237】

なお、シリコン(Si)は、n型不純物(リンなど)、又はp型不純物ボロンなど)を含むことが可能である。シリコンが不純物を含むことにより、導電率の向上や、通常の導体と同様な振る舞いをすることが可能になったりするので、配線、又は電極などとして利用しやすくなる。

## 【0238】

なお、シリコンとして、単結晶、多結晶(ポリシリコン)、微結晶(マイクロクリスタルシリコン)など、様々な結晶性を有するシリコン、又は非晶質(アモルファスシリコン)などの結晶性を有さないシリコンなどを用いることが可能である。シリコンとして、単結晶シリコンまたは多結晶シリコンを用いることにより、配線、電極、導電層、導電膜、端子などの抵抗を小さくすることができる。シリコンとして、非晶質シリコンまたは微結晶シリコンを用いることにより、簡単な工程で配線などを形成することができる。

## 【0239】

なお、導電層として、シリコンなどの半導体材料を用いる場合、シリコンなどの半導体材料をトランジスタが有する半導体層と同時に形成することが可能である。

## 【0240】

なお、アルミニウム、又は銀は、導電率が高いため、信号遅延を低減することができる。さらに、アルミニウム、又は銀は、エッチングしやすいので、パターニングしやすく、微細加工を行うことができる。

## 【0241】

なお、銅は、導電率が高いため、信号遅延を低減することができる。銅が導電層として用

10

20

30

40

50

いられる場合、密着性を向上させるために積層構造にすることが好ましい。

【0242】

なお、モリブデンまたはチタンは、酸化物半導体（ITO、IZOなど）、又はシリコンと接触しても、不良を起こしにくい、エッチングしやすい、耐熱性が高いなどの利点を有するので、望ましい。よって、酸化物半導体、又はシリコンと接触する導電層としては、モリブデン又はチタンを用いることが好ましい。

【0243】

なお、タンゲステンは、耐熱性が高いなどの利点を有するため、望ましい。

【0244】

なお、ネオジムは、耐熱性が高いなどの利点を有するため、望ましい。特に、導電層としてネオジムとアルミニウムとの合金材料を用いることによって、アルミニウムがヒロックを起こしにくくなる。ただし、これに限定されず、アルミニウムと、タンタル、ジルコニアム、チタン、又はセリウムとの合金材料を用いることによっても、アルミニウムがヒロックを起こしにくくなる。特に、アルミニウムとセリウムとの合金材料は、アーキングを大幅に低減することができる。

10

【0245】

なお、ITO、IZO、ITSO、ZnO、Si、SnO、CTO、又はカーボンナノチューブなどは、透光性を有しているので、これらの材料を画素電極、対向電極、又は共通電極などの光を透過させる部分に用いることが可能である。特に、IZOは、エッチングしやすく、加工しやすいため、望ましい。IZOは、エッチングしたときに、残渣が残ってしまう、ということが起こりにくい。したがって、画素電極としてIZOを用いると、液晶素子や発光素子に不具合（ショート、配向乱れなど）をもたらすことを低減することができる。

20

【0246】

なお、導電層は、単層構造とすることが可能であるし、多層構造とすることが可能である。単層構造にすることにより、配線、電極、導電層、導電膜、端子などの製造工程を簡略化することができ、工程日数を少なくでき、コストを低減することができる。一方で、多層構造にすることにより、それぞれの材料のメリットを生かしつつ、デメリットを低減させ、性能の良い配線、電極などを形成することができる。例えば、低抵抗材料（アルミニウムなど）を多層構造の中に含むことにより、配線の低抵抗化を図ることができる。別の例として、低耐熱性の材料を、高耐熱性の材料で挟む積層構造にすることにより、低耐熱性の材料の持つメリットを生かしつつ、配線、電極などの耐熱性を高くすることができる。このような積層構造の一例としては、アルミニウムを含む層を、モリブデン、チタン、ネオジムなどを含む層で挟む積層構造にすると望ましい。

30

【0247】

なお、配線、電極など同士が直接接する場合、お互いに悪影響を及ぼすことがある。例えば、一方の配線、電極などが他方の配線、電極など材料の中に入ってしまって、性質を変えてしまい、本来の目的を果たせなくなる場合がある。別の例として、高抵抗な部分を形成又は製造するときに、問題が生じて、正常に製造できなくなる場合がある。このような場合、他の材料に反応して性質が変わってしまう材料を、当該他の材料に反応しにくい材料によって挟んだり、覆ったりすることが可能である。例えば、ITOとアルミニウムとを接続させる場合は、ITOとアルミニウムとの間に、チタン、モリブデン、ネオジム合金などを挟むことが可能である。例えば、シリコンとアルミニウムとを接続させる場合は、シリコンとアルミニウムとの間に、チタン、モリブデン、ネオジム合金を挟むことが可能である。

40

なお、これらの材料は、配線、電極、導電層、導電膜、端子、ビア、プラグなどにも用いることが可能である。

【0248】

絶縁層5265、絶縁層5267、絶縁層5269、絶縁層5305、及び絶縁層5358の一例としては、単層構造の絶縁層、又はこれらの積層構造などがある。当該絶縁層の

50

一例としては、酸化珪素(SiO<sub>x</sub>)膜、窒化珪素(SiN<sub>x</sub>)膜、若しくは酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜等の酸素若しくは窒素を含む膜、DLC(ダイヤモンドライクカーボン)等の炭素を含む膜、又は、シロキサン樹脂、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、若しくはアクリル等の有機材料などがある。

【0249】

発光層5270の一例としては、有機EL素子、又は無機EL素子などがある。有機EL素子の一例としては、正孔注入材料からなる正孔注入層、正孔輸送材料からなる正孔輸送層、発光材料からなる発光層、電子輸送材料からなる電子輸送層、電子注入材料からなる電子注入層など、若しくはこれらの材料のうち複数の材料を混合した層の単層構造、若しくはこれらの積層構造などがある。

10

【0250】

液晶層5307の一例としては、ネマチック液晶、コレステリック液晶、スマクチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC)、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶(PALC)、バナナ型液晶などを挙げができる。また、液晶の駆動方式としては、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、IPS(In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi-domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、ゲストホストモード、ブルー相(Blue Phase)モードなどがある。

20

【0251】

なお、絶縁層5305の上及び導電層5306の上には、配向膜として機能する絶縁層、突起部として機能する絶縁層などを形成することが可能である。

30

【0252】

なお、導電層5308の上には、カラーフィルタ、ブラックマトリクス、又は突起部として機能する絶縁層などを形成することが可能である。導電層5308の下には、配向膜として機能する絶縁層を形成することが可能である。

【0253】

なお、図17(A)の断面構造において、絶縁層5269、発光層5270、及び導電層5271を省略し、図17(B)に示す液晶層5307、導電層5308を絶縁層5267の上及び導電層5268の上に形成することが可能である。

40

【0254】

なお、図17(B)の断面構造において、液晶層5307、導電層5308を省略し、図17(A)に示す絶縁層5269、発光層5270、及び導電層5271を絶縁層5305の上及び導電層5306の上に形成することが可能である。

【0255】

なお、図17(C)の断面構造において、絶縁層5358及び導電層5359の上に、図17(A)に示す絶縁層5269、発光層5270、及び導電層5271を形成することが可能である。あるいは、図17(B)に示す液晶層5307、導電層5308を絶縁層5358の上及び導電層5359の上に形成することが可能である。

50

**【0256】**

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に對して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

**【0257】****(実施の形態9)**

本実施の形態においては、電子機器の例について説明する。

**【0258】**

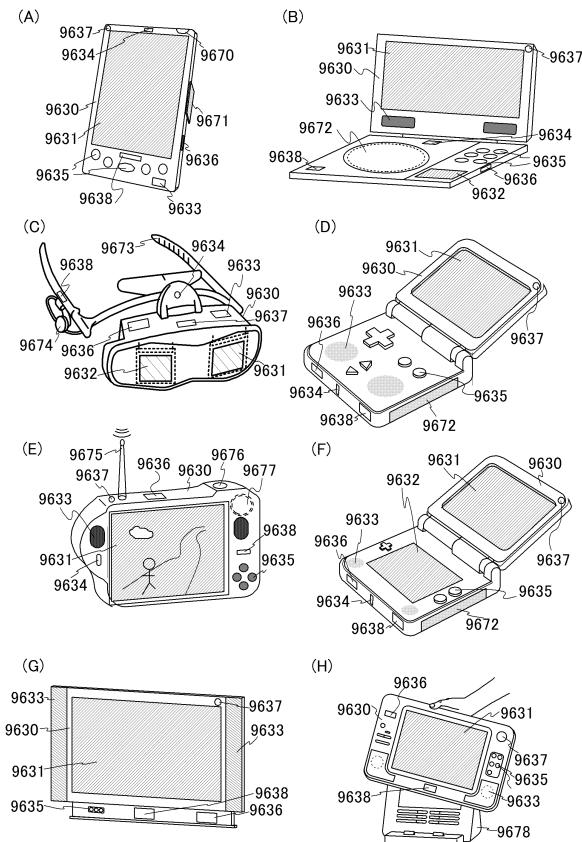

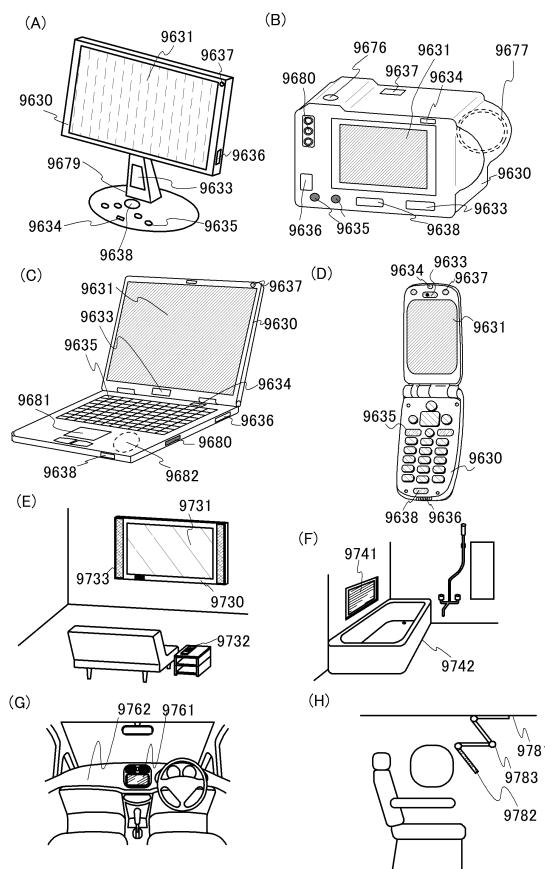

図18(A)乃至図18(H)、図19(A)乃至図19(D)は、電子機器を示す図である。これらの電子機器は、筐体9630、表示部9631、スピーカ9633、LEDランプ9634、操作キー9635、接続端子9636、センサ9637(力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの)、マイクロフォン9638、等を有することができる。

10

**【0259】**

図18(A)はモバイルコンピュータであり、上述したものの他に、スイッチ9670、赤外線ポート9671、等を有することができる。図18(B)は記録媒体を備えた携帯型の画像再生装置(たとえば、DVD再生装置)であり、上述したものの他に、第2表示部9632、記録媒体読込部9672、等を有することができる。図18(C)はゴーグル型ディスプレイであり、上述したものの他に、第2表示部9632、支持部9673、イヤホン9674、等を有することができる。図18(D)は携帯型遊技機であり、上述したものの他に、記録媒体読込部9672、等を有することができる。図18(E)はテレビ受像機能付きデジタルカメラであり、上述したものの他に、アンテナ9675、シャッターボタン9676、受像部9677、等を有することができる。図18(F)は携帯型遊技機であり、上述したものの他に、第2表示部9632、記録媒体読込部9672、等を有することができる。図18(G)はテレビ受像器であり、上述したものの他に、チューナ、画像処理部、等を有することができる。図18(H)は持ち運び型テレビ受像器であり、上述したものの他に、信号の送受信が可能な充電器9678、等を有することができる。図19(A)はディスプレイであり、上述したものの他に、支持台9679、等を有することができる。図19(B)はカメラであり、上述したものの他に、外部接続ポート9680、シャッターボタン9676、受像部9677、等を有することができる。図19(C)はコンピュータであり、上述したものの他に、ポインティングデバイス9681、外部接続ポート9680、リーダ/ライタ9682、等を有することができる。図19(D)は携帯電話機であり、上述したものの他に、送信部、受信部、携帯電話・移動端末向けの1セグメント部分受信サービス用チューナ、等を有することができる。

20

**【0260】**

図18(A)乃至図18(H)、図19(A)乃至図19(D)に示す電子機器は、様々な機能を有することができる。例えば、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、タッチパネル機能、カレンダー、日付又は時刻などを表示する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、無線通信機能、無線通信機能を用いて様々なコンピュータネットワークに接続する機能、無線通信機能を用いて様々なデータの送信又は受信を行う機能、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能、等を有することができる。さらに、複数の表示部を有する電子機器においては、一つの表示部を主として画像情報を表示し、別の一つの表示部を主として文字情報を表示する機能、または、複数の表示部に視差を考慮した画像を表示することで立体的な画像を表示する機能、等を有することができる。さらに、受像部を有する電子機器においては、静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する機能、撮影した画像を記録媒体(外部又はカメラに内蔵)に保存する機能、撮影した画像を表示部に表示する機能、等を有することができる。なお、図18(A)乃至図18(H)、図19(A)乃至図19(D)に示す電子機器が有することのできる機能はこれらに限定されず、様々な機能を有することができる。

30

40

50

## 【0261】

本実施の形態において述べた電子機器は、何らかの情報を表示するための表示部を有することを特徴とする。電子機器は、表示部において、トランジスタの特性バラツキの影響が低減されているため、非常に均一な画像を表示させることが出来る。

## 【0262】

次に、半導体装置の応用例を説明する。

## 【0263】

図19(E)に、半導体装置を、建造物と一体にして設けた例について示す。図19(E)は、筐体9730、表示部9731、操作部であるリモコン装置9732、スピーカ9733等を含む。半導体装置は、壁かけ型として建物と一体となっており、設置するスペースを広く必要とすることなく設置可能である。

10

## 【0264】

図19(F)に、建造物内に半導体装置を、建造物と一体にして設けた別の例について示す。表示パネル9741は、ユニットバス9742と一緒に取り付けられており、入浴者は表示パネル9741の視聴が可能になる。

## 【0265】

なお、本実施の形態において、建造物として壁、ユニットバスを例としたが、本実施の形態はこれに限定されず、様々な建造物に半導体装置を設置することができる。

## 【0266】

次に、半導体装置を、移動体と一体にして設けた例について示す。

20

## 【0267】

図19(G)は、半導体装置を、自動車に設けた例について示した図である。表示パネル9761は、自動車の車体9762に取り付けられており、車体の動作又は車体内外から入力される情報をオンデマンドで表示することができる。なお、ナビゲーション機能を有していてもよい。

## 【0268】

図19(H)は、半導体装置を、旅客用飛行機と一体にして設けた例について示した図である。図19(H)は、旅客用飛行機の座席上部の天井9781に表示パネル9782を設けたときの、使用時の形状について示した図である。表示パネル9782は、天井9781とヒンジ部9783を介して一緒に取り付けられており、ヒンジ部9783の伸縮により乗客は表示パネル9782の視聴が可能になる。表示パネル9782は乗客が操作することで情報を表示する機能を有する。

30

## 【0269】

なお、本実施の形態において、移動体としては自動車車体、飛行機車体について例示したがこれに限定されず、自動二輪車、自動四輪車(自動車、バス等を含む)、電車(モノレール、鉄道等を含む)、船舶等、様々なものに設置することができる。

## 【0270】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【符号の説明】

40

## 【0271】

- 101 トランジスタ

- 102 容量素子