(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5676189号

(P5676189)

(45) 発行日 平成27年2月25日(2015.2.25)

(24) 登録日 平成27年1月9日(2015.1.9)

|              |                               |

|--------------|-------------------------------|

| (51) Int.Cl. | F 1                           |

| G 11 C 19/28 | (2006.01) G 11 C 19/28 D      |

| G 11 C 19/00 | (2006.01) G 11 C 19/00 J      |

| G 09 G 3/36  | (2006.01) G 09 G 3/36         |

| G 09 G 3/20  | (2006.01) G 09 G 3/20 6 2 2 E |

|              | G 09 G 3/20 6 1 1 D           |

請求項の数 8 (全 18 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2010-213511 (P2010-213511) |

| (22) 出願日     | 平成22年9月24日(2010.9.24)        |

| (65) 公開番号    | 特開2011-70761 (P2011-70761A)  |

| (43) 公開日     | 平成23年4月7日(2011.4.7)          |

| 審査請求日        | 平成25年8月9日(2013.8.9)          |

| (31) 優先権主張番号 | 200910093182.0               |

| (32) 優先日     | 平成21年9月25日(2009.9.25)        |

| (33) 優先権主張国  | 中国(CN)                       |

|           |                                                          |

|-----------|----------------------------------------------------------|

| (73) 特許権者 | 507134301<br>北京京東方光電科技有限公司<br>中華人民共和国北京經濟技術開發區西環中<br>路8號 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                   |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                    |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                   |

| (72) 発明者  | 胡 明<br>中華人民共和国北京經濟技術開發區西環中<br>路8號                        |

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】シフト・レジスタおよびゲートライン駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

シフト・レジスタであって、

ゲートがプルアップノードとなる第1のノードに接続され、ソースが第1のクロック信号端子(C L K)に接続され、ドレーンが本段の出力端子に接続される第1の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがローレベル信号端子に接続される第2の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースがプルダウンノードとなる第2のノードに接続され、ドレーンがローレベル信号端子に接続され、前述第2のノードが本段の出力端に接続される第3の薄膜トランジスタと、

前記第1のノードと本段の出力端子との間に接続されるコンデンサと、

上段の第1のトリガー信号端子(Q a ( n - 1 ))及び第2のトリガー信号端子(Q b ( n - 1 ))と、第1のクロック信号端子(C L K)及び第2のクロック信号端子(C L K B)と、前記第1のノードに接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュールと、

第1及び第2のクロック信号端子と前記フィードバックモジュールと本段の出力端子に接続され、且つローレベル信号端子に接続されるオン/オフモジュールと、を備え、

前記フィードバックモジュールは上段のフィードバックモジュールの第1及び第2のトリガー信号と第2のクロック信号を受信して前記第1のノードのレベルをプルアップし、

10

20

且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールに第1及び第2のトリガー信号を出力し、前記オン／オフモジュールは、本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持し、

前記フィードバックモジュールは、

ゲートが上段のフィードバックモジュールの第1のトリガー信号端子に接続され、ソースが第5の薄膜トランジスタのゲートに接続され、ドレーンが第2のクロック信号端子に接続される第4の薄膜トランジスタと、

ゲートが第4の薄膜トランジスタのソースに接続され、ソースが前記第1のノードに接続され、ドレーンが上段のフィードバックモジュールの第2のトリガー信号端子に接続される第5の薄膜トランジスタと、

ゲートが前記第1のノードに接続され、ソースが前記第1のクロック信号端子に接続され、ドレーンが本段のフィードバックノードとなる第3のノードに接続される第6の薄膜トランジスタとをさらに備える

ことを特徴とするシフト・レジスタ。

#### 【請求項2】

前記オン／オフモジュールは、

ゲートとドレーンとが共に接続されて前記第2のクロック信号端子に接続され、ソースが第2のオン／オフモジュールと第3のオン／オフモジュールとに接続される第7の薄膜トランジスタと、ゲートが前記第2のクロック信号端子に接続され、ソースがインターロックノードとなる第4のノードに接続され、ドレーンがローレベル信号端子に接続される第8の薄膜トランジスタと、ゲートとソースとが共に接続されて前記第1のクロック信号端子に接続され、ドレーンが前記第4のノードに接続される第9の薄膜トランジスタとを有し、後述の第1のオン／オフモジュール、第2のオン／オフモジュールおよび第3のオン／オフモジュールを制御する第1段のオン／オフモジュールと、

ゲートが前記第2のクロック信号端子に接続され、ソースが前記第2のノードに接続され、ドレーンがローレベル信号端子に接続される第10の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第2のノードに接続され、ドレーンがローレベル信号端子に接続される第11の薄膜トランジスタとを有し、本段のシフト・レジスタが動作しない時に、本段の出力端子をローレベルに保持する第1のオン／オフモジュールと、

ゲートが第7の薄膜トランジスタのソースに接続され、ソースが前記第1のノードに接続され、ドレーンが上段のフィードバックモジュールに接続される第12の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第2のノードに接続され、ドレーンが前記第1のノードに接続される第13の薄膜トランジスタとを有し、本段のシフト・レジスタが動作しない時に、前記第1のノードをローレベルに保持する第2のオン／オフモジュールと、

ゲートが第7の薄膜トランジスタのソースに接続され、ソースが前記第3のノードに接続され、ドレーンがローレベル信号端子に接続される第14の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第3のノードに接続され、ドレーンがローレベル信号端子に接続される第15の薄膜トランジスタとを有し、本段のシフト・レジスタが動作しない時に前記第3のノードをローレベルに保持する第3のオン／オフモジュールと、備える

ことを特徴とする請求項1に記載のシフト・レジスタ。

#### 【請求項3】

ゲートがオン／オフ信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがローレベル信号端子に接続される第16の薄膜トランジスタをさらに備える

ことを特徴とする請求項1または請求項2に記載のシフト・レジスタ。

#### 【請求項4】

ゲートがオン／オフ信号端子に接続され、ソースがリセット信号端子に接続され、ドレ

10

20

30

40

50

ーンが前記第2のノードに接続される第17の薄膜トランジスタを更に備えることを特徴とする請求項1または請求項2に記載のシフト・レジスタ。

【請求項5】

直列に接続された複数のシフト・レジスタを備えるゲートライン駆動装置であって、前記シフト・レジスタは、

ゲートがプルアップノードとなる第1のノードに接続され、ソースが第1のクロック信号端子に接続され、ドレーンが本段の出力端子に接続される第1の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがローレベル信号端子に接続される第2の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースがプルダウンノードとなる第2のノードに接続され、ドレーンがローレベル信号端子に接続され、前述第2のノードが本段の出力端に接続される第3の薄膜トランジスタと、

前記第1のノードと本段の出力端子との間に接続されるコンデンサと、

上段の第1のトリガー信号端子及び第2のトリガー信号端子と、前記第1のクロック信号端子及び第2のクロック信号端子と、前記第1のノードに接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュールと、

、

第1及び第2のクロック信号端子と前記フィードバックモジュールと本段の出力端子との間に接続され、且つローレベル信号端子に接続されるオン／オフモジュールと、を備え、

前記フィードバックモジュールは上段のフィードバックモジュールの第1及び第2のトリガー信号と第2のクロック信号を受信して前記第1のノードのレベルをプルアップし、且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールにトリガー信号を出力し、前記オン／オフモジュールは、本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持し、

前記フィードバックモジュールは、

ゲートが上段のフィードバックモジュールの前記第1のトリガー信号端子に接続され、ソースが第5の薄膜トランジスタのゲートに接続され、ドレーンが前記第2のクロック信号端子に接続される第4の薄膜トランジスタと、

ゲートが第4の薄膜トランジスタのソースに接続され、ソースが前記第1のノードに接続され、ドレーンが上段のフィードバックモジュールの第2のトリガー信号端子に接続される第5の薄膜トランジスタと、

ゲートが前記第1のノードに接続され、ソースが前記第1のクロック信号端子に接続され、ドレーンが本段のフィードバックノードとなる第3のノードに接続される第6の薄膜トランジスタとをさらに備える

ことを特徴とするゲートライン駆動装置。

【請求項6】

前記オン／オフモジュールは、

ゲートとドレーンとが共に接続されて前記第2のクロック信号端子に接続され、ソースが第2のオン／オフモジュールと第3のオン／オフモジュールとに接続される第7の薄膜トランジスタと、ゲートが前記第2のクロック信号端子に接続され、ソースがインターロックノードとなる第4のノードに接続され、ドレーンがローレベル信号端子に接続される第8の薄膜トランジスタと、ゲートとソースとが共に接続されて前記第1のクロック信号端子に接続され、ドレーンが前記第4のノードに接続される第9の薄膜トランジスタとを有し、後述の第1のオン／オフモジュール、第2のオン／オフモジュールおよび第3のオン／オフモジュールを制御する第1段のオン／オフモジュールと、

ゲートが前記第2のクロック信号端子に接続され、ソースが前記第2のノードに接続され、ドレーンがローレベル信号端子に接続される第10の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第2のノードに接続され、ドレーンがローレベル信号端子に接続される第11の薄膜トランジスタとを有し、本段のシフト・レジスタ

10

20

30

40

50

が動作しない時に、本段の出力端子をロー・レベルに保持する第1のオン／オフモジュールと、

ゲートが第7の薄膜トランジスタのソースに接続され、ソースが前記第1のノードに接続され、ドレーンが上段のフィードバックモジュールに接続される第12の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第2のノードに接続され、ドレーンが前記第1のノードに接続される第13の薄膜トランジスタとを有し、本段のシフト・レジスタが動作しない時に、前記第1のノードをロー・レベルに保持する第2のオン／オフモジュールと、

ゲートが第7の薄膜トランジスタのソースに接続され、ソースが前記第3のノードに接続され、ドレーンがロー・レベル信号端子に接続される第14の薄膜トランジスタと、ゲートが前記第4のノードに接続され、ソースが前記第3のノードに接続され、ドレーンがロー・レベル信号端子に接続される第15の薄膜トランジスタとを有し、本段のシフト・レジスタが動作しない時に前記第3のノードをロー・レベルに保持する第3のオン／オフモジュールと、を備える

ことを特徴とする請求項5に記載のゲートライン駆動装置。

#### 【請求項7】

前記シフト・レジスタは、

ゲートがオン／オフ信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがロー・レベル信号端子に接続される第16の薄膜トランジスタをさらに備える

ことを特徴とする請求項5または請求項6に記載のゲートライン駆動装置。

#### 【請求項8】

前記シフト・レジスタは、

ゲートがオン／オフ信号端子に接続され、ソースがリセット信号端子に接続され、ドレーンが前記第2のノードに接続される第17の薄膜トランジスタを更に備える

ことを特徴とする請求項5または請求項6に記載のゲートライン駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶ディスプレーの技術分野に係わり、特にシフト・レジスタおよびゲートライン駆動装置に関するものである。

##### 【背景技術】

##### 【0002】

液晶ディスプレーの画素アレイは交差した複数行のゲートラインと複数列のデータラインを備える。複数のシフト・レジスタからなるゲートライン駆動装置は、画素アレイの複数行のゲートラインにオン／オフ信号を提供することで、複数行のゲートラインを順次にオンにするように制御し、且つ対応した行のデータラインにより画素アレイ中の画素電極に充電して、画像の各グレースケールの表示に必要とする階調電圧を形成し、さらに各フレームの画像を表示する。

##### 【0003】

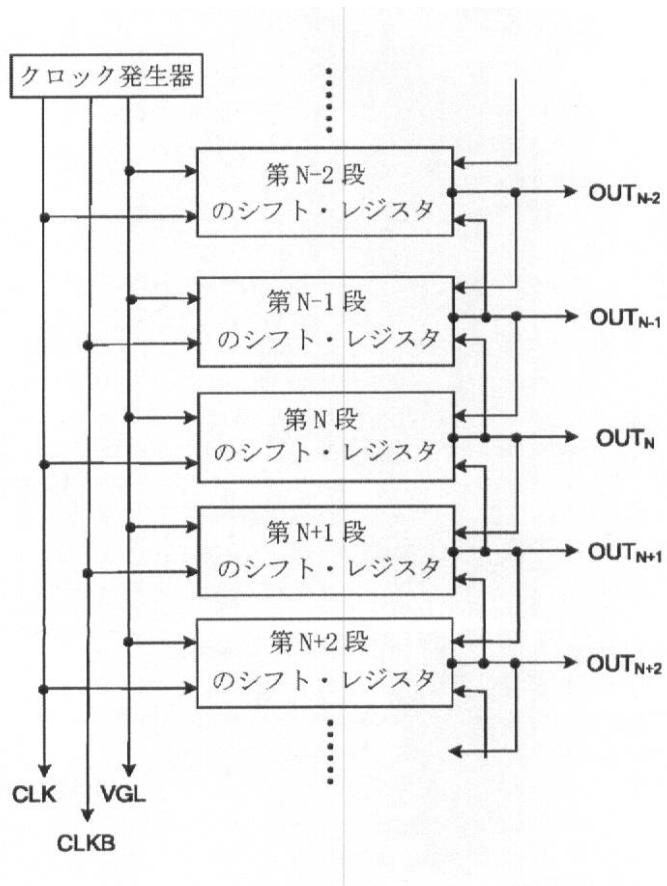

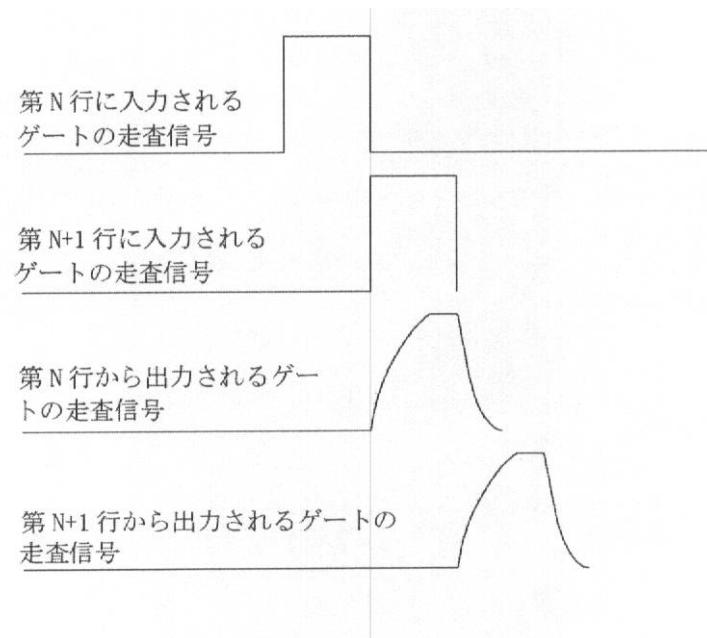

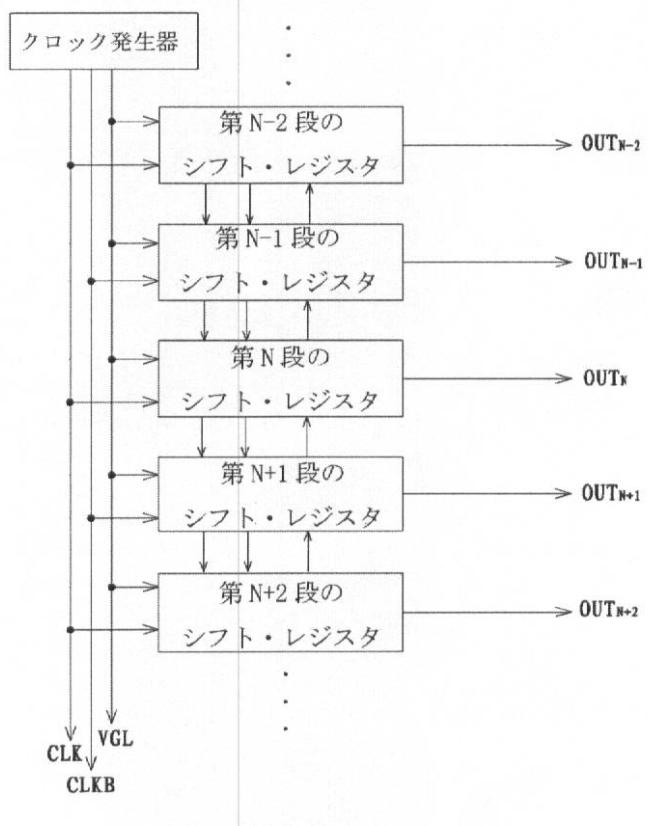

図1に示すように、従来のゲートライン駆動装置は、複数のシフト・レジスタを備える。第N段のシフト・レジスタの出力OUTNは、第N-1段のシフト・レジスタをオフにするように第N-1段のシフト・レジスタにフィードバックするだけでなく、それと共に第N+1段シフト・レジスタのトリガー信号として該第N+1段のシフト・レジスタに出力される。しかしながら、図2に示すように、その中の一段のシフト・レジスタの出力を他の一段のシフト・レジスタのトリガー信号とする場合に、出力端子に接続された負荷が大きいため、入力端子で方形波に接近した信号は、出力端子で遅延が生じる。遅延が大きい場合に、連続する二つの行のゲートラインは同時にオンされる現象が生じるとともに、画素アレイが出力端子に干渉するため、出力端子信号の安定性の低下を招く。それによって、リード／ライトエラーが生じやすいので、画像の品質に影響を伝える。

##### 【0004】

10

20

30

40

50

なお、その中の一段のシフト・レジスタの出力を他の一段のシフト・レジスタのトリガ-信号とする場合に、クロック信号CLK、CKLBがこの出力と同期してトリガーされる必要がある。このように、図3に示すように、クロック信号CLK、CKLBそれぞれのデューティ比は50%に保持される必要がある。このデューティ比により、二行のゲートライン駆動の間に冗長時間が予め残されなくて、その中の一段のシフト・レジスタが十分にオフされた後に、他の一段のシフト・レジスタがオンされることを保障することができない。また、これによって、連続する二行のゲートラインが同時にオンされて、信号のクロストークが発生やすいので、最後に画像の品質に影響する。

【発明の概要】

【発明が解決しようとする課題】

10

【0005】

本発明が解決しようとする技術課題は、ゲートラインのオンエラーを低減して画像の品質を向上できるシフト・レジスタを提供することである。

【課題を解決するための手段】

【0006】

上記技術課題を解決するために、本発明は以下のような技術案を採用する。

シフト・レジスタは、

ゲートがプルアップノードとなる第1のノードに接続され、ソースがクロック信号端子に接続され、ドレーンが本段の出力端子に接続される第1の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがローレベル信号端子に接続される第2の薄膜トランジスタと、

20

ゲートが下段のフィードバック信号端子に接続され、ソースがプルダウンノードとなる第2のノードに接続され、ドレーンがローレベル信号端子に接続される第3の薄膜トランジスタと、

前記第1のノードと本段の出力端子との間に接続されるコンデンサと、

上段のトリガー信号端子とクロック信号端子と前記第1のノードとの間に接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュールと、

クロック信号端子と前記フィードバックモジュールと本段の出力端子との間に接続され、且つローレベル信号端子に接続されるオン/オフモジュールと、を備え、

30

前記フィードバックモジュールは上段のフィードバックモジュールのトリガー信号とクロック信号を受信して前記第1のノードのレベルをプルアップし、且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールにトリガー信号を出力し、前記オン/オフモジュールは、本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持される。

【0007】

本発明が提供したシフト・レジスタは、前記フィードバックモジュールによって、前記シフト・レジスタの中間信号をフィードバック信号として上段のシフト・レジスタに出力し、トリガー信号として下段のシフト・レジスタに出力する。このように、一方、この中間信号が負荷を駆動する必要がないので、遅延が小さく、且つこの中間信号が画素アレイに干渉されなく、安定性が一層高くなる。他方、前記シフト・レジスタの出力信号を上記フィードバック信号とトリガー信号としないので、出力信号とクロック信号が同期を取る必要がないので、クロック信号のデューティ比を低減し、且つ二行のゲートライン駆動の間に冗長時間が予め残される。上記両方で、連続した二行のゲートラインが同時にオンする現象をよりよく防止するので、ゲートラインのオンエラーを低減し、画像の品質を向上することができる。

【0008】

本発明が解決しようとするほかの技術課題はゲートラインのオンエラーを低減して画像の品質を向上できるゲートライン駆動装置を提供することである。

【0009】

40

50

上記技術課題を解決するために、本発明は以下のような技術案を採用する。

直列に接続された複数のシフト・レジスタを備えるゲートライン駆動装置であって、

前記シフト・レジスタは、

ゲートがブルアップノードとなる第1のノードに接続され、ソースがクロック信号端子に接続され、ドレーンが本段の出力端子に接続される第1の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースが前記第1のノードに接続され、ドレーンがローレベル信号端子に接続される第2の薄膜トランジスタと、

ゲートが下段のフィードバック信号端子に接続され、ソースがブルダウンノードとなる第2のノードに接続され、ドレーンがローレベル信号端子に接続され、前述第2のノードが本段の出力端に接続される第3の薄膜トランジスタと、

10

前記第1のノードと本段の出力端子との間に接続されるコンデンサと、

上段のトリガー信号端子とクロック信号端子と前記第1のノードとの間に接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュールと、

クロック信号端子、前記フィードバックモジュールと本段の出力端子に接続され、且つローレベル信号端子に接続されるオン/オフモジュールと、を備え、

前記フィードバックモジュールは上段のフィードバックモジュールのトリガー信号とクロック信号を受信して前記第1のノードのレベルをブルアップし、且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールにトリガー信号を出力し、前記オン/オフモジュールは、本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持することを特徴とするゲートライン駆動装置。

20

#### 【0010】

本発明が提供したゲートライン駆動装置において、シフト・レジスタには、前記フィードバックモジュールによって、前記シフト・レジスタの中間信号をフィードバック信号として上段のシフト・レジスタに出力し、トリガー信号として下段のシフト・レジスタに出力する。このように、この中間信号が負荷を駆動する必要がないので、遅延が小さく、且つこの中間信号が画素アレイに干渉されなく、安定性が一層高くなる。一方、前記シフト・レジスタの出力信号を上記フィードバック信号とトリガー信号としないので、出力信号とクロック信号が同期を取る必要がないので、クロック信号のデューティ比を低減し、且つ二行のゲートライン駆動の間に冗長時間が予め残される。上記両方で、連続した二行のゲートラインが同時にオンする現象をよりよく避けるので、ゲートラインのオンエラーを低減し、画像の品質を向上することができる。

30

#### 【図面の簡単な説明】

#### 【0011】

【図1】従来技術に係るゲートライン駆動装置の概略図。

【図2】従来技術に係るゲートライン駆動における入力端子信号と出力端子信号の概略図。

。

【図3】従来技術に係るクロック信号の概略図。

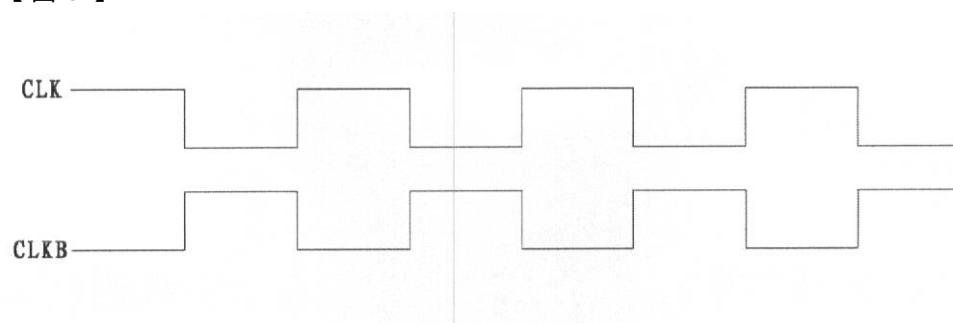

【図4】本発明に係るシフト・レジスタの概略図。

40

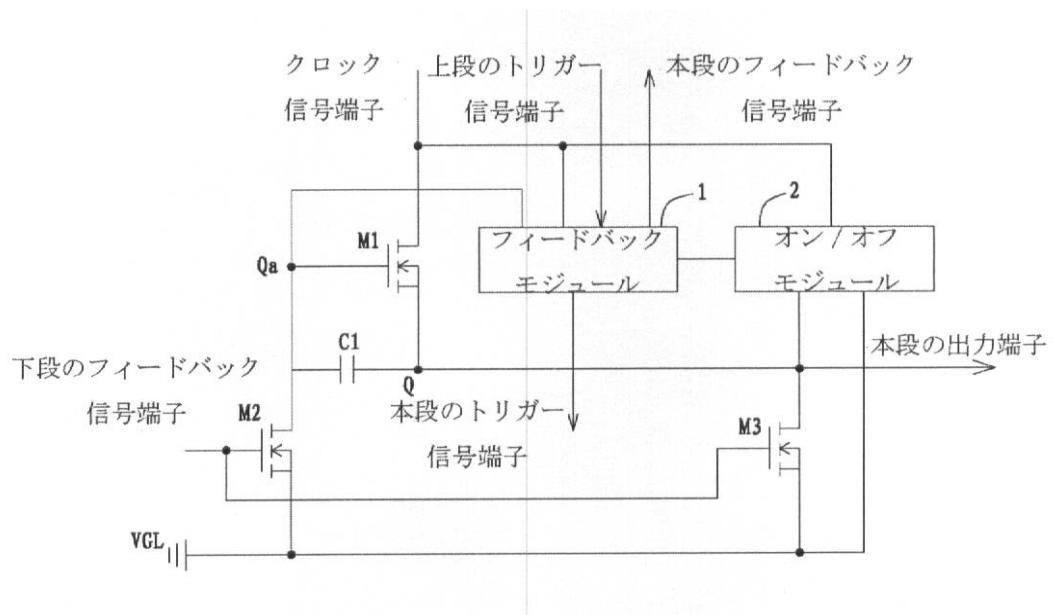

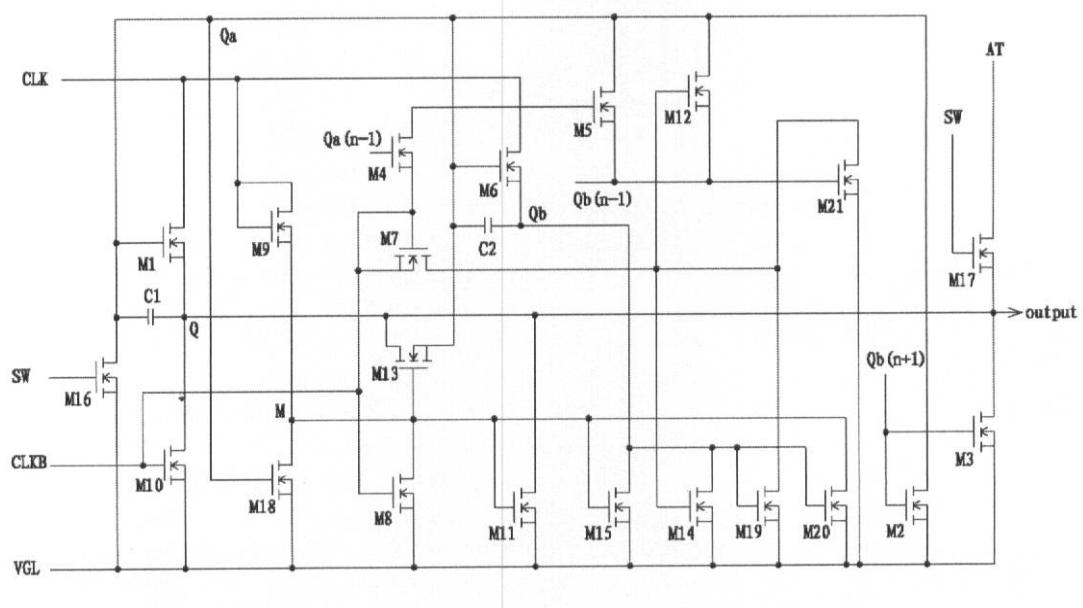

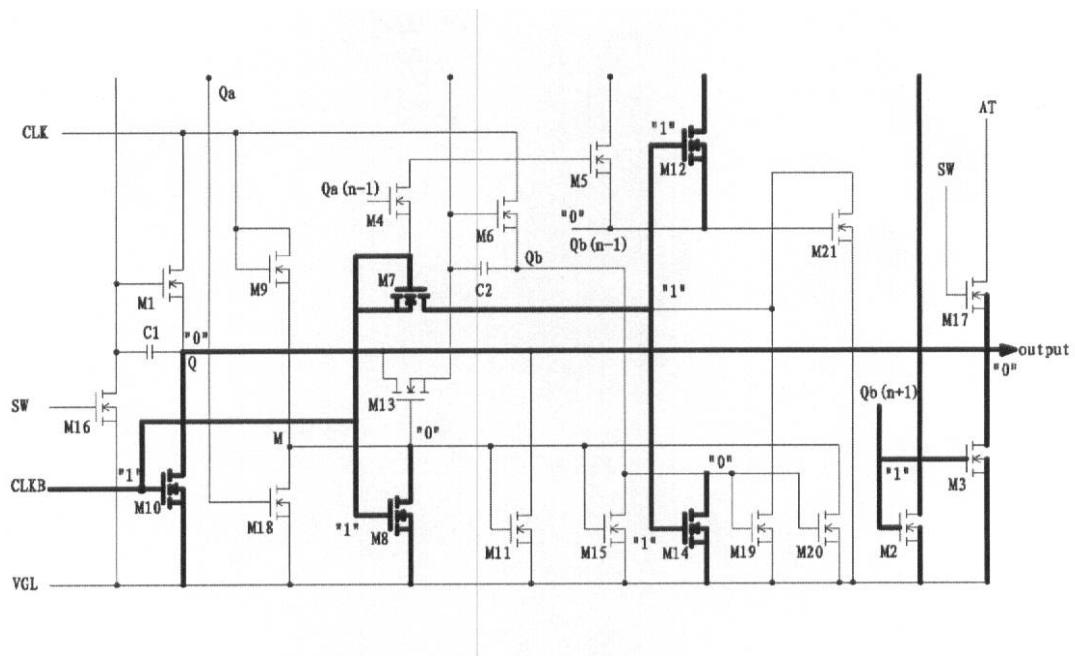

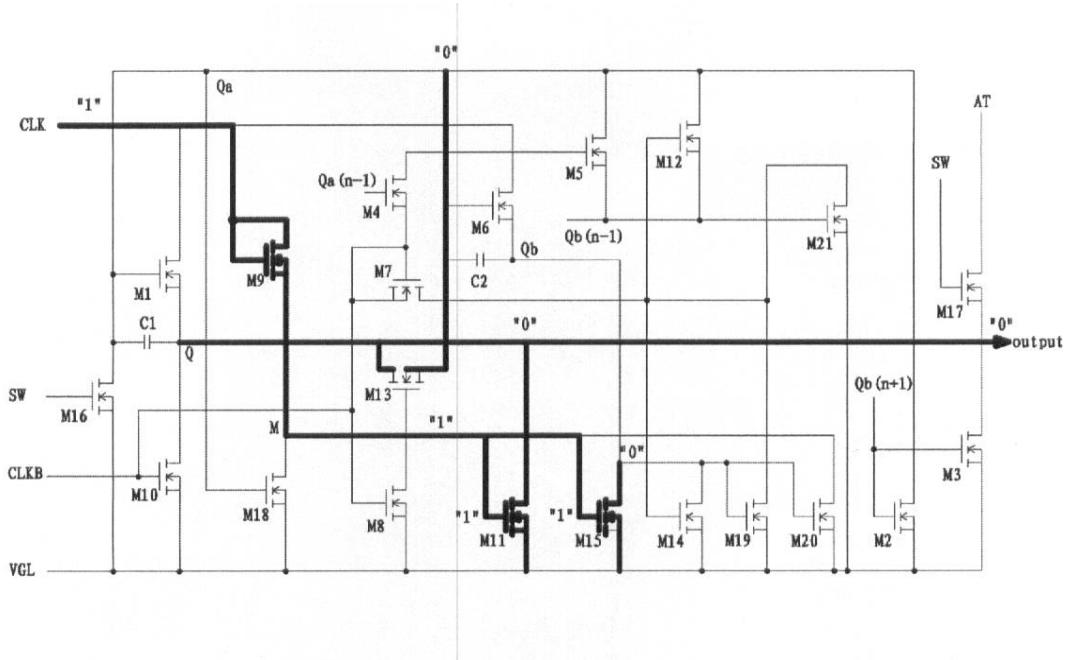

【図5】本発明に係るシフト・レジスタの実施例の概略図。

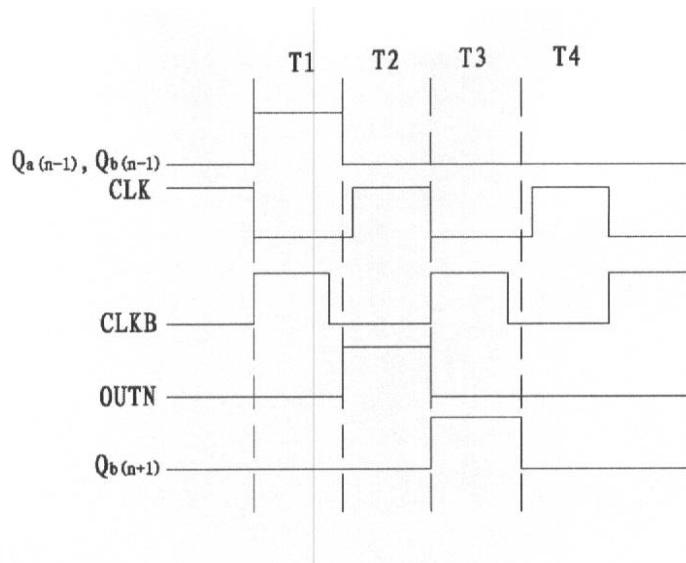

【図6】本発明に係るシフト・レジスタの実施例における信号の概略図。

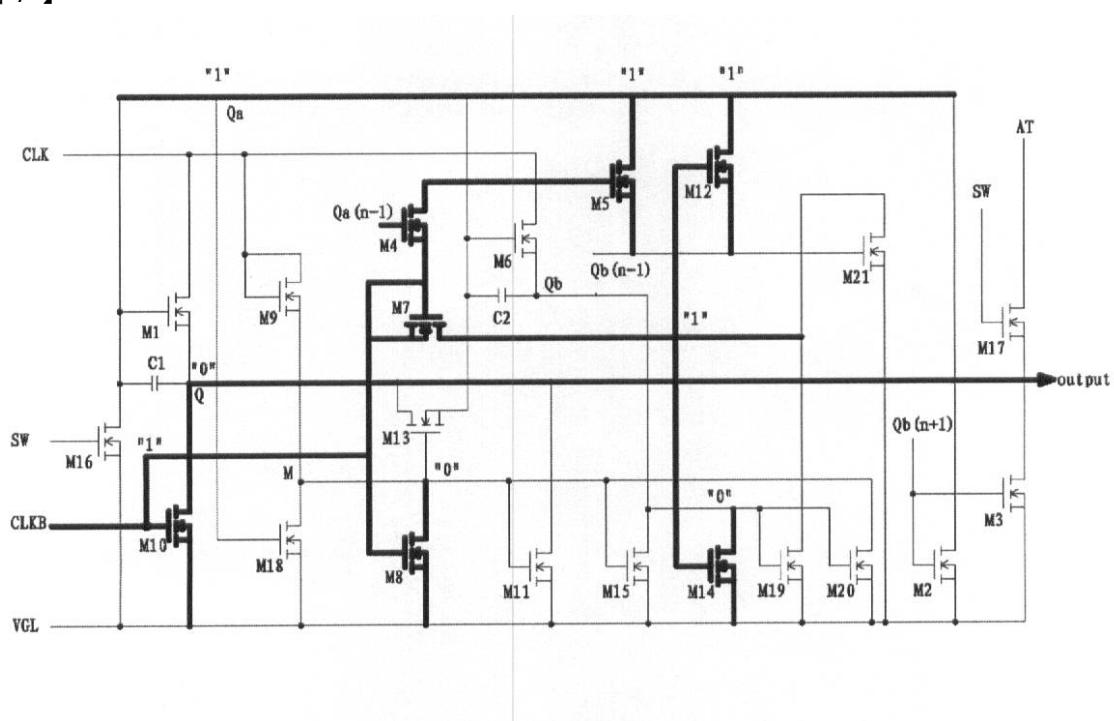

【図7】図4に示したシフト・レジスタのT1段階における動作の概略図。

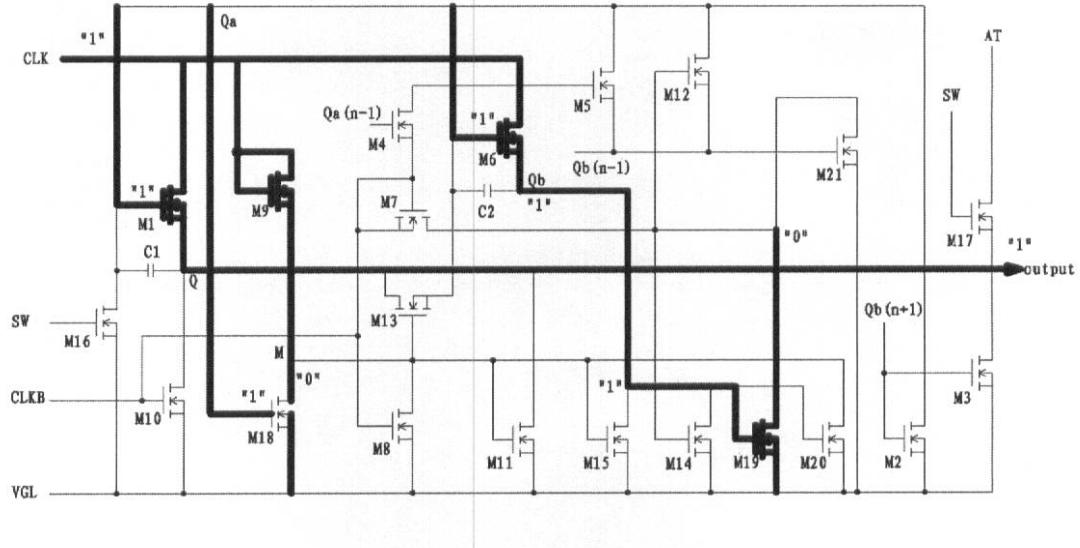

【図8】図4に示したシフト・レジスタのT2段階における動作の概略図。

【図9】図4に示したシフト・レジスタのT3段階における動作の概略図。

【図10】図4に示したシフト・レジスタのT4段階における動作の概略図。

【図11】本発明に係るゲートライン駆動装置の実施例の概略図。

#### 【発明を実施するための形態】

#### 【0012】

本発明はゲートラインのオンエラーを低減して画像の品質を改善できるシフト・レジス

50

タ及びゲートライン駆動装置を提供することを目的にする。

以下は図面と実施例を通じて本発明の技術方案をさらに詳細に説明する。

【0013】

図4に示すように、本発明のシフト・レジスタは、3つの水素化アモルファスシリコン薄膜トランジスタと、1つの記憶コンデンサと、1つのフィードバックモジュールと、1つのオン/オフモジュールと、対応する入力/出力端子を備える。当該シフト・レジスタは、そのゲートがプルアップノードとなる第1のノードQaに接続され、そのソースがクロック信号端子に接続され、そのドレーンが本段の出力端子に接続され、その作用は、そのゲートに接続される第1のノードQaがハイレベルであり且つそのソースがハイレベル信号を受信した時に、シフト・レジスタに動作を始めさせるように制御することである第1の薄膜トランジスタM1と、そのゲートが下段のフィードバック信号端子に接続され、そのソースが第1のノードQaに接続され、そのドレーンがローレベル信号端子に接続され、その作用は、下段のフィードバック信号がハイレベルである時に第1のノードQaをローレベルに保持させて第1の薄膜トランジスタM1のゲートをローレベルに維持することである第2の薄膜トランジスタM2と、そのゲートが下段のフィードバック信号端子に接続され、そのソースがプルダウンノードとなる第2のノードQに接続され（その中、前述第2のノードQが本段の出力端に接続される）、そのドレーンがローレベル信号端子に接続され、その作用は、下段のフィードバック信号がハイレベルである時に第2のノードQをローレベルに保持させて本段の出力端子をローレベルに維持することである第3の薄膜トランジスタM3と、第1のノードQaと本段の出力端子との間に接続されるコンデンサC1と、上段のトリガー信号端子とクロック信号端子と第1のノードQaとの間に接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュール1と、クロック信号端子とフィードバックモジュール1と本段の出力端子との間に接続され、且つローレベル信号端子に接続されるオン/オフモジュール2と、を備える。フィードバックモジュール1は上段のフィードバックモジュールのトリガー信号とクロック信号を受信して第1のノードQaのレベルをプルアップし、且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールにトリガー信号を出力することに用いられる。オン/オフモジュール2は本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持することに用いられる。

【0014】

本発明が提供したシフト・レジスタは、フィードバックモジュール1によって、前記シフト・レジスタの中間信号をフィードバック信号として上段のシフト・レジスタに出力し、且つトリガー信号として下段のシフト・レジスタに出力することができる。このように、この中間信号が負荷を駆動する必要がないので、遅延が小さく、且つこの中間信号が画素アレイに干渉されなく、安定性が一層高くなる一方、前記シフト・レジスタの出力信号を上記フィードバック信号とトリガー信号としないので、出力信号とクロック信号が同期を取る必要がないので、クロック信号のデューティ比を低減し、且つ二行のゲートライン駆動の間に冗長時間が予め残されることができる。上記の両方で、連続した二行のゲートラインが同時にターンオンする現象をよりよく避けるので、ゲートラインのオンエラーを低減し、画像の品質を向上させることができる。

【0015】

図5は本発明シフト・レジスタ実施例の構造概略図である。本実施例においては、前記シフト・レジスタは21個の水素化アモルファスシリコン薄膜トランジスタと、1つの記憶コンデンサと、対応する入力出力端子と、を備える。この21個の水素化アモルファスシリコン薄膜トランジスタはそれぞれ第1の薄膜トランジスタM1と、第2の薄膜トランジスタM2と、第3の薄膜トランジスタM3と、第4の薄膜トランジスタM4と、第5の薄膜トランジスタM5と、第6の薄膜トランジスタM6と、第7の薄膜トランジスタM7と、第8の薄膜トランジスタM8と、第9の薄膜トランジスタM9と、第10の薄膜トランジスタM10と、第11の薄膜トランジスタM11と、第12の薄膜トランジスタM12と、第13の薄膜トランジスタM13と、第14の薄膜トランジスタM14と、第15の薄膜トランジスタM15と、第16の薄膜トランジスタM16と、第1

10

20

30

40

50

7の薄膜トランジスタM17と、第18の薄膜トランジスタM18と、第19の薄膜トランジスタM19と、第20の薄膜トランジスタM20と、第21の薄膜トランジスタM21である。記憶コンデンサはコンデンサC1である。入力出力端子は本段の出力端子outputと、周期的に切り替えて使用する第1のクロック信号端子CLK及び第2のクロック信号端子CLKBと、上段のシフト・レジスタのトリガー信号を受信する第1のトリガー信号端子Qa(n-1)及び第2のトリガー信号端子Qb(n-1)と、下段のフィードバック信号端子Qb(n+1)と、ローレベル信号端子VGLと、オン/オフ信号端子SWと、リセット信号端子ATである。

#### 【 0 0 1 6 】

具体的には、第1の薄膜トランジスタM1は、そのゲートがプルアップノードとなる第1のノードQaに接続され、そのソースが第1のクロック信号端子CLKに接続され、そのドレーンが本段の出力端子outputに接続される。第2の薄膜トランジスタM2は、そのゲートが下段のフィードバック信号端子Qb(n+1)に接続され、そのソースが第1のノードQaに接続され、そのドレーンがローレベル信号端子VGLに接続される。第3の薄膜トランジスタM3は、そのゲートが下段のフィードバック信号端子Qb(n+1)に接続され、そのソースがプルダウンノードとなる第2のノードQに接続され（その中、前述第2ノードQが本段の出力端outputに接続される）、そのドレーンがローレベル信号端子VGLに接続される。第4の薄膜トランジスタM4は、そのゲートが上段のシフト・レジスタのトリガー信号を受信する第1のトリガー信号端子Qa(n-1)に接続され、そのソースが第5の薄膜トランジスタM5のゲートに接続され、そのドレーンが第2のクロック信号端子CLKBに接続される。第5の薄膜トランジスタM5は、そのゲートが第4の薄膜トランジスタM4のソースに接続され、そのソースが第1のノードQaに接続され、そのドレーンが上段のシフト・レジスタのトリガー信号を受信する第2のトリガー信号端子Qb(n-1)に接続される。第6の薄膜トランジスタM6は、そのゲートが第1のノードQaに接続され、そのソースが第1のクロック信号端子CLKに接続され、そのドレーンが本段のフィードバックノードとなる第3のノードQbに接続される。第7の薄膜トランジスタM7は、そのゲートとドレーンとが共に接続されて第2のクロック信号端子CLKBに接続され、そのソースが第12の薄膜トランジスタM12のゲートと第14の薄膜トランジスタM14のゲートとに接続される。第8の薄膜トランジスタM8は、そのゲートが第2のクロック信号端子CLKBに接続され、そのソースがインターロックノードとなる第4のノードMに接続され、そのドレーンがローレベル信号端子VGLに接続される。第9の薄膜トランジスタM9は、そのゲートとソースとが共に接続されて第1のクロック信号端子CLKに接続され、そのドレーンが第4のノードMに接続される。第10の薄膜トランジスタM10は、そのゲートが第2のクロック信号端子CLKBに接続され、そのソースが第2のノードQに接続され、そのドレーンがローレベル信号端子VGLに接続される。第11の薄膜トランジスタM11は、そのゲートが第4のノードMに接続され、そのソースが第2のノードQに接続され、そのドレーンがローレベル信号端子VGLに接続される。第12の薄膜トランジスタM12は、そのゲートが第7の薄膜トランジスタM7のソースに接続され、そのソースが第1のノードQaに接続され、そのドレーンが上段のシフト・レジスタの第2のトリガー信号端子Qb(n-1)に接続される。第13の薄膜トランジスタM13は、そのゲートが第4のノードMに接続され、そのソースが第2のノードQに接続され、そのドレーンが第1のノードQaに接続される。第14の薄膜トランジスタM14は、そのゲートが第7の薄膜トランジスタM7のソースに接続され、そのソースが第3のノードQbに接続され、そのドレーンがローレベル信号端子VGLに接続される。第15の薄膜トランジスタM15は、そのゲートが第4のノードMに接続され、そのソースが第3のノードQbに接続され、そのドレーンがローレベル信号端子VGLに接続される。第16の薄膜トランジスタM16は、そのゲートがオン/オフ信号端子SWに接続され、そのソースが第1のノードQaに接続され、そのドレーンがローレベル信号端子VGLに接続される。第17の薄膜トランジスタM17は、そのゲートがオン/オフ信号端子SWに接続され、そのソースがリセット信号端子ATに接続され、そのドレーンが第2のノードQに接続される。第18の薄膜トランジスタM18は、そのゲートが第1のノードQaに接続され、そのソースが第4のノードMに接続され、そのドレーンがローレベル信号端子VGLに接続される。第19の薄膜トランジスタM19は、そのゲートが第3のノードQbに接続され、そのソースが第7の薄膜トランジスタM7のソースに接続され、そ

10

20

30

40

50

のドレーンがローレベル信号端子VGLに接続される。第20の薄膜トランジスタM20は、そのゲートが第3のノードQbに接続され、そのソースが第4のノードMに接続され、そのドレーンがローレベル信号端子VGLに接続される。第21の薄膜トランジスタM21は、そのゲートが上段のシフト・レジスタの第2のトリガー信号端子Qb(n-1)に接続され、そのソースが第7の薄膜トランジスタM7のソースに接続され、そのドレーンがローレベル信号端子VGLに接続される。しかも、記憶コンデンサC1は第1のノードQaと本段の出力端子outputとの間に接続される。

【0017】

第4の薄膜トランジスタM4と第5の薄膜トランジスタM5と第6の薄膜トランジスタM6とは本実施例のフィードバックモジュールを構成している。このフィードバックモジュールは前記シフト・レジスタの中間信号をフィードバック信号として上段のシフト・レジスタに出力し、且つトリガー信号として下段のシフト・レジスタに出力する。このように、この中間信号が負荷を駆動する必要がないので、遅延が小さく且つこの中間信号が画素アレイに干渉されなく、その安定性が高い。一方、前記シフト・レジスタの出力信号を上記フィードバック信号とトリガー信号としないので、出力信号とクロック信号が同期を取る必要がないので、クロック信号のデューティ比を低減し、且つ二行のゲートライン駆動の間に冗長時間が予め残される。上記両方で、連続した二行のゲートラインが同時にオンする現象をよりよく避けるので、ゲートラインのオンエラーを低減し、画像の品質を向上することができる。

【0018】

また、上記第10の薄膜トランジスタM10と第11の薄膜トランジスタM11とは第1のオン/オフモジュールを構成している。この第1のオン/オフモジュールは、本段のシフト・レジスタが動作しない時に本段の出力端子outputをローレベルに保持することで、本段の出力端子outputが他の干渉信号によってハイレベルになって制御したこの行のゲートラインがハイレベルによってオンして、最終にゲートラインのオンエラーが生じることを防止することに用いられる。第10の薄膜トランジスタM10は、第2のクロック信号CLKBによって本段の出力端子outputをローレベルに保持し、第11の薄膜トランジスタM11は第1のクロック信号CLKによって本段の出力端子outputをローレベルに保持する。

【0019】

上記第12の薄膜トランジスタM12と第13の薄膜トランジスタM13とが第2のオン/オフモジュールを構成している。この第2のオン/オフモジュールは本段のシフト・レジスタが動作しない時に、プルアップノードとなる第1のノードQaをローレベルに保持することで、第1の薄膜トランジスタM1をオンさせないようにして、更に本段の出力端子outputをローレベルに保持する。第12の薄膜トランジスタM12は第2のクロック信号CLKBによって第1のノードQaをローレベルに保持し、第13の薄膜トランジスタM13は第1のクロック信号CLKによって第1のノードQaをローレベルに保持する。

【0020】

上記第14の薄膜トランジスタM14と第15の薄膜トランジスタM15とが第3のオン/オフモジュールを構成している。この第3のオン/オフモジュールは本段のシフト・レジスタが動作しない時に第3のノードQbをローレベルに保持することで、上段のシフト・レジスタと下段のシフト・レジスタに干渉しないように第3のノードQbが上段のシフト・レジスタに出力したフィードバック信号と下段のシフト・レジスタに出力したトリガー信号とをローレベルにする。第14の薄膜トランジスタM14は第2のクロック信号CLKBによって第3のノードQbをローレベルに保持し、第15の薄膜トランジスタM15は第1のクロック信号CLKによって第3のノードQbをローレベルに保持する。

【0021】

上記第7の薄膜トランジスタM7と第8の薄膜トランジスタM8と第9の薄膜トランジスタM9とが第1段のオン/オフモジュールを構成している。この第1段のオン/オフモジュールは上記第1のオン/オフモジュールと第2のオン/オフモジュールと第3のオン/オフモジュールを制御することに用いられる。ここで、上記「制御」とは、上記各オン/オフモジュールを

10

20

30

40

50

オン／オフし、及び上記各オン／オフモジュールにおける、第1のクロック信号で動作する薄膜トランジスタと第2のクロック信号で動作する薄膜トランジスタをインターロックすることである。

【0022】

最終には、上記第1のオン／オフモジュールと第2のオン／オフモジュールと第3のオン／オフモジュールと第1段のオン／オフモジュールは本実施例におけるオン／オフモジュールを構成している。このオン／オフモジュールは本段のシフト・レジスタが動作しない時に本段のシフト・レジスタの出力端子をローレベルに保持する。

【0023】

更に、図5に示すように、本段のシフト・レジスタは、ゲートがオン／オフ信号端子SWに接続され、ソースが第1のノードQaに接続され、ドレーンがローレベル信号端子VGLに接続される第16の薄膜トランジスタM16を更に備える。この第16の薄膜トランジスタM16は、特定の場合にオンされ、例えば、人工で本段のシフト・レジスタをオフにする場合にオンされて、第1のノードQaのレベルをプルダウンする。そして第1の薄膜トランジスタM1がオフされ、最終に本段の出力端子outputがローレベルに保持される。

【0024】

更に、図5に示すように、本段のシフト・レジスタは、ゲートがオン／オフ信号端子SWに接続され、ソースがリセット信号端子ATに接続され、ドレーンが第2のノードQ（即ち本段の出力端子output）に接続される第17の薄膜トランジスタM17を更に備える。この第17の薄膜トランジスタM17はオン／オフ信号SWでオンされてリセット信号ATを受信する。このリセット信号ATは液晶ディスプレーの画像をクリーンするように、すべてのシフト・レジスタをターンオフすることができる。

【0025】

上記第18の薄膜トランジスタM18と第19の薄膜トランジスタM19と第20の薄膜トランジスタM20と第21の薄膜トランジスタM21とは、本段のシフト・レジスタの動作を補佐することができる。

【0026】

実際の使用においては、本実施例の上記技術方案は水素化アモルファスシリコン薄膜トランジスタに適用するだけでなく、他の薄膜トランジスタにも適用する。

【0027】

説明することには、上記実施例が本発明のシフト・レジスタの好適な実施形態にすぎなく、それを限定するものではない。

【0028】

以下は、図5に示したシフト・レジスタ及び制御シーケンスを結合して本実施例のシフト・レジスタの動作過程を説明する。

図6は本実施例に係わる信号の概略図である。T1、T2、T3、及びT4という四つの段階に分けることができる。

【0029】

T1段階において、Qa(n-1)=1、Qb(n-1)=1、CLK=0、CLKB=1、Qb(n+1)=0とする。

図7における太くされた部分に示すように、Qa(n-1)=1、即ち第1のトリガー信号端子がハイレベルであるため、第4の薄膜トランジスタがオンされると共に、CLKB=1、即ち第2のクロック信号がハイレベルであるため、第5の薄膜トランジスタM5がオンされ、又Qb(n-1)=1、即ち第2のトリガー信号端子がハイレベルであるので、第1のノードQaがハイレベルにプルアップされ、即ちQa=1となり、且つ記憶コンデンサC1によって第1のノードQaがハイレベルに保持される。しかしながら、この時にCLKB=1となるので、第10の薄膜トランジスタM10がオンされて、本段の出力端子outputをそのままローレベルに保持させ、即ちOUTN=0にする。この時に、本段のシフト・レジスタはオフ状態となる。

【0030】

T2段階においては、Qa(n-1)=0、Qb(n-1)=0、CLK=1、CLKB=0、Qb(n+1)=0とする。

図8における太くされた部分に示すように、T1段階においてQa=1であるので、第1の薄膜

10

20

30

40

50

トランジスタM1がオンされ、この時にCLK=1となるので、本段の出力端子outputがハイレベルとなり、即ちOUTN=1となる。この時に本段のシフト・レジスタはオン状態となる。それと同時に、第1のノードQa=1となるので、第6の薄膜トランジスタM6がオンされ、それにCLK=1となるので、フィードバックノードQbがハイレベルとなる、即ちQb=1となる。この段階において、ノードQaとQbが下段のシフト・レジスタに二つのトリガー信号を出力することで、下段のシフト・レジスタがこの二つのトリガー信号によってオンされることができる。更に、上段のシフト・レジスタをオフにするように、ノードQbを通じて上段のシフト・レジスタにフィードバック信号を出力することができる。

#### 【 0 0 3 1 】

T3段階においては、Qa(n-1)=0、Qb(n-1)=0、CLK=0、CLKB=1、Qb(n+1)=1とする。 10

図9における太くされた部分に示すように、Qb(n+1)=1、即ち下段のフィードバック信号端子がハイレベルであるので、この時に第2の薄膜トランジスタM2と第3の薄膜トランジスタM3がオンされることがある。第3の薄膜トランジスタM3のオンによって本段の出力端子outputがローレベルになり、即ちOUTN=0になる。この時に本段のシフト・レジスタはオフ状態となる。第2の薄膜トランジスタM2のオンによって第1のノードQaがローレベルになり、即Qa=0になる。このように、第1の薄膜トランジスタM1をそのままオフさせて、本段の出力端子outputがローレベルとなることを保証する。これだけでなく、CLKB=1となるので、第7の薄膜トランジスタM7がオンされて、第12の薄膜トランジスタM12と第14の薄膜トランジスタM14とがオンされる。この時にQb(n-1)=0となるので、第12の薄膜トランジスタM12がオンされた後にも、第1のノードQaをローレベルにすることができる。更に、第14の薄膜トランジスタM14がローレベル信号端子VGLに接続されるため、第14の薄膜トランジスタM14がオンされた後に、第3のノードQbをローレベルにすることができる。このように、ノードQaとQbは、下段のシフト・レジスタのオンと上段のシフト・レジスタのオフをトリガーすることができない。 20

#### 【 0 0 3 2 】

T4段階においては、Qa(n-1)=0、Qb(n-1)=0、CLK=1、CLKB=0、Qb(n+1)=0とする。

図10における太くされた部分に示すように、CLK=1なので、第9の薄膜トランジスタM9をオンして、第11の薄膜トランジスタM11、第13の薄膜トランジスタM13、及び第15の薄膜トランジスタM15をオンさせる。第11の薄膜トランジスタM11がローレベル信号端子VGLに接続されるので、本段の出力端子outputをローレベルに保持し、即ちOUTN=0に保持する。この時に本段のシフト・レジスタはオフ状態となる。しかも、第13の薄膜トランジスタM13をオンした後に第1のノードQaをローレベルに保持し、第15の薄膜トランジスタM15をオンした後に第3のノードQbをローレベルに保持して、更に本段の出力端子outputがローレベルを安定に出力することを保持する。 30

#### 【 0 0 3 3 】

上記の説明から分かるように、本実施例におけるシフト・レジスタはゲートラインのオンエラーをより良く低減して、画像の品質を改善することができる。

#### 【 0 0 3 4 】

これに加え、本発明は更にゲートライン駆動装置を提出する。図11に示すように、このゲートライン駆動装置は直列に接続する複数のシフト・レジスタを備える。図4と合わせて、その中のシフト・レジスタは3つの水素化アモルファスシリコン薄膜トランジスタと、1つの記憶コンデンサと、1つのフィードバックモジュールと、1つのオン/オフモジュールと、対応する入/出力端子と、を備える。前述シフト・レジスタは、そのゲートがブルアップノードとなる第1のノードQaに接続され、そのソースがクロック信号端子に接続され、そのドレーンが本段の出力端子に接続され、その作用は、そのゲートに接続される第1のノードQaがハイレベルとなり、かつそのソースがハイレベル信号を受信した時に、シフト・レジスタに動作を始めさせるように制御することである第1の薄膜トランジスタM1と、そのゲートが下段のフィードバック信号端子に接続され、そのソースが第1のノードQaに接続され、そのドレーンがローレベル信号端子に接続され、その作用は、下段のフィードバック信号がハイレベルである時に第1のノードQaをローレベルに保持して第1の薄膜 40

トランジスタM1のゲートをローレベルに維持することである第2の薄膜トランジスタM2と、そのゲートが下段のフィードバック信号端子に接続され、そのソースがプルダウンノードとなる第2のノードQに接続され（その中、前述第2のノードQが本段の出力端に接続される）、そのドレーンがローレベル信号端子に接続され、その作用は、下段のフィードバック信号がハイレベルである時に第2のノードQをローレベルに保持して本段の出力端子をローレベルに維持することである第3の薄膜トランジスタM3と、第1のノードQaと本段の出力端子との間に接続される。コンデンサC1と、上段のトリガー信号端子とクロック信号端子と第1のノードQaとの間に接続され、且つ本段のフィードバック信号端子と本段のトリガー信号端子とに接続されるフィードバックモジュール1と、クロック信号端子とフィードバックモジュール1と本段の出力端子との間に接続され、且つローレベル信号端子に接続されるオン/オフモジュール2と、を備える。フィードバックモジュール1は上段のフィードバックモジュールのトリガー信号とクロック信号を受信して第1のノードQaのレベルをプルアップし、且つ上段のシフト・レジスタにフィードバック信号を出力し、下段のフィードバックモジュールにトリガー信号を出力することに用いられる。オン/オフモジュール2は本段のシフト・レジスタが動作しない時に、本段のシフト・レジスタの出力端子をローレベルに保持することに用いられる。10

#### 【0035】

本発明が提供したゲートライン駆動装置は、その中のシフト・レジスタには、フィードバックモジュール1によって、前記シフト・レジスタの中間信号をフィードバック信号として上段のシフト・レジスタに出力し、且つトリガー信号として下段のシフト・レジスタに出力することができる。このように、この中間信号が負荷を駆動する必要がないので、遅延が小さく、且つこの中間信号が画素アレイに干渉されなく、安定性が一層高くなる。一方、前記シフト・レジスタの出力信号を上記フィードバック信号とトリガー信号としないので、出力信号とクロック信号が同期を取る必要がないので、クロック信号のデューティ比を低減し、且つ二行のゲートライン駆動の間に冗長時間が予め残される。上記両方で、連続した二行のゲートラインが同時にオンする現象をよりよく避けるので、ゲートラインのオンエラーを低減し、画像の品質を向上することができる。20

#### 【0036】

説明する必要があることは、本実施例における前記シフト・レジスタの構成と機能が上記実施例のシフト・レジスタの構造と機能と同じであるので、ここでその説明が省略される。30

以上は本発明の具体的な実施形態にすぎない。本発明が保護した範囲はこれに限定されなく、当業者は本発明に記載の技術範囲内で、その変更又は取替えを容易に想到しうる。その変更又は取替えは本発明が保護した範囲内にある。従って、本発明が保護した範囲は請求項に記載の保護範囲を基本とするのである。

#### 【符号の説明】

#### 【0037】

Qa 第1のノード

Q 第2のノード

M1 第1の薄膜トランジスタ

40

M2 第2の薄膜トランジスタ

M3 第3の薄膜トランジスタ

C1 コンデンサ

1 フィードバックモジュール

2 オン/オフモジュール

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開2008-112550(JP,A)

特開2007-95190(JP,A)

特開2011-204343(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 19 / 28

G 11 C 19 / 00