## ITALIAN PATENT OFFICE

Document No.

102010901863248A1

**Publication Date**

20120202

**Applicant**

SELEX SISTEMI INTEGRATI S.P.A.

Title

FABBRICAZIONE DI TRANSISTORI AD ALTA MOBILITA' ELETTRONICA CON ELETTRODO DI CONTROLLO A LUNGHEZZA SCALABILE

#### DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"FABBRICAZIONE DI TRANSISTORI AD ALTA MOBILITA' ELETTRONICA

CON ELETTRODO DI CONTROLLO A LUNGHEZZA SCALABILE"

di SELEX SISTEMI INTEGRATI S.P.A.

di nazionalità italiana

con sede: VIA TIBURTINA, 1231

ROMA (RM)

Inventori: PERONI Marco, ROMANINI Paolo

\* \* \*

#### SETTORE TECNICO DELL'INVENZIONE

La presente invenzione è relativa in generale a transistori ad alta mobilità elettronica ("High Electron Mobility Transistors" - HEMTs), ed in particolare alla fabbricazione di HEMT con elettrodo di controllo a lunghezza scalabile ("scalable gate lenght"), area fissa della sezione dell'elettrodo di controllo ("fixed gate section area") e ridotte correnti di perdita fra gli elettrodi di controllo e di sorgente e di pozzo e di sorgente ("low gate-source and drain-source current leakage").

#### STATO DELL'ARTE

Com'è noto, i circuiti integrati a microonde monolitici ("Monolithic Microwave Integrated Circuits" - MMIC)

- 1 -

utilizzati in applicazioni di alta potenza e/o alta frequenza sono chiamati a svolgere diverse funzionalità a radio frequenza (RF), quali la commutazione, l'amplificazione a basso rumore, e l'amplificazione di potenza, come ad esempio richiesto ai front-end dei moduli di trasmissione e ricezione operanti nelle bande di frequenza a microonde, sia a banda stretta che larga.

crescente richiesta del mercato per MMIC Le caratteristiche prestazionali sempre più spinte ha portato l'industria elettronica verso ali HEMT, caratteristiche elettriche sono tali da permettere a tale crescente richiesta di essere soddisfatta. Tuttavia, diverse funzionalità RF richieste ai MMIC comportano esigenze implementative che possono essere anche molto differenti fra loro, il soddisfacimento delle richiede l'impiego di HEMT con prestazioni altrettanto differenti.

Fra le caratteristiche che hanno maggiore incidenza sulle prestazioni di un HEMT, rivestono senza dubbio un ruolo di primaria importanza le caratteristiche elettriche del materiale semiconduttore con cui l'HEMT è realizzato. Pertanto, le diverse funzionalità RF che i circuiti integrati possono essere chiamati a svolgere, così come lo sviluppo di nuove funzionalità RF, comportano l'utilizzo di inevitabilmente strati di materiale semiconduttore con differenti caratteristiche di spessore, composizione e drogaggio, realizzate in modo tale da ottenere le caratteristiche elettriche dell'HEMT volute. Visto che il processo di fabbricazione degli HEMT è legato alle caratteristiche del materiale semiconduttore di partenza, le differenti caratteristiche sopra menzionate comportano conseguentemente l'adozione o lo sviluppo di differenti processi di fabbricazione degli HEMT.

Inoltre, alcune applicazioni possono richiedere che uno stesso MMIC implementi differenti funzionalità RF. In queste applicazioni, gli HEMT necessari per le funzionalità richieste al circuito integrato RF sono tutti realizzati su uno stesso substrato, le cui caratteristiche elettriche non possono quindi che essere il frutto di un compromesso fra le diverse richieste prestazionali degli HEMT, il quale può dare, e frequentemente dà, origine a criticità sulle prestazioni globali del MMIC.

Va inoltre rilevato che per la realizzazione di dispositivi multifunzionali su materiale semiconduttore del III-V gruppo a base Arsenico epitassiale, sovente si realizza per ciascun dispositivo nell'MMIC degli attacchi chimici o chimico/fisici a basso danneggiamento, in modo tale che i contatti elettrici degli elettrodi di tali dispositivi siano deposti sulla superficie sullo strato semiconduttore della struttura epitassiale per avere la

funzionalità desiderata ottimale. Questo approccio, però, è difficilmente utilizzato in Nitruri di un elemento del III gruppo ("Group-III Nitrides") quale quelli utilizzati per la fabbricazione dei GaNHEMT, per l'ulteriore difficoltà di realizzare attacchi a basso danneggiamento, ad esempio per la realizzazione del recesso del Gate, a causa della maggiore energia necessaria per erodere tali strati semiconduttori.

Tali criticità sono acuite quando si debbono realizzare qli HEMT presenti nei circuiti amplificatori MMIC operanti nello spettro di frequenza più alta delle microonde fino alle onde millimetriche, ed in particolare quando richiede uno spettro di funzionamento particolarmente largo (quali i circuiti integrati amplificatori multi-banda). In tal caso, si richiede un aumento delle frequenze di taglio degli HEMT, intese come la frequenza associata al guadagno unitario in corrente  $(f_T)$  e quella associata al guadagno unitario in potenza  $(f_{MAX})$ , che comporta una diminuzione della lunghezza dell'elettrodo di controllo per diminuirne la capacità parassita. Sebbene la variazione geometrica della giunzione dell'elettrodo di controllo consenta di raggiungere tale vantaggio, essa può essere associata alla variazione di altri parametri caratteristici degli HEMT, che hanno un'influenza negativa allo stesso aumento delle frequenze di taglio  $f_T$  ed  $f_{MAX}$ . Una variazione è legata alla diminuzione dell'area della sezione della metallizzazione dell'elettrodo di controllo, che comporta un aumento della resistenza parassita dell'elettrodo di controllo, che va a discapito dell'aumento della frequenza di taglio fmax. Tale problema viene parzialmente superato dalla realizzazione di una geometria a "T", "F" o "Y" della sezione della metallizzazione dell'elettrodo di controllo, che consente di realizzare una giunzione (piede dell'elettrodo controllo) con lunghezza di contatto di piccole dimensioni, unita, verso la sua parte superiore, ad un estensione della stessa metallizzazione (testa dell'elettrodo di controllo), di dimensioni maggiori e sollevata rispetto al piede. La differenza fra le dimensioni laterali della testa e del piede dell'elettrodo di controllo, così come l'altezza della testa rispetto alla base del piede, non possono però superare certi limiti senza aumentare sensibilmente la fragilità meccanica della metallizzazione stessa, negative sulla resa di fabbricazione consequenze dei HEMT stessi, limitando così di fatto la diminuzione della lunghezza della giunzione dell'elettrodo di controllo per una fissata area della sezione e capacità parassita associata all'estensione della testa. L'area sezione della metallizzazione dell'elettrodo controllo per un fissato requisito sulla sua resistenza parassita, è poi funzionale alle diverse dimensioni degli HEMT, dovendo essere maggiore quanto più è estesa la larghezza, come tipicamente realizzato per dispositivi dalle dimensioni maggiori, in particolare quando è richiesto il suo utilizzo per le applicazioni di potenza, mentre può essere minore per dispositivi più piccoli, come generalmente implementato nei dispositivi utilizzati nei circuiti amplificatori a basso rumore.

La diminuzione della lunghezza della giunzione dell'elettrodo di controllo comporta inoltre generalmente un calo della transconduttanza dell'HEMT, frequentemente descritto come "effetto di canale corto", effetto che anch'esso ha consequenze negative sull'aumento frequenze di taglio  $f_T$  ed  $f_{MAX}$ . Tale effetto è più marcato quando si polarizza l'HEMT per basse correnti ed alte tensioni di pozzo, condizioni tipicamente raggiunte nelle applicazioni ad elevata potenza. Anche questo risvolto comporta una maggiore criticità per la riduzione della lunghezza dell'elettrodo di controllo quando HEMT ottimizzati realizzare per applicazioni di amplificatori ad elevata potenza rispetto a quelli a basso rumore, dove per migliorare le prestazioni di rumore RF si tende ad ottimizzare le caratteristiche dell'HEMT affinché la polarizzazione ottima sia per tensioni polarizzazione dell'elettrodo di pozzo più basse possibili.

L'effetto di canale corto, generalmente attribuito ad

mancato confinamento degli elettroni del canale presenza di elevati campi elettrici, può essere mitigato dal drogaggio con l'incorporazione di impurezze accettrici (generalmente atomi di Ferro o Carbonio) all'interno dello strato semiconduttore buffer situato al di sotto del canale di elettroni, realizzato uniformemente su tutta l'area del wafer in fase di crescita epitassiale, poiché tale strato così drogato agisce come una barriera alla diffusione degli elettroni dal canale. La concentrazione ed il profilo di tale drogaggio vanno però ottimizzati anche per ottenere il miglior compromesso fra il controllo dell'effetto di canale e la compensazione di impurezze donatrici strato buffer, non di rado introdotte non intenzionalmente durante crescita epitassiale, l'aumento la е della resistenza del gas bidimensionale di elettroni causato dalla presenza delle impurezze accettrici, consequentemente al loro effetto sulla diminuzione sia della concentrazione di carica che della mobilità degli elettroni del canale. Dal punto di vista delle caratteristiche elettriche degli HEMT ed il guadagno nell'amplificazione RF, se da un lato l'effetto di tale drogaggio permette di aumentare sia la transconduttanza e l'impedenza d'uscita del dispositivo (a vantaggio dell'aumento di  $f_T$  ed  $f_{MAX}$ ), la distribuzione uniforme di impurezze accettrici nel buffer su tutta la superficie del wafer conduce ad un aumento di resistenza e

diminuzione della carica anche nelle porzioni del canale presenti nel canale attivo ai lati dell'elettrodo di Gate, procurando un aumento delle resistenze parassite di accesso al dispositivo intrinseco ed una diminuzione della massima corrente di pozzo che hanno la conseguenza negativa di produrre un calo del guadagno RF, un aumento della figura di rumore ed una minore potenza d'uscita a parità di tensione di polarizzazione.

Lo strato buffer drogato con impurezze accettrici ha anche l'effetto di ridurre i campi elettrici in prossimità della giunzione dell'elettrodo di controllo, contribuendo a limitare la corrente parassita del elettrodo di controllo a parità di polarizzazione, e quindi mitigare il degrado delle caratteristiche del semiconduttore e delle giunzioni elettriche dei dispositivi con esso realizzato ed ad aumentare la tensione di rottura ("break down") consentendo così di incrementare i limiti con cui si può polarizzare l'elettrodo di pozzo, a vantaggio della massima potenza RF dell'HEMT. Proprio per tale scopo, la tecnica che consiste nell' applicare un drogaggio di impurezze accettrici, viene ad esempio implementata nei dispositivi di potenza MOSFET a basso drogaggio dell'elettrodo di pozzo ("Low Doping Drain" - LDD) realizzati in silicio (Si), ma in questo caso il profilo di drogaggio è confinato solo al di sotto del canale in corrispondenza dell'elettrodo di controllo ed a lato verso l'elettrodo di pozzo, affinché sia ottimale per il miglior compromesso per ottenere basse resistenze parassite e bassi campi elettrici.

Altre soluzioni tecniche, tipo quella descritta da R. Vetury, J.B. Shealy, D. S. Green, J. McKenna, J. D. Brown, K. Leverich, P. M. Garber e M. J. Poulton nell'articolo ("conference paper") "Performance and RF Reliability of GaN-on-SiC HEMTs using Dual-Gate Architectures", presentato riunione del simposio internazionale alla microelettronica del 2006 ("submitted to the Proceedings of 2006 International Microelectronics Symposium") e pubblicato ("appearing") in Microwave Symposium Digest, 2006, IEEE MTT-S International, 11-16 Giugno 2006, pagine 714-717, sono generalmente utilizzate per proteggere l'HEMT da elevati campi elettrici, ma possono andare a discapito alcune prestazioni, e pertanto vanno ottimizzate a della prescelta. seconda funzionalità Ciò viene frequentemente realizzato, in particolare nella fabbricazione dei GaN HEMT, con l'introduzione di ulteriori metallizzazioni sopra il canale dell'HEMT, tra l'elettrodo di controllo e quello di pozzo, generalmente chiamate Field Plate, sia singole che multiple, connesse ad un potenziale elettrico di massa, che realizzano una giunzione Schottky o Metallo Isolante Semiconduttore (MIS) con gli elettroni del canale tra l'elettrodo di controllo e l'elettrodo di pozzo,

il cui effetto è di ridurre la massima intensità del picco elettrico all'interno del materiale campo semiconduttore, per fissata polarizzazione una dispositivo. Alla presenza di tali metallizzazioni, sono però associate delle capacità parassite che hanno l'effetto di ridurre il quadagno ad alta frequenza e/o la loro ampiezza di banda. Inoltre, l'uso di una doppia giunzione Schottky, connessa direttamente ad un potenziale elettrico di massa, se da una parte permette di ridurre drasticamente il campo elettrico, ha anche l'effetto negativo di limitare la corrente di elettrodo di pozzo quando la tensione dell'elettrodo di controllo assume valori positivi, riducendo così la dinamica dell'ampiezza del segnale d'uscita e quindi la linearità e la massima potenza del segnale RF amplificato. C'è da considerare inoltre che, riducendo il campo elettrico nel canale, a parità della tensione di pozzo, aumenta corrispondentemente anche la tensione di ginocchio  $V_{DS}^{K}$ , ovvero la tensione per cui le caratteristiche della corrente di pozzo  $I_{\text{D}}$  in funzione della tensione fra elettrodo di pozzo ed elettrodo di Sorgente ("Drain-Source voltage") arrivano ad un valore di saturazione. Tale aumento della tensione di ginocchio  $V_{DS}^{K}$ , rende necessario l'uso di tensioni più alte, e quindi dissipazioni maggiori che generalmente non vanno beneficio delle prestazioni di basso rumore ad alta

frequenza. Pertanto tali soluzioni "Field Plate", specie quando introdotte negli HEMT ad alta frequenza, mentre sono preferibili per applicazioni di alta potenza, potrebbero essere controproducenti per l'amplificazione a basso rumore.

#### OGGETTO E RIASSUNTO DELL'INVENZIONE

Scopo della presente invenzione è pertanto quello di mettere a disposizione una tecnologia di fabbricazione di HEMT che consenta di superare gli inconvenienti delle tecnologie di fabbricazione note sopra descritti, in particolare che consenta l'ottimizzazione delle prestazioni degli HEMT per diverse funzionalità RF senza che sia necessario dover modificare le caratteristiche, in termini di composizione e/o drogaggio, del materiale semiconduttore con cui gli HEMT sono fabbricati e, conseguentemente, i processi di fabbricazione degli stessi.

Tale scopo è raggiunto dalla presente invenzione, la quale è relativa ad un processo di fabbricazione di un HEMT ed a un HEMT così ottenuto, come definiti nelle rivendicazioni allegate.

In particolare, l'ottimizzazione delle prestazioni degli HEMT per diverse funzionalità RF viene raggiunta agendo, anziché sulle caratteristiche elettriche del materiale semiconduttore con cui l'HEMT è realizzato, su

quelle dell'elettrodo di controllo. Ciò permette variare, a partire da un medesimo substrato semi-isolante, caratteristiche elettriche di ogni singolo realizzato su tale substrato semi-isolante, se è il caso anche localmente, rispetto a quelle disponibili in singola tipologia di transistori che assolve alle diverse funzionalità RF. Ciò consente anche la realizzazione di un circuito integrato RF ottimizzato per molteplici funzionalità RF, con vantaggi economici, soprattutto in fase di assemblaggio, rispetto all'attuale realizzazione di in cui siano presenti molteplici MMIC ottimizzato per una rispettiva funzionalità RF, mitigando così le criticità sulle prestazioni globali del derivanti dal compromesso sulla scelta di caratteristiche elettriche dell'HEMT comuni a tutte le funzionalità.

In dettaglio, le caratteristiche elettriche dell'elettrodo di controllo vengono ottimizzate effettuando una doppia metallizzazione, fra le quali viene realizzato un trattamento termico di stabilizzazione e ricottura ("annealing") per rimuovere il danneggiamento introdotto dai precedenti passi del processo di fabbricazione, quali gli attacchi chimici, di deposizione od altri eventuali.

Durante la prima metallizzazione, viene depositata solo la parte inferiore dell'elettrodo di controllo in maniera tale da realizzare sia una giunzione Schottky con lo strato

semiconduttore sottostante delle dimensioni minime di poche decine di nm, e che, assieme allo strato di passivazione circostante, realizza un incapsulamento della superficie il successivo trattamento termico. Durante durante la metallizzazione, viene seconda invece depositata la restante parte superiore dell'elettrodo di controllo, indipendentemente maniera tale da realizzare, dalla geometria del parte inferiore dello stesso, un compromesso fra capacità e resistenza parassita, mitigando le criticità di maggiore fragilità meccanica associata alla minore lunghezza di contatto della base del Gate, non essendo più equivalente alla lunghezza della giunzione Schottky che, invece, è equivalente a quella della apertura del piede realizzata durante la prima metallizzazione. Oltre a ciò, si consente così di utilizzare, in questa seconda fase, metalli che non sono necessariamente compatibili con cicli termici ad alta temperatura utilizzati nella fase di formazione della inferiore dell'elettrodo di parte controllo. Inoltre, è poi possibile realizzare, individualmente o in combinazione, un'impiantazione impurezze accettrici allineata all'elettrodo di controllo per migliorare l'effetto canale corto, un secondo elettrodo con giunzione Schottky per realizzare un field plate Schottky che consenta di aumentare il quadaqno dell'HEMT, specialmente quando vengono raggiunte elevate tensioni di Drain, e un HEMT con giunzione Metallo Isolante Semiconduttore (MIS) integrato con l'HEMT con giunzione Schottky.

### BREVE DESCRIZIONE DEI DISEGNI

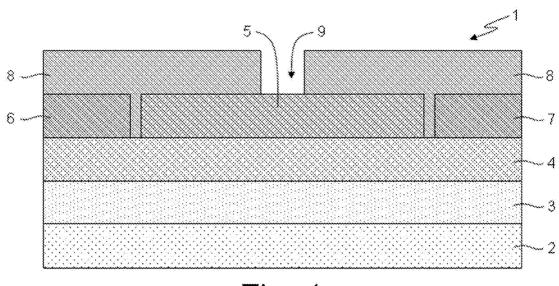

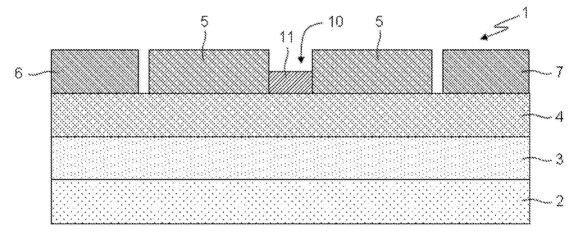

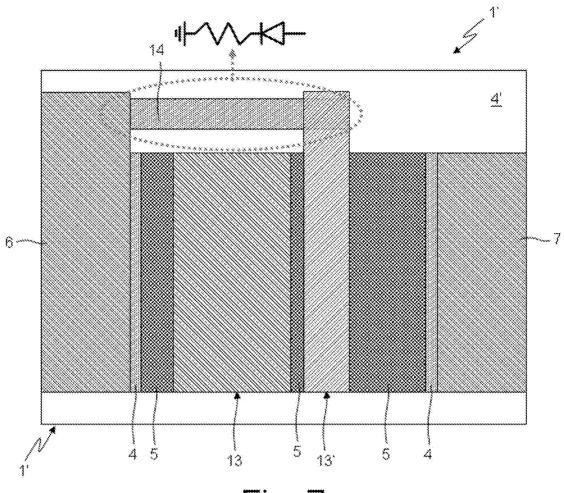

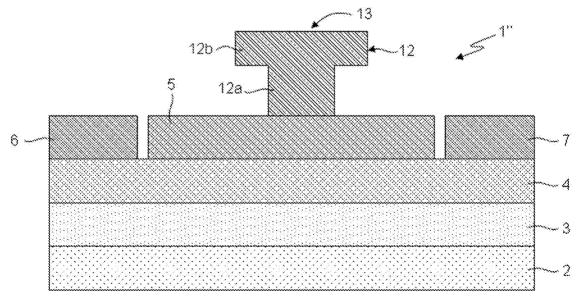

- le Figure 1-3 sono viste schematiche in sezione di un HEMT secondo una preferita forma di realizzazione dell'invenzione:

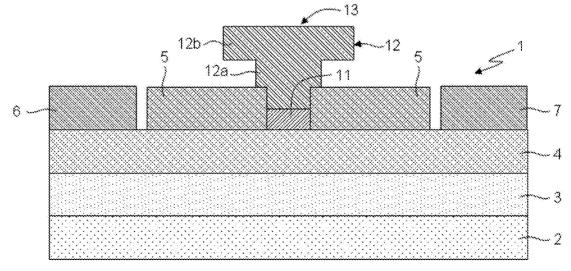

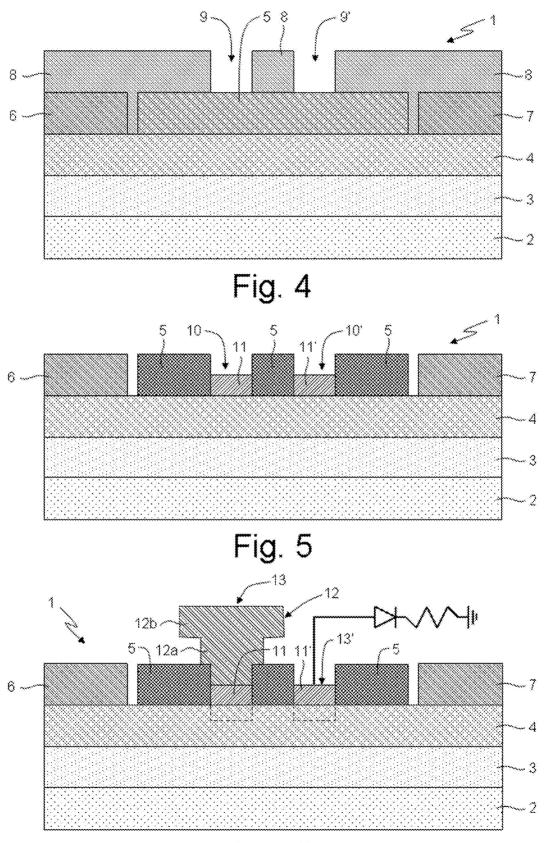

- le Figure 4-6 sono viste schematiche in sezione di un HEMT secondo una differente forma di realizzazione dell'invenzione;

- la Figura 7 è una vista in pianta dell'HEMT di Figura 6; e

- la Figura 8 è una vista schematica in sezione di un HEMT con elettrodo di controllo Metallo-Isolante-Semiconduttore.

# DESCRIZIONE DETTAGLIATA DI PREFERITE FORME DI REALIZZAZIONE DELL'INVENZIONE

La presente invenzione verrà ora descritta in dettaglio con riferimento alle figure allegate per permettere ad una persona esperta di realizzarla ed utilizzarla. Varie modifiche alle forme di realizzazione descritte saranno immediatamente evidenti alle persone esperte ed i generici principi descritti possono essere applicati ad altre forme

di realizzazione ed applicazioni senza per questo uscire dall'ambito protettivo della presente invenzione, come definito nelle rivendicazioni allegate. Pertanto, la presente invenzione non deve essere considerata limitata alle forme di realizzazione descritte ed illustrate, ma gli si deve accordare il più ampio ambito protettivo conforme i principi e le caratteristiche qui descritte e rivendicate.

Le Figure 1-3 illustrano schematicamente in sezione un HEMT secondo una preferita forma di realizzazione della presente invenzione e durante differenti fasi del suo processo di fabbricazione.

In particolare, nella Figura 3 è indicato nel suo insieme con 1 un HEMT comprendente:

- un substrato epitassiale comprendente:

- un substrato semi-isolante 2, generalmente di materiale semiconduttore, ad esempio di Silicio (Si), Carburo di Silicio (SiC), Nitruro di Gallio (GaN) o Zaffiro (Al<sub>2</sub>O<sub>3</sub>);

- uno strato buffer 3, preferibilmente comprendente

Nitruro di un elemento del III gruppo quale

Nitruro di Gallio o Gallio Alluminio e/o Indio

(GaN/AlGaN/InGaN/AlInGaN), convenientemente

Nitruro di Gallio (GaN), formato sul substrato

semi-isolante 2, eventualmente tramite

l'interposizione di altri strati; ed

- uno strato barriera 4, preferibilmente comprendente anch'esso un Nitruro di un elemento del III gruppo, in particolare Nitruro di Gallio, Indio e Alluminio (InAlGaN), formato sullo strato buffer 3, eventualmente a sua volta formato da strati con variazione nella composizione e drogaggio; e

- uno strato di protezione meccanica e/o di passivazione 5, preferibilmente di materiale dielettrico quale Nitruro di Silicio Biossido di Silicio (SiO<sub>2</sub>), formato sullo strato barriera 4 ed in cui sono lasciate esposte porzioni dello strato barriera 4 definenti una prima ed una seconda regione di contatto ohmico;

- un elettrodo di sorgente 6 ed un elettrodo di pozzo 7 formati rispettivamente su, ed in contatto ohmico con, le porzioni esposte dello strato barriera 4, nelle prima e, rispettivamente, nella seconda regione di contatto ohmico; ed

- un elettrodo di controllo ("control gate") 13 formato su, ed in contatto Schottky con, lo strato barriera 4, fra gli elettrodi di sorgente 6 e di pozzo 7, dai quali è lateralmente separato.

Sullo strato di protezione meccanica e/o di passivazione 5 e sui contatti ohmici 6 e 7 possono poi essere depositati uno o più ulteriori strati di

passivazione.

di sorgente 6 e di pozzo 7 elettrodi convenientemente realizzati formando, al di sopra dello strato di protezione meccanica e/o di passivazione 5, una maschera formata convenientemente da uno strato di resist fotolitografico che viene modellato ("patterned") maniera tale da formare una prima ed una seconda finestra in corrispondenza della prima e della seconda regione di contatto ohmico. Lo strato di protezione meccanica e/o di passivazione 5 viene quindi attaccato chimicamente ("etching") in corrispondenza della prima e della seconda finestra fino all'interfaccia con lo strato barriera 4 e viene quindi effettuata una deposizione metallica in corrispondenza delle porzioni esposte dello strato barriera 4, la quale porta alla formazione degli elettrodi sorgente 6 e di pozzo 7. Si sottopone quindi l'HEMT 1 ad un ciclo termico di lega degli elettrodi di sorgente 6 e di pozzo 7 con lo strato barriera 4 sottostante, in modo da formare un contatto non rettificante (ohmico) tra metallo ed elettroni presenti nel canale.

In una forma di realizzazione alternativa, gli elettrodi di sorgente 6 e di pozzo 7 possono essere formati sullo strato barriera 4 prima dello strato di protezione meccanica e/o di passivazione 5, e quest'ultimo essere poi successivamente depositato fra gli elettrodi di sorgente 6

e di pozzo 7.

Gli elettrodi di sorgente 6 e di pozzo 7 possono essere convenientemente formati in maniera tale da risultare più piccoli delle rispettive finestre nello strato Ьi protezione meccanica e/o di passivazione 5, così da risultare distanziati da quest'ultimo. Preferibilmente, questa differenza tra le dimensioni delle finestre nello strato di protezione meccanica e/o di passivazione 5 e quelle degli elettrodi di sorgente 6 e di pozzo 7, viene ottenuta utilizzando un attacco chimico isotropico, parzialmente tale, per la rimozione dello strato di protezione meccanica e/o passivazione 5, dopo applicato la maschera per la definizione degli elettrodi di sorgente 6 e di pozzo 7, e prima della deposizione del metallo. Preferibilmente, quando lo strato di protezione meccanica e/o passivazione 5 è realizzato mediante strati di Nitruro di Silicio (SiN) e/o Biossido di Silicio (SiO<sub>2</sub>), l'attacco chimico isotropico può essere ottenuto mediante immersione in una soluzione liquida basata sulla miscela di  $NH_4F$ , HF ed  $H_2O$ .

Per definire le aree di semiconduttore elettricamente conduttive della superficie dell'MMIC dove vengono realizzati i dispositivi attivi, rispetto alle aree di semiconduttore elettricamente non conduttive, dove vengono generalmente realizzati i componenti passivi, si rende lo

strato barriera 4 elettricamente isolato all'esterno dell'area attiva dell'HEMT 1. Ciò si può realizzare avendo protetto prima la superficie che si desidera lasciare elettricamente conduttiva con una maschera formata convenientemente da uno strato di resist fotolitografico modellato, e successivamente rendendo opportunamente elettricamente non conduttiva l'area non coperta da tale maschera tramite un processo di bombardamento della superficie, ad esempio mediante impiantazione di Fluoro ad energia compresa fra 50KeV e 300KeV e dose compresa fra  $5 \times 10^{13}$  cm<sup>-2</sup> e  $2 \times 10^{14}$  cm<sup>-2</sup>, od in alternativa rimuovendo le parti conduttive del materiale semiconduttore presenti all'esterno della maschera, operando un attacco chimico-fisico del materiale non protetto da essa fino ad eliminare completamente lo strato barriera 4 all'esterno ed esporre lo stato buffer 3 sottostante. Per entrambe le procedure, il processo di isolamento viene realizzato definizione dell'elettrodo precedentemente alla di controllo 13, come descritto di seguito.

L'elettrodo di controllo 13 è utilizzato per modulare il segnale di ingresso ed è realizzato nel modo qui di seguito descritto con riferimento alle Figure 1 e 2. Come illustrato, sullo strato di protezione meccanica e/o di passivazione 5 e sul primo e secondo contatto ohmico 6, 7 (e su eventuali ulteriori strati di passivazione su di

questi deposti) viene formato uno strato di mascheratura 8 provvisto di un'apertura 9 passante che espone una porzione dello strato di protezione meccanica e/o di passivazione 5 fra i contatti ohmici 6 e 7. Preferibilmente, lo strato di mascheratura 8 è uno strato di resist fotolitografico, il quale viene fotolitograficamente modellato ("patterned") per formare l'apertura 9, la quale può convenientemente avere dimensioni minime dell'ordine di alcune decine di nm.

Una finestra 10 passante viene quindi formata nello strato di protezione meccanica e/o di passivazione 5, in corrispondenza dell'apertura 9 nello strato di mascheratura 8, in maniera tale da esporre una superficie dello strato barriera 4 definente una regione di contatto Schottky nella quale verrà successivamente realizzato l'elettrodo di controllo 13. In particolare, la finestra 10 viene realizzata mediante un attacco chimico selettivo a basso danneggiamento ("low damage") che erode lo strato di protezione meccanica e/o di passivazione 5 fino all'interfaccia con lo strato barriera 4.

Una porzione inferiore 11 dell'elettrodo di controllo 13, nel seguito indicata con il termine "piede" ("gate foot"), viene quindi formata sulla porzione esposta dello strato barriera 4, nella finestra 10, ad esempio per deposizione di Nichel (Ni) o Platino (Pt) oppure di un metallo refrattario quale molibdeno (Mo) o tungsteno (W),

ovvero una deposizione di molteplici strati composti da metalli con tali caratteristiche. In particolare, il piede 11 viene formato in maniera tale da estendersi attraverso lo strato di protezione meccanica e/o di passivazione 5 per un'altezza non superiore, convenientemente inferiore, a spessore complessivo dello quella dello strato di protezione meccanica e/o di passivazione 5 e di eventuali ulteriori strati di passivazione, così da non fuoriuscire finestra 10. Ciò consente di facilitare dalla separazione fisica fra il metallo deposto sullo strato barriera 4 e quello deposto sopra lo strato di mascheratura 8, e quindi la successiva rimozione di quest'ultimo metallo, utilizzando l'esposizione in solventi (come ad esempio acetone o N-Methyl-2-pyrrolidone/NMP) dello strato di mascheratura nel caso esso sia composto da resist fotolitografico, come nella forma di realizzazione precedentemente descritta.

L'HEMT 1 viene quindi sottoposto ad un trattamento termico di stabilizzazione e ricottura al fine di rimuovere il danneggiamento al reticolo cristallino della superficie del semiconduttore introdotto dai passi di processo precedenti, quali l'attacco chimico, la deposizione ed altri eventuali, e stabilizzare l'interfaccia metallosemiconduttore della giunzione Schottky. Per una rimozione efficace del danneggiamento in un Nitruro di un elemento

del III gruppo, le temperature raggiunte durante tale trattamento termico superano 450°C, e quindi possono essere superiori a quelle di diffusione dell'Oro (Au) p e/o dell'Alluminio (Al) nei metalli precedentemente citati, e che formano la barriera Schottky durante la definizione del piede 11.

Con riferimento nuovamente alla Figura 3, una porzione superiore 12 dell'elettrodo di controllo 13, nel seguito indicata con il termine "testa" ("gate head"), viene quindi formata sul piede 11, ad esempio per deposizione di un metallo a bassa resistività quale oro (Au) o alluminio (Al) con elevato spessore, eventualmente tramite l'interposizione di altri strati metallici di barriera quali nichel (Ni) o titanio (Ti) al fine di limitare la possibilità di una reazione chimica con il piede 11.

In particolare, la testa 12 viene formata in maniera tale da fuoriuscire dalla finestra 10 e da presentare, preferibilmente, una prima porzione 12a che si estende lateralmente sulla superficie dello strato di protezione meccanica e/o di passivazione 5, all'esterno della finestra 10, in maniera tale da appoggiarsi su e risultare meccanicamente supportata da quest'ultimo, migliorando così l'aderenza meccanica dell'elettrodo di controllo 13 alle porzioni con cui risulta a contatto, ma senza aumentare significativamente la capacità parassita globale dell'elettrodo di controllo 13. In altri termini, la testa 12 è modellata in maniera tale da definire in sezione, congiuntamente al piede 11, un profilo a gradino ("stairstep profile") in corrispondenza della prima porzione 12a.

La testa 12 viene inoltre formata in maniera tale da una seconda porzione 12b verticalmente presentare distanziata dalla ed estendentisi lateralmente da uno o da entrambi i lati della prima porzione 12a, cosi da fornire alla testa 12 una sezione a profilo ottimizzato, ad esempio la cui geometria assuma un aspetto assimilabile a quella delle lettere "T", "Y" o "F", per minimizzare la resistenza capacità parassite dell'elettrodo di controllo di utilizzare metalli consentendo che non sono necessariamente compatibili con cicli termici ad alta temperatura utilizzati nella prima fase di formazione del piede 11.

Nella sua forma di realizzazione preferita, per ottenere la geometria a "T" "Y" o "T" della testa 12, ci si avvale di un processo che utilizza la litografia a fascio elettronico il quale, impressionando strati multipli di resist, deposti con diversi spessori e sensibilità sulla superficie del wafer, le aree dove deve essere realizzata la maschera formata da tali resist, consentano di ottenere delle aperture, dopo la successiva fase di sviluppo, il cui profilo sia ottimizzato per fornire alla metallizzazione

della testa la geometria voluta, oltre che facilitare la separazione fisica fra il metallo deposto in coincidenza di quello del piede e quello deposto sopra la maschera del multistrato di resist.

La formazione in due fasi dell'elettrodo di controllo 13, con trattamento termico dopo la formazione del piede 11, consente di superare i limiti fisici imposti alla di rinvenimento in presenza delle temperatura metallizzazioni a bassa resistività (Au o Al) della testa 12: queste ultime, infatti, se sottoposte a temperature prossime a quelle di fusione (660°C per l'Al e 1064°C per l'Au), o di lega con la metallizzazione del piede 11, possono deformarsi non mantenendo la geometria originaria ottenuta dopo la deposizione, possono ridurre la complessiva della metallizzazione resistività dell'elettrodo di controllo 13, essendo le leghe di tali metalli più resistive, ed anche possono diffondere nello barriera 4, peggiorando le caratteristiche strato rettificanti del contatto Schottky. Tali limitazioni possono essere invece superate utilizzando il trattamento termico di annealing dopo la deposizione della metallizzazione del piede 11 in assenza di quella della testa 12, consentendo così di utilizzare metalli che non sono necessariamente compatibili con cicli termici ad alta temperatura utilizzati nella fase di formazione del piede Un altro vantaggio della formazione in due fasi dell'elettrodo di controllo 13 consiste nella possibilità di utilizzare, nelle fasi litografiche, uno strato di resist fotolitografico più sottile per la deposizione del piede 11, che rende meno critica la realizzazione di giunzioni di qualche decina di nanometri, di quello per la deposizione della testa 12, dove le esigenze di deposizione di elevati spessori metallici (centinaia di nm) per abbattere la resistenza parassita dell'elettrodo di controllo 13 rendono necessario l'utilizzo di uno spessore di resist più elevato.

Inoltre, il processo costruttivo in due fasi dell'elettrodo di controllo 13 consente di variare le proprietà di quest'ultimo affinché caratteristiche le elettriche degli HEMT nel MMIC abbiano caratteristiche ottimizzate per ogni funzionalità RF, ad esempio adattando differenti dimensioni del piede 11 a seconda applicazione richiesta, a partire dallo stesso materiale semiconduttore, rispetto a quelle disponibili singola tipologia di transistore che assolve alle diverse funzionalità RF. Ciò porta ad una tecnologia modulare adatta a diverse applicazioni, senza che sia necessario cambiare le caratteristiche del materiale semiconduttore con cui l'HEMT 1 è realizzato, evitando così di modificare conseguentemente i processi di fabbricazione richiesti per lo sviluppo di nuove funzioni. Diventa inoltre accessibile anche realizzare in un unico MMIC transistori ottimizzati per molteplici funzioni RF, con vantaggi economici, soprattutto in fase di assemblaggio, rispetto alla attuale realizzazione di moduli in cui siano presenti molteplici MMIC, ognuno ottimizzato per ogni funzionalità RF. Inoltre, un MMIC multifunzionale basato sul processo costruttivo oggetto dell'invenzione consente di ottimizzare le caratteristiche di ciascun HEMT utilizzato nel MMIC, migliorando le sue prestazioni globali rispetto ad un MMIC in cui le caratteristiche elettriche degli HEMT fossero comuni a tutte le funzionalità RF.

Le Figure 4-6 illustrano schematicamente in sezione un HEMT secondo una differente forma di realizzazione dell'invenzione, il quale è realizzabile sullo stesso substrato semiconduttore contemporaneamente alla forma di realizzazione precedentemente descritta, е integrabile nello stesso circuito integrato monolitico MMIC. In particolare, l'HEMT illustrato nelle Figure 4 e 5, indicato nel suo complesso con 1', differisce dall'HEMT 1 illustrato nelle Figure 1-3 per il fatto di essere provvisto di un elettrodo di field plate, indicato con 13', formato su, ed in contatto Schottky con, lo strato barriera 4, fra gli elettrodi di controllo 13 e di pozzo 7, dai quali è lateralmente separato.

In particolare, l'elettrodo di controllo 13, che è utilizzato per modulare il segnale di ingresso, realizzato prossimo all'elettrodo di sorgente 6, mentre l'elettrodo di field plate 13', che svolge appunto la funzione di "field plate" Schottky per mitigare il campo 1', aumentandone all'interno dell'HEMT elettrico l'affidabilità e la robustezza, e ridurre gli effetti di canale corto a vantaggio del quadagno RF dell'HEMT 1', è realizzato prossimo all'elettrodo di pozzo 7. In questa di realizzazione, il trattamento termico stabilizzazione e ricottura finalizzato a rimuovere danneggiamento introdotto dai passi di processo precedenti coinvolge entrambi i piedi 11 e 11'.

Per realizzare l'elettrodo di field plate 13', un'ulteriore finestra passante, indicata con 10', è realizzata nello strato di protezione meccanica e/o di passivazione 5, contestualmente alla finestra passante 10. La seconda finestra 10' può avere anch'essa dimensioni dell'ordine di poche decine di nm ed è interposta fra la finestra 10 e l'elettrodo di pozzo 7, dai quali è lateralmente separata, ed espone un'ulteriore superficie dello strato barriera 4 definente una regione di contatto Schottky nella quale, contemporaneamente alla formazione del piede 11 dell'elettrodo di controllo 13, viene

realizzato il solo piede, indicato con 11', dell'elettrodo di field plate 13', che svolge la funzione di "field plate" Schottky per mitigare il campo elettrico all'interno dell'HEMT 1', aumentandone l'affidabilità e la robustezza, e ridurre gli effetti di canale corto a vantaggio del quadagno RF dell'HEMT 1'.

Opzionalmente, prima della deposizione della metallizzazione dei piedi 11 e 11' dell'elettrodo di controllo 13 e dell'elettrodo di field plate 13' potrebbe essere realizzato un attacco chimico dello strato barriera 4 in corrispondenza delle finestre 10 e 10' in maniera tale da realizzare recessi nello strato barriera 4, illustrati in Figura 6 con linea tratteggiata, facendo così sì che le metallizzazioni dei piedi 11 e 11' dell'elettrodo di controllo 13 e dell'elettrodo di field plate 13' penetrino parzialmente nello strato barriera 4. In una variante non illustrata, utilizzando mascherature differenti, potrebbe essere realizzato anche uno solo dei due convenientemente solo quello in corrispondenza del piede 11 dell'elettrodo di controllo 13, configurazione, quest'ultima, che permette di limitare l'effetto di strozzamento causato dalla presenza dell'elettrodo di field plate 13'.

L'elettrodo di field plate 13' è connesso ad un potenziale elettrico di massa, o più in generale ad un

potenziale elettrico di riferimento che potrebbe essere differente dal potenziale elettrico di massa. attraverso un collegamento esterno alla regione di canale dell'HEMT 1'. Il motivo di tale soluzione consiste nel fatto che l'elettrodo di field plate 13' ha la funzione di il campo elettrico nel canale grazie diminuire alla modulazione degli elettroni del canale fornito dalla giunzione Schottky, altrimenti indicato come effetto "Field Plate", e di migliorare così l'affidabilità dell'HEMT 1'. Siccome l'elettrodo di field plate 13' non deve trasportare un segnale RF ma applicare un campo elettrico statico, non è necessario ridurre la sua resistenza sovrapponendoci una metallizzazione di testa come nell'elettrodo di controllo 13, e così la realizzazione di una giunzione Schottky con effetto Field Plate realizzata con la sola metallizzazione del piede 11' facilita la sua collocazione in prossimità dell'elettrodo di controllo 13, in modo tale da modulare la caduta di tensione nel canale dell'HEMT 1' tra l'elettrodo di controllo 13 e l'elettrodo di pozzo 7, permettendo così di controllare il campo elettrico in tale zona diminuendone il suo valore di picco, e mitigando conseguentemente gli associati rischi per l'affidabilità dell'HEMT 1', quale la piezoelettricità inversa o la generazione di carica per ionizzazione da impatto.

L'elettrodo di field plate 13' ha anche l'ulteriore

- 29 -

Mirko BERGADANO (Iscrizione Albo nr. 843/BM)

funzione protettiva di limitare sia la corrente che fluisce attraverso l'elettrodo di controllo 13, schermando raccogliendo la carica in eccesso generata dai fenomeni di ionizzazione da impatto, sia limitando la massima corrente di pozzo nel caso l'elettrodo di controllo 13 superi la tensione di accensione del diodo Schottky. Infatti l'elettrodo di field plate 13', essendo connesso ad una tensione fissata, limita la corrente del canale in quanto tale giunzione polarizzata ha l'effetto di svuotare gli elettroni presenti sotto tale giunzione, limitando così la corrente che fluisce nel canale a seconda del potenziale elettrico. Per evitare però che tale potenziale elettrico abbia un effetto di limitazione eccessiva sulla massima corrente di pozzo, comprimendo perciò la dinamica dell'ampiezza del segnale RF in ai capi dell'elettrodo di pozzo, la connessione elettrica dell'elettrodo di field plate 13' si può realizzare attraverso un'appropriata circuitazione elettrica comprendente un contatto rettificante ed eventualmente una resistenza elettrica aggiuntiva in serie al contatto rettificante, in modo tale che. nelle condizioni di polarizzazione elettriche operative dell'HEMT 1', l'elettrodo di field plate 13' si auto-polarizzi portando il potenziale elettrico della giunzione Schottky a valori positivi prossimi alla tensione di accensione della giunzione. Ciò è realizzabile,

esempio, contattando il secondo elettrodo di field plate 13' con l'anodo di un diodo, il quale a sua volta ha il catodo collegato a massa attraverso un elemento resistivo, così come raffigurato schematicamente in Figura 6.

Grazie ad una siffatta connessione, l'elettrodo field plate 13' si autopolarizza alla tensione di ginocchio di un diodo (tipicamente +1 V, se si realizza il diodo con un contatto Schottky con gli elettroni nel GaN), evitando in tal modo che il canale dell'HEMT 1' possa rimanere strozzato dall'elettrodo di field plate 13' quando RF applicato all'elettrodo di controllo 13 segnale raggiunge valori di tensione positivi. Inoltre, la presenza di una rete resistiva tra l'elettrodo di field plate 13' e la massa consente di limitare le perdite del segnale RF in uscita, poiché la capacità parassita del secondo elettrodo di field plate così non è connessa direttamente a massa attraverso un corto-circuito, ma attraverso un filtro RC serie.

La connessione ad un potenziale elettrico di massa dell'elettrodo di field plate 13' con le caratteristiche sopra descritte può essere convenientemente realizzata in modo tale da essere integrata nello stesso MMIC, come illustrato schematicamente nella Figura 7. In particolare, durante la fase di isolamento elettrico dell'area, indicata in Figura 7 con 4', dello strato barriera 4 all'esterno

dell'area attiva dell'HEMT 1, formando in quest'area, attraverso una opportuna modellizzazione della maschera di protezione, una linea resistiva 14 di materiale semiconduttore, avente una prima estremità elettricamente connessa all'elettrodo di field plate 13', formando così con quest'ultimo una giunzione Schottky, ed una seconda estremità elettricamente connessa a massa mediante un contatto ohmico.

Nell'esempio illustrato nella Figura 7, il collegamento della striscia resistiva 14 ad un potenziale elettrico di massa viene preferibilmente realizzato sovrapponendo la seconda estremità della linea resistiva 14 all'elettrodo di sorgente 6, che generalmente è collegato a massa. La sovrapposizione di un'estremità della linea resistiva 14 con l'elettrodo di field plate 13' realizza il contatto rettificante con le caratteristiche volute sopra descritte, la cui capacità è controllabile in base all'area della sovrapposizione fra la linea resistiva 14 e l'elettrodo di field plate 13'. Inoltre, tale sovrapposizione permette di realizzare, in combinazione con la geometria della linea resistiva 14, che regola la resistenza R, sua combinazione dei valori di resistenza e capacità (RC) serie per ottenere l'isolamento RF voluto dell'elettrodo di field plate 13'.

Gli stessi vantaggi che la forma di realizzazione

- 32 -

Mirko BERGADANO (Iscrizione Albo nr. 843/BM)

precedentemente descritta ed illustrata nella Figura 7 potrebbero essere ottenuti omettendo il contatto rettificante e collegando l'elettrodo di field plate 13' ad un potenziale elettrico di riferimento positivo, di valore tale da non causare lo strozzamento del canale, attraverso una resistenza elettrica.

L'approccio costruttivo in due fasi sopra descritto consente quindi di realizzare sia HEMT a singolo elettrodo di controllo, che sono più appropriati alla funzione di amplificazione a basso rumore, che HEMT all'elettrodo di controllo è abbinato un elettrodo di field plate, che hanno vantaggi nella funzione di amplificazione potenza, con un unico processo costruttivo, con di potenzialità di realizzare sullo stesso circuito monolitico dispositivi integrati a semiconduttore con caratteristiche ottimizzate per funzioni diverse, specialmente per quelle destinate ad applicazioni ad alta frequenza.

Un altro potenziale vantaggio dell'approccio costruttivo in due fasi dell'elettrodo di controllo 13 consiste nella possibilità di depositare la metallizzazione della testa 12 anche senza aver realizzato precedentemente la metallizzazione del piede 11. In tal modo, è possibile realizzare dispositivi elettronici integrati comprendenti, oltre a HEMT a singolo elettrodo di controllo e/o a HEMT con elettrodo di controllo ed elettrodo di field plate,

anche HEMT con giunzione di controllo ("gate junction") del tipo Metallo-Isolante-Semiconduttore (MIS), come mostrato a titolo di esempio nella Figura 8 ed indicato con 1", i quali offrono vantaggi nelle applicazioni di commutazione ("switching") grazie alla loro minore perdita d'inserzione ("insertion loss") e maggiore robustezza a largo segnale nello stato chiuso ("on"), oltre che maggiore isolamento e robustezza alle alte tensioni quando operanti nello stato aperto ("off"). In una forma di realizzazione preferita, la realizzazione di HEMT con giunzione di controllo di tipo MIS per applicazioni di commutazione con ulteriori vantaggi prestazioni RF, si ottiene realizzando una o più giunzioni MIS, che si appoggiano sopra lo strato protezione meccanica e/o passivazione 5 tra gli elettrodi di sorgente 6 e di pozzo 7, e dove ciascuna metallizzazione della giunzione MIS è connessa all'elettrodo di controllo 13 attraverso degli elementi resistivi che, come è noto, hanno la funzione di diminuire le perdite del segnale RF l'esterno del dispositivo. Nella verso sua forma preferenziale, la realizzazione di tali elementi resistivi convenientemente venire realizzati in forma integrata all'interno dell'MMIC definendo delle aree di semiconduttore elettricamente conduttive esterne al canale dell'HEMT, durante la fase di isolamento elettrico, così descritto in precedenza realizzazione come per la

dell'elemento resistivo per la connessione a massa dell'elettrodo di field plate 13'.

La scelta delle dimensioni della giunzione di controllo può essere fatta in base alla funzione di ciascun dispositivo del MMIC, al fine di trovare per ciascuno di essi il compromesso ottimale fra guadagno RF, controllo della modulazione, robustezza, ecc.

Risulta infine chiaro che al processo di fabbricazione descritto ed illustrato possono essere apportate modifiche e varianti senza per questo uscire dall'ambito protettivo della presente invenzione, come definito nelle rivendicazioni allegate.

In particolare, sia nell'HEMT 1 che nell'HEMT 1' possibile impiantare ioni di impurezze accettrici in modo allineato all'elettrodo di controllo 13, ad esempio Carbonio(C) o Ferro (Fe), al di sotto del o sovrapposte regione di canale che si forma al di dell'elettrodo di controllo 13, fra lo strato buffer 3 e lo strato barriera 4, in prossimità della giunzione controllo, per migliorare l'effetto canale corto. Lo scopo di tale impiantazione ionica è quello di favorire l'aumento del guadagno dell'HEMT 1 е 1' in condizioni polarizzazione con bassa corrente di controllo e/o alta tensione di pozzo, da applicare sopratutto nel caso in cui la lunghezza dell'elettrodo di controllo sia troppo piccola per controllare i fenomeni di canale corto. l'impiantazione selettiva sotto il canale in corrispondenza dell'elettrodo di controllo 13, consente di confinare gli elettroni del canale poiché il drogaggio con impurezze barriera alla diffusione impiantate agisce come deali elettroni del canale. Ouesta impiantazione ha anche l'effetto di ridurre i campi elettrici in prossimità della giunzione, contribuendo a limitare la corrente parassita di controllo a parità di polarizzazione. Rispetto ad altre soluzioni in cui tale drogaggio è realizzato uniformemente sulla superficie del wafer in fase di crescita epitassiale, l'impiantazione fornisce lo stesso effetto senza diminuire la carica del canale ovunque, consentendo di non aumentare accesso le resistenze parassite di dispositivo al intrinseco, con le limitazioni nelle prestazioni GaNHEMT dello stato dell'arte, quali quelle descritte nella parte introduttiva ed originate dall'uso di materiale semiconduttore il cui buffer è drogato ovunque impurezze accettrici.

In una forma di realizzazione preferita, l'impiantazione ionica di impurezze accettrici può essere effettuata attraverso lo strato dielettrico precedentemente alla realizzazione del piede 11, affinché la presenza di tale strato dielettrico utilizzato possa fungere come incapsulante durante il ciclo termico di annealing dopo

l'impiantazione ionica stessa, necessario per rimuovere il danno al reticolo cristallino conseguente all'impatto degli ioni impiantati. Tale ciclo termico di annealing, potrebbe essere accorpato a quello di lega degli elettrodi di sorgente 6 e di pozzo 7, e/o durante il ciclo termico realizzato dopo la deposizione della metallizzazione del piede 11.

L'impiantazione ionica di impurezze accettrici può essere quindi effettuata mediante una maschera applicata precedentemente alla definizione del piede 11, oppure utilizzando lo stesso strato di mascheratura 8 utilizzato per la di definizione del piede 11. Quest'ultimo caso consente di avere due ulteriori vantaggi:

- il primo vantaggio riguarda le prestazioni dell'HEMT, accettrici impiantate perché le impurezze risultano confinate in un area molto stretta sotto la giunzione Schottky, limitando l'aumento delle resistenze d'accesso, anche aumentando la compensazione della carica fino ad concentrazione del annullare la gas elettronico bidimensionale ("two dimensional electron gas" 2DEG) con elettrodo di controllo polarizzato a 0 V (HEMT enhanched);

- il secondo vantaggio riguarda la semplicità di realizzazione, perché l'impiantazione ionica di impurezze accettrici è auto-allineata all'elettrodo di controllo 13, annullando la criticità dell'allineamento con la formazione

del piede 11, e non è necessario effettuare altri passaggi tecnologici per la mascheratura ed il rinvenimento per l'impiantazione.

Realizzando l'impiantazione ionica selettiva dі impurezze accettrici, in particolare per i dispositivi di potenza, facendo si che il loro drogaggio sia realizzato in prossimità dell'elettrodo di controllo 13 con una maggiore estensione verso l'elettrodo di pozzo 7, attraverso un'opportuna apertura della maschera per l'impiantazione se realizzata in precedenza alla definizione del piede 11, si ottiene l'effetto di diminuire la concentrazione elettroni nel canale sul lato rivolto verso l'elettrodo di pozzo 7 rispetto all'elettrodo di controllo 13, consentendo così di realizzare un profilo di drogaggio analogo a quello implementato nei dispositivi di potenza MOSFET a basso drogaggio di pozzo ("Low Doping Drain" - LDD) realizzati in silicio (Si), ottenendo benefici analoghi a descritti nella parte introduttiva con riferimento allo stato dell'arte. Una simile distribuzione di impurezze accettrici, ottenuta mediante l'impiantazione selettiva, può essere abbinata anche alla realizzazione di un elettrodo di field plate 13' (Figure 4-6), ed in particolare effettuata attraverso le due aperture 9 sullo strato di mascheratura 8.

## RIVENDICAZIONI

- 1. Processo di fabbricazione di un transistore ad alta mobilità elettronica (1; 1'), comprendente:

- predisporre un substrato epitassiale comprendente un substrato semi-isolante (2), uno strato buffer (3) ed uno strato barriera (4) sequenzialmente impilati;

- formare un primo ed un secondo elettrodo di conduzione di corrente (6, 7) sul, ed in contatto ohmico con, lo strato barriera (4); e

- formare un elettrodo di controllo (13) sul, ed in contatto Schottky con, lo strato barriera (4), fra il primo ed il secondo elettrodo di conduzione di corrente (6, 7);

caratterizzato dal fatto che formare un elettrodo di controllo (13) sullo strato barriera (4) comprende:

- formare una porzione inferiore (11) dell'elettrodo di controllo (13);

- effettuare un trattamento termico di stabilizzazione e ricottura per rimuovere il danneggiamento al reticolo cristallino della superficie del semiconduttore introdotto dai passi di processo precedenti e stabilizzare l'interfaccia metallo-semiconduttore della giunzione Schottky; e

- formare una porzione superiore (12) dell'elettrodo di controllo (13) sul, ed in contatto elettrico con, la porzione inferiore (11) dell'elettrodo di controllo (13).

- 2. Metodo di fabbricazione secondo la rivendicazione 1, in cui una porzione inferiore (11) dell'elettrodo di controllo (13) comprende:

- formare uno strato di protezione meccanica e/o di passivazione (5) sullo strato barriera (4), fra il primo ed il secondo elettrodo di conduzione di corrente (6, 7);

- formare una prima finestra (10) nello strato di protezione meccanica e/o di passivazione (5), in maniera tale da esporre una superficie dello strato barriera (4);

- formare la porzione inferiore (11) del primo elettrodo di controllo (13) sulla superficie esposta dello strato barriera (4), in maniera tale da non fuoriuscire dallo strato di protezione meccanica e/o passivazione (5);

in cui formare una porzione superiore (12) dell'elettrodo di controllo (13) comprende:

• formare la porzione superiore (12) del primo elettrodo di controllo (13) sulla porzione inferiore (11) del primo elettrodo di controllo (13), in maniera tale da fuoriuscire dallo strato di protezione meccanica e/o passivazione (5);

ed in cui formare la porzione superiore (12) del primo elettrodo di controllo (13) comprende:

• formare una prima porzione (12a) che si estende lateralmente sullo strato di protezione meccanica e/o di passivazione (5), così da appoggiarsi su e risultare

meccanicamente supportate da quest'ultimo; e

- formare una seconda porzione (12b) verticalmente distanziata dalla ed estendentisi lateralmente da uno o entrambi i lati della prima porzione (12a).

- 3. Metodo di fabbricazione secondo la rivendicazione 1 o 2, in cui almeno uno degli strati del substrato epitassiale comprendente un Nitruro di un elemento del III gruppo, in particolare Nitruro di Gallio (GaN), ed in cui le temperature raggiunte durante il trattamento termico di stabilizzazione e ricottura superiore a 450°C.

- 4. Metodo di fabbricazione secondo una qualsiasi delle rivendicazioni precedenti, comprendente inoltre:

- formare un elettrodo di field plate (13') sul, ed in contatto Schottky con, lo strato barriera (4), fra il primo ed il secondo elettrodo di conduzione di corrente (6, 7);

in cui formare un elettrodo di field plate (13') sullo strato barriera (4) comprende:

- formare solo una porzione inferiore (11') dell'elettrodo di field plate (13') contemporaneamente alla porzione inferiore (11) dell'elettrodo di controllo (13), e tale da non fuoriuscire dallo strato di protezione meccanica e/o passivazione (5).

- 5. Metodo di fabbricazione secondo la rivendicazione 4, in cui il primo ed il secondo elettrodo di conduzione di corrente (6, 7) sono destinati ad operare come elettrodi di

sorgente e, rispettivamente, di pozzo, ed in cui l'elettrodo di controllo (13) è formato adiacente all'elettrodo di sorgente (6) ed è destinato a ricevere un segnale di ingresso ad alta frequenza, mentre l'elettrodo di field plate (13') è formato adiacente all'elettrodo di pozzo (7) ed è polarizzato ad un potenziale elettrico di riferimento.

- 6. Metodo di fabbricazione secondo la rivendicazione 4 o 5, comprendente inoltre:

- collegare elettricamente l'elettrodo di field plate (13') ad un potenziale elettrico di riferimento attraverso un contatto rettificante e/o una resistenza elettrica.

- 7. Metodo di fabbricazione secondo la rivendicazione 6, in cui collegare elettricamente l'elettrodo di field plate (13') ad un potenziale elettrico di riferimento attraverso un contatto rettificante e/o una resistenza elettrica comprende:

- formare un'area elettricamente non conduttiva (4')

nello strato barriera (4), all'esterno dell'area

elettricamente conduttiva dove è realizzato il transistore

ad alta mobilità elettronica (1; 1');

- formare nell'area elettricamente non conduttiva (4')

una striscia (14) di materiale semiconduttore avente una

resistenza elettrica dipendente dalle dimensioni

geometriche e dalla resistività del materiale

semiconduttore; la striscia (14) avendo una prima estremità elettricamente connessa all'elettrodo di field plate (13'), formando così con questo il detto contatto rettificante, ed una seconda estremità elettricamente connessa ad un potenziale elettrico di riferimento mediante un contatto ohmico.

- 8. Metodo di fabbricazione secondo una qualsiasi delle rivendicazioni precedenti, comprendente inoltre:

- impiantare ionicamente impurezze accettrici al di sotto dell'elettrodo di controllo (13), in corrispondenza della regione di canale del transistore ad alta mobilità elettronica (1; 1').

- 9. Transistore ad alta mobilità elettronica (1') comprendente:

- un substrato epitassiale includente un substrato semi-isolante (2), uno strato buffer (3) ed uno strato barriera (4) sequenzialmente impilati;

- un primo ed un secondo elettrodo di conduzione di corrente (6, 7) formati sul, ed in contatto elettrico con, lo strato barriera (4);

- un elettrodo di controllo (13) ed un elettrodo di field plate (13') formati sul, ed in contatto Schottky con, lo strato barriera (4), fra il primo ed il secondo elettrodo di conduzione di corrente (6, 7); ed

- un circuito elettrico comprendente un contatto

rettificante e/o una resistenza elettrica e formato per collegare elettricamente l'elettrodo di field plate (13') ad un potenziale elettrico di riferimento.

10. Transistore ad alta mobilità elettronica (1') secondo la rivendicazione 9, in cui l'elettrodo di controllo (13) è realizzato secondo una qualsiasi delle rivendicazioni da 1 a 8.

11. Dispositivo integrato a semiconduttore comprendente almeno uno fra un transistore ad alta mobilità elettronica (1) realizzato secondo una qualsiasi delle rivendicazioni da 1 a 8 ed un transistore ad alta mobilità elettronica (1') secondo la rivendicazione 9, ed un transistore ad alta mobilità elettronica (1') con giunzione di controllo Metallo-Isolante-Semiconduttore.

p.i.: SELEX SISTEMI INTEGRATI S.P.A.

Mirko BERGADANO

## CLAIMS

- 1. Process of manufacturing a high electron mobility transistor (1; 1'), comprising:

- providing an epitaxial substrate comprising a semiinsulating substrate (2), a buffer layer (3) and a barrier layer (4) sequentially stacked;

- forming first and second current conducting electrodes (6, 7) on, and in ohmic contact with, the barrier layer (4); and

- forming a gate electrode (13) on, and in Schottky contact with, the barrier layer (4), between the first and second current conducting electrodes (6, 7);

characterized in that forming a gate electrode (13) on the barrier layer (4) comprises:

- forming a lower portion (11) of the gate electrode (13);

- carrying out a thermal stabilization and annealing treatment for removing from the surface of the semiconductor the crystal lattice damage caused by the preceding steps of the process and stabilizing the metal-semiconductor interface of the Schottky junction; and

- forming an upper portion (12) of the gate electrode (13) on, and in electric contact with, the lower portion (11) of the gate electrode (13).

- 2. The manufacturing process of claim 1, wherein

forming a lower portion (11) of the gate electrode (13) comprises:

- forming a mechanical protection and/or passivation layer (5) on the barrier layer (4) between the first and second current conducting electrodes (6, 7);

- forming a first window (10) in the mechanical protection and/or passivation layer (5) so as to expose a surface of the barrier layer (4);

- forming the lower portion (11) of the gate electrode (13) on the exposed surface of the barrier layer (4) so as not to leak from the mechanical protection and/or passivation layer (5);

wherein forming an upper portion (12) of the gate electrode (13) comprises:

- forming the upper portion (12) of the gate electrode (13) on the lower portion (11) of the gate electrode (13) so as to leak from the mechanical protection and/or passivation layer (5);

wherein forming the upper portion (12) of the gate electrode (13) comprises:

- forming a first portion (12a), which extends laterally on the mechanical protection and/or passivation layer (5) so as to rest on, and be mechanically supported by, the latter; and

- forming a second portion (12b) vertically spaced

apart from, and laterally extending from either one or both of the sides of, the first portion (12a).

- 3. The manufacturing process according to claim 1 or 2, wherein at least one of the layers of the epitaxial substrate comprises a Nitride of an element in the III group, in particular Gallium Nitride (GaN), and wherein the temperatures reached during the thermal stabilization and annealing treatment are higher than 450°C.

- 4. The manufacturing process according to any preceding claim, further comprising:

- forming a field plate electrode (13') on, and in Schottky contact with, the barrier layer (4) between the first and second current conducting electrodes (6, 7);

wherein forming a field plate electrode (13') on the barrier layer (4) comprises:

- forming only a lower portion (11') of the field plate electrode (13') at the same time as the lower portion (11) of the gate electrode (13), and such that not to leak from the mechanical protection and/or passivation layer (5).

- 5. The manufacturing process of claim 4, wherein the first and second current conducting electrodes (6, 7) are intended to be operated as source and drain electrodes, respectively, and wherein the gate electrode (13) is formed adjacent to the source electrode (6) and is intended to

receive a high-frequency input signal, while the field plate electrode (13') is formed adjacent to the drain electrode (7) and is polarized to a reference electric potential.

- 6. The manufacturing process according to claim 4 or 5, further comprising:

- electrically connecting the field plate electrode (13') to a reference electric potential by means of a rectifying contact and/or an electric resistor.

- 7. The manufacturing process of claim 6, wherein electrically connecting the field plate electrode (13') to a reference electric potential by means of a rectifying contact and/or an electric resistor comprises:

- forming an electrically non-conductive area (4') in the barrier layer (4), outside the electrically conductive area where the high electron mobility transistor (1; 1') is made;

- forming in the electrically non-conductive area (4') a strip (14) of semiconductor material having an electric resistance depending on the geometric dimensions and resistivity of the semiconductor material; the strip (14) having a first end electrically connected to the field plate connector (13'), thus forming therewith said rectifying contact, and a second end electrically connected to a reference electric potential by means of an ohmic

contact.

- 8. The manufacturing process according to any preceding claim, further comprising:

- ionically implanting accepting impurities underneath the gate electrode (13), at the channel region of the high electronic mobility transistor (1; 1').

- 9. High electron mobility transistor (1') comprising:

- an epitaxial substrate including a semi-insulating substrate (2), a buffer layer (3) and a barrier layer (4) sequentially stacked;

- first and second current conducting electrodes (6, 7) formed on, and in electric contact with, the barrier layer (4);

- a gate electrode (13) and a field plate electrode (13') formed on, and in Schottky contact with, the barrier layer (4) between the first and second current conducting electrodes (6, 7); and

- an electric circuit comprising a rectifying contact and/or an electric resistor, and formed to electrically connect the field plate electrode (13') to a reference electric potential.

- 10. The high electron mobility transistor (1') of claim 9, wherein the gate electrode (13) is made according to any claim from 1 to 8.

- 11. Integrated semiconductor device comprising at

least one of either a high electronic mobility transistor (1) made according to any claim from 1 to 8, or a high electron mobility transistor (1') according to claim 9, and a high electron mobility transistor (1") with Metal-Insulator-Semiconductor gate junction.

Fig. 1

Fig. 2

Fig. 3

p.i.: SELEX SISTEMI INTEGRATI S.P.A.

Mirko BERGADANO (Iscrizione Albo nr. 843/BM)

Fig. 6

p.i.: SELEX SISTEMI INTEGRATI S.P.A.

Mirko BERGADANO (Iscrizione Albo nr. 843/BM)

Fig. 7

Fig. 8

p.i.: SELEX SISTEMI INTEGRATI S.P.A.

Mirko BERGADANO (Iscrizione Albo nr. 843/BM)