(19) 日本国特許庁 (JP)

(12) 特 許 公 報(B2)

(11) 特許番号

特許第4732138号

(P4732138)

(45) 発行日 平成23年7月27日(2011.7.27)

(24) 登録日 平成23年4月28日 (2011.4.28)

(51) Int.Cl.

H O 1 L 23/50 (2006.01)

F 1

HO 1 L 23/50

K

請求項の数 7 (全 25 頁)

(21) 出願番号 特願2005-327635 (P2005-327635)

(22) 出願日 平成17年11月11日 (2005.11.11)

(65) 公開番号 特開2007-134585 (P2007-134585A)

(43) 公開日 平成19年5月31日 (2007.5.31)

審査請求日 平成20年11月7日 (2008.11.7)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100083552

弁理士 秋田 収喜

(72) 発明者 天野 賢治

北海道亀田郡七飯町字中島145番地 株式会社ルネサス北日本セミコンダクタ内

(72) 発明者 長谷部 一

北海道亀田郡七飯町字中島145番地 株式会社ルネサス北日本セミコンダクタ内

審查官 馳平 烏一

最終頁に続く

(54) 【発明の名称】 半導体装置及びその製造方法

(57) 【特許請求の範囲】

### 【請求項 1】

上面、前記上面とは反対側の下面を有するチップ搭載部と、

主面、前記主面とは反対側の裏面、及び前記主面に形成された複数の電極パッドを有し

、前記チップ搭載部の前記上面上に搭載された半導体チップと、

前記チップ搭載部の周囲に配置された複数のリードと、

前記チップ搭載部に連なる複数の吊りリードと、

前記半導体チップの前記複数の電極パッドと前記複数のリード、および前記半導体チップの前記複数の電極パッドと前記チップ搭載部をそれぞれ電気的に接続する複数のボンディングワイヤと、

表面、前記表面とは反対側の実装面を有し、前記複数のリードのそれぞれの一部、前記チップ搭載部の前記下面、および前記複数の吊りリードのそれぞれの一部が前記実装面から露出するように、前記半導体チップ、前記複数のリード及び前記複数のボンディングワイヤを封止する樹脂封止体と、

を含み、

前記樹脂封止体の平面形状は、4つの辺を有する四角形から成り、

前記複数のリードは、前記樹脂封止体の各辺に沿って配置され、

前記複数の吊りリードは、前記チップ搭載部から前記樹脂封止体の前記4つの辺のうち

の複数辺に向かってそれぞれ延在しており、

前記複数の吊りリードのそれぞれは、第1の部分と、前記第1の部分と前記チップ搭載

部との間に位置し、かつ、前記第1の部分の厚さよりも小さい第2の部分とを有していることを特徴とする半導体装置。

【請求項2】

前記複数のリードは、前記半導体チップ側に位置する一端部と、前記樹脂封止体の前記各辺側に位置する他端部とを有し、

前記複数のリードのそれぞれの前記一端部における配列ピッチは、前記複数のリードのそれぞれの前記他端部の配列ピッチと同一であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記半導体チップの前記裏面の一部は、前記樹脂封止体と接触していることを特徴とする請求項2に記載の半導体装置。 10

【請求項4】

前記チップ搭載部の平面サイズは、前記半導体チップの平面サイズよりも小さいことを特徴とする請求項2に記載の半導体装置。

【請求項5】

前記半導体チップの前記電極パッドは、前記ボンディングワイヤ及び前記吊りリードを介して、前記チップ搭載部と電気的に接続されていることを特徴とする請求項3又は4に記載の半導体装置。

【請求項6】

前記複数のリードは、前記ボンディングワイヤが接続される第1の面と、前記第1の面の反対側に位置し、前記樹脂封止体の前記実装面から露出する第2の面と、前記第1の面よりも前記第2の面側に位置する第3の面とを有し、 20

前記複数のリードのそれぞれは、前記第3の面が前記半導体チップと平面的に重なるように、配置されていることを特徴とする請求項5に記載の半導体装置。

【請求項7】

(a) 上面、前記上面とは反対側の下面を有するチップ搭載部と、前記チップ搭載部の周囲に配置された複数のリードと、前記チップ搭載部に連なる複数の吊りリードとを備えたリードフレームを準備する工程、

(b) 主面、前記主面とは反対側の裏面、及び前記主面に形成された複数の電極パッドを有する半導体チップを、前記チップ搭載部の前記上面上に搭載する工程、 30

(c) 前記半導体チップの前記複数の電極パッドと前記複数のリード、および前記半導体チップの前記複数の電極パッドと前記チップ搭載部を、複数のボンディングワイヤを介してそれぞれ電気的に接続する工程、

(d) 前記半導体チップ、前記複数のリード及び前記複数のボンディングワイヤを樹脂で封止する工程、

(e) 前記リードフレームの一部を切断する工程、

を含み、

前記(d)工程により形成される樹脂封止体は、表面と、前記表面とは反対側の実装面とを有し、

前記樹脂封止体の平面形状は、4つの辺を有する四角形から成り、 40

前記複数のリードは、前記樹脂封止体の各辺に沿って配置され、

前記複数のリード、前記チップ搭載部、および前記複数の吊りリードは、前記複数のリードのそれぞれの一部、前記チップ搭載部の前記下面、および前記複数の吊りリードのそれぞれの一部が前記樹脂封止体の前記実装面から露出するように、前記樹脂で封止され、

前記複数の吊りリードは、前記チップ搭載部から前記樹脂封止体の前記4つの辺のうちの複数辺に向かってそれぞれ延在してあり、

前記複数の吊りリードのそれぞれは、第1の部分と、前記第1の部分と前記チップ搭載部との間に位置し、かつ、前記第1の部分の厚さよりも小さい第2の部分とを有していることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、半導体装置及びその製造技術に関し、特に、ノンリード型半導体装置に適用して有効な技術に関するものである。

**【背景技術】****【0002】**

集積回路が搭載された半導体チップを樹脂封止してなる半導体装置においては、様々なパッケージ構造のものが提案され、製品化されている。その中の1つに、例えばQFN (Quad Flat Non-Leaded Package) 型と呼称される半導体装置が知られている。このQFN型半導体装置は、半導体チップの電極と電気的に接続されたリードを外部接続用端子として樹脂封止体の裏面から露出させたパッケージ構造になっているため、半導体チップの電極と電気的に接続されたリードを樹脂封止体の側面から突出させて所定の形状に折り曲げ成型したパッケージ構造、例えばQFP (Quad Flat Package) 型と呼称される半導体装置と比較して、平面サイズの小型化を図ることができる。10

**【0003】**

QFN型半導体装置は、その製造においてリードフレームが使用される。リードフレームは、金属板に精密プレスによる打ち抜き加工やエッティング加工を施して所定のパターンを形成することによって製造される。リードフレームは、メインフレーム及びサブフレームを含むフレーム本体で区画された複数の製品形成領域を有し、各製品形成領域には、半導体チップを搭載するためのチップ搭載部（タブ、ダイパッド、チップ支持体）や、このチップ搭載部の周囲に一端部（先端部）を臨ませる複数のリード等が配置されている。チップ搭載部は、リードフレームのフレーム本体から延在する吊りリードによって支持されている。リードは、その一端部（先端部）と反対側の他端部がリードフレームのフレーム本体に支持されている。20

**【0004】**

このようなリードフレームを使用してQFN型半導体装置を製造する場合、リードフレームのチップ搭載部に半導体チップを搭載し、その後、半導体チップの電極とリードとを導電性のワイヤで電気的に接続し、その後、半導体チップ、ワイヤ、チップ搭載部、吊りリード等を樹脂封止して樹脂封止体を形成し、その後、リードフレームの不要な部分を切断除去する。30

**【0005】**

QFN型半導体装置の樹脂封止体は、大量生産に好適なトランスファ・モールディング法（移送成形法）によって形成される。トランスファ・モールディング法による樹脂封止体の形成は、成形金型（モールディング金型）のキャビティ（樹脂充填部）の内部に、半導体チップ、リード、チップ搭載部、吊りリード、及びボンディングワイヤ等が配置されるように、成形金型の上型と下型との間にリードフレームを型締めし、その後、成形金型のキャビティの内部に熱硬化性樹脂を注入することによって行われる。

**【0006】**

なお、QFN型半導体装置については、例えば特開2003-37219号公報に記載されている。また、同公報には、「インナーリード部4のダイパッド部1に対向した先端部上面は、その厚みが薄く構成され、先端部は薄厚部7を有しているので、ダイパッド部1上に搭載した半導体素子3の周縁部をそのインナーリード部4の先端部上面の薄厚部7に近接させることができ、インナーリード部4と半導体素子3との接触を避けつつ、大型の半導体素子を搭載して、CSP化を実現できるものである。しかもインナーリード部4の先端部上面が薄厚部7を有しているので、ダイパッド部1に上方にあげた支持部を設けてアップセットする必要はなく、樹脂封止型半導体装置としてチップ占有率を高めて薄厚化を実現できるものである。」という技術が記載されている。40

**【0007】****【特許文献1】特開2003-37219号公報****【発明の開示】**

## 【発明が解決しようとする課題】

## 【0008】

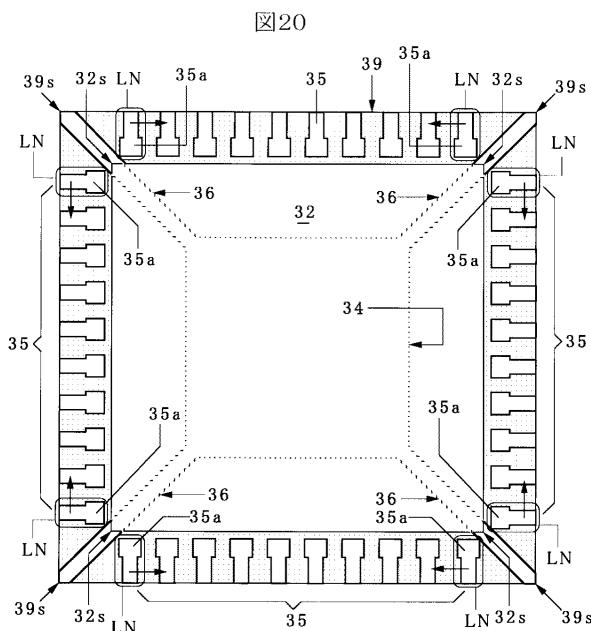

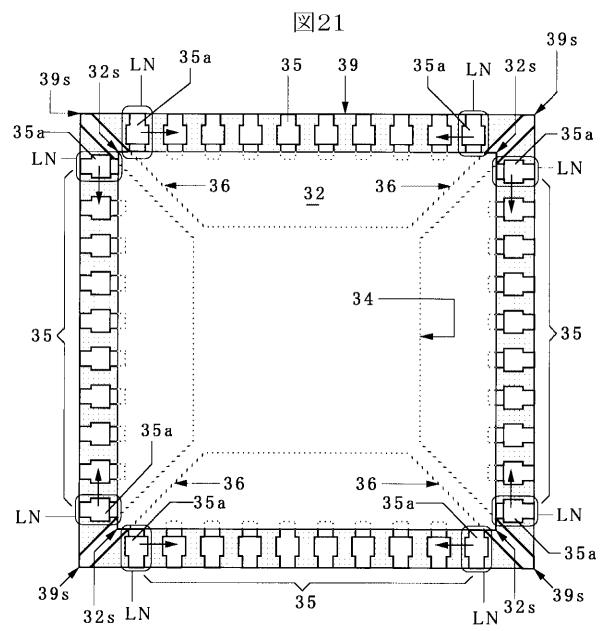

QFN型半導体装置は、様々な電子機器に搭載されているが、特に携帯電話等の小型携帯機器に搭載されるQFN型半導体装置においては、更なる小型化が要求されている。また、半導体チップに搭載される集積回路の高速化、多機能化、及び高集積化に伴い、QFN型半導体装置においても多ピン化が要求されている。そこで、本発明者は、QFN型半導体装置の小型化及び多ピン化について検討した。図20及び図21は、従来のQFN型半導体装置の内部構造を示す模式的平面図である。

## 【0009】

QFN型半導体装置の小型化は、図20に示すように、半導体チップ32の辺に沿って配置される複数のリード35からなるリード列（リード群）の長さを半導体チップ32の辺の長さよりも小さく（短く）し、出来る限り半導体チップ32の辺に向かってリード35を近づけることによって実現できる。また、図21に示すように、各々の先端部が半導体チップ32の裏面と平面的に重なるように半導体チップ32の辺に沿って複数のリード35を配置することによって更に小型化を実現できる。

## 【0010】

しかしながら、従来のQFN型半導体装置においては、図20に示すように、チップ搭載部34に連なる4本の吊りリード36が、チップ搭載部34から樹脂封止体39の角部39sに向かって放射状に延在し、半導体チップ32の角部32sに配置されている。即ち、4本の吊りリード36は、リード35の延在方向に対して鋭角となる角度で斜めになって半導体チップ32の角部32sに配置されている。

## 【0011】

このような吊りリード36の配置では、図20に示すように、半導体チップ32の辺に沿って配置された複数のリード35を半導体チップ32の辺に向かって近づけると、吊りリード36と、この吊りリード36に隣接するリード35aの先端部との間隔が狭くなり、吊りリード36にリード35aが干渉し易くなるため、吊りリード36とリード35aとの干渉を考慮すると、吊りリード36から半導体チップ32の辺に沿ってリード35aを遠ざける必要があり、半導体チップ32の角部32s付近にリード35を設置することが困難となる。半導体チップ32の角部32s付近にリード35を設置できない非リード設置領域LNは、1本の吊りリード36に対して2箇所発生するため、4本の吊りリード36で合計8本のリード35が設置できなくなる。

## 【0012】

特に、図21に示すように、各々の先端部が半導体チップ32の裏面と重なるように半導体チップ32の辺に沿って複数のリード35を配置する場合においては、吊りリード36から半導体チップ32の辺に沿ってリード35aを更に遠ざける必要があり、半導体チップ32の角部32s付近へのリード設置が更に困難となる。

## 【0013】

このように、半導体チップ32の角部付近へのリード設置が困難になることは、樹脂封止体39の裏面からリード35の一部を露出させて得られる外部接続用端子の取得数低減となり、多ピン化の要求に対して逆行する。従って、半導体チップ32の辺に沿って配置される複数のリード35を半導体チップ32の辺に向かって近づけて小型化を実現するためには、半導体チップ32の角部32s付近にリード35を設置できるように（非リード設置領域を排除できるように）工夫してリード本数の増加（多ピン化）を実現する必要がある。

## 【0014】

本発明の目的は、半導体装置の小型化及び多ピン化を図ることが可能な技術を提供することにある。

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかになるであろう。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記のとおりである。

## 【0016】

上記目的は、半導体チップの辺に沿って配置される複数のリードからなるリード列に、チップ搭載部に連なる吊りリードを配置する、換言すれば、半導体チップの辺に沿って配置される複数のリードのうち、1本のリードをチップ搭載部に連なる吊りリードとして使用することによって達成される。

## 【0017】

チップ搭載部と連なる吊りリードは、半導体チップの角部を通る（横切る）ことなく、リードの延在方向に沿ってチップ搭載部から樹脂封止体の辺に向かって延在していれば何処に配置しても良い。 10

## 【0018】

また、チップ搭載部に連なる吊りリードは、半導体チップの電極パッドにボンディングワイヤを介して電気的に接続されるリードとして使用、即ち半導体チップの電極パッドと吊りリードとをボンディングワイヤで電気的に接続しても良い。

## 【0019】

また、チップ搭載部に連なる吊りリードは、半導体チップの辺毎に設けてもよいが、少なくとも1本あれば良い。吊りリードが1本の場合、モールディング工程において、封止用キャビティに注入される樹脂の流動によってチップ搭載部が変動し易くなるが、チップ搭載部の変動は、樹脂封止体が形成される主面と反対側の裏面にバックテープが貼り付けられたリードフレームを使用することによって抑制することができる。 20

## 【0020】

バックテープが貼り付けられたリードフレームを使用する場合、バックテープのしわを抑制するため、吊りリードには、チップ搭載部をリードよりも上方に位置させるオフセット加工を施さず、リード、吊りリード及びチップ搭載部の高さ位置がフラットになっていることが望ましい。

## 【発明の効果】

## 【0021】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。 30

本発明によれば、半導体装置の小型化及び多ピン化を図ることができる。

## 【発明を実施するための最良の形態】

## 【0022】

以下、図面を参照して本発明の実施例を詳細に説明する。なお、発明の実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

## 【実施例1】

## 【0023】

本実施例1では、チップ搭載部に2本の吊りリードが連なる例について説明する。 40

## 【0024】

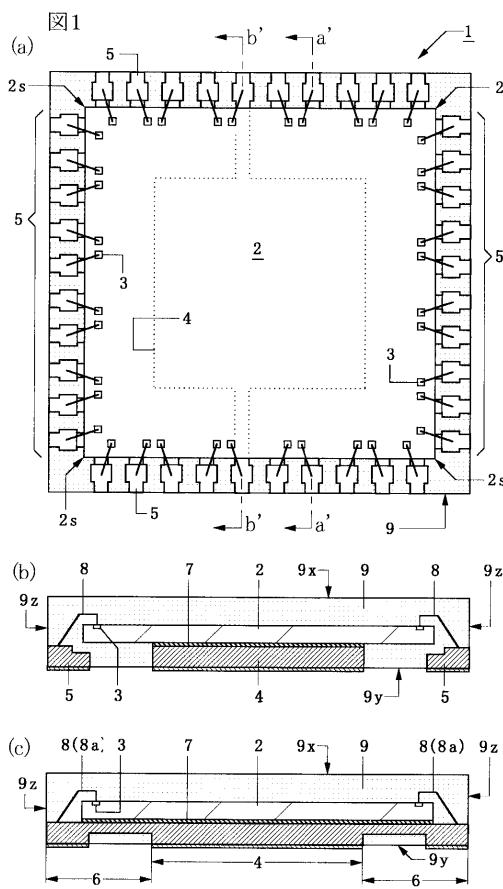

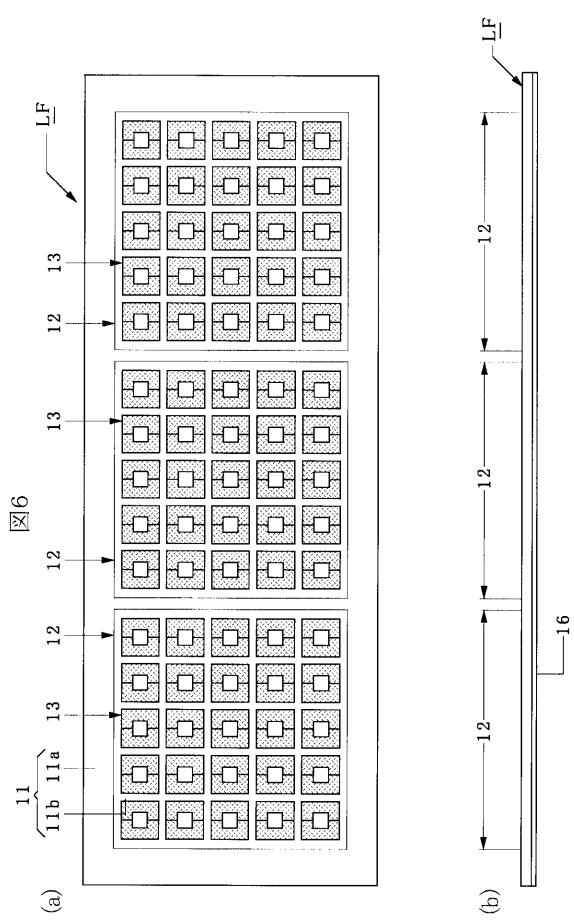

図1乃至図17は、本発明の実施例1であるQFN型半導体装置に係る図であり、

図1は、半導体装置の内部構造を示す図（（a）は模式的平面図、（b）は（a）のa'-a'線に沿う模式的断面図、（c）は（a）のb'-b'線に沿う模式的断面図）、

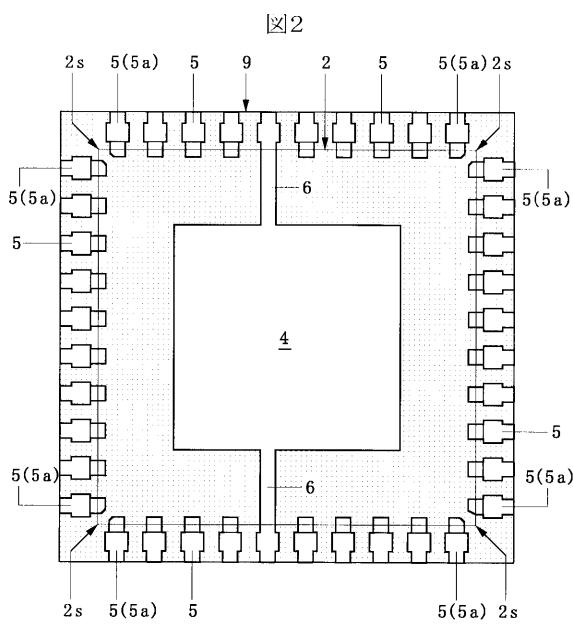

図2は、図1（a）に示す半導体チップ及びボンディングワイヤを省略した模式的平面図、

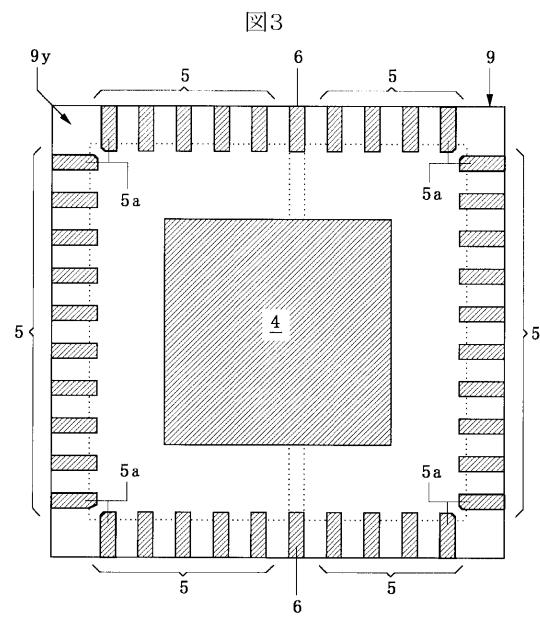

図3は、半導体装置の裏面側を示す模式的底面図、

図4は、図1（b）の一部を拡大した模式的断面図、

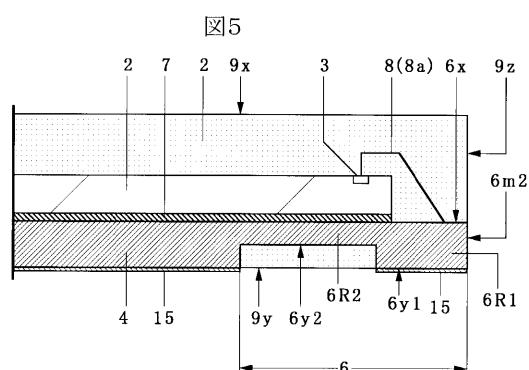

図5は、図1（c）の一部を拡大した模式的断面図、

図6は、半導体装置の製造に使用されるリードフレームの概略構成を示す図（（a）は 50

模式的平面図、(b)は模式的側面図)、

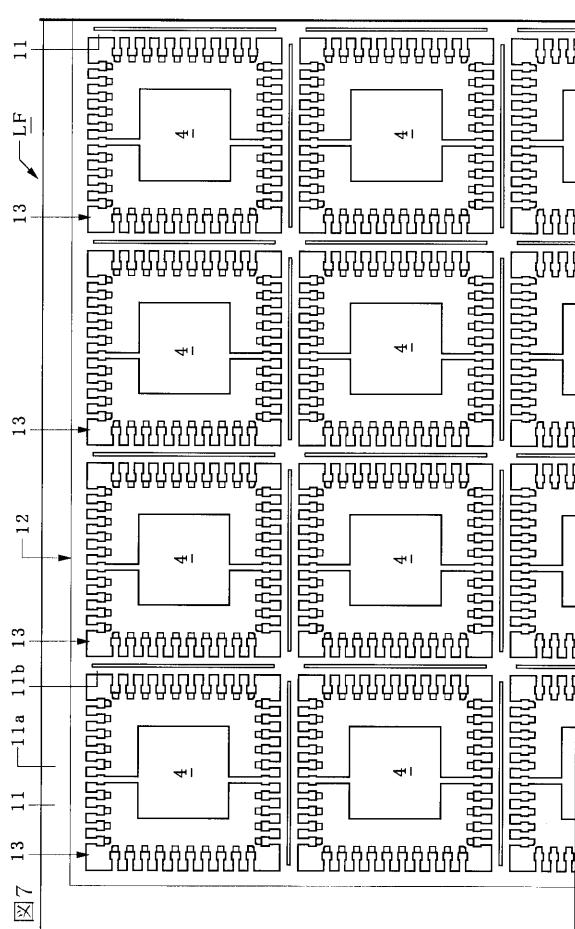

図7は、図6(a)の一部を拡大した模式的平面図、

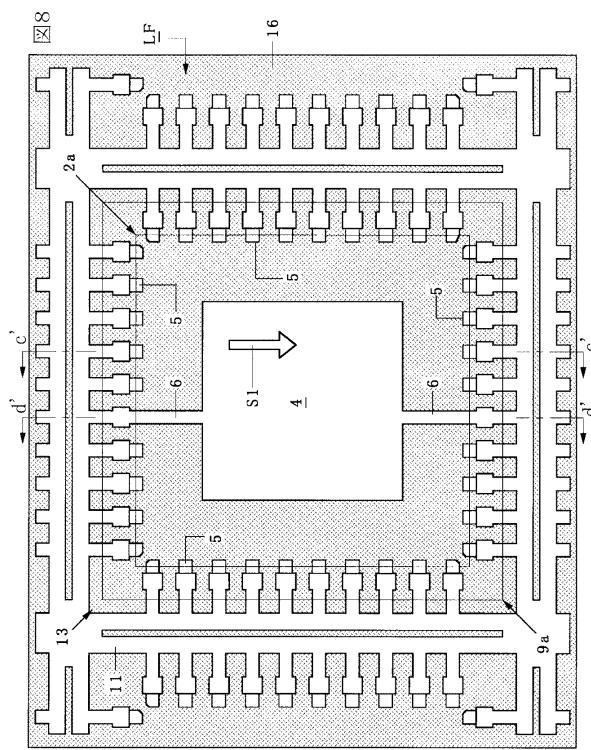

図8は、図7の一部を拡大した模式的平面図、

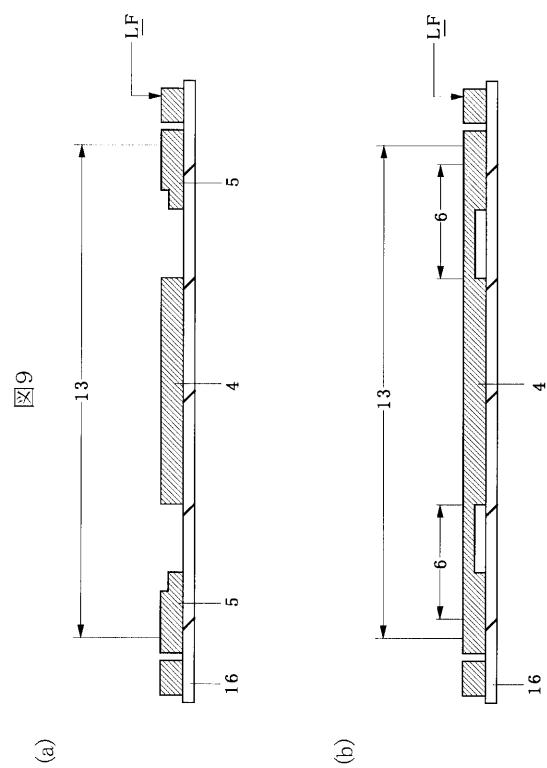

図9において、(a)は図8のc'-c'線に沿う模式的断面図、(b)は図8のd'-d'線に沿う模式的断面図、

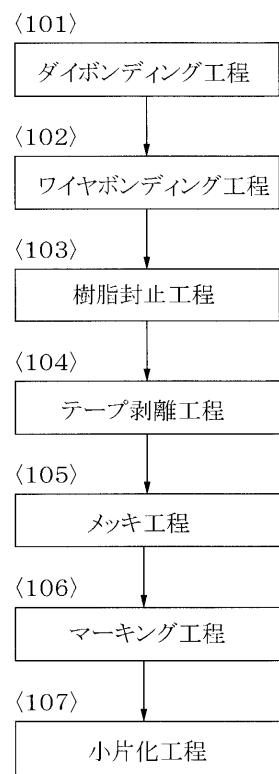

図10は、半導体装置の製造工程を示すフローチャート、

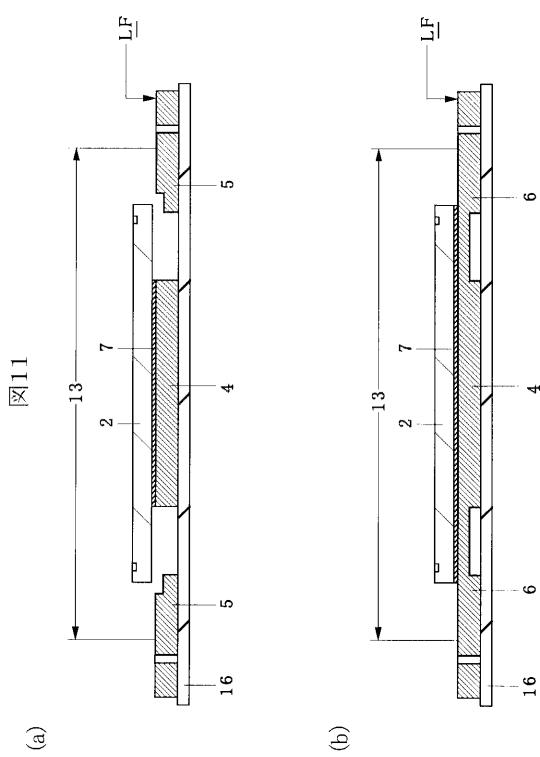

図11は、図10のダイポンディング工程を示す図((a)は図8のc'-c'線に沿う位置での模式的断面図、(b)は図8のd'-d'線に沿う位置での模式的断面図)、

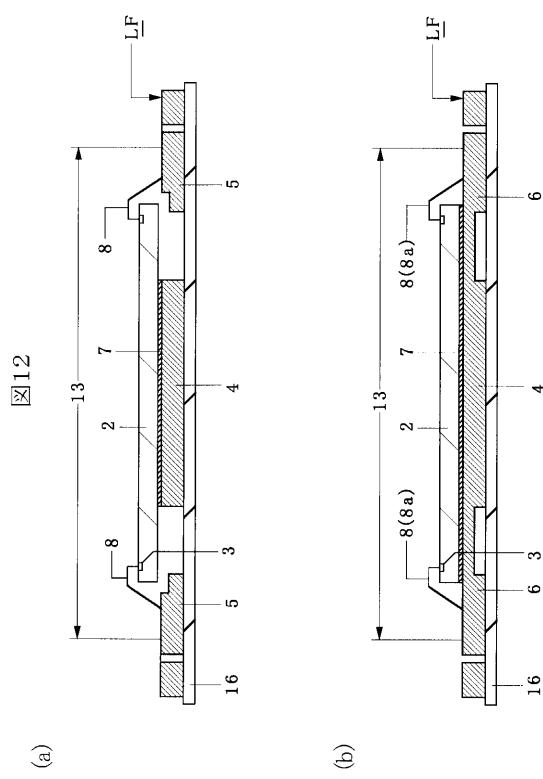

図12は、図10のワイヤボンディング工程を示す図((a)は図8のc'-c'線に沿う位置での模式的断面図、(b)は図8のd'-d'線に沿う位置での模式的断面図) 10

、

図13は、図10の樹脂封止工程を示す図(成形金型にリードフレームを型締め固定した状態を示す模式的断面図)、

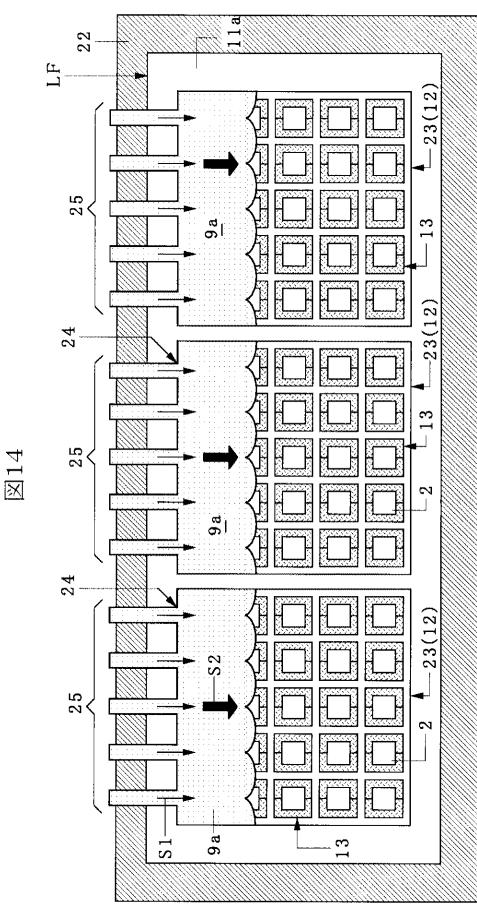

図14は、成形金型のキャビティに注入された樹脂の流れを示す模式的平面図、

図15は、成形金型の封止用キャビティに樹脂封止体が形成された状態を透視して示す模式的平面図、

図16は、図10のバックテープ剥離工程を示す図((a)は模式的平面図、(b)は模式的側面図))、

図17は、図10の小片化(個片化)工程を示す図((a)は模式的平面図、(b)は模式的側面図))である。 20

#### 【0025】

本実施例1の半導体装置1は、図1((a),(b),(c))及び図2に示すように、半導体チップ2、チップ搭載部(タブ、ダイパッド、チップ支持体)4、複数のリード5、2本の吊りリード6(6a, 6b)、複数のボンディングワイヤ8等を樹脂封止体9によって封止したパッケージ構造になっている。

#### 【0026】

半導体チップ2は、その厚さ方向と交差する平面形状が方形状になっており、本実施例1では例えば4mm×4mmの正方形になっている。半導体チップ2は、これに限定されないが、例えば、半導体基板、この半導体基板の主面に形成された複数のトランジスタ素子、前記半導体基板の主面上において絶縁層、配線層の夫々を複数段積み重ねた多層配線層、この多層配線層を覆うようにして形成された表面保護膜(最終保護膜)等を有する構成になっている。 30

#### 【0027】

半導体チップ2は、互いに反対側に位置する主面(回路形成面)及び裏面を有し、半導体チップ2の主面側には集積回路が形成されている。集積回路は、主に、半導体基板の主面に形成されたトランジスタ素子、及び多層配線層に形成された配線によって構築されている。

#### 【0028】

半導体チップ2の主面には、複数の電極パッド(ボンディングパッド)3が形成されている。複数の電極パッド3は、半導体チップ2の各辺(4つの辺)に沿って配置されている。複数の電極パッド3は、半導体チップ2の多層配線層のうちの最上層の配線層に形成され、各々のボンディングパッド3に対応して半導体チップ2の表面保護膜に形成されたボンディング開口によって露出されている。 40

#### 【0029】

樹脂封止体9は、厚さ方向と交差する平面形状が方形状になっており、本実施例1では例えば4.7mm×4.7mmの正方形になっている。樹脂封止体9は、互いに反対側に位置する主面(上面)9x及び裏面(下面、実装面)9yを有し、樹脂封止体9の平面サイズ(外形サイズ)は、半導体チップ2の平面サイズ(外形サイズ)よりも大きくなっている。

#### 【0030】

10

20

30

40

50

樹脂封止体9は、低応力化を図る目的として、例えば、フェノール系硬化剤、シリコーンゴム及びフィラー等が添加されたビフェニール系の熱硬化性樹脂で形成されている。樹脂封止体9の形成方法としては、大量生産に好適なトランスファモールディング法を用いている。トランスファ・モールディング法は、ポット、ランナ、樹脂注入ゲート、及びキャビティ等を備えた成形金型（モールド金型）を使用し、ポットからランナ及び樹脂注入ゲートを通してキャビティの内部に熱硬化性樹脂を注入して樹脂封止体を形成する方法である。

【0031】

ここで、樹脂封止型半導体装置の製造においては、複数の製品形成領域（デバイス形成領域）を有するリードフレームを使用し、各製品形成領域に搭載された半導体チップを各製品形成領域毎に樹脂封止する個別方式のトランスファモールディング法や、複数の製品形成領域を有するリードフレームを使用し、各製品形成領域に搭載された半導体チップを一括して樹脂封止する一括方式のトランスファモールディング法が採用されている。本実施例1では、例えば一括方式のトランスファモールディング法を採用している。一括方式のトランスファモールディング法の場合、樹脂封止体を形成した後、リードフレーム及び樹脂封止体は、例えばダイシングによって複数の小片（個片）に分割される。

【0032】

複数のリード5は、半導体チップ2の4つの辺に対応して4つのリード列（リード群）に分かれて配置されており、各リード列の複数のリード5は、対応する半導体チップ2の辺に沿って一列で配置されている。各リード列の長さは、半導体チップ2の辺の長さよりも小さくなっている。

【0033】

各リード列（各リード群）において、複数のリード5は、各々の先端部が半導体チップ2の裏面と平面的に重なるようにして半導体チップ2の辺に沿って配置されている。また、複数のリード5は、半導体チップ2の裏面から樹脂封止体9の辺（外周辺）に向かって真っ直ぐ延在し、樹脂封止体9の側面9zで終端している。また、複数のリード5は、半導体チップ2側における一端部（先端部）と樹脂封止体9の辺側（側面9z側）における他端部との配列ピッチが設計値で同一になっている。

【0034】

なお、リード5の一端部と他端部との配列ピッチに関しては、あくまでも設計値であり、実際の寸法は加工精度のバラツキ等により若干ずれることは言うまでもない。

【0035】

チップ搭載部4は、半導体チップ2の平面サイズよりも小さい平面サイズで形成されている。本実施例1のチップ搭載部4は、これに限定されないが、その厚さ方向と交差する平面形状が例えば方形形状になっており、半導体チップ2の平面サイズ（4mm×4mm）に対して、例えば2mm×2mmの正方形（長方形）になっている。

【0036】

チップ搭載部4は、互いに反対側に位置する主面及び裏面を有し、その主面には接着材7を介在して半導体チップ2の裏面が接着されている。チップ搭載部4の裏面は、図3に示すように、樹脂封止体9の裏面9yから露出されている（換言すれば、樹脂で覆われていない）。また、チップ搭載部4の平面サイズは、半導体チップ2の平面サイズよりも小さいため、半導体チップ2の裏面の一部は、チップ搭載部4から露出されている（換言すれば、チップ搭載部で覆われていない）。

【0037】

2本の吊りリード6（6a, 6b）は、各々の一端部が半導体チップ2の裏面と平面的に重なるようにしてチップ搭載部4と一体的に連なっている。また、2本の吊りリード6（6a, 6b）は、チップ搭載部4から樹脂封止体9の辺に向かって真っ直ぐ延在し、樹脂封止体9の側面9zで終端している。本実施例1において、2本の吊りリード6（6a, 6b）は、チップ搭載部4を境にして互いに反対側に位置し、一方の吊りリード6aは、チップ搭載部4から樹脂封止体9の第1の辺に向かって延在し、他方の吊りリード6b

10

20

30

40

50

は、チップ搭載部4から樹脂封止体9の第1の辺と反対側の第2の辺に向かって延在している。また、後で詳細に説明するが、2本の吊りリード6(6a, 6b)は、各々の延在方向が樹脂封止工程において成形金型のキャビティに注入される樹脂の注入方向に沿うようにして配置されている。

【0038】

半導体チップ2の複数の電極パッド3と、複数のリード5は、複数のボンディングワイヤ8によって夫々電気的に接続されている。ボンディングワイヤ8の一端部は、半導体チップ2の電極パッド3に接続され、ボンディングワイヤ8の一端部と反対側の他端部は、半導体チップ2の周囲(外側)においてリード5と接続されている。ボンディングワイヤ8としては、例えば金(Au)ワイヤが用いられている。ボンディングワイヤ8の接続方法としては、例えば熱圧着に超音波振動を併用したネイルヘッドボンディング(ボールボンディング)法が用いられている。

【0039】

2本の吊りリード6(6a, 6b)の各々は、ボンディングワイヤ8aを介して半導体チップ2の電極パッド3と電気的に接続されている。ボンディングワイヤ8aの一端部は、半導体チップ2の電極パッド3と接続され、ボンディングワイヤ8aの一端部と反対側の他端部は、半導体チップ2の周囲(外側)において吊りリード6と接続されている。本実施例1において、複数のボンディングワイヤ8は、半導体チップ2の電極パッド3と一方の吊りリード6aとを電気的に接続するボンディングワイヤ8a、並びに半導体チップ2の電極パッド3と他方の吊りリード6bとを電気的に接続するボンディングワイヤ8aを含んでいる。

【0040】

図4に示すように、複数のリード5の各々は、第1の先端面5m1と、この第1の先端面5m1と反対側の第2の先端面(切断面)5m2とを有し、第1の先端面5m1は、半導体チップ2の裏面と平面的に重なるようにしてその裏面下に位置し、第2の先端面5m2は、樹脂封止体9の側面9zとほぼ同一面に位置している。第2の先端面5m2は、半導体装置の製造において、一括方式のトランスファモールディング法に基づいてリードフレームの主面側に樹脂封止体を形成した後、樹脂封止体及びリードフレームを複数の小片(個片)に分割することによって形成される。

【0041】

複数のリード5の各々は、ボンディングワイヤ8が接続される第1の面5x1と、この第1の面5x1の反対側に位置し、かつ樹脂封止体9の裏面9yから露出する(換言すれば、樹脂で覆われない)第2の面5yと、第2の面5yの反対側に位置し、かつ第1の面5x1よりも第2の面5y側に位置する第3の面5x2とを有する構成になっている。複数のリード5は、樹脂封止体9から裏面9y側に抜け落ちないように、図2に示すように、第1の面5x1の一部の幅が第2の面5yの幅よりも大きく形成されている。これにより、樹脂封止体9の裏面9yから露出する複数のリード5それぞれの形状は、例えば長方形となっている。

【0042】

第3の面5x2、及び第1の面5x1は、この順番で第1の先端面5m1から第2の先端面5m2に向かって配置、換言すれば半導体チップ2側から樹脂封止体9の外周辺(側面9z)に向かって配置されている。第3の面5x2は、第1の先端面5m1に連なり、第1の面5x1は第2の先端面5m2に連なり、第2の面5yは第1及び第2の先端面5m1, 5m2に連なっている。

【0043】

即ち、本実施例1のリード5は、第1の面5x1、第2の面5y、及び第2の先端面5m2を含む第1の部分5R1と、第3の面5x2、第2の面5y、及び第1の先端面5m1を含み、かつ第1の部分5R1よりも厚さが薄い第2の部分5R2とを有する構成になっている。

【0044】

10

20

30

40

50

リード 5 は、第 3 の面  $5 \times 2$  の一部（第 2 の部分  $5 R 2$  の一部）が半導体チップ 2 の裏面と平面的に重なり、かつ半導体チップ 2 の裏面から離間して配置されている。第 3 の面  $5 \times 2$  の一部と半導体チップ 2 の裏面との間には樹脂封止体 9 の樹脂が設けられており、リード 5 と半導体チップ 2 は絶縁分離されている。

【0045】

樹脂封止体 9 の裏面  $9 y$  から露出する複数のリード 5 それぞれの第 2 の部分  $5 y$  は、後に外部接続用端子として使用される。ここで、外部接続用端子の長さが短くなると、配線基板に半導体装置を半田付け実装する時、配線基板の電極パッド（ランド）と半導体装置の外部接続用端子との接合面積が小さくなり、両者の接合強度が低下するため、配線基板から半導体装置が剥がれるといった実装不良が発生する可能性が高くなる。そのため、接合強度を確保するために、樹脂封止体 9 の裏面  $9 y$  から露出する複数のリード 5 の第 2 の部分  $5 y$  の長さ（面積）は短く（小さく）形成することができない。しかし、半導体装置の小型化に伴い、半導体チップ 2 の端部と複数のリード 5 それぞれの端部の間隔が狭いため、接触する可能性がある。そこで、本実施例では、複数のリード 5 それぞれに第 3 の面  $5 \times 2$  を形成している。更に、単に接合強度を確保するだけなら、第 2 の部分  $5 y$  の長さ（面積）を長く（大きく）すればよいが、半導体装置を実装する配線基板側に形成される電極の長さ（面積）も長く（大きく）する必要がある。しかしながら、配線基板側に形成される電極の長さ（面積）も長く（大きく）すると、配線基板の主面上に形成する配線パターンの引き回しが困難となる。そこで、第 2 の部分  $5 y$  は、少なくとも接合強度が確保できる長さ（面積）に形成することが好ましい。

【0046】

図 5 に示すように、2 本の吊りリード 6 は、一端部とは反対側の他端部に、樹脂封止体 9 の側面  $9 z$  と同一面に位置する先端面（切断面） $6 m 2$  を有している。この先端面  $6 m 2$  は、半導体装置の製造において、一括方式のトランスマーチャンジング法に基づいてリードフレームの主面側に樹脂封止体を形成した後、樹脂封止体及びリードフレームを複数の小片（個片）に分割することによって形成される。

【0047】

2 本の吊りリード 6 は、樹脂封止体 9 の内部に位置する（換言すれば、樹脂で覆われた）第 1 の面  $6 x$  と、この第 1 の面  $6 x$  の反対側に位置し、かつ樹脂封止体 9 の裏面  $9 y$  から露出する（換言すれば、樹脂で覆われない）第 2 の面  $6 y 1$  と、第 1 の面  $6 x$  の反対側に位置し、かつ第 2 の面  $6 y 1$  よりも第 1 の面  $6 x$  側に位置し、かつ樹脂封止体 9 の内部に位置する第 3 の面  $6 y 2$  とを有する構成になっている。

【0048】

第 3 の面  $6 y 2$ 、及び第 2 の面  $6 y 1$  は、この順番でチップ搭載部 4 側から樹脂封止体 9 の外周辺（側面  $9 z$ ）に向かって配置されている。第 1 の面  $6 x$  は、チップ搭載部 4 の主面及び先端面  $6 m 2$  に連なり、第 2 の面  $6 y 1$  は、先端面  $6 m 2$  に連なり、第 3 の面  $6 y 2$  は、チップ搭載部 4 の側面に連なっている。

【0049】

即ち、本実施例 1 の吊りリード 6 は、第 1 の面  $6 x$ 、第 2 の面  $6 y 1$ 、及び先端面  $6 m 2$  を含む第 1 の部分  $6 R 1$  と、第 1 の面  $6 x$ 、及び第 3 の面  $6 y 2$  を含み、かつ第 1 の部分よりも厚さが薄い第 2 の部分  $6 R 2$  とを有する構成になっている。

【0050】

第 1 の部分よりも厚さが薄い第 2 の部分  $6 R 2$  を形成する理由として、複数のリード 5 の第 2 の部分  $5 y$  と同様に、接合強度を確保しながら、配線基板の主面上に形成する配線パターンの引き回しを容易とするためである。第 2 の面  $6 y 1$  の長さ（面積、形状）は、複数のリード 5 の第 2 の部分  $5 y$  とほぼ同じ長さ（面積、形状）で形成されている。

【0051】

2 本の吊りリード 6 には、チップ搭載部 4 をリード 5 よりも上方に位置させるためのオフセット加工が施されておらず、複数のリード 5、2 本の吊りリード 6、及びチップ搭載部 4 は、同一平面内に位置し、高さ方向の位置がフラットになっている。更に説明すると

10

20

30

40

50

、複数のリード 5 の第 1 の面  $5 \times 1$  、 2 本の吊りリード 6 の第 1 の面  $6 \times$  、及びチップ搭載部 4 の主面は、同一平面内に位置し、高さ方向の位置がフラットになっている。

なお、本実施例 1 において、ボンディングワイヤ 8 a の他端部は、吊りリード 6 の第 1 の面  $6 \times$  に接続されている。

#### 【 0 0 5 2 】

図 4 及び図 5 に示すように、複数のリード 5 の各々の第 2 の面  $5 y$  、及び 2 本の吊りリード 6 の各々の第 2 の面  $6 y 1$  には、これらの第 2 の面を覆うようにして夫タメッキ層 15 が形成されている。メッキ層 15 は、例えば錫系の鉛フリー半田メッキ膜からなり、配線基板に半導体装置を半田付け実装する時の半田濡れ性を確保する目的で設けられている。

10

#### 【 0 0 5 3 】

リード 5 の第 2 の面  $5 y$  、及び吊りリード 6 の第 2 の面  $6 y 1$  は、樹脂封止体 9 の裏面  $9 y$  から露出され、外部接続用端子として使用されている。即ち、本実施例 1 の QFN 型半導体装置 1 は、図 3 に示すように、複数のリード 5 の各々の一部、並びに 2 本の吊りリード 6 の各々の一部を樹脂封止体 9 の裏面  $9 y$  から露出することによって得られる複数の外部接続用端子を有する構成になっている。

#### 【 0 0 5 4 】

なお、図 4 及び図 5 に示すように、チップ搭載部 4 の裏面にも、この裏面を覆うようにしてメッキ層 15 が形成されている。チップ搭載部 4 は、配線基板に半導体装置を半田付け実装する時、配線基板に半田付けしても良いし、しなくても良い。チップ搭載部 4 を配線基板に半田付けする場合、集積回路の動作によって半導体チップ 2 で発生した熱を配線基板に効率良く伝達することができるため、半導体装置の放熱性向上を図ることができる。また、配線基板と半導体装置との接着強度向上を図るために、配線基板から半導体装置が剥がれるといった実装不良を抑制することもできる。

20

#### 【 0 0 5 5 】

次に、半導体装置 1 の製造に使用されるリードフレームについて、図 6 乃至図 9 を用いて説明する。

#### 【 0 0 5 6 】

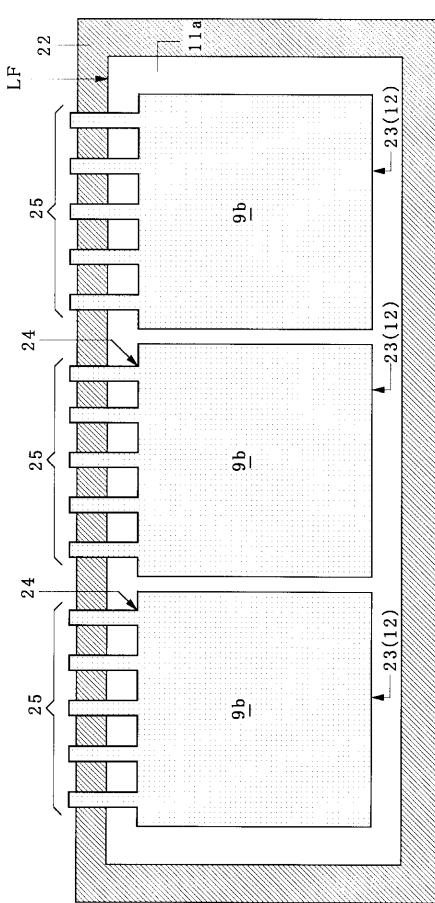

図 6 ( ( a ) , ( b ) ) 及び図 7 に示すように、リードフレーム LF は、厚さ方向と交差する平面形状が例えば長方形になっている。リードフレーム LF は、メインフレーム 11 a 及びサブフレーム 11 b を含むフレーム本体 11 と、メインフレーム 11 a で区画され、かつ長手方向に沿って配置された複数の樹脂封止領域 12 とを有し、各樹脂封止領域 12 には、サブフレーム 11 b によって区画された複数の製品形成領域 13 が行列状に配置されている。本実施例 1 において、樹脂封止領域 12 は例えば 3 つ設けられ、各樹脂封止領域 12 には例えば  $5 \times 5$  の行列配置で複数の製品形成領域 13 が設けられている。各樹脂封止領域 12 には、各々の樹脂封止領域 12 に設けられた複数の製品形成領域 13 を一括して樹脂封止する樹脂封止体が形成される。

30

#### 【 0 0 5 7 】

各製品形成領域 13 は、平面が方形状になっている。各製品形成領域 13 には、図 8 に示すように、複数のリード 5 、 2 本の吊りリード 6 、及びチップ搭載部 4 が配置されている。複数のリード 5 は 4 つのリード列 (リード群) に分かれて製品形成領域 13 の各辺毎に配置されている。

40

#### 【 0 0 5 8 】

チップ搭載部 4 は、製品形成領域 13 の中央に配置され、半導体チップ 2 の平面サイズよりも小さい平面サイズで形成されている。チップ搭載部 4 は、2 本の吊りリード 6 を介してフレーム本体 11 に支持されている。

#### 【 0 0 5 9 】

各リード列 (リード群) の長さは、チップ搭載部 4 に搭載される半導体チップ 2 の辺の長さよりも小さくなっている。各リード列の複数のリード 5 は、チップ搭載部 4 に半導体チップ 2 を搭載した時、各々の一端部 (先端部) が半導体チップ 2 の裏面と平面的に重な

50

るようにして半導体チップ2の辺に沿って配置され、更に半導体チップ2の裏面から製品形成領域13の辺に向かって真っ直ぐ延在している。各リード列の複数のリード5は、先端部と反対側の他端部がフレーム本体11と一体的に連なり、フレーム本体11に支持されている。また、各リード列の複数のリード5は、半導体チップ2側(チップ搭載部4側)における一端部(先端部)と、製品形成領域13の辺側における他端部とが設計値で同一の配列ピッチになっている。

【0060】

2本の吊りリード6の各々は、一端部側がチップ搭載部4と一体的に連なり、一端部側と反対側の他端部側がフレーム本体11と一体的に連なり、チップ搭載部4と共にフレーム本体11に支持されている。また、2本の吊りリード6の各々は、チップ搭載部4から製品形成領域13の辺に向かって真っ直ぐ延在し、チップ搭載部4に半導体チップ2を搭載した時、半導体チップ2の角部を通る(横切る)位置ではなく、半導体チップ2の辺を通る(横切る)位置に配置されている。

【0061】

本実施例1において、2本の吊りリード6(6a, 6b)は、チップ搭載部4を境にして互いに反対側に位置し、一方の吊りリード6aは、チップ搭載部4から製品形成領域13の第1の辺に向かって延在し、他方の吊りリード6bは、チップ搭載部4から製品形成領域13の第1の辺と反対側の第2の辺に向かって延在している。また、後で詳細に説明するが、2本の吊りリード6(6a, 6b)は、各々の延在方向が樹脂封止工程において成形金型の封止用キャビティに注入される樹脂の注入方向S1に沿うようにして配置されている。

【0062】

2本の吊りリード6には、チップ搭載部4をリード5よりも上方に位置させるためのオフセット加工が施されておらず、複数のリード5、2本の吊りリード6、チップ搭載部4、及びフレーム本体11は、同一平面内に位置し、高さ方向の位置がフラットになっている。

【0063】

なお、図6のリードフレームLFの状態におけるリード5、及び吊りリード6は、図4及び図5のパッケージングされた状態におけるリード5、及び吊りリード6に対して、切断面(先端面5m2, 6m2)を除いて同様の形状になっているため、詳細な形状については説明を省略する。

【0064】

このように構成されたリードフレームLFは、Cu(銅)、又はCu系合金、又はFi(鉄)-Ni(ニッケル)系合金等からなる金属板に、エッチング加工、又はプレス加工、又はエッティング加工及びプレス加工を施して所定のリードパターンを形成することによって製造される。

【0065】

リードフレームLFは、図9((a), (b))に示すように、樹脂封止体が形成される主面と反対側の裏面にバックテープ16が貼り付けられている。バックテープ16は、リードフレームLFの製品形成領域13を覆うようにして、フレーム本体11、複数のリード5、2本の吊りリード6、及びチップ搭載部4の各々の裏面に貼り付けられている。バックテープ16としては、例えばポリイミド樹脂からなる樹脂基材の一表面に接着層が設けられた可撓性テープが用いられている。フレーム本体11、複数のリード5、2本の吊りリード6、及びチップ搭載部4は、バックテープ16の接着層によってバックテープ16に接着固定されている。

【0066】

なお、バックテープ16は、リードフレームLFの主面に樹脂封止体を形成した後、リードフレームLFから剥がされて取り除かれる。従って、バックテープ16の接着層としては、リードフレームLFからバックテープ16を剥離する前の段階において、リードフレームLFからバックテープ16が容易に剥がれない程度の接着力を有し、リードフレー

10

20

30

40

50

ム LF からバックテープ 16 を剥離する工程において、リードフレーム LF からバックテープ 16 が容易に剥がれる程度の接着力を有することが望ましい。

【0067】

次に、半導体装置 1 の製造に使用される成形金型について、図 13 及び図 14 を用いて説明する。なお、成形金型の構成については、成形金型の上型と下型との間にリードフレームを位置決めして型締めした状態で説明する。

【0068】

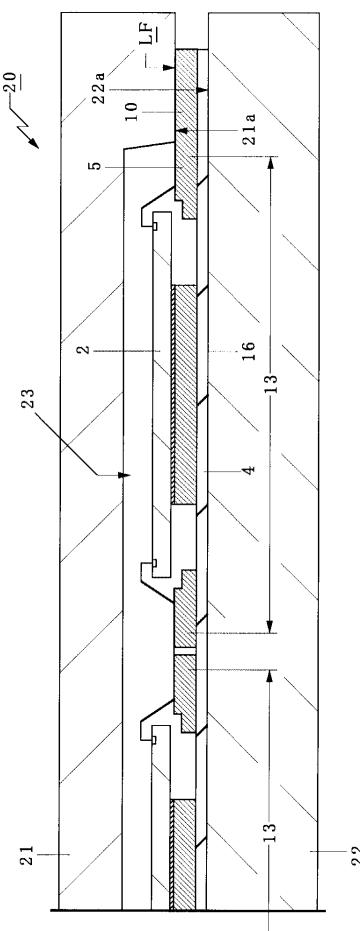

図 13 に示すように、成形金型 20 は、上下方向に重ね合う上型 21 及び下型 22 を有し、更に樹脂封止体を形成するための封止用キャビティ（樹脂封止体形成部）23 等を有する構成になっている。リードフレーム LF は、上型 21 の狭持面（合わせ面）21a と下型 22 の狭持面（合わせ面）22aとの間に配置され、上型 21 と下型 22 とを型締めしたと時の型締め力によって狭持固定される。

【0069】

封止用キャビティ 23 は、リードフレーム LF の樹脂封止領域 12 に対応して設けられ、本実施例 1 では例えれば 3 つ設けられている。各封止用キャビティ 23 は、例えは上型 21 側に設けられ、上型 21 の狭持面 21a よりも深さ方向に窪む凹部で構成されている。

【0070】

各封止用キャビティ 23 は、リードフレーム LF の主面上に位置し、対応する樹脂封止領域 12 の複数の製品形成領域 13 を一括して覆う大きさ（平面サイズ）で形成されている。各封止用キャビティ 23 の平面形状は方形形状になっており、本実施例 1 では樹脂封止領域 12 の平面形状に対応して例えれば長方形になっている。

【0071】

各封止用キャビティ 23 には、図 14 に示すように、複数のランナ 25 が夫々樹脂注入ゲート 24 を介して連結されている。複数のランナ 25 は、封止用キャビティ 23 の互いに反対側に位置する 2 つの辺のうちの一方の辺側にこの一方の辺に沿って配置されている。複数のランナ 25 は、図示していないが、樹脂タブレットが投入されるポットに連結されている。ランナ 25 は、ポットから封止用キャビティ 23 に樹脂を流すための樹脂流路であり、樹脂注入ゲート 24 は、封止用キャビティ 23 に注入される樹脂の入り口であって流量を制御するためのものである。ランナ 25 は、封止用キャビティ 23 と同様に上型 21 側に設けられ、上型 21 の狭持面 21a よりも深さ方向に窪む凹部で構成されている。

【0072】

次に、半導体装置 1 の製造について、図 10 乃至図 17 を用いて説明する。

【0073】

まず、図 6 乃至図 9 に示すリードフレーム LF を準備する。リードフレーム LF の裏面には、予めバックテープ 16 が貼り付けられている。

【0074】

次に、リードフレーム LF の各製品形成領域 13 において、図 11 ((a), (b)) に示すように、チップ搭載部 4 の正面に半導体チップ 2 を搭載する（図 10 のダイボンディング工程 101）。半導体チップ 2 の搭載は、チップ搭載部 4 の正面に接着材 7 を介在して半導体チップ 2 の裏面を接着固定することによって行われる。

【0075】

この工程において、各リード列（リード群）の長さは、半導体チップ 2 の辺の長さよりも小さくなっている。また、各リード列の複数のリード 5 は、各々の一端部（先端部）が半導体チップ 2 の裏面と平面的に重なるようにして半導体チップ 2 の辺に沿って配置され、更に半導体チップ 2 の裏面から製品形成領域 13 の辺に向かって真っ直ぐ延在している。また、各リード列の複数のリード 5 は、半導体チップ 2 側（チップ搭載部 4 側）における一端部（先端部）と、製品形成領域 13 の辺側における他端部とが設計値で同一の配列ピッチになっている。

【0076】

10

20

30

40

50

2本の吊りリード6の各々は、チップ搭載部4から製品形成領域13の辺に向かって真っ直ぐ延在し、半導体チップ2の角部を通る（横切る）位置ではなく、半導体チップ2の辺を通る（横切る）位置に配置されている。

#### 【0077】

次に、リードフレームLFの各製品形成領域13において、図12((a),(b))に示すように、半導体チップ2の複数の電極パッド3と、複数のリード5及び2本の吊りリード6とを複数のボンディングワイヤ8で夫々電気的に接続する（図10のワイヤボンディング工程102）。

#### 【0078】

次に、図13に示すように、成形金型20の上型21と下型22との間にリードフレームLFを位置決めして型締めする（図10の樹脂封止工程103）。

リードフレームLFの型締めは、リードフレームLFと下型22の狭持面22aとの間にバックテープ16が位置する状態で行われる。

また、リードフレームLFの型締めは、リードフレームLFの各樹脂封止領域12に対応して上型21に設けられた各封止用キャビティ23の内部に、各樹脂封止領域12の複数の製品形成領域13が位置する状態で行われる。

また、リードフレームLFの型締めは、リードフレームLFの樹脂封止領域12を区画するフレーム本体11及びこのフレーム本体11の裏面に位置するバックテープ16を上型21の狭持面21a及び下型22の狭持面22aで上下方向から挟み込むことによって行われる。

#### 【0079】

次に、図13に示すようにリードフレームLFを型締めした状態で、図14に示すように、ポットからランナ25及び樹脂注入ゲート24を通して封止用キャビティ23の内部に流動性の樹脂（熱硬化性樹脂）9aを加圧注入し、その後、樹脂9aを硬化させて図15に示すように樹脂封止体9bを形成する（図10の樹脂封止工程103）。樹脂封止体9bは、リードフレームLFの3つの樹脂封止領域12に対応して3つ形成される。1つの樹脂封止領域12において、複数の製品形成領域13、並びに各製品形成領域13における半導体チップ2、チップ搭載部4、複数のリード5、2本の吊りリード6及び複数のボンディングワイヤ8等は、一括して1つの樹脂封止体9bによって樹脂封止される。

#### 【0080】

この工程において、各製品形成領域13のチップ搭載部4、リード5、及び吊りリード6の各々の裏面は、バックテープ16に接着されているため、これらの裏面がレジンバリ（レジンフラッシュ）によって覆われてしまうといった不具合の発生を抑制することができる。

#### 【0081】

また、この工程において、チップ搭載部4の裏面、リード5の第2の面5y、及び吊りリード6の第2の面6y1が樹脂封止体9bの裏面から露出する。

#### 【0082】

次に、樹脂封止体9bの硬化を安定させるキュア工程を施した後、成形金型20を型開きして、成形金型20からリードフレームLFを取り出す。

#### 【0083】

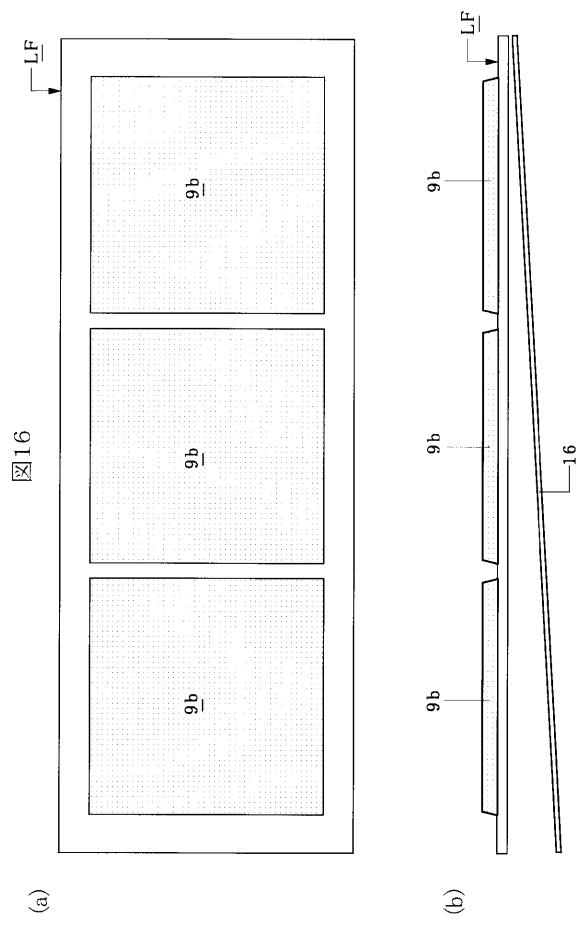

次に、図16((a),(b))に示すように、リードフレームLFの裏面に貼り付けられたバックテープ16を剥離する（図10のバックテープ剥離工程104）。

#### 【0084】

次に、樹脂封止体9bの裏面から露出する、リード5の第2の面5y（図4参照）、吊りリード6の第2の面6y1（図5参照）、及びチップ搭載部4の裏面（図4及び図5参照）に、これらの面を覆うようにして夫々メッキ層15を形成する（図10のメッキ工程105）。メッキ層15は、例えば錫系の鉛フリー半田メッキ膜からなり、配線基板に半導体装置を半田付け実装する時の半田濡れ性を確保する目的で形成される。メッキ層

10

20

30

40

50

15の形成は、例えば大量生産に好適な電界メッキ法で行われる。

【0085】

次に、リードフレームLFの各製品形成領域13に対応して各々の樹脂封止体9bの上面に、例えば品名、社名、品種、製造ロット番号等の識別マークを、インクジェットマーキング法、ダイレクト印刷法、レーザマーキング法等を用いて形成する(図10のマーキング工程106)。

【0086】

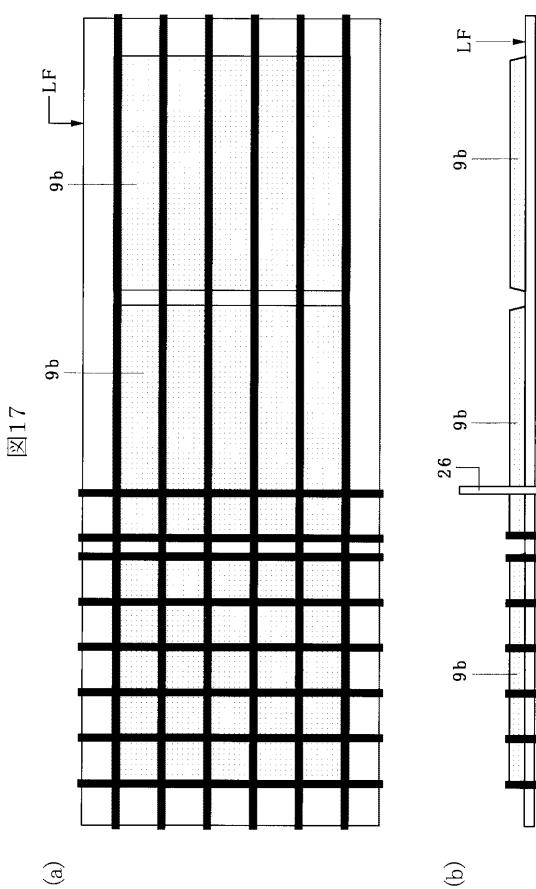

次に、図17に示すように、各々の樹脂封止体9b及びリードフレームLFを各製品形成領域13に対応して複数の小片(個片)に分割する(図10の小片化工程107)。この分割は、例えば、図17に示すように、リードフレームLFの各製品形成領域13を区画するダイシングラインに沿ってリードフレームLF及び樹脂封止体9bをダイシングブレード26でダイシングすることによって行われる。この工程により、図1に示すQFN型半導体装置1がほぼ完成する。

【0087】

ところで、QFN型半導体装置の小型化は、半導体チップ2の辺に沿って配置される複数のリード5からなるリード列の長さを半導体チップ2の辺の長さよりも小さくし、半導体チップ2の辺に出来るだけリード5を近づけることによって実現できる。また、本実施例1のように、各々の先端部が半導体チップ2の裏面と平面的に重なるようにして半導体チップ2の辺に沿って複数のリード5を配置することによって更に小型化を実現できる。

【0088】

このようにしてQFN型半導体装置の小型化を実現するためには、チップ搭載部4に連なる吊りリード6の配置を工夫する必要がある。

【0089】

従来のQFN型半導体装置では、図20に示すように、チップ搭載部34に連なる4本の吊りリード36が、チップ搭載部34から樹脂封止体39の角部39sに向かって放射状に延在し、半導体チップ32の角部32sに配置されている。即ち、4本の吊りリード36は、リード35の延在方向に対して鋭角となる角度で斜めになって半導体チップ32の角部32sに配置されている。

【0090】

このような吊りリード36の配置では、半導体チップ32の辺に沿って配置された複数のリード35を半導体チップ32の辺に向かって近づけると、吊りリード36と、この吊りリード36に隣接するリード35aの先端部との間隔が狭くなり、吊りリード36にリード35aが干渉し易くなるため、吊りリード36とリード35aとの干渉を考慮すると、吊りリード36から半導体チップ32の辺に沿ってリード35aを遠ざける必要があり、半導体チップ32の角部32s付近にリード35を設置することが困難となる。半導体チップ32の角部32s付近にリード35を設置できない非リード設置領域LNは、1本の吊りリード36に対して2箇所発生するため、4本の吊りリード36で合計8本のリード35が設置できなくなる。

【0091】

特に、図21に示すように、各々の先端部が半導体チップ32の裏面と重なるように半導体チップ32の辺に沿って複数のリード35を配置する場合においては、吊りリード36から半導体チップ32の辺に沿ってリード35aを更に遠ざける必要があり、半導体チップ32の角部32s付近へのリード設置が更に困難となる。

【0092】

これに対して、本実施例1のQFN型半導体装置1では、図1(a)及び図2に示すように、チップ搭載部4に連なる2本の吊りリード6が、リード5の延在方向に沿ってチップ搭載部4から樹脂封止体9の辺(外周辺)に向かって真っ直ぐ延在し、半導体チップ2の角部2sを避けて配置されている。

【0093】

このような構成にすることにより、半導体チップ2の辺に沿って配置された複数のリード

10

20

30

40

50

ド5を半導体チップ2の辺に近づけても、また、本実施例1のように各々の先端部が半導体チップ2の裏面と重なるように半導体チップ2の辺に沿って複数のリード5を配置しても、リード5が吊りリード6と接触する恐れが無いため、半導体チップ2の角部2s付近にリード5(5a)を設置することができる。本実施例1では、半導体チップ2の1つの角部2sに対して2本のリード5(5a)を設置でき、半導体チップ2の4つの角部2sで合計8本のリード5(5a)を設置できる。

【0094】

ここで、本実施例1のように吊りリード6を配置すると、1本の吊りリード6に対して1本のリード5が設置できなくなるため、有効リード(半導体チップの電極パッドと外部との電気的な接続を仲介するリード)の本数増加は、半導体チップ2の角部2s付近の設置本数(4箇所×2本)から吊りリード6の本数(本実施例1では2本)を引いた数となる。

10

【0095】

しかしながら、本実施例1のように、半導体チップ2の電極パッド3と吊りリード6とをボンディングワイヤ8aで接続し、吊りリード6を有効リード(リード5)として使用することにより、吊りリード6による有効リードの本数削減を抑制できる。本実施例1では、2本の吊りリード6を有効リード(リード5)として使用しているため、半導体チップ2の角部2s付近の設置本数(4箇所×2本)がそのまま有効リードの本数増加(8本)となる。

【0096】

20

従って、本実施例1によれば、QFN型半導体装置1の小型化及び多ピン化を実現することができる。

なお、半導体チップ2の電極パッド3と吊りリード6とをボンディングワイヤ8aで電気的に接続せず、吊りリード6を有効リード(リード5)として使用しなくても、吊りリード6の本数が7本までなら有効リードの本数増加となる。

【0097】

また、吊りリード6を有効リードとして使用する場合、半導体チップ2とチップ搭載部4とを電気的に分離する必要がある場合は、接着材7として絶縁性のものを使用する。

【0098】

また、本実施例1では、1つのチップ搭載部4に2本の吊りリード6が連なっている。この場合、2本の吊りリード6を機能が異なる有効リードとして使用することができないので、2本の吊りリード6は、多機能化や高速化に伴って本数の増加要求が高い電源用リードとして使用することが望ましい。

30

【0099】

QFN型半導体装置1の小型化は、リード5の長さを短くし、半導体チップ2の側面と樹脂封止体9の側面9zとの間の距離を短くすることによって実現できる。しかしながら、リード5の長さを短くすると、樹脂封止体9の裏面からリード5の一部を露出することによって得られる外部接続用端子の長さも短くなってしまう。外部接続用端子の長さが短くなると、配線基板に半導体装置を半田付け実装する時、配線基板の電極パッド(ランド)と半導体装置の外部接続用端子との接合面積が小さくなり、両者の接合強度が低下するため、配線基板から半導体装置が剥がれるといった実装不良が発生する可能性が高くなる。半導体装置の実装信頼性を確保するには、外部接続用端子の長さが最低でも0.45mm程度必要とされる。本実施例1では、各々の先端部が半導体チップ2の裏面と平面的に重なるように半導体チップ2の辺に沿って複数のリード5を配置しているため、半導体装置の実装信頼性の確保に必要なリード5の長さを確保しつつ小型化を実現できる。従って、本実施例1のQFN型半導体装置1においては、実装信頼性を確保しつつ小型化及び多ピン化を実現することができる。

40

【0100】

従来のQFN型半導体装置には、図20に示すように、チップ搭載部に連なる吊りリード36が4本設けられている。有効リードの本数を増加するには、出来るだけ吊りリード

50

の本数を少なくすることが有効である。しかしながら、吊りリードの本数を少なくすると、樹脂封止工程において、成形金型の封止用キャビティに注入された樹脂の流動によってチップ搭載部が変動し易くなり、樹脂の未充填や、樹脂封止体から半導体チップ並びにボンディングワイヤ等が露出するといった不具合の要因となるため、半導体装置の製造歩留まりが低下してしまう。

#### 【0101】

これに対し、本実施例1では、樹脂封止工程（図10の103）において、図13に示すように、バックテープ16にチップ搭載部4を接着固定しているため、吊りリード6を2本にしても、成形金型20のキャビティ23に注入された樹脂9aの流動によるチップ搭載部4の変動を抑制することができる。従って、本実施例1においては、有効リードの本数を増加するために、吊りリード6の本数を少なくしても、QFN型半導体装置1の製造歩留まり低下を抑制することができる。10

#### 【0102】

バックテープ16にチップ搭載部6を接着固定することにより、吊りリード6が無くても、成形金型20のキャビティ23に注入された樹脂9aの流動によるチップ搭載部4の変動を抑制できるが、リードフレームLFの製造において、リードフレームLFのフレーム本体11にチップ搭載部4を吊りリード6で支持する必要があるため、有効リードの本数増加を考慮すると、吊りリード6は少なくとも1本あればよい。

#### 【0103】

バックテープ16は、図6乃至図8に示すように、予めリードフレームLFの裏面に貼り付けられている。バックテープ16の使用により、バックテープ16に半導体チップ2を直に接着固定することも可能である。しかしながら、本実施例1では、実装不良の発生を抑制するために樹脂封止体9の裏面から露出される外部接続用端子の長さを確保しながら、半導体装置1の小型化を実現するために、各々の先端部が半導体チップ2の裏面と平面的に重なるように半導体チップ2の辺に沿って複数のリード5を配置した構成を取っている。そのため、チップ搭載部4に半導体チップ2を固定することで、半導体チップ2の裏面がリード5の先端部よりも上側に位置するようにしている。20

#### 【0104】

バックテープ16が貼り付けられたリードフレームLFを使用する場合、バックテープ16のしわを抑制するため、吊りリード6には、チップ搭載部4をリード5よりも上方に位置させるオフセット加工を施さず、リード5、吊りリード6及びチップ搭載部4の高さ位置がフラットになっていることが望ましい。30

#### 【0105】

ここで、トランスファモールディングにおいては、成形金型の上型と下型との間に樹脂シート（樹脂フィルム）を配置し、その後、樹脂シート上にリードフレームを装着して型締めし、その後、成形金型の封止用キャビティに樹脂を加圧注入して樹脂封止体を形成する技術（以下、シートモールディング技術と呼ぶ）が知られている。このシートモールディング技術によれば、リードフレーム及び樹脂シートを上型の狭持面と下型の狭持面とで上下方向から挟み込む狭持力（型締め力）により、リード及びチップ搭載部に樹脂シートを押し付ける力（押圧力）が働き、この押圧力によってリード及びチップ搭載部が樹脂シートに密着するため、リード及びチップ搭載部がレジンバリ（レジンフラッシュ）によって覆われてしまうといった不具合を抑制することができる。40

#### 【0106】

しかしながら、リードフレーム及び樹脂シートは、封止用キャビティの周囲において、上型の狭持面と下型の狭持面とで上下方向から挟み込まれてあり、リード及びチップ搭載部が樹脂シートを押し付ける押圧力は、封止用キャビティの周縁から内側に遠ざかるにつれて弱くなる。リードフレームの各製品形成領域毎に樹脂封止する個別方式のトランスファモールディングでは問題ないが、リードフレームの複数の製品形成領域を一括して樹脂封止する一括方式のトランスファモールディングでは、封止用キャビティの周縁から離れて配置された製品形成領域が存在し、特に封止用キャビティの中央部に配置された製品形

10

20

30

40

50

成領域においては、リード及びチップ搭載部が樹脂シートを押し付ける押圧力が弱くなる。このため、シートモールディング技術でリードフレームの複数の製品形成領域を一括して樹脂封止する場合、リード及びチップ搭載部がレジンバリによって覆われてしまうといった不具合が発生し易くなる。

【0107】

これに対し、バックテープ16が貼り付けられたリードフレームLFでは、複数の製品形成領域の各々において、チップ搭載部4にオフセット加工は施されておらずフラットに形成されている。そのため、リード5及びチップ搭載部4がバックテープ16に貼り付けられているため、樹脂封止工程において、成形金型20の封止用キャビティ23の周縁から内側に向かって離れた製品形成領域13においても、リード5及びチップ搭載部4がレジンバリによって覆われてしまうといった不具合を抑制することができる。10

【0108】

従って、本実施例1のように、リードフレームLFの複数の製品形成領域13を1つの封止用キャビティ23で一括して樹脂封止する場合においては、予めバックテープ16が貼り付けられたリードフレームLFを採用することが望ましく、小型化及び多ピン化に好適なQFP型半導体装置1を高い歩留まりで製造することができる。

【0109】

一括モールディング方式では、封止用キャビティの厚さ（高さ）に対する平面積の比が非常に大きくなるため、熱硬化性樹脂の硬化が始まって流動性が低下するまでの限られた時間の中で、迅速にかつ均一に熱硬化性樹脂を充填する必要がある。迅速にかつ均一に熱硬化性樹脂を充填するには、封止用キャビティの中を流れる熱硬化性樹脂の流動抵抗を低くする必要がある。20

【0110】

図14に示すように、封止用キャビティ23に注入された樹脂9aは、封止用キャビティ23の一辺側（樹脂注入ゲート24が設けられた辺側）からこの一辺とは反対側の他辺側に向かって流れる。本実施例1において、チップ搭載部4に連なる2本の吊りリード6は、樹脂封止工程において、封止用キャビティ23内を封止用キャビティ23の一辺側から他辺側に向かって樹脂9aが流れる方向S2、並びに封止用キャビティ23に注入される樹脂9aの注入方向S1に沿って配置されているため、封止用キャビティ23の中を流れる樹脂9aの流動抵抗が低くなる。このように吊りリード6を配置することにより、迅速にかつ均一に熱樹脂9aを充填することができるため、ボイドの発生を抑制でき、QFN型半導体装置1の製造歩留まり向上を図ることができる。30

【0111】

本実施例1において、図4に示すように、リード5は、第1の部分5R1と、この第1の部分5R1よりも厚さが薄い第2の部分5R2とを有し、第2の部分5R2が半導体チップ2の裏面と平面的に重なるように配置されている。このような構成にすることにより、チップ搭載部4を上方に位置させるオフセット加工を吊りリード6に施さなくても、リード5とチップ搭載部4との干渉を抑制しつつ、先端部が半導体チップ2の裏面と平面的に重なるようにリード5を配置できるため、QFN型半導体装置1の薄型化も実現できる。40

【実施例2】

【0112】

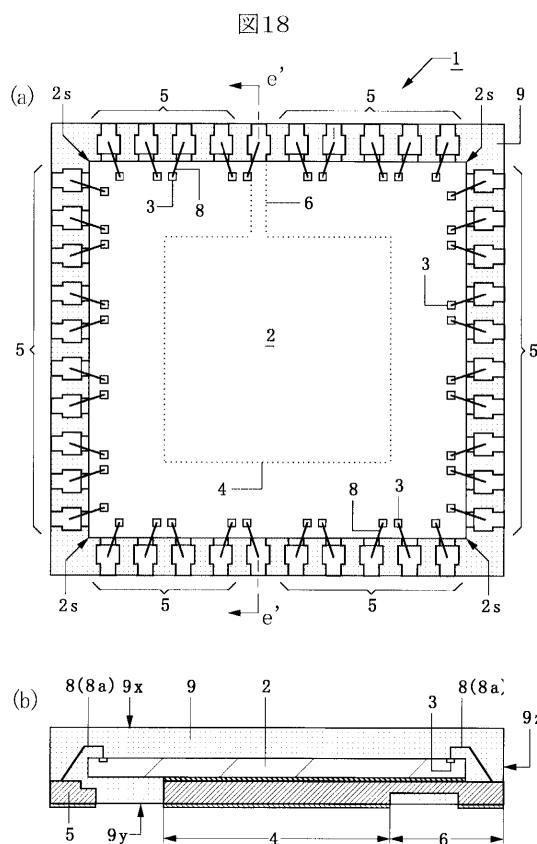

図18は、本発明の実施例2である半導体装置の内部構造を示す図（（a）は模式的平面図、（b）は（a）のe'-e'線に沿う模式的断面図）である。

本実施例2は、図18に示すように、チップ搭載部4に連なる吊りリード6を1本設けた例である。このような構造においても、前述の実施例1と同様の効果が得られる。また、吊りリード6を有効リードとして使用する場合、前述の実施例1と比較して、有効リードの本数が1本増加する。

【実施例3】

【0113】

50

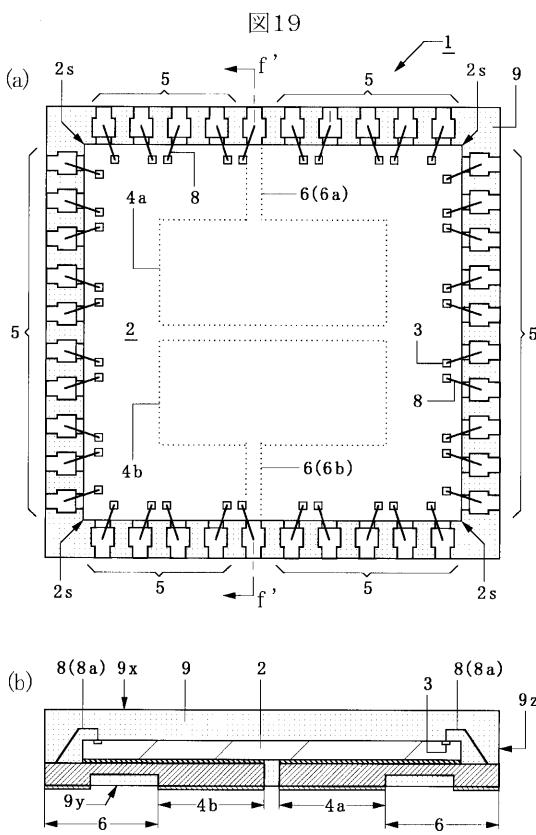

図19は、本発明の実施例3である半導体装置の内部構造を示す図((a)は模式的平面図、(b)は(a)のf'-f'線に沿う模式的断面図)である。

前述の実施例1では、1つのチップ搭載部4に2本の吊りリード6が連なる例について説明したが、本実施例3では、図19に示すように、2つのチップ搭載部(4a, 4b)にそれぞれ1本の吊りリード6(6a, 6b)が連なっている。このような構成により、2本の吊りリード6を機能が異なる有効リードとして使用することができる。例えば吊りリード6aは、信号用リードとして使用し、吊りリード6bは電源用リードとして使用することができる。

【0114】

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。 10

【図面の簡単な説明】

【0115】

【図1】本発明の実施例1である半導体装置の内部構造を示す図((a)は模式的平面図、(b)は(a)のa'-a'線に沿う模式的断面図、(c)は(a)のb'-b'線に沿う模式的断面図)である。

【図2】図1(a)に示す半導体チップ及びボンディングワイヤを省略した模式的平面図である。

【図3】図1の半導体装置の裏面側を示す模式的底面図である。 20

【図4】図1(b)の一部を拡大した模式的断面図である。

【図5】図1(c)の一部を拡大した模式的断面図である。

【図6】本発明の実施例1である半導体装置の製造に使用されるリードフレームの概略構成を示す図((a)は模式的平面図、(b)は模式的側面図)である。

【図7】図6(a)の一部を拡大した模式的平面図である。

【図8】図7の一部を拡大した模式的平面図である。

【図9】図8のc'-c'線に沿う模式的断面図(a)及びd'-d'線に沿う模式的断面図(b)を示す図である。

【図10】本発明の実施例1である半導体装置の製造工程を示すフローチャートである。

【図11】図10のダイボンディング工程を示す図((a)は図8のc'-c'線に沿う位置での模式的断面図、(b)は図8のd'-d'線に沿う位置での模式的断面図)である。 30

【図12】図10のワイヤボンディング工程を示す図((a)は図8のc'-c'線に沿う位置での模式的断面図、(b)は図8のd'-d'線に沿う位置での模式的断面図)である。

【図13】図10の樹脂封止工程を示す図(成形金型にリードフレームを型締めした状態を示す模式的断面図)である。

【図14】成形金型の封止用キャビティに注入された樹脂の流れを示す模式的平面図である。

【図15】成形金型の封止用キャビティに樹脂封止体が形成された状態を透視して示す模式的平面図である。 40

【図16】図10のバックテープ剥離工程を示す図((a)は模式的平面図、(b)は模式的側面図)である。

【図17】図10の小片化(個片化)工程を示す図((a)は模式的平面図、(b)は模式的側面図)である。

【図18】本発明の実施例2である半導体装置の内部構造を示す図((a)は模式的平面図、(b)は(a)のe'-e'線に沿う模式的断面図)である。

【図19】本発明の実施例3である半導体装置の内部構造を示す図((a)は模式的平面図、(b)は(a)のf'-f'線に沿う模式的断面図)である。

【図20】従来の半導体装置の内部構造を示す模式的平面図である。 50

【図21】従来の半導体装置の内部構造を示す模式的平面図である。

## 【符号の説明】

【 0 1 1 6 】

1 … 半導体装置、 2 … 半導体チップ、 3 … 電極パッド（ボンディングパッド）、 4 … チップ支持体（タブ、 ダイパッド）、 5 … リード、 6 … 吊りリード、 7 … 接着材、 8 … ボンディングワイヤ、 9 … 樹脂封止体、 11 … フレーム本体、 11a … メインフレーム、 11b … サブフレーム、 12 … モールディング領域（封止領域）、 13 … 製品形成領域、 15 … メッキ層、 16 … バックテープ、 20 … 成形金型、 21 … 上型、 22 … 下型、 21a … 22a … 狹持面、 23 … 封止用キャビティ（樹脂封止体成形部）、 24 … 樹脂注入ゲート、 25 … ランナ。

10

【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

図10

【図11】

## 【図12】

【図14】

【 図 1 3 】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(56)参考文献 特開2000-299423(JP,A)

特開2005-057067(JP,A)

特開2003-037219(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/50