**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.<sup>7</sup>

G02F 1/136

(45) 공고일자 2005년07월25일

(11) 등록번호 10-0503128

(24) 등록일자 2005년07월14일

---

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2000-0052147 | (65) 공개번호 | 10-2002-0018849 |

| (22) 출원일자 | 2000년09월04일     | (43) 공개일자 | 2002년03월09일     |

---

(73) 특허권자 엘지.필립스 엘시디 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자 채기성

인천광역시연수구동춘동한양1차아파트111동607호

(74) 대리인 특허법인네이트

**심사관 : 임동재**

---

**(54) 액정표시장치용 어레이기판과 그 제조방법**

---

**요약**

본 발명은 액정표시장치용 어레이기판에 관한 것으로, 기판 상에 구성되고, 어레이 제작공정 중 정전기 방지와 함께 배선의 단선 및 단락 테스트를 위해 게이트배선과 연결되어 구성되는 게이트단락배선을 포함하는 어레이기판의 제작공정에 있어서, 장기 게이트 단락배선을 제거하는 과정 중 기판의 절단면에 게이트금속이 존재하지 않도록 어레이기판을 구성하여, 물리적인 충격에 의해 쉽게 들뜨기 쉬운 게이트배선의 접촉불량을 방지 할 수 있다.

**대표도**

도 5

**명세서**

**도면의 간단한 설명**

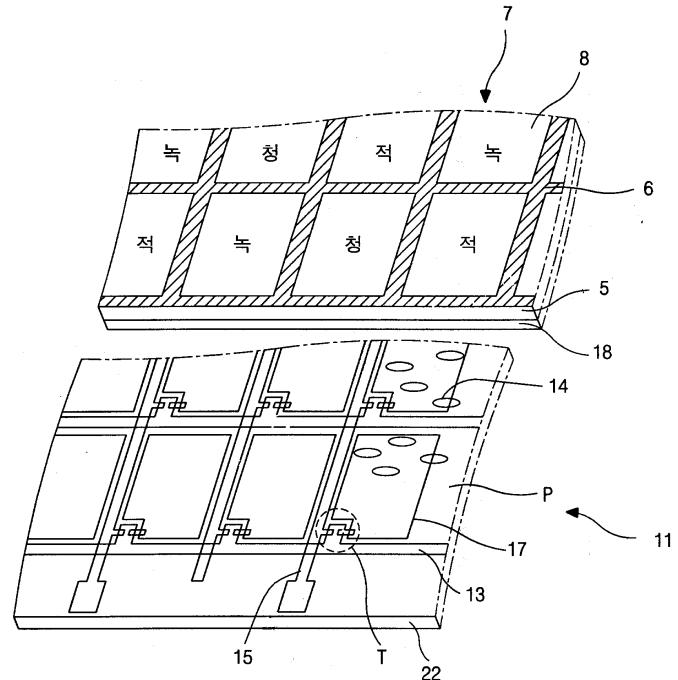

도 1은 일반적인 액정 표시장치를 도시한 분해 사시도이고,

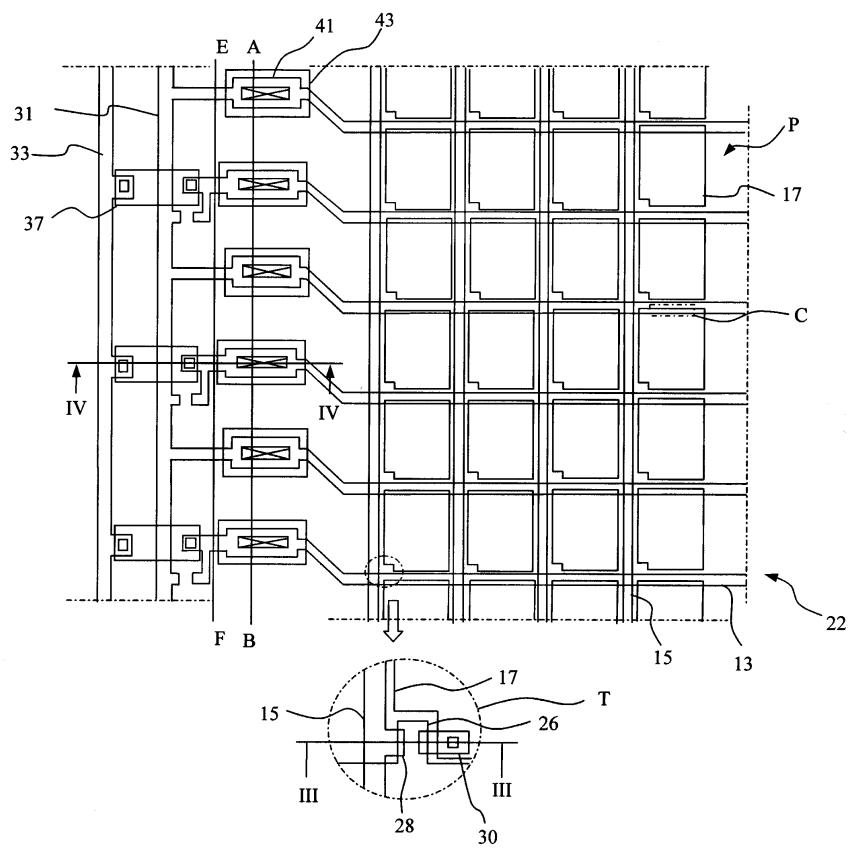

도 2는 종래의 액정표시장치용 어레이기판의 일부 화소를 도시한 확대 평면도이고,

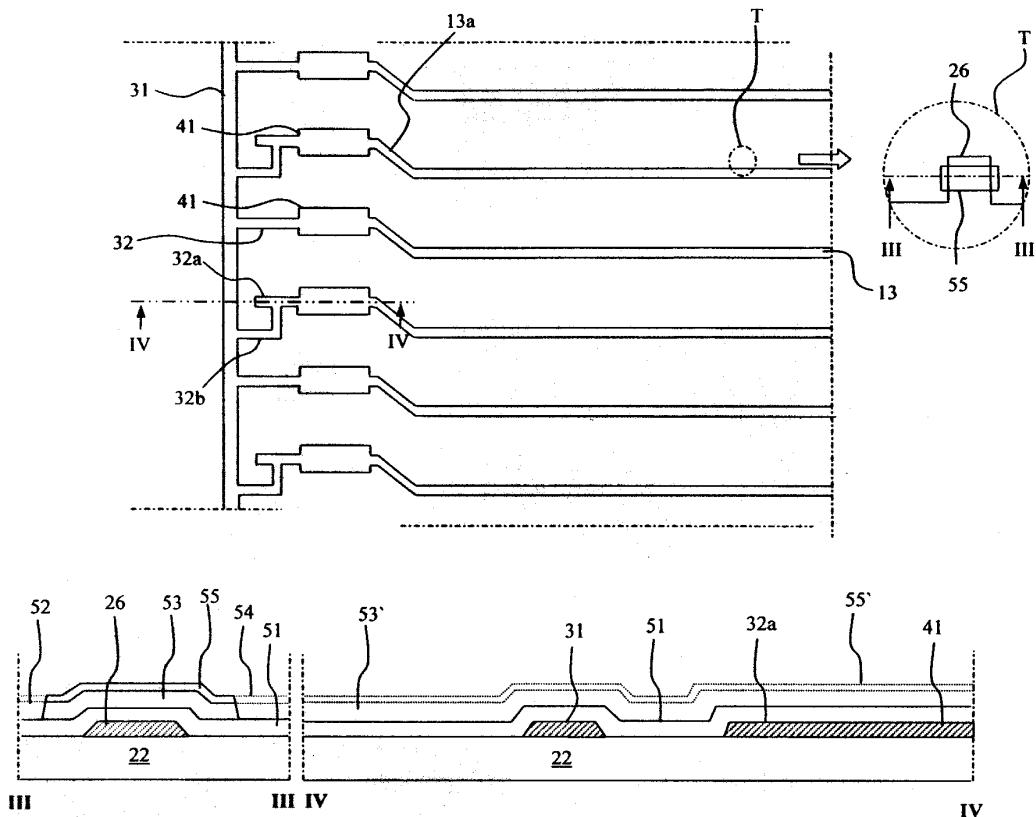

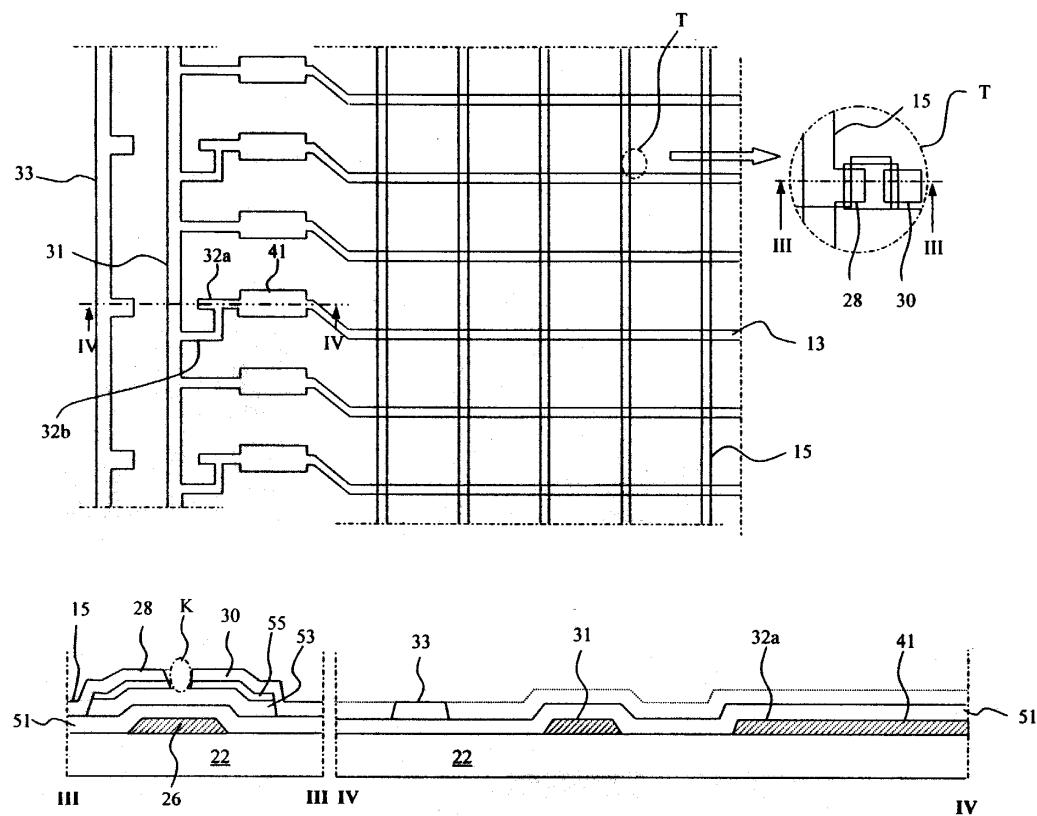

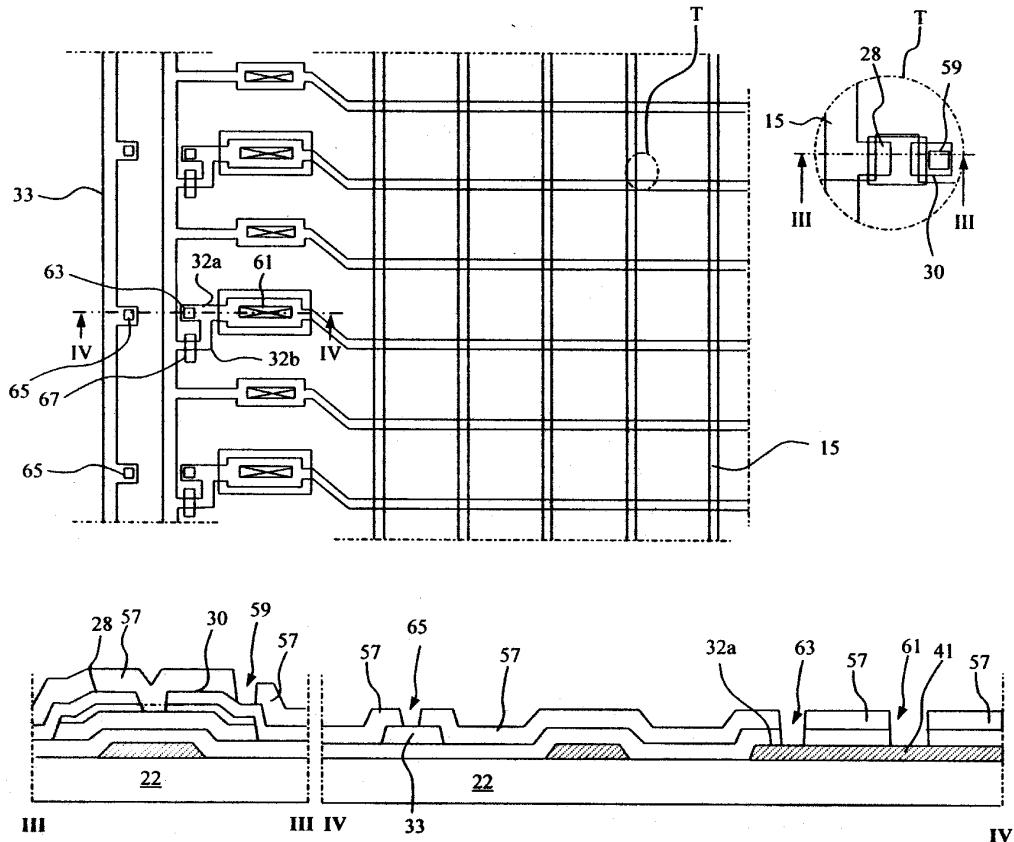

도 3a 내지 도 3d는 도 2의 구성을 공정순서에 따라 도시한 공정평면도와 이를 III-III과 IV-IV를 따라 절단한 단면도이고,

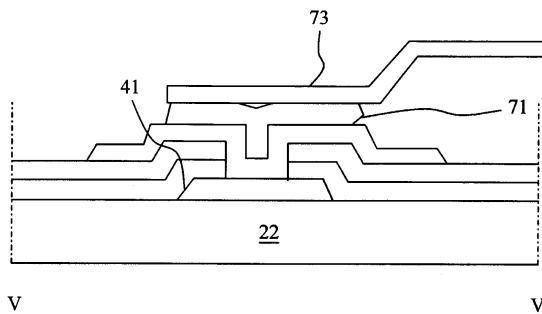

도 4는 도 3d의 V-V를 따라 절단한 단면도이고,

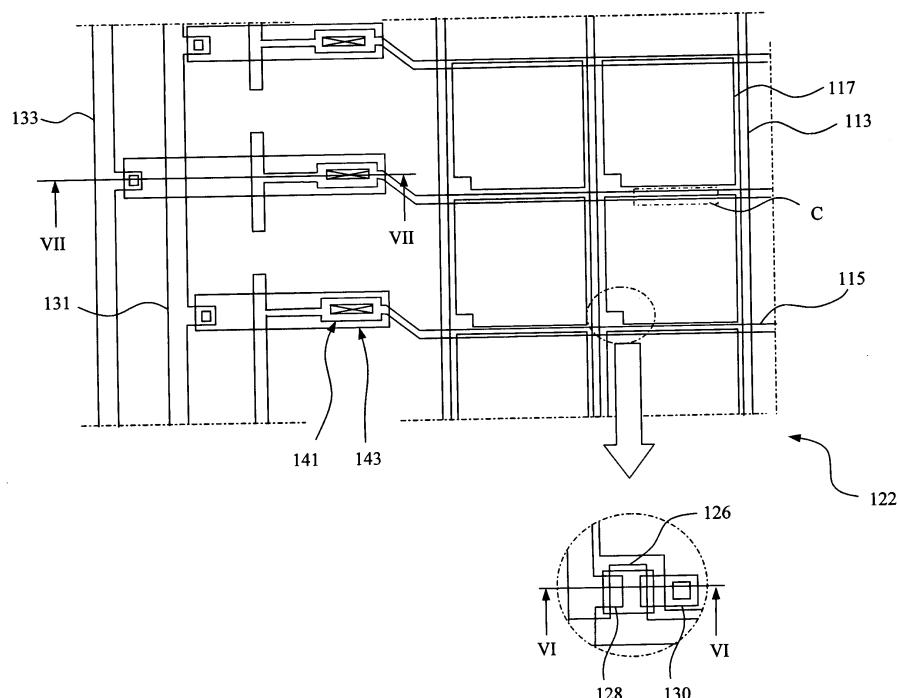

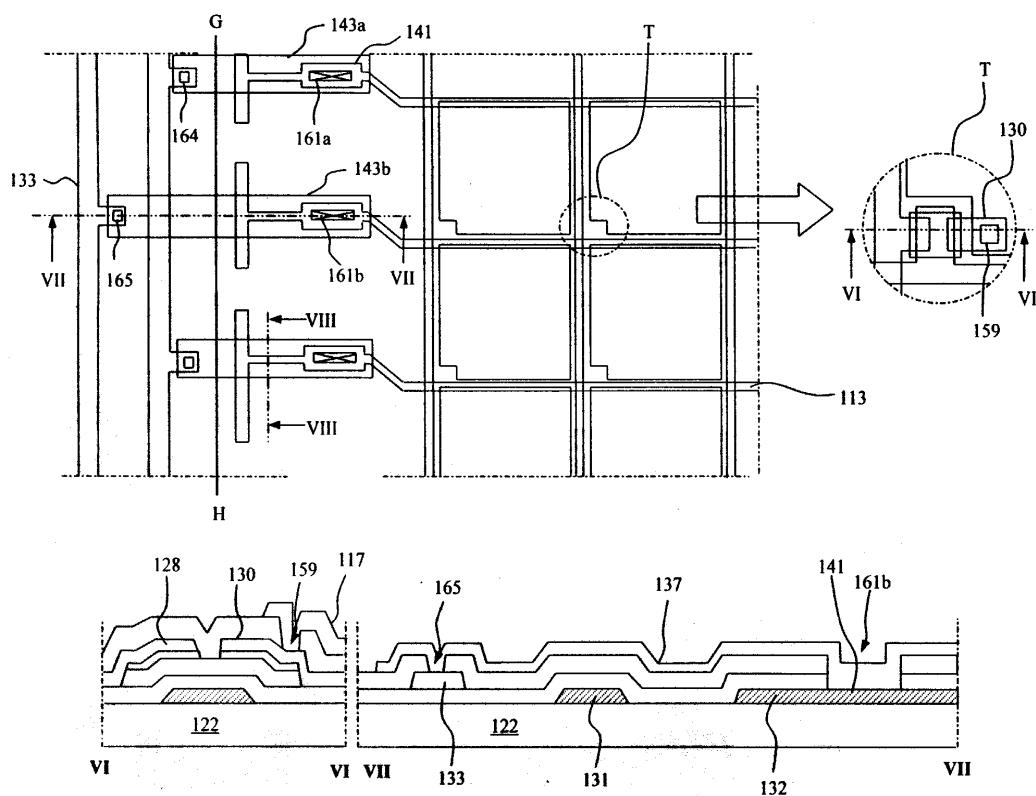

도 5는 본 발명에 따른 액정표시장치용 어레이기판의 일부 화소를 도시한 확대 평면도이고,

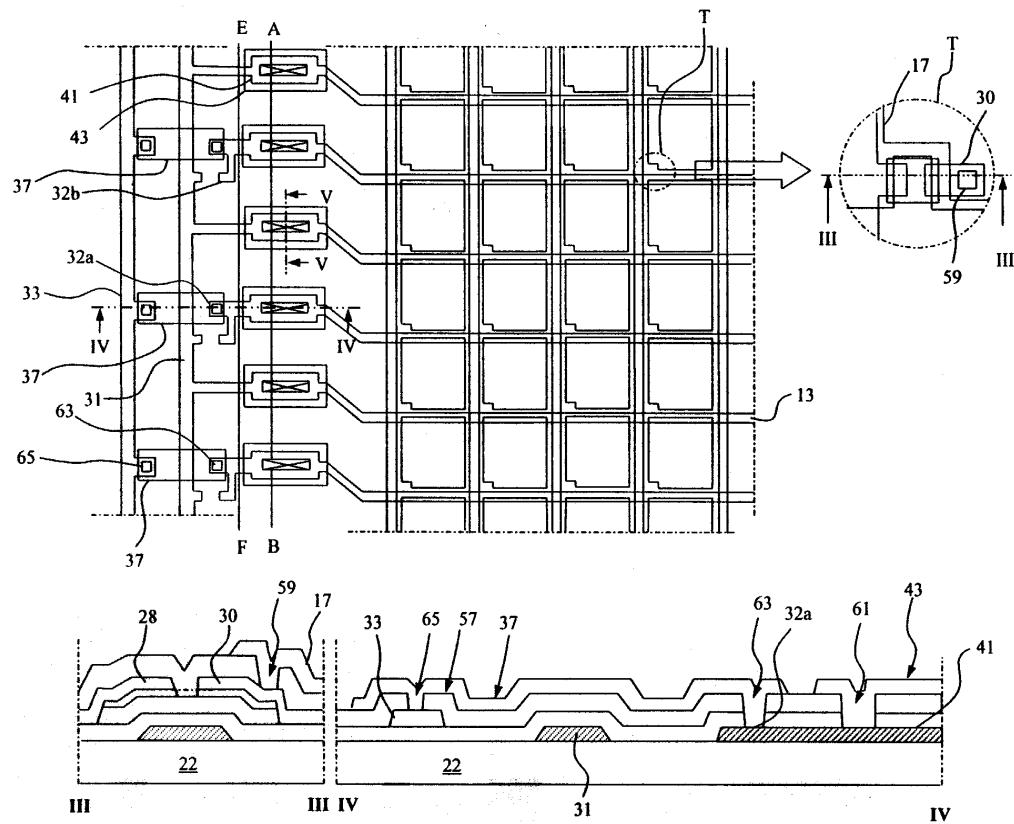

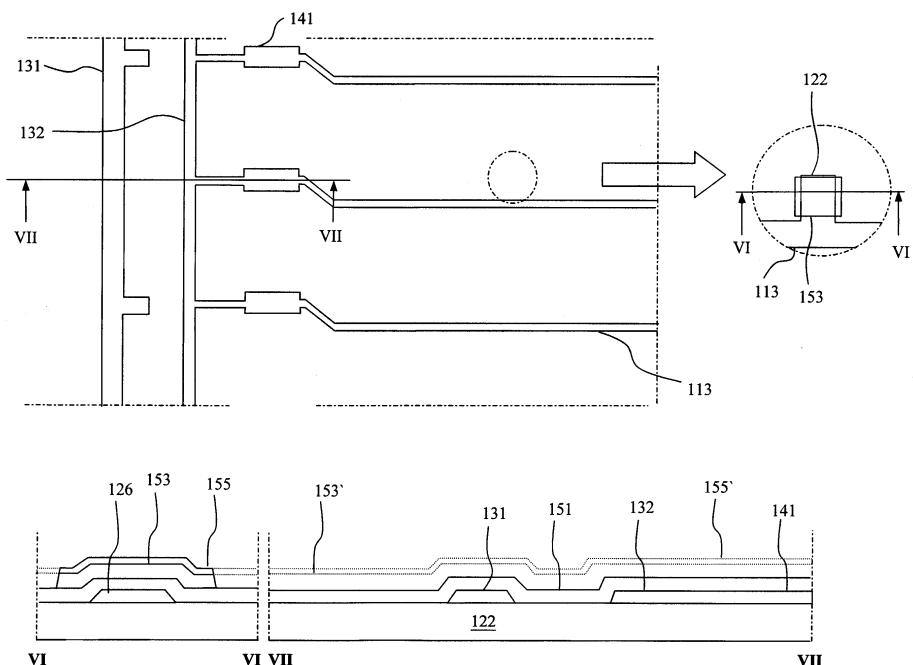

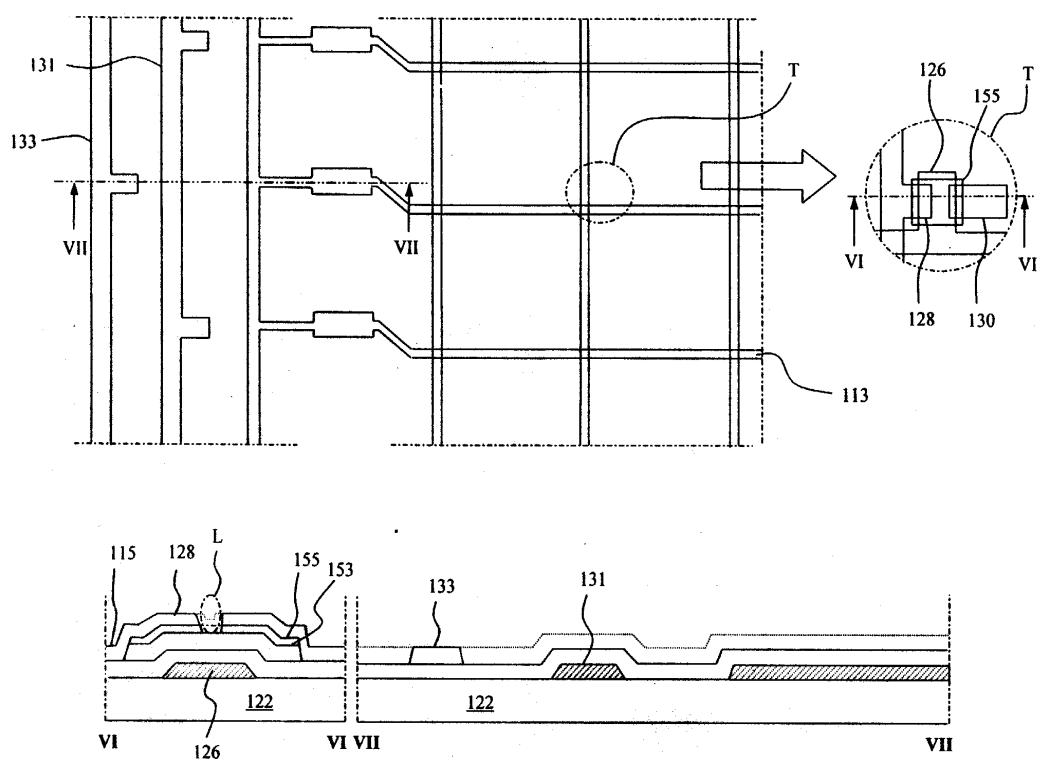

도 6a 내지 도 6d는 도 5의 구성을 공정순서에 따라 도시한 공정평면도와 이를 VI-VI과 VII-VII를 따라 절단한 단면도이고,

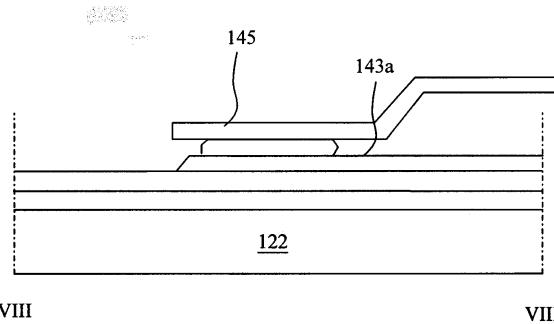

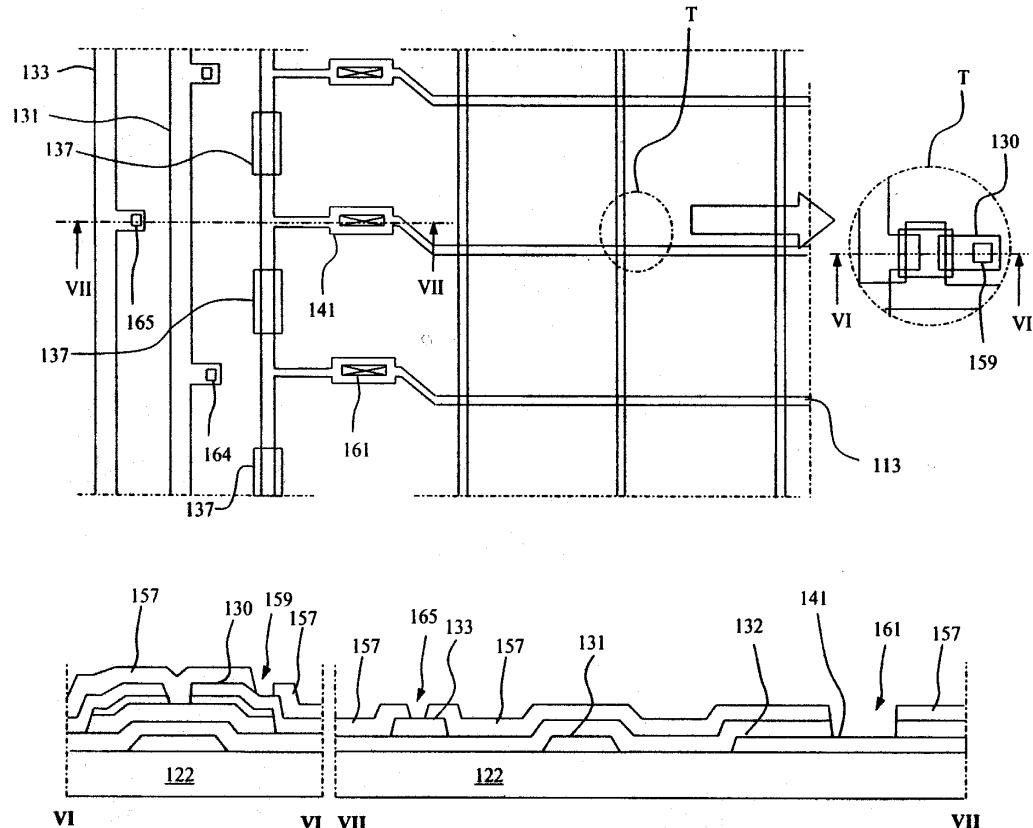

도 7은 도 6d의 VIII-VIII을 절단한 단면도이다.

**<도면의 주요 부분에 대한 부호의 설명>**

113 : 게이트배선 115 : 데이터배선

117 : 화소전극 122 : 기판

126 : 게이트전극 128 : 소스전극

130 : 드레인전극 131 : 제 1 게이트 단락배선

133 : 제 2 게이트 단락배선 137 : 수직패턴

141 : 게이트패드 143 : 게이트패드 단자

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정표시장치에 관한 것으로 특히, 액정표시장치용 어레이기판을 제작하는 공정 중 기판에 구성되는 도전성 금속배선이 정전기에 의해 단선되지 않도록 다수의 배선을 하나로 묶어 등전위를 형성하도록 하는 단락배선과 상기 다수의 배선과의 연결구조에 관한 것이다.

액정 표시장치의 구동원리는 액정의 광학적 이방성과 분극성질을 이용한다. 상기 액정은 구조가 가늘고 길기 때문에 분자의 배열에 방향성을 갖고 있으며, 인위적으로 액정에 전기장을 인가하여 분자배열의 방향을 제어할 수 있다.

따라서, 상기 액정의 분자배열 방향을 임의로 조절하면, 액정의 분자배열이 변하게 되고, 광학적 이방성에 의하여 상기 액정의 분자 배열 방향으로 빛이 굴절하여 화상정보를 표현할 수 있다.

현재에는 전술한 바 있는 박막 트랜지스터와 상기 박막 트랜지스터에 연결된 화소전극이 행렬방식으로 배열된 능동행렬 액정 표시장치(Active Matrix LCD : AM-LCD)가 해상도 및 동영상 구현능력이 우수하여 가장 주목받고 있다.

일반적으로 액정 표시장치를 구성하는 기본적인 부품인 액정 패널의 구조를 살펴보면 다음과 같다.

도 1은 일반적인 액정표시장치를 개략적으로 도시한 분해사시도이다

도시한 바와 같이, 일반적인 액정표시장치는 블랙매트릭스(6)와 서브컬러필터(적, 녹, 청)(8)를 포함한 컬러필터(7)와 컬러필터 상에 투명한 공통전극(18)이 형성된 상부기판(5)과, 화소영역(P)과 화소영역 상에 형성된 화소전극(17)과 스위칭소자(T)를 포함한 어레이배선이 형성된 하부기판(22)으로 구성되며, 상기 상부기판(5)과 하부기판(22)사이에는 액정(14)이 충진되어 있다.

상기 하부기판(22)은 어레이기판이라고도 하며, 스위칭 소자인 박막트랜지스터(T)가 매트릭스형태(matrix type)로 위치하고, 이러한 다수의 박막트랜지스터를 교차하여 지나가는 게이트배선(13)과 데이터배선(15)이 형성된다.

상기 화소영역(P)은 상기 게이트배선(13)과 데이터배선(15)이 교차하여 정의되는 영역이다. 상기 화소영역(P)상에 형성되는 화소전극(17)은 인듐-틴-옥사이드(indium-tin-oxide : ITO)와 같이 빛의 투과율이 비교적 뛰어난 투명도전성 금속을 사용한다.

전술한 바와 같이 구성되는 액정표시장치는 상기 화소전극(17)상에 위치한 액정층(14)이 상기 박막트랜지스터(T)로부터 인가된 신호에 의해 배향되고, 상기 액정층의 배향정도에 따라 상기 액정층(14)을 투과하는 빛의 양을 조절하는 방식으로 화상을 표현할 수 있다.

상기 게이트배선(13)은 상기 박막트랜지스터(T)의 제 1 전극인 게이트전극을 구동하는 펄스전압을 전달하며, 상기 데이터배선(15)은 상기 박막트랜지스터(T)의 제 2 전극인 소스전극을 구동하는 신호전압을 전달하는 수단이다.

도 2는 종래의 액정표시장치용 어레이기판의 일부 화소를 도시한 확대 평면도이다.

도시한 바와 같이, 어레이기판(22)은 다수의 화소(P)로 구성되며, 화소는 스위칭소자인 박막트랜지스터(thin film transistor)(T)와 화소전극(pixel electrode)(17)과 보조용량인 스토리지 캐패시터(storage capacitor)(C)로 구성된다.

상기 박막트랜지스터(T)는 게이트전극(26)과 소스전극(28)과 드레인전극(30)과 액티브층(active layer)(미도시)으로 구성되고, 상기 소스전극(28)은 데이터배선(15)과 연결되며 상기 게이트전극(26)은 상기 데이터배선(15)과 교차하여 화소영역(P)을 정의하는 게이트배선(13)과 연결되도록 구성된다.

여기서, 상기 게이트배선(13)과 데이터배선(15)의 끝단에는 소정면적으로 연장 형성된 게이트패드(41)와 데이터패드(미도시)가 구성되고, 상기 각 패드는 투명 패드단자(43)가 구성되어 외부신호를 입력받는다.

상기 게이트패드 상에 구성된 투명 패드단자는 게이트패드 단자라 하고, 데이터패드 상에 구성된 투명 패드단자는 데이터패드 단자라 한다.

상기 게이트배선(13)과 데이터배선(15)은 홀수번째와 짝수번째로 나뉘어져 각각 단락배선(shorting bar : "쇼팅 바")으로 연결되도록 구성한다.

일반적으로, 액정패널의 기판(22)은 일반적으로 투명한 글라스기판을 사용하기 때문에 공정 중 발생하는 정전기가 기판 및 기판 상부의 어레이패턴에 유입되어 국소적으로 존재하게 된다.

이러한 정전기는 전하량은 매우 작지만 국소적으로 존재하기 때문에 그 전압은 매우 높아 박막트랜지스터 등의 세밀한 소자들에게 데미지(damage)를 입힌다.

이를 방지하기 위한 방법으로 상기 다수의 게이트배선(13)과 데이터배선(15)을 전술한 단락배선으로 연결하여 등전위를 형성하도록 하며, 이러한 단락배선은  $2n$ 번째와  $2n+1$ 번째 배선들을 각각 하나로 연결한다.

이와 같이 구성된 기판은 배선의 단선 또는 단락여부를 테스트(IPT 방식)하게 되며, 이러한 전기적인 테스트가 끝난 후에 상기 단락배선은 기판으로부터 제거된다.

도 2의 구성에서 게이트배선(13)은 제 1 게이트 단락배선(31)에 일체화하여 연결되며, 제 2 게이트 단락배선(33)은 상기 데이터배선(15)과 동일층에 동일물질로 구성된다.

이러한 구성에서, 상기 게이트배선(13)의 단선(open) 및 단락(short) 테스트를 위해, 상기 게이트배선(13)은  $2n$ 번째와  $2n+1$ 번째로 나뉘어져 전압을 인가한 후 테스트하게 된다.(이하, 게이트배선은 모두 동일한 번호를 사용함)

따라서, 상기 게이트배선(13)은 홀수번째와 짝수번째로 나뉘어 구성하는 것이 필요하며, 이때 상기 제 1 게이트 단락배선(31)에 연결된 게이트배선(13) 중 홀수번째 또는 짝수번째 게이트배선(13) 상부에 절단부를 구성하여, 상기 절단부를 통해 상기 게이트배선(13)을 절단한 후, 절단된 게이트배선을 상기 제 2 게이트 단락배선(33)에 연결하여 주는 공정이 필요하다. (편의상 상기 제 2 게이트 단락배선과 연결되는 배선은 짝수번째 게이트배선이라 한다.)

따라서, 상기 짝수번째 게이트배선(13)은 상기 제 1 게이트 단락배선(31)과 연결된 부위가 절단되며 연속으로 상기 제 2 게이트 단락배선(33)과는 투명전극 패턴(37)에 의해 연결되는 구조로 형성된다.

이와 같은 구성에서, 상기 게이트배선(13)과 연결된 제 1 게이트 단락배선(31)과 제 2 게이트 단락배선(33)은 기판제작과 테스트가 끝난 후, 도시한 바와 같이 A-B 또는 E-F를 따라 절단하여 제거하게 된다.

이때, 만약 상기 게이트배선(13)이 상기 투명기판(22)인 글라스의 계면과 접촉특성이 좋지 않은 구리(Cu) 또는 구리합금류의 금속재질로 형성되었다면, 상기 절단된 게이트패드(41)부는 물리적인 충격에 의해 상기 글라스와의 접촉면이 약해져 둘뜨게 되는 현상이 발생하게 된다.

이와 같은 종래의 액정표시장치용 어레이기판의 구조를 이하, 도 3a 내지 3e를 참조하여 설명한다.

도 3a 내지 도 3d는 도 2의 구성을 공정순서에 따라 도시한 공정 평면도와, 이를 III-III과 IV-IV를 따라 절단하여 도시한 공정단면도이다. (이하, 설명은 5마스크 공정을 예를 들어 설명한다.)

일반적으로 액정표시장치에 사용되는 박막 트랜지스터의 구조는 역 스태거드(Inverted Staggered)형 구조가 많이 사용된다. 이는 구조가 간단하면서도 성능이 우수하기 때문이다.

또한, 상기 역 스태거드형 박막 트랜지스터는 채널 형성 방법에 따라 백 채널 에치형(back channel etch : EB)과 에치스 타퍼형(etch stopper : ES)으로 나뉘며, 구조가 간단한 백 채널 에치형 구조가 적용되는 액정 표시소자 제조공정에 관해 설명한다.

먼저, 기판(22)에 이물질이나 유기성 물질을 제거하고, 증착될 게이트물질의 금속박막과 유리기판의 접촉성(adhesion)을 좋게 하기 위하여 세정을 실시한 후, 스퍼터링(sputtering)에 의하여 금속막을 증착한다.

도 3a에 도시한 바와 같이, 기판 상에 구리(Cu) 또는 구리합금을 증착하고 패턴하여, 끝단에 소정면적으로 연장 형성된 게이트패드(41)를 포함하는 게이트배선(13)과, 상기 게이트배선(13)에서 일방향으로 돌출 형성된 게이트전극(26)과, 상기 다수의 게이트배선(13)을 연결하는 게이트 제 1 게이트 단락배선(31)을 형성한다.

여기서, 상기 게이트배선 중 짝수번째 게이트배선(13)은 상기 게이트패드에서 연장 형성되고, 제 1 배선(32a)과 제 2 배선(32b)으로 분기되어 형성되며, 상기 제 2 배선(32b)이 상기 제 1 게이트 단락배선(31)으로 연장 형성된다.

다음으로, 상기 게이트배선(13) 등이 형성된 기판(22) 상에 절연물질(51)과, 순순 비정질실리콘(a-Si:H)(53')과 불순물이 함유된 비정질실리콘(n+ a-Si:H)(55')을 적층한 후, 상기 비정질 실리콘을 패턴하여, 상기 게이트전극(26) 상부에 아일랜드형태로 액티브층(53)과 오믹콘택층(55)을 형성한다.

다음으로, 도 3b에 도시한 바와 같이, 상기 액티브층(53)과 오믹콘택층이 패턴된 기판(22) 상에 도전성 금속을 증착하고 패턴하여, 데이터배선(15)과 상기 데이터배선(15)에서 일방향으로 돌출 형성된 소스전극(28)과 이와는 소정간격 이격된 드레인전극(30)을 형성한다.

동시에, 상기 제 1 게이트 단락배선(31)과 소정간격 이격되어 평행하게 구성된 제 2 게이트 단락배선(33)을 형성한다.

이때, 상기 소스전극(28)과 드레인전극(30)은 마스킹 레이어(masking layer)로 이용되고, 이를 마스크로 하여 노출된 오믹콘택층(55)의 일부(K)가 식각된다.

도 3c에 도시한 바와 같이, 상기 소스 및 드레인전극 등이 형성된 기판 상에 절연물질을 증착하고 보호층(57)을 형성한다.

다음으로, 상기 보호층(57)을 패턴하여, 상기 드레인전극(28) 상부에 드레인 콘택홀(59)과, 상기 게이트패드(41) 상부에 게이트패드 콘택홀(61)과, 상기 제 1 배선(32a) 상부에 제 1 접촉콘택홀(63)과, 제 1 배선(32a)에 근접한 위치의 상기 제 2 데이터 단락배선(33) 상부에 제 2 접촉콘택홀(65)을 형성한다.

동시에, 상기 제 2 배선(32a) 상부에 식각홀(67)을 형성한다.

다음 단계로, 도 3d에 도시한 바와 같이, 상기 패턴된 보호층(57)의 상부에 투명도전성 금속을 증착하고 패턴하여, 상기 드레인 콘택홀(59)을 통해 상기 드레인전극(30)과 접촉하고 상기 화소영역(P) 상에 구성되는 화소전극(17)을 형성한다.

동시에, 상기 게이트 패드(41) 상부에 아일랜드 형태로 게이트패드 단자전극(43)을 형성하고, 상기 제 1 접촉 콘택홀(63)과 제 2 접촉 콘택홀(65)을 통해 상기 제 2 게이트 단락배선(33)과 상기 짹수번째 게이트배선(13)을 연결하는 투명연결전극(37)을 형성한다.

이와 동시에, 상기 식각홀(67)에 의해 노출된 하부 제 2 배선(32b)을 식각하여 상기 제 1 게이트 단락배선(31)과 상기 짹수번째 배선(13)을 단선처리 한다.

이와 같이 구성하면, 상기 홀수번째 게이트배선은 상기 제 1 게이트 단락배선에 모두 연결되는 구조가 되고 상기 짹수번째 게이트배선은 상기 제 2 게이트 단락배선에 모두 연결되는 구조가 된다. 이와 같은 구성 후, 배선의 단선 또는 단락여부를 테스트하게 되며, 테스트가 끝난 후, 도시한 바와 같이 A-B 또는 E-F를 절단하여 어레이기판을 완성하게 된다.

이때, 상기 구리(Cu)로 형성한 게이트배선은 다른 금속에 비해 전기적 특성은 우수하나, 상기 글라스 기판과의 접착특성이 좋지 않은 단점이 있다.

따라서, 상기 단락배선을 절단하는 과정에서, 상기 절단부(A-B, E-F)의 게이트배선은 절단과정 중 받는 물리적 충격에 의해 상기 기판과의 접착력이 약해진다.

도 4는 도 3d의 V-V를 따라 절단된 단면도이다.(E-F 절단부를 예를 들어 설명한다.)

도시한 바와 같이, 상기 단락배선이 절단된 게이트패드(41) 상부에 전도성 접착제(ACF)(71)를 이용하여 구동회로가 실장된 TCP(73)를 부착하는 공정 중, 만약 상기 TCP(73)와 게이트 패드(41)가 미스얼라인(misalign)에 의해 접촉불량이 발생하였다면, 상기 TCP(73)를 접착제로부터 분리하여 다시 얼라인하여 부착하는 과정인 리워크(rework)과정을 수행하게 된다.

이러한 공정을 거치면서, 상기 절단과정 중 상기 기판과의 접착력이 약화된 배선은 상기 기판으로부터 이탈되어 뜯겨지는 문제가 발생한다.

### 발명이 이루고자 하는 기술적 과제

상기와 같은 문제를 해결하기 위해 본 발명은 상기 게이트패드와 상기 게이트단락배선 사이의 절단부에 상기 게이트 금속배선이 존재하지 않도록 하는 어레이기판 구조를 제안하여, 게이트패드 불량이 없는 액정표시장치용 어레이기판을 제공하는 데 그 목적이 있다.

### 발명의 구성 및 작용

전술한 바와 같은 목적을 달성하기 위한 본 발명에 따른 액정표시장치용 어레이기판은 기판과; 기판의 일측에 서로 평행하게 이격하여 일방향으로 구성된 제 1 게이트 단락배선과 제 2 게이트 단락배선과; 상기 제 1 게이트 단락배선과 소정간격 이격하여 구성되고 별도의 제 1 전극으로 연결된  $2n+1$  번째 게이트배선과, 상기 제 2 게이트 단락배선과 소정간격 이격하여 구성되고 별도의 제 2 전극으로 연결된  $2n$  번째 게이트배선과; 상기 다수의 게이트배선과 교차하여 화소영역을 정의하는 데이터배선과; 상기 게이트배선과 데이터배선의 교차지점에 구성된 스위칭소자와; 상기 화소영역 상에 구성된 화소전극을 포함한다.

상기 제 1 게이트단락배선과 게이트배선은 구리(Cu)로 형성된 것을 특징으로 한다.

상기 스위칭소자는 게이트전극과 소스전극 및 드레인 전극으로 구성되는 것을 특징으로 한다.

제 1 전극과 제 2 전극은 투명도전성 금속인 것을 특징으로 한다.

상기 투명도전성 금속은 ITO 또는 IZO인 것을 특징으로 한다.

본 발명의 특징에 따른 액정표시장치용 어레이기판의 제조방법은 기판을 구비하는 단계와; 기판의 일측에 일 방향으로 구성된 수직패턴에 직교하여 구성되는 다수의 게이트배선과, 상기 게이트배선에서 일 방향으로 돌출 형성된 다수의 게이트전극과, 상기 수직패턴과 소정간격 이격하여 평행하게 구성된 제 1 게이트 단락배선을 형성하는 단계와; 상기 게이트배선이 형성된 기판의 전면에 절연층과 비정질 실리콘층과 불순물 실리콘층을 적층한 후 이를 패턴하여, 상기 게이트전극 상부에 적층된 액티브층과 오믹콘택층을 형성하는 단계와; 상기 오믹콘택층이 형성된 기판의 전면에 도전성 금속을 증착한 후, 이를 패턴하여 소스전극 및 드레인 전극과, 상기 제 1 게이트 단락배선과 소정간격 이격하여 일 방향으로 평행하게 제 2 게이트 단락배선을 형성하는 단계와; 상기 소스 및 드레인 전극이 구성된 기판의 전면에 절연물질을 증착 또는 도포하여 보호층을 형성한 후 이를 패턴하여, 상기 게이트배선의 끝단인 게이트패드 상부에 게이트패드 콘택홀과, 상기 홀수번재 게이트배선과 근접한 제 1 게이트단락배선 상부에 제 1 접촉홀과, 상기 짹수번재 게이트배선과 근접한 제 2 게이트단락배선 상부에 제 2 접촉홀과, 상기 게이트배선과 게이트배선 사이의 수직패턴 상부에 식각홀을 형성하는 단계와; 상기 패턴된 보호층이 구성된 기판의 전면에 투명도전성 금속을 증착하고 패턴하여, 상기 드레인전극과 접촉하고 상기화소영역 상에 구성된 화소전극과, 상기 제 1 접촉홀과 상기 게이트패드 콘택홀을 통해 상기 제 1 게이트단락배선과 홀수번재 게이트배선을 연결하는 제 1 전극과, 상기 제 2 접촉홀과 상기 게이트패드 콘택홀을 통해 상기 제 2 게이트 단락배선과 짹수번재 게이트배선을 연결하는 제 2 전극을 형성하고, 동시에 상기 식각홀을 통해 노출된 하부 수직패턴을 식각하는 단계를 포함한다.

상기 게이트배선은 상기 식각홀을 통해 식각되어 홀수번재와 짹수번재의 게이트배선이 독립적으로 구성되는 것을 특징으로 한다.

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 설명한다.

도 5는 본 발명의 실시예에 따른 액정표시장치용 어레이기판(122)의 일부를 도시한 확대 평면도이다.

도시한 바와 같이, 액정표시장치용 어레이기판은 게이트배선(113)과 데이터배선(115)과 상기 게이트배선(113)과 데이터배선(115)의 교차영역에 위치하고 게이트전극(126)과 소스전극(128) 및 드레인전극(130)으로 구성된 박막트랜지스터(T)와, 상기 박막트랜지스터(T)의 드레인전극(130)과 접촉하는 동시에 화소영역(P)에 구성되고, 상기 게이트배선(113)상부로 연장되어 스토리지 캐패시터(C)를 이루는 화소전극(117)을 포함한다.

상기 게이트배선(113)의 끝단에서 소정면적으로 연장 형성된 게이트패드(141)를 구성하며, 상기 다수의 게이트배선(113) 중 짹수번재 게이트배선은 제 1 게이트 단락배선(131)과 연결하며, 상기 홀수번재 게이트배선은 제 2 게이트 단락배선(133)과 전기적으로 연결되도록 구성한다.

이때, 상기 각 게이트 단락배선(131, 133)과 다수의 게이트배선(113)은 서로 이격되어 구성되며, 각각은 아일랜드 형태로 패턴된 투명전극 단자(143)에 의해 전기적으로 연결되도록 구성한다.

이와 같이 구성하면, 종래와는 달리 상기 배선의 단선과 단락불량 테스트 후, 상기 단락배선(131, 133)을 제거하기 위해 기판을 절단할 때, 상기 절단부(G, H)의 하부에는 상기 게이트배선(113) 금속이 존재하지 않게 된다.

따라서, 본 발명에 따른 액정표시장치용 어레이기판은 전술한 바와 같은 위치에서, 절단공정 줄 물리적인 충격에 의해 금속배선의 틀림 현상 등이 발생하지 않는 구조이다.

이하 도 6a 내지 도 6d를 참조하여 본 발명에 따른 액정표시장치용 어레이기판 제조방법과 그 제조방법에 의한 구조를 설명한다.

도 6a 내지 도 6d는 도 5의 구성을 공정순서에 따라 도시한 공정 평면도와, 이를 VI-VI와 VII-VII를 따라 절단한 단면도이다.

먼저, 도 6a에 도시한 바와 같이, 기판 상에 구리(Cu) 또는 구리합금을 증착하고 패턴하여, 끝단에 소정면적으로 연장 형성된 게이트패드(141)를 포함하는 게이트배선(113)과, 상기 게이트배선(113)에서 일 방향으로 돌출 형성된 게이트전극(126)을 형성한다.

이때, 상기 다수의 게이트배선(113)은 게이트배선과 직교하면서 연장되어 일 방향으로 형성된 수직패턴(132)에 의해 일체화되어 형성된다.

이와 같이, 구성하면 모든 게이트배선이 등전위를 형성하므로 상기 게이트배선(113)이 정전기에 대한 영향을 받지 않는다.

상기 게이트배선(113)을 상기 수직패턴(132)과 일체화하여 패턴하는 동시에, 상기 수직패턴(131)과 소정간격 이격하여 일 방향으로 평행하게 제 1 게이트 단락배선(131)을 형성한다.

다음으로, 상기 게이트배선(113) 등이 형성된 기판(122) 상에 절연물질(151)과, 순순 비정질실리콘(a-Si:H)(153)과 불순물이 함유된 비정질실리콘(n<sup>+</sup> a-Si:H)(155)을 적층한 후 상기 비정질 실리콘을 패턴하여, 상기 게이트전극(126) 상부에 아일랜드형태로 액티브층(153)과 오믹콘택층(155)을 형성한다.

이때, 상기 절연물질은 질화실리콘(SiN<sub>X</sub>)과 산화실리콘(SiO<sub>2</sub>)등이 포함된 무기절연물질과, 경우에 따라서는 벤조사이클로부텐(benzocyclobutene)과 아크릴(acryl)계 수지(resin)등이 포함된 유기절연물질 중 선택하여 사용한다.

다음으로, 도 6b에 도시한 바와 같이, 상기 액티브층(153)과 오믹콘택층(155)이 패턴된 기판(122)상에 텅스텐(W), 몰리브덴(Mo), 크롬(Cr)등을 포함하는 도전성 금속그룹 중 하나를 선택하여 증착하고 패턴하여, 데이터배선(115)과 상기 데이터배선(115)에서 일 방향으로 돌출 형성된 소스전극(128)과 이와는 소정간격 이격된 드레인 전극(130)을 형성한다.

동시에, 상기 제 1 게이트 단락배선(131)과 소정간격 이격되어 평행하게 일 방향으로 구성된 제 2 게이트 단락배선(133)을 형성한다.

이때, 상기 소스전극(128)과 드레인 전극(130)은 마스킹 레이어(masking layer)로 이용되고, 이를 마스크로 하여 노출된 오믹콘택층(155)의 일부(L)를 식각한다.

다음으로 도 6c에 도시한 바와 같이, 상기 소스 및 드레인 전극 등이 형성된 기판(122)상에 절연물질을 증착하고 보호층(157)을 형성한다.

다음으로, 상기 보호층(157)을 패턴하여, 상기 드레인 전극(130) 상부에 드레인 콘택홀(159)과, 상기 게이트패드(141) 상부에 게이트패드 콘택홀(161)과, 상기 다수의 게이트패드 중 홀수번째 게이트패드와 근접한 상기 제 1 게이트 단락배선(131)의 상부에 제 1 접촉홀(164)과, 짝수번째 게이트패드(141)와 근접한 부분의 상기 제 2 게이트 단락배선(133)의 상부에 제 2 접촉홀(165)을 형성한다.

이와 동시에, 상기 보호층(157)을 패턴할 때, 상기 게이트배선(113)과 게이트배선 사이에 존재하는 수직패턴(132) 상부의 일부 보호층을 식각하여 식각홀(137)을 형성한다.

다음은 도 6d에 도시한 바와 같이, 상기 패턴된 보호층(157)의 상부에 인듐-틴-옥사이드(indium-tin-oxide : ITO)와 인듐-징크-옥사이드(indium-zinc-oxide : IZO)등의 투명도전성 금속을 증착하고 패턴하여, 상기 드레인 콘택홀(159)을 통해 상기 드레인 전극(130)과 접촉하면서 상기 화소영역(P) 상부로 연장하여 화소전극(117)을 형성한다.

동시에, 상기 홀수번째 게이트패드 콘택홀(161a)과 상기 제 1 접촉홀(164)에 동시에 충진되어 상기 홀수번째 게이트배선과 상기 제 1 게이트 단락배선(131)을 연결하는 제 1 게이트패드 단자(161a)와, 상기 짝수번째 게이트패드 콘택홀(161b)과 상기 제 2 접촉홀(165)에 동시에 충진되어 상기 짝수번째 게이트배선과 상기 제 2 게이트 단락배선(133)을 연결하는 제 2 게이트패드 단자(143b)를 형성한다.

이와 같은 구성은 상기 게이트패드와 상기 단락배선 사이에 게이트금속이 존재하지 않는 구조가 된다.

전술한 바와 같이, 어레이기판을 구성한 후 IPT방식을 사용한 배선의 단선 및 단락 테스트를 거친 후, 상기 단락배선을 절단하는 공정을 행하게 된다.

이때, 도시한 바와 같이 상기 게이트패드와 게이트 단락배선 사이를 G-H를 따라 절단한다.

상기 G-H부분은 게이트 배선이 존재하지 않고, 상기 게이트배선과 단락배선을 전기적으로 연결하는 투명전극과, 그 하부의 절연층이 존재하는 구조이다.

즉, 상기 절단공정에 의해 상기 기판 상에 구성된 게이트패드가 손상되지 않는 구조이다.

도 7은 도 6d의 G-H의 일부인 VIII-VIII을 따라 절단한 단면도이다.

도시한 바와 같이, 상기 절단 부위는 게이트금속이 존재하지 않고, 상기 게이트패드와 전기적으로 연결된 게이트패드 단자만(143a)이 존재하게 된다.

따라서, 상기 금속배선의 들뜸 현상이 없는 부분이므로, 상기 구동회로를 실장한 TCP(145)를 접착하는 과정이나, 이를 리워크하는 과정에서도 패드의 들뜸에 의한 패널불량은 발생하지 않는다.

이와 같은 구조는 본 발명과 같이 구리배선을 게이트금속으로 사용하는 예 외에도, 이와 유사한 금속으로 게이트배선을 사용하는 모든 액정표시장치용 어레이기판의 구조에 적용 가능하다.

### 발명의 효과

따라서, 본 발명은 상기 게이트 단락배선을 제거하기 위한 절단부에 상기 금속배선이 존재하지 않도록 하는 구조이므로, 물리적 충격에 의한 배선의 접촉불량 유발현상이 없으므로, 액정패널의 수율을 향상시킬 수 있는 효과가 있다.

### (57) 청구의 범위

#### 청구항 1.

기판과;

기판의 일측에 서로 평행하게 이격하여 일 방향으로 구성된 제 1 게이트 단락배선과 제 2 게이트 단락배선과;

상기 제 1 게이트 단락배선과 소정간격 이격하여 구성되고 별도의 제 1 전극으로 연결된  $2n+1$  번째 게이트배선과, 상기 제 2 게이트 단락배선과 소정간격 이격하여 구성되고 별도의 제 2 전극으로 연결된  $2n$  번째 게이트배선과;

상기 다수의 게이트배선과 교차하여 화소영역을 정의하는 데이터배선과;

상기 게이트배선과 데이터배선의 교차지점에 구성된 스위칭소자와;

상기 화소영역 상에 구성된 화소전극

을 포함하는 액정표시장치용 어레이기판.

#### 청구항 2.

제 1 항에 있어서,

상기 제 1 게이트단락배선과 게이트배선은 구리로 형성된 액정표시장치용 어레이기판.

#### 청구항 3.

제 1 항에 있어서,

상기 스위칭소자는 게이트전극과 소스전극 및 드레인 전극 구성된 액정표시장치용 어레이기판.

#### 청구항 4.

제 1 항에 있어서,

제 1 전극과 제 2 전극은 투명도전성 금속인 액정표시장치용 어레이기판.

#### 청구항 5.

제 4 항에 있어서,

상기 투명도전성 금속은 ITO 또는 IZO인 액정표시장치용 어레이기판.

#### 청구항 6.

기판을 구비하는 단계와;

기판의 일측에 일 방향으로 구성된 수직패턴에 직교하여 구성되는 다수의 게이트배선과, 상기 게이트배선에서 일 방향으로 돌출 형성된 다수의 게이트전극과, 상기 수직패턴과 소정간격 이격하여 평행하게 구성된 제 1게이트 단락배선을 형성하는 단계와;

상기 게이트배선이 형성된 기판의 전면에 절연층과 비정질 실리콘층과 불순물 실리콘층을 적층한 후 이를 패턴하여, 상기 게이트전극 상부에 아일랜드 형태로 적층된 액티브층과 오믹콘택층을 형성하는 단계와;

상기 오믹콘택층이 형성된 기판의 전면에 도전성 금속을 증착한 후, 이를 패턴하여 소스전극 및 드레인전극과, 상기 제 1 게이트 단락배선과 소정간격 이격하여 일 방향으로 평행하게 제 2 게이트 단락배선을 형성하는 단계와;

상기 소스 및 드레인전극이 구성된 기판의 전면에 절연물질을 증착 또는 도포하여 보호층을 형성한 후 이를 패턴하여, 상기 게이트배선의 끝단인 게이트패드 상부에 게이트패드 콘택홀과, 상기 홀수번째 게이트배선과 근접한 제 1 게이트단락배선 상부에 제 1 접촉홀과, 상기 짹수번째 게이트배선과 근접한 제 2 게이트단락배선 상부에 제 2 접촉홀과, 상기 게이트배선과 게이트배선 사이의 수직패턴 상부에 식각홀을 형성하는 단계와;

상기 패턴된 보호층이 구성된 기판의 전면에 투명도전성 금속을 증착하고 패턴하여, 상기 드레인전극과 접촉하고 상기화소영역 상에 구성된 화소전극과, 상기 제 1 접촉홀과 상기 게이트패드 콘택홀을 통해 상기 제 1 게이트단락배선과 홀수번째 게이트배선을 연결하는 제 1 전극과, 상기 제 2 접촉홀과 상기 게이트패드 콘택홀을 통해 상기 제 2 게이트 단락배선과 짹수번째 게이트배선을 연결하는 제 2 전극을 형성하고, 동시에 상기 식각홀을 통해 노출된 하부 수직패턴을 식각하는 단계를

포함하는 액정표시장치용 어레이기판 제조방법.

## 청구항 7.

제 6 항에 있어서,

상기 게이트배선은 구리로 형성된 액정표시장치용 어레이기판 제조방법.

## 청구항 8.

제 6 항에 있어서,

상기 투명전극은 인듐옥사이드를 포함하는 투명전극인 것을 특징으로 하는 액정표시장치용 어레이기판 제조방법.

## 청구항 9.

제 6 항에 있어서,

상기 게이트배선은 상기 식각홀을 통해 식각되어 홀수번째와 짹수번째의 게이트배선이 독립적으로 구성된 액정표시장치용 어레이기판 제조방법.

**도면**

도면1

도면2

도면3a

도면3b

도면3c

도면3d

도면4

도면5

도면6a

도면6b

도면6c

도면6d

도면7