República Federativa do Brasil

Ministério da Economia

Instituto Nacional da Propriedade Industrial

**(11) BR 112016002454-0 B1**

**(22) Data do Depósito: 07/08/2014**

**(45) Data de Concessão: 04/01/2022**

**(54) Título:** SISTEMA E MÉTODO PARA INTERCALAÇÃO DE CANAL DE MEMÓRIA COM ENERGIA SELETIVA OU OTIMIZAÇÃO DE DESEMPENHO

**(51) Int.Cl.:** G06F 1/32; G06F 12/06.

**(30) Prioridade Unionista:** 08/08/2013 US 13/962,746.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** DEXTER CHUN; YANRU LI; ALEX TU; HAW-JING LO.

**(86) Pedido PCT:** PCT US2014050208 de 07/08/2014

**(87) Publicação PCT:** WO 2015/021316 de 12/02/2015

**(85) Data do Início da Fase Nacional:** 03/02/2016

**(57) Resumo:** SISTEMA E MÉTODO PARA INTERCALAÇÃO DE CANAL DE MEMÓRIA COM ENERGIA SELETIVA OU OTIMIZAÇÃO DE DESEMPENHO. Sistemas e métodos são descritos para fornecimento de intercalação de canal de memória com energia seletiva ou otimização de desempenho. Um método envolve a configuração de um mapa de endereço de memória para dois ou mais dispositivos de memória acessados através de dois ou mais canais de memória respectivos com uma região intercalada e uma região linear. A região intercalada compreende um espaço de endereço intercalado para casos de utilização de desempenho relativamente mais alto. A região linear compreende um espaço de endereço linear para casos de utilização de energia relativamente menor. Solicitações de memória são recebidas de um ou mais clientes. As solicitações de memória compreendem uma preferência por economia de energia ou desempenho. As solicitações de memória recebidas são designadas para a região linear ou região intercalada de acordo com a preferência por economia de energia ou desempenho.

**"SISTEMA E MÉTODO PARA INTERCALAÇÃO DE CANAL DE MEMÓRIA COM ENERGIA SELETIVA OU OTIMIZAÇÃO DE DESEMPENHO"**

**Descrição da Técnica Relacionada**

[0001] Muitos dispositivos de computação, incluindo dispositivos de computação portáteis tal como telefones móveis, incluem um Sistema em Chip ("SoC"). SoCs demandam um desempenho de energia cada vez maior e uma capacidade cada vez maior dos dispositivos de memória, tal como, dispositivos de memória de taxa de dados dupla (DDR). Essas demandas resultam em ambos velocidades de relógio mais altas e barramentos mais largos, que são então tipicamente divididos em múltiplos canais de memória mais estreitos a fim de permanecerem eficientes. Múltiplos canais de memória podem ser intercalados com endereço juntos para distribuir uniformemente o tráfego de memória através de dispositivos de memória e otimizar o desempenho. Os dados de memória são uniformemente distribuídos pela designação de endereços para alternar os canais de memória. Essa técnica é comumente referida como intercalação de canal simétrico.

[0002] As técnicas de intercalação de canal de memória simétrica existentes exigem que todos os canais sejam ativados. Para casos de utilização de desempenho alto, isso é intencional e necessário para se alcançar o nível desejado de desempenho. Para casos de utilização de baixo desempenho, no entanto, isso resulta em energia desperdiçada e ineficiência. De acordo, permanece uma necessidade na técnica por sistemas e métodos aperfeiçoados para fornecimento de intercalação de canal de memória.

**Sumário da Descrição**

[0003] Sistemas e métodos são descritos para fornecer intercalação de canal de memória com energia seletiva ou otimização de desempenho. Uma modalidade é um

método de intercalação de canal de memória com energia seletiva ou otimização de desempenho. Um método desses compreende: a configuração de um mapa de endereço de memória para dois ou mais dispositivos de memória acessados através de dois ou mais canais de memória respectivos com uma região intercalada e uma região linear, a região intercalada compreendendo um espaço de endereço intercalado para casos de utilização de desempenho relativamente maior e a região linear compreendendo um espaço de endereço linear para casos de utilização de energia relativamente menor; recebendo solicitações de memória de um ou mais clientes, as solicitações de memória compreendendo uma preferência por economia de energia ou desempenho; e designando solicitações de memória para a região linear ou a região intercalada de acordo com a preferência por economia de energia ou desempenho.

[0004] Outra modalidade é um sistema para fornecimento de intercalação de canal de memória com energia seletiva ou otimização de desempenho. Um sistema desses compreende um Sistema em Chip (SoC), um mapa de endereço de memória, e um intercalador de canal de memória. O SoC compreende uma ou mais unidades de processamento para geração de solicitações de memória para acessar dois ou mais dispositivos de memória externos conectados ao SoC e acessados através de dois ou mais canais de memória respectivos. As solicitações de memória compreendem uma preferência por economia de energia ou desempenho. O mapa de endereço de memória é associado com os dispositivos de memória externa e compreende uma região intercalada e uma região linear. A região intercalada compreende um espaço de endereço intercalado para casos de utilização de desempenho relativamente maiores. A região linear compreende um espaço de endereço linear para casos de utilização de energia

relativamente menores. O intercalador de canal de memória reside no SoC e é configurado para designar solicitações de memória para a região linear ou região intercalada de acordo com a preferência por economia de energia ou desempenho.

Breve Descrição dos Desenhos

[0005] Nas figuras, referencias numericas similares se referem a partes similares por todas as várias vistas a menos que indicado o contrário. Para referencias numericas com designações de caractere alfabetico tal como "102A" ou "102B", as designações de caractere alfabetico podem diferenciar duas partes ou elementos similares presentes na mesma figura. As designações de caractere alfabetico para referencias numericas podem ser omitidas quando se pretende que um número de referência englobe todas as partes possuindo a mesma referência numérica em todas as figuras.

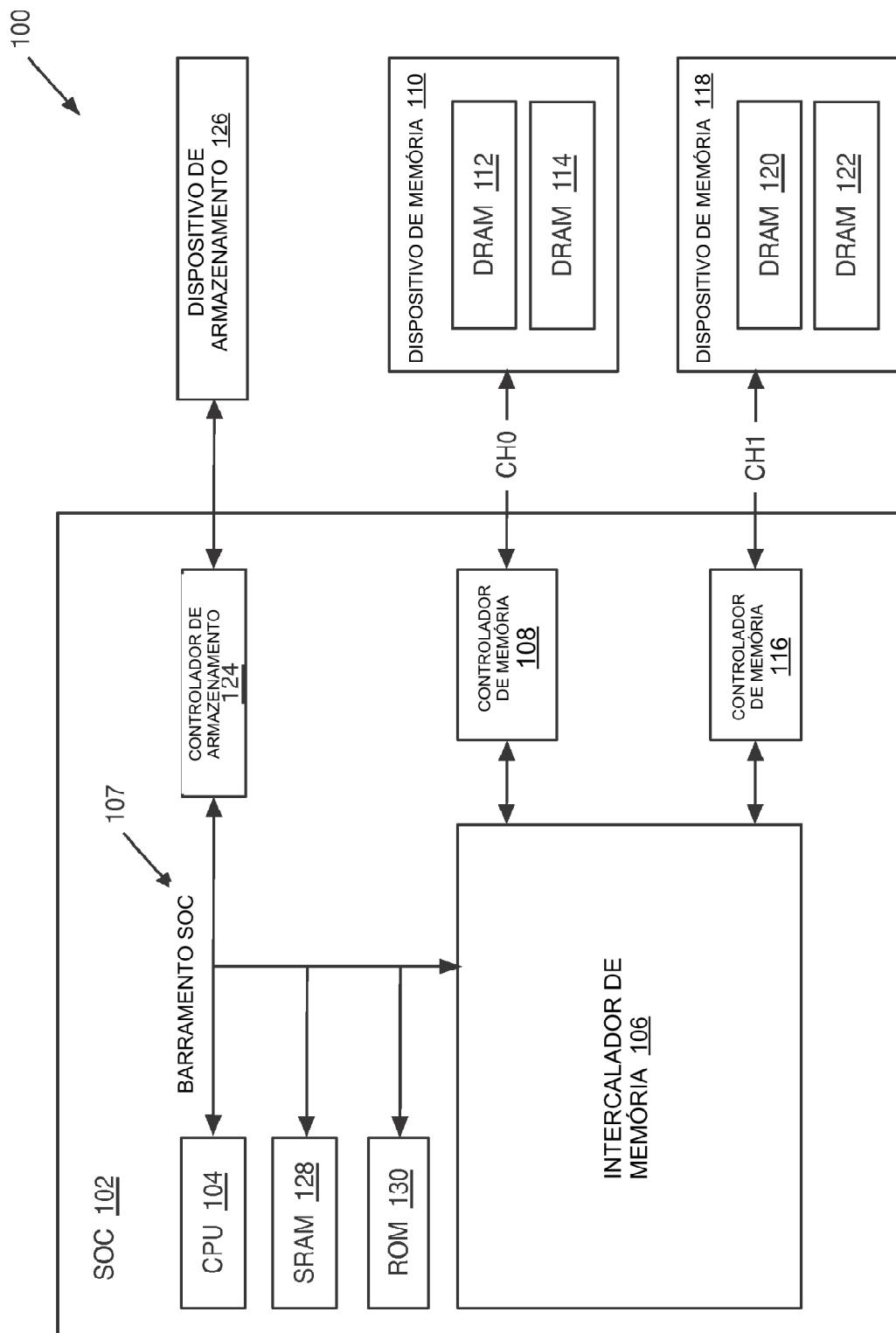

[0006] A figura 1 é um diagrama em bloco de uma modalidade do sistema para fornecimento de intercalação de canal de memória com energia seletiva ou otimização de desempenho;

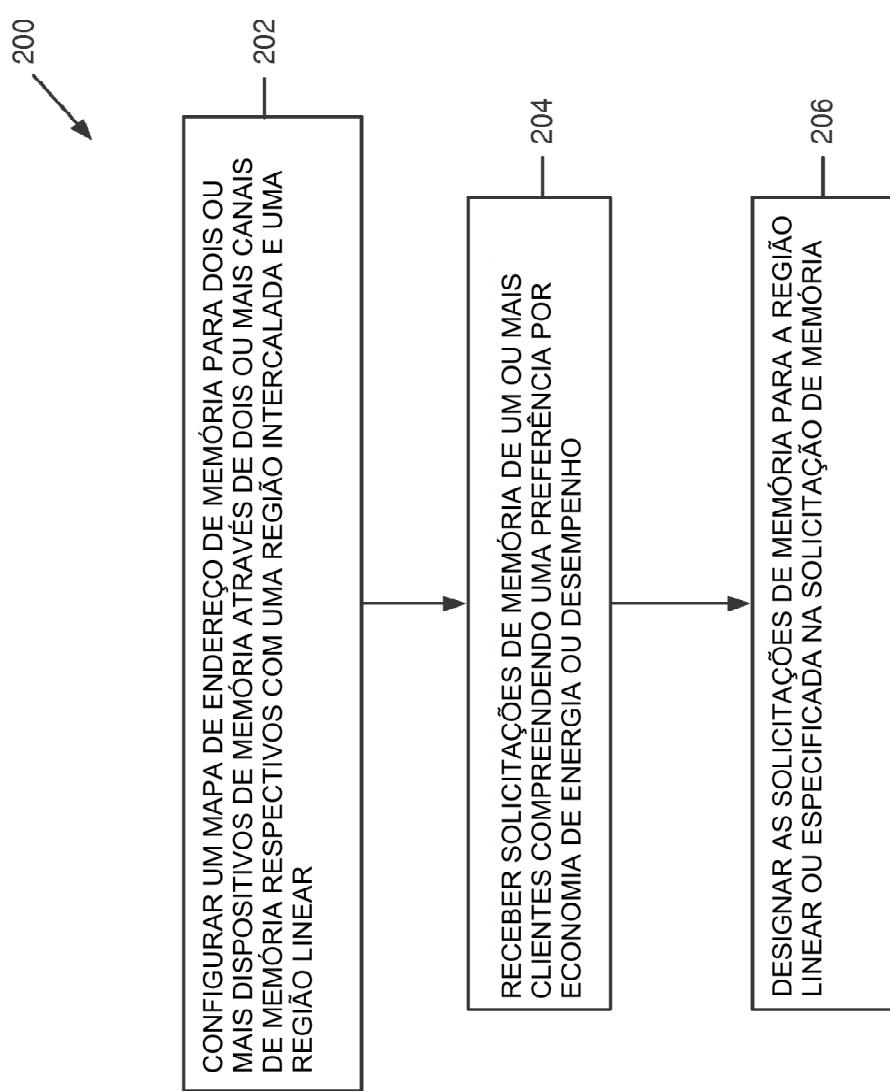

[0007] A figura 2 é um fluxograma ilustrando uma modalidade de um método implementado no sistema da figura 1 para fornecimento de intercalação de canal de memória com energia seletiva ou otimização de desempenho.

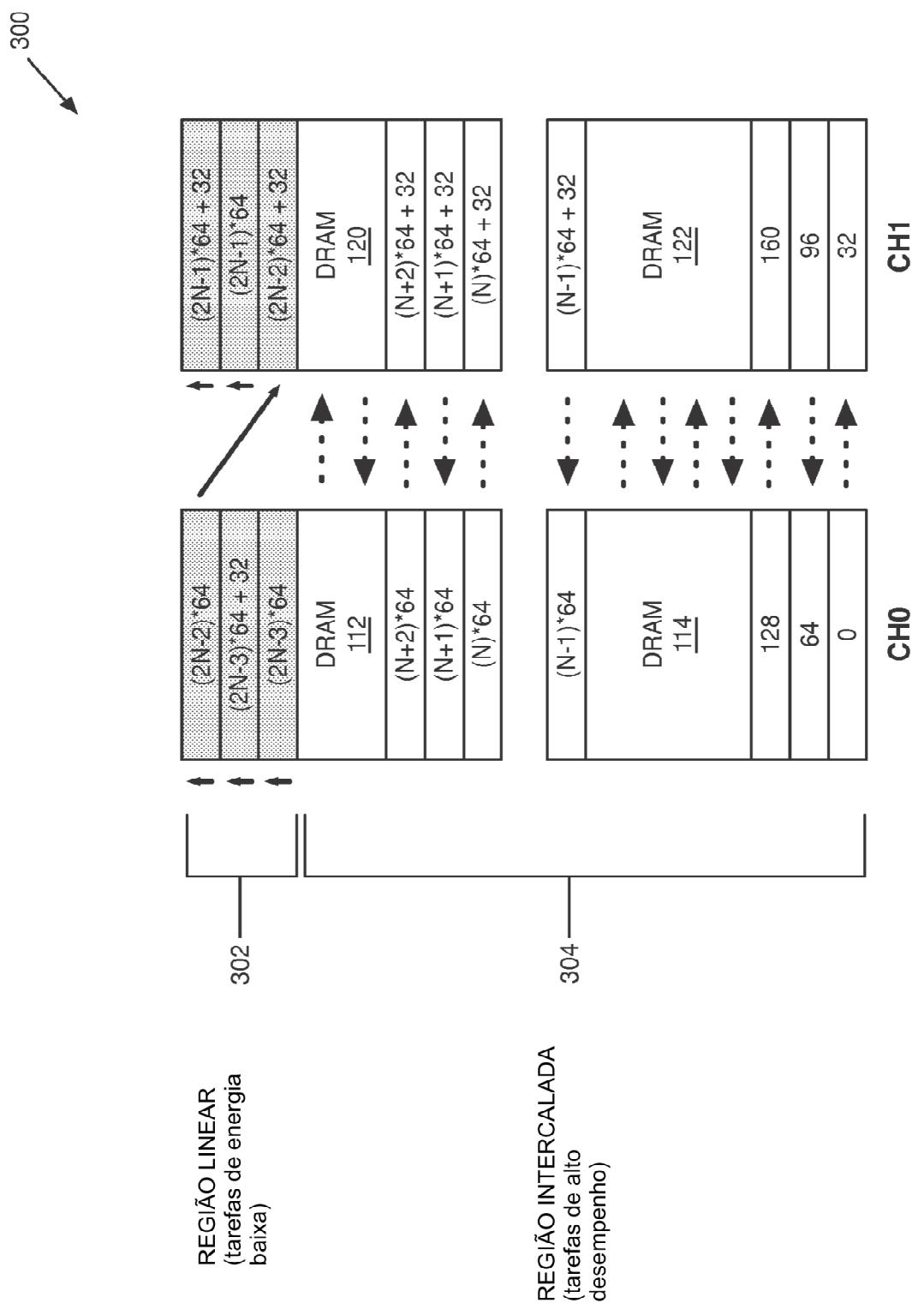

[0008] A figura 3 é um diagrama de dados/fluxograma ilustrando a estrutura e operação de um mapa de endereço de memória ilustrativo no sistema da figura 1;

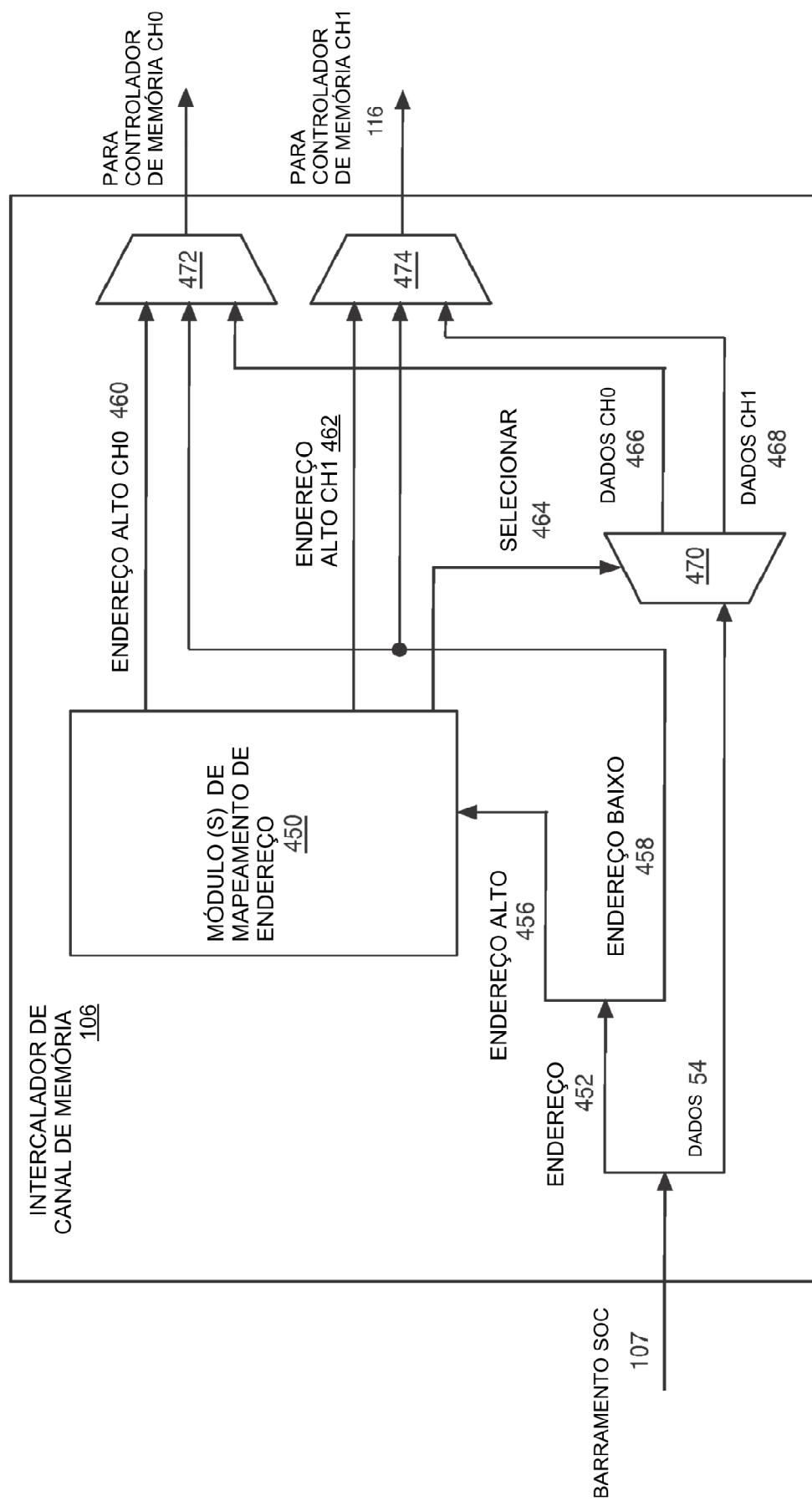

[0009] A figura 4 é um diagrama em bloco/fluxograma ilustrando a uma modalidade do intercalador de canal de memória da figura 1;

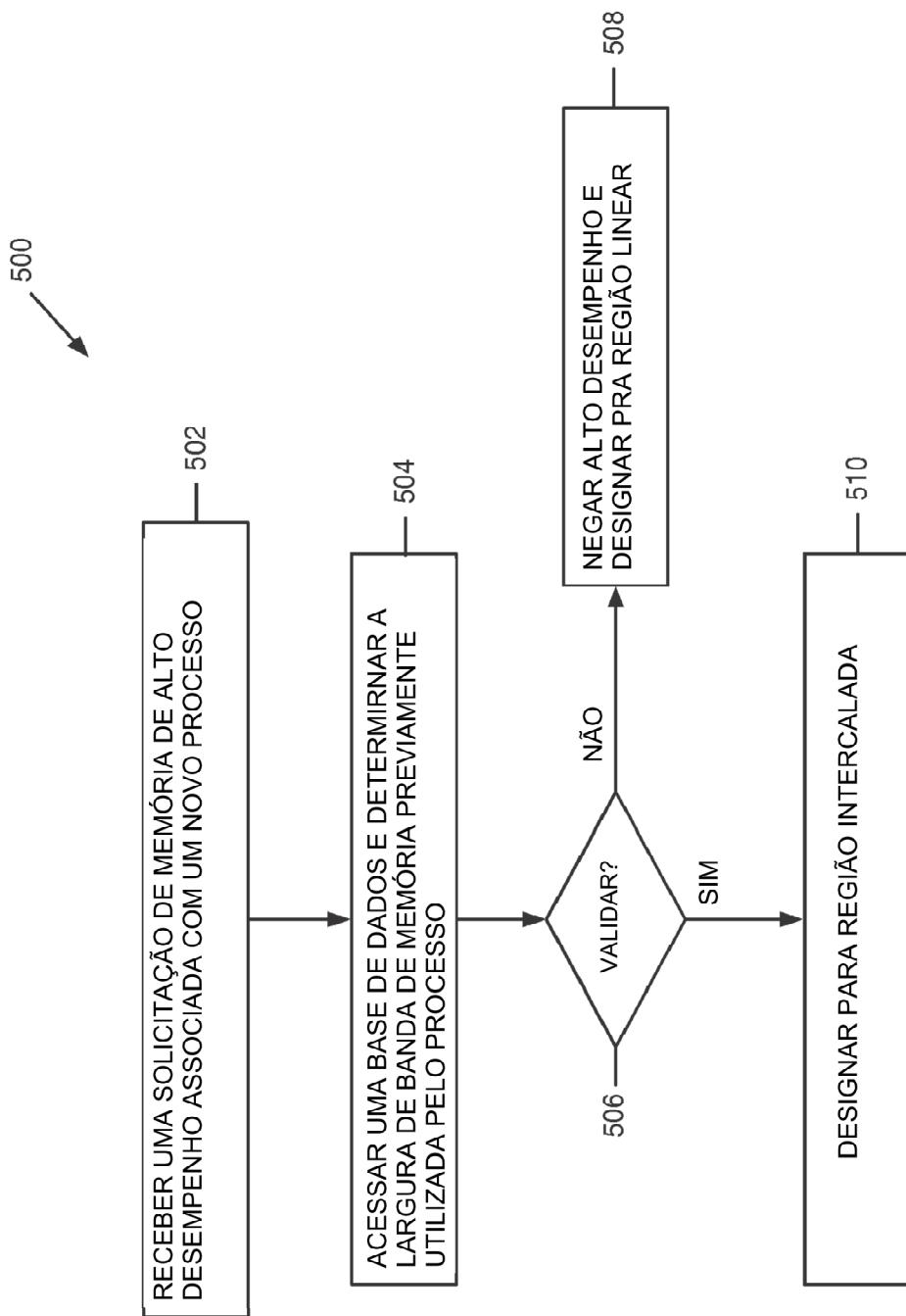

[0010] A figura 5 é um fluxograma ilustrando uma modalidade de um método de validação ou eliminação de solicitações de memória de alto desempenho;

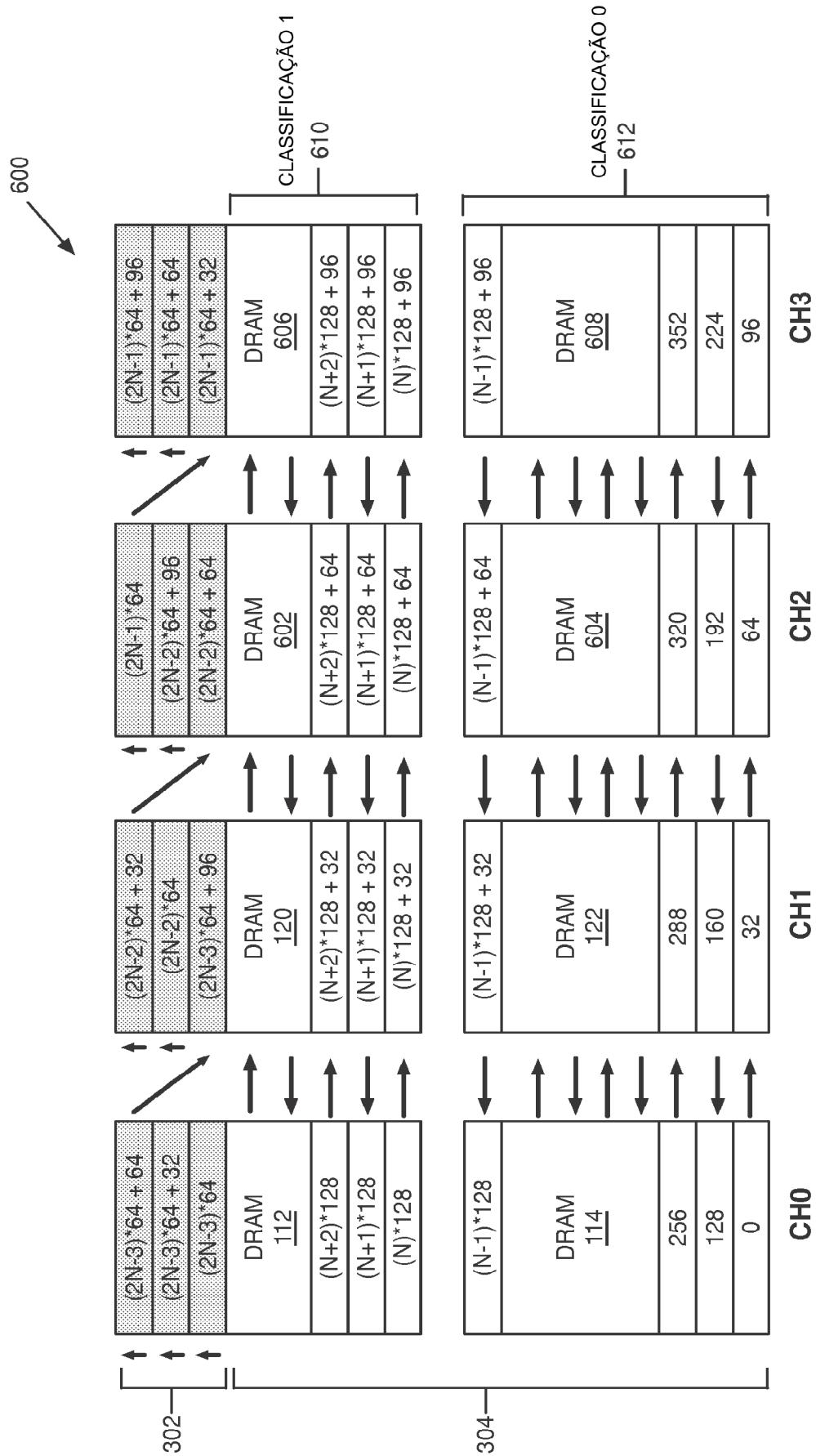

[0011] A figura 6 ilustra outra modalidade de um mapa de endereço de memória com uma região linear e uma região intercalada utilizando quatro canais de memória e duas classificações;

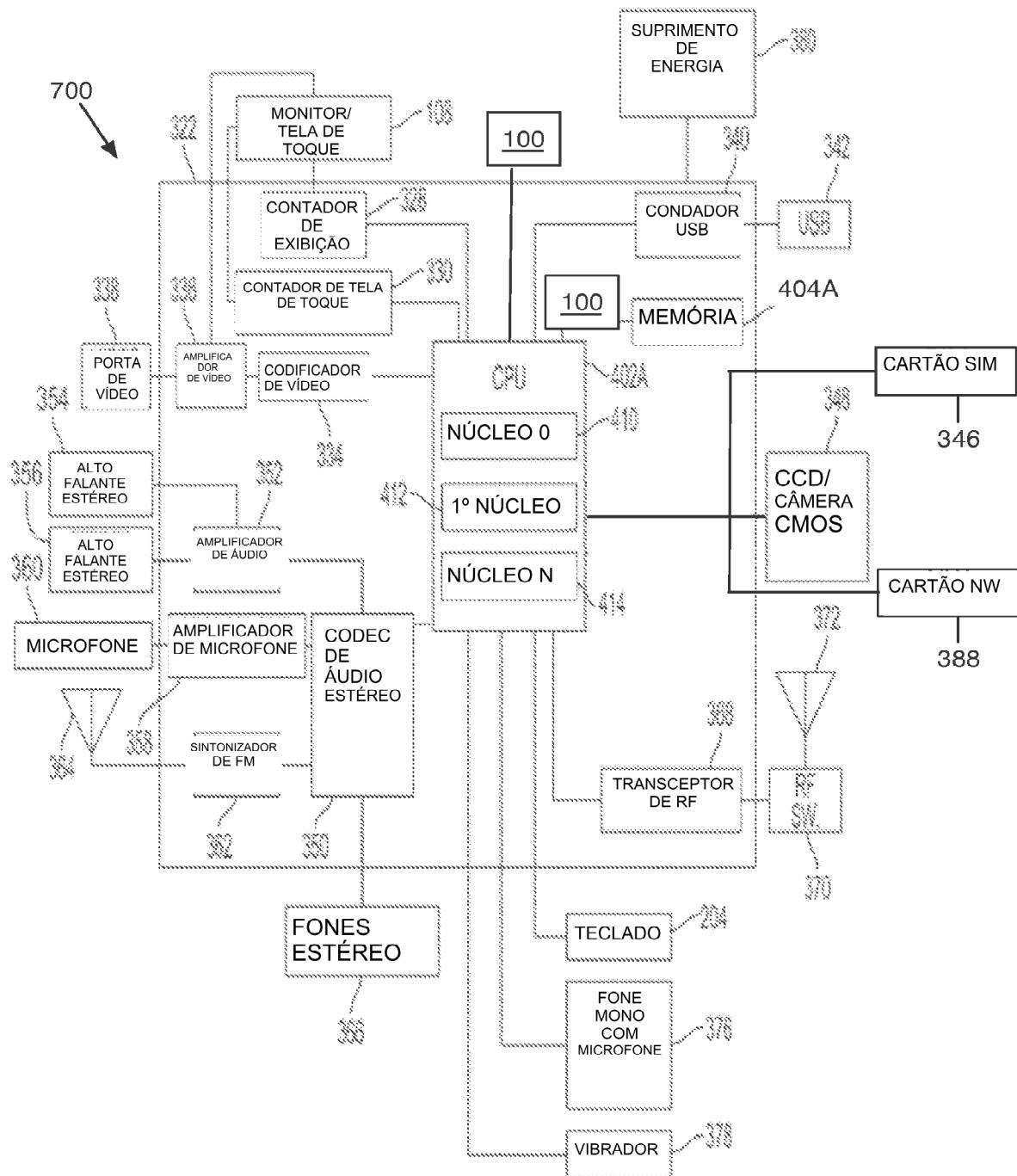

[0012] A figura 7 é um diagrama em bloco de uma modalidade de um dispositivo de computador portátil compreendendo o sistema da figura 1.

#### Descrição Detalhada

[0013] O termo "ilustrativo" é utilizado aqui para significar "servindo como um exemplo, caso ou ilustração". Qualquer aspecto descrito aqui como "ilustrativo" não deve ser necessariamente considerado como preferido ou vantajoso sobre outros aspectos.

[0014] Nessa descrição, o termo "pedidos" também pode incluir arquivos possuindo conteúdo executável, tal como: código de objeto, scripts, código de byte, arquivos de linguagem de marcação, e emendas. Adicionalmente, um "pedido" referido aqui, também pode incluir arquivos que não são executáveis por natureza, tal como documentos que possam necessitar ser abertos ou outros arquivos de dados que precisem ser acessados.

[0015] O termo "conteúdo" também pode incluir arquivos possuindo conteúdo executável, tal como: código de objeto, scripts, código de byte, arquivos de linguagem de marcação, e emendas. Adicionalmente, "conteúdo" referido aqui, também pode incluir arquivos que não são executáveis por natureza, tal como documentos que precisem ser abertos ou outros arquivos de dados que precisem ser acessados.

[0016] Como utilizado nessa descrição, os termos "componente", "base de dados", "módulo", "sistema" e

similares devem se referir a uma entidade relacionada com computador, seja ela hardware, firmware, uma combinação de hardware e software, software, ou software em execução. Por exemplo, um componente pode ser, mas não está limitado a ser, um processo rodando em um processador, um processador, um objeto, um elemento executável, uma sequência de execução, um programa e/ou um computador. Por meio de ilustração, ambos um aplicativo rodando em um dispositivo de computação e o dispositivo de computação pode ser um componente. Um ou mais componentes podem residir dentro de um processo e/ou sequência de execução, e um componente pode ser localizado em um computador e/ou distribuído entre dois ou mais computadores. Adicionalmente, esses componentes podem ser executados a partir de vários meios legíveis por computador possuindo várias estruturas de dados armazenadas nos mesmos. Os componentes podem se comunicar por meio de processos locais e/ou remotos tal como de acordo com um sinal possuindo um ou mais pacotes de dados (por exemplo, dados de um componente interagindo com outro componente em um sistema local, sistema distribuído, e/ou através de uma rede tal como a Internet com outros sistemas por meio de sinal).

[0017] Nessa descrição, os termos "dispositivo de comunicação", "dispositivo sem fio", "telefone sem fio", "dispositivo de comunicação sem fio" e "aparelho sem fio" são utilizados de forma intercambiável. Com o advento da tecnologia sem fio de terceira geração ("3G") e quarta geração ("4G"), uma maior disponibilidade de largura de banda tem permitido mais dispositivos de computação portáteis com uma maior variedade de capacidades sem fio. Portanto, um dispositivo de computação portátil pode incluir um telefone celular, um pager, um PDA, um

smartphone, um dispositivo de navegação, ou um computador portátil com uma conexão ou link sem fio.

[0018] A figura 1 ilustra um sistema 100 para fornecimento de intercalação de canal de memória com desempenho seletivo ou otimização de energia. O sistema 100 pode ser implementado em qualquer dispositivo de computação, incluindo um computador pessoal, uma estação de trabalho, um servidor, um dispositivo de computação portátil (PCD), tal como um telefone celular, um assistente digital portátil (PDA), um console de jogos portátil, um computador palmtop, ou um computador tablet.

[0019] Como ilustrado na modalidade da figura 1, o sistema 100 compreende um Sistema em Chip (SoC) 102 compreendendo vários componentes em chip e vários componentes externos conectados ao SoC 102. O SoC 102 compreende uma ou mais unidades de processamento, um intercalador de canal de memória 106, um controlador de armazenamento 124, e memória embutida (por exemplo, uma memória de acesso randômico estática (SRAM) 128, memória de leitura apenas (ROM) 130, etc.) interconectados por um barramento SoC 107. O controlador de armazenamento 124 é eletricamente conectado a e se comunica com um dispositivo de armazenamento externo 126. Como é sabido na técnica, o intercalador de canal de memória 106 recebe solicitações de escrita/leitura de memória associadas com a CPU 104 (ou outros clientes de memória) e distribui os dados de memória entre dois ou mais controladores de memória, que são conectados aos dispositivos de memória externa respectivos através de um canal de memória dedicado. No exemplo da figura 1, o sistema 100 compreende dois dispositivos de memória 110 e 118. O dispositivo de memória 110 é conectado ao controlador de memória 108 e comunica através de um primeiro canal de memória (CH0). O dispositivo de memória

118 é conectado ao controlador de memória 116 e se comunica através de um segundo canal de memória (CH1).

[0020] Deve-se apreciar que qualquer número de dispositivos de memória, controladores de memória, e canais de memória podem ser utilizados no sistema 100 com qualquer tipo, tamanho ou configuração desejável da memória (por exemplo, memória de taxa de dados dupla (DDR)). Na modalidade da figura 1, o dispositivo de memória 110 suportado através do canal CH0 compreende dois dispositivos de memória de acesso randômico dinâmica (DRAM): uma DRAM 112 e uma DRAM 114. O dispositivo de memória 118 suportado através do canal CH1 também compreende dois dispositivos DRAM: uma DRAM 120 e uma DRAM 122.

[0021] O intercalador de canal de memória 106 compreende um intercalador de canal de memória especialmente configurado para fornecer seletivamente a otimização de desempenho e economia de energia. O intercalador de canal de memória 106 é configurado para fornecer seletivamente as regiões de memória de alto desempenho (intercalada) e baixo desempenho (linear). A figura 3 ilustra um mapa de endereço de memória ilustrativo 300 controlado pelo intercalador de canal de memória 106. O mapa de endereço de memória 300 será descrito para ilustrar a operação, arquitetura, e funcionalidade gerais do sistema 100 e do intercalador de canal de memória 106. O mapa de endereço de memória 300 corresponde ao sistema ilustrativo 100 ilustrado na figura 1 com o dispositivo de memória 110 compreendendo DRAMs 112 e 114 (acessadas através do canal de memória CH0) e o dispositivo de memória 118 compreendendo DRAMs 120 e 122 (acessadas através do canal de memória CH1).

[0022] O mapa de endereço de memória 300 compreende uma região linear 302 e uma região intercalada

304. A região linear 302 pode ser utilizada para casos de utilização de energia relativamente baixa e/ou tarefas, e a região intercalada 304 pode ser utilizada para casos de utilização e/ou tarefas de energia relativamente alta. Cada região compreende um espaço de endereço de memória alocado em separado com uma faixa de endereço correspondente dividida entre os dois canais de memória CH0 e CH1. A região intercalada 304 compreende um espaço de endereço intercalado, e a região linear 302 compreende um espaço de endereço linear.

[0023] Com referência ao exemplo da figura 3, e com relação ao espaço de endereço intercalado, um primeiro endereço (endereço 0) pode ser designado para um endereço inferior associado com a DRAM 114 e o canal de memória CH0. O próximo endereço na faixa de endereço intercalado (endereço 32) pode ser designado para um endereço inferior associado com DRAM 122 e o canal de memória CH1. Dessa forma, um padrão de endereços alternados pode ser "striped" ou intercalado através dos canais de memória CH0 e CH1, ascendendo ao topo ou último endereço associado com a DRAM 112 e DRAM 112, que definem um limite entre a região intercalada 304 e a região linear 302. Na região intercalada 304, as setas tracejadas horizontais entre os canais CH0 e CH1 ilustram como os endereços realizando o movimento de "pingue-pongue" entre os canais de memória. Os clientes solicitando recursos de memória (por exemplo, CPU 104) para leitura/escrita de dados para os dispositivos de memória podem ser servidos por ambos os canais de memória CH0 e CH1 visto que os endereços de dados podem ser considerados aleatórios e, portanto, podem ser uniformemente distribuídos através de ambos os canais CH0 e CH1.

[0024] A região linear 302 compreende faixas de endereço de memória consecutivas e separadas dentro do mesmo canal. Como ilustrado na modalidade da figura 3, uma primeira faixa de endereços de memória consecutivos pode ser designada para a DRAM 112 em CH0, e uma segunda faixa de endereços consecutivos pode ser designada para DRAM 120 em CH1. O próximo endereço em DRAM 112 acima do limite intercalado/linear pode receber o primeiro endereço  $(2N-3)*64$  no espaço de endereço linear. As setas verticais ilustram que os endereços consecutivos são designados dentro de CH0 até um último endereço ou endereço superior na DRAM 112 ser alcançado (endereço  $(2N*64)$ ). Quando o último endereço disponível em CH0 é alcançado, o próximo endereço no espaço de endereço linear pode ser designado para o próximo endereço disponível na DRAM 120 acima do limite intercalado/linear (endereço  $(2N-2)*64+32$ ). Então, o esquema de alocação segue os endereços de memória consecutivos em CH1 até que um endereço superior seja alcançado (endereço  $(2N-1)*64+32$ ).

[0025] Dessa forma, deve-se apreciar que os dados de caso de utilização de baixo desempenho podem ser contidos completamente em qualquer canal CH0 ou canal CH1. Em operação, apenas um dos canais CH0 e CH1 pode estar ativo enquanto o outro canal é colocado em um modo inativo ou "de atualização automática" para conservar energia de memória. Isso pode ser estendido para qualquer número de N canais de memória.

[0026] A figura 2 ilustra um método 200 implementado pelo sistema 100 (figura 1) para fornecimento de intercalação de canal de memória com desempenho seletivo ou otimização de energia. No bloco 202, um mapa de endereço de memória 300 é configurado para os dispositivos de memória disponíveis (por exemplo, DRAMs 112, 114, 120 e

122) acessados através de dois ou mais canais disponíveis (por exemplo, canais de memória CH0 e CH1) com uma região intercalada 304 e uma região linear 302. O mapa de endereço de memória 300 pode ser configurado com base em casos de utilização de alto e baixo desempenhos, impressão ou tamanho da memória esperada. Durante a inicialização, com base no perfil de plataforma, o intercalador de canal de memória 106 pode fornecer uma quantidade predeterminada de espaço de memória intercalado e linear. Durante o tempo de funcionamento, um sistema operacional pode alocar a região intercalada 304 para solicitações de cliente por alto desempenho, tal como, a unidade de processamento gráfico (GPU), o monitor, recursos de multimídia, câmera, etc. O sistema operacional pode alocar memória linear para solicitações de cliente por desempenho relativamente mais baixo e/ou para todas as outras solicitações de cliente. Por exemplo, a região linear 302 pode ser alocada para recursos de sistema operacional, aplicativos de desempenho baixo geral, serviços, etc. Deve-se apreciar que a memória pode ser dinamicamente alocada para a GPU para a região intercalada 304. Em outras modalidades, referidas como alocação estática, a GPU pode utilizar memória que foi predeterminada, por exemplo, durante a inicialização para uso da região intercalada 304 a fim de alcançar um alto desempenho.

[0027] Em uma modalidade, a alocação de memória para a região linear 302 e a região intercalada 304 pode ser configurada com base nos casos de utilização desejáveis. A alocação de memória em regiões lineares diferentes pode ser agrupada com base nos casos de utilização. Por exemplo, um primeiro caso de utilização de "economia de energia" pode ser permitido para acessar um primeiro espaço de endereço linear associado com CH0, e um

segundo caso de utilização de "economia de energia" pode ser permitido para acessar um segundo espaço de endereço linear associado com CH1. Dessa forma, a economia de energia de memória pode ser realizada no canal de memória enquanto o outro está ativo.

[0028] Com referência novamente à figura 2, no bloco 204, o intercalador de canal de memória 106 pode receber solicitações de memória de um ou mais clientes (por exemplo, CPU 104) solicitando recursos de memória. Uma solicitação de memória pode incluir uma "dica", parâmetros ou outros dados indicando uma preferência por economia de energia ou desempenho. Em uma modalidade, a preferência por energia/desempenho pode ser especificada através de uma chamada de sistema para um sistema operacional. A esse respeito, o sistema 100 pode incluir um sistema operacional (não ilustrado) que fornece suporte para alocação de memória. O sistema operacional pode ter a capacidade de alocar memória de pilhas específicas como indicado por um chamador. O intercalador de canal de memória 106 e o sistema 100 fornecem a capacidade de especificar um tipo de memória (isso é, intercalado X linear) de acordo com, por exemplo, um grau de preferência por economia de energia X desempenho e, dessa forma, alcançar a economia de energia de memória e/ou rendimento de largura de banda alto.

[0029] Por exemplo, o acesso à memória não uniforme (NUMA), que é utilizado no multiprocessamento, pode realizar alocação de memória com base nos nós de memória relativos a um processador (por exemplo, CPU 104). Sob NUMA, um processador tem informação da diferença de desempenho de diferentes nós de memória, e pode ser capaz de alocar de forma inteligente a memória a partir dos nós preferidos. O sistema 100 pode implementar esse mecanismo para alocar memória a partir de uma lista de nós

disponíveis com inteligência para alocar a memória a partir do nó que resulta em um melhor desempenho ou com base nas características de consumo de energia. Adicionalmente, em alguns sistemas operacionais (por exemplo, Linux Android®), o alocador de memória pode ter um argumento de entrada para indicar uma ou mais pilhas de memória a partir das quais se aloca, com o fallback ordenado de acordo com qual pilha de memória foi a primeira a ser adicionada através de chamadas durante a inicialização. O intercalador de canal de memória 106 pode suportar tal mecanismo para alocar a memória a partir de um tipo de pilha específico com base em qualquer um dentre o desempenho ou o consumo de energia como solicitado pelos clientes.

[0030] No bloco 206, o intercalador de canal de memória 106 designa as solicitações de memória recebidas para a região linear 302 ou região intercalada 304 de acordo com a preferência especificada na solicitação de memória (ou de outra forma) e o mapa de endereço de memória 300.

[0031] Como ilustrado no método 500 da figura 5, o intercalador de canal de memória 106 também pode fornecer um mecanismo para validação de solicitações de memória de alto desempenho contra uma base de dados compreendendo um arquivo de histórico de utilização de largura de banda de memória para tipos específicos de tarefas, processos, etc. No bloco 502, o intercalador de canal de memória 106 pode receber uma solicitação de memória de alto desempenho associada com um novo processo. No bloco 504, o arquivo de histórico pode ser acessado para determinar a largura de banda de memória previamente utilizada pelo processo.

[0032] Dessa forma, as solicitações de memória podem ser alocadas de acordo com um rastreamento de histórico de demanda por largura de banda para cada tarefa

em andamento. Em uma modalidade, os contadores de transação podem ser utilizados para arquivar a largura de banda de demanda para cada uma das tarefas em andamento no sistema 100 e acumulando um histórico para cada nome de processo, que pode ser armazenado em um sistema de arquivo ou outra memória. Um gerenciador de memória pode acessar a base de dados quando da alocação de memória a novas tarefas. Como descrito acima, a tarefa pode fornecer uma dica de que é de alto desempenho ou baixo desempenho. A tarefa também pode especificar se o armazenador é compartilhável. O gerenciador de memória pode acessar a base de dados para validar a solicitação. Se o alto desempenho não tiver sido empiricamente arquivado e justificado, o alocador de memória pode negar a dica e alocar apenas a memória de baixo desempenho para economizar energia. O alocador de memória também pode confirmar se o armazenador foi declarado como compartilhável e aderir à dica original se for compartilhável visto que uma tarefa diferente utilizando o mesmo armazenador compartilhado pode exigir uma largura de banda alta.

[0033] Com referência novamente à figura 5, no bloco de decisão 506, o intercalador de canal de memória 106 determina se a solicitação de memória de alto desempenho foi validada. Se a largura de banda anterior não corresponder a um limite predeterminado para designação para a região intercalada 304, a solicitação de memória pode ser negada e, em vez disso, designada para a região linear 302 (bloco 508). Se a solicitação de memória de alto desempenho for validada, no entanto, a solicitação de memória pode ser designada para a região intercalada (bloco 510).

[0034] A figura 4 é um diagrama esquemático/fluxograma ilustrando a arquitetura, operação

e/ou funcionalidade de uma modalidade do intercalador de canal de memória 106. O intercalador de canal de memória 106 recebe o registro no barramento SoC 107 e fornece saídas para os controladores de memória 108 e 116 (canais de memória CH0 e CH1, respectivamente) através de barramentos de controlador de memória separados. Os barramentos de controlador de memória podem rodar a meia taxa do barramento SoC 107 com o rendimento de dados líquido sendo combinado. Os módulos de mapeamento de endereço 450 podem ser programados através do barramento SoC 107. Os módulos de mapeamento de endereço 450 podem configurar e acessar o mapa de memória de endereço 300, como descrito acima, com a região linear 302 e a região intercalada 304. O tráfego de dados que entra no barramento SoC 107 é direcionado para um seletor de dados 470, que envia os dados para os controladores de memória 108 e 116 através de componentes de mistura 472 e 474, respectivamente, com base em um sinal de seleção 464 fornecido pelos módulos de mapeamento de endereço 450. Para cada pacote de tráfego, um endereço alto 456 entra no módulo de mapeamento de endereço 450. Os módulos de mapeamento de endereço 450 compararam o endereço alto 456 com os endereços de região linear e intercalada pré-programados, realiza a reordenação de posição de bit de endereço, e então envia a mesma para um endereço alto CH0 460 ou endereço alto CH1 462 com base em parâmetros de intercalação. O sinal de seleção 464 específica se CH0 ou CH1 foi selecionado. Os componentes de mistura 472 e 474 podem compreender uma recombinação dos endereços altos 460 e 462, endereço baixo 405, e dados CH0 466 e dados CH1 468.

[0035] A figura 6 ilustra outra modalidade de um mapa de endereço de memória 600 adaptado para quatro canais de memória e utilizando uma pluralidade de classificações.

O mapa de endereço de memória 600 adiciona dois canais de memória CH2 e CH3, em comparação com o mapa de endereço de memória 300 (figura 3) discutido acima. O canal de memória CH2 é associado com DRAMs adicionais 602 e 604. O canal de memória CH3 é associado com DRAMs adicionais 606 e 608. Como ilustrado na figura 6, o mapa de endereço de memória 600 fornece um esquema de classificação (classificação 1 e classificação 0), cada um com configurações de intercalação personalizadas para fornecer um equilíbrio desejado entre o desempenho e o consumo de energia. A região linear 302 pode estar na classificação 1 e utilizar, por exemplo, um mecanismo de intercalação DRAM de Banco-Fileira-Coluna (BRC) para fornecer economia de energia. Uma primeira parte 610 da região intercalada 304 (que reside nas DRAMs 112, 120, 602 e 606) também pode estar na classificação 1 e utilizar um mecanismo de intercalação DRAM de Fileira-Banco-Coluna para desempenho. Uma segunda parte 612 da região intercalada 304 (que engloba toda a memória disponível nas DRAMs 114, 122, 604 e 608) pode estar em uma classificação diferente (isso é, classificação 0). DRAMs 114, 122, 604 e 608 podem entrar na classificação 0 utilizando o mecanismo de intercalação DRAM BRC para desempenho.

[0036] Como mencionado acima, o sistema 100 pode ser incorporado em qualquer sistema operacional desejável. A figura 7 ilustra o sistema 100 incorporado a um dispositivo de computação portátil ilustrativo (PCD) 700. O sistema 100 pode ser incluído no SoC 322, que pode incluir uma CPU de múltiplos núcleos 402A. A CPU de múltiplos núcleos 402A pode incluir um núcleo zero 410, um primeiro núcleo 412, e um núcleo N 414. Um dos núcleos pode compreender, por exemplo, uma unidade de processamento gráfica (GPU) com um ou mais dos outros compreendendo a CPU

104 (figura 1). De acordo com modalidades ilustrativas alternativas, a CPU 402a também pode compreender os tipos de núcleo singular e não um que possua múltiplos núcleos, caso no qual a CPU 104 e a GPU podem ser processadores dedicados, como ilustrado no sistema 100.

[0037] Um controlador de exibição 328 e um controlador de tela de toque 330 podem ser acoplados à CPU 402a. Por sua vez, o monitor de tela de toque 108 externo ao sistema em chip 322 pode ser acoplado ao controlador de exibição 328 e ao controlador de tela de toque 330.

[0038] A figura 7 ilustra adicionalmente que um codificador de vídeo 334, por exemplo, um codificador de linha de alternância de fase (PAL), um codificador sequencial color a memoire (SECAM), ou um codificador do comitê nacional de sistemas de televisão (NTSC), é acoplado à CPU de múltiplos núcleos 402A. Adicionalmente, um amplificador de vídeo 336 é acoplado ao codificador de vídeo 334 e ao monitor de tela de toque 108. Além disso, uma porta de vídeo 338 é acoplada ao amplificador de vídeo 336. Como ilustrado na figura 7, um controlador de barramento serial universal (USB) 340 é acoplado à CPU de múltiplos núcleos 402A. Além disso, uma porta USB 342 é acoplada ao controlador USB 340. A memória 404A e um cartão de módulo de identidade de assinante (SIM) 346 também podem ser acoplados à CPU de múltiplos núcleos 402A. A memória 404A pode compreender dispositivos de memória 110 e 118 (figura 1), como descrito acima. O sistema 100 (figura 1) pode ser acoplado à CPU 402A.

[0039] Adicionalmente, como ilustrado na figura 7, uma câmera digital 348 pode ser acoplada à CPU de múltiplos núcleos 402A. Em um aspecto ilustrativo, a câmera digital 348 é uma câmera de dispositivo acoplado à carga

(CCD) ou uma câmera semicondutora de óxido de metal complementar (CMOS).

[0040] Como ilustrado adicionalmente na figura 7, um codificador-decodificador de áudio estéreo (CODEC) 350 pode ser acoplado à CPU de múltiplos núcleos 402A. Ademais, um amplificador de áudio 352 pode ser acoplado ao CODEC de áudio estéreo 350. Em um aspecto ilustrativo, um primeiro alto falante estéreo 354 e um segundo alto falante estéreo 356 são acoplados ao amplificador de áudio 352. A figura 7 ilustra que um amplificador de microfone 358 também pode ser acoplado ao CODEC de áudio estéreo 350. Adicionalmente, um microfone 360 pode ser acoplado ao amplificador de microfone 358. Em um aspecto em particular, um sintonizador de rádio de modulação de frequência (FM) 362 pode ser acoplado ao CODEC de áudio estéreo 350. Além disso, uma antena de FM 364 é acoplada ao sintonizador de rádio FM 362. Adicionalmente, fones estéreo 366 podem ser acoplados ao CODEC de áudio estéreo 350.

[0041] A figura 7 ilustra adicionalmente que um transceptor de frequência de rádio (RF) 368 pode ser acoplado à CPU de múltiplos núcleos 402A. Um comutador de RF 370 pode ser acoplado ao transceptor de RF 368 e uma antena de RF 372. Como ilustrado na figura 7, um teclado 204 pode ser acoplado à CPU de múltiplos núcleos 402A. Além disso, um fone mono com um microfone 376 pode ser acoplado à CPU de múltiplos núcleos 402A. Adicionalmente, um dispositivo vibrador 378 pode ser acoplado à CPU de múltiplos núcleos 402A.

[0042] A figura 7 também ilustra que um suprimento de energia 380 pode ser acoplado ao sistema em chip 322. Em um aspecto em particular, o suprimento de energia 380 é um suprimento de energia de corrente direta (DC) que fornece energia para vários componentes do PCD 700

que adquirem energia. Adicionalmente, em um aspecto em particular, o suprimento de energia é uma bateria DC recarregável ou um suprimento de energia DC que é derivado de um transformador de corrente alternada (AC) para DC que é conectado a uma fonte de energia AC.

[0043] A figura 7 indica adicionalmente que PCD 700 também pode incluir um cartão de rede 388 que pode ser utilizado para acessar uma rede de dados, por exemplo, uma rede de área local, uma rede de área pessoal, ou qualquer outra rede. O cartão de rede 388 pode ser um cartão de rede Bluetooth, um cartão de rede WiFi, um cartão de rede de área pessoal (PAN), um cartão de rede de tecnologia de energia ultra baixa de rede de área pessoal (PeANUT), um sintonizador de televisão/cabo/satélite, ou qualquer outro cartão de rede bem conhecido da técnica. Adicionalmente, o cartão de rede 388 pode ser incorporado a um chip, isso é, o cartão de rede 388 pode ser uma solução completa em um chip, e pode não ser um cartão de rede separado 388.

[0044] Como apresentado na figura 7, o monitor de tela de toque 108, a porta de vídeo 338, a porta USB 342, a câmera 348, o primeiro alto falante estéreo 354, o segundo alto falante estéreo 356, o microfone 360, a antena FM 364, os fones estéreo 366, o comutador de RF 370, a antena de RF 372, o teclado 374, o fone mono 376, o vibrador 378, o suprimento de energia 380 pode ser externo ao sistema em chip 322.

[0045] Deve-se apreciar que uma ou mais das etapas de método descritas aqui podem ser armazenadas na memória como instruções de programa de computador, tal como módulos descritos acima. Essas instruções podem ser executadas por qualquer processador adequado em combinação com o módulo correspondente para realização dos métodos descritos aqui.

[0046] Determinadas etapas nos processos ou fluxos de processo nessa especificação precedem naturalmente outras para a invenção funcionar como descrito. No entanto, a invenção não está limitada à ordem das etapas descritas se tal ordem ou sequência não alterar a funcionalidade da invenção. Isso é, é reconhecido que algumas etapas podem ser realizadas antes, depois ou em paralelo (substancialmente simultaneamente) com outras etapas sem se distanciar do escopo e espírito da invenção. Em alguns casos, determinadas etapas podem ser omitidas ou não realizadas sem se distanciar da invenção. Adicionalmente, palavras como "doravante", "então", "a seguir", etc. não devem limitar a ordem das etapas. Essas palavras são simplesmente utilizadas para orientar o leitor através da descrição do método ilustrativo.

[0047] Adicionalmente, um dos versados na técnica de programação pode escrever um código de computador ou identificar hardware e/ou circuitos adequados para implementação da invenção descrita sem dificuldade com base nos fluxogramas e descrição associada nessa especificação, por exemplo.

[0048] Portanto, a descrição de um conjunto particular de instruções de código de programa ou dispositivos de hardware detalhados não é considerada necessária para uma compreensão adequada de como criar e fazer uso da invenção. A funcionalidade inventiva dos processos implementados por computador reivindicados é explicada em maiores detalhes na descrição acima e em conjunto com as figuras que podem ilustrar vários fluxos de processo.

[0049] Em um ou mais aspectos ilustrativos, as funções descritas podem ser implementadas em hardware, software, firmware ou qualquer combinação dos mesmos. Se

implementadas em software, as funções podem ser armazenadas em ou transmitidas como uma ou mais instruções ou código em um meio legível por computador. O meio legível por computador inclui ambos o meio de armazenamento em computador e o meio de comunicação incluindo qualquer meio que facilite a transferência de um programa de computador de um lugar para outro. Um meio de armazenamento pode ser qualquer meio disponível que possa ser acessado por um computador. Por meio de exemplo, e não de limitação, tal meio legível por computador pode compreender RAM, ROM, EEPROM, flash NAND, flash NOR, M-RAM, P-RAM, R-RAM, CD-ROM ou outro armazenamento em disco ótico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnético ou qualquer outro meio que possa ser utilizado para portar ou armazenar código de programa desejado na forma de instruções ou estruturas de dados e que possa ser acessado por um computador.

[0050] Além disso, qualquer conexão é adequadamente chamada de meio legível por computador. Por exemplo, se o software for transmitido a partir de um sitio de rede, servidor ou outra fonte remota utilizando um cabo coaxial, um cabo de fibra ótica, um par torcido, uma linha de assinante digital ("DSL"), ou tecnologias sem fio tal como infravermelho, rádio e micro-ondas, então o cabo coaxial, o cabo de fibra ótica, o par torcido, DSL ou tecnologias sem fio tal como infravermelho, rádio e micro-ondas estão incluídos na definição de meio.

[0051] Disquete e disco, como utilizados aqui, incluem disco compacto ("CD"), disco a laser, disco ótico, disco versátil digital ("DVD"), disquete e disco blu-ray onde disquetes normalmente reproduzem os dados magneticamente, enquanto discos reproduzem dados oticamente

com lasers. Combinações do acima exposto também devem ser incluídas dentro do escopo do meio legível por computador.

[0052] Modalidades alterantivas se tornarão aparentes aos versados na técnica à qual a invenção pertence sem se distanciar de seu espírito e escopo. Portanto, apesar de aspectos selecionados terem sido ilustrados e descritos em detalhe, será compreendido que várias substituições e alterações podem ser feitas aqui sem se distanciar do espírito e escopo da presente invenção, como definido pelas reivindicações a seguir.

## REIVINDICAÇÕES

1. Método de intercalação de canal de memória (200) com energia seletiva ou otimização de desempenho, o método **caracterizado pelo fato de que** compreende:

a configuração (202) de um mapa de endereço de memória (300) para pelo menos um primeiro dispositivo de memória (110) e um segundo dispositivo de memória (118),

em que o primeiro dispositivo de memória (110) está conectado à um primeiro controlador de memória (108) e se comunica através de um primeiro canal de memória ( $CH_0$ ) e em que o segundo dispositivo de memória (118) está conectado à um segundo controlador de memória (116) e se comunica através de um segundo canal de memória ( $CH_1$ ),

em que o mapa de endereço de memória (300) compreende uma região linear (302) e uma região intercalada (304), cada região (302, 304) compreendendo espaço de endereço de memória alocada separada com uma faixa de endereços correspondentes dividida entre os dois canais de memória ( $CH_0$ ,  $CH_1$ ), a região intercalada (304) compreendendo um espaço de endereço intercalado para casos de utilização de desempenho relativamente mais altos e a região linear (302) compreendendo um espaço de endereço linear para casos de utilização de energia relativamente mais baixa;

o recebimento (204), em um intercalador de canal de memória (106), de solicitações de memória de um ou mais clientes (104), as solicitações de memória compreendendo uma preferência por economia de energia ou desempenho;

a designação (206), pelo intercalador de canal de memória (106), das solicitações de memória para a região linear (302) ou região intercalada (304) de acordo com a preferência para economia de energia ou desempenho,

em que endereço linear compreende uma primeira faixa de endereço associada com o primeiro dispositivo de memória (110) e acessada através do primeiro canal de memória ( $CH_0$ ) e uma segunda faixa de endereço associada com o segundo dispositivo de memória (118) e acessada através do segundo canal de memória ( $CH_1$ ),

em que a designação das solicitações de memória para a região linear (302) compreende a utilização da primeira faixa de endereço associada com o primeiro dispositivo de memória (110) enquanto o segundo dispositivo de memória (118) é colocado em um modo de economia de energia,

em que o método compreende adicionalmente:

a validação de solicitações de memória possuindo a preferência por desempenho com uma base de dados compreendendo um arquivo de histórico da largura de banda de memória; e

se não for validado, a eliminação da preferência por desempenho e a designação da solicitação de memória não validada para a região linear (302).

2. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** compreende adicionalmente quando um último endereço de memória na primeira faixa de endereço da região linear (302) é alcançado:

a colocação do primeiro dispositivo de memória (110) no modo de economia de energia;

a ativação do segundo dispositivo de memória (118); e

a designação de uma próxima solicitação de memória recebida compreendendo a preferência por economia de energia para um primeiro endereço de memória correspondendo à segunda faixa de endereço associada ao segundo dispositivo de memória (118).

3. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** a preferência por economia de energia ou desempenho é especificada através de uma chamada de sistema para um sistema operacional.

4. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** a preferência por economia de energia ou desempenho compreende um parâmetro especificando um tipo de pilha de memória.

5. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** os dispositivos de memória (110, 118) compreendem dispositivos de memória de acesso randômico dinâmica, DRAM (112, 114, 120, 122).

6. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** o intercalador de canal (106) recebe as solicitações de memória através de um barramento de Sistema em Chip, SOC (107).

7. Método, de acordo com a reivindicação 1, **caracterizado pelo fato de que** a designação das solicitações de memória para a região linear (302) ou região intercalada (304) compreende a alocação de memória dinâmica ou alocação de memória estática predeterminada.

8. Sistema para fornecer intercalação de canal de memória com energia seletiva ou otimização de desempenho, o sistema **caracterizado pelo fato de que** compreende:

meios para configuração (202) de um mapa de endereço de memória (300) para pelo menos um primeiro dispositivo de memória (110) e um segundo dispositivo de memória (118),

em que o primeiro dispositivo de memória (110) está conectado à um primeiro controlador de memória (108) e é configurado para se comunicar através de um primeiro canal de memória ( $CH_0$ ) e em que o segundo dispositivo de memória (118) está conectado à um segundo controlador de

memória (116) e se comunica através de um segundo canal de memória (CH<sub>1</sub>),

em que o mapa de endereço de memória (300) compreende uma região linear (302) e uma região intercalada (304), cada região (302, 304) compreendendo espaço de endereço de memória alocada separada com uma faixa de endereços correspondentes dividida entre os dois canais de memória (CH<sub>0</sub>, CH<sub>1</sub>), a região intercalada (304) compreendendo um espaço de endereço intercalado para casos de utilização de desempenho relativamente mais altos e a região linear (302) compreendendo um espaço de endereço linear para casos de utilização de energia relativamente mais baixa;

meios para o recebimento (204) de solicitações de memória de um ou mais clientes (104), as solicitações de memória compreendendo uma preferência por economia de energia ou desempenho;

a designação (206) das solicitações de memória para a região linear (302) ou região intercalada (304) de acordo com a preferência para economia de energia ou desempenho,

em que endereço linear compreende uma primeira faixa de endereço associada com o primeiro dispositivo de memória (110) e acessada através do primeiro canal de memória (CH<sub>0</sub>) e uma segunda faixa de endereço associada com o segundo dispositivo de memória (118) e acessada através do segundo canal de memória (CH<sub>1</sub>),

em que a designação das solicitações de memória para a região linear (302) compreende a utilização da primeira faixa de endereço associada com o primeiro dispositivo de memória (110) enquanto o segundo dispositivo de memória (118) é colocado em um modo de economia de energia,

em que o sistema compreende adicionalmente:

meios para validação de solicitações de memória possuindo a preferência por desempenho com uma base de dados compreendendo um arquivo de histórico de largura de banda de memória; e

meios para eliminação da preferência por desempenho para solicitações de memória não validada e designação da solicitação de memória não validada para a região linear (302).

9. Sistema, de acordo com a reivindicação 8, **caracterizado pelo fato de que** compreende adicionalmente quando um último endereço de memória na primeira faixa de endereço da região linear (302) é alcançado:

meios para colocar o primeiro dispositivo de memória (110) no modo de economia de energia;

meios para ativar o segundo dispositivo de memória (118); e

meios para designar uma próxima solicitação de memória recebida compreendendo a preferência por economia de energia para um primeiro endereço de memória correspondendo à segunda faixa de endereço associada ao segundo dispositivo de memória (118).

10. Sistema, de acordo com a reivindicação 8, **caracterizado pelo fato de que** a preferência por economia de energia ou desempenho é especificada através de uma chamada de sistema para um sistema operacional.

11. Sistema, de acordo com a reivindicação 8, **caracterizado pelo fato de que** a preferência por economia de energia ou desempenho compreende um parâmetro especificando um tipo de pilha de memória.

12. Sistema, de acordo com a reivindicação 8, **caracterizado pelo fato de que** os dispositivos de memória

(110, 118) compreendem dispositivos de memória de acesso randômico dinâmica, DRAM (112, 114, 120, 122).

13. Memória, caracterizada pelo fato de que compreende instruções que, quando executadas, fazem com que um computador realize um método conforme definido em qualquer uma das reivindicações 1 a 7.

**FIG. 2**

FIG. 3

FIG. 4

FIG. 5

FIG. 6

**FIG. 7**