(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7585646号

(P7585646)

(45)発行日 令和6年11月19日(2024.11.19)

(24)登録日 令和6年11月11日(2024.11.11)

(51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 29/861 (2006.01) | H 01 L | 29/91 | K       |

| H 01 L | 29/868 (2006.01) | H 01 L | 29/86 | 3 0 1 D |

| H 01 L | 29/872 (2006.01) | H 01 L | 29/91 | F       |

| H 01 L | 29/06 (2006.01)  | H 01 L | 29/86 | 3 0 1 F |

| H 01 L | 29/739 (2006.01) | H 01 L | 29/91 | C       |

請求項の数 27 (全42頁) 最終頁に続く

(21)出願番号 特願2020-131895(P2020-131895)

(22)出願日 令和2年8月3日(2020.8.3)

(65)公開番号 特開2021-34726(P2021-34726A)

(43)公開日 令和3年3月1日(2021.3.1)

審査請求日 令和5年7月13日(2023.7.13)

(31)優先権主張番号 特願2019-148604(P2019-148604)

(32)優先日 令和1年8月13日(2019.8.13)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74)代理人 110000877

弁理士法人 R Y U K A 国際特許事務所

田村 隆博

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

根本 道生

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72)発明者

杉山 芳弘

審査官

最終頁に続く

(54)【発明の名称】 半導体装置および半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記第1アノード領域の面積は、前記半導体基板のおもて面において、前記第2アノード領域の面積よりも大きい

半導体装置。

## 【請求項2】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

10

20

前記第1アノード領域の下端の深さは、前記第2アノード領域の下端の深さの半分よりも浅い

半導体装置。

【請求項3】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記第1アノード領域の下端の深さは、前記第2アノード領域の下端の深さの半分よりも深く、前記第2アノード領域の下端の深さよりも浅い

半導体装置。

【請求項4】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記第1アノード領域の下方における前記第2アノード領域の深さ方向の厚さは、0.5 μm以上である

半導体装置。

【請求項5】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記アノード電極と接触する領域における前記第2アノード領域の下端の深さは、前記第1アノード領域の下方に設けられた前記第2アノード領域の下端の深さよりも浅い

半導体装置。

【請求項6】

前記第2アノード領域の下端の最も浅い部分は、上面視において、前記第2アノード領域が前記アノード電極と接触する領域の中央に位置する

請求項5に記載の半導体装置。

【請求項7】

前記アノード電極に接する前記第2アノード領域のドーピング濃度は、前記第1アノード領域のドーピング濃度よりも低い。

請求項5または6に記載の半導体装置。

【請求項8】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

10

20

30

40

50

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、複数のトレンチ部を更に備え、

前記第1アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記第1アノード領域および前記第2アノード領域は、メサ長手方向において、交互に並んで設けられる

半導体装置。

【請求項9】

半導体基板のおもて面側に設けられたアノード電極と、

10

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接觸された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、複数のトレンチ部を更に備え、

前記第1アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記第2アノード領域の面積は、前記半導体基板のおもて面において、前記複数のトレンチ部に挟まれたメサ部の全面積の1%以下である

20

半導体装置。

【請求項10】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接觸された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、複数のトレンチ部を更に備え、

30

前記第1アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記第2アノード領域の上面は、前記複数のトレンチ部に挟まれた複数のメサ部のいずれかのメサ部において、前記第1アノード領域に全面が覆われる

半導体装置。

【請求項11】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接觸された第1導電型の第1アノード領域と、

40

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、複数のトレンチ部を更に備え、

前記第1アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記複数のトレンチ部は、前記半導体基板のおもて面から裏面に向けて徐々にトレンチ幅が大きくなる構造を有し、

前記おもて面における前記メサ部の幅は、前記複数のトレンチ部の最大のトレンチ幅よ

50

りも小さい

半導体装置。

【請求項 1 2】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第 1 導電型のドリフト領域と、

前記アノード電極とショットキー接触された第 1 導電型の第 1 アノード領域と、

前記第 1 導電型と異なる第 2 導電型の第 2 アノード領域と

を備え、

前記第 1 アノード領域は、前記第 2 アノード領域のドーピング濃度以下のドーピング濃度

10

を有し、前記第 2 アノード領域によって前記ドリフト領域と離間されており、

複数のトレンチ部を更に備え、

前記第 1 アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ

部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記ドリフト領域よりドーピング濃度の高い第 1 導電型である複数の蓄積領域を備え、

前記第 1 アノード領域の下端の深さは、前記第 2 アノード領域の下端の深さの半分よりも深く、

前記第 2 アノード領域の下端の深さは、前記複数の蓄積領域の上端から下端までの厚みよりも小さい

半導体装置。

【請求項 1 3】

前記複数の蓄積領域のうち最も深い蓄積領域の下端は、

前記複数のトレンチ部のうち隣接するトレンチ部の半分の深さ位置よりも深く、

前記トレンチ部が前記半導体基板の裏面に向かって延伸する側壁領域と、前記トレンチ部の底部に向かって前記トレンチ部の幅が減少する底部領域との境界と同一またはそれよりも浅い

請求項 1 2 に記載の半導体装置。

【請求項 1 4】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第 1 導電型のドリフト領域と、

前記アノード電極とショットキー接触された第 1 導電型の第 1 アノード領域と、

30

前記第 1 導電型と異なる第 2 導電型の第 2 アノード領域と

を備え、

前記第 1 アノード領域は、前記第 2 アノード領域のドーピング濃度以下のドーピング濃度

を有し、前記第 2 アノード領域によって前記ドリフト領域と離間されており、

複数のトレンチ部を更に備え、

前記第 1 アノード領域は、前記複数のトレンチ部の間に設けられた前記半導体基板のメサ

部に設けられ、当該メサ部の両端の前記複数のトレンチ部と接し、

前記ドリフト領域よりドーピング濃度の高い第 1 導電型である蓄積領域を備え、

前記蓄積領域の下端は、

前記複数のトレンチ部のうち隣接するトレンチ部の半分の深さ位置よりも深く、

前記トレンチ部が前記半導体基板の裏面に向かって延伸する側壁領域と、前記トレンチ部の底部に向かって前記トレンチ部の幅が減少する底部領域との境界と同一またはそれよりも浅く、

前記第 1 アノード領域の下端の深さは、前記第 2 アノード領域の下端の深さの半分よりも深く、

前記第 2 アノード領域の下端の深さは、前記蓄積領域の上端から下端までの厚みよりも小さい

半導体装置。

【請求項 1 5】

半導体基板のおもて面側に設けられたアノード電極と、

10

20

30

40

50

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接觸された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度

を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記アノード電極に接觸する第2導電型のコンタクト領域を備え、

前記コンタクト領域は、上面視で、前記第2アノード領域が前記コンタクト領域と前記第

1アノード領域との間に於いて前記おもて面に露出することにより、前記第1アノード領

域と離間されている

半導体装置。

10

【請求項16】

半導体基板のおもて面側に設けられたアノード電極と、

前記半導体基板に設けられた第1導電型のドリフト領域と、

前記アノード電極とショットキー接觸された第1導電型の第1アノード領域と、

前記第1導電型と異なる第2導電型の第2アノード領域と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度

を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記第1アノード領域の側面および下面是、前記第2アノード領域によって覆われている

半導体装置。

20

【請求項17】

前記ドリフト領域よりドーピング濃度の高い第1導電型の蓄積領域を備え、

前記蓄積領域は、前記第1アノード領域および前記第2アノード領域の下方に設けられる

請求項1から11、15および16のいずれか一項に記載の半導体装置。

【請求項18】

前記半導体基板の裏面側に設けられたカソード電極と、

前記半導体基板の裏面において、前記カソード電極と接して設けられたカソード層とを

備え、

前記カソード層は、

第1導電型の第1カソード領域と、

前記第1カソード領域と隣接して設けられた第2導電型の第2カソード領域と

を含む

請求項1から17のいずれか一項に記載の半導体装置。

30

【請求項19】

前記第2カソード領域の面積は、前記半導体基板の裏面において、前記第1カソード領

域の面積よりも大きい

請求項18に記載の半導体装置。

【請求項20】

前記第1カソード領域の面積は、前記半導体基板の裏面において、前記第1カソード領

域および前記第2カソード領域の合計面積の10%以下である

請求項18または19に記載の半導体装置。

40

【請求項21】

前記カソード層は、

前記半導体基板に設けられた裏面側カソード部と、

前記裏面側カソード部よりも前記半導体基板のおもて面側に設けられた、第2導電型の

もおもて面側カソード部を備え、

前記裏面側カソード部は、前記第1カソード領域および前記第2カソード領域の繰り返

し構造を含む

請求項18から20のいずれか一項に記載の半導体装置。

50

## 【請求項 2 2】

前記おもて面側カソード部は、前記第1カソード領域および前記第2カソード領域と隣接して設けられ、前記第1カソード領域のおもて面側に設けられた開口を有する

請求項2\_1に記載の半導体装置。

## 【請求項 2 3】

前記開口の直径Dは、前記第1カソード領域のトレンチ配列方向の幅Cよりも小さい

請求項2\_2に記載の半導体装置。

## 【請求項 2 4】

前記第1アノード領域と前記アノード電極とを接続するための接続部を備え、

前記接続部は、Ti、V、Ni、およびPtの少なくとも1つを含む

請求項1から2\_3のいずれか一項に記載の半導体装置。

10

## 【請求項 2 5】

前記半導体基板に設けられたトランジスタ部を更に備える

請求項1から2\_4のいずれか一項に記載の半導体装置。

## 【請求項 2 6】

前記第1アノード領域のドーピング濃度は、 $1 \times 10^{15} \text{ cm}^{-3}$ 以上、 $1 \times 10^{18} \text{ cm}^{-3}$ 以下

である

請求項1から2\_5のいずれか一項に記載の半導体装置。

20

## 【請求項 2 7】

半導体基板のおもて面側に、アノード電極を設ける段階と、

前記半導体基板に、第1導電型のドリフト領域を設ける段階と、

前記アノード電極とショットキー接触された第1導電型の第1アノード領域を設ける段階と、

前記第1導電型と異なる第2導電型の第2アノード領域を設ける段階と

を備え、

前記第1アノード領域は、前記第2アノード領域のドーピング濃度以下のドーピング濃度を有し、前記第2アノード領域によって前記ドリフト領域と離間されており、

前記第1アノード領域の面積は、前記半導体基板のおもて面において、前記第2アノード領域の面積よりも大きい

半導体装置の製造方法。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

## 【背景技術】

## 【0002】

従来、Pアノード領域がN層で遮られたダイオード部を有する半導体装置が知られている（例えば、特許文献1参照）。

特許文献1 特開2016-6891号公報

40

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0003】

半導体装置の逆回復特性を向上させる。

## 【課題を解決するための手段】

## 【0004】

本発明の第1の態様においては、半導体基板のおもて面側に設けられたアノード電極と、半導体基板に設けられた第1導電型のドリフト領域と、アノード電極とショットキー接触された第1導電型の第1アノード領域と、第1導電型と異なる第2導電型の第2アノード領域とを備え、第1アノード領域は、第2アノード領域のドーピング濃度以下のドーピング濃度を有し、第2アノード領域によってドリフト領域と離間されている半導体装置を

50

提供する。

【0005】

第1アノード領域のドーピング濃度は、 $1 \times 10^5 \text{ cm}^{-3}$ 以上、 $1 \times 10^8 \text{ cm}^{-3}$ 以下であってよい。

【0006】

第1アノード領域の面積は、半導体基板のおもて面において、第2アノード領域の面積よりも大きくてよい。

【0007】

第1アノード領域の下端の深さは、第2アノード領域の下端の深さの半分よりも浅くてよい。

10

【0008】

第1アノード領域の下端の深さは、第2アノード領域の下端の深さの半分よりも深く、第2アノード領域の下端の深さよりも浅くてよい。

【0009】

第1アノード領域の下方における第2アノード領域の下端の深さ方向の膜厚は、 $0.5 \mu\text{m}$ 以上であってよい。

【0010】

アノード電極と接触する領域における第2アノード領域の下端の深さは、第1アノード領域の下方に設けられた第2アノード領域の下端の深さよりも浅くてよい。

【0011】

第2アノード領域の下端の最も浅い部分は、上面視において、第2アノード領域がアノード電極と接触する領域の中央に位置してよい。

20

【0012】

アノード電極に接する第2アノード領域のドーピング濃度は、第1アノード領域のドーピング濃度よりも低くてよい。

【0013】

半導体装置は、複数のトレンチ部を更に備えてよい。第1アノード領域は、複数のトレンチ部の間に設けられた半導体基板のメサ部に設けられ、当該メサ部の両端の複数のトレンチ部と接してよい。

【0014】

第1アノード領域および第2アノード領域は、メサ長手方向において、交互に並んで設けられてよい。

30

【0015】

第2アノード領域の面積は、半導体基板のおもて面において、複数のトレンチ部に挟まれたメサ部の全面積の1%以下であってよい。

【0016】

第2アノード領域の上面は、複数のトレンチ部に挟まれた複数のメサ部のいずれかのメサ部において、第1アノード領域に全面が覆われてよい。

【0017】

複数のトレンチ部は、半導体基板のおもて面から裏面に向けて徐々にトレンチ幅が大きくなる構造を有してよい。おもて面におけるメサ部の幅は、複数のトレンチ部の最大のトレンチ幅よりも小さくてよい。

40

【0018】

半導体装置は、ドリフト領域よりドーピング濃度の高い第1導電型である複数の蓄積領域を備えてよい。第1アノード領域の下端の深さは、第2アノード領域の下端の深さの半分よりも深くてよい。第2アノード領域の下端の深さは、複数の蓄積領域の上端から下端までの厚みよりも小さくてよい。

【0019】

複数の蓄積領域のうち最も深い蓄積領域の下端は、複数のトレンチ部のうち隣接するトレンチ部の半分の深さ位置よりも深く、トレンチ部が半導体基板の裏面に向かって延伸す

50

る側壁領域と、トレンチ部の底部に向かってトレンチ部の幅が減少する底部領域との境界と同一またはそれよりも浅くてよい。

【0020】

半導体装置は、ドリフト領域よりドーピング濃度の高い第1導電型である蓄積領域を備えてよい。蓄積領域の下端は、複数のトレンチ部のうち隣接するトレンチ部の半分の深さ位置よりも深く、トレンチ部が半導体基板の裏面に向かって延伸する側壁領域と、トレンチ部の底部に向かってトレンチ部の幅が減少する底部領域との境界と同一またはそれよりも浅くてよい。第1アノード領域の下端の深さは、第2アノード領域の下端の深さの半分よりも深くてよい。第2アノード領域の下端の深さは、蓄積領域の上端から下端までの厚みよりも小さくてよい。

10

【0021】

半導体装置は、ドリフト領域よりドーピング濃度の高い第1導電型の蓄積領域を備えてよい。蓄積領域は、第1アノード領域および第2アノード領域の下方に設けられてよい。

【0022】

半導体装置は、半導体基板の裏面側に設けられたカソード電極と、半導体基板の裏面において、カソード電極と接して設けられたカソード層とを備えてよい。カソード層は、第1導電型の第1カソード領域と、第1カソード領域と隣接して設けられた第2導電型の第2カソード領域とを含んでよい。

【0023】

第2カソード領域の面積は、半導体基板の裏面において、第1カソード領域の面積よりも大きくてよい。

20

【0024】

第1カソード領域の面積は、半導体基板の裏面において、第1カソード領域および第2カソード領域の合計面積の10%以下であってよい。

【0025】

カソード層は、半導体基板に設けられた裏面側カソード部と、裏面側カソード部よりも半導体基板のおもて面側に設けられた、第2導電型のおもて面側カソード部を備えてよい。裏面側カソード部は、第1カソード領域および第2カソード領域の繰り返し構造を含んでよい。

【0026】

おもて面側カソード部は、第1カソード領域および第2カソード領域と隣接して設けられ、第1カソード領域のおもて面側に設けられた開口を有してよい。

30

【0027】

開口の直径Dは、第1カソード領域のトレンチ配列方向の幅Cよりも小さくてよい。

【0028】

半導体装置は、第1アノード領域とアノード電極とを接続するための接続部を備えてよい。接続部は、T<sub>i</sub>、V、N<sub>i</sub>、およびP<sub>t</sub>の少なくとも1つを含んでよい。

【0029】

半導体装置は、半導体基板に設けられたトランジスタ部を更に備えてよい。

【0030】

本発明の第2の態様においては、半導体基板のおもて面側に、アノード電極を設ける段階と、半導体基板に、第1導電型のドリフト領域を設ける段階と、アノード電極とショットキー接觸された第1導電型の第1アノード領域を設ける段階と、第1導電型と異なる第2導電型の第2アノード領域を設ける段階とを備え、第1アノード領域は、第2アノード領域のドーピング濃度以下のドーピング濃度を有し、第2アノード領域によってドリフト領域と離間されている半導体装置の製造方法を提供する。

40

【0031】

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。

【図面の簡単な説明】

50

## 【0032】

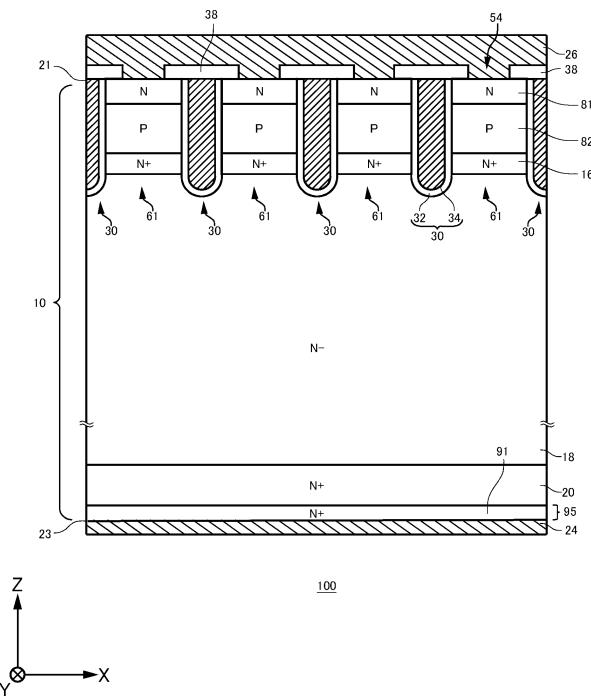

【図1A】プレーナ型である半導体装置100の断面図の一例を示す。

【図1B】実施例1に係る半導体装置100の上面図の一例を示す。

【図1C】実施例2に係る半導体装置100の上面図の一例を示す。

【図1D】半導体装置100の深さ方向のドーピング濃度分布とバンド図の一例を示す。

【図1E】図1Dのc)のN-N断面における、おもて面21のネット・ドーピング濃度分布を示す。

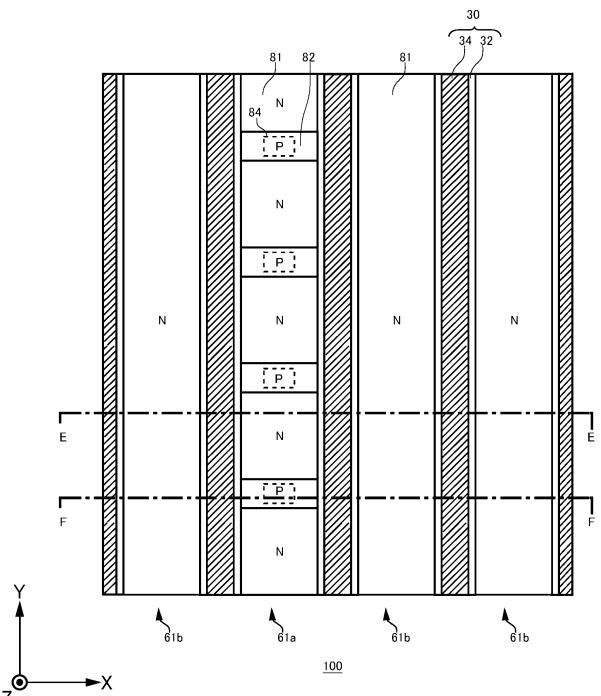

【図2A】トレンチ型である半導体装置100の上面図の一例を示す。

【図2B】実施例3に係る半導体装置100の断面図の一例を示す。

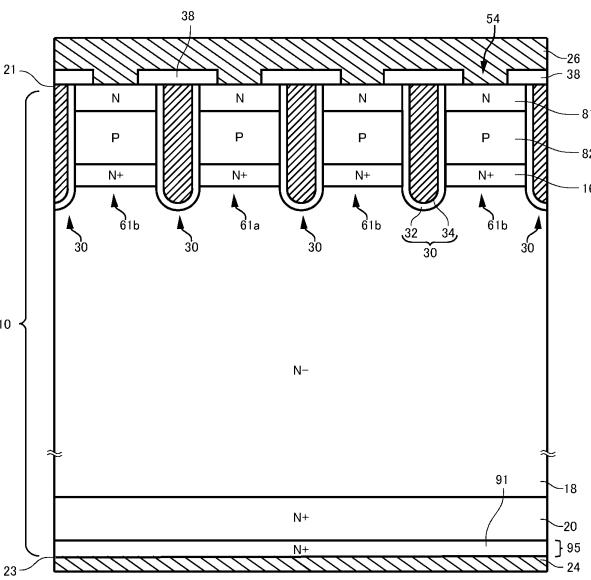

【図2C】実施例3に係る半導体装置100の断面図の一例を示す。

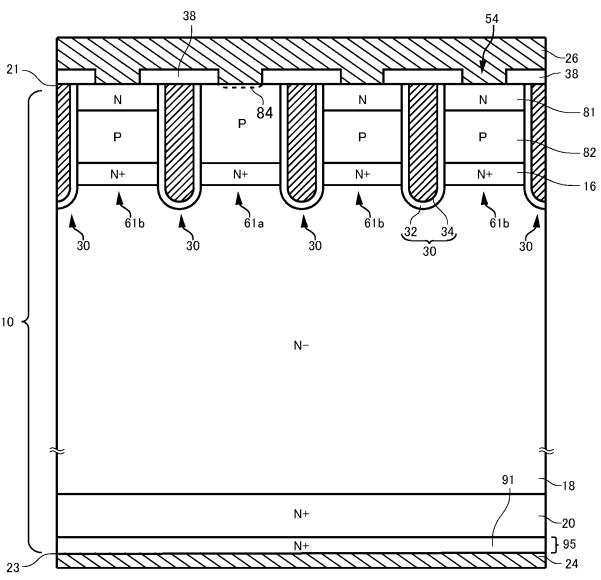

【図2D】実施例4に係る半導体装置100の断面図の一例を示す。

【図3A】トレンチ型である半導体装置100の上面図の一例を示す。

【図3B】実施例5に係る半導体装置100の断面図の一例を示す。

【図3C】実施例5に係る半導体装置100の断面図の一例を示す。

【図4A】半導体装置100のおもて面21側の構造を示す拡大図の一例である。

【図4B】半導体装置100のおもて面21側の構造を示す拡大図の一例である。

【図4C】半導体装置100のおもて面21側の構造を示す拡大図の一例である。

【図4D】半導体装置100のおもて面21側の構造を示す拡大図の一例である。

【図5A】トレンチ型である半導体装置100の上面図の一例を示す。

【図5B】実施例6に係る半導体装置100の断面図の一例を示す。

【図5C】実施例6に係る半導体装置100の断面図の一例を示す。

【図5D】実施例7に係る半導体装置100の断面図の一例を示す。

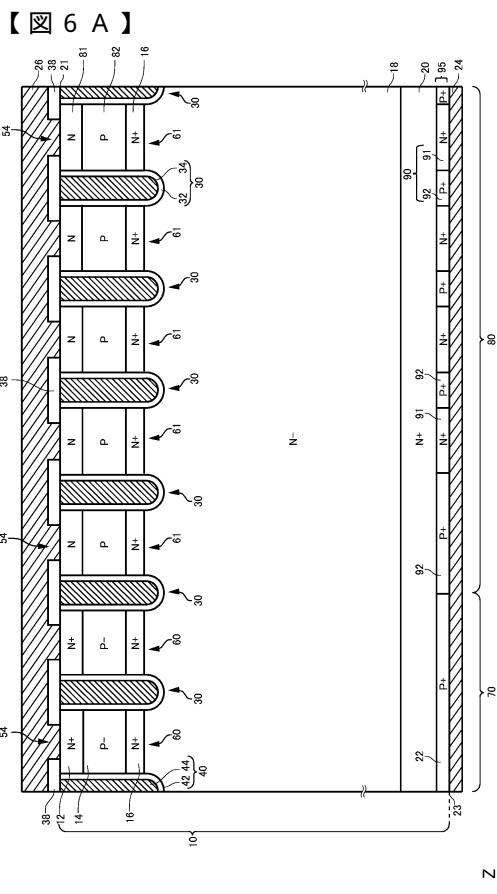

【図6A】実施例8に係る半導体装置100の断面図の一例を示す。

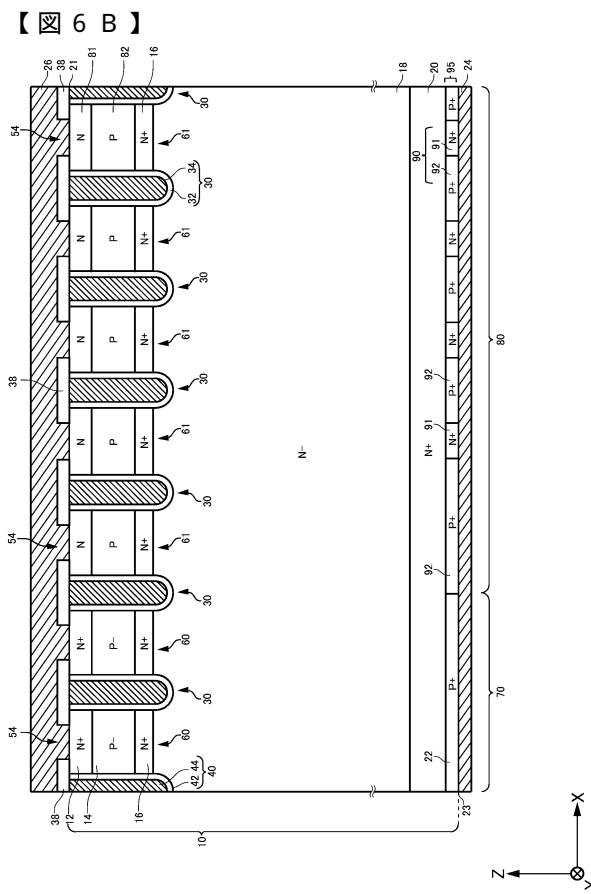

【図6B】実施例9に係る半導体装置100の断面図の一例を示す。

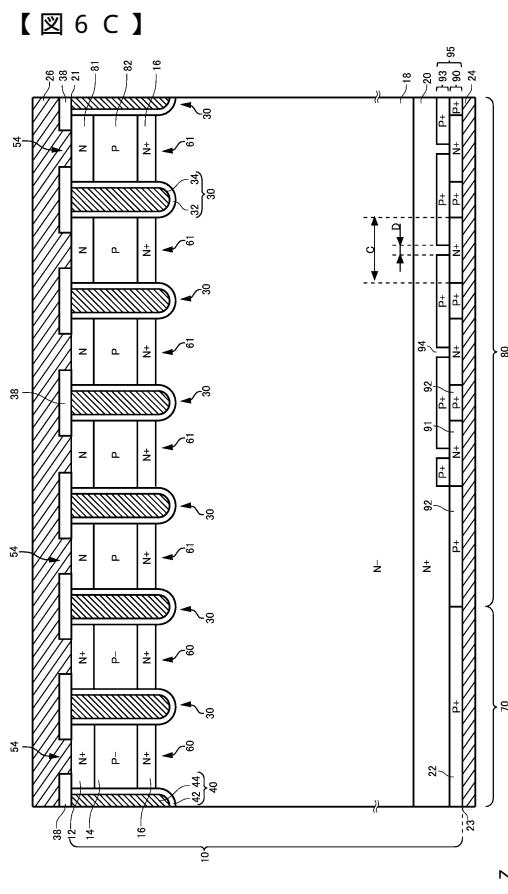

【図6C】実施例10に係る半導体装置100の断面図の一例を示す。

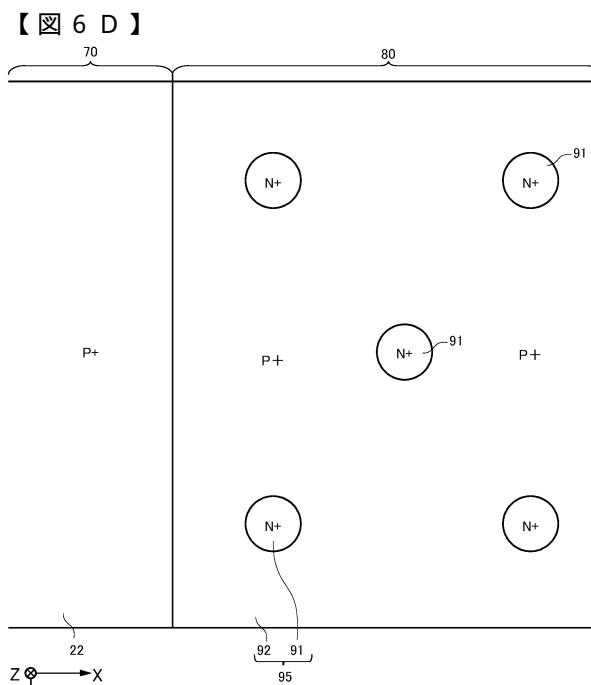

【図6D】実施例11に係る半導体装置100の裏面23における下面図の一例を示す。

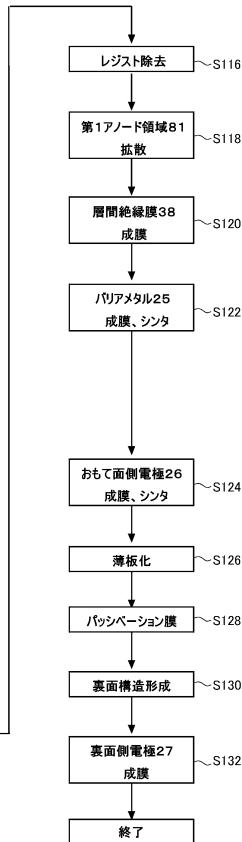

【図7A】プレーナ型である半導体装置100の製造方法の一例を示す。

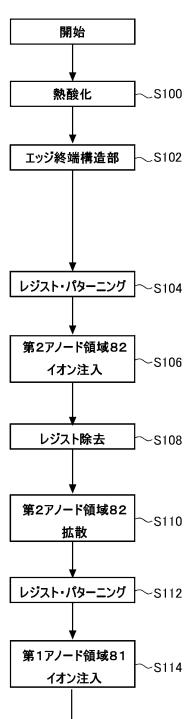

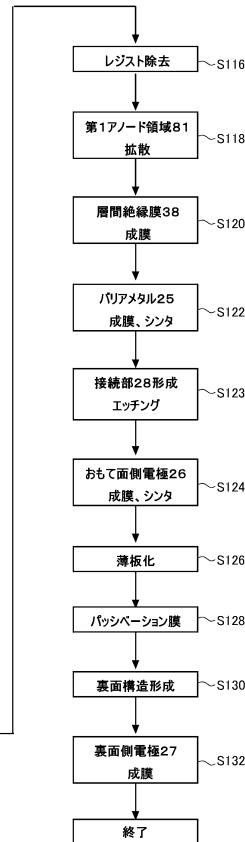

【図7B】トレンチ型である半導体装置100の製造方法の一例を示す。

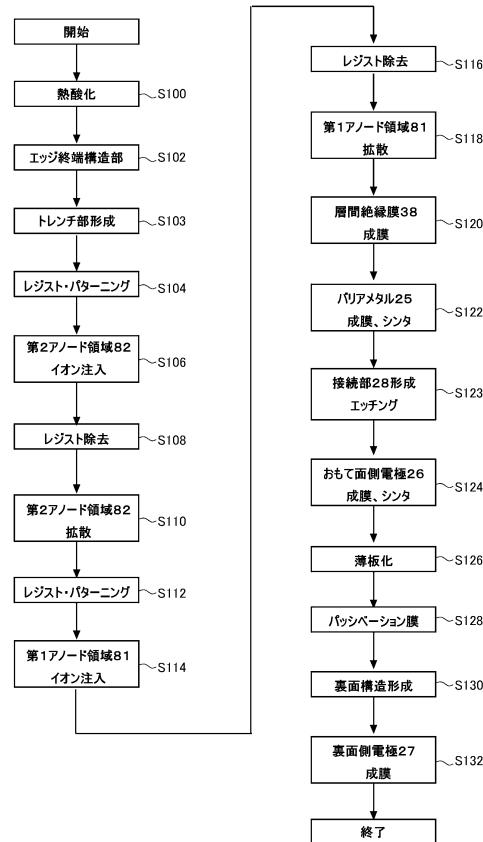

【図8】第1アノード領域81および第2アノード領域82の製造工程の一例を示す。

【図9A】プレーナ型である半導体装置100の断面図の変形例を示す。

【図9B】図9Aに係る半導体装置100の深さ方向のドーピング濃度分布とエネルギー・バンド図の一例を示す。

【図9C】図9Bのf)のT-T断面について、おもて面21のネット・ドーピング濃度分布を示す。

【図10】おもて面21と裏面23の対応関係を説明するための図である。

## 【発明を実施するための形態】

## 【0033】

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

## 【0034】

本明細書においては半導体基板の深さ方向と平行な方向における一方の側を「上」、他方の側を「下」と称する。基板、層またはその他の部材の2つの主面のうち、一方の面を上面、他方の面を下面と称する。「上」、「下」の方向は、重力方向または半導体装置の実装時における方向に限定されない。

## 【0035】

本明細書では、X軸、Y軸およびZ軸の直交座標軸を用いて技術的事項を説明する場合がある。直交座標軸は、構成要素の相対位置を特定するに過ぎず、特定の方向を限定するものではない。例えば、Z軸は地面に対する高さ方向を限定して示すものではない。なお、+Z軸方向と-Z軸方向とは互いに逆向きの方向である。正負を記載せず、Z軸方向と

10

20

30

40

50

記載した場合、+ Z 軸および- Z 軸に平行な方向を意味する。

【 0 0 3 6 】

本明細書では、半導体基板の上面および下面に平行な直交軸を X 軸および Y 軸とする。また、半導体基板の上面および下面と垂直な軸を Z 軸とする。本明細書では、Z 軸の方向を深さ方向と称する場合がある。また、本明細書では、X 軸および Y 軸を含めて、半導体基板の上面および下面に平行な方向を、水平方向と称する場合がある。

【 0 0 3 7 】

本明細書において「同一」または「等しい」のように称した場合、製造ばらつき等に起因する誤差を有する場合も含んでよい。当該誤差は、例えは 10 % 以内である。

【 0 0 3 8 】

本明細書においては、不純物がドーピングされたドーピング領域の導電型を P 型または N 型として説明している。本明細書においては、不純物とは、特に N 型のドナーまたは P 型のアクセプタのいずれかを意味する場合があり、ドーパントと記載する場合がある。本明細書においては、ドーピングとは、半導体基板にドナーまたはアクセプタを導入し、N 型の導電型を示す半導体または P 型の導電型を示す半導体とすることを意味する。

【 0 0 3 9 】

本明細書においては、ドーピング濃度とは、熱平衡状態におけるドナーの濃度またはアクセプタの濃度を意味する。本明細書においては、ネット・ドーピング濃度とは、ドナー濃度を正イオンの濃度とし、アクセプタ濃度を負イオンの濃度として、電荷の極性を含めて足し合わせた正味の濃度を意味する。一例として、ドナー濃度を  $N_D$  、アクセプタ濃度を  $N_A$  とすると、任意の位置における正味のネット・ドーピング濃度は  $N_D - N_A$  となる。

【 0 0 4 0 】

ドナーは、半導体に電子を供給する機能を有している。アクセプタは、半導体から電子を受け取る機能を有している。ドナーおよびアクセプタは、不純物自体には限定されない。例えば、半導体中に存在する空孔 (V) 、酸素 (O) および水素 (H) が結合した VOH 欠陥は、電子を供給するドナーとして機能する。

【 0 0 4 1 】

本明細書において P + 型または N + 型と記載した場合、P 型または N 型よりもドーピング濃度が高いことを意味し、P - 型または N - 型と記載した場合、P 型または N 型よりもドーピング濃度が低いことを意味する。また、本明細書において P + + 型または N + + 型と記載した場合には、P + 型または N + 型よりもドーピング濃度が高いことを意味する。

【 0 0 4 2 】

また、ドナー、アクセプタまたはネット・ドーピングの濃度分布がピークを有する場合、当該ピーク値を当該領域におけるドナー、アクセプタまたはネット・ドーピングの濃度としてよい。ドナー、アクセプタまたはネット・ドーピングの濃度がほぼ均一な場合等においては、当該領域におけるドナー、アクセプタまたはネット・ドーピングの濃度の平均値をドナー、アクセプタまたはネット・ドーピングの濃度としてよい。

【 0 0 4 3 】

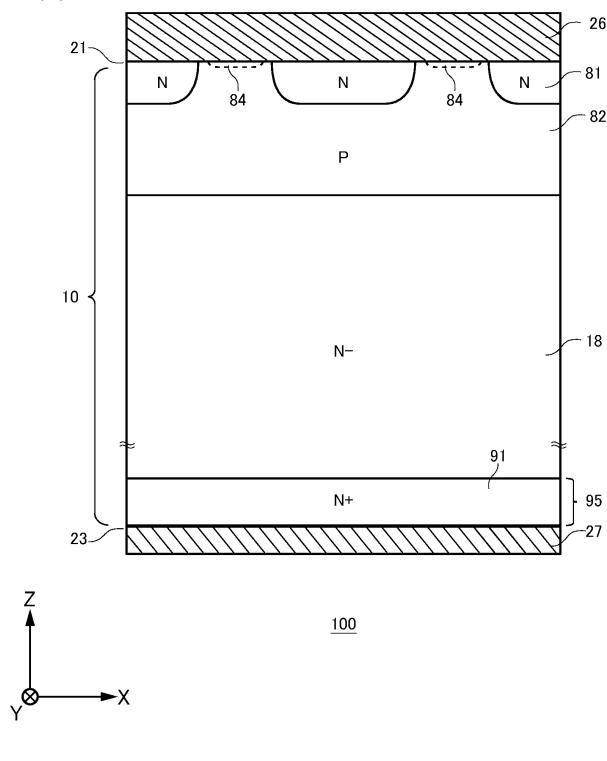

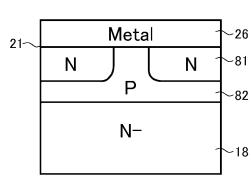

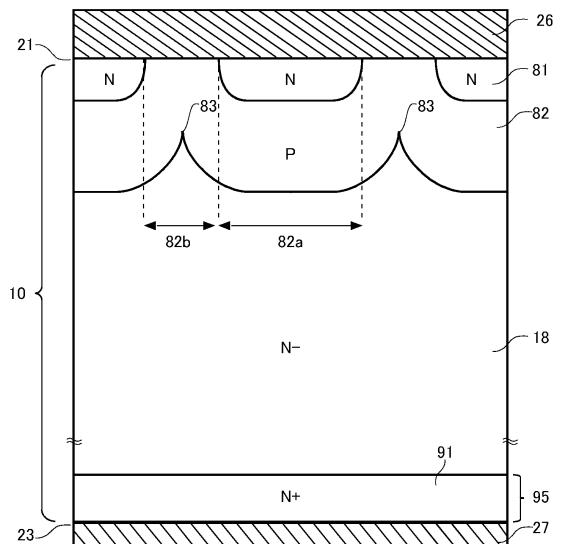

図 1 A は、プレーナ型である半導体装置 100 の断面図の一例を示す。半導体装置 100 は、半導体基板 10 を備える。半導体装置 100 は、ダイオードを有する半導体チップである。本例の半導体装置 100 は、半導体基板 10 において、ドリフト領域 18 と、第 1 アノード領域 81 と、第 2 アノード領域 82 と、コンタクト領域 84 とを備える。また、半導体装置 100 は、おもて面側電極 26 および裏面側電極 27 を備える。

【 0 0 4 4 】

半導体基板 10 は、半導体材料で形成された基板である。半導体基板 10 は、シリコン基板であってよく、炭化シリコン基板であってよく、窒化ガリウム等の窒化物半導体基板等であってもよい。本例の半導体基板 10 は、シリコン基板である。半導体基板 10 は、おもて面 21 および裏面 23 を有する。

【 0 0 4 5 】

また、半導体基板 10 は、N 型基板であってよく、P 型基板を N 型化した基板であって

10

20

30

40

50

もよい。半導体基板 10 は、半導体のインゴットから切り出したウエハであってよく、ウエハを個片化したチップであってもよい。半導体のインゴットは、チョクラルスキー法 (CZ 法)、磁場印加型チョクラルスキー法 (MCZ 法)、フロートゾーン法 (FZ 法) のいずれかで製造されよい。本例では、半導体基板 10 は、MCZ 法で製造したインゴットから切り出したウエハである。

#### 【 0 0 4 6 】

ドリフト領域 18 は、半導体基板 10 に設けられた第 1 導電型の領域である。本例のドリフト領域 18 は、一例として N - 型である。ドリフト領域 18 は、半導体基板 10 において他のドーピング領域が形成されずに残存した領域であってよい。即ち、ドリフト領域 18 のドーピング濃度は、半導体基板 10 のドーピング濃度であってもよい。

10

#### 【 0 0 4 7 】

おもて面側電極 26 は、半導体基板 10 のおもて面 21 側に設けられる。本例のおもて面側電極 26 は、半導体基板 10 のおもて面 21 に接して設けられる。おもて面側電極 26 は、金属を含む材料で形成される。例えば、おもて面側電極 26 の少なくとも一部の領域は、アルミニウム、アルミニウムシリコン合金、またはアルミニウムシリコン-銅合金で形成される。おもて面側電極 26 は、アルミニウム等で形成された領域の下層にチタンやチタン化合物等で形成されたバリアメタルを有してよい。一例において、おもて面側電極 26 は、アノード電極である。

#### 【 0 0 4 8 】

裏面側電極 27 は、半導体基板 10 の裏面 23 側に設けられる。本例の裏面側電極 27 は、半導体基板 10 の裏面 23 に接して設けられる。裏面側電極 27 は、金属等の導電材料で形成される。裏面側電極 27 の材料は、おもて面側電極 26 の材料と同一であっても、異なっていてもよい。例えば、裏面側電極 27 の少なくとも一部の領域は、アルミニウム、アルミニウムシリコン合金、またはアルミニウムシリコン-銅合金で形成される。一例において、裏面側電極 27 は、カソード電極である。

20

#### 【 0 0 4 9 】

カソード層 95 は、半導体基板 10 の裏面 23 側に設けられる。カソード層 95 は、裏面側電極 27 と電気的に接続される。本例のカソード層 95 は、第 1 カソード領域 91 を含む。本例のカソード層 95 は、第 1 導電型の領域を有するが、第 2 導電型の領域を有してもよい。

30

#### 【 0 0 5 0 】

第 1 カソード領域 91 は、第 1 導電型の領域である。第 1 カソード領域 91 は、一例として N + 型である。本例の第 1 カソード領域 91 は、裏面 23 の全面に設けられているが、裏面 23 の一部に選択的に設けられてもよい。例えば、第 1 カソード領域 91 のドーピング濃度は、 $1 E 19 \text{ cm}^{-3}$  以上である。なお、E は 10 のべき乗を意味し、例えば  $1 E 19 \text{ cm}^{-3}$  は  $1 \times 10^{19} \text{ cm}^{-3}$  を意味する。

#### 【 0 0 5 1 】

第 1 アノード領域 81 は、おもて面側電極 26 とショットキー接觸された第 1 導電型の領域である。当該ショットキー接觸は、第 1 アノード領域 81 のドーピング濃度を適切に調整することにより実現される。例えば、第 1 アノード領域 81 のドーピング濃度は、 $1 E 15 \text{ cm}^{-3}$  以上、 $1 E 18 \text{ cm}^{-3}$  以下である。第 1 アノード領域 81 のドーピング濃度が  $1 E 19 \text{ cm}^{-3}$  よりも高ドーピング濃度である場合、オーミック接觸となる場合がある。本例の第 1 アノード領域 81 は、第 2 アノード領域 82 のドーピング濃度以下のドーピング濃度を有している。

40

#### 【 0 0 5 2 】

第 2 アノード領域 82 は、第 2 導電型の領域である。本例の第 2 アノード領域 82 は、半導体基板 10 のおもて面 21 側に設けられる。第 2 アノード領域 82 は、おもて面側電極 26 と電気的に接続されている。第 2 アノード領域 82 の少なくとも一部は、おもて面側電極 26 と接觸している。例えば、第 2 アノード領域 82 のドーピング濃度は、 $1 E 16 \text{ cm}^{-3}$  以上、 $1 E 17 \text{ cm}^{-3}$  以下である。

50

## 【0053】

第1アノード領域81は、第2アノード領域82によってドリフト領域18と離間されている。第1アノード領域81の側面および下面是、第2アノード領域82によって覆われている。即ち、半導体装置100は、深さ方向において、第1アノード領域81、第2アノード領域82およびドリフト領域18の順に設けられた構造を備える。このように、第1アノード領域81は、少なくとも第2アノード領域82を挟んでドリフト領域18と接触せずに離間してよい。第1アノード領域81の下方における第2アノード領域82の深さ方向の膜厚は、空乏層の広がりを考慮して設定される。即ち、第2アノード領域82の膜厚は、第2アノード領域82とドリフト領域18とのPN接合で生じる空乏層が第1アノード領域81と接触しないように設定される。一例において、第1アノード領域81の下方における第2アノード領域82の深さ方向の膜厚は、0.5 μm以上である。

10

## 【0054】

コンタクト領域84は、第2アノード領域82のおもて面21側に設けられる。コンタクト領域84は、第2導電型の領域である。コンタクト領域84は、おもて面側電極26に接する。コンタクト領域84の深さは、第1アノード領域81よりも浅くてよい。コンタクト領域84の深さは、第1アノード領域81の深さの10%よりも浅くてよい。コンタクト領域84の深さは、0.1 μm以下であってよい。コンタクト領域84の深さは、デバイ長さより深くてよい。コンタクト領域84の深さは、デバイ長さの100倍かそれよりも浅くてよい。コンタクト領域84は、第2導電型のドーパント（ボロンやアルミニウムなど）の他に、フッ素を含んでよい。半導体装置100は、コンタクト領域84を備えなくてもよい。

20

## 【0055】

コンタクト領域84のドーピング濃度は、第2アノード領域82のドーピング濃度よりも高くてよい。コンタクト領域84のドーピング濃度は、第2アノード領域82のドーピング濃度の最大値の100倍以上であってよい。コンタクト領域84のドーピング濃度は、 $1 \times 10^8 \text{ cm}^{-3}$ 以上であってよく、 $1 \times 10^9 \text{ cm}^{-3}$ 以下であってよい。

30

## 【0056】

コンタクト領域84は、上面視で第1アノード領域81と隣接する。コンタクト領域84は、上面視で、第1アノード領域81に接してもよく、第1アノード領域81とは離れていてよい。本例では、コンタクト領域84は第1アノード領域81と離れている。上面視で、コンタクト領域84と第1アノード領域81との間において、第2アノード領域82がおもて面21に露出してよい。

40

## 【0057】

第2アノード領域82とおもて面側電極26との接触は、オーミック接触であってよい。コンタクト領域84は、第2アノード領域82とおもて面側電極26との接触をオーミック接触として、接触抵抗を低減する効果を有する。一方、コンタクト領域84は、第2アノード領域82よりもドーピング濃度が高いので、第2アノード領域82からドリフト領域18への正孔の注入量を増加させる場合がある。コンタクト領域84の深さを予め定められた大きさにすることで、コンタクト領域84を備える場合であっても、正孔の注入量を抑えることができる。また、コンタクト領域84のドーピング濃度を予め定められた大きさにすることで、コンタクト領域84を備える場合であっても、正孔の注入量を抑えることができる。なお、第2アノード領域82とおもて面側電極26が直接接する場合において、第2アノード領域82とおもて面側電極26との接触がオーミック接触であれば、コンタクト領域84を備えなくてもよい。

40

## 【0058】

以上の通り、半導体装置100は、おもて面21において、第1アノード領域81および第2アノード領域82を備える。第1アノード領域81の面積は、おもて面21において、第2アノード領域82の面積よりも大きくてよい。第1アノード領域81および第2アノード領域82の面積は、面積比で示される。面積比は、第1アノード領域81および第2アノード領域82の合計面積に対する第2アノード領域82の面積の比である。

50

## 【0059】

順バイアス時において、第1アノード領域81とおもて面側電極26との接触がショットキー接触であるので、少数キャリアの蓄積が少なく、第2アノード領域82からの正孔の注入が少ない。そして、ダイオード順バイアス時の正孔注入効率は、おもて面21における第1アノード領域81および第2アノード領域82の面積比で決まる。第1アノード領域81の面積の比率を大きくすることにより、正孔注入効率を低減できる。また、ショットキー接触された第1アノード領域81は、リーク電流を増加させない。よって、が1%以下であってもよい。これにより、正孔注入効率を低減できる。

## 【0060】

逆バイアス時において、ショットキー接触面から第1アノード領域81に広がる空乏層が、ドリフト領域18と第2アノード領域82とのPN接合から第2アノード領域82に広がる空乏層と接続されないことが好ましい。この場合、第2アノード領域82における再結合によって、さらにリーク電流を低減することができる。

10

## 【0061】

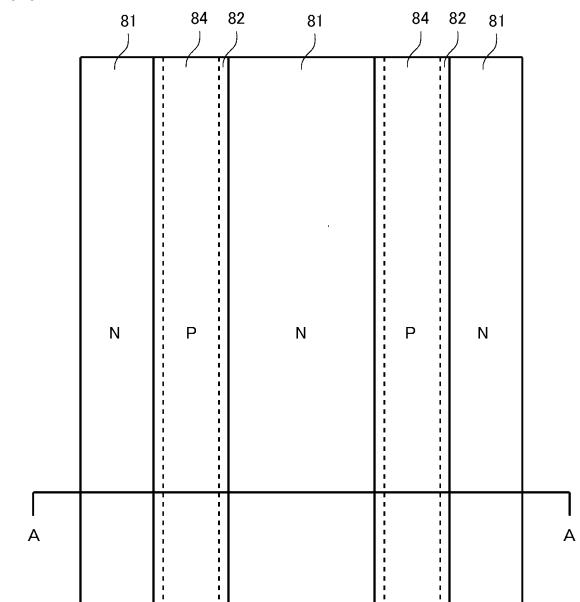

図1Bは、実施例1に係る半導体装置100の上面図の一例を示す。本例の上面図は、図1Aの半導体装置100の上面図の一例である。図1BのA-A断面が、図1Aに相当する。半導体装置100は、半導体基板10のおもて面21において、ストライプ状に設けられた第1アノード領域81および第2アノード領域82を備える。破線で示すように、第2アノード領域82のおもて面21側にコンタクト領域84を備えてもよい。

## 【0062】

第1アノード領域81は、おもて面21において、Y軸方向に延伸して設けられている。同様に、第2アノード領域82は、おもて面21において、Y軸方向に延伸して設けられている。第1アノード領域81および第2アノード領域82は、X軸方向において、交互に設けられている。第1アノード領域81のX軸方向の幅は、第2アノード領域82のX軸方向の幅よりも大きい。即ち、第1アノード領域81の面積は、半導体基板10のおもて面21において、第2アノード領域82の面積よりも大きい。例えば、第1アノード領域81の面積は、おもて面21において、第2アノード領域82の面積の2倍である。

20

## 【0063】

図1Cは、実施例2に係る半導体装置100の上面図の一例を示す。本例の上面図は、図1Aの半導体装置100の上面図の他の例である。図1CのB-B断面が、図1Aに相当する。本例の半導体装置100は、第2アノード領域82が円形を有する点で、図1Bの実施例1と相違する。破線で示すように、第2アノード領域82のおもて面21側にコンタクト領域84を備えてもよい。

30

## 【0064】

第2アノード領域82は、おもて面21において、予め定められた直径の真円形状を有する。第2アノード領域82の形状は、楕円であっても、円形以外の形状であってもよい。第2アノード領域82は、おもて面21において規則的に設けられる。例えば、第2アノード領域82は、1つの真円に対して、4つの真円が等間隔に配置された構造を有する。但し、第2アノード領域82の配置は不規則であってもよい。

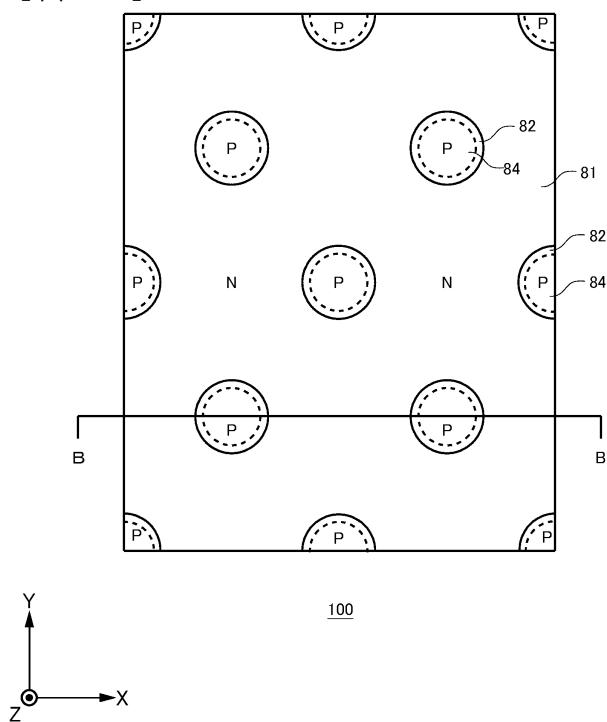

## 【0065】

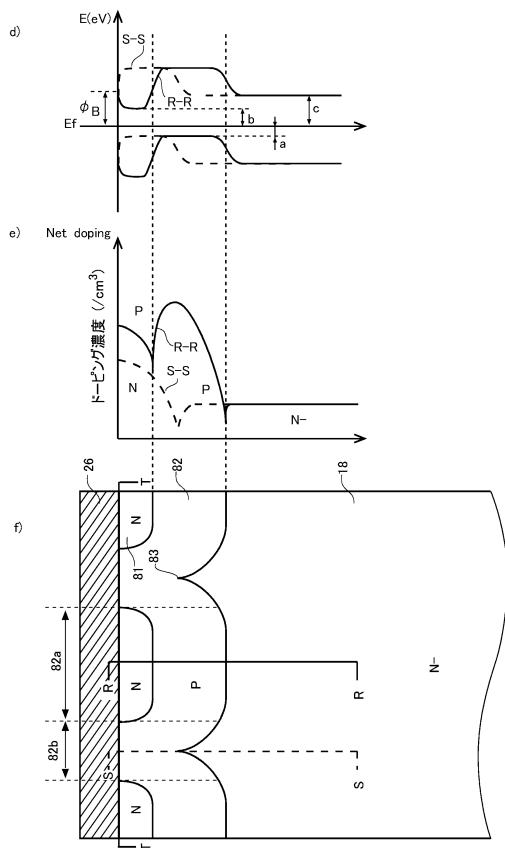

図1Dは、半導体装置100の断面図c)と、その深さ方向のドーピング濃度b)とエネルギー・バンド図a)の一例を示す。図1Dのa)~c)の深さ方向の位置はそれぞれ対応している。図1Dは、コンタクト領域84を備えない場合に対応している。同図は、半導体装置100のP-P線およびQ-Q線におけるドーピング濃度分布およびエネルギー・バンド図の一例を示している。エネルギー・バンド図の縦軸は、電子または正孔のエネルギーであり、単位は一例としてエレクトロン・ボルト(eV)である。バンドギャップ(禁制帯)にフェルミ準位(Ef)が存在する。バンドギャップよりも上のバンドが伝導帯であり、バンドギャップよりも下のバンドが価電子帯である。ドーピング濃度の縦軸は常用対数スケールのドーピング濃度である。単位は一例としてcm<sup>-3</sup>である。ドーピング濃度の横軸はおもて面21を原点として裏面23に向かう深さ位置である。単位は一

40

50

例として  $\mu m$  である。

【 0 0 6 6 】

P - P 線は、おもて面 2 1 に第 1 アノード領域 8 1 が設けられた領域を通過する断面に対応する。Q - Q 線は、おもて面 2 1 に第 2 アノード領域 8 2 が設けられた領域を通過する断面に対応する。

【 0 0 6 7 】

ドーピング濃度の実線は、P - P 線におけるドーピング濃度の分布を示す。第 1 アノード領域 8 1 は、おもて面 2 1 から、予め定められたドーズ量でドーパントを注入して設けられている。第 1 アノード領域 8 1 のドーピング濃度は、おもて面 2 1 付近においてピークを示して、深さ方向に向けて減少している。ドーピング濃度の破線は、Q - Q 線におけるドーピング濃度の分布を示す。

10

【 0 0 6 8 】

バンド図 a ) の実線は、P - P 線における熱平衡状態のバンド図を示す。第 1 アノード領域 8 1 は、おもて面側電極 2 6 とショットキー接觸している。おもて面 2 1 にはフェルミ準位から  $E_B$  のショットキー障壁が形成されている。第 1 アノード領域 8 1 をショットキー接觸させることにより、順バイアス時の正孔の注入を抑制できる。一方、逆バイアス時においても、ショットキー接觸面から第 1 アノード領域 8 1 に広がる空乏層によってリーケ電流を抑制できる。

【 0 0 6 9 】

第 1 アノード領域 8 1 のドーピング濃度は、第 1 アノード領域 8 1 がおもて面側電極 2 6 とショットキー接觸となる濃度とする。第 1 アノード領域 8 1 のドーピング濃度が  $1 E 18 \text{ cm}^{-3}$  よりも高くなると、ショットキー障壁の深さ方向の厚さが薄くなり、トンネル電流が流れるようになる。そのため、第 1 アノード領域 8 1 はおもて面側電極 2 6 とオーミック接觸となる。したがって、第 1 アノード領域 8 1 のドーピング濃度は  $1 E 18 \text{ cm}^{-3}$  よりも低くする。

20

【 0 0 7 0 】

フェルミ準位  $E_f$  からドリフト領域 1 8 の伝導帯の底までのエネルギー差  $c$  は、フェルミ準位  $E_f$  から第 1 アノード領域 8 1 の伝導帯の底までのエネルギー差  $b$  よりも大きくてよい。フェルミ準位  $E_f$  から第 1 アノード領域 8 1 の伝導帯の底までのエネルギー差  $b$  は、第 2 アノード領域 8 2 の価電子帯の最上部からフェルミ準位  $E_f$  までのエネルギー差  $a$  より大きくてよい。第 1 アノード領域 8 1 のドーピング濃度は、第 2 アノード領域 8 2 のドーピング濃度よりも低くてよい。この濃度差により、第 1 アノード領域 8 1 の伝導帯の底部とフェルミ準位  $E_f$  とのエネルギー差  $b$  は、第 2 アノード領域 8 2 の価電子帯上部とフェルミ準位  $E_f$  とのエネルギー差  $a$  よりも大きくなる。これにより、第 1 アノード領域 8 1 とおもて面側電極 2 6 とのショットキー障壁の深さ方向の厚さが薄くなりすぎてオーミック接觸になること防ぐことができる。即ち、第 1 アノード領域 8 1 とおもて面側電極 2 6 とがショットキー接觸を良好に形成することができ、順バイアス時のドリフト領域 1 8 への正孔注入を十分低減できる。

30

【 0 0 7 1 】

バンド図 a ) の破線は、Q - Q 線における熱平衡状態のバンド図を示す。第 2 アノード領域 8 2 は、おもて面側電極 2 6 とオーミック接觸している。第 2 アノード領域 8 2 は、半導体基板 1 0 のおもて面 2 1 に、高ドーピング濃度の領域を設けてもよい。

40

【 0 0 7 2 】

第 1 アノード領域 8 1 とおもて面側電極 2 6 との界面に、ダングリング・ボンドを終端する水素を備えてよい。これにより、逆バイアス時に、ショットキー接觸の欠陥（即ち、ダングリング・ボンド）に起因する漏れ電流を、低減することができる。後述するバッファ領域 2 0 の水素が、第 1 アノード領域 8 1 とおもて面側電極 2 6 との界面におけるダングリング・ボンドを終端してよい。バッファ領域 2 0 の水素は、3 0 0 から 4 0 0 のアニーリングにより、おもて面 2 1 に向かって拡散し、第 1 アノード領域 8 1 とおもて面側電極 2 6 との界面に達することができる。

50

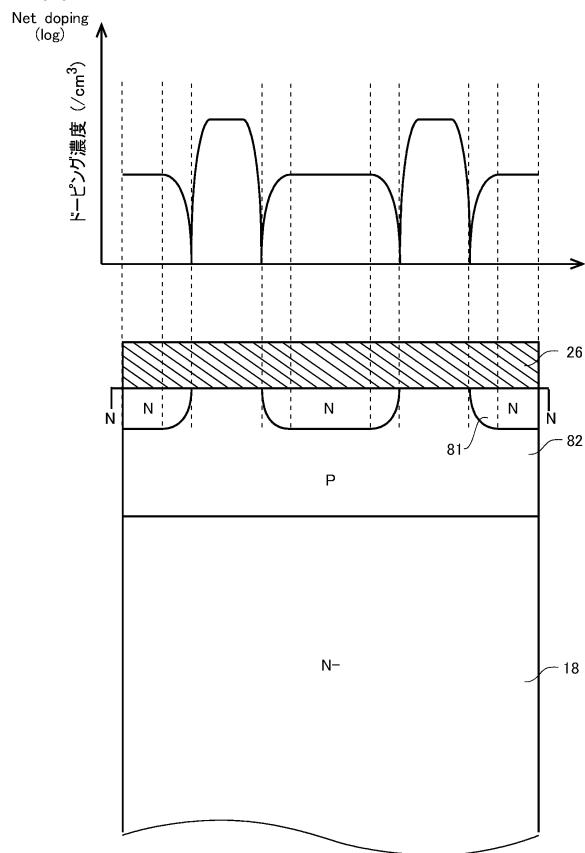

## 【0073】

図1Eは、図1Dのc)のN-N断面における、おもて面21のネット・ドーピング濃度分布を示す。図1Eも、コンタクト領域84を備えない場合に対応している。第1アノード領域81は、X軸方向に略平坦なドーピング濃度分布を有する。第1アノード領域81のドーピング濃度分布は、第2アノード領域82とのPN接合がおもて面21に露出する位置の近傍で、減少する。第2アノード領域82は、X軸方向に略平坦なドーピング濃度分布を有する。第2アノード領域82のドーピング濃度分布は、第1アノード領域81とのPN接合がおもて面21に露出する位置の近傍で、減少する。おもて面21における第1アノード領域81の最大ドーピング濃度は、おもて面21における第2アノード領域82の最大ドーピング濃度よりも小さくてよい。

10

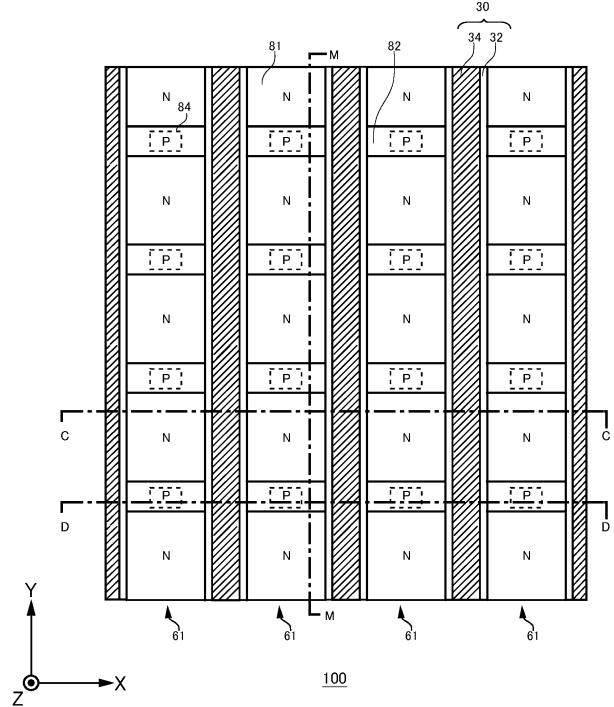

## 【0074】

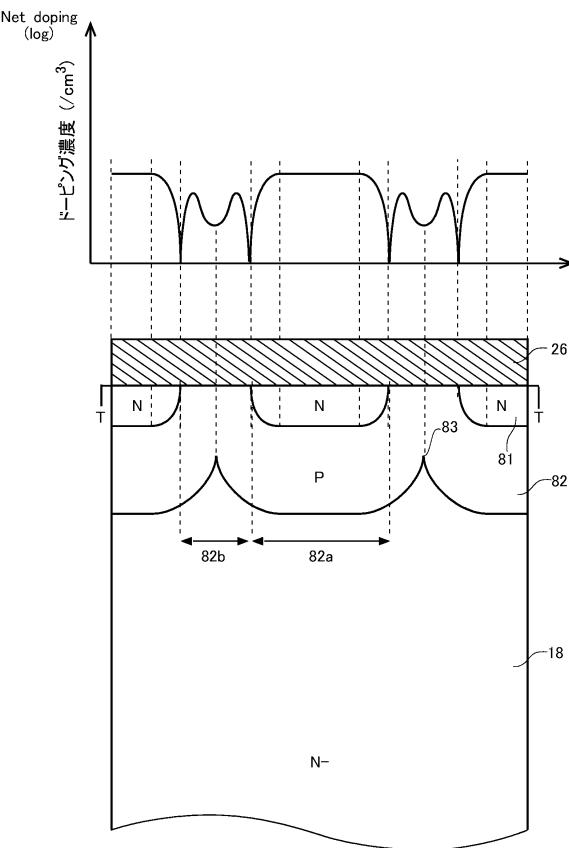

図2Aは、トレンチ型である半導体装置100の上面図の一例を示す。本例の半導体装置100は、トレンチ型構造を有する。半導体装置100は、複数のダミートレンチ部30を有する。破線で示すように、第2アノード領域82のおもて面21側にコンタクト領域84を備えてもよい。なお、図2Aでは、おもて面21の上方に設けられた電極および層間絶縁膜を省略している。

20

## 【0075】

第1アノード領域81は、複数のダミートレンチ部30の間に設けられた半導体基板10のメサ部61に設けられ、当該メサ部61の両端の複数のダミートレンチ部30と接する。この場合、トレンチのリサーフ効果によって、第1アノード領域81の表面電界が緩和される。本例のダミートレンチ部30は、ダミー絶縁膜32およびダミー導電部34を含む。

20

## 【0076】

メサ部は、半導体基板10の内部において、トレンチ部に挟まれた領域を指す。例えば、メサ部61は、ダミートレンチ部30に挟まれた半導体基板10の領域である。一例として、メサ部の上端は半導体基板10のおもて面21である。メサ部の下端の深さ位置は、トレンチ部の下端の深さ位置と同一である。

## 【0077】

第1アノード領域81および第2アノード領域82は、メサ長手方向において、交互に並んで設けられる。即ち、第2アノード領域82は、メサ長手方向において、第1アノード領域81に挟んで設けられる。第1アノード領域81の深さ方向(Z軸の負側の方向)には、第2アノード領域82が設けられ、おもて面21に露出する第2アノード領域82と一体的に形成されている。メサ長手方向とは、トレンチの延伸方向(即ち、Y軸方向)である。第1アノード領域81の面積は、おもて面21において、第2アノード領域82がおもて面21に露出する面積よりも大きい。本例の第1アノード領域81および第2アノード領域82の面積比率は、各メサ部で同一であるが、メサ部毎に異なっていてもよい。

30

## 【0078】

一例において、第1アノード領域81のY軸方向の幅と第2アノード領域82のY軸方向の幅との比率は3:1である。第1アノード領域81のY軸方向の幅と第2アノード領域82のY軸方向の幅との比率は、2:1であってもよく、4:1であってもよく、5:1であってよく、9:1であってよく、19:1であってよく、49:1であってよく、99:1であってよく、199:1であってよく、999:1であってもよい。当該比率は、同一のメサ部内で異なっていてもよい。

40

## 【0079】

例えば、第2アノード領域82の面積は、複数のダミートレンチ部30に挟まれたメサ部61のいずれかのおもて面21において、全面積の30%以下(2:1に相当)であってよく、25%以下(3:1に相当)であってよく、20%以下(4:1に相当)であってよく、10%以下(9:1に相当)であってよく、5%以下(19:1に相当)であってよく、2%以下(49:1に相当)であってよく、1%以下(99:1に相当)であってよく、0.5%以下(199:1に相当)であってよく、0.1%以下(999:1に相当)であってよく、

50

相当)であってもよい。また、第2アノード領域82の面積は、複数のダミートレンチ部30に挟まれたメサ部61のいずれかのおもて面21において、全面積の0.01%以下であってもよい。

#### 【0080】

なお、M-M線は、メサ部61をY軸方向に延伸する。M-M線を通るYZ断面は、図1Aの断面と構造が同一であってよい。即ち、図1Aの構造は、図1Bおよび図1Cのようなプレーナ型である半導体装置100のみならず、トレンチ型である半導体装置100にも適用されてよい。

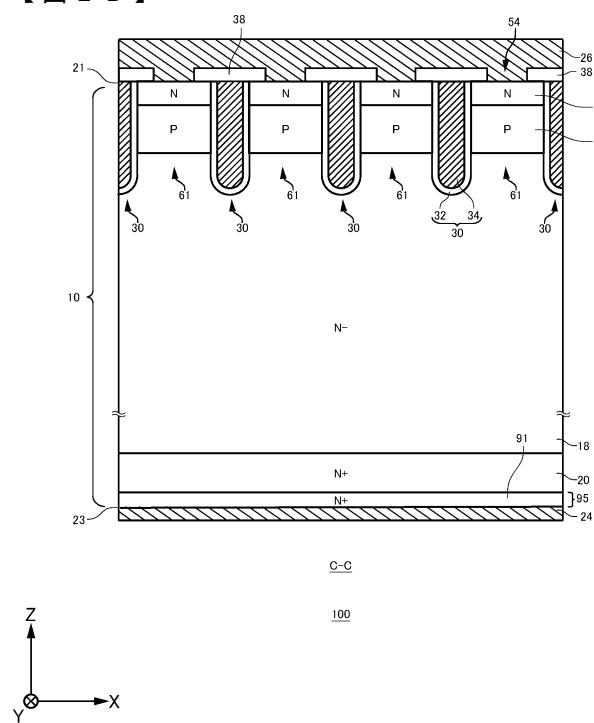

#### 【0081】

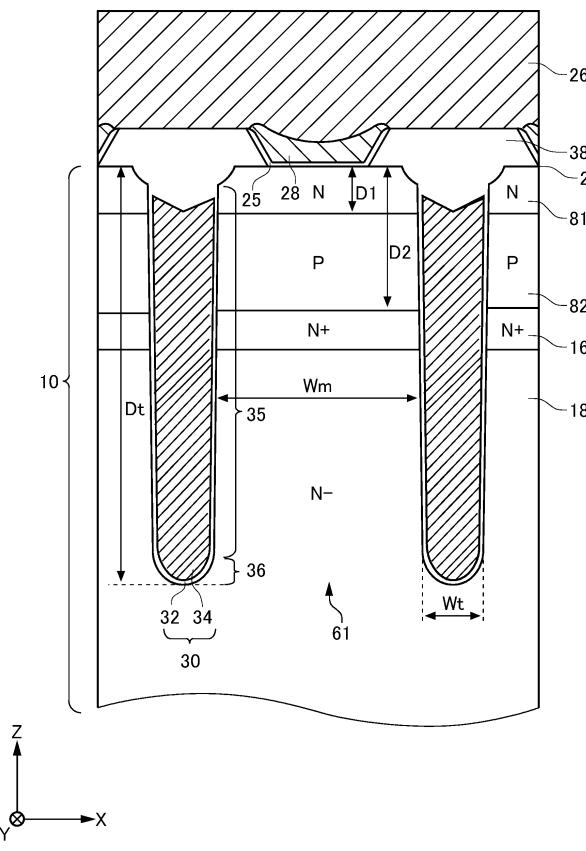

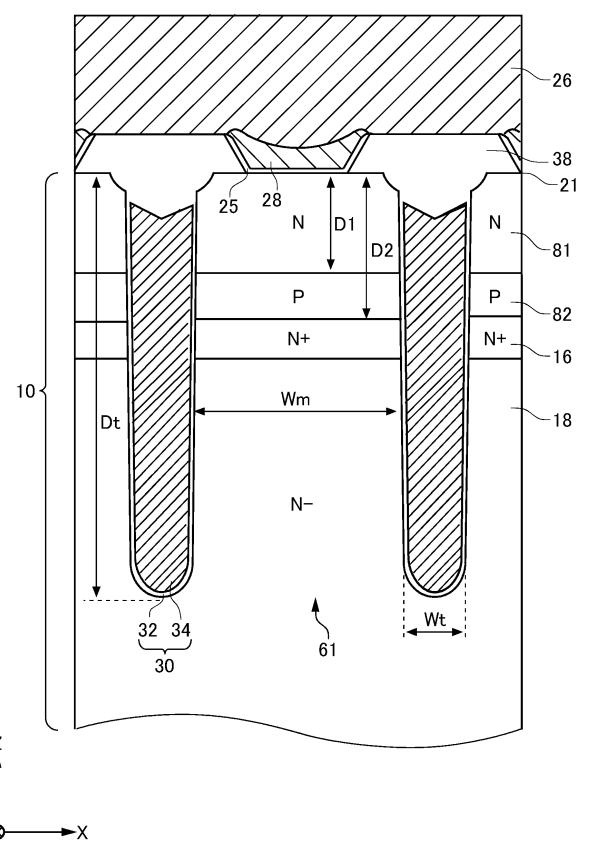

図2Bは、実施例3に係る半導体装置100の断面図の一例を示す。図2Bは、図2AのC-C断面の一例を示す。C-C断面は、おもて面21に第1アノード領域81が設けられた領域の断面である。第1アノード領域81の下方には、第2アノード領域82が設けられている。

10

#### 【0082】

ダミートレンチ部30は、半導体基板10のおもて面21に設けられたダミートレンチ、ダミー絶縁膜32およびダミー導電部34を有する。ダミー導電部34は、おもて面側電極26に電気的に接続されている。ダミー絶縁膜32は、ダミートレンチの内壁を覆つて設けられる。ダミー導電部34は、ダミートレンチの内部に設けられ、且つ、ダミー絶縁膜32よりも内側に設けられる。ダミー絶縁膜32は、ダミー導電部34と半導体基板10とを絶縁する。

20

#### 【0083】

層間絶縁膜38は、半導体基板10のおもて面21において、ダミートレンチ部30を覆っている。例えば、層間絶縁膜38は、HTO膜、BPSG膜、またはこれらの積層膜である。層間絶縁膜38には、コンタクトホール54が設けられ、おもて面側電極26と半導体基板10のおもて面21とが接続される。

#### 【0084】

第1アノード領域81は、メサ部61において第2アノード領域82よりもおもて面21側に設けられる。第1アノード領域81の半導体基板10の深さ方向の厚さは、第2アノード領域82の厚さよりも薄い。本例の第1アノード領域81の厚さは、第2アノード領域82の厚さの半分である。

30

#### 【0085】

バッファ領域20は、ドリフト領域18の下方に設けられる。バッファ領域20は、ドリフト領域18とカソード層95との間に設けられている。バッファ領域20の導電型は、N+型である。バッファ領域20のドーピング濃度は、ドリフト領域18のドーピング濃度よりも高い。バッファ領域20は、ドリフト領域18よりもドーピング濃度の高い1つまたは複数のドーピング濃度ピークを有する。複数のドーピング濃度ピークは、半導体基板10の深さ方向における異なる位置に配置される。バッファ領域20のドーピング濃度ピークは、例えば水素またはリンのドナー濃度ピークであってよい。あるいは、バッファ領域20が省略されてもよい。

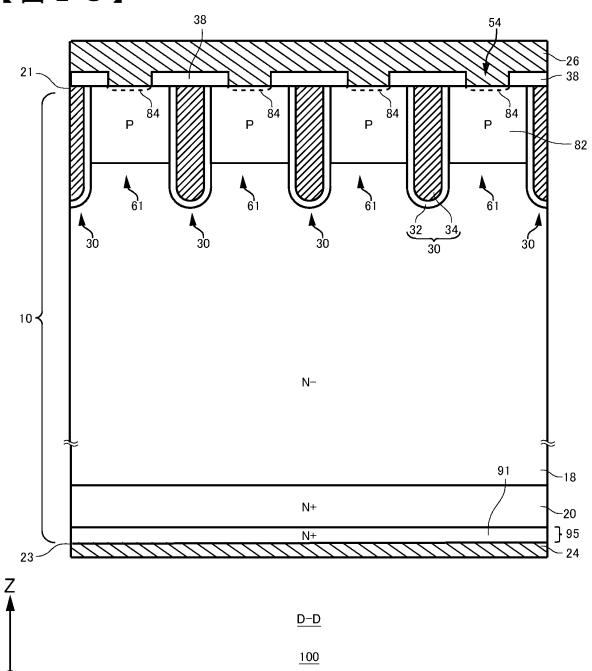

#### 【0086】

図2Cは、実施例3に係る半導体装置100の断面図の一例を示す。図2Cは、図2AのD-D断面の一例を示す。D-D断面は、おもて面21に第2アノード領域82が設けられた領域の断面である。破線で示すように、第2アノード領域82のおもて面21側にコンタクト領域84を備えてもよい。コンタクト領域84は、上面視でコンタクトホール54の形成されるおもて面21に形成されてよい。層間絶縁膜38の端部を除いて、第2アノード領域82が層間絶縁膜38と接する。層間絶縁膜38の端部は、コンタクト領域84がしみだしてよい。第2アノード領域82の下方には、ドリフト領域18が設けられている。D-D断面における第2アノード領域82の深さは、図2BのC-C断面における第2アノード領域82の深さと同一であってよい。

40

#### 【0087】

50

図 2 D は、実施例 4 に係る半導体装置 100 の断面図の一例を示す。本例の半導体装置 100 は、蓄積領域 16 を備える点で実施例 3 に係る半導体装置 100 と相違する。上面図は、図 2 A と共にあってよい。

【0088】

蓄積領域 16 は、ドリフト領域 18 よりドーピング濃度の高い第 1 導電型の領域である。蓄積領域 16 は、第 1 アノード領域 81 および第 2 アノード領域 82 の下方に設けられる。本例の蓄積領域 16 は、第 2 アノード領域 82 とドリフト領域 18 との間に設けられる。蓄積領域 16 は、メサ部 61 の全面に設けられてよい。蓄積領域 16 は、後述する配列方向において、メサ部 61 にわたってドーピング濃度が実質的に一様であってよい。あるいは、蓄積領域 16 は、メサ部 61 の配列方向における中央部に向かって、ドーピング濃度が減少してよく、増加してもよい。本例の蓄積領域 16 は、メサ部 61 にわたってドーピング濃度が実質的に一様である。

10

【0089】

なお、半導体装置 100 が蓄積領域 16 を備えるか否かについて、各実施例に限定されるものではない。即ち、半導体装置 100 は、蓄積領域 16 を有さない他の実施例においても、蓄積領域 16 を適宜備えてもよい。各実施例において、蓄積領域 16 が全面に設けられてもよく、選択的に設けられてもよい。

【0090】

図 3 A は、トレンチ型である半導体装置 100 の上面図の一例を示す。本例の半導体装置 100 では、おもて面 21 における第 1 アノード領域 81 と第 2 アノード領域 82 の比率が図 2 A の場合と相違する。なお、図 3 A では、おもて面 21 の上方に設けられた電極および層間絶縁膜を省略している。

20

【0091】

第 2 アノード領域 82 の上面は、複数のダミートレンチ部 30 に挟まれた複数のメサ部のいずれかのメサ部において、第 1 アノード領域 81 に全面が覆われる。これにより、第 2 アノード領域 82 の面積比を更に低下することができる。例えば、第 2 アノード領域 82 の面積は、複数のダミートレンチ部 30 に挟まれたメサ部のいずれかのおもて面 21 において、全面積の 1 % 以下である。また、第 2 アノード領域 82 の面積は、複数のダミートレンチ部 30 に挟まれたメサ部のいずれかのおもて面 21 において、全面積の 0.01 % 以下であってもよい。

30

【0092】

メサ部 61a は、おもて面 21 において、第 1 アノード領域 81 と第 2 アノード領域 82 とが交互に設けられたメサ部である。メサ部 61a において、第 1 アノード領域 81 および第 2 アノード領域 82 は、図 2 A の配置と同様に配置されてよい。即ち、第 1 アノード領域 81 の面積は、メサ部 61a のおもて面 21 において、第 2 アノード領域 82 の面積よりも大きくてよい。本例において、第 1 アノード領域 81 の Y 軸方向の幅と第 2 アノード領域 82 の Y 軸方向の幅との比率は 3 : 1 である。

【0093】

メサ部 61a の第 2 アノード領域 82 がおもて面 21 に露出する部分において、破線で示すように、第 2 アノード領域 82 のおもて面 21 側にコンタクト領域 84 を備えてもよい。

40

【0094】

メサ部 61b は、おもて面 21 において、第 1 アノード領域 81 が全面に設けられたメサ部である。即ち、メサ部 61b において、第 2 アノード領域 82 の上面は、第 1 アノード領域 81 に完全に覆われている。

【0095】

メサ部 61b は、メサ部 61a よりも多く設けられている。本例では、1 つのメサ部 61a に対して、3 つのメサ部 61b が設けられている。メサ部 61a とメサ部 61b の比率は、1 : 1 であってもよく、1 : 2 であってもよく、1 : 3 であってもよい。半導体装置 100 の全体を考慮した第 1 アノード領域 81 および第 2 アノード領域 82 の比率は

50

、メサ部 6 1 a およびメサ部 6 1 b の比率と、メサ部 6 1 a における第 1 アノード領域 8 1 と第 2 アノード領域 8 2 との比率とによって適宜調整されてよい。

【 0 0 9 6 】

図 3 B は、実施例 5 に係る半導体装置 1 0 0 の断面図の一例を示す。図 3 B は、図 3 A の E - E 断面に対応する。E - E 断面は、メサ部 6 1 a のおもて面 2 1 において、第 1 アノード領域 8 1 が設けられた領域の断面である。E - E 断面では、メサ部 6 1 a において、第 1 アノード領域 8 1 の下方に第 2 アノード領域 8 2 が設けられている。

【 0 0 9 7 】

図 3 C は、実施例 5 に係る半導体装置 1 0 0 の断面図の一例を示す。図 3 C は、図 3 A の F - F 断面に対応する。F - F 断面は、メサ部 6 1 a のおもて面 2 1 において、第 2 アノード領域 8 2 が設けられた領域の断面である。F - F 断面では、メサ部 6 1 a に第 1 アノード領域 8 1 が設けられていない。破線で示すように、第 2 アノード領域 8 2 のおもて面 2 1 側にコンタクト領域 8 4 を備えてもよい。コンタクト領域 8 4 は、上面視でコンタクトホール 5 4 の形成されるおもて面 2 1 に形成されてよい。層間絶縁膜 3 8 の端部を除いて、第 2 アノード領域 8 2 が層間絶縁膜 3 8 と接する。層間絶縁膜 3 8 の端部は、コンタクト領域 8 4 がしみだしてよい。

【 0 0 9 8 】

図 4 A は、半導体装置 1 0 0 のおもて面 2 1 側の構造を示す拡大図の一例である。本例では、ダミートレンチ部 3 0 の間のメサ部 6 1 が拡大されている。

【 0 0 9 9 】

第 1 アノード領域 8 1 の下端の深さ D 1 は、第 2 アノード領域 8 2 の下端の深さ D 2 の半分よりも浅い。例えば、第 2 アノード領域 8 2 の下端の深さ D 2 が  $3 \mu m$  の場合、第 1 アノード領域 8 1 の下端の深さ D 1 が  $1.5 \mu m$  よりも小さくなる。

【 0 1 0 0 】

接続部 2 8 は、第 1 アノード領域 8 1 とおもて面側電極 2 6 とを接続する。接続部 2 8 は、第 1 アノード領域 8 1 とショットキー接触する材料を含む。接続部 2 8 は、バリアメタル 2 5 を含んでよい。例えば、接続部 2 8 の材料は、タンゲステンである。接続部 2 8 は、コンタクトホール 5 4 等の開口に埋め込まれる。接続部 2 8 は、おもて面側電極 2 6 と接続されるプラグの一例である。

【 0 1 0 1 】

バリアメタル 2 5 は、接続部 2 8 において、半導体基板 1 0 のおもて面 2 1 に接して設けられる。バリアメタル 2 5 は、Ti、V、Ni、Mo、W、Pd、Cr および Pt の少なくとも 1 つを含んでよい。例えば、バリアメタル 2 5 は、Ti、V、Ni および Pt の少なくとも 1 つを含む。また、バリアメタル 2 5 は、チタン化合物等の化合物を含んでよい。バリアメタル 2 5 は、おもて面側電極 2 6 に含まれるアルミニウム原子の半導体基板 1 0 への拡散を抑制する。ショットキー障壁 B は、 $0.9 eV$  以下であってよく、 $0.7 eV$  以下であってよく、 $0.5 eV$  以下であってよく、 $0.3 eV$  以下であってもよい。

【 0 1 0 2 】

ダミートレンチ部 3 0 のトレンチ深さ D t は、第 2 アノード領域 8 2 の下端の深さ D 2 よりも深い。例えば、ダミートレンチ部 3 0 のトレンチ深さ D t は、 $5 \mu m$  以上、 $7 \mu m$  以下である。また、ダミートレンチ部 3 0 のトレンチ深さ D t は、第 2 アノード領域 8 2 の下端の深さ D 2 の 2 倍以上であってよい。

【 0 1 0 3 】

メサ幅 W m は、メサ部 6 1 の X 軸方向の幅である。即ち、メサ幅 W m は、隣接するダミートレンチ部 3 0 の間隔を示す。例えば、メサ幅 W m は、 $0.8 \mu m$  である。メサ幅 W m は、ダミートレンチ部 3 0 のトレンチ幅 W t よりも小さい。例えば、トレンチ幅 W t は、 $1.0 \mu m$  である。メサ幅 W m を小さくすることにより、ピンチオフ効果でリーク電流をさらに低減しやすくなる。

【 0 1 0 4 】

ダミートレンチ部 3 0 は、側壁領域 3 5 および底部領域 3 6 を有する。側壁領域 3 5 は

10

20

30

40

50

、ダミー絶縁膜32を挟んでダミー導電部34と対向するとともに、おもて面21側から裏面23側に向かってダミートレンチ部30が延伸する領域である。底部領域36は、ダミートレンチ部30の側壁領域35から、ダミートレンチ部30の最も深い（即ち、最も裏面23に近い）底部に向かって、ダミートレンチ部30の幅が減少する領域である。なお、本例のトレンチ構造の大きさは、ダミートレンチ部30のみならず後述するゲートトレンチ部40の場合にも共通に用いられてよい。

#### 【0105】

図4Bは、半導体装置100のおもて面21側の構造を示す拡大図の一例である。本例では、第1アノード領域81の下端の深さD1が図4Aの場合と相違する。

#### 【0106】

第1アノード領域81の下端の深さD1は、第2アノード領域82の下端の深さD2の半分よりも深く、第2アノード領域82の下端の深さD2よりも浅い。例えば、第2アノード領域82の深さが3μmの場合、第1アノード領域81の下端の深さD1が1.5μm以上である。また、第2アノード領域82の深さ方向の膜厚は、0.5μm以上であつてよい。

#### 【0107】

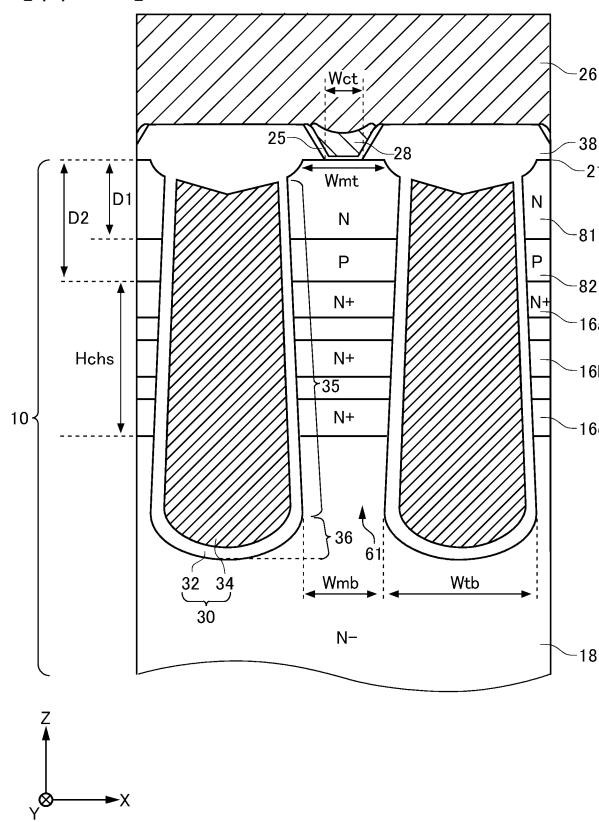

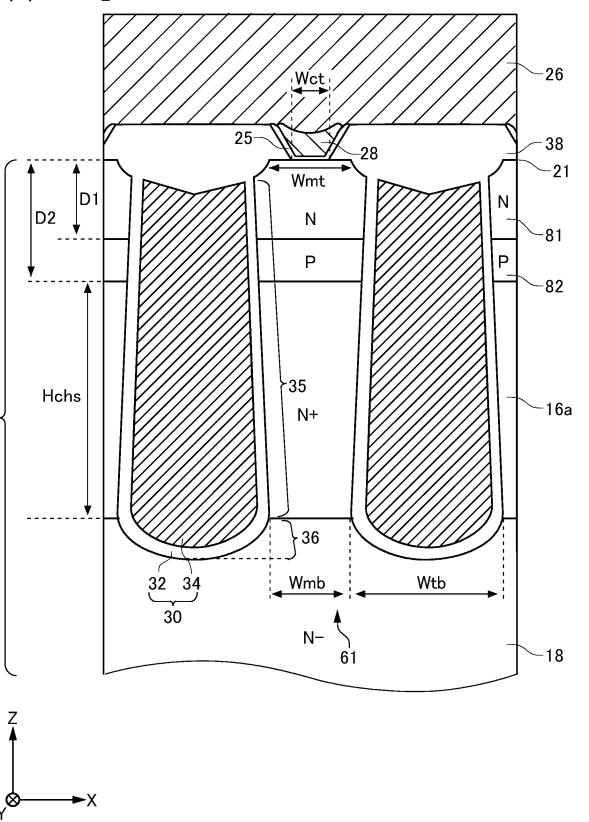

図4Cは、半導体装置100のおもて面21側の構造を示す拡大図の一例である。本例の構造は、メサ部61およびダミートレンチ部30の変形例である。本例の半導体装置100は、複数の蓄積領域16を備える。本例の蓄積領域16は、蓄積領域16a、蓄積領域16bおよび蓄積領域16cを含む。

#### 【0108】

蓄積領域16aは、第2アノード領域82の下方に設けられる。本例の蓄積領域16aは、第2アノード領域82の下端と接して設けられている。蓄積領域16bは、深さ方向において、蓄積領域16aと蓄積領域16cとの間に設けられる。蓄積領域16cは、蓄積領域16bの下方に設けられる。蓄積領域16aと蓄積領域16bとの間および蓄積領域16bと蓄積領域16cとの間には、ドリフト領域18が設けられてよい。蓄積領域16a、蓄積領域16bおよび蓄積領域16cのドーピング濃度は、同一であつてもよいし、異なっていてもよい。

#### 【0109】

蓄積領域16の深さ方向の幅Hchsは、複数の蓄積領域16が設けられている場合、複数の蓄積領域16の上端から下端までの厚みを示す。本例の幅Hchsは、蓄積領域16aの上端から蓄積領域16cの下端までの厚みを示す。本例では、蓄積領域16a、蓄積領域16bおよび蓄積領域16cの深さ方向の厚みが等しい。但し、蓄積領域16a、蓄積領域16bおよび蓄積領域16cの深さ方向の厚みは、それぞれ異なっていてもよい。

#### 【0110】

複数の蓄積領域16は、ドーピング濃度分布の複数のピークを備えてよい。複数のピーク間には、ドーピング濃度分布の谷を備えてよい。ドーピング濃度分布の谷のドーピング濃度は、ドリフト領域18よりもドーピング濃度が高くてよい。あるいは、複数の蓄積領域16は、ドーピング濃度分布がキンク状の濃度分布を備えてよい。複数の蓄積領域16は、ドナーとなる不純物（例えば、リン、水素等）を、異なる加速エネルギーで複数回にわたりイオン注入することで形成してよい。

#### 【0111】

複数の蓄積領域16のうち最も深い蓄積領域（本例では蓄積領域16c）の下端は、ダミートレンチ部30の半分の深さ位置よりも深くてよい。また、複数の蓄積領域16のうち最も深い蓄積領域の下端は、側壁領域35と底部領域36との境界と同一またはそれよりも浅くてよい。

#### 【0112】

上部メサ幅Wmtは、半導体基板10のおもて面21におけるメサ部61の幅である。上部メサ幅Wmtは、メサ部61における第1アノード領域81の上端の幅である。おもて面21に第1アノード領域81が設けられた領域は、おもて面21に第2アノード領域

10

20

30

40

50

8 2 が設けられた領域と同一の上部メサ幅  $W_{m\ t}$  を有してよい。

【 0 1 1 3 】

上部コンタクト幅  $W_{c\ t}$  は、半導体基板 1 0 のおもて面 2 1 に形成されるコンタクトホールの、おもて面 2 1 における幅である。コンタクトホールの幅とは、複数のダミートレンチ部 3 0 またはゲートトレンチ部 4 0 が配列する配列方向に沿った幅である。なお、配列方向は、平面視でおもて面 2 1 に平行であって、かつダミートレンチ部 3 0 またはゲートトレンチ部 4 0 が、細長く延伸して形成される延伸方向（または長手方向）に垂直な方向であってよい。

【 0 1 1 4 】

下部メサ幅  $W_{m\ b}$  は、ダミートレンチ部 3 0 の下部におけるメサ幅である。本例の下部メサ幅  $W_{m\ b}$  は、メサ部 6 1 の幅が最も狭くなる位置におけるメサ幅であってよい。

10

【 0 1 1 5 】

下部トレンチ幅  $W_{t\ b}$  は、下部メサ幅  $W_{m\ b}$  と同一の深さにおけるダミートレンチ部 3 0 の幅である。言い換えると、下部トレンチ幅  $W_{t\ b}$  は、ダミートレンチ部 3 0 の最大のトレンチ幅である。

【 0 1 1 6 】

上部メサ幅  $W_{m\ t}$  は、下部メサ幅  $W_{m\ b}$  よりも大きくてよい。即ち、本例のメサ部 6 1 は、おもて面 2 1 から裏面 2 3 に向けて徐々にメサ幅が狭くなっている。よって、本例のダミートレンチ部 3 0 は、おもて面 2 1 から裏面 2 3 に向けて徐々にトレンチ幅が大きくなる構造を有する。ゲートトレンチ部 4 0 も本例のダミートレンチ部 3 0 と同一の構造を有してよい。

20

【 0 1 1 7 】

上部メサ幅  $W_{m\ t}$  は、下部トレンチ幅  $W_{t\ b}$  よりも小さくてよい。下部トレンチ幅  $W_{t\ b}$  を大きくて、メサ部 6 1 の上端のメサ幅を狭くすることにより、おもて面側電極 2 6 からの正孔の注入をさらに抑制できる。

【 0 1 1 8 】

下部メサ幅  $W_{m\ b}$  は、上部コンタクト幅  $W_{c\ t}$  よりも小さくてよい。これにより、おもて面側電極 2 6 からの正孔の注入をさらに抑制できる。ダイオード部 8 0 における正孔の注入を抑えることで、逆回復電流あるいは逆回復電荷を低減することができ、逆回復特性を向上させることができる。

30

【 0 1 1 9 】

第 1 アノード領域 8 1 の下端の深さ  $D_1$  は、第 2 アノード領域 8 2 の下端の深さ  $D_2$  の半分よりも深い。言い換えると、第 1 アノード領域 8 1 の下端の深さ  $D_1$  は、第 1 アノード領域 8 1 の下端の深さ  $D_1$  と第 2 アノード領域 8 2 の下端の深さ  $D_2$  との差分よりも大きくてよい。例えば、第 2 アノード領域 8 2 の下端の深さ  $D_2$  が  $3\ \mu m$  の場合、第 1 アノード領域 8 1 の下端の深さ  $D_1$  が  $1.5\ \mu m$  よりも大きくなる。第 2 アノード領域 8 2 の下端の深さ  $D_2$  は、深さ方向の幅  $H_{c\ h\ s}$  よりも小さくてよい。これにより、さらに正孔の注入を抑制できる。

【 0 1 2 0 】

本例の半導体装置 1 0 0 は、メサ部 6 1 のメサ幅をおもて面 2 1 から裏面 2 3 に向けて徐々に小さくすることにより、第 1 アノード領域 8 1 の下端の深さ  $D_1$  が深い場合であっても、空乏層の第 1 アノード領域 8 1 へのパンチスルーパーを防ぐことができる。

40

【 0 1 2 1 】

なお、半導体装置 1 0 0 は、図 4 A または図 4 B のように、メサ部 6 1 の幅が裏面に向かって狭くならない実施例においても、複数の蓄積領域 1 6 を備えてよい。

【 0 1 2 2 】

図 4 D は、半導体装置 1 0 0 のおもて面 2 1 側の構造を示す拡大図の一例である。本例の構造は、メサ部 6 1 およびダミートレンチ部 3 0 の変形例である。本例の半導体装置 1 0 0 は、単一の蓄積領域 1 6 a を備える点で、図 4 C の半導体装置 1 0 0 と相違する。本例の蓄積領域 1 6 a は、図 4 C の蓄積領域 1 6 a よりも深さ方向における厚みが厚い。そ

50

の他の点では、図 4 C の半導体装置 100 と同一でよい。

【0123】

蓄積領域 16a は、第 2 アノード領域 82 の下方に設けられる。本例の蓄積領域 16a は、第 2 アノード領域 82 の下端と接して設けられている。蓄積領域 16a の深さ方向の厚さ  $H_{ch5}$  は、第 2 アノード領域 82 の下端の深さ  $D2$  より大きくてよい。蓄積領域 16a の下端は、ダミートレンチ部 30 の幅が、側壁領域 35 から、裏面 23 に向かって狭くなる底部に位置してよい。蓄積領域 16a は、配列方向において、メサ部 61 にわたって実質的に一様なドーピング濃度分布を有してよく、メサ部 61 の中央に向かってドーピング濃度が低下するドーピング濃度分布を有してよい。本例の蓄積領域 16a のドーピング濃度分布は、メサ部 61 の中央に向かってドーピング濃度が低下する。

10

【0124】

蓄積領域 16a は、深さ方向においてメサ部 61 にわたって実質的に一様なドーピング濃度分布を有してよく、裏面 23 に向かってドーピング濃度が増加する濃度分布を有してよい。本例の蓄積領域 16a は、深さ方向においてメサ部 61 にわたって裏面 23 に向かってドーピング濃度が増加する濃度分布を有する。

【0125】

蓄積領域 16a の下端は、ダミートレンチ部 30 の半分の深さ位置よりも深くてよい。また、蓄積領域 16a の下端は、側壁領域 35 と底部領域 36 との境界と同一またはそれよりも浅くてよい。本例の蓄積領域 16a の下端は、側壁領域 35 と底部領域 36 との境界と同一の深さにある。

20

【0126】

下部メサ幅  $W_{mb}$  は、熱平衡状態において、メサ部 61 が完全に空乏化する幅であってよい。あるいは、蓄積領域 16a の深さ方向においてドーピング濃度を積分した積分値が、熱平衡状態においてメサ部 61 が完全に空乏化する積分値であってよい。これにより、半導体装置 100 の耐圧低下を抑制できる。

【0127】

本例の蓄積領域 16a は、ドナーとなるドーパント（例えば、リン、水素等）を、ドーパントのピーク濃度が異なるように、予め定められた加速エネルギーで複数回にわたりイオン注入することで形成してよい。また、蓄積領域 16a は、ダミートレンチ部 30 の側壁において、ドナーとなるドーパントの1回のイオン注入により形成してもよい。

30

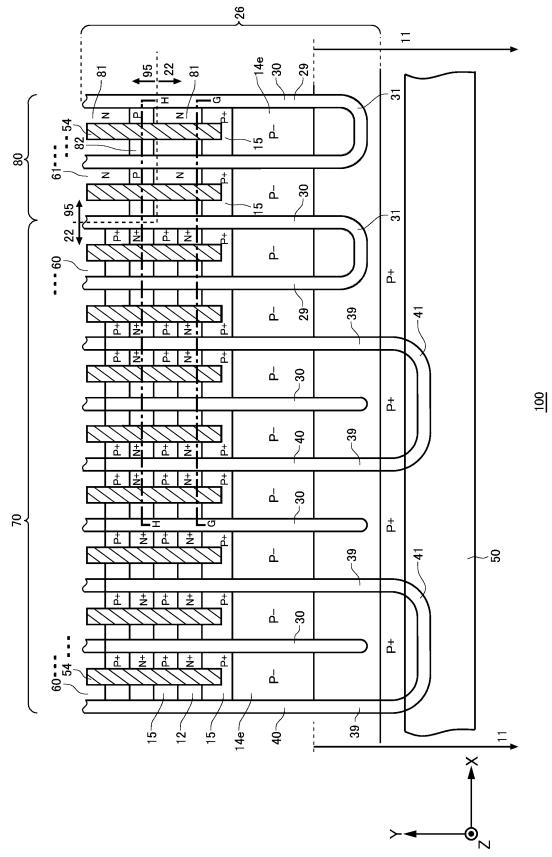

【0128】

図 5 A は、トレンチ型である半導体装置 100 の上面図の一例を示す。本例の半導体装置 100 は、トランジスタ部 70 およびダイオード部 80 を備える半導体チップである。例えば、半導体装置 100 は、逆導通 IGBT (RC-IGBT : Reverse Conducting IGBT) である。

【0129】

トランジスタ部 70 は、半導体基板 10 の裏面 23 側に設けられたコレクタ領域 22 を半導体基板 10 のおもて面 21 に投影した領域である。コレクタ領域 22 は、第 2 導電型を有する。本例のコレクタ領域 22 は、一例として P+ 型である。トランジスタ部 70 は、IGBT 等のトランジスタを含む。

40

【0130】

ダイオード部 80 は、カソード層 95 を半導体基板 10 のおもて面 21 に投影した領域であってよい。ダイオード部 80 は、半導体基板 10 のおもて面 21 においてトランジスタ部 70 と隣接して設けられた還流ダイオード (FWD : Free Wheel Diode) 等のダイオードを含む。

【0131】

なお、図 5 A においては、トランジスタ部 70 およびダイオード部 80 のエッジ側の領域を示しており、他の領域を省略している。例えば、本例の半導体装置 100 には、エッジ終端構造部が設けられてよい。エッジ終端構造部は、半導体基板 10 のおもて面 21 側の電界集中を緩和する。エッジ終端構造部は、例えばガードリング、フィールドプレート

50

、リサーフおよびこれらを組み合わせた構造を有する。

【0132】

おもて面21において、半導体装置100は、ゲートトレンチ部40、ダミートレンチ部30、ウェル領域11、エミッタ領域12、ベース領域14、コンタクト領域15、第1アノード領域81および第2アノード領域82を備える。ゲートトレンチ部40およびダミートレンチ部30は、それぞれがトレンチ部の一例である。

【0133】

おもて面側電極26およびゲート金属層50は、おもて面21の上方に設けられる。おもて面側電極26およびゲート金属層50は、互いに分離して設けられる。おもて面側電極26およびゲート金属層50と、おもて面21との間には層間絶縁膜が設けられるが、図5Aでは省略している。本例の層間絶縁膜には、コンタクトホール54が、当該層間絶縁膜を貫通して設けられる。図5Aにおいては、それぞれのコンタクトホール54に斜線のハッチングを付している。

10

【0134】

おもて面側電極26は、ゲートトレンチ部40、ダミートレンチ部30、ウェル領域11、エミッタ領域12、ベース領域14、コンタクト領域15、第1アノード領域81および第2アノード領域82の上方に設けられる。おもて面側電極26は、コンタクトホール54を通って、半導体基板10の上面におけるエミッタ領域12、コンタクト領域15、ベース領域14、第1アノード領域81および第2アノード領域82と接触する。また、おもて面側電極26は、層間絶縁膜に設けられたコンタクトホールを通って、ダミートレンチ部30内のダミー導電部と接続される。おもて面側電極26は、Y軸方向におけるダミートレンチ部30の先端において、ダミートレンチ部30のダミー導電部と接続されてよい。

20

【0135】

ゲート金属層50は、金属を含む材料で形成される。例えば、ゲート金属層50の少なくとも一部の領域は、アルミニウム、アルミニウムシリコン合金、またはアルミニウムシリコン-銅合金で形成されてよい。ゲート金属層50は、アルミニウム等で形成された領域の下層にチタンやチタン化合物等で形成されたバリアメタルを有してよい。ゲート金属層50は、層間絶縁膜に設けられたコンタクトホールを通って、ゲートトレンチ部40と接続する。ゲート金属層50は、Y軸方向におけるゲートトレンチ部40の先端部41において、ゲートトレンチ部40のゲート導電部と接続されてよい。ゲート金属層50は、ダミートレンチ部30内のダミー導電部とは接続されない。

30

【0136】

ウェル領域11は、ゲート金属層50と重なって設けられている。ウェル領域11は、ゲート金属層50と重ならない範囲にも、予め定められた幅で延伸して設けられている。本例のウェル領域11は、コンタクトホール54のY軸方向の端から、ゲート金属層50側に離れて設けられている。ウェル領域11は、ベース領域14よりもドーピング濃度の高い第2導電型の領域である。例えば、ベース領域14はP-型であり、ウェル領域11はP+型である。

40

【0137】

トランジスタ部70およびダイオード部80のそれぞれは、配列方向に複数配列されたトレンチ部を有する。本例のトランジスタ部70には、配列方向に沿って1以上のゲートトレンチ部40と、1以上のダミートレンチ部30とが交互に設けられている。本例のダイオード部80には、複数のダミートレンチ部30が、配列方向に沿って設けられている。本例のダイオード部80には、ゲートトレンチ部40が設けられていない。本例の配列方向はX軸方向である。

【0138】

ゲートトレンチ部40は、配列方向と垂直な延伸方向に沿って延伸する2つの直線部分39（延伸方向に沿って直線状であるトレンチの部分）と、2つの直線部分39を接続する先端部41を有してよい。本例の延伸方向はY軸方向である。

50

## 【0139】

先端部41の少なくとも一部は、上面視において曲線状に設けられることが好ましい。2つの直線部分39のY軸方向における端部どうしを先端部41が接続することで、直線部分39の端部における電界集中を緩和できる。

## 【0140】

トランジスタ部70において、ダミートレンチ部30はゲートトレンチ部40のそれぞれの直線部分39の間に設けられる。それぞれの直線部分39の間には、1本のダミートレンチ部30が設けられてよく、複数本のダミートレンチ部30が設けられていてもよい。ダミートレンチ部30は、延伸方向に延伸する直線形状を有してよく、ゲートトレンチ部40と同様に、直線部分29と先端部31とを有していてもよい。本例の半導体装置100は、先端部31を有さない直線形状のダミートレンチ部30と、先端部31を有するダミートレンチ部30の両方を含んでいる。

10

## 【0141】

ウェル領域11の拡散深さは、ゲートトレンチ部40およびダミートレンチ部30の深さよりも深くてよい。ゲートトレンチ部40およびダミートレンチ部30のY軸方向の端部は、上面視においてウェル領域11に設けられる。つまり、各トレンチ部のY軸方向の端部において、各トレンチ部の深さ方向の底部は、ウェル領域11に覆われている。これにより、各トレンチ部の当該底部における電界集中を緩和できる。

## 【0142】

メサ部60は、トランジスタ部70に設けられる。メサ部61は、ダイオード部80に設けられる。メサ部60およびメサ部61は、配列方向において各トレンチ部の間に設けられる。メサ部60およびメサ部61は、半導体基板10のおもて面21において、トレンチに沿って延伸方向（即ち、Y軸方向）に延伸して設けられている。

20

## 【0143】

それぞれのメサ部には、ベース領域14または第2アノード領域82が設けられる。メサ部において半導体基板10の上面に露出したベース領域14のうち、ゲート金属層50に最も近く配置された領域をベース領域14eとする。図5Aにおいては、それぞれのメサ部の延伸方向における一方の端部に配置されたベース領域14eを示しているが、それぞれのメサ部の他方の端部にもベース領域14eが配置されている。

## 【0144】

エミッタ領域12は、半導体基板10のおもて面21に設けられた第1導電型の領域である。本例のエミッタ領域12はN+型である。エミッタ領域12は、半導体基板10の上面に露出して、おもて面側電極26と電気的に接続されている。エミッタ領域12は、メサ部60に設けられている。エミッタ領域12は、ゲートトレンチ部40に接して設けられている。

30

## 【0145】

コンタクト領域15は、半導体基板10のおもて面21に設けられた第2導電型の領域である。本例のコンタクト領域15はP+型である。コンタクト領域15は、半導体基板10の上面に露出して、おもて面側電極26と電気的に接続されている。コンタクト領域15は、メサ部60に設けられている。エミッタ領域12およびコンタクト領域15は、深さ方向において、ベース領域14とおもて面21との間に設けられてよい。コンタクト領域15は、ゲートトレンチ部40に接するメサ部60に設けられてよい。

40

## 【0146】

メサ部60におけるエミッタ領域12およびコンタクト領域15のそれぞれは、X軸方向における一方のトレンチ部から、他方のトレンチ部まで設けられる。一例として、メサ部60のエミッタ領域12およびコンタクト領域15は、トレンチ部の延伸方向（即ち、Y軸方向）に沿って交互に配置されている。

## 【0147】

他の例においては、メサ部60のエミッタ領域12およびコンタクト領域15は、トレンチ部の延伸方向（即ち、Y軸方向）に沿ってストライプ状に設けられていてよい。例

50

えば、トレンチ部に接する領域にエミッタ領域 1 2 が設けられ、エミッタ領域 1 2 に挟まれた領域にコンタクト領域 1 5 が設けられる。

【 0 1 4 8 】

メサ部 6 1 には、第 1 アノード領域 8 1 および第 2 アノード領域 8 2 が設けられる。メサ部 6 1 には、エミッタ領域 1 2 が設けられていない。メサ部 6 1 は、他の実施例で示された配置で第 1 アノード領域 8 1 および第 2 アノード領域 8 2 が設けられてよい。即ち、メサ部 6 1 は、おもて面 2 1 において、第 1 アノード領域 8 1 および第 2 アノード領域 8 2 の繰り返し構造を有してもよく、第 1 アノード領域 8 1 のみを有してもよい。

【 0 1 4 9 】

メサ部 6 0 およびメサ部 6 1 の上方には、コンタクトホール 5 4 が設けられている。コンタクトホール 5 4 は、ベース領域 1 4 e に挟まれた領域に配置されている。本例のコンタクトホール 5 4 は、エミッタ領域 1 2 、ベース領域 1 4 、コンタクト領域 1 5 、第 1 アノード領域 8 1 および第 2 アノード領域 8 2 の各領域の上方に設けられる。コンタクトホール 5 4 は、ベース領域 1 4 e およびウェル領域 1 1 に対応する領域には設けられていない。コンタクトホール 5 4 は、メサ部の配列方向（即ち、X 軸方向）における中央に配置されてよい。

【 0 1 5 0 】

ダイオード部 8 0 において、半導体基板 1 0 の裏面 2 3 と隣接する領域には、カソード層 9 5 が設けられる。図 5 A においては、カソード層 9 5 およびコレクタ領域 2 2 の境界を破線で示している。

【 0 1 5 1 】

カソード層 9 5 は、Y 軸方向においてウェル領域 1 1 から離れて配置されている。これにより、比較的にドーピング濃度が高く、且つ、深い位置まで形成されている P 型の領域（ウェル領域 1 1 ）と、カソード層 9 5 との距離を確保して、耐圧を向上できる。本例のカソード層 9 5 の Y 軸方向における端部は、コンタクトホール 5 4 の Y 軸方向における端部よりも、ウェル領域 1 1 から離れて配置されている。他の例では、カソード層 9 5 の Y 軸方向における端部は、ウェル領域 1 1 とコンタクトホール 5 4 との間に配置されていてよい。

【 0 1 5 2 】

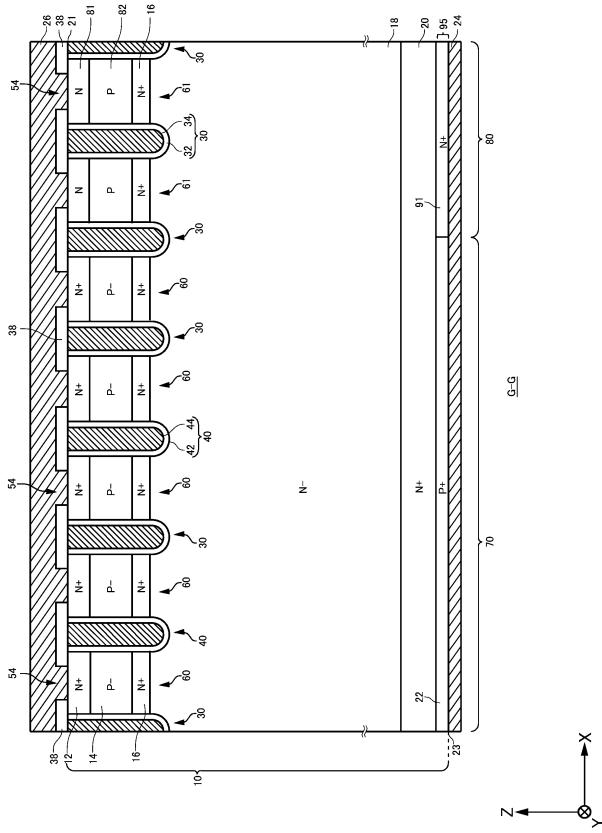

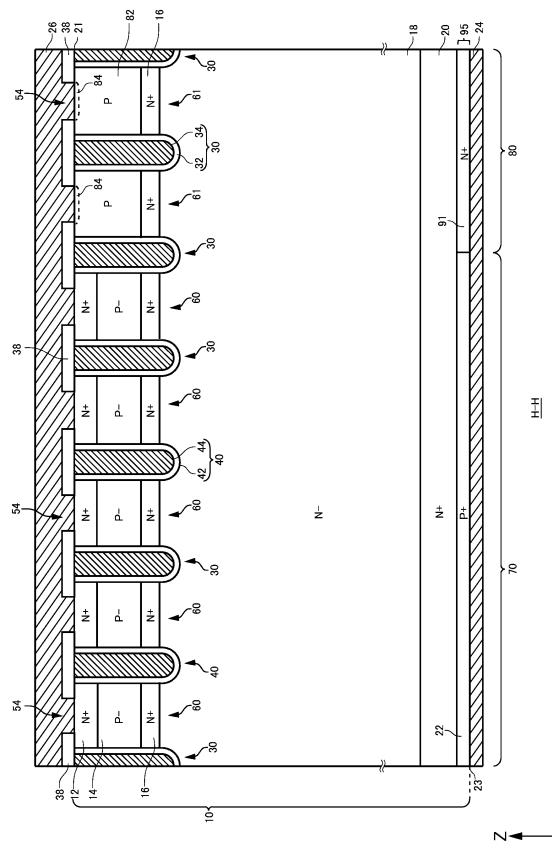

図 5 B は、実施例 6 に係る半導体装置 1 0 0 の断面図の一例を示す。図 5 B は、図 5 A の G - G 断面の一例を示す。G - G 断面は、ダイオード部 8 0 のおもて面 2 1 において、第 1 アノード領域 8 1 を含む断面である。

【 0 1 5 3 】

蓄積領域 1 6 は、ベース領域 1 4 の下方に設けられている。蓄積領域 1 6 は、ドリフト領域 1 8 よりもドーピング濃度が高い N + 型の領域である。ドリフト領域 1 8 とベース領域 1 4 との間に高濃度の蓄積領域 1 6 を設けることで、キャリア注入促進効果（ I E 効果）を高めて、オン電圧を低減できる。蓄積領域 1 6 は、各メサ部 6 0 におけるベース領域 1 4 の下面全体を覆うように設けられてよい。

【 0 1 5 4 】

また、蓄積領域 1 6 は、第 2 アノード領域 8 2 の下方にも設けられている。蓄積領域 1 6 は、各メサ部 6 1 における第 2 アノード領域 8 2 の下面全体を覆うように設けられてよい。トランジスタ部 7 0 およびダイオード部 8 0 の蓄積領域 1 6 は、同一のプロセスで設けられてよい。

【 0 1 5 5 】

半導体装置 1 0 0 は、キラーが設けられていないノンキラー構造を有してよい。ノンキラー構造の場合、裏面 2 3 側のキャリアに電界がかからず、再結合でキャリアが消滅するので、消滅に時間がかかる。また、ノンキラー構造のダイオードは、キラーを備えたライフタイムの低いダイオードに比べて、定格電流に必要な深さ方向の総電荷量が 1 枝以上多くなる場合がある。総電荷量の増加により逆回復電荷  $Q_{rr}$  が増加するので、注入効率を低減することが好ましい。本例の半導体装置 1 0 0 は、第 1 アノード領域 8 1 および第 2

10

20

30

40

50

アノード領域 8 2 の比率を調整することにより注入効率を低減して、ノンキラー構造を実現することができる。

【 0 1 5 6 】

また、半導体装置 1 0 0 は、ノンキラー構造なので、長時間通電時にキラーの密度が低下することにより生じるダイオードの順方向電圧  $V_f$  の低下を抑制できる。但し、半導体装置 1 0 0 は、ノンキラー構造に限定されるものではない。

【 0 1 5 7 】

バッファ領域 2 0 は、トランジスタ部 7 0 およびダイオード部 8 0 のそれぞれにおいて、ドリフト領域 1 8 の下方に設けられてよい。バッファ領域 2 0 の導電型は、N + 型である。バッファ領域 2 0 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。バッファ領域 2 0 は、ドリフト領域 1 8 よりもドーピング濃度の高い 1 つまたは複数のドーピング濃度ピークを有する。複数のドーピング濃度ピークは、半導体基板 1 0 の深さ方向における異なる位置に配置される。バッファ領域 2 0 のドーピング濃度ピークは、例えば水素またはリンのドナー濃度ピークであってよい。バッファ領域 2 0 は、ベース領域 1 4 の下端から広がる空乏層が、コレクタ領域 2 2 および第 1 カソード領域 9 1 に到達することを防ぐフィールドストップ層として機能してよい。

10

【 0 1 5 8 】

コレクタ領域 2 2 は、トランジスタ部 7 0 において、バッファ領域 2 0 よりも裏面 2 3 側に設けられる。本例のコレクタ領域 2 2 は、P + 型である。コレクタ領域 2 2 のドーピング濃度は、ベース領域 1 4 および第 2 アノード領域 8 2 のドーピング濃度より高い。コレクタ領域 2 2 は、ベース領域 1 4 と同一のアクセプタを含んでよく、異なるアクセプタを含んでもよい。コレクタ領域 2 2 のアクセプタは、例えばボロンである。

20

【 0 1 5 9 】

第 1 カソード領域 9 1 は、ダイオード部 8 0 において、バッファ領域 2 0 よりも裏面 2 3 側に設けられる。本例の第 1 カソード領域 9 1 は、N + 型である。第 1 カソード領域 9 1 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度より高い。例えば、第 1 カソード領域 9 1 のドーピング濃度は、 $1 E 1 9 \text{ cm}^{-3}$  以上である。第 1 カソード領域 9 1 のドナーは、例えば水素またはリンである。なお、各領域のドナーおよびアクセプタとなる元素は、上述した例に限定されない。

30

【 0 1 6 0 】

コレクタ領域 2 2 および第 1 カソード領域 9 1 は、半導体基板 1 0 の裏面 2 3 に露出しており、裏面側電極 2 7 と電気的に接続されている。裏面側電極 2 7 は、半導体基板 1 0 の裏面 2 3 全体と接触してよい。おもて面側電極 2 6 および裏面側電極 2 7 は、アルミニウム等の金属材料で形成されている。

【 0 1 6 1 】

半導体基板 1 0 のおもて面 2 1 側には、1 以上のゲートトレンチ部 4 0 、および、1 以上のダミートレンチ部 3 0 が設けられる。各トレンチ部は、半導体基板 1 0 のおもて面 2 1 から、ベース領域 1 4 または第 2 アノード領域 8 2 を貫通して、ドリフト領域 1 8 に到達している。エミッタ領域 1 2 、コンタクト領域 1 5 、蓄積領域 1 6 および第 1 アノード領域 8 1 の少なくともいずれかが設けられている領域においては、各トレンチ部はこれらのドーピング領域も貫通して、ドリフト領域 1 8 に到達している。トレンチ部がドーピング領域を貫通するとは、ドーピング領域を形成してからトレンチ部を形成する順序で製造したものに限定されない。トレンチ部を形成した後に、トレンチ部の間にドーピング領域を形成したものも、トレンチ部がドーピング領域を貫通しているものに含まれる。

40

【 0 1 6 2 】

ゲートトレンチ部 4 0 は、半導体基板 1 0 のおもて面 2 1 に設けられたゲートトレンチ、ゲート絶縁膜 4 2 およびゲート導電部 4 4 を有する。ゲート絶縁膜 4 2 は、ゲートトレンチの内壁を覆って設けられる。ゲート絶縁膜 4 2 は、ゲートトレンチの内壁の半導体を酸化または窒化して形成してよい。ゲート導電部 4 4 は、ゲートトレンチの内部においてゲート絶縁膜 4 2 よりも内側に設けられる。つまりゲート絶縁膜 4 2 は、ゲート導電部 4

50

4と半導体基板10とを絶縁する。ゲート導電部44は、ポリシリコン等の導電材料で形成される。

【0163】

ゲート導電部44は、深さ方向において、ベース領域14よりも長く設けられてよい。当該断面におけるゲートトレンチ部40は、半導体基板10のおもて面21において層間絶縁膜38により覆われる。ゲート導電部44は、ゲート配線に電気的に接続されている。ゲート導電部44に所定のゲート電圧が印加されると、ベース領域14のうちゲートトレンチ部40に接する界面の表層に電子の反転層によるチャネルが形成される。

【0164】

ダミー導電部34は、ゲート導電部44と同一の材料で形成されてよい。例えばダミー導電部34は、ポリシリコン等の導電材料で形成される。ダミー導電部34は、深さ方向においてゲート導電部44と同一の長さを有してよい。

10

【0165】

本例のゲートトレンチ部40およびダミートレンチ部30は、半導体基板10のおもて面21において層間絶縁膜38により覆われている。なお、ダミートレンチ部30およびゲートトレンチ部40の底部は、下側に凸の曲面状(断面においては曲線状)であってよい。

【0166】

図5Cは、実施例6に係る半導体装置100の断面図の一例を示す。図5Aは、図5AのH-H断面の一例を示す。H-H断面は、ダイオード部80のおもて面21において、第2アノード領域82を含む断面である。H-H断面では、メサ部61には第1アノード領域81が設けられていない。ダイオード部80のおもて面21において、破線で示すように、第2アノード領域82のおもて面21側にコンタクト領域84を備えてもよい。コンタクト領域84は、上面視でコンタクトホール54の形成されるおもて面21に形成されてよい。層間絶縁膜38の端部を除いて、第2アノード領域82が層間絶縁膜38と接する。層間絶縁膜38の端部は、コンタクト領域84がしみだしてよい。第2アノード領域82とドリフト領域18との間には、蓄積領域16が設けられてよい。

20

【0167】

図5Dは、実施例7に係る半導体装置100の断面図の一例を示す。図5Aは、図5AのG-G断面の他の例を示す。本例の半導体装置100は、キラー65を備える点で図5Bの実施例と相違する。

30

【0168】

キラー65は、ドリフト領域18に設けられる。キラー65は、再結合中心であってよい。本例のキラー65は、蓄積領域16の下方に設けられる。キラー65は、メサ部60およびメサ部61にも設けられてよい。キラー65は、キャリアのライフタイムを短く制御する。本例の半導体装置100は、第1アノード領域81および第2アノード領域82を備えるので、ドリフト領域18に設けるキラーの濃度を高ドーピング濃度にする必要がない。

【0169】

一例において、キラー65は、半導体基板10に空孔型格子欠陥を生成することにより設けられる。例えば、空孔型格子欠陥は、水素イオンの注入により生成される。また、空孔型欠陥は、ヘリウムイオン、電子線等、水素イオン以外の荷電粒子を半導体基板10に照射することで生成されてもよい。即ち、キラー65は空孔型格子欠陥であってよく、ヘリウムであってもよく、水素であってもよい。

40

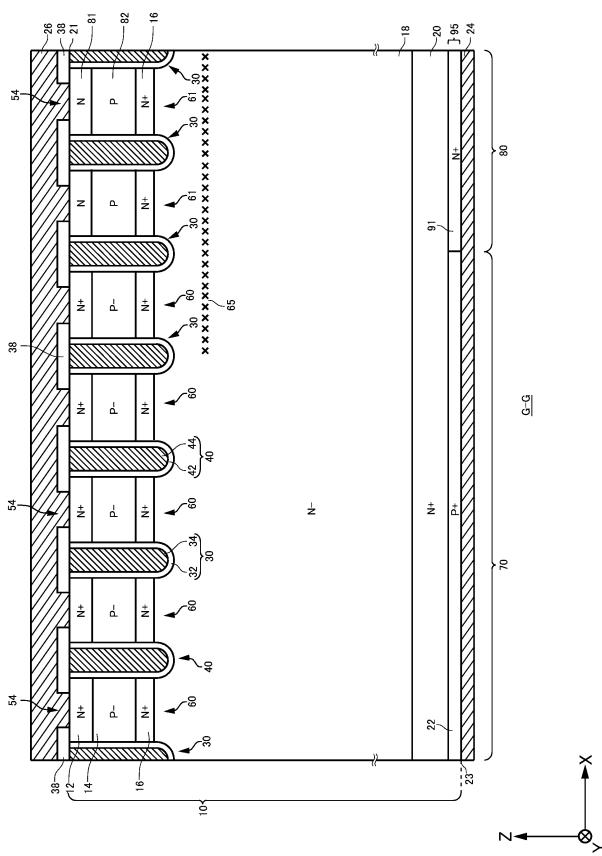

【0170】

図6Aは、実施例8に係る半導体装置100の断面図の一例を示す。図6Aは、トランジスタ部70とダイオード部80との境界近傍におけるカソード層95の他の例を示している。本例の半導体装置100は、カソード層95として、裏面側カソード部90を備える。なお、本例のカソード層95の構造は、他の実施例においても、適宜適用されてよい。

【0171】

50

裏面側カソード部 9 0 は、裏面 2 3 に設けられる。裏面側カソード部 9 0 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 を備える。本例の裏面側カソード部 9 0 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 の繰り返し構造を含む。

【 0 1 7 2 】

第 1 カソード領域 9 1 は、第 1 導電型の領域である。本例の第 1 カソード領域 9 1 は、N + 型である。第 1 カソード領域 9 1 は、半導体基板 1 0 の裏面 2 3 側に設けられている。第 1 カソード領域 9 1 は、裏面側電極 2 7 と接して設けられる。

【 0 1 7 3 】

第 2 カソード領域 9 2 は、第 1 カソード領域 9 1 と隣接して設けられた第 2 導電型の領域である。本例の第 2 カソード領域 9 2 は、P + 型である。第 2 カソード領域 9 2 は、半導体基板 1 0 の裏面 2 3 側に設けられている。第 2 カソード領域 9 2 は、第 1 カソード領域 9 1 と隣接して設けられる。本例の第 2 カソード領域 9 2 は、第 1 カソード領域 9 1 と接して設けられる。第 2 カソード領域 9 2 は、裏面側電極 2 7 と接して設けられる。例えば、第 2 カソード領域 9 2 のドーピング濃度は、 $1 E 1 5 \text{ cm}^{-3}$  以上、 $1 E 1 8 \text{ cm}^{-3}$  以下である。

10

【 0 1 7 4 】

本例の半導体装置 1 0 0 は、カソード層 9 5 として、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 の両方を備える。また、第 2 カソード領域 9 2 の面積は、裏面 2 3 において、第 1 カソード領域 9 1 の面積よりも大きくてよい。このように、N + 型である第 1 カソード領域 9 1 の面積の比率を小さくすることにより、裏面 2 3 側からの電子の注入効率も低下させることができる。第 1 カソード領域 9 1 および第 2 カソード領域 9 2 は、電流の集中を防止するために、規則的な繰り返し構造であることが好ましい。

20

【 0 1 7 5 】

図 6 B は、実施例 9 に係る半導体装置 1 0 0 の断面図の一例を示す。本例では、裏面 2 3 に設けられる第 1 カソード領域 9 1 と第 2 カソード領域 9 2 との面積の比率が、図 6 A の場合と相違する。なお、本例のカソード層 9 5 の構造は、他の実施例においても、適宜適用されてよい。

【 0 1 7 6 】

裏面 2 3 において、第 2 カソード領域 9 2 の面積は、第 1 カソード領域 9 1 の面積よりも大きい。例えば、第 2 カソード領域 9 2 の X 軸方向の幅は、第 1 カソード領域 9 1 の X 軸方向の幅よりも大きい。第 2 カソード領域 9 2 の X 軸方向の幅は、第 1 カソード領域 9 1 の X 軸方向の幅の 1.5 倍以上であってもよく、2 倍以上であってもよい。裏面 2 3 における第 2 カソード領域 9 2 の面積を、第 1 カソード領域 9 1 の面積よりも大きくすることにより、裏面 2 3 からの電子の注入を抑制しやすくなる。

30

【 0 1 7 7 】

図 6 C は、実施例 1 0 に係る半導体装置 1 0 0 の断面図の一例を示す。図 6 C は、トランジスタ部 7 0 とダイオード部 8 0 との境界近傍におけるカソード層 9 5 の他の例を示している。本例の半導体装置 1 0 0 は、カソード層 9 5 として、裏面側カソード部 9 0 およびおもて面側カソード部 9 3 の 2 層構造を備える。なお、本例のカソード層 9 5 の構造は、他の実施例においても、適宜適用されてよい。

40

【 0 1 7 8 】

裏面側カソード部 9 0 は、半導体基板 1 0 の裏面 2 3 において、裏面側電極 2 7 と接して設けられる。裏面側カソード部 9 0 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 を備える。裏面側カソード部 9 0 は、図 6 A または図 6 B の裏面側カソード部 9 0 と同一の構造を有してよい。即ち、裏面側カソード部 9 0 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 の繰り返し構造を有する。

【 0 1 7 9 】

おもて面側カソード部 9 3 は、裏面側カソード部 9 0 よりも半導体基板 1 0 のおもて面側に設けられた、第 2 導電型の領域である。本例のおもて面側カソード部 9 3 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 と隣接して設けられている。例えば、おもて

50

面側カソード部 9 3 は、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 と接して設けられる。おもて面側カソード部 9 3 は、開口 9 4 を有する。

【 0 1 8 0 】

また、おもて面側カソード部 9 3 は、裏面側カソード部 9 0 の第 2 カソード領域 9 2 と同時に形成されてよい。即ち、第 2 カソード領域 9 2 およびおもて面側カソード部 9 3 を形成するためのイオン注入は、同一の工程によって実行されてよい。

【 0 1 8 1 】

開口 9 4 は、第 1 カソード領域 9 1 のおもて面側に設けられている。開口 9 4 の直径 D は、第 1 カソード領域 9 1 のトレーナ配列方向 (X 軸方向) の幅 C よりも小さい。開口 9 4 の直径 D は、第 1 カソード領域 9 1 の幅 C の半分以下であってもよい。開口 9 4 の直径 D を調整することにより、さらに電子の注入効率を調整してもよい。例えば、開口 9 4 の直径 D をより小さくすることにより、電子の注入効率が低減する。

10

【 0 1 8 2 】

図 6 D は、実施例 1 1 に係る半導体装置 1 0 0 の裏面 2 3 における下面図の一例を示す。図 6 D は、半導体基板 1 0 の裏面 2 3 を、Z 軸方向の負側から正側に見た図である。本例の半導体装置 1 0 0 は、カソード層 9 5 として、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 を有する。なお、本例のカソード層 9 5 の構造は、他の実施例においても、適宜適用されてよい。

20

【 0 1 8 3 】

第 1 カソード領域 9 1 は、裏面 2 3 において、予め定められた直径の真円形状を有する。第 1 カソード領域 9 1 の形状は、橢円であっても、円形以外の形状であってもよい。第 1 カソード領域 9 1 は、裏面 2 3 において規則的に設けられる。例えば、第 1 カソード領域 9 1 は、1 つの真円の周囲に、4 つの真円が等間隔に配置された構造を有する。但し、第 1 カソード領域 9 1 の配置は不規則であってもよい。第 1 カソード領域 9 1 は、ダイオード部 8 0 に設けられ、トランジスタ部 7 0 に設けられなくてよい。

【 0 1 8 4 】

第 1 カソード領域 9 1 の面積は、裏面 2 3 において、第 2 カソード領域 9 2 の面積よりも小さくてよい。これにより、裏面 2 3 側からの電子の注入効率が低下する。第 1 カソード領域 9 1 の面積は、半導体基板 1 0 の裏面において、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 の合計面積の 50 % 以下であってよく、25 % 以下であってよく、10 % 以下であってよい。本例の第 1 カソード領域 9 1 の面積は、半導体基板 1 0 の裏面において、第 1 カソード領域 9 1 および第 2 カソード領域 9 2 の合計面積の 10 % 以下である。第 1 カソード領域 9 1 と第 2 カソード領域 9 2 との面積比率は本例に限定されない。

30

【 0 1 8 5 】

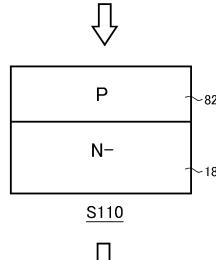

図 7 A は、プレーナ型である半導体装置 1 0 0 の製造方法の一例を示す。本例のフローチャートは、ダイオード部 8 0 を備える半導体装置 1 0 0 を製造する場合の工程を示す。本例の製造方法は、ステップ S 1 0 0 からステップ S 1 3 2 までを備える。ただし全てのステップを備えることが必須ではなく、各ステップを省略または変更できる。

30

【 0 1 8 6 】

ステップ S 1 0 0 において、半導体基板 1 0 を熱酸化する。例えば、熱酸化工程の温度は 1 2 0 0 である。ステップ S 1 0 2 において、半導体基板 1 0 のおもて面 2 1 の端部にエッジ終端構造部を形成する。例えば、エッジ終端構造部として P + 型のガードリングが設けられる。

40

【 0 1 8 7 】

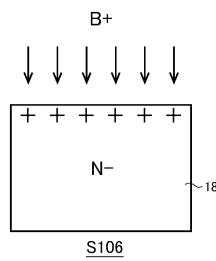

ステップ S 1 0 4 において、第 2 アノード領域 8 2 をイオン注入するためのレジストをパターニングする。ステップ S 1 0 6 において、第 2 アノード領域 8 2 をイオン注入により形成する。第 2 アノード領域 8 2 は、おもて面 2 1 側から一様にイオン注入することにより形成されてよい。例えば、ボロンが、加速エネルギー 1 0 0 k e V 以上、3 0 0 k e V 以下で、ドーズ量 1 E 1 3 c m - 2 以上、1 E 1 4 c m - 2 以下の条件でイオン注入される。ステップ S 1 0 8 において、レジストを除去する。ステップ S 1 1 0 において、拡散

50

工程により第2アノード領域82を形成する。例えば、温度1050以上、1200以下で、1時間以上、3時間以下の条件で拡散される。

【0188】

ステップS112において、第1アノード領域81をイオン注入するためのレジストをパターニングする。ステップS114において、第1アノード領域81のイオン注入を行う。例えば、ドーズ量2E13cm<sup>-2</sup>以上、2E14cm<sup>-2</sup>以下で、加速エネルギー50keV以上、250keV以下の条件でリンがイオン注入される。即ち、第2アノード領域82のドーパントの加速エネルギーよりも、第1アノード領域81のドーパントの加速エネルギーが低い。ステップS116において、レジストを除去する。ステップS118において、拡散工程により第1アノード領域81を形成する。例えば、温度1000以上、1150以下で、1時間以上、3時間以下の条件で拡散される。

10

【0189】

ステップS120において、半導体基板10のおもて面21上に層間絶縁膜38を成膜する。例えば、層間絶縁膜38は、HTO膜、BPSG膜、またはこれらの積層膜である。一例において、層間絶縁膜38の膜厚が1.5μmであり、970でリフローされる。ステップS122において、層間絶縁膜38を開口する。開口後、950でアニールしてもよい。層間絶縁膜38を開口した領域にバリアメタル25を成膜して、シンターする。バリアメタル25の材料は、Ti、V、Ni、Mo、W、Pd、CrおよびPtの少なくとも1つを含んでよい。一例において、バリアメタル25は、スパッタリングによって成膜される。例えば、バリアメタル25の膜厚は500である。シンターの温度は、600以上、900以下であってよい。

20

【0190】

ステップS124において、おもて面側電極26を成膜する。例えば、おもて面側電極26は、スパッタリングにより成膜されたAlSi膜である。一例において、AlSi膜の膜厚は、5μmである。その後、420程度でシンターされてよい。

【0191】

ステップS126において、半導体基板10は、バックグラインド等の処理により薄板化される。本例の裏面23は、バックグラインド等の研削面であってよい。薄板化により、半導体基板10が120μm程度の最終厚を有してよい。ステップS128において、パシベーション膜を成膜する。例えば、パシベーション膜はポリイミド膜である。

30

【0192】

ステップS130において、半導体装置100の裏面構造を形成する。半導体装置100の裏面構造には、コレクタ領域22、カソード層95およびバッファ領域20等が含まれる。バッファ領域20にはプロトンが注入されてよい。また、バッファ領域20には、ヘリウムイオンまたは電子線の注入によって、ライフトайム制御処理が実行されてよい。

【0193】

ステップS132において、裏面側電極27を形成する。例えば、Al、Ti、NiおよびAuをスパッタリングによって成膜して裏面側電極27を形成する。

【0194】

図7Bは、トレンチ型である半導体装置100の製造方法の一例を示す。本例の製造方法は、半導体装置100がトレンチ部を有する場合の製造方法である。本例では、図7Aと相違する点について特に説明する。

40

【0195】

ステップS103において、半導体基板10のおもて面21にトレンチ部を形成する。より具体的には、トレンチエッティング工程、犠牲酸化工程、ゲート酸化工程およびポリシリコン形成工程等を含む。これにより、ダミートレンチ、ダミー絶縁膜32およびダミー導電部34からなるダミートレンチ部30が形成される。一例において、ステップS103は、図7AのステップS102とステップS104との間で実行される。

【0196】

ステップS123において、接続部28を形成する。接続部28は、タンゲステンであ

50

り、膜厚が $0.5\text{ }\mu\text{m}$ であってよい。接続部28は、エッチング方式またはリフトオフ方式によって成膜されてよい。本例の接続部28は、エッチング方式で成膜される。一例において、ステップS123は、図7AのステップS122とステップS124との間で実行される。

#### 【0197】

なお、RC-IGBTの場合、ベース領域14は、第2アノード領域82と同一の工程により形成されてよい。この場合、ベース領域14は、第2アノード領域82と同一の深さとなってよい。ゲートトレンチ部40は、ダミートレンチ部30と同一のプロセスにより形成されてよい。

#### 【0198】

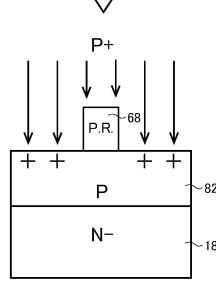

図8は、第1アノード領域81および第2アノード領域82の製造工程の一例を示す。各ステップSは、図7Aおよび図7Bの各ステップに対応している。

#### 【0199】

ステップS106では、N-型の半導体基板10にボロンをイオン注入している。これにより、ステップS110で示したように第2アノード領域82が半導体基板10のおもて面21側に形成されている。

#### 【0200】

ステップS114では、レジスト68を介してリンをイオン注入している。ステップS118の拡散工程により、第1アノード領域81が第2アノード領域82の上方に設けられる。ステップS124において、おもて面側電極26がおもて面21上に設けられる。

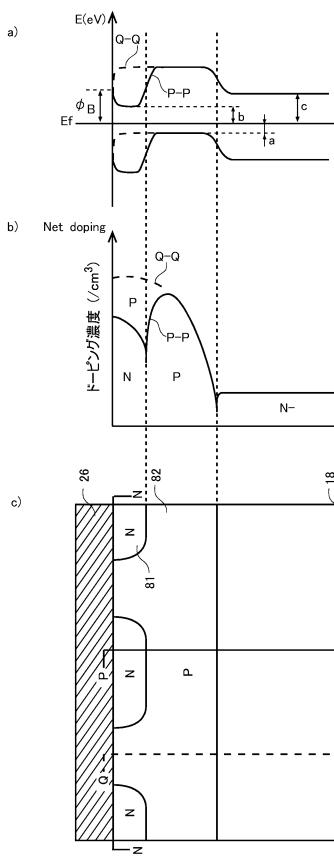

#### 【0201】

図9Aは、プレーナ型またはトレンチ型である半導体装置100の断面図の変形例を示す。本例の半導体装置100は、図1Aと異なる構造の第2アノード領域82を備える。本例では、図1Aと相違する点について説明する。本例の第2アノード領域82は、第2アノード領域82aおよび第2アノード領域82bを含む。

#### 【0202】

第2アノード領域82aは、おもて面21において、おもて面側電極26と接触していない領域である。本例の第2アノード領域82aの上方には、第1アノード領域81が設けられている。第2アノード領域82aの深さ方向の厚みは、第2アノード領域82とドリフト領域18とのPN接合で生じる空乏層が第1アノード領域81と接触しないように設定される。

#### 【0203】

第2アノード領域82bは、おもて面21において、おもて面側電極26と接触している領域である。本例の第2アノード領域82bは、隣り合う第1アノード領域81の間に設けられる。第2アノード領域82bのドーピング濃度は、同一の深さで比較した場合に、第2アノード領域82aのドーピング濃度よりも低くてよい。また、第2アノード領域82bの下端の深さは、第2アノード領域82aの下端の深さよりも浅くてよい。

#### 【0204】

上面視における半導体装置100のおもて面21の構造は、図1Aのおもて面21の構造と同様であってよい。即ち、本例の半導体装置100は、図1Bで示されたように、ストライプ状に設けられた第1アノード領域81および第2アノード領域82を備えてよい。また、半導体装置100は、図1Cで示されたように、円形の第2アノード領域82を複数有してもよい。

#### 【0205】

なお、本例の半導体装置100のおもて面21は、上面視において、他の実施例に係る半導体装置100のおもて面21の構造が適用されてよい。即ち、図9Aの構造は、図1Bおよび図1Cのようなプレーナ型である半導体装置100のみならず、図2Aおよび図3Aのようなトレンチ型である半導体装置100にも適用されてよい。本例の断面図は、トレンチ型である半導体装置100に適用される場合、トレンチ部の延伸方向に沿った断面の構造と同様であってよい。

10

20

30

40

50

【 0 2 0 6 】

部分 8 3 は、第 2 アノード領域 8 2 b の下端の深さ方向における最も浅い部分である。第 2 アノード領域 8 2 b の下端の最も浅い部分 8 3 は、上面視において、第 2 アノード領域 8 2 b の中央に位置してよい。例えば、第 1 アノード領域 8 1 および第 2 アノード領域 8 2 がストライプ状に設けられる場合、第 2 アノード領域 8 2 b の下端の最も浅い部分 8 3 は、ストライプが配列された方向における中心位置に設けられる。また、第 2 アノード領域 8 2 b が円形に設けられる場合、第 2 アノード領域 8 2 b の下端の最も浅い部分 8 3 は、第 2 アノード領域 8 2 b の円の中心位置に設けられてよい。言い換えると、第 2 アノード領域 8 2 b の最も浅い部分は、上面視において、隣り合う第 1 アノード領域 8 1 の中に位置してよい。

10

【 0 2 0 7 】

なお、本例においても、半導体装置 100 は、図 1A と同様に第 2 アノード領域 82 のおもて面 21 側に、コンタクト領域 84 を備えてよいし、備えなくてもよい。本例の半導体装置 100 は、コンタクト領域 84 を備えていない。

【 0 2 0 8 】

本例の半導体装置 100 は、第 2 アノード領域 82b とおもて面側電極 26 との接触面からの正孔の注入を抑制することができる。また、半導体装置 100 は、第 2 アノード領域 82 とドリフト領域 18 との P-N 接合で生じる空乏層のパンチスルーパーを防止することができる。したがって、半導体装置 100 は、ライフタイムキラーを有さないノンキラーダイオードであっても、逆回復電流を低減することができる。また、半導体装置 100 は、蓄積電荷 (Qrr) も低減して、ソフトリカバリー特性を実現できる。

20

〔 0 2 0 9 〕

図 9 B は、図 9 A に係る半導体装置 100 の深さ方向のドーピング濃度分布とエネルギー・バンド図の一例を示す。本例では、半導体装置 100 の断面図 f ) と、その深さ方向のドーピング濃度分布 e ) とエネルギー・バンド図 d ) とを示す。図 9 B の d ) ~ f ) の深さ方向の位置はそれぞれ対応している。図 9 B は、コンタクト領域 84 を備えない場合に対応している。同図は、半導体装置 100 の R - R 線および S - S 線におけるドーピング濃度分布およびエネルギー・バンド図の一例を示している。

( 0 2 1 0 )

R - R 線は、ドーピング濃度分布およびエネルギー・バンド図について、図 1 D の P - P 線と同一である。本例では、図 1 D の場合と相違する点について特に説明する。S - S 線は、第 2 アノード領域 8 2 b において、第 2 アノード領域 8 2 b の下端の最も浅い部分 8 3 を通過する断面に対応する。

30

[ 0 2 1 1 ]

バンド図 d ) の破線は、 S - S 線における熱平衡状態のバンド図を示す。第 2 アノード領域 8 2 b は、おもて面側電極 2 6 とオーミック接触している。第 2 アノード領域 8 2 b とドリフト領域 1 8 との境界は、第 2 アノード領域 8 2 a とドリフト領域 1 8 との境界よりも浅い位置に設けられている。

(0212)

ドーピング濃度分布 e ) の破線は、 S - S 線におけるドーピング濃度を示す。第 2 アノード領域 8 2 b のおもて面側電極 2 6 との接触面では、第 1 アノード領域 8 1 とおもて面側電極 2 6 との接触面よりも、ドーピング濃度が低くなっている。また、おもて面側電極 2 6 に接する第 2 アノード領域 8 2 b の最小ドーピング濃度は、第 1 アノード領域 8 1 のドーピング濃度よりも低い。第 2 アノード領域 8 2 b のドーピング濃度は、第 1 アノード領域 8 1 のドーピング濃度よりも低い。

40

〔 0 2 1 3 〕

第2アノード領域82bのドーピング濃度を低下させることにより、第2アノード領域82とおもて面側電極26との接触面からの正孔注入が減少する。一方、第1アノード領域81の下方においては、第2アノード領域82bよりも高いドーピング濃度の第2アノード領域82aが設けられているので、空乏層のパンチスルーや防止できる。

50

## 【0214】

図9Cは、図9Bのf)のT-T断面について、おもて面21のネット・ドーピング濃度分布を示す。図9Cも、コンタクト領域84を備えない場合に対応している。第1アノード領域81は、X軸方向に略平坦なドーピング濃度分布を有する。第1アノード領域81のドーピング濃度分布は、第2アノード領域82とのPN接合がおもて面21に露出する位置の近傍で減少する。

## 【0215】

第2アノード領域82は、X軸方向に沿って、中央部（即ち、第1アノード領域81に挟まれた中心部）で極小値を有するドーピング濃度分布を示す。第2アノード領域82のドーピング濃度分布は、中央部から、第1アノード領域81とのPN接合がおもて面21に露出する位置に向かって、極小値よりもドーピング濃度が増加した極大値を有する。第2アノード領域82のドーピング濃度分布は、極大値を示す位置から、第1アノード領域81とのPN接合がおもて面21に露出する位置に向かって、減少する。

10

## 【0216】

おもて面21における第1アノード領域81の最大ドーピング濃度は、おもて面21における第2アノード領域82のドーピング濃度の極小値よりも大きくてよい。おもて面21における第1アノード領域81の最大ドーピング濃度は、おもて面21における第2アノード領域82のドーピング濃度の極大値よりも大きくてよい。これにより、第2アノード領域82bとおもて面側電極26との接触面からの正孔の注入を抑制することができる。また、半導体装置100は、第2アノード領域82とドリフト領域18とのPN接合で生じる空乏層のパンチスルーや防止することができる。したがって、半導体装置100は、ライフトайムキラーを有さないノンキラーダイオードであっても、逆回復電流を低減することができる。また、半導体装置100は、蓄積電荷(Qrr)も低減して、ソフトリカバリー特性を実現できる。

20

## 【0217】

なお、コンタクト領域84を備える場合は、T-T断面を、コンタクト領域84と第2アノード領域82が接する深さよりも深い位置における断面としてよい。

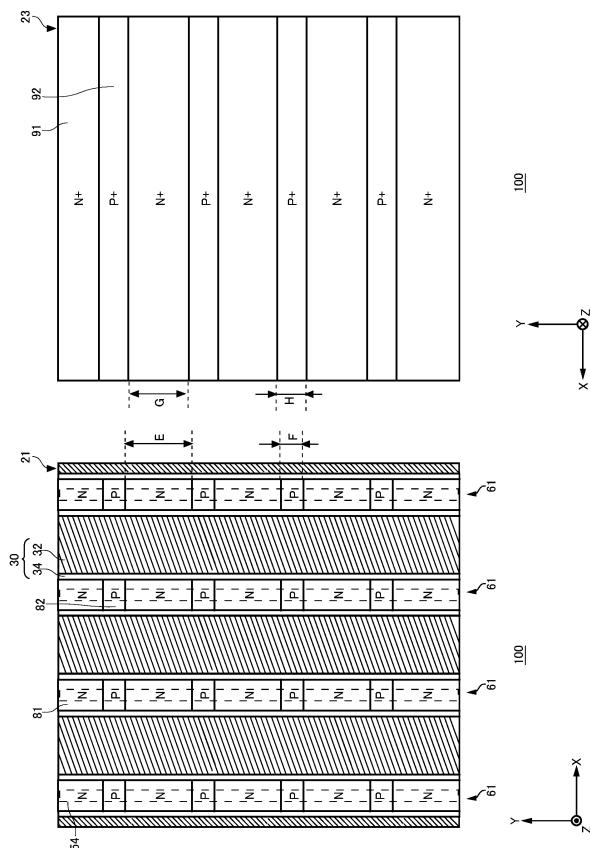

## 【0218】

図10は、おもて面21と裏面23の対応関係を説明するための図である。おもて面21の第1アノード領域81および第2アノード領域82は、裏面23の第1カソード領域91または第2カソード領域92と予め定められた位置関係となるように配置される。即ち、おもて面21の構造が裏面23の構造と対応づけられている。

30

## 【0219】

第1アノード領域81および第2アノード領域82は、メサ部61において、Y軸方向に沿って交互に配置されている。ダミートレンチ部30は、Y軸方向に延伸して設けられ、X軸方向に配列されている。第1カソード領域91および第2カソード領域92は、X軸方向に延伸して設けられ、Y軸方向に沿って交互に配置されている。

## 【0220】

第1アノード領域81は、第1カソード領域91と対応した位置に設けられる。第1アノード領域81の下方には、第1カソード領域91が設けられる。即ち、上面視において、第1アノード領域81が第1カソード領域91を覆っている。

40

## 【0221】

第2アノード領域82は、第2カソード領域92と対応した位置に設けられる。第2アノード領域82の下方には、第2アノード領域82よりも面積の大きな第2カソード領域92が設けられる。即ち、上面視において、第2カソード領域92が第2アノード領域82の周囲を覆っている。

## 【0222】

幅Eは、おもて面21の第1アノード領域81のY軸方向における幅である。幅Fは、おもて面21の第2アノード領域82のY軸方向における幅である。本例の幅Eは、幅Fよりも大きい。これにより、第2アノード領域82とおもて面側電極26との接触面から

50

の正孔の注入を抑制しやすくなる。

【0223】

幅Gは、裏面23の第1カソード領域91のY軸方向における幅である。幅Hは、裏面23の第2カソード領域92のY軸方向における幅である。本例の幅Gは、幅Hよりも大きい。幅Hは、幅Fよりも大きくてよい。幅Gは、幅Eよりも小さくてよい。これにより、裏面23からの電子の注入を抑制しやすくなる。

【0224】

本例の半導体装置100は、おもて面21と裏面23において、第1導電型の領域と第2導電型の領域とを対応づけている。半導体装置100は、第1導電型の領域と第2導電型の領域との比を適切に設定することにより、導電時において、おもて面21からの正孔注入と、裏面23からの電子注入を抑制することができる。

10

【0225】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【0226】

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

20

【符号の説明】

【0227】

10 . . . 半導体基板、11 . . . ウェル領域、12 . . . エミッタ領域、13 . . . 14 . . . ベース領域、15 . . . コンタクト領域、16 . . . 蓄積領域、18 . . . ドリフト領域、20 . . . バッファ領域、21 . . . おもて面、22 . . . コレクタ領域、23 . . . 裏面、25 . . . バリアメタル、26 . . . おもて面側電極、27 . . . 裏面側電極、28 . . . 接続部、29 . . . 直線部分、30 . . . ダミートレンチ部、31 . . . 先端部、32 . . . ダミー絶縁膜、34 . . . ダミー導電部、35 . . . 側壁領域、36 . . . 底部領域、38 . . . 層間絶縁膜、39 . . . 直線部分、40 . . . ゲートトレチ部、41 . . . 先端部、42 . . . ゲート絶縁膜、44 . . . ゲート導電部、50 . . . ゲート金属層、54 . . . コンタクトホール、60 . . . メサ部、61 . . . メサ部、65 . . . キラー、68 . . . レジスト、70 . . . トランジスタ部、80 . . . ダイオード部、81 . . . 第1アノード領域、82 . . . 第2アノード領域、83 . . . 部分、84 . . . コンタクト領域、90 . . . 裏面側カソード部、91 . . . 第1カソード領域、92 . . . 第2カソード領域、93 . . . おもて面側カソード部、94 . . . 開口、95 . . . カソード層、100 . . . 半導体装置

30

40

50

## 【図面】

## 【図 1 A】

## 【図 1 B】

10

20

## 【図 1 C】

## 【図 1 D】

30

40

50

【図 1 E】

【図 2 A】

10

20

【図 2 B】

30

40

【図 2 C】

50

【図 2 D】

【図 3 A】

10

20

【図 3 B】

【図 3 C】

30

40

E-E

F-F

50

【図 4 A】

【図 4 B】

10

20

【図 4 C】

【図 4 D】

30

40

50

### 【図 5 A】

【図5B】

【図5C】

【図5D】

10

20

30

40

50

Z

Y

X

10

Z

Y

X

20

30

40

50

【図 7 A】

【図 7 B】

【図 8】

【図 9 A】

10

20

30

40

50

【図 9 B】

【図9C】

【図10】

## フロントページの続き

## (51)国際特許分類

|                         | F I          |         |

|-------------------------|--------------|---------|

| H 01 L 29/78 (2006.01)  | H 01 L 29/06 | 3 0 1 F |

| H 01 L 21/336(2006.01)  | H 01 L 29/06 | 3 0 1 V |

| H 01 L 21/329(2006.01)  | H 01 L 29/78 | 6 5 5 G |

| H 01 L 21/8234(2006.01) | H 01 L 29/78 | 6 5 7 D |

| H 01 L 27/06 (2006.01)  | H 01 L 29/78 | 6 5 2 J |

|                         | H 01 L 29/78 | 6 5 3 A |

|                         | H 01 L 29/78 | 6 5 5 B |

|                         | H 01 L 29/78 | 6 5 8 H |

|                         | H 01 L 29/91 | J       |

|                         | H 01 L 29/78 | 6 5 5 D |

|                         | H 01 L 29/78 | 6 5 5 C |

|                         | H 01 L 29/78 | 6 5 8 A |

|                         | H 01 L 29/86 | 3 0 1 P |

|                         | H 01 L 29/91 | A       |

|                         | H 01 L 27/06 | 1 0 2 A |

|                         | H 01 L 29/78 | 3 0 1 D |

|                         | H 01 L 29/78 | 3 0 1 V |

## (56)参考文献

特開2014-135419(JP, A)

特開2019-125763(JP, A)

## (58)調査した分野 (Int.Cl. , DB名)

|                     |

|---------------------|

| H 01 L 29 / 8 6 1   |

| H 01 L 29 / 8 6 8   |

| H 01 L 29 / 8 7 2   |

| H 01 L 29 / 0 6     |

| H 01 L 29 / 7 3 9   |

| H 01 L 29 / 7 8     |

| H 01 L 21 / 3 3 6   |

| H 01 L 21 / 3 2 9   |

| H 01 L 21 / 8 2 3 4 |