(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

(43) International Publication Date

22 September 2005 (22.09.2005)

PCT

(10) International Publication Number

**WO 2005/088693 A1**

(51) International Patent Classification<sup>7</sup>: **H01L 21/311**

(21) International Application Number:

PCT/US2005/007386

(22) International Filing Date: 2 March 2005 (02.03.2005)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/798,456 10 March 2004 (10.03.2004) US

(71) Applicant (for all designated States except US): **LAM RESEARCH CORPORATION** [US/US]; 4650 Cushing Parkway, Fremont, CA 94438-6470 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): **CHOI, Youngjin** [KR/US]; 3025 Bolero Court, Pleasanton, CA 94588 (US). **ZHU, Helen, H.** [US/US]; 300 Tiffany Terrace, Fremont,

CA 94536 (US). **LEE, Sangheon** [KR/US]; 755 E. Capitol Ave. H-209, Milpitas, CA 95035 (US). **KANG, Sean, S.** [KR/US]; 4657 Rothbury Common, Fremont, CA 94536 (US).

(74) Agent: **LEE, Michael**; Beyer Weaver & Thomas, LLP, P.O. Box 07250, Oakland, CA 94612-0250 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH,

[Continued on next page]

(54) Title: LINE EDGE ROUGHNESS CONTROL

(57) Abstract: A method for etching a layer through a photoresist mask with an ARC layer between the layer to be etched and the photoresist mask over a substrate is provided. The substrate is placed into a processing chamber. An ARC open gas mixture is provided into the processing chamber. The ARC open gas mixture comprises an etchant gas and a polymerization gas comprising CO and CH<sub>3</sub>F. An ARC open plasma is formed from the ARC open gas mixture. The ARC layer is etched with the ARC open plasma until the ARC layer is opened. The ARC open gas mixture stopped before the layer to be etched is completely etched.

WO 2005/088693 A1

GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

**Published:**

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

## LINE EDGE ROUGHNESS CONTROL

### RELATED APPLICATIONS

This application is a continuation-in-part of U.S. Patent Application No.

5 10/170,424 (Attorney Docket No. P0930) which published as US 2003/0232504 A1, entitled "Process For Etching Dielectric Films With Improved Resist And/Or Etch Profile Characteristics," by Eppler et al. filed June 14, 2002, and which is incorporated by reference for all purposes.

### BACKGROUND OF THE INVENTION

10 1. Field of the Invention

The invention relates to semiconductor devices. More specifically, the invention relates to the production of semiconductor devices with reduced line edge roughness.

2. Description of the related art

In the formation of semiconductor devices, line edge roughening increases the 15 critical dimensions of the devices. In addition, uneven etching results across a wafer surface may further increase critical dimensions.

### SUMMARY OF THE INVENTION

To achieve the foregoing and in accordance with the purpose of the present invention, a method for etching a layer through a photoresist mask with an ARC layer 20 between the layer to be etched and the photoresist mask over a substrate is provided. The substrate is placed into a processing chamber. An ARC open gas mixture is provided into the processing chamber. The ARC open gas mixture comprises an etchant gas and a polymerization gas comprising CO and CH<sub>3</sub>F. An ARC open plasma is formed from the ARC open gas mixture. The ARC layer is etched with the 25 ARC open plasma until the ARC layer is opened. The ARC open gas mixture stopped before the layer to be etched is completely etched.

In another manifestation of the invention a method for forming a 30 semiconductor device is provided. A layer to be etched is placed over a substrate. An organic ARC layer is formed over the layer to be etched. A photoresist mask is formed over the ARC layer. The substrate into is placed into a processing chamber. An ARC open gas mixture is provided into the processing chamber. The ARC open gas mixture comprises an etchant gas and a polymerization gas comprising CO and CH<sub>3</sub>F. An ARC open plasma is formed from the ARC open gas mixture. The ARC

layer is etched with the ARC open plasma until the ARC layer is opened. The ARC open gas mixture is stopped, so that none of the layer to be etched is etched by the ARC open plasma. An etch plasma different than the ARC open plasma is provided. The layer to be etched is etched with the etch plasma.

5 These and other features of the present invention will be described in more details below in the detailed description of the invention and in conjunction with the following figures.

#### BRIEF DESCRIPTION OF THE DRAWINGS

10 The present invention is illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings and in which like reference numerals refer to similar elements and in which:

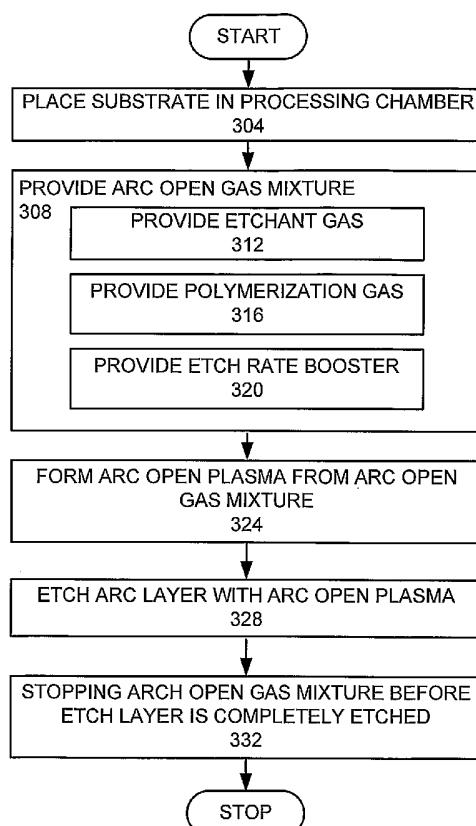

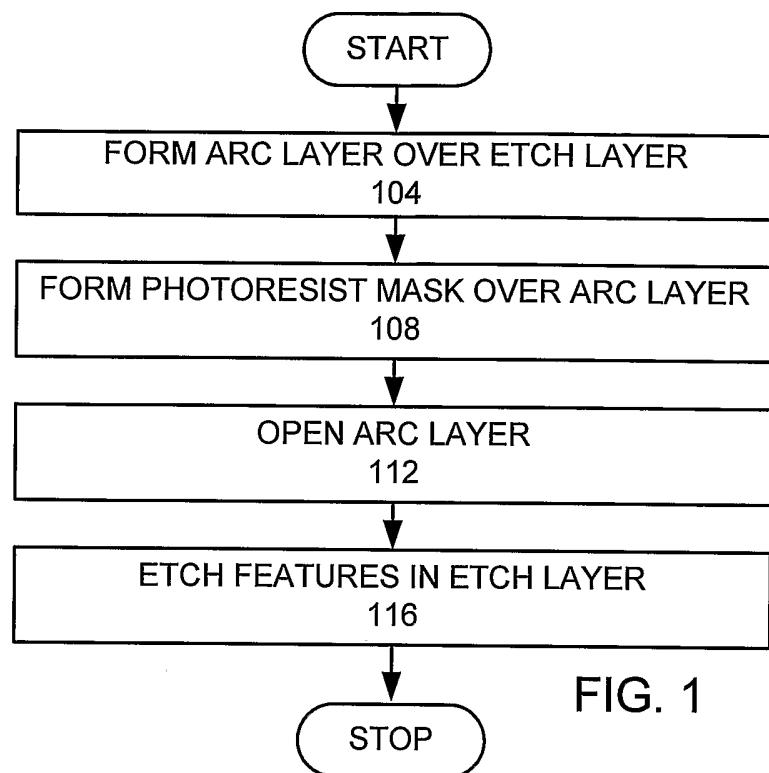

FIG. 1 is a high level flow chart for forming a feature in a dielectric layer, which uses an inventive antireflective coating (ARC) open process.

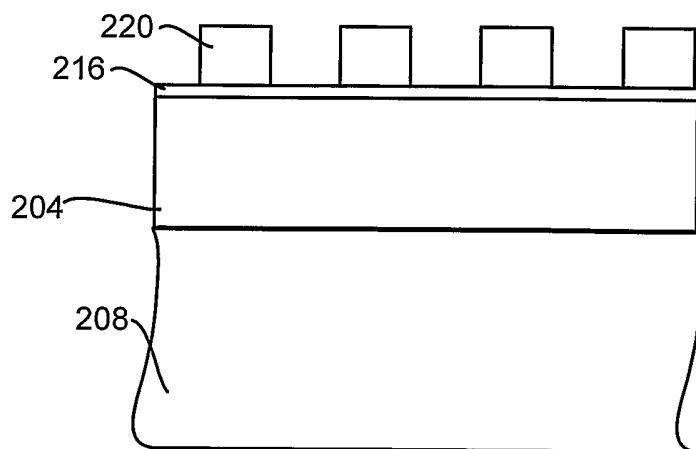

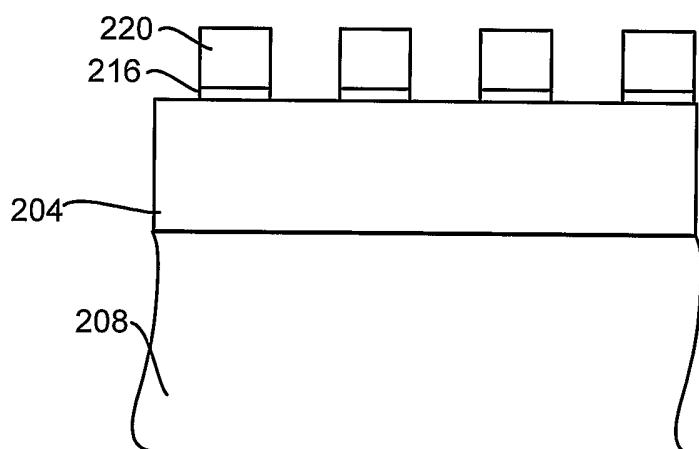

15 FIG.'s 2A-C are cross-sectional views of an etch layer over a substrate during the formation of features using the inventive ARC open process.

FIG. 3 is a more detailed flow chart of a step of the opening of the ARC layer.

FIG. 4 is a schematic view of a process chamber that may be used in a preferred embodiment of the invention.

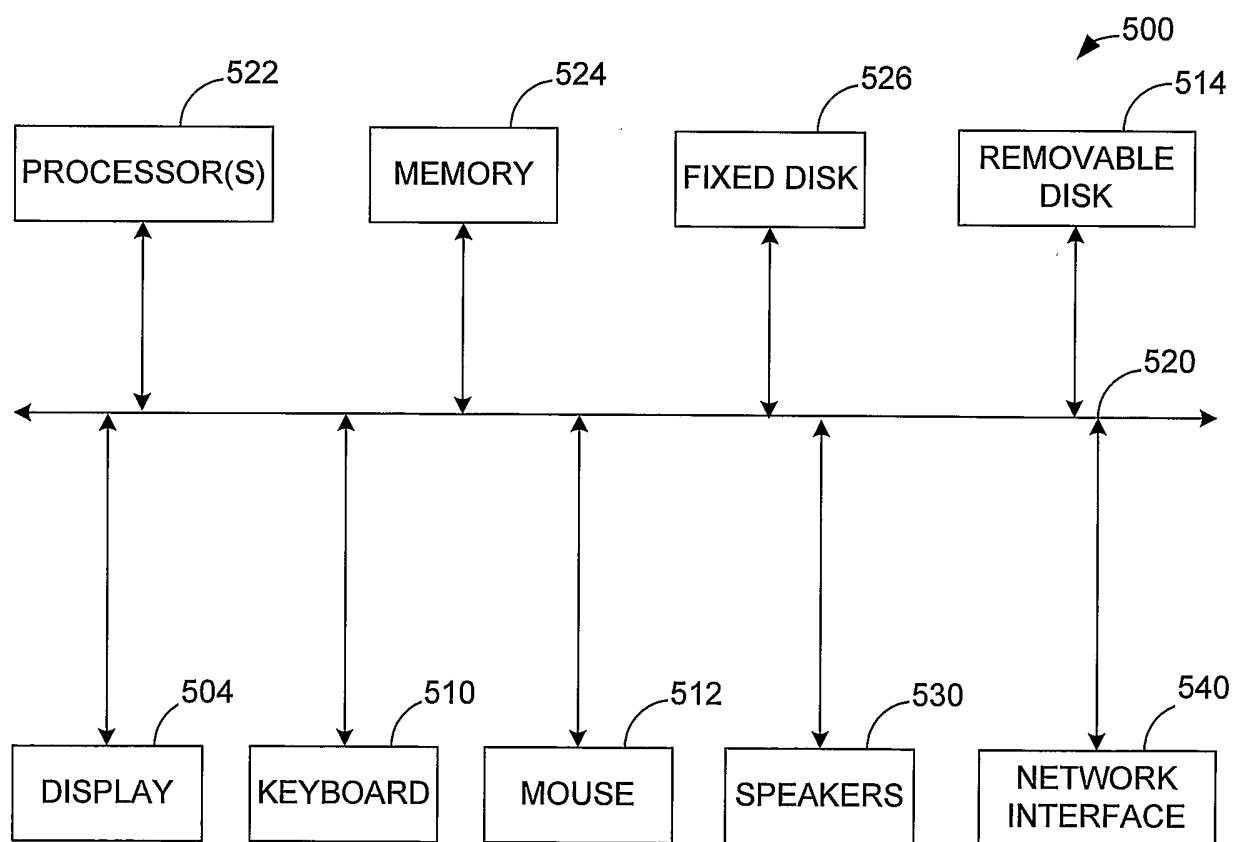

20 FIG.'s 5A and 5B illustrate a computer system, which is suitable for implementing a controller.

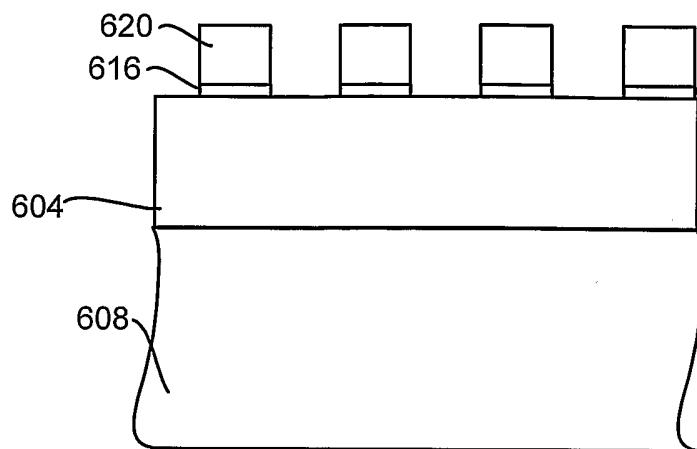

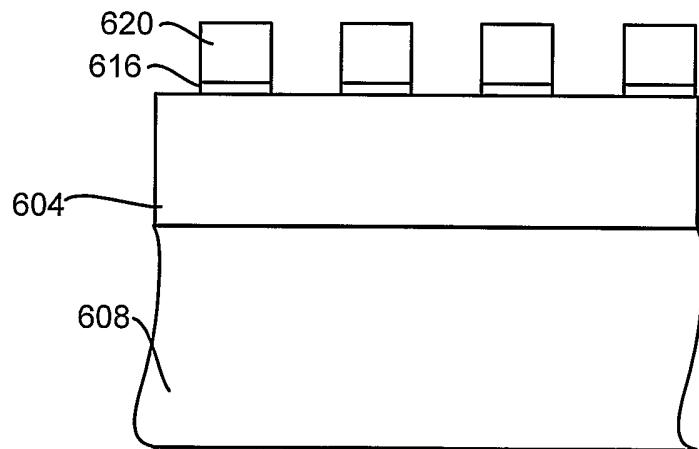

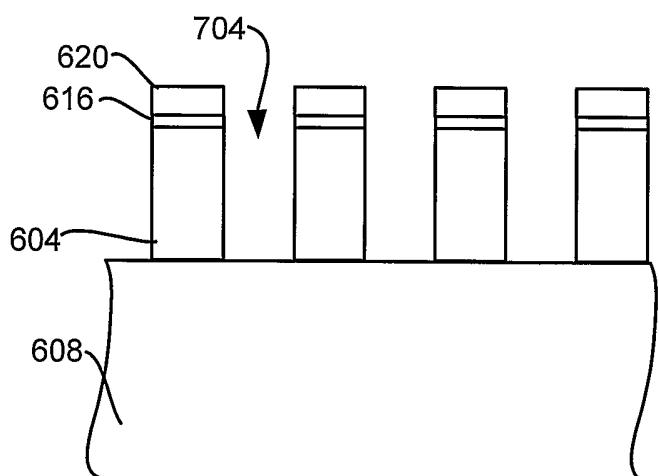

FIG.'s 6A-B are cross-sectional views of an etch layer over a substrate after an ARC opening is performed.

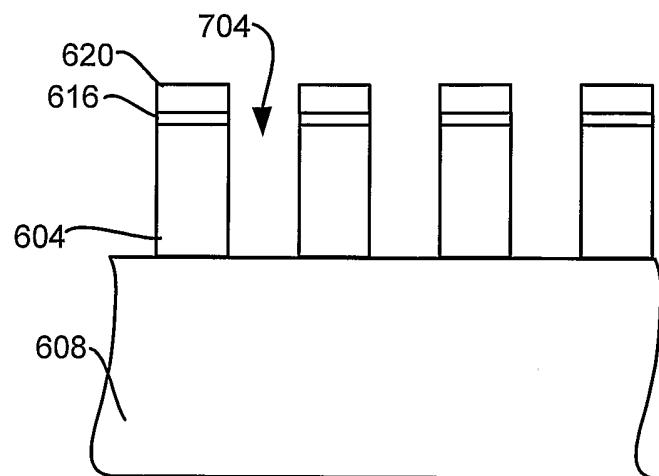

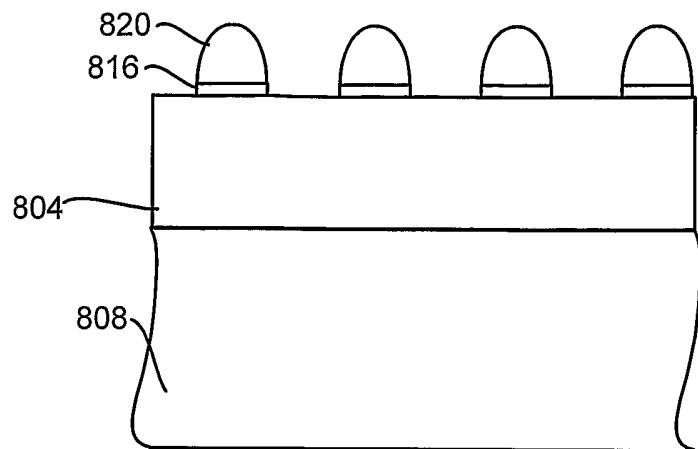

FIG.'s 7A-B are cross-sectional views of an etch layer over a substrate after features have been etched into the etch layer.

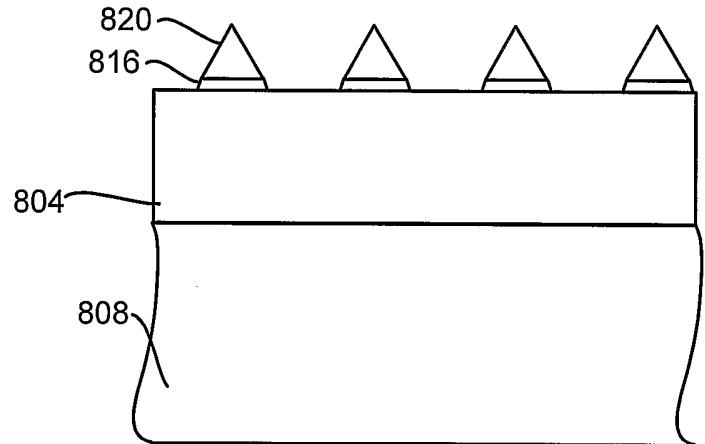

25 FIG.'s 8A-B are cross-sectional views of an etch layer over a substrate after an ARC opening is performed using a prior art ARC open process.

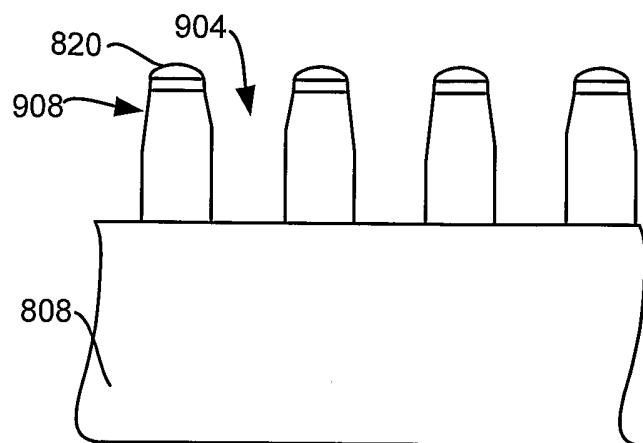

FIG.'s 9A-B are cross-sectional views of an etch layer over a substrate after features have been etched into the etch layer after a prior art ARC open process has been used.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The present invention will now be described in detail with reference to a few preferred embodiments thereof as illustrated in the accompanying drawings. In the following description, numerous specific details are set forth in order to provide a

thorough understanding of the present invention. It will be apparent, however, to one skilled in the art, that the present invention may be practiced without some or all of these specific details. In other instances, well known process steps and/or structures have not been described in detail in order to not unnecessarily obscure the present

5 invention.

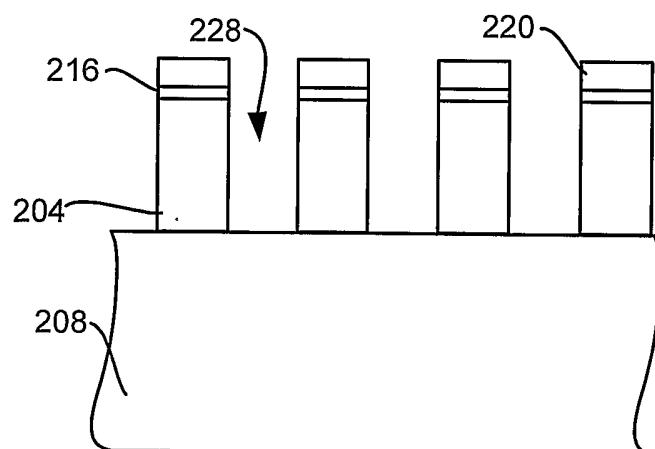

To facilitate understanding. FIG. 1 is a high level flow chart for forming a feature in a dielectric layer, which uses the inventive antireflective coating (ARC) open process. An ARC layer is formed over an etch layer, which is a layer to be etched (step 104). FIG. 2A is a cross-sectional view of an etch layer 204 over a

10 substrate 208. An ARC layer 216 has been formed over the etch layer 204. A photoresist mask 220 is formed over the ARC layer 216 (step 108). The ARC layer is opened (step 112). FIG. 2B is a cross-sectional view of the ARC layer 216 after it is opened. Features 228 are then etched into the etch layer 212 through the photoresist mask 220 and the ARC layer 216, as shown in FIG. 2C. The photoresist mask 220

15 and ARC layer 216 may be completely removed during a subsequent photoresist stripping process.

Although the etch layer 204 is shown as being on top of the substrate 208, one or more layers may be between the etch layer 204 and the substrate 208.

Alternatively, the substrate may be the etch layer.

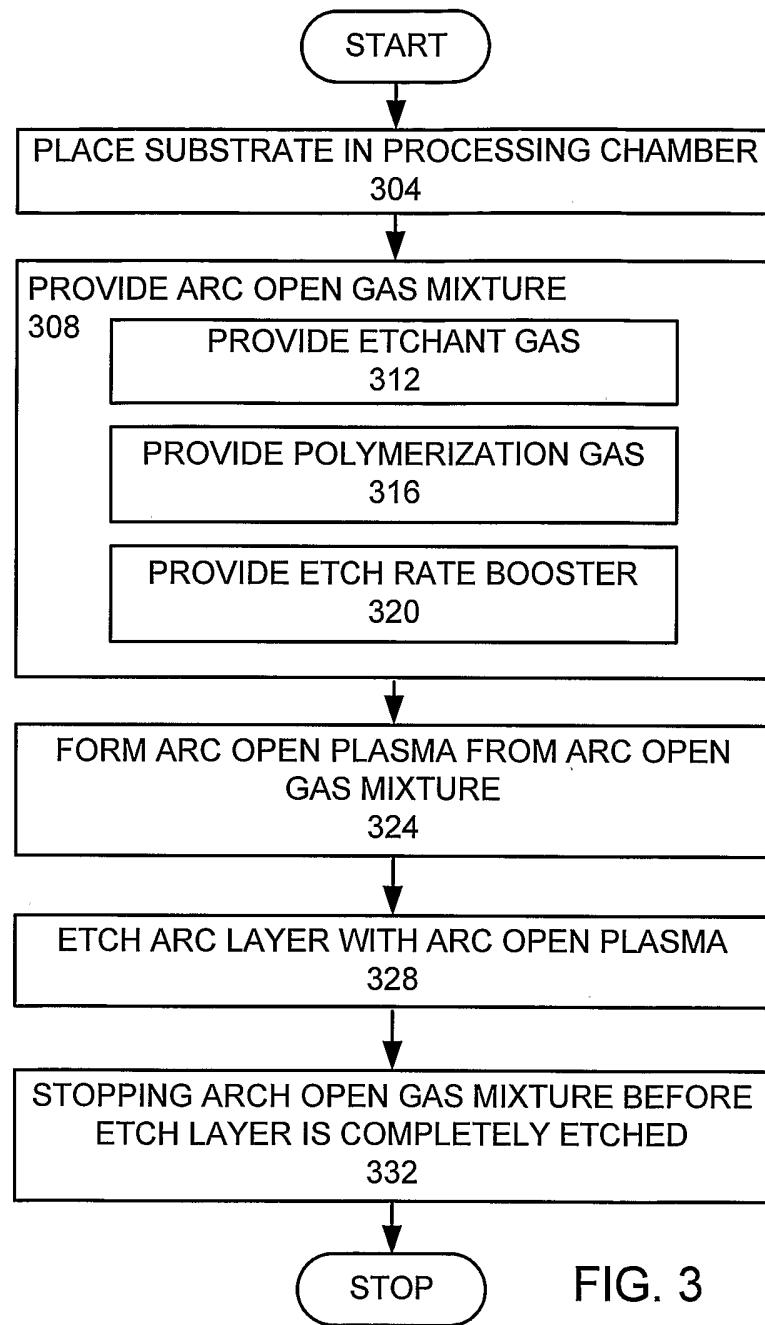

20 FIG. 3 is a more detailed flow chart of the step of opening the ARC layer (step 112). The substrate is placed in a processing chamber (step 304). This step may occur before the step of opening the ARC layer (step 112). An ARC open gas mixture is provided into the processing chamber (step 308). This step comprises providing an etchant gas to the processing chamber (step 312), providing a

25 polymerization gas to the processing chamber (step 316), and providing an etch rate booster to the processing chamber (step 320). The polymerization gas is CO and CH<sub>3</sub>F. The etch rate booster is O<sub>2</sub>.

#### Example

30 In an example of the invention, the etch layer 204 is a silicon oxide dielectric layer over a silicon wafer substrate 208. The ARC layer is a bottom antireflective coating (BARC), which is an organic ARC material. It is preferred that BARC be similar to photoresist, so that the BARC have similar stripping characteristics. In other embodiments, the ARC layer may be made of other organic

5 materials to form an organic ARC layer. The photoresist mask 220 is made of 193 photoresist. In other examples the photoresist mask may be of 193 and higher generation photoresist masks. Such mask materials may be soft and therefore cause line edge roughening or non-uniform etching. The invention is able to compensate for such soft photoresist materials.

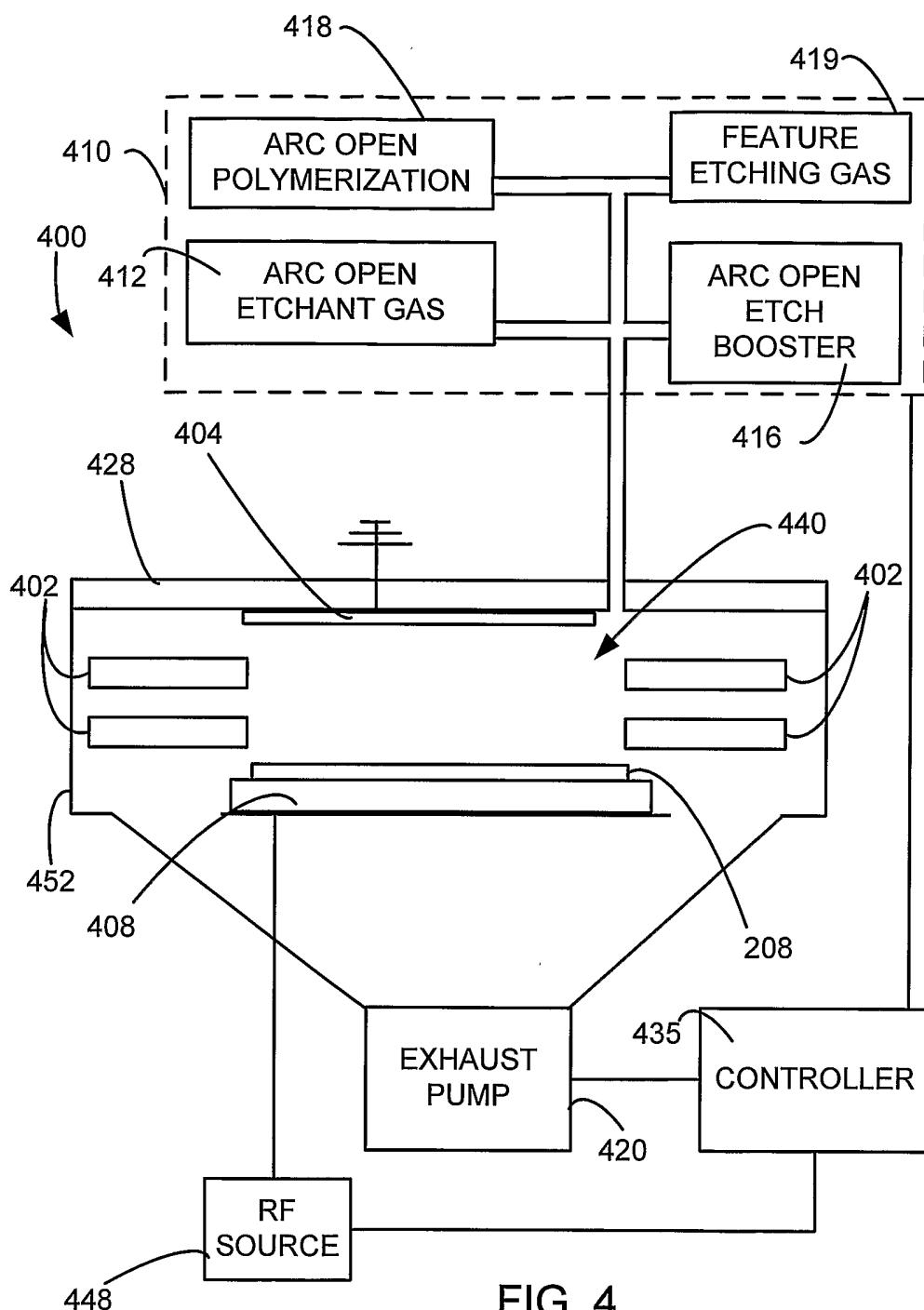

FIG. 4 is a schematic view of a plasma processing chamber 400 that may be used for opening the ARC layer and etching the features in this example. The plasma processing chamber 400 comprises confinement rings 402, an upper electrode 404, a lower electrode 408, a gas source 410, and an exhaust pump 420. For the ARC 10 opening step, the gas source 410 comprises an ARC open etchant gas source 412, an ARC open etch booster gas source 418, an ARC open polymerization gas source 418, and an gas source for etching features in the etch layer 419, if the features are etched in the same process chamber. The gas source 410 may comprise additional gas sources. Within plasma processing chamber 400, the substrate 208 is positioned upon 15 the lower electrode 408. The lower electrode 408 incorporates a suitable substrate chucking mechanism (e.g., electrostatic, mechanical clamping, or the like) for holding the substrate 208. The reactor top 428 incorporates the upper electrode 404 disposed immediately opposite the lower electrode 408. The upper electrode 404, lower electrode 408, and confinement rings 402 define the confined plasma volume. Gas is 20 supplied to the confined plasma volume by the gas source 410 and is exhausted from the confined plasma volume through the confinement rings 402 and an exhaust port by the exhaust pump 420. An RF source 448 is electrically connected to the lower electrode 408. The upper electrode 404 is grounded. Chamber walls 452 surround the confinement rings 402, the upper electrode 404, and the lower electrode 408. The RF 25 source 448 may comprise a 27 MHz power source and a 2 MHz power source. An Exelan 2300™, which is made by LAM Research Corporation™ of Fremont, California, was used in this example of the invention. Different combinations of connecting RF power to the electrode are possible in other embodiments, such as having an RF source connected to the upper electrode 404.

30 FIG.'s 5A and 5B illustrate a computer system 500, which is suitable for implementing a controller 435 used in embodiments of the present invention. FIG. 5A shows one possible physical form of the computer system. Of course, the computer system may have many physical forms ranging from an integrated circuit, a

printed circuit board, and a small handheld device up to a huge super computer. Computer system 500 includes a monitor 502, a display 504, a housing 506, a disk drive 508, a keyboard 510, and a mouse 512. Disk 514 is a computer-readable medium used to transfer data to and from computer system 500.

5 FIG. 5B is an example of a block diagram for computer system 500. Attached to system bus 520 is a wide variety of subsystems. Processor(s) 522 (also referred to as central processing units or CPUs) are coupled to storage devices, including memory 524. Memory 524 includes random access memory (RAM) and read-only memory (ROM). As is well known in the art, ROM acts to transfer data and instructions unidirectionally to the CPU and RAM is used typically to transfer data and instructions in a bi-directional manner. Both of these types of memories may include any suitable of the computer-readable media described below. A fixed disk 526 is also coupled bi-directionally to CPU 522; it provides additional data storage capacity and may also include any of the computer-readable media described below. Fixed disk 526 may be used to store programs, data, and the like and is typically a secondary storage medium (such as a hard disk) that is slower than primary storage. It will be appreciated that the information retained within fixed disk 526 may, in appropriate cases, be incorporated in standard fashion as virtual memory in memory 524. Removable disk 514 may take the form of any of the computer-readable media described below.

10

15

20 CPU 522 is also coupled to a variety of input/output devices, such as display 504, keyboard 510, mouse 512 and speakers 530. In general, an input/output device may be any of: video displays, track balls, mice, keyboards, microphones, touch-sensitive displays, transducer card readers, magnetic or paper tape readers, tablets, styluses, voice or handwriting recognizers, biometrics readers, or other computers.

25 CPU 522 optionally may be coupled to another computer or telecommunications network using network interface 540. With such a network interface, it is contemplated that the CPU might receive information from the network, or might output information to the network in the course of performing the above-described method steps. Furthermore, method embodiments of the present invention may 30 execute solely upon CPU 522 or may execute over a network such as the Internet in conjunction with a remote CPU that shares a portion of the processing.

In addition, embodiments of the present invention further relate to computer storage products with a computer-readable medium that have computer code thereon

for performing various computer-implemented operations. The media and computer code may be those specially designed and constructed for the purposes of the present invention, or they may be of the kind well known and available to those having skill in the computer software arts. Examples of computer-readable media include, but are not limited to: magnetic media such as hard disks, floppy disks, and magnetic tape; optical media such as CD-ROMs and holographic devices; magneto-optical media such as floptical disks; and hardware devices that are specially configured to store and execute program code, such as application-specific integrated circuits (ASICs), programmable logic devices (PLDs) and ROM and RAM devices. Examples of computer code include machine code, such as produced by a compiler, and files containing higher level code that are executed by a computer using an interpreter. Computer readable media may also be computer code transmitted by a computer data signal embodied in a carrier wave and representing a sequence of instructions that are executable by a processor.

15        In this example, for the ARC open the etchant gas comprises 75 sccm N<sub>2</sub> and 50 sccm H<sub>2</sub>. The ARC open polymerization gas comprises 200 sccm CO and 6 sccm CH<sub>3</sub>F. The ARC open etch booster gas comprises 3 sccm O<sub>2</sub>. The chamber pressure is set to 260 mTorr. The power provided by the lower electrode is 0 Watts at 27 MHz and 600 Watts at 2 MHz. The power provided during this step is kept low to reduce 20 the removal of any of the photoresist mask 220. This ARC open gas mixture which uses H<sub>2</sub> and N<sub>2</sub> as the ARC open etchant gases is highly selective for etching BARC with respect to silicon oxide. This high selectivity is defined as being greater than 20:1. More preferably, the ARC open etch to silicon oxide selectivity is greater than 50:1. Most preferably, the ARC open selectivity is greater than infinity, so that there 25 is no etching of the silicon oxide during the ARC open. Preferably, the lower electrode is kept at a temperature between -20° and 40° C .

FIG. 6A is a schematic cross-sectional view of a part of an etch layer near the center of a wafer after ARC opening is performed using this example. FIG. 6B is a schematic cross-sectional view of a part of an etch layer near the edge of a wafer after 30 ARC opening is performed using this example. The photoresist mask 620 is protected to minimize damage to the photoresist mask 620 near both the center and edge of the wafer, to increase uniformity.

Using the structures shown in FIG. 6A and FIG. 6B, features may be etched into the etch layer, which may result in features 704 as illustrated in FIG. 7A and FIG. 7B, where FIG. 7A is a schematic cross-sectional view of a part of an etch layer near the center of a wafer after a features are etched in the layer and FIG. 7B is a schematic cross-sectional view of a part of an etch layer near the edge of a wafer. The inventive 5 ARC open allows the formation of more uniform features and reduces line edge roughness.

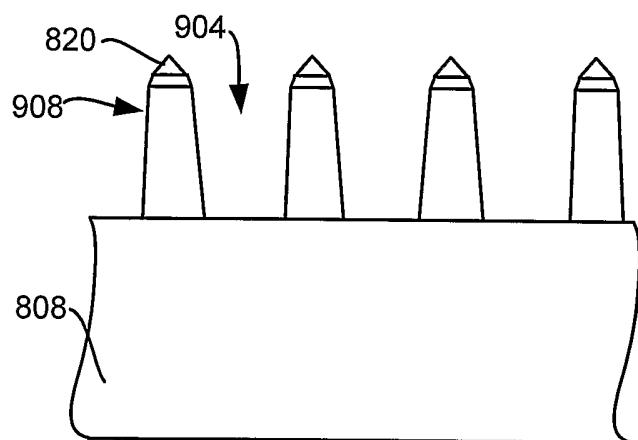

FIG. 8A is a schematic cross-sectional view of a part of an etch layer 804 over a substrate 808 near the center of a wafer after ARC opening is performed using a prior 10 art process. FIG. 8B is a schematic cross-sectional view of a part of an etch layer near the edge of a wafer after ARC opening is performed using a prior art process. Part of the photoresist mask 820 over an ARC layer 816 has been removed during the ARC open process. This is illustrated by the non-rectangular cross-sectional view of the parts of the photoresist mask 820 for both the center and the edge of the wafer, as 15 shown in FIG. 8A and FIG. 8B. In addition, the erosion of the photoresist during the ARC open process of this example of the prior art is not uniform between the center of the wafer and the edge of the wafer. This is illustrated by the difference in the cross-sectional views of the photoresist mask 820 between the center of the wafer, shown in FIG. 8A, and the edge of the wafer, shown in FIG. 8B. In this example of 20 the prior art, more of the photoresist mask is eroded near the edge of the wafer than the center of the wafer.

Using the structures shown in FIG. 8A and FIG. 8B, features may be etched into the etch layer, which may result in features 904 as illustrated in FIG. 9A and FIG. 9B, where FIG. 9A is a schematic cross-sectional view of a part of an etch layer near the center of a wafer after a features are etched in the etch layer and FIG. 9B is a schematic cross-sectional view of a part of an etch layer near the edge of a wafer. The erosion of the photoresist near the center of the wafer causes some line edge 25 roughening 908 on the sides of the features 904, as shown in FIG. 9A. The increased erosion of the photoresist near the edge of the wafer causes increased line edge 30 roughening 912 on the sides of the features 904, causing less uniform etch results over the surface of the wafer.

Preferably, the ARC layer is an organic material, since the preferred ARC open recipe is known to open layers of organic material. Therefore, BARC, which is

an organic ARC, is used in the preferred embodiment of the invention. The inventive ARC open is able to slowly etch an organic ARC such as BARC, but since the ARC is thin, the slow etch is sufficient. The inventive ARC open recipe is not able etch inorganic layers or etches inorganic silicon based layers so much slower than organic 5 layers that attempting to etch a thin ARC inorganic layer may be too time consuming. Having an etch that is able to etch an organic layer but unable to etch an inorganic layer at a desirable speed allows for the high etch selectivity for etching an organic ARC over an inorganic dielectric layer.

Table 1 provides preferred, more preferred, and most preferred ranges for the 10 break through etch.

Table 1

|                                 | Preferred Range | More Preferred | Most Preferred |

|---------------------------------|-----------------|----------------|----------------|

| N <sub>2</sub>                  | 30-110 sccm     | 50-90 sccm     | 60-80 sccm     |

| H <sub>2</sub>                  | 20-80 sccm      | 30-70 sccm     | 40-60 sccm     |

| CO                              | 50-500 sccm     | 100-400 sccm   | 150-300 sccm   |

| CH <sub>3</sub> F               | 1-16 sccm       | 2-10 sccm      | 4-8 sccm       |

| 27 MHz Power                    | 0-1000 Watts    | 0-500 Watts    | 0-200 Watts    |

| 2 MHz Power                     | 100-1000 Watts  | 100-600 Watts  | 200-600 Watts  |

| Pressure                        | 50-500 mTorr    | 100-400 mTorr  | 200-300 mTorr  |

| Flow ratio CO:CH <sub>3</sub> F | 70:1-20:1       | 60:1-30:1      | 50:1-40:1      |

| Temperature                     | 20° C           | 20° C          | 20° C          |

While this invention has been described in terms of several preferred 15 embodiments, there are alterations, permutations, modifications and various substitute equivalents, which fall within the scope of this invention. It should also be noted that there are many alternative ways of implementing the methods and apparatuses of the present invention. It is therefore intended that the following appended claims be interpreted as including all such alterations, permutations, modifications, and various substitute equivalents as fall within the true spirit and scope of the present invention.

## CLAIMS

What is claimed is:

1. A method for etching a layer through a photoresist mask with an ARC layer between the layer to be etched and the photoresist mask over a substrate, comprising:

- 5 placing the substrate into a processing chamber;

- providing an ARC open gas mixture into the processing chamber, wherein the ARC open gas mixture comprises:

- an etchant gas; and

- a polymerization gas comprising CO and CH<sub>3</sub>F;

- 10 forming an ARC open plasma from the ARC open gas mixture;

- etching the ARC layer with the ARC open plasma until the ARC layer is opened; and

- stopping the ARC open gas mixture before the layer to be etched is completely etched.

- 15 2. The method, as recited in claim 1, wherein ARC open plasma highly selectively etches the ARC with respect to the layer to be etched.

3. The method, as recited in any of claims 1-2, wherein the flow rate of CO is at least 150 sccm.

4. The method, as recited in any of claims 1-3, wherein the ARC open gas

- 20 mixture further comprises an etch rate booster, wherein the etch rate booster is O<sub>2</sub>.

5. The method, as recited in any of claims 1-4, wherein the layer to be etched is a dielectric layer and wherein the etchant gas comprises at least one of an N<sub>2</sub> and H<sub>2</sub> mixture and CF<sub>4</sub>.

6. The method, as recited in any of claims 1-5, further comprising providing a

- 25 photoresist mask over the stack.

7. The method, as recited in any of claims 1-6, wherein the photoresist mask is of a 193 or higher generation photoresist.

8. The method, as recited in any of claims 1-7, wherein the ARC layer is of an organic material.

- 30 9. The method, as recited in any of claims 1-8, wherein the ARC layer is of an organic material and wherein the photoresist mask is of a 193 or higher generation photoresist.

10. The method, as recited in any of claims 1-9, wherein the ARC open plasma

etches the ARC with respect to the layer to be etched with a selectivity greater than 50:1.

11. The method, as recited in any of claims 1-10, wherein the layer to be etched is silicon oxide.

5 12. The method, as recited in any of claims 1-11, wherein the ARC open plasma does not etch the layer to be etched.

13. A semiconductor device formed by the method of any of claims 1-12.

14. An apparatus with computer readable media for performing the method of any of claims 1-12.

10 15. A method for forming a semiconductor device, comprising:

placing a layer to be etched over a substrate;

forming an organic ARC layer over the layer to be etched;

forming a photoresist mask over the ARC layer;

placing the substrate into a processing chamber;

15 providing an ARC open gas mixture into the processing chamber, wherein the ARC open gas mixture comprises:

an etchant gas; and

a polymerization gas comprising CO and CH<sub>3</sub>F;

forming an ARC open plasma from the ARC open gas mixture;

20 etching the ARC layer with the ARC open plasma until the ARC layer is opened;

stopping the ARC open gas mixture, so that none of the layer to be etched is etched by the ARC open plasma;

providing an etch plasma different than the ARC open plasma; and

25 etching the layer to be etched with the etch plasma.

16. The method, as recited in claim 15, wherein the ARC open gas mixture further comprises an etch rate booster, wherein the etch rate booster is O<sub>2</sub>.

17. The method, as recited in any of claims 15-16, wherein the layer to be etched is a dielectric layer and wherein the etchant gas for providing ARC open comprises at 30 least one of an N<sub>2</sub> and H<sub>2</sub> mixture and CF<sub>4</sub>.

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 3

FIG. 4

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 8A (PRIOR ART)

FIG. 8B (PRIOR ART)

FIG. 9A (PRIOR ART)

FIG. 9B (PRIOR ART)

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2005/007386

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L21/311

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, INSPEC, CHEM ABS Data, PAJ

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                        | Relevant to claim No.                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| P, X       | US 2004/171260 A1 (CHOI YOUNGJIN ET AL)<br>2 September 2004 (2004-09-02)<br>the whole document<br>-----<br>X US 6 080 662 A (CHEN ET AL)<br>27 June 2000 (2000-06-27)<br>column 3<br>-----<br>X PATENT ABSTRACTS OF JAPAN<br>vol. 2003, no. 09,<br>3 September 2003 (2003-09-03)<br>-& JP 2003 133287 A (MATSUSHITA ELECTRIC<br>IND CO LTD; MITSUBISHI ELECTRIC CORP),<br>9 May 2003 (2003-05-09)<br>abstract; claims 1,4,5<br>paragraphs '0028! - '0075!<br>-----<br>-/- | 1-17<br><br>1-4,6,7,<br>10,12-14<br><br>1,3-7,<br>11,13,14 |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

° Special categories of cited documents :

- °A° document defining the general state of the art which is not considered to be of particular relevance

- °E° earlier document but published on or after the international filing date

- °L° document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- °O° document referring to an oral disclosure, use, exhibition or other means

- °P° document published prior to the international filing date but later than the priority date claimed

- °T° later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- °X° document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- °Y° document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- °&° document member of the same patent family

Date of the actual completion of the international search

21 July 2005

Date of mailing of the international search report

29/07/2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Szarowski, A

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2005/007386

## C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                       | Relevant to claim No. |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 2003/181054 A1 (LEE SUNG-KWON ET AL)<br>25 September 2003 (2003-09-25)<br>paragraphs '0032! - '0055!; figures 2a-2e                                                                                                                   | 13                    |

| A        | -----                                                                                                                                                                                                                                    | 1-12,<br>14-17        |

| X        | WO 2004/003988 A (TOKYO ELECTRON LIMITED;<br>YAMAGUCHI, TOMOYO; FUSE, TAKASHI;<br>FUJIMOTO, KI) 8 January 2004 (2004-01-08)<br>page 49, line 11 - page 56, line 10                                                                       | 13                    |

| A        | -----                                                                                                                                                                                                                                    | 1-12,<br>14-17        |

| E        | -& US 2005/103748 A1 (YAMAGUCHI TOMOYO ET<br>AL) 19 May 2005 (2005-05-19)<br>paragraphs '0210! - '0237!                                                                                                                                  | 13                    |

| A        | -----                                                                                                                                                                                                                                    | 1-17                  |

| P, A     | WO 03/030237 A (TOKYO ELECTRON LIMITED;<br>HARADA, AKITOSHI; INAZAWA, KOICHIRO)<br>10 April 2003 (2003-04-10)<br>pages 8-9<br>-& US 2004/209469 A1 (HARADA AKITOSHI ET<br>AL) 21 October 2004 (2004-10-21)<br>paragraphs '0035! - '0038! | 1-17                  |

|          | -----                                                                                                                                                                                                                                    |                       |

**INTERNATIONAL SEARCH REPORT**

formation on patent family members

International Application No

PCT/US2005/007386

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |    | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|----|------------------|

| US 2004171260                          | A1 | 02-09-2004       | US | 2003232504              | A1 | 18-12-2003       |

|                                        |    |                  | AU | 2003251519              | A1 | 31-12-2003       |

|                                        |    |                  | EP | 1518265                 | A2 | 30-03-2005       |

|                                        |    |                  | WO | 03107410                | A2 | 24-12-2003       |

| US 6080662                             | A  | 27-06-2000       |    | NONE                    |    |                  |

| JP 2003133287                          | A  | 09-05-2003       |    | NONE                    |    |                  |

| US 2003181054                          | A1 | 25-09-2003       | KR | 2003049908              | A  | 25-06-2003       |

| WO 2004003988                          | A  | 08-01-2004       | AU | 2003244166              | A1 | 19-01-2004       |

|                                        |    |                  | WO | 2004003988              | A1 | 08-01-2004       |

|                                        |    |                  | US | 2005103748              | A1 | 19-05-2005       |

| US 2005103748                          | A1 | 19-05-2005       | AU | 2003244166              | A1 | 19-01-2004       |

|                                        |    |                  | WO | 2004003988              | A1 | 08-01-2004       |

| WO 03030237                            | A  | 10-04-2003       | JP | 2003100718              | A  | 04-04-2003       |

|                                        |    |                  | WO | 03030237                | A1 | 10-04-2003       |

|                                        |    |                  | US | 2004209469              | A1 | 21-10-2004       |

| US 2004209469                          | A1 | 21-10-2004       | JP | 2003100718              | A  | 04-04-2003       |

|                                        |    |                  | WO | 03030237                | A1 | 10-04-2003       |